(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6433655号

(P6433655)

(45) 発行日 平成30年12月5日(2018.12.5)

(24) 登録日 平成30年11月16日(2018.11.16)

(51) Int.Cl.

F 1

H03K 19/173 (2006.01)

H01L 21/82 (2006.01)H03K 19/173 130

H01L 21/82 A

請求項の数 5 (全 42 頁)

(21) 出願番号 特願2013-260256 (P2013-260256)

(22) 出願日 平成25年12月17日 (2013.12.17)

(65) 公開番号 特開2014-143680 (P2014-143680A)

(43) 公開日 平成26年8月7日 (2014.8.7)

審査請求日 平成28年11月28日 (2016.11.28)

(31) 優先権主張番号 特願2012-280383 (P2012-280383)

(32) 優先日 平成24年12月24日 (2012.12.24)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 黒川 義元

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 及川 尚人

最終頁に続く

(54) 【発明の名称】プログラマブルロジックデバイス及び半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1配線と、

前記第1配線に直接接続される回路と、

前記回路に直接接続される第2配線と、

前記第1配線に直接接続される第1プログラマブルロジックエレメントと、

前記第2配線に直接接続される第2プログラマブルロジックエレメントと、を有し、

第1の期間において、前記第1配線に、コンフィギュレーションデータが供給される機能と、第2の期間において、前記第1配線に、第1プログラマブルロジックエレメントから出力される信号が供給される機能と、を有し、

前記回路は、それぞれ、第1スイッチと、第2スイッチと、第3スイッチと、を有し、

前記第1の期間において、前記コンフィギュレーションデータは、前記第1スイッチを介して、前記第2スイッチに供給され、

前記第1の期間において、前記第3スイッチは、オフとなり、

前記第1の期間に前記第2スイッチに供給された前記コンフィギュレーションデータに応じて、前記第2の期間において、前記第2スイッチ及び前記第3スイッチを介して、前記第1配線と前記第2配線とが電気的に接続されるか否かが定まるプログラマブルロジックデバイスを有する半導体装置。

## 【請求項 2】

第1配線と、

10

20

前記第1配線に直接接続される回路と、

前記回路に直接接続される第2配線と、

前記第2配線に直接接続されるI/Oエレメントと、

前記第1配線に直接接続される第1プログラマブルロジックエレメントと、を有し、

前記第1の配線に、コンフィギュレーションデータが供給される第1の期間と、第1プログラマブルロジックエレメントから出力される信号が供給される第2の期間とを有し、

前記回路は、それぞれ、第1スイッチと、第2スイッチと、第3スイッチと、を有し、

前記第1の期間において、前記コンフィギュレーションデータは、前記第1スイッチを介して、前記第2スイッチに供給され、

前記第1の期間において、前記第3スイッチは、オフとなり、

10

前記第1の期間に前記第2スイッチに供給された前記コンフィギュレーションデータに応じて、前記第2の期間において、前記第2スイッチ及び前記第3スイッチを介して、前記第1配線と前記第2配線とが電気的に接続されるか否かが定まるプログラマブルロジックデバイスを有する半導体装置。

#### 【請求項3】

請求項1または請求項2において、

前記第1配線は、前記第1スイッチの第1端子に直接接続され、

前記第1配線は、前記第2スイッチの第1端子に直接接続され、

前記第2スイッチの第2端子は、前記第3スイッチの第1端子に直接接続され、

前記第1スイッチの第2端子は、前記第2スイッチの第3端子に直接接続されるプログラマブルロジックデバイスを有する半導体装置。

20

#### 【請求項4】

請求項1乃至請求項3において、

前記第1スイッチは、酸化物半導体膜にチャネル形成領域を有するトランジスタであるプログラマブルロジックデバイスを有する半導体装置。

#### 【請求項5】

請求項4において、

前記酸化物半導体膜は、In、Ga、又はZnを有するプログラマブルロジックデバイスを有する半導体装置。

30

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明は、例えば、半導体装置、表示装置、発光装置、蓄電装置、それらの駆動方法、または、それらの製造方法に関する。本発明の一態様は、ハードウェアの構成を変更することができるプログラマブルロジックデバイスと、半導体装置に関する。

#### 【背景技術】

#### 【0002】

プログラマブルロジックデバイス（PLD：Programmable Logic Device）は、適当な規模のプログラマブルロジックエレメント（基本ブロック）で論理回路が構成されており、各プログラマブルロジックエレメントの機能や、プログラマブルロジックエレメント間の接続構造を、製造後において変更できることを特徴とする。具体的に、上記PLDは、複数のプログラマブルロジックエレメントと、プログラマブルロジックエレメント間の接続を制御する配線リソースとを有する。プログラマブルロジックエレメントと配線リソースとは、それぞれレジスタを有している。そして、上記レジスタは、各プログラマブルロジックエレメントの機能と、配線リソースにより構成されるプログラマブルロジックエレメント間の接続構造とを定義するための回路情報（コンフィギュレーションデータ）が、格納される。

40

#### 【0003】

50

コンフィギュレーションデータを格納するためのレジスタは、コンフィギュレーションメモリと呼ばれる。コンフィギュレーションデータのコンフィギュレーションメモリへの格納は、コンフィギュレーションと呼ばれる。特に、コンフィギュレーションメモリへのコンフィギュレーションデータの新たな格納は、リコンフィギュレーション（再構成）と呼ばれる。

【0004】

下記の特許文献1には、DRAMから送られてきたコンフィギュレーションデータを、SRAMで構成されるコンフィギュレーションメモリに格納することで、短時間でリコンフィギュレーションを行うプログラマブルLSIについて記載されている。

【先行技術文献】

10

【特許文献】

【0005】

【特許文献1】特開平10-285014号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

プログラマブルロジックデバイスの回路規模が増大すると、より大きな記憶容量を有するコンフィギュレーションメモリが必要となるため、プログラマブルロジックデバイスの面積を小さく抑えるのが難しくなる。

【0007】

20

そこで、本発明の一態様は、回路規模が増大してもレイアウトの面積を小さく抑えることができるプログラマブルロジックデバイスの提供を、課題の一つとする。

【0008】

または、本発明の一態様は、回路規模が増大しても小型化を実現することができる半導体装置などの提供を、課題の一つとする。

【0009】

なお、本明細書においての課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

30

【0010】

例えば、本発明の一態様は、配線間に大量に電流が流れるのを防ぐことができる半導体装置などの提供を、課題の一つとする。または、本発明の一態様は、破損が引き起こされることを低減することができる半導体装置などの提供を、課題の一つとする。または、本発明の一態様は、貫通電流が流れることを低減することができる半導体装置などの提供を、課題の一つとする。または、本発明の一態様は、オフ電流の低い半導体装置などを提供することを課題とする。または、本発明の一態様は、消費電力の低い半導体装置などを提供することを課題とする。または、本発明の一態様は、目に優しい表示装置などを提供することを課題とする。または、本発明の一態様は、透明な半導体層を用いた半導体装置などを提供することを課題とする。または、本発明の一態様は、信頼性の高い半導体層を用いた半導体装置などを提供することを課題とする。または、本発明の一態様は、新規な半導体装置などを提供することを課題とする。または、本発明の一態様は、良い半導体装置などを提供することを課題とする。

40

【課題を解決するための手段】

【0011】

本発明の一態様では、配線リソースに含まれるスイッチ回路に、その導通状態または非導通状態を保持する記憶装置としての機能を付加する。具体的に、スイッチ回路は、第1の期間において、コンフィギュレーションデータを含む信号が与えられ、なおかつ、第2の期間において、複数の第1プログラマブルロジックエレメントの出力端子にそれぞれ電気的に接続されている複数の第1配線と、第2プログラマブルロジックエレメントの入力端

50

子に電気的に接続されている第2配線と、複数の上記第1配線にそれぞれ対応する複数の回路とを有し、上記回路は、第1スイッチと、対応する上記第1配線から上記第1スイッチを介してコンフィギュレーションデータを含む信号が与えられるノードの電位により、導通状態または非導通状態が選択される第2スイッチと、対応する上記第1配線と上記第2配線の電気的な接続を上記第2スイッチと共に制御する第3スイッチとを、少なくとも有する。

#### 【0012】

そして、コンフィギュレーションデータに従って、複数の上記回路の一において上記第2スイッチが導通状態になり、なおかつ、上記複数の回路の全てにおいて上記第3スイッチが導通状態になることで、複数の第1配線と、上記第2配線との電気的な接続構造が定められる。

10

#### 【0013】

本発明の第一の態様では、上記構成により、複数の第1プログラマブルロジックエレメントと第2プログラマブルロジックエレメントの電気的な接続構造を、一のスイッチ回路により制御することができる。そして、スイッチ回路において第1スイッチを非導通状態にすることで、上記接続構造を保持することができるので、スイッチ回路は記憶装置としての機能を果たすことができる。よって、本発明の一態様により、配線リソースに含まれるトランジスタなどの素子数を小さく抑えることができるので、プログラマブルロジックデバイスの回路規模が増大するのを抑え、その面積を小さく抑えることができる。

#### 【発明の効果】

20

#### 【0014】

本発明の一態様により、回路規模が増大してもレイアウトの面積を小さく抑えることができるプログラマブルロジックデバイスを提供できる。また、本発明の一態様により、小型化された半導体装置を提供できる。

#### 【図面の簡単な説明】

#### 【0015】

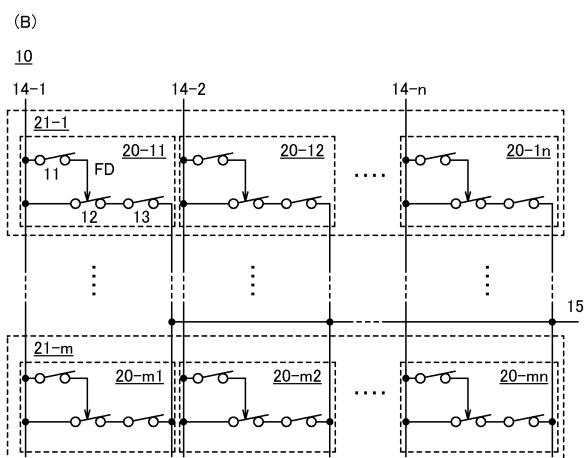

【図1】スイッチ回路の構成例。

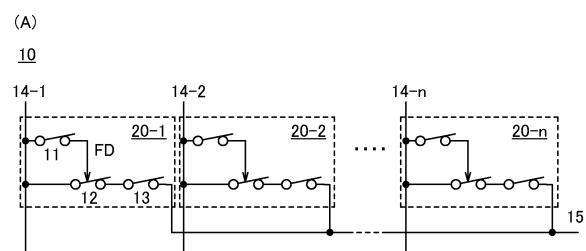

【図2】スイッチ回路の構成例。

【図3】スイッチ回路の構成例。

【図4】駆動回路の構成例。

30

【図5】プログラマブルロジックエレメントの構成例。

【図6】タイミングチャート。

【図7】ラッチの構成例。

【図8】プログラマブルロジックエレメントの構成例。

【図9】PLDの構成を示す図。

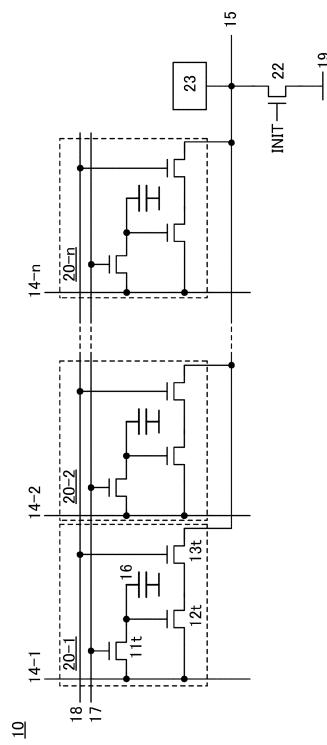

【図10】スイッチ回路の構成を示す図。

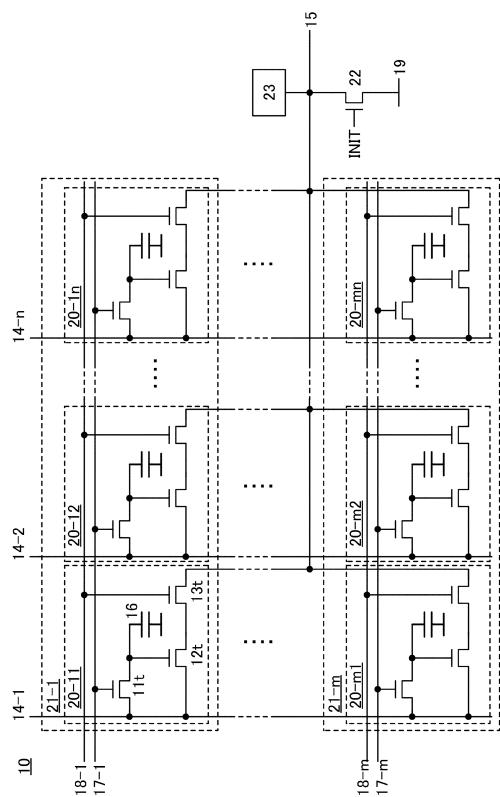

【図11】PLDの構成を示す図。

【図12】PLDの上面図。

【図13】LUTの構成を示す図。

【図14】セルの断面図。

40

【図15】電子機器の図。

【図16】チップとモジュールの図。

【図17】システムの図。

#### 【発明を実施するための形態】

#### 【0016】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

#### 【0017】

50

なお、本発明の一態様のプログラマブルロジックデバイスは、マイクロプロセッサ、画像処理回路、半導体表示装置用のコントローラ、DSP (Digital Signal Processor)、マイクロコントローラなどの、半導体素子を用いた各種半導体集積回路をその範疇に含む。また、本発明の一態様の半導体装置は、上記半導体集積回路を用いたRFタグ、半導体表示装置などの各種装置を、その範疇に含む。半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD (Digital Micromirror Device)、PDP (Plasma Display Panel)、FED (Field Emission Display)等や、半導体素子を駆動回路に有しているその他の半導体表示装置が、その範疇に含まれる。

10

#### 【0018】

##### スイッチ回路の構成例

まず、本発明の一態様に係る半導体装置が有する、スイッチ回路の構成例について説明する。

#### 【0019】

図1(A)に、スイッチ回路10の構成を例示する。スイッチ回路10は、配線14-1乃至配線14-n(nは複数の自然数)で表される複数の配線14と、配線15とを有する。さらに、スイッチ回路10は、スイッチ11と、スイッチ12と、スイッチ13とを少なくとも有する回路20を、複数有する。図1(A)では、回路20-1乃至回路20-nとして図示されている複数の回路20を、スイッチ回路10が有する場合を例示している。

20

#### 【0020】

複数の配線14は、複数の回路20にそれぞれ対応している。図1(A)では、配線14-i(iはn以下の自然数)が回路20-iに対応している場合を例示している。

#### 【0021】

そして、配線14の一つは、対応する回路20が有するスイッチ11を介して、回路20内のノードFDに電気的に接続されている。すなわち、スイッチ11は、配線14が有する電位の、ノードFDへの供給を制御する機能を有する。また、スイッチ12は、ノードFDの電位に従って、導通状態または非導通状態が選択される。スイッチ13は、配線14と配線15の間ににおいて、スイッチ12と直列に電気的に接続されている。

30

#### 【0022】

なお、本明細書において接続とは電気的な接続を意味しており、電流、電圧または電位が、供給可能、或いは伝送可能な状態に相当する。従って、接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧または電位が、供給可能、或いは伝送可能であるように、配線、抵抗、ダイオード、トランジスタなどの回路素子を介して電気的に接続している状態も、その範疇に含む。

#### 【0023】

配線14に与えられる信号は、期間によって異なる。第1の期間では、配線14にコンフィギュレーションデータを含む信号の電位が与えられ、それにより、スイッチ回路10へのコンフィギュレーションデータの書き込みが行われる。また、第2の期間では、配線14にプログラマブルロジックエレメント(PLE)から出力される信号の電位が与えられ、それにより、複数の配線14と配線15の接続構造が定められる。

40

#### 【0024】

具体的に、図1(A)に示す回路では、上記第1の期間において、配線14にコンフィギュレーションデータを含む信号の電位が与えられ、なおかつ、スイッチ11が導通状態(オン)になると、スイッチ11を介してノードFDに上記電位が供給される。次いで、スイッチ11が非導通状態(オフ)になると、ノードFDに与えられた電位が保持される。そして、スイッチ12は、コンフィギュレーションデータが反映されたノードFDの電位に従って、導通状態または非導通状態が選択される。

#### 【0025】

50

スイッチ13は、スイッチ12と直列に電気的に接続されているため、スイッチ12と共に、配線14と配線15の電気的な接続を制御する機能を有する。具体的には、スイッチ12及びスイッチ13が導通状態であるとき、配線14と配線15とが電気的に接続される。また、スイッチ12及びスイッチ13の少なくとも一つが非導通状態であるとき、配線14と配線15とは電気的に分離した状態となる。

#### 【0026】

また、図1(A)に示す回路では、上記第2の期間において、配線14にプログラマブルロジックエレメント(PLD)から出力される信号の電位が与えられ、なあかつ、スイッチ13が導通状態になると、スイッチ12が導通状態か非導通状態かによって、配線14と配線15が電気的に接続されるか、電気的に分離されるかが定まる。すなわち、スイッチ回路10の各回路20に書き込まれたコンフィギュレーションデータに従って、複数の配線14と配線15の接続構造が定められることとなる。10

#### 【0027】

なお、配線15は、PLDやI/Oエレメント(I/O)の入力端子に電気的に接続されている。I/Oは、プログラマブルロジックデバイス(PLD)の外部からPLDへの信号の入力、またはPLDからPLDの外部への信号の出力を制御する、インターフェースとしての機能を有する。コンフィギュレーションデータに従って、複数の配線14と配線15の接続構造が定められるということは、複数のPLDまたはI/Oの出力端子と、一のPLDまたはI/Oの入力端子との接続構造が定められることを意味する。20

#### 【0028】

なお、本明細書において入力端子とは、入力信号が与えられる配線などのノードを意味し、当該ノードを介して入力信号の電位、電圧、電流などが回路に与えられる。よって、入力端子に電気的に接続された配線も、入力端子の一部であると見なすことができる。また、本明細書において出力端子とは、出力信号が与えられる配線などのノードを意味し、当該ノードを介して出力信号の電位、電圧、電流などが回路から出力される。よって、出力端子に電気的に接続された配線も、出力端子の一部であると見なすことができる。20

#### 【0029】

本発明の第一の態様では、複数のPLDまたは複数のI/Oと、一のPLDまたはI/Oとの電気的な接続構造を、上述した一のスイッチ回路10により制御することができる。そして、スイッチ回路10においてスイッチ11を非導通状態にすることで、上記接続構造を保持することができるので、スイッチ回路10はコンフィギュレーションメモリとしての機能を果たすことができる。よって、スイッチ回路10を配線リソースに用いることで、配線リソースに含まれるトランジスタなどの素子数を小さく抑えることができるので、PLDの回路規模が増大するのを抑え、その面積を小さく抑えることができる。30

#### 【0030】

次いで、本発明の一態様に係る半導体装置が有する、スイッチ回路の別の構成例について説明する。

#### 【0031】

図1(B)に、スイッチ回路10の構成を例示する。図1(B)は、マルチコンテキスト方式を用いて動的再構成(ダイナミックリコンフィギュレーション)を実現することができるスイッチ回路10の一例を、示している。40

#### 【0032】

図1(B)に示すスイッチ回路10は、配線14-1乃至配線14-n(nは複数の自然数)で表される複数の配線14と、配線15とを有する点において、図1(A)に示すスイッチ回路10と構成が同じである。また、図1(B)に示すスイッチ回路10は、スイッチ11と、スイッチ12と、スイッチ13とを少なくとも有する回路20を、複数有する点において、図1(A)に示すスイッチ回路10と構成が同じである。しかし、図1(B)に示すスイッチ回路10では、任意に選ばれた一の配線14に、2つ以上の回路20が対応している点において、図1(A)に示すスイッチ回路10と構成が異なる。

#### 【0033】

10

20

30

40

50

具体的に、図1(B)に示すスイッチ回路10は、 $n \times m$ 個( $m$ は複数の自然数)の回路20を有している。そして、一の配線14には、 $m$ 個の回路20が接続されている。また、 $n \times m$ 個の回路20は、互いに異なる配線14に接続された $n$ 個の回路20で構成される組21が、 $m$ 個ある。図1(B)では、組21-1乃至組21-mで図示される $m$ 個の組21が、スイッチ回路10に設けられている。 $n \times m$ 個の回路20は、組21毎に、スイッチ13の動作が制御される。

#### 【0034】

図1(B)では、配線14-iに接続され、組21-j( $j$ は $m$ 以下の自然数)に含まれる回路20を、回路20-j<sub>i</sub>として図示する。

#### 【0035】

図1(B)に示すスイッチ回路10では、組21ごとに、回路20へのコンフィギュレーションデータの書き込みを行う。具体的には、一の組21に含まれる複数の回路20において、スイッチ11を導通状態にし、スイッチ11を介してノードFDにコンフィギュレーションデータを含む信号の電位を供給する。そして、当該一の組21に含まれる複数の回路20において、スイッチ11を非導通状態にし、ノードFDの電位を保持する。次いで、別の組21に含まれる複数の回路20においても、順に同様の動作を繰り返すことで、全ての回路20への、コンフィギュレーションデータの書き込みを行うことができる。

#### 【0036】

また、図1(B)に示すスイッチ回路10では、複数の組21の一つを選択し、選択された組21に含まれる複数の回路20において、保持されているコンフィギュレーションデータに従って、複数の配線14と配線15の接続構造を定めることができる。複数の配線14と配線15の接続構造を変更する場合は、スイッチ回路10において、複数の組21の別の一つを選択し、選択された組21に含まれる複数の回路20において、保持されているコンフィギュレーションデータに従って、複数の配線14と配線15の接続構造を定めれば良い。

#### 【0037】

図1(B)に示すスイッチ回路10は、図1(A)に示すスイッチ回路10と同様に、複数のPLEまたは複数のIOと、一のPLEまたはIOとの電気的な接続構造を制御する機能と、当該接続構造を保持するコンフィギュレーションメモリとしての機能とを有する。よって、図1(B)に示すスイッチ回路10を配線リソースに用いることで、配線リソースに含まれるトランジスタなどの素子数を小さく抑えることができるので、PLDの回路規模が増大するのを抑え、その面積を小さく抑えることができる。

#### 【0038】

また、図1(B)に示すスイッチ回路10の場合、複数のコンフィギュレーションデータが組21ごとに保持されており、なおかつ、コンフィギュレーションデータの選択を、組21の選択により自由に行うことができる。そのため、一のコンフィギュレーションデータにより回路構成が定められたPLDを動作させている間に、他のコンフィギュレーションデータを書き換えることができる。

#### 【0039】

なお、上述した特許文献1の場合、マルチコンテキスト方式においてコンフィギュレーションデータを切り換えるのに、DRAMからコンフィギュレーションデータを読み出す必要があり、当該コンフィギュレーションデータの読み出しにはセンスアンプを用いる必要がある。図1(B)に示すスイッチ回路10を用いた本発明の一態様に係るPLDの場合、回路構成を切り換える度に、DRAMなどからセンスアンプを用いてコンフィギュレーションデータの読み出しを行う必要がない。そのため、回路構成の切り換えにかかる時間を短くでき、よって、プログラマブルロジックデバイスにおける論理回路の再構成を高速で行うことができる。

#### 【0040】

また、図1(A)及び図1(B)に示すスイッチ回路10では、配線14が、コンフィギュレーションデータを含む信号の電位を回路20に供給する機能と、PLEから出力され

10

20

30

40

50

る信号の電位を回路 20 に供給する機能とを併せ持っている。よって、コンフィギュレーションデータを含む信号の電位を回路 20 に供給する機能を有する配線と、P L E から出力される信号の電位を回路 20 に供給する機能を有する配線とを、回路 20 に接続させる構成に比べて、スイッチ回路 10 に設けられる配線の数を少なく抑えることができる。よって、図 1 (A) 及び図 1 (B) に示すスイッチ回路 10 を用いることで、配線リソースの小型化を実現し、回路規模が増大してもレイアウトの面積を小さく抑えることができるプログラマブルロジックデバイスを実現することができる。また、配線リソースの小型化を実現することで、半導体装置の小型化を実現することができる。

#### 【0041】

##### スイッチ回路の具体的な構成例

10

次いで、図 1 (A) に示したスイッチ回路 10 の、具体的な構成の一例について説明する。図 2 に示すスイッチ回路 10 は、配線 14 - 1 乃至配線 14 - n で示す複数の配線 14 と、配線 15 と、配線 17 と、配線 18 とを有する。さらに、図 2 に示すスイッチ回路 10 は、回路 20 - 1 乃至回路 20 - n で示す複数の回路 20 を有する。各回路 20 は、スイッチ 11 としての機能を有するトランジスタ 11t と、スイッチ 12 としての機能を有するトランジスタ 12t と、スイッチ 13 としての機能を有するトランジスタ 13t と、容量素子 16 とを、少なくとも有する。

#### 【0042】

具体的に、回路 20 - iにおいて、トランジスタ 11t は、そのゲートが配線 17 に電気的に接続されている。また、トランジスタ 11t のソース及びドレインは、一方が配線 14 - i に電気的に接続され、他方がトランジスタ 12t のゲートに電気的に接続されている。トランジスタ 12t のソース及びドレインは、一方が配線 14 - i に電気的に接続され、他方がトランジスタ 13t のソース及びドレインの一方に電気的に接続されている。トランジスタ 13t のソース及びドレインの他方は、配線 15 に電気的に接続されている。トランジスタ 13t のゲートは、配線 18 に電気的に接続されている。

20

#### 【0043】

なお、トランジスタのソースとは、活性層として機能する半導体膜の一部であるソース領域、或いは上記半導体膜に電気的に接続されたソース電極を意味する。同様に、トランジスタのドレインとは、活性層として機能する半導体膜の一部であるドレイン領域、或いは上記半導体膜に電気的に接続されたドレイン電極を意味する。また、ゲートはゲート電極を意味する。

30

#### 【0044】

トランジスタが有するソースとドレインは、トランジスタのチャネル型及び各端子に与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、n チャネル型トランジスタでは、低い電位が与えられる端子がソースと呼ばれ、高い電位が与えられる端子がドレインと呼ばれる。また、p チャネル型トランジスタでは、低い電位が与えられる端子がドレインと呼ばれ、高い電位が与えられる端子がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

40

#### 【0045】

回路 20 は、必要に応じて、トランジスタ、ダイオード、抵抗素子、容量素子、インダクタなどのその他の回路素子を、さらに有していても良い。

#### 【0046】

さらに、図 2 に示すスイッチ回路 10 は、配線 15 に、所定の電位が与えられた配線 19 との電気的な接続を制御するスイッチ 22 が、設けられている場合を例示している。図 2 では、スイッチ 22 として、一のトランジスタが用いられている場合を例示している。スイッチ 22 は信号 I N I T に従って導通状態または非導通状態の選択(スイッチング)が行われる。具体的に、スイッチ 22 が導通状態であるとき、配線 19 の電位が配線 15 に与えられ、スイッチ 22 が非導通状態であるとき、配線 19 の電位は配線 15 に与えられ

50

ない。

#### 【0047】

スイッチ22を導通状態とすることで、配線15の電位が所定の高さになるよう初期化することができる。なお、配線15や配線14の電位は、PLDの電源が切断された後に、不定状態となりやすい。また、PLDの電源が切断された後、コンフィギュレーションメモリが有する記憶素子の構成によっては、コンフィギュレーションデータが消失することがある。この場合、PLDに電源が投入されると、配線15と複数の配線14とがスイッチ回路10を介して導通状態になり、配線15と複数の配線14とで電位が異なる場合、これらの配線に大量の電流が流れることがある。しかし、上述したように、配線15の電位を初期化することで、配線15と複数の配線14の間に大量に電流が流れるのを防ぐことができる。それにより、PLDの破損が引き起こされるのを、防ぐことができる。10

#### 【0048】

また、PLDに電源が投入された直後は、PLEの入力端子が、ハイレベルとローレベルの間の中間電位になってしまう場合がある。中間電位がPLEの入力端子に与えられると、PLEの有するCMOS回路において貫通電流が生じやすい。しかし、上述したように、配線15の電位を初期化することができるので、電源が投入された直後において入力端子が中間電位になるのを防ぐことができ、よって、上記貫通電流が生じるのを防ぐことができる。

#### 【0049】

また、配線15に、ラッチが電気的に接続されていても良い。図2では、初期化を行うためのスイッチ22に加えて、ラッチ23が配線15に電気的に接続されている場合を例示する。ラッチ23は、PLEの入力端子に電気的に接続された配線15の電位を、ハイレベルかローレベルのいずれか一方に保つ機能を有する。ラッチ23を配線15に電気的に接続させることによって、PLDに電源が投入された後に、配線15の電位をハイレベルかローレベルのいずれか一方に保つことができるので、中間の電位が配線15に与えられることで、配線15にその入力端子が接続されたPLEに貫通電流が生じるのを、防ぐことができる。20

#### 【0050】

次いで、図1(B)に示したスイッチ回路10の一例について説明する。図3に示すスイッチ回路10は、配線14-1乃至配線14-nで示す複数の配線14と、配線15と、配線17-1乃至配線17-mで示す複数の配線17と、配線18-1乃至配線18-mで示す複数の配線18とを有する。さらに、図3に示すスイッチ回路10は、m×n個の回路20を有する。各回路20は、スイッチ11としての機能を有するトランジスタ11tと、スイッチ12としての機能を有するトランジスタ12tと、スイッチ13としての機能を有するトランジスタ13tと、容量素子16とを、少なくとも有する。30

#### 【0051】

そして、m×n個の回路20は、配線17-j及び配線18-jに接続されているn個の回路20で構成されている組21を、m個有する。図3では、m個の組21を、組21-1乃至組21-mとして図示する。40

#### 【0052】

具体的に、回路20-jiにおいて、トランジスタ11tは、そのゲートが配線17-jに電気的に接続されている。また、トランジスタ11tのソース及びドレインは、一方が配線14-iに電気的に接続され、他方がトランジスタ12tのゲートに電気的に接続されている。トランジスタ12tのソース及びドレインは、一方が配線14-iに電気的に接続され、他方がトランジスタ13tのソース及びドレインの一方に電気的に接続されている。トランジスタ13tのソース及びドレインの他方は、配線15に電気的に接続されている。トランジスタ13tのゲートは、配線18-jに電気的に接続されている。

#### 【0053】

回路20は、必要に応じて、トランジスタ、ダイオード、抵抗素子、容量素子、インダク50

タなどのその他の回路素子を、さらに有していても良い。

#### 【0054】

さらに、図3に示すスイッチ回路10は、図2に示すスイッチ回路10と同様に、配線15に、所定の電位が与えられた配線19との電気的な接続を制御するスイッチ22が、設けられている場合を例示している。また、図3では、ラッチ23が配線15に電気的に接続されている場合を例示している。ラッチ23は、PLCの入力端子に電気的に接続された配線15の電位を、ハイレベルかローレベルのいずれか一方に保つ機能を有する。

#### 【0055】

なお、図2及び図3に示すスイッチ回路10において、トランジスタ11tは、ノードFDの電位を保持する機能を有しているため、オフ電流の著しく小さいトランジスタであることが望ましい。シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体膜に、チャネル形成領域が形成されることを特徴とするトランジスタは、オフ電流が著しく小さいので、トランジスタ11tとして用いるのに好適である。このような半導体としては、例えば、シリコンの2倍以上の大きなバンドギャップを有する、酸化物半導体、窒化ガリウムなどが挙げられる。上記半導体を有するトランジスタは、通常のシリコンやゲルマニウムなどの半導体で形成されたトランジスタに比べて、オフ電流を極めて小さくすることができる。よって、上記構成を有するトランジスタ11tを用いることで、ノードFDに保持されている電荷が、リークするのを防ぐことができる。

#### 【0056】

また、図2及び図3に示すスイッチ回路10において、回路20では、スイッチ11が非導通状態にあるときノードFDが、他の電極や配線との間ににおける絶縁性が極めて高い浮遊状態になることから、以下に述べるブースティング効果が期待できる。すなわち、回路20では、ノードFDが浮遊状態にあると、配線14の電位がローレベルからハイレベルに変化するのに伴い、スイッチ12として機能するトランジスタのソースとゲートの間に形成される容量Cgsにより、ノードFDの電位が上昇する。そして、そのノードFDの電位の上昇幅は、上記トランジスタのゲートに入力されたコンフィギュレーションデータの論理レベルによって異なる。具体的に、回路20に入力されたコンフィギュレーションデータが“0”的場合、上記トランジスタは弱反転モードにあるため、ノードFDの電位の上昇に寄与する容量Cgsには、ゲート電極の電位、すなわちノードFDの電位に依存しない容量Cosが含まれる。具体的に、容量Cosには、ゲート電極とソース領域とが重畳する領域に形成されるオーバーラップ容量と、ゲート電極とソース電極の間に形成される寄生容量などが含まれる。一方、回路20に書き込まれたコンフィギュレーションデータが“1”的場合、上記トランジスタは強反転モードにあるため、ノードFDの電位の上昇に寄与する容量Cgsには、上述した容量Cosに加えて、チャネル形成領域とゲート電極の間に形成される容量Coxの一部が含まれる。したがって、コンフィギュレーションデータが“1”的場合、ノードFDの電位の上昇に寄与する容量Cgsが、コンフィギュレーションデータが“0”的場合よりも大きいこととなる。よって、回路20では、コンフィギュレーションデータが“1”的場合の方が、コンフィギュレーションデータが“0”的場合よりも、配線14の電位の変化に伴い、ノードFDの電位をより高く上昇させるというブースティング効果を得ることができる。よって、コンフィギュレーションデータが“1”的場合に、配線14に入力されたコンフィギュレーションデータを含む信号の電位に対して、スイッチ11が有するトランジスタの閾値電圧分、ノードFDの電位が下降していたとしても、ブースティング効果によりノードFDの電位を上昇させることができるので、スイッチ12として機能するトランジスタの導通状態を確保することができ、回路20のスイッチ速度を向上させることができる。また、コンフィギュレーションデータが“0”的場合には、スイッチ12として機能する上記トランジスタの非導通状態を確保することができる。

#### 【0057】

##### 駆動回路の構成例

次いで、図4に、配線14への、コンフィギュレーションデータを含む信号の供給を制御

10

20

30

40

50

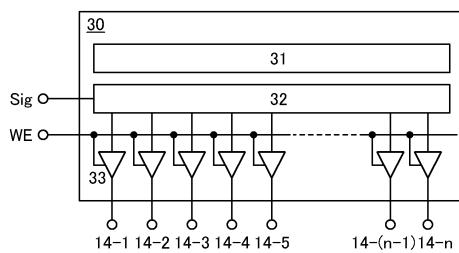

する駆動回路 3 0 の構成を、一例として示す。図 4 に示す駆動回路 3 0 は、コンフィギュレーションデータを含む信号 S i g の、サンプリングのタイミングを制御する、シフトレジスタなどの回路 3 1 と、回路 3 1 で定められたタイミングに従って、上記信号のサンプリングを行う回路 3 2 と、サンプリングされた上記信号の、配線 1 4 - 1 乃至配線 1 4 - n への供給をそれぞれ制御する複数のスイッチ 3 3 とを有する。図 4 では、スイッチ 3 3 として、信号 W E に従ってハイインピーダンスとなるスリーステートバッファを用いる場合を例示する。

#### 【 0 0 5 8 】

具体的に、図 4 では、信号 W E の電位がハイレベルのとき、スイッチ 3 3 は、入力端子に入力された信号と同じ論理値を有する信号を、配線 1 4 - 1 乃至配線 1 4 - n に与える。

また、信号 W E の電位がローレベルのとき、スイッチ 3 3 はハイインピーダンスとなり、入力端子に入力された信号は、配線 1 4 - 1 乃至配線 1 4 - n に与えられない。

10

#### 【 0 0 5 9 】

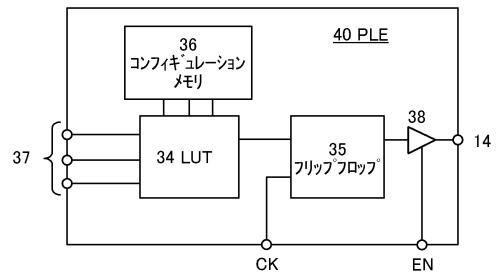

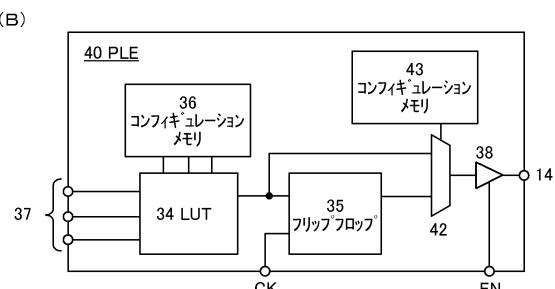

##### P L E の構成例 1

図 5 に、P L E 4 0 の一形態を例示する。図 5 に示す P L E 4 0 は、L U T (ルックアップテーブル) 3 4 と、フリップフロップ 3 5 と、コンフィギュレーションメモリ 3 6 と、を有する。コンフィギュレーションメモリ 3 6 は、メモリエレメントから送られてきたコンフィギュレーションデータを記憶する機能を有する。L U T 3 4 は、コンフィギュレーションメモリ 3 6 において記憶されているコンフィギュレーションデータによって、定められる論理演算が異なる。そして、コンフィギュレーションデータにより L U T 3 4 にて行われる論理演算が確定すると、L U T 3 4 は、入力端子 3 7 に与えられた複数の入力信号に対応する出力信号を、出力する。フリップフロップ 3 5 は、L U T 3 4 から出力される信号を保持し、クロック信号 C K に同期して当該信号に対応した出力信号を出力する。

20

#### 【 0 0 6 0 】

スイッチ 3 8 は、フリップフロップ 3 5 から出力された信号の、配線 1 4 への供給を制御する機能を有する。図 5 では、スイッチ 3 8 として、信号 E N に従ってハイインピーダンスとなるスリーステートバッファを用いる場合を例示する。

#### 【 0 0 6 1 】

具体的に、図 5 では、信号 E N の電位がハイレベルのとき、スイッチ 3 8 は、入力端子に入力された信号と同じ論理値を有する信号を、配線 1 4 に与える。また、信号 E N の電位がローレベルのとき、スイッチ 3 8 はハイインピーダンスとなり、入力端子に入力された信号は、配線 1 4 に与えられない。

30

#### 【 0 0 6 2 】

なお、P L E 4 0 がさらにマルチプレクサ回路を有し、当該マルチプレクサ回路によって、L U T 3 4 からの出力信号がフリップフロップ 3 5 を経由するか否かを選択できるようにも良い。

#### 【 0 0 6 3 】

また、コンフィギュレーションデータによって、フリップフロップ 3 5 の種類を定義できる構成にしても良い。具体的には、コンフィギュレーションデータによって、フリップフロップ 3 5 が D 型フリップフロップ、T 型フリップフロップ、J K 型フリップフロップ、または R S 型フリップフロップのいずれかの機能を有するようにしても良い。

40

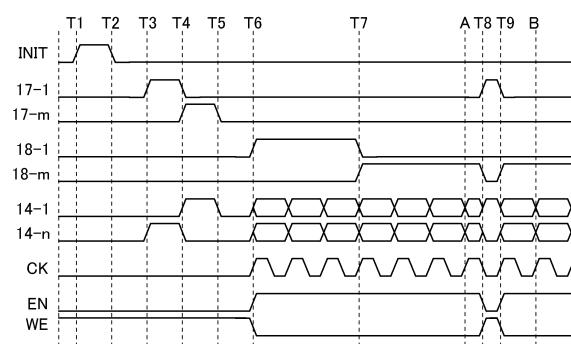

#### 【 0 0 6 4 】

##### スイッチ回路の動作例

次いで、図 3 に示したスイッチ回路 1 0 の動作の一例について、図 6 に示すタイミングチャートを用いて説明する。図 6 に示すタイミングチャートには、図 4 に示す駆動回路 3 0 にて、スイッチ 3 3 の動作を制御する信号 W E と、図 5 に示す P L E 4 0 にて、フリップフロップ 3 5 の出力信号の出力を制御するクロック信号 C K と、スイッチ 3 8 の動作を制御する信号 E N の、タイミングチャートも併せて示す。また、図 6 に示すタイミングチャートでは、トランジスタ 1 1 t 乃至トランジスタ 1 3 t が n チャネル型である場合を例示している。また、配線 1 9 にはローレベルの電位 V S S が与えられているものとする。

50

**【 0 0 6 5 】**

まず、P L D に電源を投入した後、時刻 T 1 乃至時刻 T 2 において行われる、配線 1 5 の電位の初期化について説明する。

**【 0 0 6 6 】**

時刻 T 1 乃至時刻 T 2 において、スイッチ 2 2 に用いられているトランジスタのゲートに、ハイレベルの電位を有する信号 I N I T が入力され、スイッチ 2 2 は導通状態となる。よって、スイッチ 2 2 を介して、配線 1 9 の電位 V S S が配線 1 5 に与えられる。

**【 0 0 6 7 】**

配線 1 5 に電位 V S S を与えることで、P L D に電源を投入した直後に配線 1 5 の電位が不定状態にあったとしても、配線 1 5 の電位を初期化することができる。よって、配線 1 5 に電気的に接続された P L E の入力端子の電位が不定状態にならず、当該 P L E の有する C M O S 回路において、貫通電流が発生するのを防ぐことができる。それにより、P L D の破損が引き起こされるのを防ぐことができる。なお、P L D に電源を投入するのと同時に、信号 I N I T の電位をハイレベルとしていることで、配線 1 5 の電位が不定状態となる期間を短くすることができる。10

**【 0 0 6 8 】**

また、時刻 T 1 乃至時刻 T 2 では、配線 1 8 - 1 乃至配線 1 8 - m にローレベルの電位が与えられる。上記構成により、配線 1 5 と複数の配線 1 4 とを電気的に分離させることができる。さらに、時刻 T 1 乃至時刻 T 2 では、信号 E N の電位がローレベルとなり、信号 W E の電位がハイレベルとなり、駆動回路 3 0 から、配線 1 4 - 1 乃至配線 1 4 - n に、ローレベルの電位、具体的には、配線 1 9 と同じ電位 V S S が、与えられる。上記構成により、配線 1 5 と複数の配線 1 4 とを概略同じ高さの電位にすることができる。よって、P L D に電源を投入した後に、配線 1 5 と複数の配線 1 4 とに大量の電流が流れるのを防ぐことができる。それにより、P L D の破損が引き起こされるのを、防ぐことができる。20

**【 0 0 6 9 】**

配線 1 5 の電位の初期化が済むと、時刻 T 3 以降、信号 I N I T の電位はローレベルを維持し、スイッチ 2 2 は非導通状態となる。

**【 0 0 7 0 】**

次いで、時刻 T 3 乃至時刻 T 5 において行われる、コンフィギュレーションデータの書き込みについて説明する。上記期間では、信号 E N の電位がローレベルとなるため、P L E 4 0 から配線 1 4 への信号の供給は停止される。また、上記期間では、信号 W E の電位がハイレベルとなるため、駆動回路 3 0 から配線 1 4 への、コンフィギュレーションデータを含む信号の供給が行われる。また、全ての配線 1 8 には、ローレベルの電位が与えられる。30

**【 0 0 7 1 】**

まず、時刻 T 3 乃至時刻 T 4 において、配線 1 7 - 1 にはハイレベルの電位が、配線 1 7 - m を含む配線 1 7 - 1 以外の全ての配線 1 7 にはローレベルの電位が与えられる。また、配線 1 4 - 1 にはローレベルの電位が、配線 1 4 - n にはハイレベルの電位が与えられる。上記動作により、配線 1 7 - 1 と配線 1 4 - 1 または配線 1 4 - n とに接続された回路 2 0 - 1 1 及び回路 2 0 - 1 n への、コンフィギュレーションデータの書き込みが行われる。具体的に、回路 2 0 - 1 1 では、ノード F D にローレベルの電位が与えられることによって、" 0 " の論理値に対応したコンフィギュレーションデータが格納される。また、回路 2 0 - 1 n では、ノード F D にハイレベルの電位が与えられることによって、" 1 " の論理値に対応したコンフィギュレーションデータが格納される。40

**【 0 0 7 2 】**

次いで、時刻 T 4 乃至時刻 T 5 において、配線 1 7 - 1 を含む配線 1 7 - m 以外の全ての配線 1 7 にはローレベルの電位が、配線 1 7 - m にはハイレベルの電位が、配線 1 4 - 1 にはハイレベルの電位が、配線 1 4 - n にはローレベルの電位が与えられる。上記動作により、配線 1 7 - m と配線 1 4 - 1 または配線 1 4 - n とに接続された回路 2 0 - m 1 及び回路 2 0 - m n への、コンフィギュレーションデータの書き込みが行われる。具体的に50

、回路 20 - m 1 では、ノード FD にハイレベルの電位が与えられることによって、” 1 ” の論理値に対応したコンフィギュレーションデータが格納される。また、回路 20 - m n では、ノード FD にローレベルの電位が与えられることによって、” 0 ” の論理値に対応したコンフィギュレーションデータが格納される。

#### 【 0073 】

なお、図 6 に示すタイミングチャートでは、回路 20 - 11 、回路 20 - 1n 、回路 20 - m 1 、回路 20 - m n への、コンフィギュレーションデータの書き込みについてのみ示しているが、上記以外の回路 20 へのコンフィギュレーションデータの書き込みも、同様に行うことができる。ただし、複数の組 21 のうち、コンフィギュレーションデータが格納される組 21 は、一つのみである。

10

#### 【 0074 】

次いで、時刻 T 6 乃至時刻 T 8 において行われる、回路構成の切り換えについて説明する。上記期間では、信号 EN の電位がハイレベルとなるため、PLE 40 から配線 14 への信号の供給が行われる。また、上記期間では、信号 WE の電位がローレベルとなるため、駆動回路 30 から配線 14 への、コンフィギュレーションデータを含む信号の供給は停止される。

#### 【 0075 】

まず、時刻 T 6 乃至時刻 T 7 において、全ての配線 17 にはローレベルの電位が与えられる。そして、配線 18 - 1 にはハイレベルの電位が、配線 18 - m を含む配線 18 - 1 以外の全ての配線 18 には、ローレベルの電位が与えられる。上記動作により、配線 18 - 1 に接続された回路 20 - 11 乃至回路 20 - 1n により、配線 14 - 1 乃至配線 14 - n と配線 15 との接続構造が定められる。具体的には、回路 20 - 11 乃至回路 20 - 1n のうち、回路 20 - 1n に” 1 ” の論理値に対応したコンフィギュレーションデータが格納されているため、配線 14 - n と配線 15 とが、回路 20 - 1n を介して電気的に接続される。

20

#### 【 0076 】

また、時刻 T 7 乃至時刻 T 8 において、全ての配線 17 にはローレベルの電位が与えられる。そして、配線 18 - 1 を含む配線 18 - m 以外の全ての配線 18 には、ローレベルの電位が、配線 18 - m にはハイレベルの電位が、与えられる。上記動作により、配線 18 - m に接続された回路 20 - m 1 乃至回路 20 - m n により、配線 14 - 1 乃至配線 14 - n と配線 15 との接続構造が定められる。具体的には、回路 20 - m 1 乃至回路 20 - m n のうち、回路 20 - m 1 に” 1 ” の論理値に対応したコンフィギュレーションデータが格納されているため、配線 14 - 1 と配線 15 とが、回路 20 - m 1 を介して電気的に接続される。

30

#### 【 0077 】

次いで、時刻 T 8 乃至時刻 T 9 において行われる、コンフィギュレーションデータの書き換えについて説明する。上記期間では、信号 EN の電位がローレベルとなるため、PLE 40 から配線 14 への信号の供給は停止される。また、上記期間では、信号 WE の電位がハイレベルとなるため、駆動回路 30 から配線 14 への、コンフィギュレーションデータを含む信号の供給が行われる。また、全ての配線 18 には、ローレベルの電位が与えられる。

40

#### 【 0078 】

具体的に、時刻 T 8 乃至時刻 T 9 では、配線 17 - 1 にはハイレベルの電位が、配線 17 - m を含む配線 17 - 1 以外の全ての配線 17 にはローレベルの電位が与えられる。また、配線 14 - 1 にはハイレベルの電位が、配線 14 - n にはローレベルの電位が与えられる。上記動作により、配線 17 - 1 と配線 14 - 1 または配線 14 - n とに接続された回路 20 - 11 及び回路 20 - 1n への、コンフィギュレーションデータの書き込みが行われる。具体的に、回路 20 - 11 では、ノード FD にハイレベルの電位が与えられることによって、” 1 ” の論理値に対応したコンフィギュレーションデータが格納される。また、回路 20 - 1n では、ノード FD にローレベルの電位が与えられることによって、” 0 ”

50

”の論理値に対応したコンフィギュレーションデータが格納される。

#### 【0079】

なお、時刻T8乃至時刻T9では、全ての配線18にローレベルの電位を与えているため、ラッチ23により、時刻T8の直前に配線15に与えられた信号の論理値が保持される。具体的には、図5に示すPLE40において、時刻T8の直前にクロック信号CKの立ち上がりエッジが出現する時刻Aに同期してフリップフロップ35から出力され、なおかつ、配線14-1及び回路20-m1を介して配線15に与えられた信号が、ラッチ23により保持される。なお、クロック信号CKの上記立ち上がりエッジが出現した後、PLE40の出力信号が確定し、上記出力信号の論理値をラッチ23に格納できる程度に十分な時間を確保できるように、時刻T8を設定することが好ましい。

10

#### 【0080】

したがって、配線15に与えられた信号の論理値は、ラッチ23により保持されるため、回路20-11及び回路20-1nにおけるコンフィギュレーションデータの書き換えにより、PLDの動作が妨げられることはない。

#### 【0081】

なお、時刻Aからクロック信号CKの2周期後にて立ち上がりエッジが出現する時刻Bよりも前に時刻T9を設定することで、PLDの動作を止めることなく、コンフィギュレーションデータの書き換えを行うことができる。具体的には、時刻T9の後、PLE40の出力信号（時刻T8の直後のクロック信号CKの立ち上がりエッジに同期してPLE40のフリップフロップ35から出力された信号）が、配線14-1乃至配線14-nと、回路20-11乃至回路20-mnとを介して配線15に与えられ、配線15からPLEに入力された上記信号が、時刻Bに同期してフリップフロップ35に格納されるのに十分なセットアップ時間が確保できるように、時刻T9を設定することが好ましい。

20

#### 【0082】

なお、スイッチ回路10へのコンフィギュレーションデータの書き込みの速度が十分高くない時は、時刻T8乃至時刻T9におけるクロック信号CKの周期を、時刻T8乃至時刻T9以外の期間におけるクロック信号CKの周期よりも長く設定すればよい。上記構成により、書き込みの時間を長く確保することができ、時刻T8乃至時刻T9において、コンフィギュレーションデータの書き込みを完了させることができる。また、PLDのクリティカルパスに含まれるスイッチ回路では、要求される書き込み時間が他のスイッチ回路と異なる。このような場合、クロック信号CKの周期を、要求される書き込み時間に合わせて異ならせるようにしても良い。

30

#### 【0083】

なお、図6では、電源の投入後に配線15の電位を初期化する構成について示しているが、配線15の電位を初期化する構成に加えて、回路20内のノードFDの電位の初期化を行うようにしても良い。ノードFDの電位の初期化は、回路20ごとに順に行っても良いし、全ての回路20においてノードFDの電位を一斉に初期化しても良い。

#### 【0084】

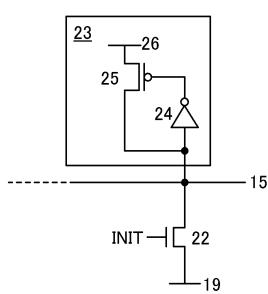

##### ラッチの構成例

次いで、図7に、ラッチ23の構成を一例として示す。図7に示すラッチ23は、インバータ24と、pチャネル型のトランジスタ25とを有する。インバータ24の入力端子は配線15に電気的に接続され、インバータ24の出力端子はトランジスタ25のゲートに電気的に接続されている。トランジスタ25のソース及びドレインは、一方が、配線19よりも高い電位が与えられている配線26に電気的に接続され、他方が、配線15に電気的に接続されている。

40

#### 【0085】

本発明の一態様では、上記構成を有するラッチ23を配線15に電気的に接続させることによって、PLDに電源が投入された後に、配線15の電位をハイレベルかローレベルのいずれか一方に保つことができるので、中間の電位が配線15に与えられることで、配線15にその入力端子が接続されたPLEに貫通電流が生じるのを、防ぐことができる。

50

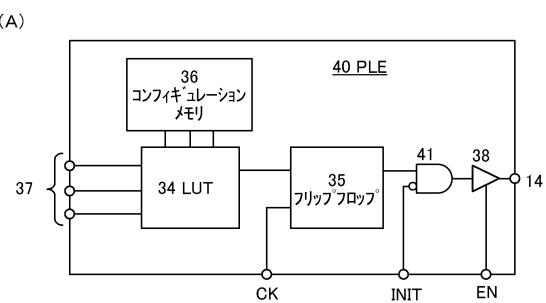

## 【0086】

## P L E の構成例 2

次いで、図 8 ( A ) に、 P L E 4 0 の別の形態を例示する。図 8 ( A ) に示す P L E 4 0 は、図 5 に示した P L E 4 0 に、 A N D 回路 4 1 が追加された構成を有している。 A N D 回路 4 1 には、フリップフロップ 3 5 からの信号が、正論理の入力として与えられ、配線 1 5 の電位を初期化するための信号 I N I T が、負論理の入力として与えられている。上記構成により、信号 I N I T に従って図 7 に示した配線 1 5 の電位が初期化される際に、 P L E 4 0 からの出力信号を、図 7 に示した配線 1 9 と同じ電位にすることができる。よって、 P L E 4 0 からの出力信号が与えられる複数の配線 1 4 と、配線 1 5 とに大量の電流が流れることを未然に防ぐことができる。それにより、 P L D の破損が引き起こされるのを、防ぐことができる。10

## 【0087】

また、図 8 ( B ) に、 P L E 4 0 の別の形態を例示する。図 8 ( B ) に示す P L E 4 0 は、図 5 に示した P L E 4 0 に、マルチプレクサ 4 2 と、コンフィギュレーションメモリ 4 3 が追加された構成を有している。図 8 ( B ) において、マルチプレクサ 4 2 は、 L U T 3 4 からの出力信号と、フリップフロップ 3 5 からの出力信号とが入力されている。そして、マルチプレクサ 4 2 は、コンフィギュレーションメモリ 4 3 に格納されているコンフィギュレーションデータに従って、上記 2 つの出力信号のいずれか一方を選択し、出力する機能を有する。マルチプレクサ 4 2 からの出力信号は、スイッチ 3 8 を介して配線 1 4 に与えられる。20

## 【0088】

## 半導体膜について

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified Oxide Semiconductor）は、i 型（真性半導体）又は i 型に限りなく近い。そのため、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタは、オフ電流が著しく小さく、信頼性が高い。

## 【0089】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が  $1 \times 10^6 \mu\text{m}$  でチャネル長が  $10 \mu\text{m}$  の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が  $1\text{V}$  から  $10\text{V}$  の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13}\text{A}$  以下という特性を得ることができる。この場合、チャネル幅で規格化したトランジスタのオフ電流は、 $100\text{zA}/\mu\text{m}$  以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、高純度化された酸化物半導体膜を上記トランジスタのチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が  $3\text{V}$  の場合に、数十  $\text{yA}/\mu\text{m}$  という、さらに小さいオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく小さい。3040

## 【0090】

なお、特に断りがない限り、本明細書でオフ電流とは、n チャネル型トランジスタにおいては、ドレインをソースとゲートよりも高い電位とした状態において、ソースの電位を基準としたときのゲートの電位が  $0$  以下であるときに、ソースとドレインの間に流れる電流のことを意味する。或いは、本明細書でオフ電流とは、p チャネル型トランジスタにおいては、ドレインをソースとゲートよりも低い電位とした状態において、ソースの電位を基準としたときのゲートの電位が  $0$  以上であるときに、ソースとドレインの間に流れる電流のことを意味する。50

## 【0091】

なお、半導体膜として酸化物半導体膜を用いる場合、酸化物半導体としては、少なくともインジウム(Indium)あるいは亜鉛(Zinc)を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Gallium)を有することが好ましい。また、スタビライザーとしてスズ(Silver)を有することが好ましい。また、スタビライザーとしてハフニウム(Hafnium)を有することが好ましい。また、スタビライザーとしてアルミニウム(Aluminum)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zirconium)を含むことが好ましい。

## 【0092】

酸化物半導体の中でもIn-Ga-Zn系酸化物、In-Sn-Zn系酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記In-Ga-Zn系酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

## 【0093】

また、他のスタビライザーとして、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Europium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplumbium)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)のいずれか一種または複数種を含んでいてもよい。

## 【0094】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、In-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

## 【0095】

なお、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを含む酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素を含んでいてもよい。In-Ga-Zn系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

## 【0096】

例えば、 $In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)$ あるいは $In : Ga : Zn = 2 : 2 : 1 (= 2 / 5 : 2 / 5 : 1 / 5)$ の原子比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)$ 、 $In : Sn : Zn = 2 : 1 : 3 (= 1 / 3 : 1 / 6 : 1 / 2)$ あるいは $In : Sn : Zn = 2 : 1 : 5 (= 1 / 4 : 1 / 8 : 5 / 8)$ の原子比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

## 【0097】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上

10

20

30

40

50

げることができる。

**【0098】**

以下では、酸化物半導体膜の構造について説明する。

**【0099】**

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜などをいう。

**【0100】**

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

10

**【0101】**

微結晶酸化物半導体膜は、例えば、1 nm以上10 nm未満の大きさの微結晶（ナノ結晶ともいう。）を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

**【0102】**

CAAC-OS 膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100 nm未満の立方体内に収まる大きさである。従って、CAAC-OS 膜に含まれる結晶部は、一辺が10 nm未満、5 nm未満または3 nm未満の立方体内に収まる大きさの場合も含まれる。CAAC-OS 膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、CAAC-OS 膜について詳細な説明を行う。

20

**【0103】**

CAAC-OS 膜を透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって観察すると、結晶部同士の明確な境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、CAAC-OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0104】**

30

CAAC-OS 膜を、試料面と概略平行な方向から TEM によって観察（断面 TEM 観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS 膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、CAAC-OS 膜の被形成面または上面と平行に配列する。

**【0105】**

本明細書において、「平行」とは、二つの直線が -10° 以上 10° 以下の角度で配置されている状態をいう。従って、-5° 以上 5° 以下の場合も含まれる。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。従って、85° 以上 95° 以下の場合も含まれる。

**【0106】**

40

一方、CAAC-OS 膜を、試料面と概略垂直な方向から TEM によって観察（平面 TEM 観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0107】**

断面 TEM 観察および平面 TEM 観察より、CAAC-OS 膜の結晶部は配向性を有していることがわかる。

**【0108】**

CAAC-OS 膜に対し、X線回折 (XRD : X-Ray Diffraction) 装置を用いて構造解析を行うと、例えば InGaN<sub>0.4</sub>O の結晶を有する CAAC-OS 膜

50

の out-of-plane 法による解析では、回折角(2)が31°。近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub>の結晶の(009)面に帰属されることから、CAAC-O<sub>S</sub>膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

#### 【0109】

一方、CAAC-O<sub>S</sub>膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、2が56°。近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub>の結晶の(110)面に帰属される。InGaN<sub>0.4</sub>の単結晶酸化物半導体膜であれば、2を56°。近傍に固定し、試料面の法線ベクトルを軸(軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAAC-O<sub>S</sub>膜の場合は、2を56°。近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

10

#### 【0110】

以上のことから、CAAC-O<sub>S</sub>膜では、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面TEM観察で確認された層状に配列した金属原子の各層は、結晶のab面に平行な面である。

#### 【0111】

なお、結晶部は、CAAC-O<sub>S</sub>膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAAC-O<sub>S</sub>膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAAC-O<sub>S</sub>膜の形状をエッティングなどによって変化させた場合、結晶のc軸がCAAC-O<sub>S</sub>膜の被形成面または上面の法線ベクトルと平行にならないこともある。

20

#### 【0112】

また、CAAC-O<sub>S</sub>膜中の結晶化度が均一でなくてもよい。例えば、CAAC-O<sub>S</sub>膜の結晶部が、CAAC-O<sub>S</sub>膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、CAAC-O<sub>S</sub>膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

#### 【0113】

30

なお、InGaN<sub>0.4</sub>の結晶を有するCAAC-O<sub>S</sub>膜のout-of-plane法による解析では、2が31°。近傍のピークの他に、2が36°。近傍にもピークが現れる場合がある。2が36°。近傍のピークは、CAAC-O<sub>S</sub>膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-O<sub>S</sub>膜は、2が31°。近傍にピークを示し、2が36°。近傍にピークを示さないことが好ましい。

#### 【0114】

CAAC-O<sub>S</sub>膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### 【0115】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAAC-O<sub>S</sub>膜のうち、二種以上を有する積層膜であってもよい。

40

#### 【0116】

CAAC-O<sub>S</sub>膜は、例えば、多結晶である金属酸化物ターゲットを用い、スパッタリング法によって成膜する。当該ターゲットにイオンが衝突すると、ターゲットに含まれる結晶領域がa-b面から劈開し、a-b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC-O<sub>S</sub>膜を成膜することができる。

#### 【0117】

また、CAAC-O<sub>S</sub>膜を成膜するために、以下の条件を適用することが好ましい。

50

## 【0118】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、処理室内に存在する不純物濃度（水素、水、二酸化炭素、及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が -80 以下、好ましくは -100 以下である成膜ガスを用いる。

## 【0119】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタリング粒子の平らな面が基板に付着する。10

## 【0120】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積%以上、好ましくは 100 体積%とする。

## 【0121】

ターゲットの一例として、In-Ga-Zn 系酸化物ターゲットについて以下に示す。

## 【0122】

In<sub>x</sub>O<sub>y</sub> 粉末、Ga<sub>y</sub>O<sub>z</sub> 粉末及びZn<sub>y</sub>O<sub>z</sub> 粉末を所定の mol 数比で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理をすることで多結晶である In-Ga-Zn 系酸化物ターゲットとする。なお、X、Y 及び Z は任意の正数である。ここで、所定の mol 数比は、例えば、In<sub>x</sub>O<sub>y</sub> 粉末、Ga<sub>y</sub>O<sub>z</sub> 粉末及びZn<sub>y</sub>O<sub>z</sub> 粉末が、2 : 2 : 1、8 : 4 : 3、3 : 1 : 1、1 : 1 : 1、4 : 2 : 3 または 3 : 1 : 2 である。なお、粉末の種類、及びその混合する mol 数比は、作製するターゲットによって適宜変更すればよい。20

## 【0123】

なお、アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうち Na は、酸化物半導体膜に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散して Na<sup>+</sup> となる。また、Na は、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、或いは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフトすることによるノーマリオン化、移動度の低下等の、トランジスタの電気的特性の劣化が起り、加えて、特性のばらつきも生じる。具体的に、二次イオン質量分析法による Na 濃度の測定値は、5 × 10<sup>-16</sup> / cm<sup>3</sup> 以下、好ましくは 1 × 10<sup>-16</sup> / cm<sup>3</sup> 以下、更に好ましくは 1 × 10<sup>-15</sup> / cm<sup>3</sup> 以下とするとよい。同様に、Li 濃度の測定値は、5 × 10<sup>-15</sup> / cm<sup>3</sup> 以下、好ましくは 1 × 10<sup>-15</sup> / cm<sup>3</sup> 以下とするとよい。同様に、K 濃度の測定値は、5 × 10<sup>-15</sup> / cm<sup>3</sup> 以下、好ましくは 1 × 10<sup>-15</sup> / cm<sup>3</sup> 以下とするとよい。30

## 【0124】

また、インジウムを含む金属酸化物が用いられている場合に、酸素との結合エネルギーがインジウムよりも大きいシリコンや炭素が、インジウムと酸素の結合を切断し、酸素欠損を形成することがある。そのため、シリコンや炭素が酸化物半導体膜に混入していると、アルカリ金属やアルカリ土類金属の場合と同様に、トランジスタの電気的特性の劣化が起こりやすい。よって、酸化物半導体膜中におけるシリコンや炭素の濃度は低いことが望ましい。具体的に、二次イオン質量分析法による C 濃度の測定値、または Si 濃度の測定値は、1 × 10<sup>-18</sup> / cm<sup>3</sup> 以下とするとよい。上記構成により、トランジスタの電気的特性の劣化を防ぐことができ、PLD または半導体装置の信頼性を高めることができる。40

## 【0125】

また、ソース電極及びドレイン電極に用いられる導電性材料によっては、ソース電極及びドレイン電極中の金属が、酸化物半導体膜から酸素を引き抜くことがある。この場合、酸50

化物半導体膜のうち、ソース電極及びドレイン電極に接する領域が、酸素欠損の形成によりn型化される。

【0126】

n型化された領域は、ソース領域またはドレイン領域として機能するため、酸化物半導体膜とソース電極及びドレイン電極との間におけるコンタクト抵抗を下げることができる。よって、n型化された領域が形成されることで、トランジスタの移動度及びオン電流を高めることができ、それにより、トランジスタを用いたスイッチ回路の高速動作を実現することができる。

【0127】

なお、ソース電極及びドレイン電極中の金属による酸素の引き抜きは、ソース電極及びドレイン電極をスパッタリング法などにより形成する際に起こりうるし、ソース電極及びドレイン電極を形成した後に行われる加熱処理によっても起こりうる。

10

【0128】

また、n型化される領域は、酸素と結合し易い導電性材料をソース電極及びドレイン電極に用いることで、より形成されやすくなる。上記導電性材料としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどが挙げられる。

【0129】

また、酸化物半導体膜は、単数の金属酸化物膜で構成されているとは限らず、積層された複数の金属酸化物膜で構成されていても良い。例えば、第1乃至第3の金属酸化物膜が順に積層されている半導体膜の場合、第1の金属酸化物膜及び第3の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つを、その構成要素に含み、伝導帯下端のエネルギーが第2の金属酸化物膜よりも0.05eV以上、0.07eV以上、0.1eV以上または0.15eV以上、かつ2eV以下、1eV以下、0.5eV以下または0.4eV以下、真空準位に近い酸化物膜である。さらに、第2の金属酸化物膜は、少なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

20

【0130】

上記構成の半導体膜をトランジスタが有する場合、ゲート電極に電圧を印加することで、半導体膜に電界が加わると、半導体膜のうち、伝導帯下端のエネルギーが小さい第2の金属酸化物膜にチャネル領域が形成される。即ち、第2の金属酸化物膜とゲート絶縁膜との間に第3の金属酸化物膜が設けられていることによって、ゲート絶縁膜と離隔している第2の金属酸化物膜に、チャネル領域を形成することができる。

30

【0131】

また、第3の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つをその構成要素に含むため、第2の金属酸化物膜と第3の金属酸化物膜の界面では、界面散乱が起こりにくい。従って、当該界面においてキャリアの動きが阻害されにくいため、トランジスタの電界効果移動度が高くなる。

【0132】

また、第2の金属酸化物膜と第1の金属酸化物膜の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、トランジスタの閾値電圧が変動してしまう。しかし、第1の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つをその構成要素に含むため、第2の金属酸化物膜と第1の金属酸化物膜の界面には、界面準位が形成されにくい。よって、上記構成により、トランジスタの閾値電圧等の電気的特性のばらつきを、低減することができる。

40

【0133】

また、金属酸化物膜間に不純物が存在することによって、各膜の界面にキャリアの流れを阻害する界面準位が形成されることがないよう、複数の酸化物半導体膜を積層させることができ望ましい。積層された金属酸化物膜の膜間に不純物が存在していると、金属酸化物膜間ににおける伝導帯下端のエネルギーの連続性が失われ、界面近傍において、キャリアがトラップされるか、あるいは再結合により消滅してしまうからである。膜間ににおける不純物を低減させることで、主成分である一の金属を少なくとも共に有する複数の金属酸化物膜を

50

、単に積層させるよりも、連続接合（ここでは特に伝導帯下端のエネルギーが各膜の間で連続的に変化するU字型の井戸構造を有している状態）が形成されやすくなる。

#### 【0134】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa乃至 $1 \times 10^{-4}$  Pa程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

10

#### 【0135】

高純度の真性な酸化物半導体を得るためにには、各チャンバー内を高真空排気するのみならず、スパッタリングに用いるガスの高純度化も重要である。上記ガスとして用いる酸素ガスやアルゴンガスの露点を、-40以下、好ましくは-80以下、より好ましくは-100以下とし、使用するガスの高純度化を図ることで、酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

#### 【0136】

例えば、第1の金属酸化物膜または第3の金属酸化物膜は、アルミニウム、シリコン、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、スズ、ランタン、セリウムまたはハフニウムを、第2の金属酸化物膜よりも高い原子数比で含む酸化物膜であればよい。具体的に、第1の金属酸化物膜または第3の金属酸化物膜として、第2の金属酸化物膜よりも上述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物膜を用いると良い。前述の元素は酸素と強く結合するため、酸素欠損が酸化物膜に生じることを抑制する機能を有する。よって、上記構成により、第1の金属酸化物膜または第3の金属酸化物膜を、第2の金属酸化物膜よりも酸素欠損が生じにくい酸化物膜にすることができる。

20

#### 【0137】

具体的に、第2の金属酸化物膜と、第1の金属酸化物膜または第3の金属酸化物膜とが、共にIn-M-Zn系酸化物である場合、第1の金属酸化物膜または第3の金属酸化物膜の原子数比を $In : M : Zn = x_1 : y_1 : z_1$ 、第2の金属酸化物膜の原子数比を $In : M : Zn = x_2 : y_2 : z_2$ とすると、 $y_1 / x_1$ が $y_2 / x_2$ よりも大きくなるように、その原子数比を設定すれば良い。なお、元素MはInよりも酸素との結合力が強い金属元素であり、例えばAl、Ti、Ga、Y、Zr、Sn、La、Ce、NdまたはHf等が挙げられる。好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも1.5倍以上大きくなるように、その原子数比を設定すれば良い。さらに好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも2倍以上大きくなるように、その原子数比を設定すれば良い。より好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも3倍以上大きくなるように、その原子数比を設定すれば良い。さらに、第2の金属酸化物膜において、 $y_2$ が $x_2$ 以上であると、トランジスタに安定した電気的特性を付与できるため好ましい。ただし、 $y_2$ が $x_2$ の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$ は、 $x_2$ の3倍未満であると好ましい。

30

#### 【0138】

なお、第1の金属酸化物膜及び第3の金属酸化物膜の厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、第2の金属酸化物膜の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下であり、さらに好ましくは3nm以上50nm以下である。

40

#### 【0139】

3層構造の半導体膜において、第1の金属酸化物膜乃至第3の金属酸化物膜は、非晶質または結晶質の両方の形態を取りうる。ただし、チャネル領域が形成される第2の金属酸化物膜が結晶質であることにより、トランジスタに安定した電気的特性を付与することがで

50

きるため、第2の金属酸化物膜は結晶質であることが好ましい。

**【0140】**

なお、チャネル形成領域とは、トランジスタの半導体膜のうち、ゲート電極と重なり、かつソース電極とドレイン電極に挟まれる領域を意味する。また、チャネル領域とは、チャネル形成領域において、電流が主として流れる領域をいう。

**【0141】**

例えば、第1の金属酸化物膜及び第3の金属酸化物膜として、スパッタリング法により形成したIn-Ga-Zn系酸化物膜を用いる場合、第1の金属酸化物膜及び第3の金属酸化物膜の成膜には、In-Ga-Zn系酸化物( In : Ga : Zn = 1 : 3 : 2 [原子数比] )であるターゲットを用いることができる。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力を0.4Paとし、基板温度を200とし、DC電力0.5kWとすればよい。10

**【0142】**

また、第2の金属酸化物膜をCAC-OS膜とする場合、第2の金属酸化物膜の成膜には、In-Ga-Zn系酸化物( In : Ga : Zn = 1 : 1 : 1 [原子数比] )であり、多結晶のIn-Ga-Zn系酸化物を含むターゲットを用いることが好ましい。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力を0.4Paとし、基板の温度300とし、DC電力0.5kWとすることができます。20

**【0143】**

なお、トランジスタは、半導体膜の端部が傾斜している構造を有していても良いし、半導体膜の端部が丸みを帯びる構造を有していても良い。

**【0144】**

また、複数の積層された金属酸化物膜を有する半導体膜をトランジスタに用いる場合においても、ソース電極及びドレイン電極に接する領域が、n型化されていても良い。上記構成により、トランジスタの移動度及びオン電流を高め、トランジスタを用いたPLDまたは半導体装置の高速動作を実現することができる。さらに、複数の積層された金属酸化物膜を有する半導体膜をトランジスタに用いる場合、n型化される領域は、チャネル領域となる第2の金属酸化物膜にまで達していることが、トランジスタの移動度及びオン電流を高め、PLDまたは半導体装置のさらなる高速動作を実現する上で、より好ましい。30

**【0145】**

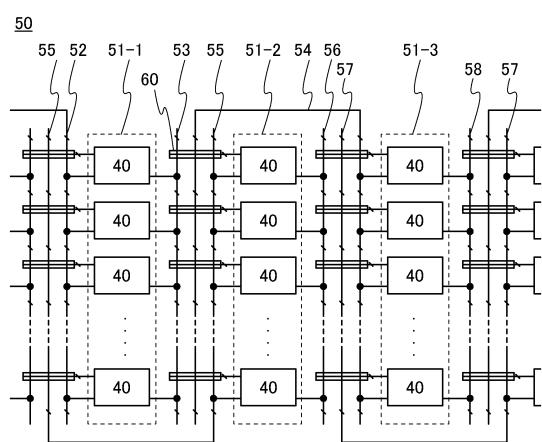

P LDの構成例

次いで、上述したスイッチ回路10を有する、本発明の一態様に係るPLDの構成の一例について説明する。図9(A)に、本発明の一態様に係るPLD50の構成の一部を、例示する。

**【0146】**

図9(A)では、複数のPLE40を有する第1の列51-1と、複数のPLE40を有する第2の列51-2と、複数のPLE40を有する第3の列51-3とが、PLD50に設けられている。図9(A)では、図面に向かって左側から順に、第1の列51-1、第2の列51-2、及び第3の列51-3が、並列に配置されている場合を例示している。40

**【0147】**

また、図9(A)では、複数の配線52と、複数の配線53と、複数の配線54と、複数の配線55と、複数の配線56と、複数の配線57と、複数の配線58とが、PLD50に設けられている。

**【0148】**

そして、第1の列51-1が有する各PLE40の第1出力端子は、複数の配線52のいずれか一つに、それぞれ電気的に接続されている。第1の列51-1が有する各PLE40の第2出力端子は、複数の配線53のいずれか一つに、それぞれ電気的に接続されている。50

**【 0 1 4 9 】**

また、第2の列51-2が有する各P L E 4 0の第1出力端子は、複数の配線55のいずれか一つに、それぞれ電気的に接続されている。第2の列51-2が有する各P L E 4 0の第2出力端子は、複数の配線56のいずれか一つに、それぞれ電気的に接続されている。

**【 0 1 5 0 】**

また、第3の列51-3が有する各P L E 4 0の第1出力端子は、複数の配線54のいずれか一つに、それぞれ電気的に接続されている。第3の列51-3が有する各P L E 4 0の第2出力端子は、複数の配線58のいずれか一つに、それぞれ電気的に接続されている。

10

**【 0 1 5 1 】**

なお、各P L E 4 0が有する第1出力端子の数と、第2出力端子の数は、必ずしも一つとは限らず、いずれか一方が複数であっても良いし、両方とも複数であっても良い。ただし、第1出力端子が複数であっても、第2出力端子が複数であっても、一の配線には、必ず一の出力端子が接続されるものとする。よって、一の列が有するP L E 4 0の数がY(Yは自然数)であるならば、P L D 5 0は、第1出力端子に接続されるY本の配線と、第2出力端子に接続されるY本の配線とを、少なくとも有する。

**【 0 1 5 2 】**

そして、第1の列51-1は、複数の配線52と複数の配線53の間に配置されている。第2の列51-2は、複数の配線55と複数の配線56の間に配置されている。第3の列51-3は、複数の配線54と複数の配線58の間に配置されている。

20

**【 0 1 5 3 】**

さらに、第2の列51-2が有する各P L E 4 0の第1出力端子に接続された複数の配線55は、第1の列51-1と第2の列51-2の間と、第1の列51-1と、図9(A)の図面に向かって第1の列51-1の左側に配置されるP L E 4 0の列(図示せず)の間に、跨るように配置されている。第3の列51-3が有する各P L E 4 0の第1出力端子に接続された複数の配線54は、第1の列51-1と第2の列51-2の間と、第2の列51-2と第3の列51-3の間に、跨るように配置されている。また、図9(A)の図面に向かって第3の列51-3の右側に配置される各P L E 4 0(図示せず)の、第1出力端子に接続された複数の配線57は、第2の列51-2と第3の列51-3の間と、第3の列51-3と第3の列51-3の右側に配置されるP L E 4 0の列(図示せず)の間に、跨るように配置されている。

30

**【 0 1 5 4 】**

すなわち、第Nの列(Nは3以上の自然数)に着目すると、上記列が有する各P L E 4 0の第1出力端子に接続された複数の配線は、第Nの列と第(N-1)の列の間と、第(N-1)の列と第(N-2)の列の間に、跨るように配置されている。なお、Nが2である場合、第2の列が有する各P L E 4 0の第1出力端子に電気的に接続された複数の配線は、第2の列と第1の列の間と、第1の列とI Oの間とに、跨るように配置される。上記I Oは、P L D外部からP L E 4 0への信号の入力、またはP L E 4 0からP L D外部への信号の出力を制御する、インターフェースとしての機能を有する。

40

**【 0 1 5 5 】**

また、本発明の一態様では、第(N-1)の列(Nは3以上の自然数)に着目すると、上記列が有する各P L E 4 0の第1出力端子に電気的に接続された複数の配線と、第Nの列が有する各P L E 4 0の第1出力端子に電気的に接続された複数の配線と、第(N-2)の列が有する各P L E 4 0の第2出力端子に電気的に接続された複数の配線とが、複数のスイッチ回路10を含むスイッチ回路60を介して、第(N-1)の列が有する各P L E 4 0の複数の入力端子に電気的に接続されている。

**【 0 1 5 6 】**

具体的に、図9(A)の場合、例えば、第2の列51-2が有する各P L E 4 0の第1出力端子に電気的に接続された複数の配線55と、第3の列51-3が有する各P L E 4 0

50

の第1出力端子に電気的に接続された複数の配線54と、第1の列51-1が有する各P

L E 4 0 の第2出力端子に電気的に接続された複数の配線53とが、スイッチ回路60を

介して、第2の列51-2が有する各P L E 4 0 の複数の入力端子に電気的に接続されて

いる。

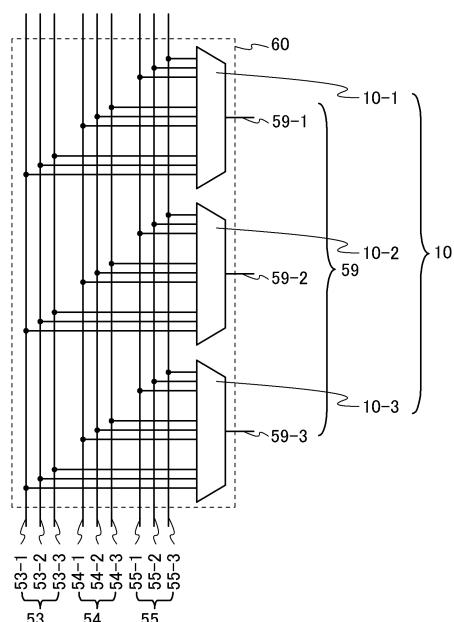

#### 【0157】

図9(B)に、図9(A)に示した、複数の配線53、複数の配線54、及び複数の配線

55と、第2の列51-2が有する各P L E 4 0 の複数の入力端子との、電気的な接続を

制御するスイッチ回路60の回路図を、抜き出して示す。図9(B)において、複数の配

線59は、第2の列51-2が有する一のP L E 4 0 の複数の入力端子に、それぞれ電気

的に接続されている。

10

#### 【0158】

そして、スイッチ回路60は、図1にて例示したスイッチ回路10を複数有する。図9(C)

に、図9(B)に示したスイッチ回路60のより具体的な構成例を示す。図9(B)

に示したスイッチ回路60は、図9(C)に示すように、スイッチ回路10-1、スイッ

チ回路10-2、スイッチ回路10-3で示す、3つのスイッチ回路10を有する。

#### 【0159】

なお、図9(C)では、3本の配線59に対応するスイッチ回路60を例示しているため

、スイッチ回路60が、スイッチ回路10-1、スイッチ回路10-2、及びスイッチ回

路10-3の、3つのスイッチ回路10を有する場合が図示されている。スイッチ回路6

0が有するスイッチ回路10の数は、P L E 4 0 が有する複数の入力端子の数に従って、

定めることができる。

20

#### 【0160】

また、図9(B)及び図9(C)では、複数の配線53、複数の配線54、及び複数の配

線55と、複数の配線59との電気的な接続を制御するスイッチ回路60を代表例として

図示しているが、図9(A)において複数の配線と複数の配線の電気的な接続を制御する

他のスイッチ回路60も、同様の構成を有するものとする。

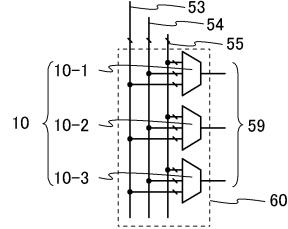

#### 【0161】

次いで、図9(C)に示すスイッチ回路60の、さらに具体的な構成例を図10に示す。

図10では、複数の配線53、複数の配線54、及び複数の配線55と、スイッチ回路6

0との接続関係をより詳細に示している。図10に示すように、各スイッチ回路10は、

複数の配線53、複数の配線54、及び複数の配線55の全てと、複数の配線59の一つ

との電気的な接続を制御する。

30

#### 【0162】

具体的に、図10では、複数の配線53が、配線53-1、配線53-2、配線53-3

を有し、複数の配線54が、配線54-1、配線54-2、配線54-3を有し、複数の

配線55が、配線55-1、配線55-2、配線55-3を有する場合を例示している。

また、図10では、複数の配線59が、配線59-1、配線59-2、配線59-3を有

する場合を例示している。

#### 【0163】

そして、図10では、スイッチ回路10-1が、複数の配線53、複数の配線54、及び

複数の配線55の全てと、配線59-1との電気的な接続を制御する。具体的に、スイッ

チ回路10-1は、複数の配線53、複数の配線54、及び複数の配線55のうち、一の

配線をコンフィギュレーションデータに従って選択し、選択された当該一の配線と配線5

9-1とを電気的に接続する機能を有する。

40

#### 【0164】

図1に示すスイッチ回路10を図10に示すスイッチ回路10-1として用いる場合、図

10に示す複数の配線53、複数の配線54、及び複数の配線55が、図1に示す配線1

4-1乃至配線14-nに相当し、図10に示す配線59-1が、図1に示す配線15に

相当する。

#### 【0165】

50

また、スイッチ回路 10 - 2 は、複数の配線 53、複数の配線 54、及び複数の配線 55 の全てと、配線 59 - 2との電気的な接続を制御する。具体的には、スイッチ回路 10 - 2 は、複数の配線 53、複数の配線 54、及び複数の配線 55 のうち、一の配線をコンフィギュレーションデータに従って選択し、選択された当該一の配線と配線 59 - 2 とを電気的に接続する機能を有する。

#### 【0166】

図 1 に示すスイッチ回路 10 を図 10 に示すスイッチ回路 10 - 2 として用いる場合、図 10 に示す複数の配線 53、複数の配線 54、及び複数の配線 55 が、図 1 に示す配線 14 - 1 乃至配線 14 - n に相当し、図 10 に示す配線 59 - 2 が、図 1 に示す配線 15 に相当する。

10

#### 【0167】

また、スイッチ回路 10 - 3 は、複数の配線 53、複数の配線 54、及び複数の配線 55 の全てと、配線 59 - 3との電気的な接続を制御する。具体的には、スイッチ回路 10 - 3 は、複数の配線 53、複数の配線 54、及び複数の配線 55 のうち、一の配線をコンフィギュレーションデータに従って選択し、選択された当該一の配線と配線 59 - 3 とを電気的に接続する機能を有する。

#### 【0168】

図 1 に示すスイッチ回路 10 を図 10 に示すスイッチ回路 10 - 3 として用いる場合、図 10 に示す複数の配線 53、複数の配線 54、及び複数の配線 55 が、図 1 に示す配線 14 - 1 乃至配線 14 - n に相当し、図 10 に示す配線 59 - 3 が、図 1 に示す配線 15 に相当する。

20

#### 【0169】

上述したように、本発明の一態様では、P L E 40 の出力端子に電気的に接続された配線 53、配線 54、配線 55などの複数の配線のうち、一の配線をコンフィギュレーションデータに従って選択し、選択された当該一の配線と、P L E 40 の入力端子に電気的に接続された配線 59などの一の配線とを、上記スイッチ回路 10 により電気的に接続する。そして、本発明の一態様では、上記構成を有するスイッチ回路 10 を含むスイッチ回路 60 と、スイッチ回路 60 により電気的な接続が制御される上記各種配線とを、第 1 の列 51 - 1、第 2 の列 51 - 2、第 3 の列 51 - 3などのP L E 40 を含む列間に設けることで、図 9 ( A ) に示した P L D 50 において、第 2 の列 51 - 2 が有する一のP L E 40 と、第 2 の列 51 - 2 が有する別の一のP L E 40 の電気的な接続を、一のスイッチ回路 10 により制御することができる。また、第 1 の列 51 - 1 が有する一のP L E 40 と第 2 の列 51 - 2 が有する一のP L E 40 の電気的な接続を、一のスイッチ回路 10 により制御することができる。また、第 2 の列 51 - 2 が有する一のP L E 40 と第 3 の列 51 - 3 が有する一のP L E 40 の電気的な接続を、一のスイッチ回路 10 により制御することができる。よって、図 9 に示す P L E 40 とスイッチ回路 60 の配置と、図 1 に示す構成を有するスイッチ回路 10 の組み合わせにより、本発明の一態様では、P L D 50 における設計の自由度を高めつつ、配線リソースに含まれるスイッチの数を抑えることができる。

30

#### 【0170】

40

I O とプログラマブルロジックエレメントの接続構造について

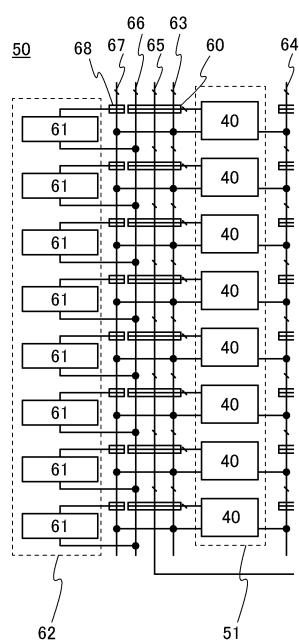

次いで、P L D 50 における、I O とプログラマブルロジックエレメントの接続構造について説明する。図 11 に、本発明の一態様に係る P L D 50 の一部を、例示する。

#### 【0171】

図 11 では、複数のP L E 40 を有する列 51 と、複数のI O 61 を有する列 62 とが、P L D 50 に設けられている。図 11 では、図面に向かって左側から順に、列 62 、及び列 51 が、並列に配置されている場合を例示している。

#### 【0172】

また、図 11 では、複数の配線 63 と、複数の配線 64 と、複数の配線 65 と、複数の配線 66 と、複数の配線 67 とが、P L D 50 に設けられている。

50

**【0173】**

そして、列51が有する各PL40の第1出力端子は、複数の配線63及び複数の配線67にそれぞれ接続されている。列51が有する各PL40の第2出力端子は、複数の配線64にそれぞれ接続されている。列62が有する各IO61の出力端子は、複数の配線66にそれぞれ接続されている。複数の配線65は、図11の図面に向かって列51の右側に配置される複数の各PL40(図示せず)が有する第1出力端子に、それぞれ接続されている。

**【0174】**

なお、各IO61が有する出力端子の数は、必ずしも一つとは限らず、複数であっても良い。ただし、上記出力端子が複数であっても、一の配線には、必ず一の出力端子が接続されるものとする。すなわち、列62が有するIO61の数がY(Yは自然数)であるならば、PLD50は、上記出力端子に電気的に接続されるY本の配線64を、少なくとも有する。

10

**【0175】**

そして、複数の配線63と、複数の配線65と、複数の配線66と、複数の配線67とは、列62と列51の間に配置されている。また、列51は、複数の配線63と複数の配線64の間に設けられている。

**【0176】**

また、図11では、複数の配線63、複数の配線65、及び複数の配線66が、スイッチ回路60を介して、列51が有する各PL40の複数の入力端子に電気的に接続されている。また、図11では、また、複数の配線67が、スイッチ回路68を介して、列62が有する各IO61の入力端子に電気的に接続されている。

20

**【0177】**

そして、スイッチ回路68は、上述した構成を有するスイッチ回路10を一つ有する。スイッチ回路10が有するスイッチ回路68は、複数の配線67のうち、一の配線をコンフィギュレーションデータに従って選択し、選択された当該一の配線と各IO61の入力端子とを接続する機能を有する。

**【0178】**

なお、図9(A)及び図11では、PL40を有する列間に設けられた複数の配線を介して、同一の列に属するPL40どうしが接続される場合を例示している。しかし、同一の列に属するPL40どうしを直接接続する配線が、PLD50に設けられていても良い。

30

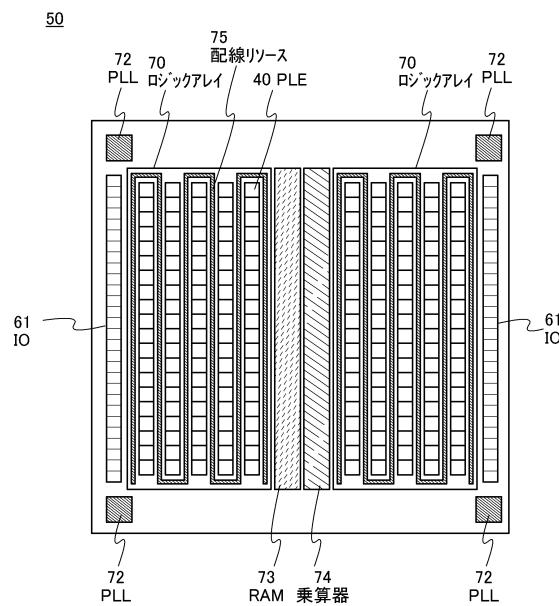

**【0179】****PLDの上面図**

図12に、PLD50の上面図を、一例として示す。

**【0180】**

図12では、PLD50が、ロジックアレイ70と、IO61と、PLL(phase lock loop)72と、RAM73と、乗算器74とを、有している。

**【0181】**

ロジックアレイ70は、複数のPL40と、PL40間の接続を制御する配線及びスイッチが含まれた配線リソース75とを有する。PLL72は、クロック信号CKを生成する機能を有する。RAM73は、論理演算に用いられるデータを格納する機能を有する。乗算器74は、乗算専用の論理回路に相当する。ロジックアレイ70に乗算を行う機能が含まれていれば、乗算器74は必ずしも設ける必要はない。

40

**【0182】**

なお、図12では、各PL40の論理回路を定めるコンフィギュレーションデータが、PLD50の外部に設けられたメモリエレメントに、格納されている場合を例示している。しかし、メモリエレメントは、PLD50に設けられていても良い。

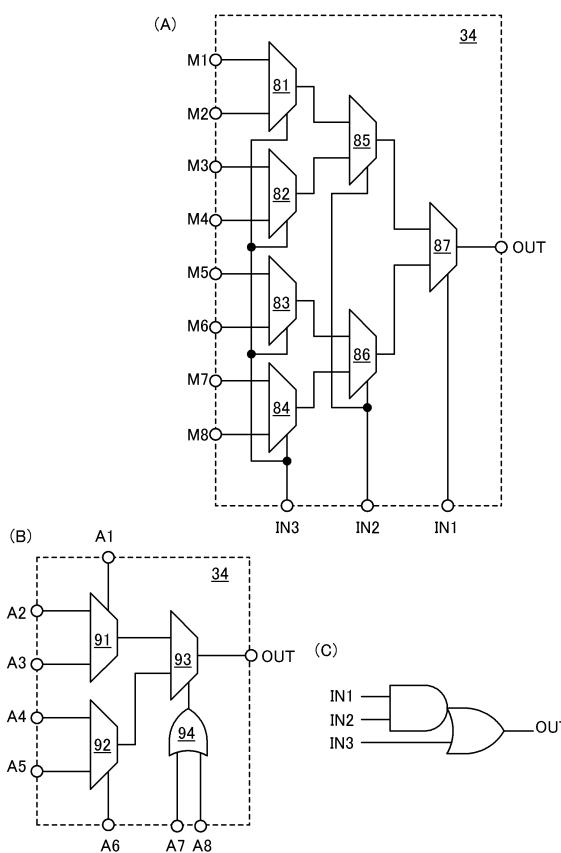

**【0183】****LUTの構成例**

50

本実施の形態では、P L E 4 0 が有するL U T 3 4 の構成例について説明する。L U T 3 4 は複数のマルチブレクサを用いて構成することができる。そして、複数のマルチブレクサの入力端子及び制御端子のうちのいずれかにコンフィギュレーションデータが入力される構成とすることができます。

**【 0 1 8 4 】**

図13(A)に、P L E 4 0 が有するL U T 3 4 の一態様を示す。

**【 0 1 8 5 】**

図13(A)において、L U T 3 4 は、2入力のマルチブレクサを7つ(マルチブレクサ8 1、マルチブレクサ8 2、マルチブレクサ8 3、マルチブレクサ8 4、マルチブレクサ8 5、マルチブレクサ8 6、マルチブレクサ8 7)用いて構成されている。マルチブレクサ8 1乃至マルチブレクサ8 4の各入力端子が、L U T 3 4 の入力端子M 1乃至M 8 に相当する。

10

**【 0 1 8 6 】**

マルチブレクサ8 1乃至マルチブレクサ8 4の各制御端子は電気的に接続されており、上記制御端子が、L U T 3 4 の入力端子I N 3 に相当する。マルチブレクサ8 1の出力端子、及びマルチブレクサ8 2の出力端子は、マルチブレクサ8 5の2つの入力端子と電気的に接続され、マルチブレクサ8 3の出力端子、及びマルチブレクサ8 4の出力端子は、マルチブレクサ8 6の2つの入力端子と電気的に接続されている。マルチブレクサ8 5及びマルチブレクサ8 6の各制御端子は電気的に接続されており、上記制御端子が、L U T 3 4 の入力端子I N 2 に相当する。マルチブレクサ8 5の出力端子、及びマルチブレクサ8 6の出力端子は、マルチブレクサ8 7の2つの入力端子と電気的に接続されている。マルチブレクサ8 7の制御端子は、L U T 3 4 の入力端子I N 1 に相当する。マルチブレクサ8 7の出力端子がL U T 3 4 の出力端子O U T に相当する。

20

**【 0 1 8 7 】**

入力端子M 1乃至入力端子M 8 に、コンフィギュレーションメモリから、当該コンフィギュレーションメモリに格納されたコンフィギュレーションデータに対応した出力信号を入力することによって、L U T 3 4 によって行われる論理演算の種類を定めることができる。

。

**【 0 1 8 8 】**

例えば、図13(A)のL U T 3 4 において、入力端子M 1乃至入力端子M 8 に、コンフィギュレーションメモリから、論理値が”0”、“1”、“0”、“1”、“0”、“1”、“1”、“1”である当該コンフィギュレーションメモリに格納されたコンフィギュレーションデータに対応した出力信号をそれぞれ入力した場合、図13(C)に示す等価回路の機能を実現することができる。

30

**【 0 1 8 9 】**

図13(B)に、P L E 4 0 が有するL U T 3 4 の別のー態様を示す。

**【 0 1 9 0 】**

図13(B)において、L U T 3 4 は、2入力のマルチブレクサを3つ(マルチブレクサ9 1、マルチブレクサ9 2、マルチブレクサ9 3)と、2入力のOR回路9 4とを用いて構成されている。

40

**【 0 1 9 1 】**

マルチブレクサ9 1の出力端子、及びマルチブレクサ9 2の出力端子は、マルチブレクサ9 3の2つの入力端子と電気的に接続されている。OR回路9 4の出力端子はマルチブレクサ9 3の制御端子に電気的に接続されている。マルチブレクサ9 3の出力端子がL U T 3 4 の出力端子O U T に相当する。

**【 0 1 9 2 】**

そして、マルチブレクサ9 1の制御端子A 1、入力端子A 2及び入力端子A 3、マルチブレクサ9 2の制御端子A 6、入力端子A 4及び入力端子A 5、OR回路9 4の入力端子A 7及び入力端子A 8のいずれかに、コンフィギュレーションメモリから、当該コンフィギュレーションメモリに格納されたコンフィギュレーションデータに対応した出力信号を入

50

力することによって、LUT34によって行われる論理演算の種類を定めることができる。

#### 【0193】

例えば、図13(B)のLUT34において、入力端子A2、入力端子A4、入力端子A5、制御端子A6、入力端子A8に、コンフィギュレーションメモリから、論理値が”0”、“1”、“0”、“0”である当該コンフィギュレーションメモリに格納されたコンフィギュレーションデータに対応した出力信号をそれぞれ入力した場合、図13(C)に示す等価回路の機能を実現することができる。なお、上記構成の場合、制御端子A1、入力端子A3、入力端子A7がそれぞれ入力端子IN1、入力端子IN2、入力端子IN3に相当する。

10

#### 【0194】

なお、図13(A)及び図13(B)では、2入力のマルチプレクサを用いて構成したLUT34の例を示したが、より多くの入力のマルチプレクサを用いて構成したLUT34であっても良い。

#### 【0195】

また、LUT34は、マルチプレクサの他に、ダイオード、抵抗素子、論理回路、スイッチのいずれかまたは全てを更に有していても良い。論理回路としては、バッファ、インバータ、NAND回路、NOR回路、スリーステートバッファ、クロックドインバータ等を用いることができる。スイッチとしては、例えばアナログスイッチ、トランジスタ等を用いることができる。

20

#### 【0196】

また、図13(A)や図13(B)に示したLUT34を用いて、図13(C)の様な3入力1出力の論理演算を行う場合について示したがこれに限定されない。LUT34及び入力するコンフィギュレーションデータを適宜定めることによって、より多くの入力、多くの出力の論理演算を実現することができる。

#### 【0197】

##### セルの断面構造の例

図14に、図2に示したスイッチ回路10が有する、トランジスタ11t、トランジスタ12t、及び容量素子16の断面構造を、一例として示す。なお、図14において、トランジスタ13tは図示されていないが、トランジスタ12tと共に作製工程を用いて形成することができる。

30

#### 【0198】

また、本実施の形態では、酸化物半導体膜にチャネル形成領域を有するトランジスタ11tと、容量素子16とが、単結晶のシリコン基板にチャネル形成領域を有するトランジスタ12t上に形成されている場合を例示している。

#### 【0199】

なお、トランジスタ12t、トランジスタ13tは、非晶質、微結晶、多結晶または单結晶である、シリコン又はゲルマニウムなどの半導体膜を活性層に用いることもできる。或いは、トランジスタ12t、トランジスタ13tは、酸化物半導体を活性層に用いていても良い。全てのトランジスタが酸化物半導体を活性層に用いている場合、トランジスタ11tはトランジスタ12t、トランジスタ13t上に積層されていなくとも良く、トランジスタ11tとトランジスタ12t、トランジスタ13tとは、同一の層に形成されても良い。

40

#### 【0200】

薄膜のシリコンを用いてトランジスタ12t、トランジスタ13tを形成する場合、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、单結晶シリコンウェハに水素イオン等を注入して表層部を剥離した单結晶シリコンなどを用いることができる。

#### 【0201】

50

トランジスタ 12t が形成される半導体基板 400 は、例えば、n 型または p 型の導電型を有するシリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板、化合物半導体基板（GaAs 基板、InP 基板、GaN 基板、SiC 基板、GaP 基板、GaInAsP 基板、ZnSe 基板等）等を用いることができる。図 14 では、n 型の導電性を有する単結晶シリコン基板を用いた場合を例示している。

#### 【0202】

また、トランジスタ 12t は、素子分離用絶縁膜 401 により、他のトランジスタと、電気的に分離されている。素子分離用絶縁膜 401 の形成には、選択酸化法（LOCOS（Local Oxidation of Silicon）法）またはトレーナー分離法等を用いることができる。

10

#### 【0203】

具体的に、トランジスタ 12t は、半導体基板 400 に形成された、ソース領域またはドレイン領域として機能する不純物領域 402 及び不純物領域 403 と、ゲート電極 404 と、半導体基板 400 とゲート電極 404 の間に設けられたゲート絶縁膜 405 とを有する。ゲート電極 404 は、ゲート絶縁膜 405 を間に挟んで、不純物領域 402 と不純物領域 403 の間に形成されるチャネル形成領域と重なる。

#### 【0204】

トランジスタ 12t 上には、絶縁膜 409 が設けられている。絶縁膜 409 には開口部が形成されている。そして、上記開口部には、不純物領域 402、不純物領域 403 にそれぞれ接する配線 410、配線 411 と、ゲート電極 404 に電気的に接続されている配線 412 とが、形成されている。

20

#### 【0205】

そして、配線 410 は、絶縁膜 409 上に形成された配線 415 に電気的に接続されており、配線 411 は、絶縁膜 409 上に形成された配線 416 に電気的に接続されており、配線 412 は、絶縁膜 409 上に形成された配線 417 に電気的に接続されている。

#### 【0206】

配線 415 乃至配線 417 上には、絶縁膜 420 及び絶縁膜 440 が順に積層するように形成されている。絶縁膜 420 及び絶縁膜 440 には開口部が形成されており、上記開口部に、配線 417 に電気的に接続された配線 421 が形成されている。

30

#### 【0207】

そして、図 14 では、絶縁膜 440 上にトランジスタ 11t 及び容量素子 16 が形成されている。

#### 【0208】

トランジスタ 11t は、絶縁膜 440 上に、酸化物半導体を含む半導体膜 430 と、半導体膜 430 上の、ソース電極またはドレイン電極として機能する導電膜 432 及び導電膜 433 と、半導体膜 430、導電膜 432 及び導電膜 433 上のゲート絶縁膜 431 と、ゲート絶縁膜 431 上に位置し、導電膜 432 と導電膜 433 の間ににおいて半導体膜 430 と重なっているゲート電極 434 と、を有する。なお、導電膜 433 は、配線 421 に電気的に接続されている。

#### 【0209】

また、ゲート絶縁膜 431 上において導電膜 433 と重なる位置に、導電膜 435 が設けられている。ゲート絶縁膜 431 を間に挟んで導電膜 433 及び導電膜 435 が重なっている部分が、容量素子 16 として機能する。

40

#### 【0210】

なお、図 14 では、容量素子 16 がトランジスタ 11t と共に絶縁膜 440 の上に設けられている場合を例示しているが、容量素子 16 は、トランジスタ 12t と共に、絶縁膜 440 の下に設けられていても良い。

#### 【0211】

そして、トランジスタ 11t、容量素子 16 上に、絶縁膜 441 及び絶縁膜 442 が順に積層するように設けられている。絶縁膜 441 及び絶縁膜 442 には開口部が設けられて

50

おり、上記開口部においてゲート電極434に接する導電膜443が、絶縁膜441上に設けられている。

#### 【0212】

なお、図14において、トランジスタ11tは、ゲート電極434を半導体膜430の片側において少なくとも有していれば良いが、半導体膜430を間に挟んで存在する一対のゲート電極を有していても良い。

#### 【0213】

トランジスタ11tが、半導体膜430を間に挟んで存在する一対のゲート電極を有している場合、一方のゲート電極には導通状態または非導通状態を制御するための信号が与えられ、他方のゲート電極は、電位が他から与えられている状態であっても良い。この場合、一対の電極に、同じ高さの電位が与えられていても良いし、他方のゲート電極にのみ接地電位などの固定の電位が与えられていても良い。他方のゲート電極に与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。10

#### 【0214】

また、図14では、トランジスタ11tが、一のゲート電極434に対応した一のチャネル形成領域を有する、シングルゲート構造である場合を例示している。しかし、トランジスタ11tは、電気的に接続された複数のゲート電極を有することで、一の活性層にチャネル形成領域を複数有する、マルチゲート構造であっても良い。

#### 【0215】

20 電子機器の例

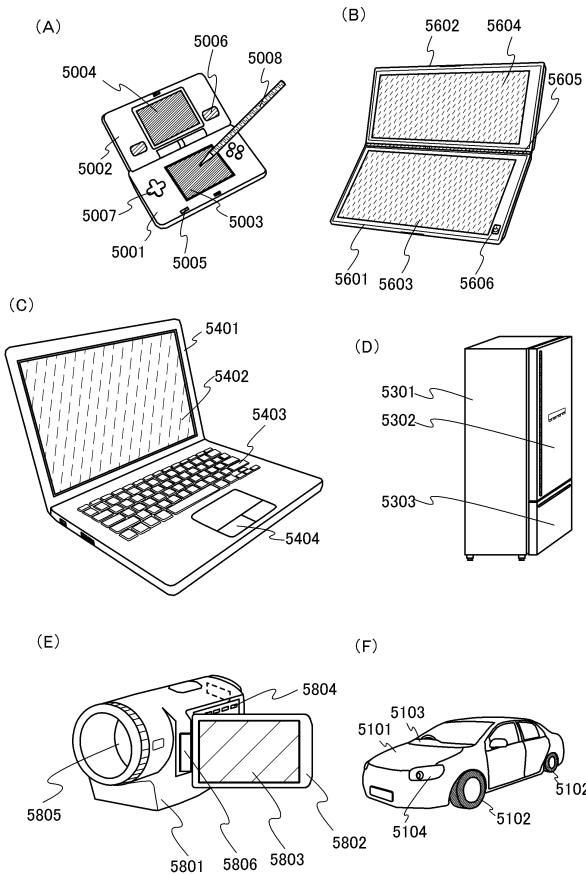

本発明の一態様に係る半導体装置またはプログラマブルロジックデバイスは、表示機器、パソコンコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置またはプログラマブルロジックデバイスを用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリント複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図15に示す。30

#### 【0216】

図15（A）は携帯型ゲーム機であり、筐体5001、筐体5002、表示部5003、表示部5004、マイクロフォン5005、スピーカー5006、操作キー5007、スタイルス5008等を有する。なお、図15（A）に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

#### 【0217】

図15（B）は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602との間の角度は、接続部5605により変更が可能である。第1表示部5603における映像を、接続部5605における第1筐体5601と第2筐体5602との間の角度に従って、切り替える構成としても良い。また、第1表示部5603及び第2表示部5604の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。40

#### 【0218】

図15( C )はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。

【0219】

図15( D )は電気冷凍冷蔵庫であり、筐体5301、冷蔵室用扉5302、冷凍室用扉5303等を有する。

【0220】

図15( E )はビデオカメラであり、第1筐体5801、第2筐体5802、表示部5803、操作キー5804、レンズ5805、接続部5806等を有する。操作キー5804及びレンズ5805は第1筐体5801に設けられており、表示部5803は第2筐体5802に設けられている。そして、第1筐体5801と第2筐体5802とは、接続部5806により接続されており、第1筐体5801と第2筐体5802の間の角度は、接続部5806により変更が可能である。表示部5803における映像を、接続部5806における第1筐体5801と第2筐体5802との間の角度に従って切り替える構成としても良い。10

【0221】

図15( F )は普通自動車であり、車体5101、車輪5102、ダッシュボード5103、ライト5104等を有する。

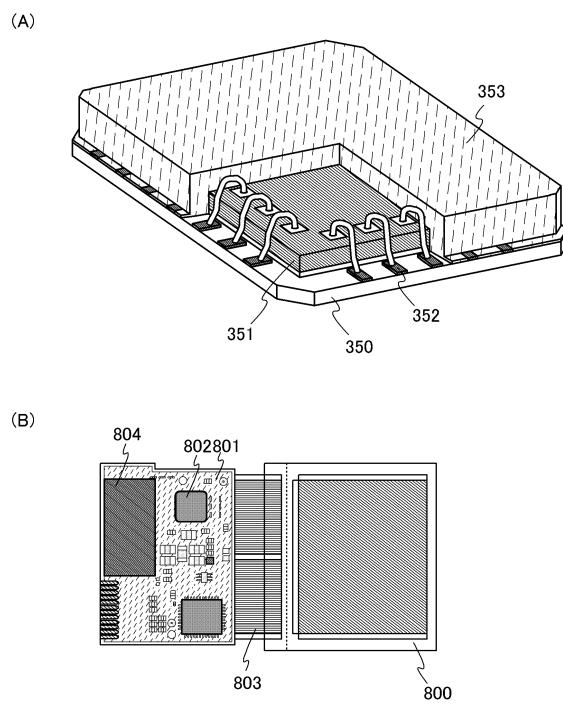

【0222】

チップの構成

図16( A )に、リードフレーム型のインターポーザを用いたパッケージの断面構造を表す斜視図を示す。20

【0223】

図16( A )に示すパッケージは、本発明の一態様にかかる半導体装置に相当するチップ351が、ワイヤボンディング法により、インターポーザ350上の端子352と接続されている。端子352は、インターポーザ350のチップ351がマウントされている面上に配置されている。そしてチップ351はモールド樹脂353によって封止されても良いが、各端子352の一部が露出した状態で封止されるようにする。

【0224】

パッケージが回路基板に実装されている電子機器のモジュールの構成を、図16( B )に示す。30

【0225】

図16( B )に示す携帯電話のモジュールは、プリント配線基板801に、パッケージ802と、バッテリー804とが実装されている。また、表示素子が設けられたパネル800に、プリント配線基板801がFPC803によって実装されている。

【0226】

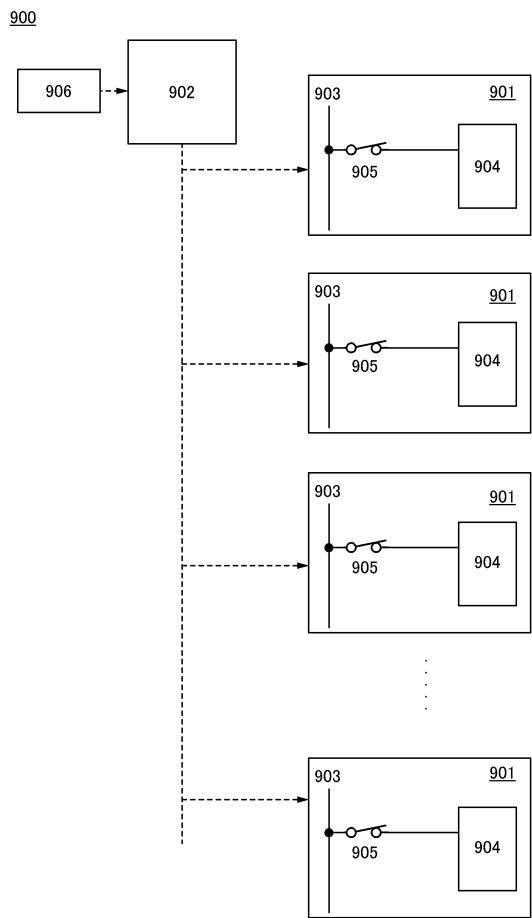

システム

図17に、本発明の一態様に係る半導体装置を用いたシステムの構成を、一例として示す。図17に示すシステム900は、単数または複数のコンポーネント901と、コンポーネント901への電力の供給を個別に制御する指令部902とを有する。本発明の一態様に係る半導体装置は、指令部902に用いることができる。40

【0227】

コンポーネント901は、電源線903と、電力を消費する負荷904と、電源線903と負荷904の電気的な接続を切り替えるスイッチ905とを、それぞれ有する。スイッチ905がオン(導通状態)であるとき、電源線903からスイッチ905を介して負荷904に電力が供給される。スイッチ905がオフ(非導通状態)であるとき、電源線903から負荷904への電力の供給は停止される。

【0228】

指令部902は、コンポーネント901がそれぞれ有するスイッチ905のオンまたはオフを個別に制御する機能を有する。そして、コンポーネント901のそれぞれにおける、スイッチ905のオンとオフの選択は、システム900の外部から指令部902に入力さ50

れる命令に従って行うことができる。

#### 【0229】

なお、コンポーネントが有する負荷が他のコンポーネントの負荷と相互作用して動作する場合、指令部902によるスイッチ905のオンまたはオフの制御を一斉に行う構成としてもよい。従って、本実施の形態のシステムは、外部からみると、所定の目的を実現するために必要なコンポーネントに、動作に必要な期間だけ電力を供給し、それぞれのコンポーネントが時間的に逐次連動して動作しているようにシステムを駆動させることができる。

#### 【0230】

或いは、システム900が、負荷904における電力の消費量を監視できる電流計などを有し、負荷904における電力の量に応じて、負荷904への電力の供給が要か不要かを、指令部902において判断しても良い。例えば、一定の期間に渡って、負荷904における電力の消費量が、負荷904が待機状態の時に消費されるリーク電力と同程度である場合に、指令部902は、負荷904への電力の供給が不要であると、判断することができる。

10

#### 【0231】

或いは、システム900がセンサ回路を有し、当該センサ回路において取得される光、音、温度、磁気、圧力などの物理量を用いて負荷904の利用環境及び／または周囲環境を監視し、該監視による変化に応じて、負荷904への電力の供給が要か不要かを、指令部902において判断しても良い。この場合、指令部902は、電力の供給が要か不要かの判断結果に従って、スイッチ905のオンとオフの選択を行う。

20

#### 【0232】

例えば、本発明の一態様に係るシステム900を家屋に適用させ、家屋に設けられた照明、電気ヒーター、空気清浄機などの家電が各コンポーネントに相当するものとする。この場合、光センサを有するセンサ回路を用いて、照明が用いられている部屋の明るさを監視する。そして、窓から差し込む光の量が変化することで部屋がある規定値よりも明るくなつた場合に、指令部902は、照明への電力の供給を停止すべく、照明のスイッチ905をオンからオフに変更させることができる。

#### 【0233】

或いは、温度センサを有するセンサ回路を用いて、具体的には、電気ヒーターが用いられている部屋の温度を監視する。そして、外気温が変化することで部屋の温度がある規定値よりも高くなつた場合に、指令部902は、電気ヒーターへの電力の供給を停止すべく、電気ヒーターのスイッチ905をオンからオフに変更させることができる。

30

#### 【0234】

或いは、光センサを有するセンサ回路906を用いて、空気清浄機が用いられている部屋の使用状況を監視する。そして、一定期間、センサ回路906により人の動きが感知できなかつた場合に、指令部902は、空気清浄機への電力の供給を停止すべく、空気清浄機のスイッチ905をオンからオフに変更させることができる。

#### 【0235】

なお、上記家電がコンポーネントに相当する場合、スイッチ905は各家電に内蔵されている。家電の外部にスイッチ905が設けられている場合、家電は負荷904に相当し、コンポーネントは、負荷904である家電とスイッチ905とを含むものとする。

40

#### 【0236】

また各コンポーネントが独立して備えられている場合、指令部902によるスイッチ905のオンとオフの選択は、無線信号を用いて行うようにすればよい。この場合、スイッチ905は不揮発性のスイッチとして、指令部902からのスイッチの状態を変更するための信号を保持する構成とすることが好ましい。

#### 【0237】

センサ回路906は、センサと、センサから出力されるセンサ信号を処理するための回路群で構成されている。そして、センサとして、温度センサ、磁気センサ、光センサ、マイ

50

クロフォン、歪みゲージ、圧力センサ、ガスセンサなどを用いることができる。温度センサは測温抵抗体、サーミスタ、熱電対、I C 温度センサなどの接触式であっても良いし、熱型赤外線センサ、量子型赤外線センサなどの非接触式であっても良い。

#### 【0238】

なお、各コンポーネントが独立して備えられている場合、コンポーネント毎にセンサ回路を設け、センサ回路で得られたデータを無線信号により指令部902に送信するようすればよい。図17に示すように、センサ回路906は、各コンポーネントに設けられ、物理量に関するデータを個別に指令部902に送信する。指令部902は、各コンポーネントに設けられたセンサ回路906で取得する物理量を監視し、負荷904への電力の供給が要か不要か判断する。

10

#### 【0239】

また、センサ回路906は、物理量に関するデータを指令部902に送信する。指令部902は、センサ回路906で取得する物理量を監視し、負荷904への電力の供給が要か不要か判断する。例えば、センサ回路906により、一のコンポーネント内の温度が規定値以上であると判断した場合に、別のコンポーネントが有する、スピーカーなどの音声を発する機器である負荷904に、電力の供給を開始することができる。上記構成によりシステム900は、警報システムとしての機能を果たすこともできる。

#### 【0240】

なおコンポーネントは、コンピュータ、検知器、テレビジョン等の電子機器や、コンピュータシステムを構成する機器(CPU、メモリ、HDD、プリンタ、モニター)や自動車に組み込まれる電気制御機器であってもよい。或いは、CPUや半導体メモリのようなLSIの内部構成であってもよい。なおここで、コンピュータとは、タブレット型のコンピュータや、ノート型のコンピュータや、デスクトップ型のコンピュータの他、サーバシステムのような大型のコンピュータを含むものである。

20

#### 【0241】

またコンポーネントの概念は、電力供給により動作する電子機器の他、システムが必要な、社会インフラ、住宅等の広い概念にも適用可能である。

#### 【0242】

ここで、本発明の一態様であるシステムを社会インフラ等の広い概念に適用する場合の、具体的な適用対象を例示する。例えば、社会インフラに本発明の一態様であるシステムを適用する場合、図17に示すコンポーネントとしては鉄道、港湾、道路等を挙げることができ、指令部としては変電所または発電所等を挙げることができる。また別の例として、図17に示すコンポーネントとしては、建物の部屋や階層等のセクションを挙げることができ、指令部として電源管理施設や配電盤等を挙げができる。

30

#### 【符号の説明】

#### 【0243】

- 10 スイッチ回路

- 10 - 1 スイッチ回路

- 10 - 2 スイッチ回路

- 10 - 3 スイッチ回路

- 11 スイッチ

- 11 t トランジスタ

- 12 スイッチ

- 12 t トランジスタ

- 13 スイッチ

- 13 t トランジスタ

- 14 配線

- 14 - i 配線

- 14 - n 配線

- 14 - 1 配線

40

50

|           |                |    |

|-----------|----------------|----|

| 1 5       | 配線             |    |

| 1 6       | 容量素子           |    |

| 1 7       | 配線             |    |

| 1 7 - j   | 配線             |    |

| 1 7 - m   | 配線             |    |

| 1 7 - 1   | 配線             |    |

| 1 8       | 配線             |    |

| 1 8 - j   | 配線             |    |

| 1 8 - m   | 配線             |    |

| 1 8 - 1   | 配線             | 10 |

| 1 9       | 配線             |    |

| 2 0       | 回路             |    |

| 2 0 - i   | 回路             |    |

| 2 0 - j i | 回路             |    |

| 2 0 - m 1 | 回路             |    |

| 2 0 - m n | 回路             |    |

| 2 0 - n   | 回路             |    |

| 2 0 - 1   | 回路             |    |

| 2 0 - 1 n | 回路             |    |

| 2 0 - 1 1 | 回路             | 20 |

| 2 0 _ m 1 | 回路             |    |

| 2 0 _ m n | 回路             |    |

| 2 0 _ 1 1 | 回路             |    |

| 2 1       | 組              |    |

| 2 1 - j   | 組              |    |

| 2 1 - m   | 組              |    |

| 2 1 - 1   | 組              |    |

| 2 2       | スイッチ           |    |

| 2 3       | ラッチ            |    |

| 2 4       | インバータ          | 30 |

| 2 5       | トランジスタ         |    |

| 2 6       | 配線             |    |

| 3 0       | 駆動回路           |    |

| 3 1       | 回路             |    |

| 3 2       | 回路             |    |

| 3 3       | スイッチ           |    |

| 3 4       | L U T          |    |

| 3 5       | フリップフロップ       |    |

| 3 6       | コンフィギュレーションメモリ |    |

| 3 7       | 入力端子           | 40 |

| 3 8       | スイッチ           |    |

| 4 0       | P L E          |    |

| 4 1       | A N D 回路       |    |

| 4 2       | マルチプレクサ        |    |

| 4 3       | コンフィギュレーションメモリ |    |

| 5 0       | P L D          |    |

| 5 1       | 列              |    |

| 5 1 - 1   | 列              |    |

| 5 1 - 2   | 列              |    |

| 5 1 - 3   | 列              | 50 |

|         |         |    |

|---------|---------|----|

| 5 2     | 配線      |    |

| 5 3     | 配線      |    |

| 5 3 - 1 | 配線      |    |

| 5 3 - 2 | 配線      |    |

| 5 3 - 3 | 配線      |    |

| 5 4     | 配線      |    |

| 5 4 - 1 | 配線      |    |

| 5 4 - 2 | 配線      |    |

| 5 4 - 3 | 配線      |    |

| 5 5     | 配線      | 10 |

| 5 5 - 1 | 配線      |    |

| 5 5 - 2 | 配線      |    |

| 5 5 - 3 | 配線      |    |

| 5 6     | 配線      |    |

| 5 7     | 配線      |    |

| 5 8     | 配線      |    |

| 5 9     | 配線      |    |

| 5 9 - 1 | 配線      |    |

| 5 9 - 2 | 配線      |    |

| 5 9 - 3 | 配線      | 20 |

| 6 0     | スイッチ回路  |    |

| 6 1     | I O     |    |

| 6 2     | 列       |    |

| 6 3     | 配線      |    |

| 6 4     | 配線      |    |

| 6 5     | 配線      |    |

| 6 6     | 配線      |    |

| 6 7     | 配線      |    |

| 6 8     | スイッチ回路  |    |

| 7 0     | ロジックアレイ | 30 |

| 7 2     | P L L   |    |

| 7 3     | R A M   |    |

| 7 4     | 乗算器     |    |

| 7 5     | 配線リソース  |    |

| 8 1     | マルチプレクサ |    |

| 8 2     | マルチプレクサ |    |

| 8 3     | マルチプレクサ |    |

| 8 4     | マルチプレクサ |    |

| 8 5     | マルチプレクサ |    |

| 8 6     | マルチプレクサ | 40 |

| 8 7     | マルチプレクサ |    |

| 9 1     | マルチプレクサ |    |

| 9 2     | マルチプレクサ |    |

| 9 3     | マルチプレクサ |    |

| 9 4     | O R 回路  |    |

| 3 5 0   | インターポーラ |    |

| 3 5 1   | チップ     |    |

| 3 5 2   | 端子      |    |

| 3 5 3   | モールド樹脂  |    |

| 4 0 0   | 半導体基板   | 50 |

|         |          |    |

|---------|----------|----|

| 4 0 1   | 素子分離用絶縁膜 |    |

| 4 0 2   | 不純物領域    |    |

| 4 0 3   | 不純物領域    |    |

| 4 0 4   | ゲート電極    |    |

| 4 0 5   | ゲート絶縁膜   |    |

| 4 0 9   | 絶縁膜      |    |

| 4 1 0   | 配線       | 10 |

| 4 1 1   | 配線       |    |

| 4 1 2   | 配線       |    |

| 4 1 5   | 配線       |    |

| 4 1 6   | 配線       |    |

| 4 1 7   | 配線       |    |

| 4 2 0   | 絶縁膜      |    |

| 4 2 1   | 配線       |    |

| 4 3 0   | 半導体膜     |    |

| 4 3 1   | ゲート絶縁膜   |    |

| 4 3 2   | 導電膜      |    |

| 4 3 3   | 導電膜      |    |

| 4 3 4   | ゲート電極    |    |

| 4 3 5   | 導電膜      | 20 |

| 4 4 0   | 絶縁膜      |    |

| 4 4 1   | 絶縁膜      |    |

| 4 4 2   | 絶縁膜      |    |

| 4 4 3   | 導電膜      |    |

| 8 0 0   | パネル      |    |

| 8 0 1   | プリント配線基板 |    |

| 8 0 2   | パッケージ    |    |

| 8 0 3   | F P C    |    |

| 8 0 4   | パッテリー    |    |

| 9 0 0   | システム     | 30 |

| 9 0 1   | コンポーネント  |    |

| 9 0 2   | 指令部      |    |

| 9 0 3   | 電源線      |    |

| 9 0 4   | 負荷       |    |

| 9 0 5   | スイッチ     |    |

| 9 0 6   | センサ回路    |    |

| 5 0 0 1 | 筐体       |    |

| 5 0 0 2 | 筐体       |    |

| 5 0 0 3 | 表示部      |    |

| 5 0 0 4 | 表示部      | 40 |

| 5 0 0 5 | マイクロフォン  |    |

| 5 0 0 6 | スピーカー    |    |

| 5 0 0 7 | 操作キー     |    |

| 5 0 0 8 | スタイラス    |    |

| 5 1 0 1 | 車体       |    |

| 5 1 0 2 | 車輪       |    |

| 5 1 0 3 | ダッシュボード  |    |

| 5 1 0 4 | ライト      |    |

| 5 3 0 1 | 筐体       |    |

| 5 3 0 2 | 冷蔵室用扉    | 50 |

|         |             |    |

|---------|-------------|----|

| 5 3 0 3 | 冷凍室用扉       |    |

| 5 4 0 1 | 筐体          |    |

| 5 4 0 2 | 表示部         |    |

| 5 4 0 3 | キー ボード      |    |

| 5 4 0 4 | ポインティングデバイス |    |

| 5 6 0 1 | 筐体          |    |

| 5 6 0 2 | 筐体          |    |

| 5 6 0 3 | 表示部         |    |

| 5 6 0 4 | 表示部         |    |

| 5 6 0 5 | 接続部         | 10 |

| 5 6 0 6 | 操作キー        |    |

| 5 8 0 1 | 筐体          |    |

| 5 8 0 2 | 筐体          |    |

| 5 8 0 3 | 表示部         |    |

| 5 8 0 4 | 操作キー        |    |

| 5 8 0 5 | レンズ         |    |

| 5 8 0 6 | 接続部         |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

(A)

(B)

(C)

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特開平07-321641(JP,A)

特開平04-188649(JP,A)

特開2011-172214(JP,A)

特開2012-231455(JP,A)

特開2010-124373(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/098 - 19/23

H01L 21/82