(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2013/119513 A1

(43) International Publication Date

15 August 2013 (15.08.2013)

WIPO | PCT

(51) International Patent Classification:

H01L 27/146 (2006.01) H01L 27/14 (2006.01)

(21) International Application Number:

PCT/US2013/024684

(22) International Filing Date:

5 February 2013 (05.02.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/596,694 8 February 2012 (08.02.2012) US

13/425,877 21 March 2012 (21.03.2012) US

(71) Applicant: GTAT CORPORATION [US/US]; 20 Trafalgar Square, Nashua, New Hampshire 03063 (US).

(72) Inventors: MURALI, Venkatesan; 1102 Queensbridge Way, San Jose, California 95120 (US). CHARI, Arvind; 14801 Gypsy Hill Road, Saratoga, California 95070 (US). PRABHU, Gopal; 3500 Quarry Park Drive, San Jose, California 95136 (US). PETTI, Christopher J.; 660 Sierra Avenue, Mountain View, California 94041 (US).

(74) Agents: MUELLER, Heather et al.; The Mueller Law Office, P.C., 12707 High Bluff Drive, Suite 200, San Diego, California 92130 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: METHOD FOR FABRICATING BACKSIDE-ILLUMINATED SENSORS

FIG. 3C

(57) Abstract: A method for fabricating a backside-illuminated sensor includes providing a thin film semiconductor lamina having a first conductivity, and forming a doped region having a second conductivity within the lamina and at a front surface of the lamina. The lamina may be provided as a free-standing lamina, or may be provided as a semiconductor donor body from which the lamina is cleaved. An electrical connection is formed to the doped region. A temporary carrier is contacted to the back surface of the semiconductor and later removed. A backside-illuminated sensor is fabricated from the semiconductor lamina, in which the thickness of the semiconductor lamina remains substantially unchanged during the fabrication process.

WO 2013/119513 A1

## METHOD FOR FABRICATING BACKSIDE-ILLUMINATED SENSORS

### RELATED APPLICATIONS

[001] This application claims priority to U.S. Patent Application No. 13/425,877, filed March 21, 2012, and entitled “Method for Fabricating Backside-Illuminated Sensors”; which claims priority to U.S. Provisional Application No. 61/596,694, filed February 8, 2012, and entitled “Method for Fabricating Backside-Illuminated Sensors,” both of which are hereby incorporated by reference for all purposes. This application is also related to U.S. Patent Application No. 13/425,870, entitled “Back-Contact Photovoltaic Cell Comprising A Thin Lamina Having A Superstrate Receiver Element,” filed March 21, 2012, and which is hereby incorporated by reference for all purposes.

### BACKGROUND OF THE INVENTION

[002] Image sensors receive light and convert the energy into electrical signals based on the amount of light received. Image sensors generally include a silicon light-sensitive layer and electrical circuitry, such as an integrated chip, for processing the electrical signals. It is desirable to increase the pixel density on a chip to improve resolution. However, increasing pixel density creates issues such as crosstalk and denser circuitry wiring.

[003] In frontside-illuminated (FSI) sensors, light enters the “front” of the chip where the metal interconnections lie. Increasing the amount of wiring causes more shadowing and therefore less efficiency of light reaching the silicon light-sensitive layer. In backside-illuminated (BSI) sensors, light enters the silicon side of the chip and therefore does not require passing through the metal interconnect layers. Thus, BSI sensors are desirable for advance image sensing technology. However, BSI sensors require thinner silicon in order for the light to pass through and reach the photoactive layer and therefore have not been as cost-effective to manufacture as FSI sensors. BSI sensors also require precision uniformity in thickness across the chip, which can be difficult to accomplish.

[004] One approach for manufacturing thin semiconductor wafers is utilizing epitaxial silicon, in which layers of silicon are grown on a bulk silicon substrate. The silicon substrate is a very thin sheet of typically less than 1.5 microns. Another approach is using a thicker silicon wafer and grinding it down to the desired thinness after the

circuitry and interconnect layers have been formed. Because it is difficult to achieve the necessary precision uniformity in thickness with grinding, BSI processing often requires both wafer level grinding and die level polishing. This creates throughput issues, increases cost, and can cause contamination. Other factors in fabricating BSI sensors include differences in processing temperatures at the various stages of manufacturing, which greatly affects the materials and sequence of manufacturing steps, and the ability to handle thin films during fabrication.

#### SUMMARY OF THE INVENTION

[005] A method for fabricating a backside-illuminated sensor includes providing a thin film semiconductor lamina having a first conductivity, and forming a doped region having a second conductivity within the lamina and at a front surface of the lamina. An electrical connection is formed to the doped region. A temporary carrier is contacted to the back surface of the semiconductor and later removed. A backside-illuminated sensor is fabricated from the semiconductor lamina, in which the thickness of the provided semiconductor lamina remains substantially unchanged during the fabrication.

[006] In other embodiments, a method for fabricating a backside-illuminated sensor includes providing a semiconductor donor body having a first conductivity. A doped region of a second conductivity is formed at a first surface of the donor body and within the donor body. Ions are implanted into the first surface to define a cleave plane, and a semiconductor lamina is cleaved from the donor body. The doped region is included in the lamina, and an electrical connection is formed to the doped region. A temporary carrier is contacted to the back surface of the semiconductor and later removed. A backside-illuminated sensor is fabricated from the semiconductor lamina, in which the thickness of the semiconductor lamina remains substantially unchanged during the fabrication.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[007] Each of the aspects and embodiments of the invention described herein can be used alone or in combination with one another. The aspects and embodiments will now be described with reference to the attached drawings.

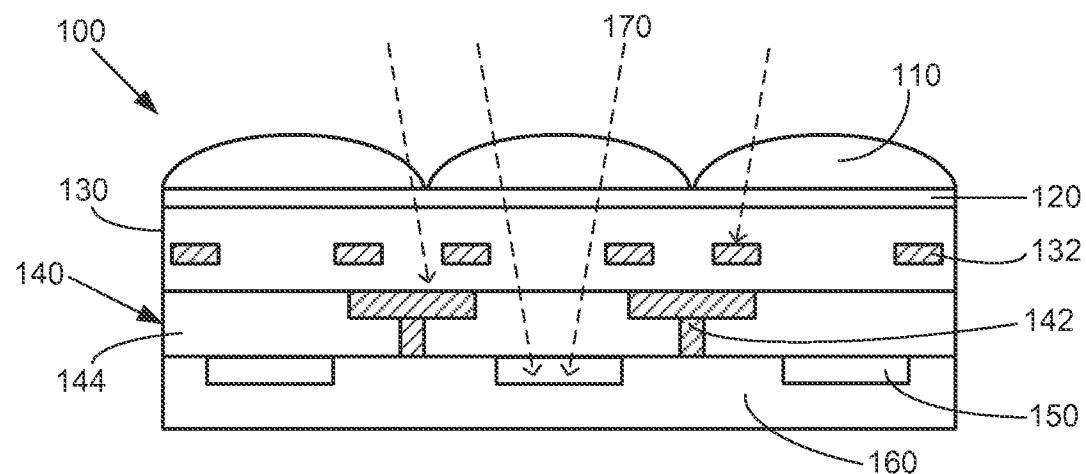

[008] FIG. 1 depicts a cross-sectional view of a conventional frontside-illuminated sensor.

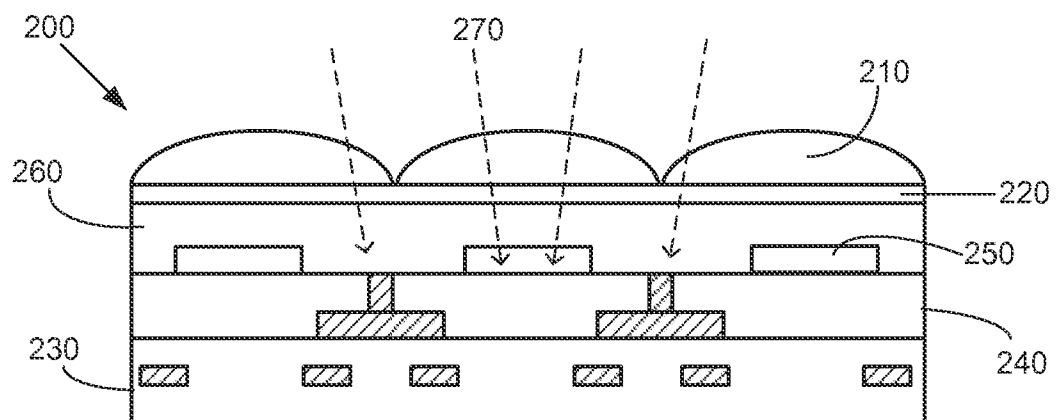

[009] FIG. 2 depicts a cross-sectional view of a conventional backside-illuminated sensor.

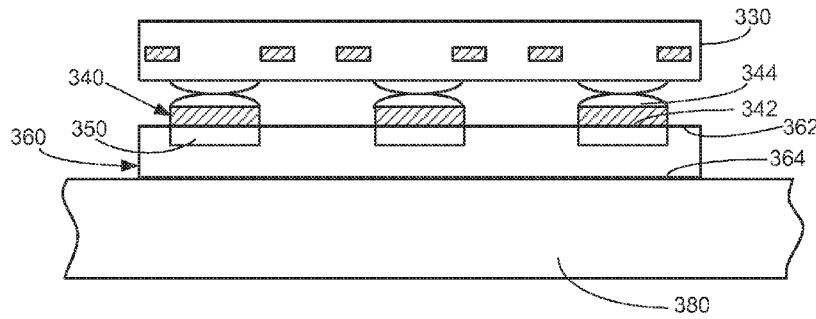

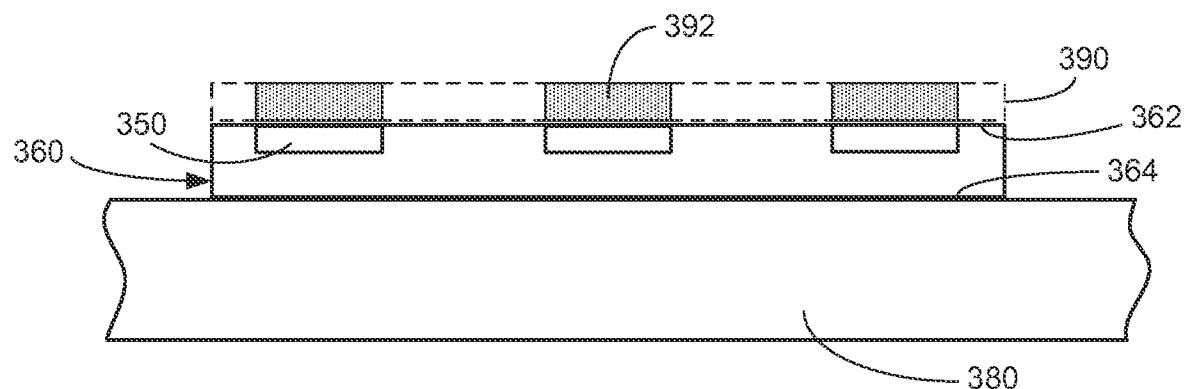

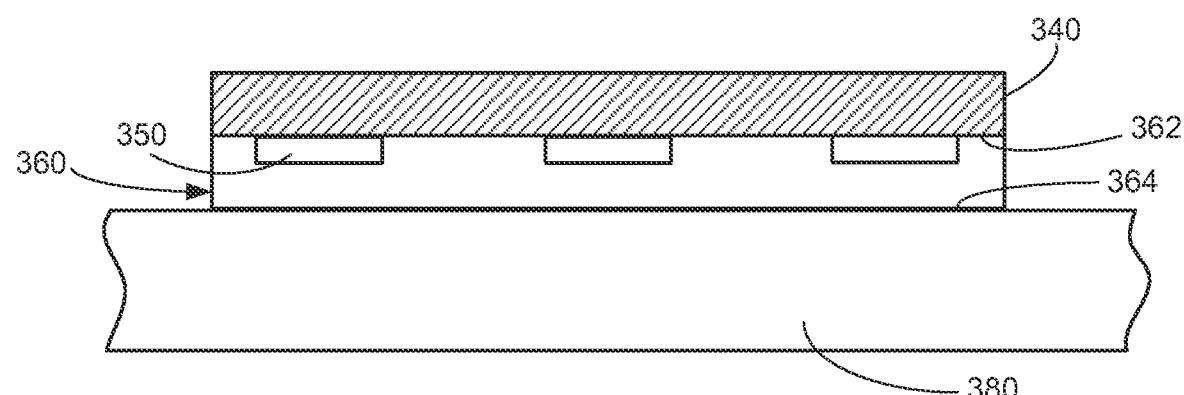

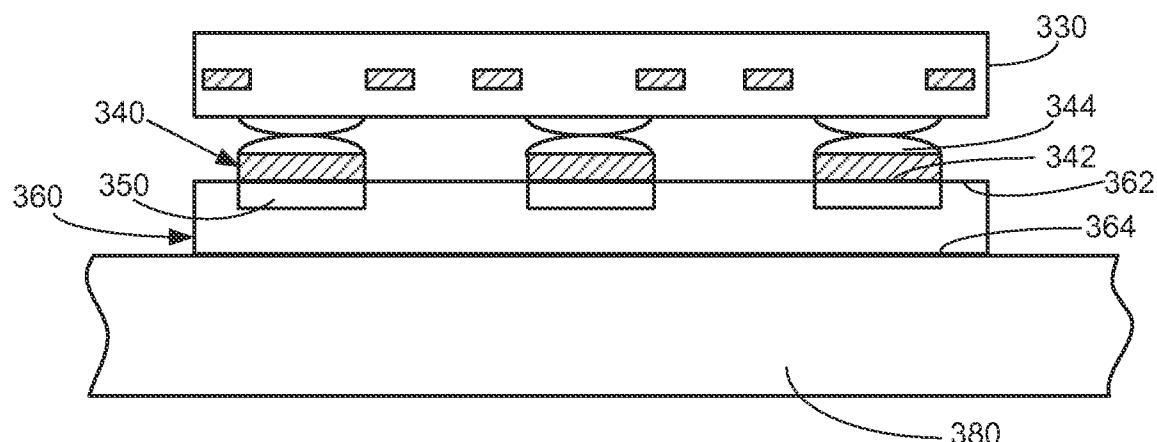

[0010] FIGs. 3A-3C are cross-sectional views of an embodiment of a backside-illuminated sensor in various stages of manufacturing.

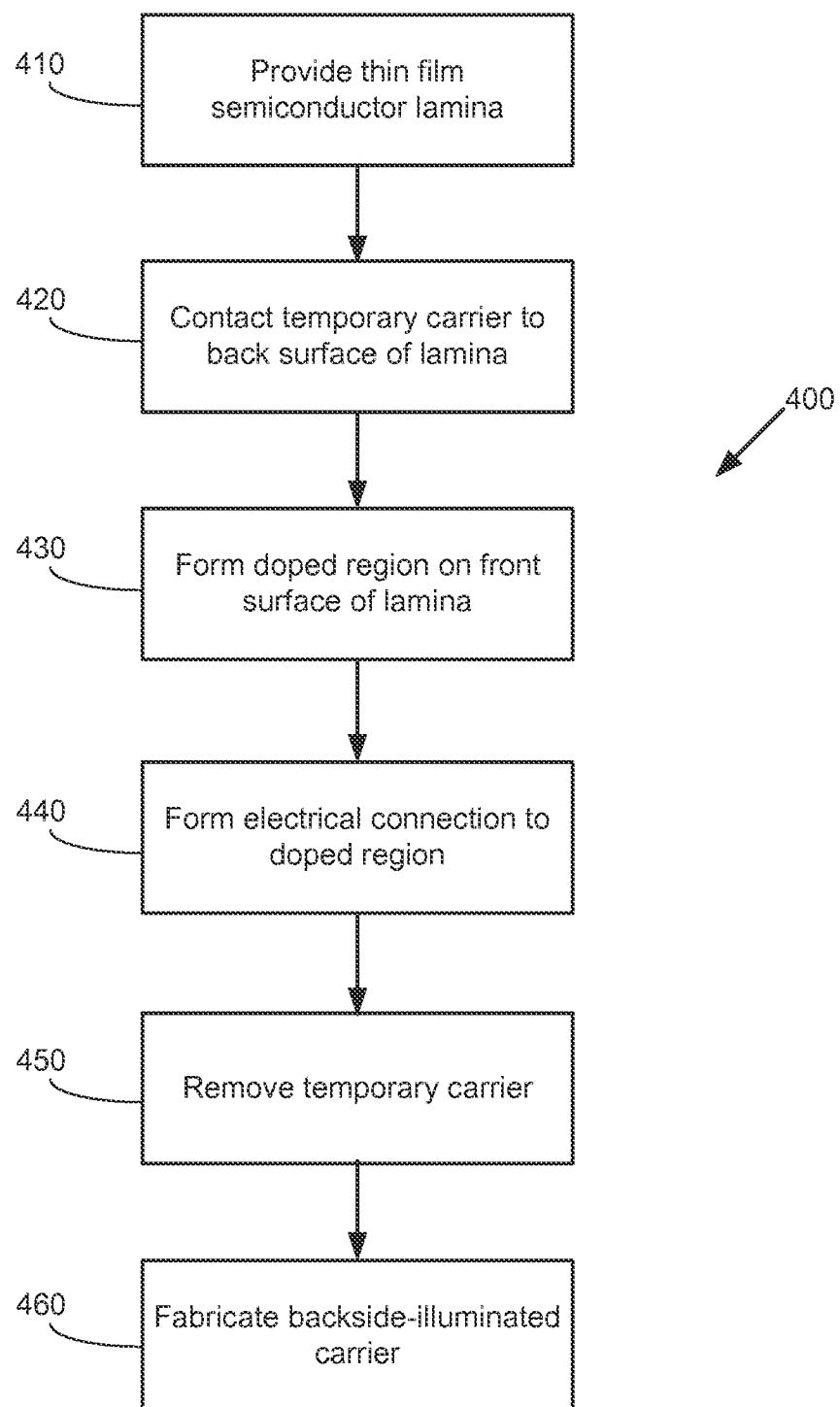

[0011] FIG. 4 is a flowchart of an exemplary method of the present invention.

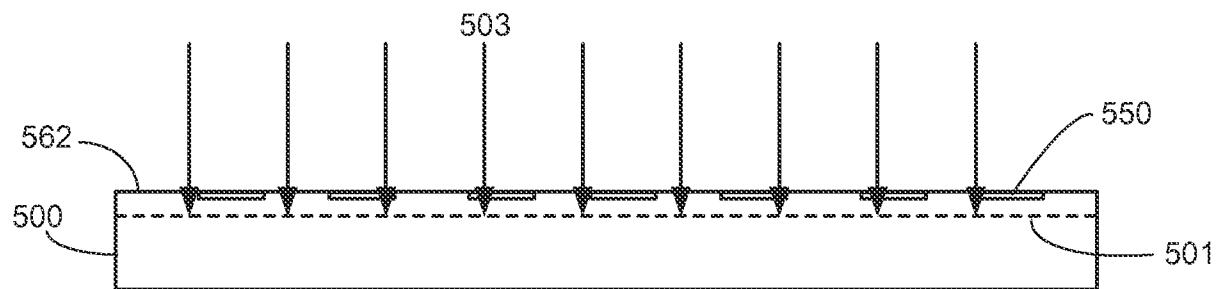

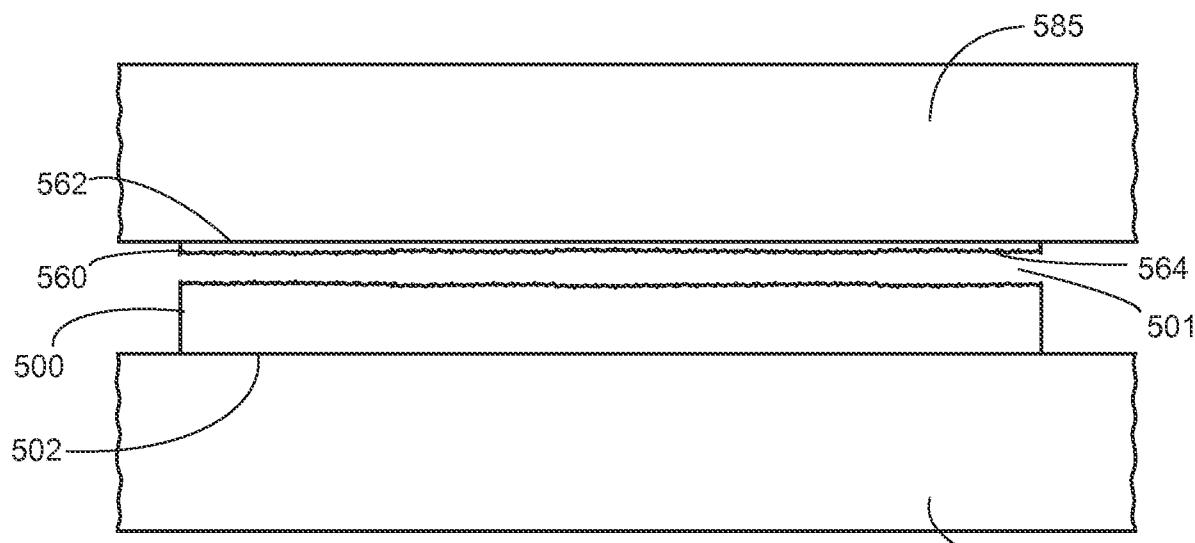

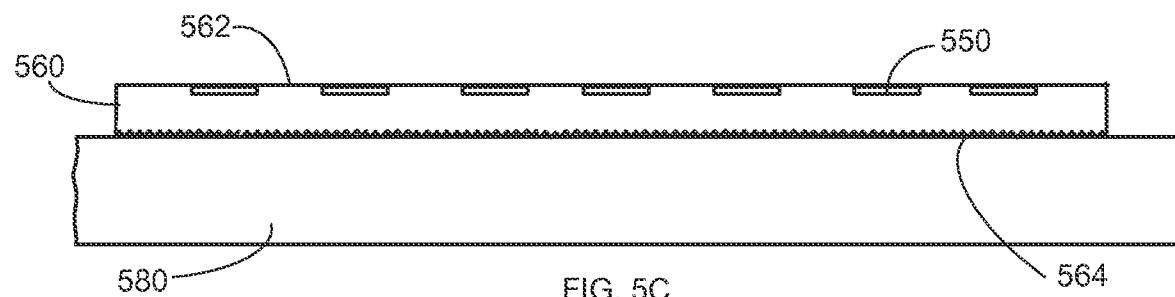

[0012] FIGs. 5A-5C show exemplary cross-sectional views of another embodiment of a backside-illuminated sensor in various stages of manufacturing.

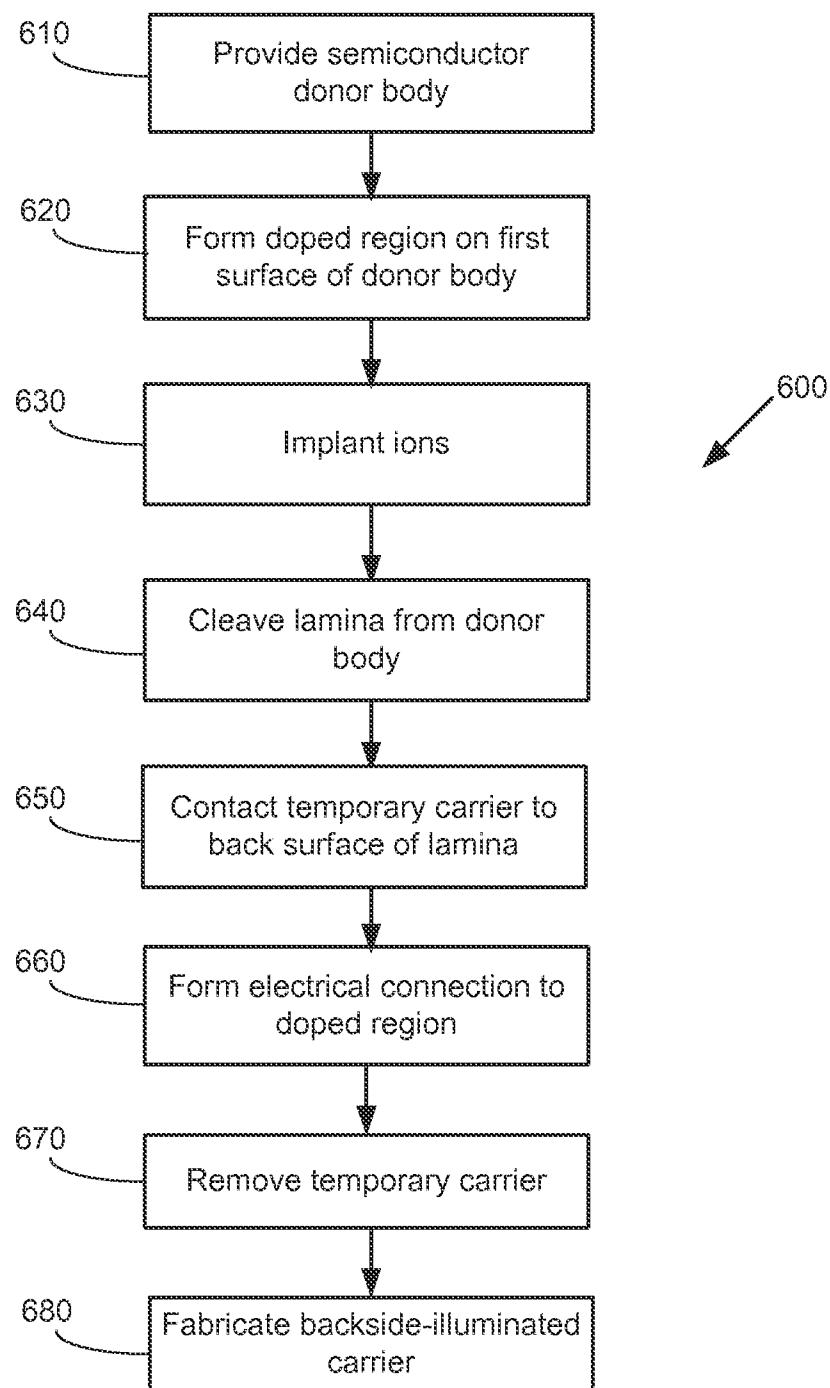

[0013] FIG. 6 is a flowchart of another exemplary method of the present invention.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

[0014] A backside-illuminated sensor is fabricated using a lamina having a thickness substantially equivalent to the desired thickness for the finished sensor device. In some embodiments, the lamina may be provided as a free-standing lamina, in which doped regions are formed within and at a front surface of the lamina. In other embodiments, doped regions are formed in a first surface of a semiconductor donor body and a lamina is cleaved from the donor body, where the doped regions are within and at the front surface of the lamina. The methods disclosed herein enable improving throughput and decreasing manufacturing cost.

[0015] FIG. 1 shows a simplified view of a conventional FSI sensor 100 which includes lenses 110, color filter 120, integrated circuit 130, metal interconnect layer 140, doped regions 150 and semiconductor substrate 160. The semiconductor substrate 160 has a first conductivity and may be, for example, silicon. The doped regions 150 are doped to a different conductivity than the semiconductor substrate 160. For instance, the semiconductor substrate 160 may be a p-type conductor while the doped regions 150 may be n-type. A depletion zone forms at the p-n junction, creating an electric field. The p-n junction between the doped regions 150 and semiconductor substrate 160 forms a photodiode. Incident photons, indicated by arrows 170, will knock electrons from the valence band to the conduction band, creating free electron-hole pairs. Within the electric field at the p-n junction, electrons tend to migrate toward the n region of the diode, while holes migrate toward the p region, resulting in current, called photocurrent. Typically the dopant concentration of one region will be higher than that of the other, so that the junction is either an n-/p+ junction or a p-/n+ junction.

**[0016]** In the FSI sensor 100 of FIG. 1, metal interconnect layer 140 may include wiring or interconnects 142 and dielectric 144. Similarly, integrated circuit 130 also includes wiring 132. Light 170 enters the “front side” of the of the FSI sensor 100, where some light rays are blocked or reflected by wiring 132 and wiring 142. Light energy that reaches the doped regions 150 is then converted to electrical signals that are processed by integrated circuit 130.

**[0017]** FIG. 2 is a simplified diagram of a conventional BSI sensor 200. A BSI sensor is essentially an inverted FSI, so that light enters the back side, through the semiconductor substrate. In FIG. 2, incident light, indicated by arrows 270, enters lens 210 and passes through color filter 220, and then proceeds through semiconductor substrate 260 to diode regions 250, unhindered by wiring in metal interconnect layer 240 and integrated circuit 230. Thus, the efficiency of capturing photons is greatly increased for BSI sensors compared to FSI sensors. However, making the semiconductor substrate 260 thin enough to allow light to reach doped regions 250 can be very difficult, as the substrate 260 also requires high precision uniformity in thickness and avoiding damage to the thin film semiconductor during processing. Grinding is typically used to thin a silicon wafer; however, wafer level grinding commonly results in thickness variation across the wafer. Therefore, additional die level polishing is often performed. The need for multiple material removal steps creates various issues such as lower throughput, higher cost, increased risk of surface contamination, and potential for damage to the semiconductor substrate due to increased handling.

**[0018]** FIGs. 3A-3C depict cross-sectional views of an embodiment of the present disclosure, in which a BSI sensor is fabricated utilizing a thin film semiconductor lamina that already possesses a thickness substantially equivalent to the desired thickness required for the finished sensor assembly. The lamina may be less than 50 microns ( $\mu\text{m}$ ) thick, such as between 1 and 20  $\mu\text{m}$  or between 1 and 10  $\mu\text{m}$  thick. The thickness of the provided lamina remains substantially unchanged, for example within at least 80% of its initially provided thickness, during processing steps for fabrication of the BSI sensor.

**[0019]** In FIG. 3A, a thin film semiconductor lamina 360 is provided, where semiconductor lamina 360 has a front surface 362, a back surface 364, and a first conductivity. The lamina 360 has a thickness measured between the front surface 362 and the back surface 364. Semiconductor lamina 360 may be contacted by a temporary support 380 at back surface 364 to aid in handling the thin film. Temporary support 380 may be contacted to lamina 360 by any type of separable force or adherence such as a

vacuum, electrostatic or chemical force. In some embodiments, semiconductor lamina 360 may be a doped n-type or p-type monocrystalline silicon. The doping concentration may be, for example, between about  $1 \times 10^{15}$  and about  $1 \times 10^{18}$  dopant atoms/cm<sup>3</sup>, or for example, about  $1 \times 10^{17}$  dopant atoms/cm<sup>3</sup>. One or more doped regions 350 are formed within semiconductor lamina 360 at front surface 362, where the doped regions 350 have a different conductivity than that of the semiconductor. One aspect of this invention is that doped regions may be formed on any lamina of any thickness, such as less than 50  $\mu\text{m}$  thick. Another aspect of this invention is that imperfections in the lamina that may have been generated by an exfoliation process may be repaired before the fabrication of doped diode regions.

[0020] The doped regions 350 in FIG. 3A may be formed by methods known in the art, including diffusion doping. For example, as shown in FIG. 3A, a doped glass layer 390 may be formed on the front surface 362 by any method such as atmospheric pressure chemical vapor deposition (PCVD). For a p-type dopant, the doped glass layer 390 may be, for example, borosilicate glass (BSG) doped with boron. The source gas may be any suitable gas that will provide boron, for example, BBr<sub>3</sub>, B<sub>2</sub>H<sub>6</sub>, or BCl<sub>3</sub>. For an n-type dopant, an appropriate gas such as POCl<sub>3</sub> may be flowed at about 880 °C for about 30 minutes on front surface 362, forming phosphosilicate glass (PSG). In other embodiments, a dopant-providing material may be spun onto the front surface 362 and baked. In still other embodiments, the doped glass may be grown thermally, by flowing O<sub>2</sub> over a solid source such as BN. The doped glass layer 390 may have a thickness between, for example, about 500 and about 1500 angstroms, for example, about 1000 angstroms. Next, the doped glass 390 is removed in selected areas, for example by screen printing etchant paste, leaving glass regions 392 (shown as shaded areas) where the doped regions 350 are to be formed. Alternatively, doped regions 350 may be formed on front surface 362 by the deposition of amorphous silicon comprising an n-type dopant. In some embodiments, an intrinsic (undoped) layer of amorphous silicon may be interposed between the doped amorphous silicon layer and front surface 362.

[0021] In an alternative process for forming the doped regions 350, a layer of Si<sub>3</sub>N<sub>4</sub> (not shown) may be deposited on the front surface 362. A screen print etchant paste is applied to etch the Si<sub>3</sub>N<sub>4</sub>, to mask any locations on front surface 362 in which doped regions 350 are not to be formed. Alternatively, conventional photolithographic techniques could be used to define these masked regions. Diffusion doping using a source of phosphorus (e.g., POCl<sub>3</sub>) is performed to form n-type doped regions, or a

boron-containing ambient (e.g.,  $\text{BBr}_3$ ) is used to form p-type regions in the exposed areas. Any remaining  $\text{Si}_3\text{N}_4$  may be etched off at this time using known methods such as hydrofluoric acid (HF). A thin oxide layer may be grown on the wafer.

[0022] An anneal, for example between about 850 and about 1000 °C, is performed in a furnace from between about 30 and about 90 minutes, and diffuses dopants from glass regions 392 into semiconductor lamina 360 at front surface 362. This diffusion forms either doped p-type (from, e.g., BSG) or n-type (from, e.g., PSG) regions 350. Next a conventional wet etch, for example an HF dip, removes the BSG or PSG, leaving doped regions 350 exposed at front surface 362. Boron and phosphorus are the most commonly used p-type and n-type dopants, respectively, but other dopants may be used.

[0023] After doped regions 350 have been formed in thin film semiconductor lamina 360, electrical connections may be formed as shown in FIG. 3B. In some embodiments, the electrical connection may include one or more sub-layers in metallization layer 340. The metallization layer 340 may be formed by, for example, sputter deposition using physical vapor deposition. The metallization layers 340 may comprise, for example, titanium, titanium-tungsten, or copper. Photolithography methods known in the art may be used to mask and etch the desired wiring patterns in metallization layers 340, to form electrical connections 342 to the doped regions 350, as depicted in FIG. 3C. Subsequent manufacturing steps may then be executed to fabricate a backside-illuminated sensor from the thin film semiconductor lamina 360. For instance, copper-tin, copper-indium or indium-tin bumps 344 may be electroplated onto the metallization layers 340 to facilitate bonding of integrated circuit 330. This bonding can be accomplished using any known method that will result in electrical connections between the integrated circuit and the lamina; for example, copper-copper thermo-compression bonding, or solid-liquid inter-diffusion bonding, using copper and tin or indium and indium or indium and tin. In some embodiments, integrated circuit 330 may be a complementary metal-oxide semiconductor (CMOS).

[0024] After the desired components have been constructed on the front surface 362 of thin film semiconductor 360, temporary support 380 is removed from back surface 364 of the lamina 360. A completed BSI sensor may be fabricated by adding, for example, coatings, color filters, and micro-lenses to back surface 364 (e.g., FIG. 2). As seen in the embodiments of FIGs. 3A-3C, the thickness of initially provided thin film

semiconductor lamin 360 remains substantially unchanged during fabrication of the backside illuminated sensor, thus reducing issues created by grinding.

[0025] Flowchart 400 of FIG. 4 illustrates the embodiments FIGs. 3A-3C. The exemplary method of flowchart 400 begins with providing a thin film semiconductor lamina in step 410. In step 420 a temporary carrier or support may be contacted to the back surface of the lamina, to support handling of the fragile lamina during processing. One or more doped regions are formed at the front surface of the lamina in step 430, where the doped regions have a conductivity opposite of the conductivity of the thin film semiconductor. In step 440, one or more electrical connections are formed to the doped region. The electrical connections may include, for example, metallization layers, solder bumps and thermo-compression interfaces. The temporary carrier is removed in step 450, after which a finished backside-illuminated sensor may be fabricated in step 460 by performing any additional manufacturing steps as desired on the back surface of the lamina. These finishing steps may include, for example, adding coatings, color filters and micro-lenses. The coatings may include layers that passivate the back surface of the lamina. These passivation layers may include a 10 Å – 300 Å layer of hydrogenated amorphous silicon, deposited by plasma-enhanced chemical vapor deposition at a temperature of < 450 C. The finishing steps may also include etching some material from the back surface of the lamina, to remove damage incurred during the cleaving implant process.

[0026] Another embodiment of the present disclosure is shown in FIGs. 5A-5C. In this embodiment, doped regions 550 of FIG. 5A are formed in a semiconductor donor body 500, and then a lamina is cleaved from the semiconductor donor body 500, where the lamina includes the doped regions 550. The donor body 500 is an appropriate semiconductor material such as a monocrystalline silicon wafer of any practical thickness, for example from about 200 to about 1000 microns thick. In alternative embodiments, the donor wafer may be thicker; maximum thickness is limited only by practicalities of wafer handling. Alternatively, wafers or ingots of other semiconductors materials, including germanium, silicon germanium, or III-V or II-VI semiconductor compounds such as GaAs, InP, etc may be used.

[0027] The process of forming monocrystalline silicon generally results in circular wafers, but the donor body can have other shapes as well. Cylindrical monocrystalline ingots are often machined to an octagonal cross section prior to cutting wafers. Multicrystalline wafers are often square. Square wafers have the advantage that,

unlike circular or hexagonal wafers, they can be aligned edge-to-edge with minimal unused gaps between them. The diameter or width of the wafer may be any standard or custom size. For simplicity this disclosure will describe the use of a monocrystalline silicon wafer as the semiconductor donor body, but it will be understood that donor bodies of other types and materials can be used.

[0028] Exfoliation of a lamina comprising the doped regions 550 may occur by any means, including an ion induced cleavage reaction. Sivaram et al., U.S. Patent Application No. 12/026530, "Method to Form a Photovoltaic Cell Comprising a Thin Lamina," filed Feb. 5, 2008, owned by the assignee of the present invention and hereby incorporated by reference, describes a semiconductor donor wafer (without doped regions 550) implanted with one or more species of gas ions, for example hydrogen and/or helium ions. The implanted ions define a cleave plane, such as cleave plane 501 of FIG. 5A, within the semiconductor donor wafer 500. Semiconductor donor wafer 500, also referred to as a donor body in this disclosure, has a first surface 562, which will become the front surface 562 of the later-exfoliated lamina. The gas ions are implanted (indicated by arrows 503) through first surface 562, to create cleave plane 501. The cost of this hydrogen or helium implant may be reduced by methods described in Parrill et al., U.S. Patent Application No. 12/122108, "Ion Implanter for Photovoltaic Cell Fabrication," filed May 16, 2008, owned by the assignee of the present invention and hereby incorporated by reference. The overall depth of cleave plane 501, as measured from first surface 562, is determined by several factors including implant energy. The depth of cleave plane 501 can be between about 0.2 and about 100  $\mu\text{m}$  from first surface 562, for example between about 0.5 and about 20  $\mu\text{m}$ ; or between about 0.5 and about 50  $\mu\text{m}$ , for example between about 1 and about 25  $\mu\text{m}$  or between about 8 microns and about 20  $\mu\text{m}$ . The depth of the cleave plane 501 will determine the thickness of cleaved lamina. Desirably, the thickness of cleaved lamina is chosen to be substantially equivalent to the desired thickness of a semiconductor substrate in the completed BSI sensor. Thus, a semiconductor substrate for a BSI according to embodiments of this invention may advantageously be produced with a specifically desired thickness and with a highly precise uniformity in thickness.

[0029] As shown in FIG. 5B, an anneal reaction causes lamina 560 to cleave from donor wafer 500 at cleave plane 501, where the cleave plane 501 creates back surface 564 of lamina 560. The first surface 562 of the semiconductor donor body 500 becomes front surface 562 of the lamina 560. Donor wafer 500 is affixed at first surface

562 to a temporary support element 585, which may be used to lift the lamina 560 from the semiconductor donor body 500.

[0030] According to embodiments of Sivaram et al., semiconductor lamina 560 may be between about 0.2 and about 100  $\mu\text{m}$  thick, for example between about 0.2 and about 50  $\mu\text{m}$ , for example between about 1 and about 25  $\mu\text{m}$  thick, in some embodiments between about 5 and about 20  $\mu\text{m}$  thick, though any thickness within the named range is possible. Using the methods of Sivaram et al., photovoltaic cells are formed of thin semiconductor laminae rather than being formed from sliced wafers, without wasting silicon through excessive kerf loss or by fabrication of an unnecessarily thick cell, thus reducing cost. The same donor wafer can be reused to form multiple laminae, further reducing cost, and may be resold after exfoliation of multiple laminae for some other use.

[0031] In the methods of Sivaram et al., though, the wafer must be contacted to a temporary or permanent support element early in the process in order to provide mechanical support to the thin lamina. Typically, lamina formed in this manner must either incorporate the support element into any resultant device or engage in a debonding step to remove the support element. In some embodiments of the present disclosure, a thin, free standing lamina may be formed and separated from a donor body without adhesive or permanent bonding to a support element and without requiring debonding or cleaning steps prior to fabricating a device from the lamina, beneficially providing for any number of processing steps to the front or back surface of the lamina. The first surface of the donor body 500 -- which will be the front surface of an exfoliated lamina -- may be placed adjacent to support element 585 and an anneal step may be performed that exfoliates a lamina from the first surface of the donor body before or after the surface is treated with a processing step. The cleaved plane creates the back surface of the lamina, and once again, any number of processing steps may then occur on either side of the exfoliated lamina. These processes may occur in the absence of a bonded support element on the lamina as described in Kell et al., "A Method and Apparatus for Forming a Thin Lamina," U.S. Patent Application No. 13/331,909 filed December 20, 2011 and hereby incorporated by reference.

[0032] Turning to FIG. 5C, prior to exfoliation, a second surface 502 of semiconductor donor body 500 of the present invention may be separably contacted to a temporary support element 586, such as a susceptor assembly. The contact between the donor body 500 and the support element 586 may comprise any type of separable force or

adherence such as a vacuum, electrostatic or chemical force. In some embodiments the interacting force between the donor body 500 and the susceptor 586 during exfoliation of a lamina is solely the weight of the donor body 500 on the susceptor 586. In other embodiments where the exfoliation equipment has a configuration which is inverted vertically from that shown in FIG. 5B, the interacting force is solely the weight of the susceptor assembly 586 on the donor body. Following the contacting of the donor body 500 to the susceptor assembly 586, heat or other force may be applied to the donor body 500 to cleave lamina 560 from the donor body 500 at the cleave plane 501. Exfoliation conditions may be optimized to cleave the lamina from the donor body in order to minimize physical defects in a lamina exfoliated in the absence of a permanently adhered support element. Exfoliation may be performed at temperatures between, for example, about 350 and about 650 degrees C. In general, exfoliation proceeds more rapidly at higher temperature.

[0033] In cleaving lamina 560 from donor wafer 500 at cleave plane 501, a back surface 564 which is opposite of the front surface 562 on lamina 560 is created, as shown in FIG. 5C. Doped regions 550 are located at front surface 562 and within lamina 560. The lamina 560 may be annealed to remove any damage caused by the ion implantation. The free-standing lamina 560 may be temporarily contacted at either the front surface 562 or back surface 564 with a temporary support element. For example, support element 580 in FIG. 5C may contact back surface 564 during further manufacturing steps, and later removed, for fabricating the lamina 560 into a backside-illuminated sensor as described in relation to FIGs. 3B-3C above.

[0034] Note that the steps of implanting ions, cleaving the semiconductor donor body, and forming doped regions occur at high temperatures, such as above 450 degrees Celsius. Performing these high temperature steps in the early stages of fabricating a BSI sensor advantageously allows for the more thermally fragile materials to be used in later steps of fabricating the backside-illuminated sensor. In some embodiments of the present invention, during manufacture of a completed BSI sensor, only the steps of implanting ions, cleaving the semiconductor donor body, and forming the doped region have processing temperatures above about 450 degrees Celsius. In other embodiments, forming a doped region occurs prior to the step of implanting ions.

[0035] Flowchart 600 of FIG. 6 illustrates an exemplary embodiment of the methods of FIGs. 5A-5C. In step 610, a semiconductor donor body is provided. One or more doped regions, which will serve as photodiodes of a finished BSI sensor assembly,

are formed in the donor body in step 620. The doped regions are formed at a first surface of the donor body and have a conductivity that is different from the conductivity of the donor body. Ions are implanted into the semiconductor donor body to form a cleave plane in step 630, and then a semiconductor lamina is cleaved from the donor body in step 640. The first surface of the semiconductor body serves as the front surface of the lamina, and the cleave plane creates the back surface of the lamina. Furthermore, the doped regions are included at a front surface of the exfoliated lamina. In step 650 a temporary carrier or support is contacted to the back surface of the semiconductor lamina. Electrical connections, such as the metallization layers described above, are coupled to the doped regions on the front side of the lamina in step 660. The temporary carrier is removed in step 670. A finished backside-illuminated sensor may be fabricated in step 680 by performing any additional manufacturing steps desired on back surface of the lamina, such as those described in relation to step 460 of FIG. 4.

[0036] As discussed above, the embodiments of the present invention provide method of providing a lamina that does not require further thinning to achieve the desired thickness for a BSI sensor, thus reducing cost and improving and manufacturability. The thickness of the provided lamina remains substantially unchanged – such as being modified by not more than 20% of its initial thickness as a result of, for example, etching – during processing of the lamina and fabrication of the backside-illuminated sensor. Embodiments of the methods also involve doping the diode regions – processes which typically require high temperatures – early in the manufacturing process, consequently allowing for use of lower temperature materials and processes in subsequent fabrication steps.

[0037] Note that additional steps may be incorporated into the flowcharts described in this disclosure, without departing from the scope of the invention. For instance, in some embodiments a temporary support may also be contacted to the front surface. Similarly, temporary supports contacting either or both of the front and back surfaces may be used to transfer the lamina through the various steps involved with fabricating a finished BSI sensor assembly. In other embodiments, etching or other surface preparation processes may be performed. An etch step may serve to remove damage at the back surface of the lamina. This etch step may be performed, for example, by a wet or plasma treatment. The plasma treatment may occur, for example, in an SF<sub>6</sub> ambient. The amount etched may be < 20% of the total lamina thickness.

[0038] While the specification has been described in detail with respect to specific embodiments of the invention, it will be appreciated that those skilled in the art, upon attaining an understanding of the foregoing, may readily conceive of alterations to, variations of, and equivalents to these embodiments. These and other modifications and variations to the present invention may be practiced by those of ordinary skill in the art, without departing from the spirit and scope of the present invention, which is more particularly set forth in the appended claims. Furthermore, those of ordinary skill in the art will appreciate that the foregoing description is by way of example only, and is not intended to limit the invention.

What is claimed is:

1. A method of fabricating a backside-illuminated sensor, the method comprising the steps of:

providing a thin film semiconductor lamina having a front surface, a back surface and a thickness between the front surface and the back surface, wherein the semiconductor lamina has a first conductivity;

forming a doped region within the semiconductor lamina at the front surface of the lamina, wherein the doped region has a second conductivity;

contacting a temporary carrier to the back surface of the semiconductor lamina;

forming an electrical connection to the doped region at the front side of the semiconductor lamina;

removing the temporary carrier from the back surface; and

fabricating a backside-illuminated sensor from the semiconductor lamina, wherein the thickness of the semiconductor lamina remains substantially unchanged during fabrication of the backside illuminated sensor.

2. The method of claim 1 further comprising the steps of:

providing a semiconductor donor body having a first surface, wherein the semiconductor donor body has the first conductivity;

implanting ions into the first surface of the semiconductor donor body to define a cleave plane; and

cleaving the semiconductor donor body at the cleave plane, wherein the cleave plane forms the back surface of the semiconductor lamina and wherein the first surface of the semiconductor donor body forms the front surface of the semiconductor lamina.

3. The method of claim 2 wherein only the steps of implanting ions, cleaving the semiconductor donor body, and forming the doped region have processing temperatures above about 450 degrees Celsius.

4. The method of claim 2 wherein the step of forming the doped region occurs prior to the step of implanting ions.

5. The method of claim 2 wherein the step of implanting ions comprises an implant energy;

- wherein the implant energy determines a depth of the cleave plane, the depth being measured from the first surface of the semiconductor donor body; and

- wherein the depth is chosen to be substantially equivalent to the thickness of the semiconductor lamina.

6. The method of claim 1 wherein the step of forming the electrical connection comprises the steps of:

- applying a metallization layer to the front side of the semiconductor lamina; and

- coupling an integrated circuit to the metallization layer.

7. The method of claim 6 wherein the integrated circuit is a complementary metal-oxide semiconductor (CMOS).

8. The method of claim 1 further comprising the step of coupling a color filter to the back surface of the semiconductor lamina.

9. The method of claim 1 wherein the thickness of the thin film semiconductor lamina is less than about 25 microns.

10. The method of claim 1 wherein the thickness of the thin film semiconductor lamina is between about 1 micron to about 50 microns.

11. The method of claim 1 wherein the thickness of the semiconductor lamina remains within a 20% deviation of its initially provided thickness during fabrication of the backside illuminated sensor.

12. A method of fabricating a backside-illuminated sensor, the method comprising the steps of:

- providing a semiconductor donor body having a first surface and a first conductivity;

- forming a doped region within the semiconductor donor body at the first surface, wherein the doped region has a second conductivity;

implanting ions into the first surface of the semiconductor donor body to define a cleave plane;

cleaving a semiconductor lamina from the semiconductor donor body at the cleave plane, wherein the cleave plane forms a back surface of the semiconductor lamina, wherein the first surface of the semiconductor donor body is a front surface of the semiconductor lamina, and wherein the front surface includes the doped region;

contacting a temporary carrier to the back surface of the semiconductor lamina;

forming an electrical connection to the doped region on the front side of the semiconductor lamina;

removing the temporary carrier from the back surface; and

fabricating a backside-illuminated sensor from the semiconductor lamina, wherein a thickness between the front side and the back surface of the semiconductor lamina remains substantially unchanged during fabrication of the backside-illuminated sensor.

13. The method of claim 12 wherein the step of forming the electrical connection comprises the steps of:

applying a metallization layer to the front side of the semiconductor lamina; and

coupling an integrated circuit to the metallization layer.

14. The method of claim 12 further comprising the step of coupling a color filter to the back surface of the semiconductor lamina.

15. The method of claim 12 wherein the step of forming the doped region occurs prior to the step of implanting ions.

16. The method of claim 12 wherein the thickness of the thin film semiconductor lamina is between about 1 micron to about 50 microns.

17. The method of claim 12 wherein the thickness of the semiconductor lamina remains within a 20% deviation of its initially provided thickness during fabrication of the backside illuminated sensor.

18. The method of claim 12 wherein the step of implanting ions comprises an implant energy, and wherein the implant energy determines a depth of the cleave plane, the depth being measured from the first surface of the semiconductor donor body.

19. The method of claim 12 wherein the thickness of the cleaved semiconductor lamina is substantially equivalent to a desired final thickness of a semiconductor substrate in the fabricated backside-illuminated sensor.

20. The method of claim 12 wherein only the steps of forming the doped region, implanting ions, and cleaving the semiconductor donor body have processing temperatures above about 450 degrees Celsius.

21. The method of claim 12 wherein the step of fabricating a backside-illuminated sensor from the lamina includes depositing a layer to passivate the back surface of the lamina.

22. The method of claim 21 wherein the passivating layer comprises hydrogenated amorphous silicon.

FIG. 1

(prior art)

FIG. 2

(prior art)

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6

**A. CLASSIFICATION OF SUBJECT MATTER****H01L 27/146(2006.01)i, H01L 27/14(2006.01)i**

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H01L 27/146; H01L 21/762; H01L 21/78; H01L 31/00; H01L 31/062

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Korean utility models and applications for utility models

Japanese utility models and applications for utility modelsElectronic data base consulted during the international search (name of data base and, where practicable, search terms used)

eKOMPASS(KIPO internal) & keywords: thin, film, lamina, backside-illuminated sensor, BSI**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                              | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | US 2010-0032007 A1 (MOHAMED M. HILALI et al.) 11 February 2010<br>See paragraphs [0019]-[0055], claims 2-17 and figures 2a-3e.  | 12-18,21-22           |

| A         |                                                                                                                                 | 1-11,19-20            |

| Y         | KR 10-2009-0057435 A (CORNING INCORPORATED) 05 June 2009<br>See abstract, paragraphs [0017], [0092]-[0103] and claim 1.         | 12-18,21-22           |

| A         |                                                                                                                                 | 1-11,19-20            |

| Y         | US 2006-0076590 A1 (BEDABRATA PAIN et al.) 13 April 2006<br>See abstract, paragraphs [0033]-[0037], claims 1-5 and figure 2.    | 21-22                 |

| A         | US 2009-0298260 A1 (RUI ZHU et al.) 03 December 2009<br>See abstract, paragraphs [0046]-[0049] and figure 7.                    | 1-22                  |

| A         | US 2010-0240169 A1 (CHRISTOPHER J. PETTI et al.) 23 September 2010<br>See paragraphs [0020]-[0047], claims 1-5 and figures 1-6. | 1-22                  |

Further documents are listed in the continuation of Box C. See patent family annex.

|                                                                                                                                                                 |                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:                                                                                                                        | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                        | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "E" earlier application or patent but published on or after the international filing date                                                                       | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of citation or other special reason (as specified) | "&" document member of the same patent family                                                                                                                                                                                                    |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                    |                                                                                                                                                                                                                                                  |

| "P" document published prior to the international filing date but later than the priority date claimed                                                          |                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                            |                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Date of the actual completion of the international search<br><br>24 May 2013 (24.05.2013)                                                                                                                  | Date of mailing of the international search report<br><br><b>27 May 2013 (27.05.2013)</b> |

| Name and mailing address of the ISA/KR<br><br>Korean Intellectual Property Office<br>189 Cheongsa-ro, Seo-gu, Daejeon Metropolitan City,<br>302-701, Republic of Korea<br><br>Facsimile No. 82-42-472-7140 | Authorized officer<br><br>CHOI, Sang Won<br><br>Telephone No. 82-42-481-8291              |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

**PCT/US2013/024684**

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                             | Publication date                                                                 |

|----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| US 2010-0032007 A1                     | 11.02.2010       | TW 201007958 A<br>US 8338209 B2<br>WO 2010-019379 A1                                                                | 16.02.2010<br>25.12.2012<br>18.02.2010                                           |

| KR 10-2009-0057435 A                   | 05.06.2009       | CN 101584046 A<br>EP 2057685 A2<br>JP 2010-503991 A<br>US 2008-0070340 A1<br>WO 2008-033508 A2<br>WO 2008-033508 A3 | 18.11.2009<br>13.05.2009<br>04.02.2010<br>20.03.2008<br>20.03.2008<br>19.06.2008 |

| US 2006-0076590 A1                     | 13.04.2006       | JP 2008-514011 A<br>US 7615808 B2<br>WO 2006-137866 A2<br>WO 2006-137866 A3<br>WO 2006-137867 A1                    | 01.05.2008<br>10.11.2009<br>28.12.2006<br>08.02.2007<br>28.12.2006               |

| US 2009-0298260 A1                     | 03.12.2009       | EP 2281307 A1<br>EP 2281307 A4<br>JP 2011-522421 A<br>US 7855128 B2<br>WO 2009-154982 A1                            | 09.02.2011<br>29.06.2011<br>28.07.2011<br>21.12.2010<br>23.12.2009               |

| US 2010-0240169 A1                     | 23.09.2010       | US 7964431 B2                                                                                                       | 21.06.2011                                                                       |