(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6036765号

(P6036765)

(45) 発行日 平成28年11月30日(2016.11.30)

(24) 登録日 平成28年11月11日(2016.11.11)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 27/04   | (2006.01) | HO1L 29/78 | 657D |

| HO1L 29/78   | (2006.01) | HO1L 29/78 | 653A |

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 652M |

| HO1L 21/8234 | (2006.01) | HO1L 29/78 | 658F |

| HO1L 27/06   | (2006.01) | HO1L 29/78 | 652J |

請求項の数 6 (全 16 頁) 最終頁に続く

(21) 出願番号

特願2014-169454 (P2014-169454)

(22) 出願日

平成26年8月22日(2014.8.22)

(65) 公開番号

特開2016-46377 (P2016-46377A)

(43) 公開日

平成28年4月4日(2016.4.4)

審査請求日

平成28年4月4日(2016.4.4)

(73) 特許権者 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

(74) 代理人 110000110

特許業務法人快友国際特許事務所

(72) 発明者 添野 明高

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

審査官 恩田 和彦

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置であって、

表面にトレンチが形成されている半導体基板と、

前記トレンチ内に配置されているトレンチ電極と、

前記トレンチ電極の表面を覆っており、前記半導体基板の前記表面から突出している層間絶縁膜と、

前記半導体基板の前記表面上に配置されており、前記層間絶縁膜から離間した位置に配置されており、前記半導体基板に対してショットキー接觸しているショットキー電極と、

前記層間絶縁膜と前記ショットキー電極の間の凹部内に配置されており、前記ショットキー電極とは異なる金属により構成されている埋め込み電極と、

前記層間絶縁膜、前記埋め込み電極及び前記ショットキー電極を覆う表面電極、

を有し、

前記埋め込み電極に覆われている範囲において、前記半導体基板の前記表面と前記ショットキー電極の側面の間の角度が90度より大きい半導体装置。

## 【請求項 2】

前記埋め込み電極に覆われている範囲において、前記半導体基板の前記表面と前記層間絶縁膜の側面の間の角度が90度より大きい請求項1の半導体装置。

## 【請求項 3】

前記ショットキー電極と前記表面電極の間、及び、前記層間絶縁膜と前記表面電極の間

10

20

に、前記埋め込み電極に対してエッチング選択性を有するバリアメタル層が配置されている請求項1または2の半導体装置。

【請求項4】

前記埋め込み電極が、前記半導体基板に対してオーム接觸している請求項1～3のいずれか一項の半導体装置。

【請求項5】

半導体装置を製造する方法であって、

半導体基板の表面にトレンチを形成する工程と、

前記トレンチ内にトレンチ電極を形成する工程と、

前記トレンチ電極の表面上に、前記トレンチ電極の表面を覆う層間絶縁膜を含み、前記半導体基板の前記表面から突出する第1凸部を形成する工程と、10

前記半導体基板の前記表面上であって前記第1凸部から離間した位置に、前記半導体基板に対してショットキー接觸しているショットキー電極を含み、前記半導体基板の前記表面から突出する第2凸部を形成する工程と、

前記第1凸部と、前記第2凸部と、前記第1凸部と前記第2凸部の間の前記半導体基板の前記表面を覆うように、埋め込み電極を成長させる工程と、

前記第1凸部と前記第2凸部の表面が露出し、前記第1凸部と前記第2凸部の間の凹部内に前記埋め込み電極が残存するように、前記埋め込み電極をエッチングする工程と、

前記エッチングの後に、前記第1凸部、前記埋め込み電極及び前記第2凸部を覆う表面電極を成長させる工程、20

を有する方法。

【請求項6】

前記埋め込み電極が、前記ショットキー電極とは異なる金属により構成されている請求項5の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書に開示の技術は、半導体装置及び半導体装置の製造方法に関する。

【背景技術】

【0002】

特許文献1に開示の半導体装置は、IGBTとショットキーダイオードを有する。このIGBTは、トレンチ型のゲート電極を有する。また、ショットキーダイオードは、半導体基板の表面の一部に対してショットキー接觸している電極を有している。30

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2013-048230号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トレンチ型のゲート電極を有する素子には、IGBTの他に、MOSFET等がある。また、ゲート電極ではない電極が、トレンチ内に配置される場合もある。このように、トレンチ内に配置された電極（以下、トレンチ電極という）は、多くの場合、その上面が層間絶縁膜により覆われる。層間絶縁膜は、半導体基板の表面から突出するよう形成される。また、この種の半導体装置では、半導体基板の表面が、表面電極により覆われる。表面電極は、層間絶縁膜を覆うように形成される。層間絶縁膜が半導体基板の表面から突出しているので、表面電極は、層間絶縁膜の上部において凸状に盛り上がった形状となる。このため、表面電極の表面に段差が形成される。40

【0005】

表面電極に対して繰り返し温度変化を加えると、表面電極にクラックが生じる。表面電50

極の平坦な箇所で発生したクラックは、表面電極の表面に沿って進行する傾向が強い。これに対し、表面電極の段差の近傍で発生したクラックは、表面電極の厚み方向に向かって進行し易い。クラックが半導体基板まで達すると、半導体装置の特性が劣化するため、問題となる。したがって、本明細書では、層間絶縁膜を覆う表面電極を容易に平坦化することが可能な技術を提供する。

【課題を解決するための手段】

【0006】

本明細書が開示する半導体装置は、半導体基板と、トレンチ電極と、層間絶縁膜と、ショットキー電極と、埋め込み電極と、表面電極を有する。半導体基板の表面上にトレンチが形成されている。トレンチ電極は、前記トレンチ内に配置されている。層間絶縁膜は、前記トレンチ電極の表面を覆っており、前記半導体基板の前記表面から突出している。ショットキー電極は、前記半導体基板の前記表面上に配置されており、前記層間絶縁膜から離間した位置に配置されており、前記半導体基板に対してショットキー接觸している。埋め込み電極は、前記層間絶縁膜と前記ショットキー電極の間の凹部内に配置されており、前記ショットキー電極とは異なる金属により構成されている。表面電極は、前記層間絶縁膜、前記埋め込み電極及び前記ショットキー電極を覆っている。

10

【0007】

なお、層間絶縁膜、埋め込み電極及びショットキー電極と、これらを覆う表面電極の間に、他の層が介在していてもよい。また、これらが表面電極と接觸していてもよい。

20

【0008】

この半導体装置は、半導体基板の表面から突出する層間絶縁膜と、半導体基板の表面上であって層間絶縁膜から離間した位置に配置されているショットキー電極を有している。したがって、層間絶縁膜とショットキー電極とに挟まれた位置が、凹部となっている。凹部内には、埋め込み電極が形成されている。製造工程において、層間絶縁膜とショットキー電極と凹部を覆うように埋め込み電極を成長させ、その後、埋め込み電極をエッティングすることで、凹部内に埋め込み電極を残存させることができる。埋め込み電極をエッティングする際に、埋め込み電極を残存させる範囲が広いと、その範囲の中央部が凹状に窪み、埋め込み電極の表面を平坦に形成することが難しい。しかしながら、狭い凹部内に埋め込み電極を残存させるのであれば、埋め込み電極の表面を比較的平坦に形成することが可能である。この半導体装置では、凹部内に埋め込み電極が残存するので、埋め込み電極の表面を平坦にことができる。その後、層間絶縁膜、埋め込み電極及びショットキー電極を覆うように表面電極を成長させることで、上記の半導体装置が完成する。層間絶縁膜とショットキー電極の間の凹部に埋め込み電極が配置されており、かつ、埋め込み電極の表面が平坦であるので、表面電極を平坦に形成することができる。

30

【0009】

本明細書が開示する半導体装置の製造方法は、半導体基板の表面上にトレンチを形成する工程と、前記トレンチ内にトレンチ電極を形成する工程と、第1凸部を形成する工程と、第2凸部を形成する工程と、埋め込み電極を成長させる工程と、埋め込み電極をエッティングする工程と、表面電極を成長させる工程を有する。第1凸部を形成する工程では、前記トレンチ電極の表面上に、前記トレンチ電極の表面を覆う層間絶縁膜を含み、前記半導体基板の前記表面から突出する第1凸部を形成する。第2凸部を形成する工程では、前記半導体基板の前記表面上であって前記第1凸部から離間した位置に、前記半導体基板に対してショットキー接觸しているショットキー電極を含み、前記半導体基板の前記表面から突出する第2凸部を形成する。埋め込み電極を成長させる工程では、前記第1凸部と、前記第2凸部と、前記第1凸部と前記第2凸部の間の前記半導体基板の前記表面を覆うように、埋め込み電極を成長させる。埋め込み電極をエッティングする工程では、前記第1凸部と前記第2凸部の表面が露出し、前記第1凸部と前記第2凸部の間の凹部内に前記埋め込み電極が残存するように、前記埋め込み電極をエッティングする。表面電極を成長させる工程では、前記エッティングの後に、前記第1凸部、前記埋め込み電極及び前記第2凸部を覆う表面電極を成長させる。

40

50

## 【0010】

なお、第2凸部は、第1凸部より先に形成してもよいし、第1凸部より後に形成してもよい。

## 【0011】

この方法によれば、平坦な表面電極を有する半導体装置を製造することができる。

## 【図面の簡単な説明】

## 【0012】

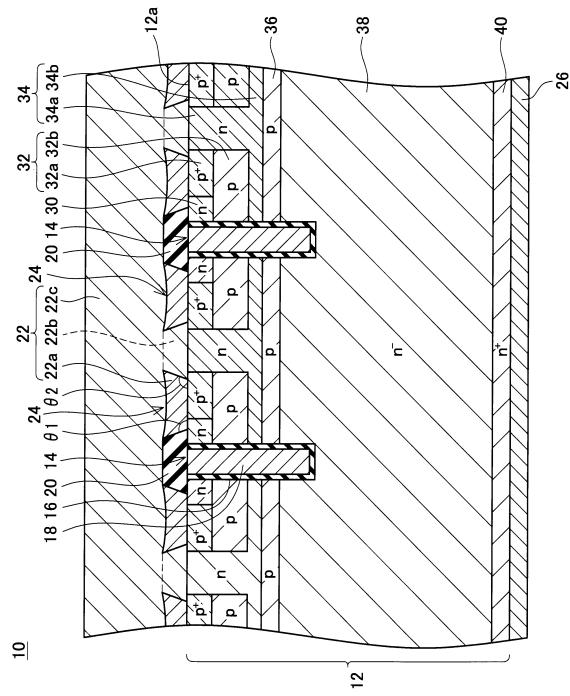

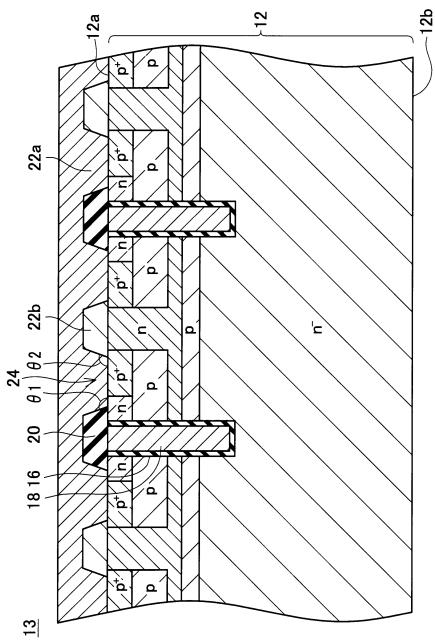

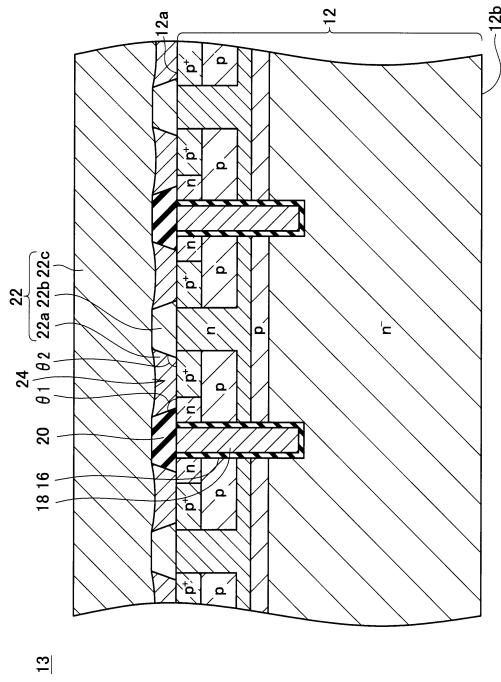

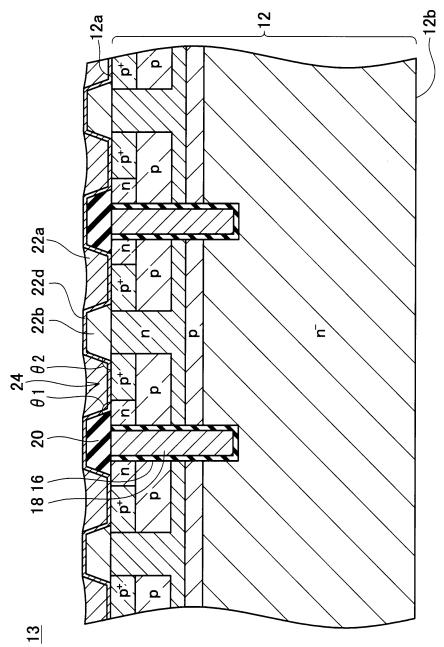

【図1】実施例1の半導体装置10の縦断面図。

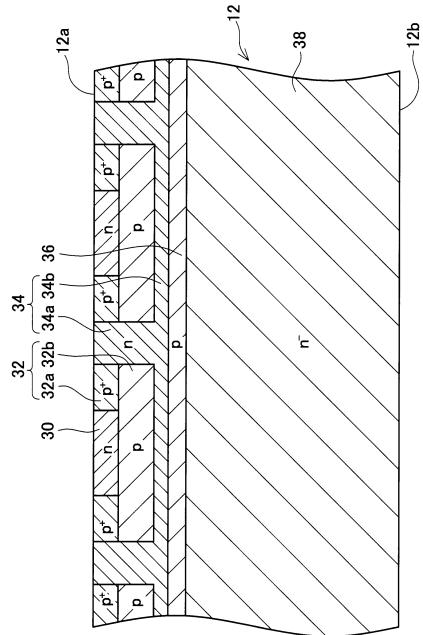

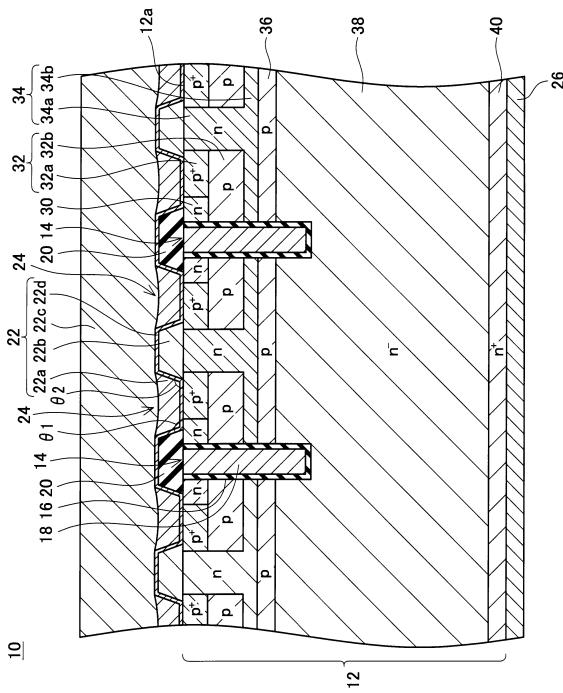

【図2】実施例1の半導体装置10の製造工程の説明図。

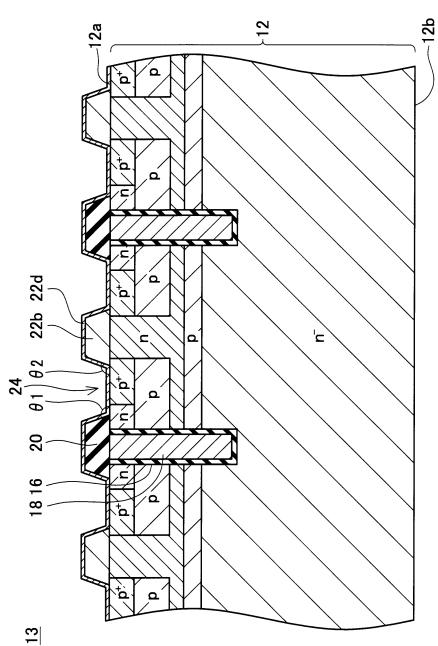

【図3】実施例1の半導体装置10の製造工程の説明図。

10

【図4】実施例1の半導体装置10の製造工程の説明図。

【図5】実施例1の半導体装置10の製造工程の説明図。

【図6】実施例1の半導体装置10の製造工程の説明図。

【図7】実施例1の半導体装置10の製造工程の説明図。

【図8】実施例1の半導体装置10の製造工程の説明図。

【図9】実施例1の半導体装置10の製造工程の説明図。

【図10】実施例1の半導体装置10の製造工程の説明図。

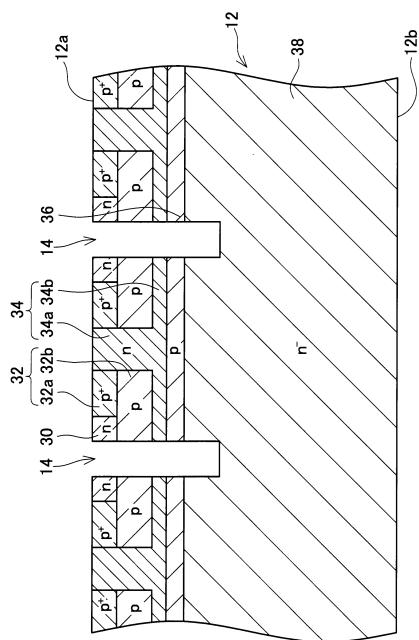

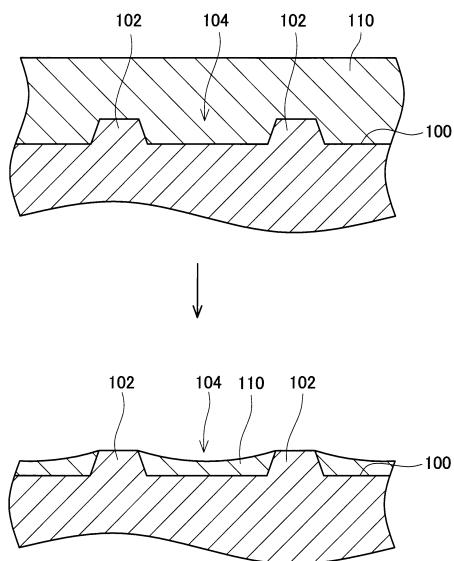

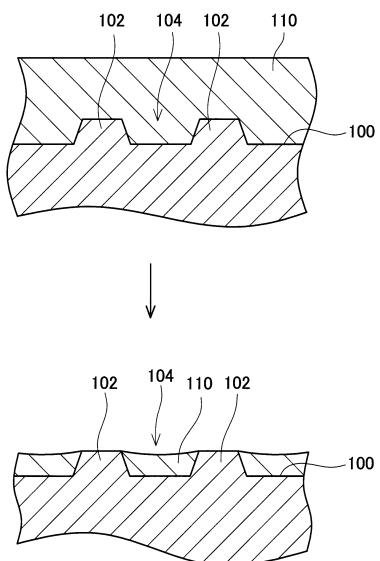

【図11】金属をエッティングする工程の説明図。

【図12】金属をエッティングする工程の説明図。

【図13】実施例1の半導体装置10の製造工程の説明図。

20

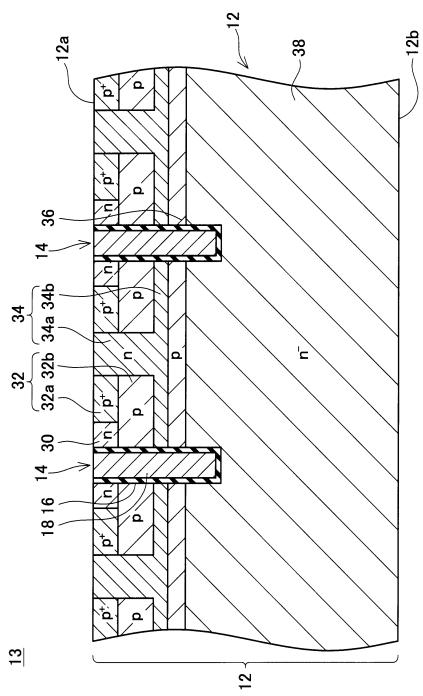

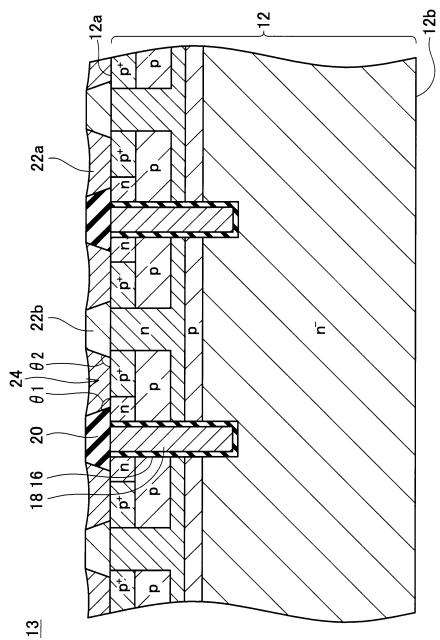

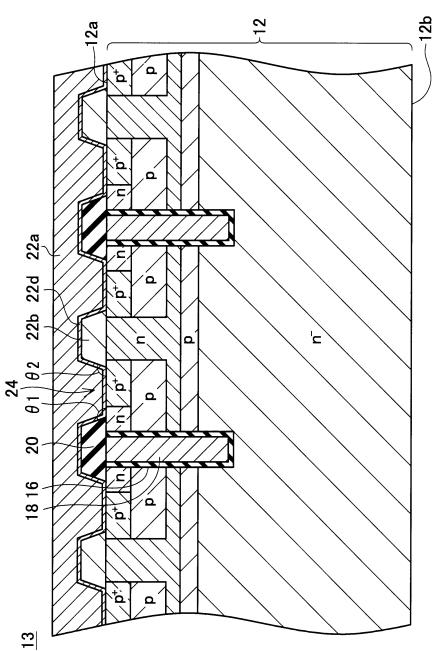

【図14】実施例2の半導体装置200の縦断面図。

【図15】実施例2の半導体装置200の製造工程の説明図。

【図16】実施例2の半導体装置200の製造工程の説明図。

【図17】実施例2の半導体装置200の製造工程の説明図。

## 【発明を実施するための形態】

## 【実施例1】

## 【0013】

図1に示す実施例の半導体装置10は、半導体基板12を有する。半導体基板12の上面12aには、複数のトレンチ14が形成されている。各トレンチ14の内面は、ゲート絶縁膜16によって覆われている。各トレンチ14内には、ゲート電極18が配置されている。各ゲート電極18は、ゲート絶縁膜16によって半導体基板12から絶縁されている。各ゲート電極18の上面は、層間絶縁膜20によって覆われている。各層間絶縁膜20は、半導体基板12の上面12aから上側に突出するように形成されている。

30

## 【0014】

半導体基板12の上面12a上には、ソース電極22が形成されている。ソース電極22は、層間絶縁膜20を覆っている。層間絶縁膜20によってソース電極22はゲート電極18から絶縁されている。ソース電極22は、埋め込み電極22aと、ショットキー電極22bと、表面電極22cを有している。

## 【0015】

ショットキー電極22bは、半導体基板12上に複数個形成されている。各ショットキー電極22bは、2つの層間絶縁膜20に挟まれた範囲内であって各層間絶縁膜20から離間した位置に配置されている。ショットキー電極22bは、半導体基板12の上面12aから上側に突出するように形成されている。半導体基板12の上面12aからショットキー電極22bの上面までの高さは、半導体基板12の上面12aから層間絶縁膜20の上面までの高さと略等しい。ショットキー電極22bは、A1(アルミニウム)により構成されている。ショットキー電極22bは、半導体基板12に対してショットキー接触している。層間絶縁膜20とショットキー電極22bの間には、凹部24が形成されている。凹部24の底面は半導体基板12の上面12aであり、凹部24の一方の側面は層間絶縁膜20の側面であり、凹部24の他方の側面はショットキー電極22bの側面である。

凹部24の底面(すなわち、半導体基板12の上面12a)と層間絶縁膜20の側面との

40

50

間の角度 1 は、90 度より大きい。また、凹部 24 の底面（すなわち、半導体基板 12 の上面 12a）とショットキー電極 22b の側面との間の角度 2 は、90 度より大きい。

#### 【0016】

埋め込み電極 22a は、各凹部 24 内に配置されている。埋め込み電極 22a は、凹部 24 内に隙間なく形成されている。埋め込み電極 22a は、凹部 24 の内面を構成する半導体基板 12 の上面 12a、層間絶縁膜 20 の側面及びショットキー電極 22b の側面に接している。埋め込み電極 22a は、W（タングステン）により構成されている。埋め込み電極 22a は、半導体基板 12 に対してオーム接觸している。

#### 【0017】

表面電極 22c は、層間絶縁膜 20、埋め込み電極 22a 及びショットキー電極 22b 上に形成されている。表面電極 22c は、層間絶縁膜 20、埋め込み電極 22a 及びショットキー電極 22b 上に跨って伸びている。表面電極 22c は、A1 により構成されている。

#### 【0018】

上記の通り、本実施例では、表面電極 22c が、ショットキー電極 22b と同じ材料により構成されている。したがって、本実施例では、表面電極 22c とショットキー電極 22b の境界を視認することが難しい。しかしながら、境界を視認できない場合でも、埋め込み電極 22a の側方に位置する A1 層をショットキー電極 22b と認め、埋め込み電極 22a の上面よりも上側に位置する A1 層を表面電極 22c と認めることができる。

#### 【0019】

半導体基板 12 の下面 12b には、ドレイン電極 26 が形成されている。ドレイン電極 26 は、半導体基板 12 に対してオーム接觸している。

#### 【0020】

半導体基板 12 の内部には、ソース領域 30、上部ボディ領域 32、中間領域 34、下部ボディ領域 36、ドリフト領域 38 及びドレイン領域 40 が形成されている。

#### 【0021】

ソース領域 30 は、n 型の半導体領域である。ソース領域 30 は、半導体基板 12 の上面 12a に露出している。ソース領域 30 は、埋め込み電極 22a に対してオーム接觸している。ソース領域 30 は、ゲート絶縁膜 16 に接觸している。

#### 【0022】

上部ボディ領域 32 は、ソース領域 30 の側方及び下側に形成されている。上部ボディ領域 32 は、p 型不純物濃度が高い p 型の半導体領域である高濃度領域 32a と、p 型不純物濃度が高濃度領域 32a よりも低い p 型の半導体領域である低濃度領域 32b を有している。高濃度領域 32a は、ソース領域 30 の側方に形成されており、半導体基板 12 の上面 12a に露出している。高濃度領域 32a は、埋め込み電極 22a に対してオーム接觸している。低濃度領域 32b は、ソース領域 30 と高濃度領域 32a の下側に形成されている。低濃度領域 32b は、ソース領域 30 の下側でゲート絶縁膜 16 に接觸している。

#### 【0023】

中間領域 34 は、比較的 n 型不純物濃度が低い n 型の半導体領域である。中間領域 34 は、上部ボディ領域 32 に接している。中間領域 34 は、上部ボディ領域 32 によってソース領域 30 から分離されている。中間領域 34 は、ピラー領域 34a とバリア領域 34b を有している。ピラー領域 34a は、半導体基板 12 の上面 12a から半導体基板 12 の厚み方向に沿って伸びる領域である。ピラー領域 34a は、半導体基板 12 の上面 12a に露出しており、ショットキー電極 22b に対してショットキー接觸している。バリア領域 34b は、上部ボディ領域 32 の下側に形成されている。バリア領域 34b は、ピラー領域 34a と繋がっている。バリア領域 34b は、上部ボディ領域 32 の下側でゲート絶縁膜 16 に接觸している。

#### 【0024】

10

20

30

40

50

下部ボディ領域36は、p型の半導体領域である。下部ボディ領域36は、中間領域34の下側に形成されている。下部ボディ領域36は、バリア領域34bの下側でゲート絶縁膜16に接触している。下部ボディ領域36は、中間領域34によって上部ボディ領域32から分離されている。

#### 【0025】

ドリフト領域38は、比較的n型不純物濃度が低いn型の半導体領域である。ドリフト領域38は、下部ボディ領域36の下側に形成されている。ドリフト領域38は、下部ボディ領域36の下側でゲート絶縁膜16に接触している。ドリフト領域38は、下部ボディ領域36によって中間領域34から分離されている。

#### 【0026】

ドレイン領域40は、ドリフト領域38よりもn型不純物濃度が高いn型の半導体領域である。ドレイン領域40は、ドリフト領域38の下側に形成されている。ドレイン領域40は、半導体基板12の下面12bに露出している。ドレイン領域40は、ドレイン電極26に対してオーム接觸している。

#### 【0027】

半導体装置10は、MOSFETとしての動作と、ダイオードとしての動作を実行することができる。

#### 【0028】

MOSFETとして動作する際には、ドレイン電極26にソース電極22よりも高い電位が印加される。ゲート電極18に閾値以上の電位を印加すると、ゲート絶縁膜16近傍の上部ボディ領域32及び下部ボディ領域36にチャネルが形成される。すると、ドレイン電極26から、ドレイン領域40、ドリフト領域38、下部ボディ領域36のチャネル、中間領域34、上部ボディ領域32のチャネル及びソース領域30を経由して、ソース電極22に向かって電流が流れる。すなわち、MOSFETがオンする。ゲート電極18の電位を閾値未満に低下させると、チャネルが消失し、電流が停止する。

#### 【0029】

ソース電極22とドレイン電極26の間には、ソース電極22と中間領域34との境界であるショットキー界面を有するショットキーダイオードと、上部ボディ領域32と中間領域34との境界であるpn接合を有するpnダイオードが形成されている。半導体装置10がダイオードとして動作する際には、ソース電極22にドレイン電極26よりも高い電位が印加される。すると、ソース電極22と中間領域34の境界のショットキー界面がオンする。これによって、ソース電極22から、中間領域34、下部ボディ領域36、ドリフト領域38及びドレイン領域40を経由して、ドレイン電極26に向かって電流が流れる。また、ショットキー界面がオンすることで、バリア領域34bの電位はソース電極22の電位と略等しい電位とされる。これによって、上部ボディ領域32と中間領域34との境界のpn接合がオンし難くなっている。上部ボディ領域32からドリフト領域38にホールが流入することが抑制される。その後、ダイオードに逆電圧を印加すると、ダイオードが逆回復動作を行う。上記のようにダイオードがオンしているときにドリフト領域38へのホールの流入が抑制されるので、逆回復動作時にダイオードに流れる逆電流が抑制される。

#### 【0030】

次に、半導体装置10の製造方法について説明する。半導体装置10は、ドリフト領域38と略同じ不純物濃度を有するn型の半導体基板12から製造される。まず、イオン注入等によって、図2に示すように、半導体基板12に、ソース領域30、上部ボディ領域32、中間領域34及び下部ボディ領域36を形成する。次に、半導体基板12の上面12aを選択的にエッチングすることによって、図3に示すように、半導体基板12の上面12aにトレンチ14を形成する。トレンチ14は、ソース領域30、低濃度領域32b、バリア領域34b及び下部ボディ領域36を貫通するように形成する。次に、図4に示すように、トレンチ14の内面に、ゲート絶縁膜16を形成する。次に、トレンチ14の内部に、ゲート電極18を形成する。なお、以下では、半導体基板12と、半導体基板1

10

20

30

40

50

2に形成された電極、絶縁層等をまとめて、ウエハ13と呼ぶ。

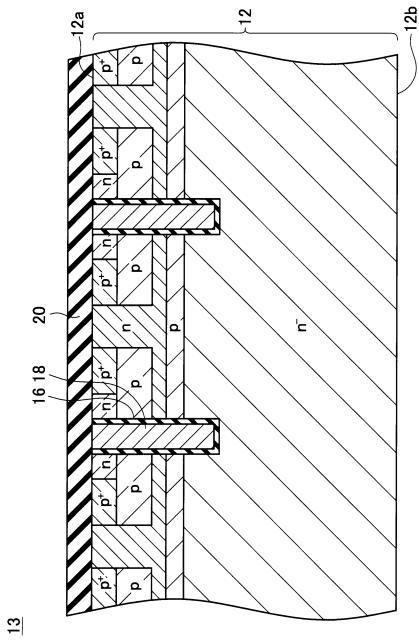

#### 【0031】

次に、図5に示すように、ウエハ13上に、層間絶縁膜20を成長させる。層間絶縁膜20は、ウエハ13の上面の全域を覆うように形成する。層間絶縁膜20を形成したら、層間絶縁膜20を選択的にエッティングする。これによって、図6に示すように、ゲート電極18の上部に層間絶縁膜20を残存させ、その他の位置の層間絶縁膜20を除去する。ここでは、図6に示すように、層間絶縁膜20の側面と、露出している範囲の半導体基板12の上面12aとの間の角度1が90度より大きくなるように、層間絶縁膜20の側面が成形される。

#### 【0032】

次に、スパッタリングによって、図7に示すように、ウエハ13上にショットキー電極22b(すなわち、A1)を成長させる。ショットキー電極22bは、半導体基板12の上面12a及び層間絶縁膜20の表面の全域を覆うように形成する。ショットキー電極22bを形成したら、ショットキー電極22bを選択的にエッティングする。これによって、図8に示すように、中間領域34が上面12aに露出する範囲にショットキー電極22bを残存させ、その他の位置のショットキー電極22bを除去する。ここでは、図8に示すように、ショットキー電極22bの側面と、露出している範囲の半導体基板12の上面12aとの間の角度2が90度より大きくなるように、ショットキー電極22bの側面が成形される。このようにショットキー電極22bをエッティングすることで、ショットキー電極22bが層間絶縁膜20から離間する。このため、ショットキー電極22bと層間絶縁膜20の間に凹部24が形成される。

10

#### 【0033】

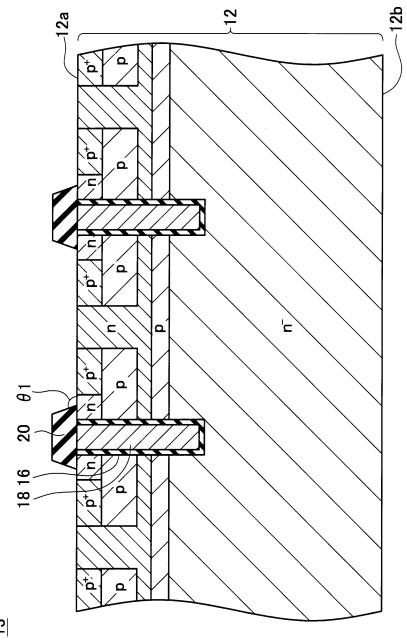

次に、図9に示すように、ウエハ13上に埋め込み電極22a(すなわち、W)を成長させる。埋め込み電極22aは、半導体基板12の上面12a、層間絶縁膜20及びショットキー電極22bの表面の全域を覆うように形成する。埋め込み電極22aの材料であるWは、基礎となる素材の表面に均等に成長する。このため、図9に示すように、層間絶縁膜20及びショットキー電極22bによってウエハ13の表面に凹凸が形成されても、埋め込み電極22aの表面が略平坦となる。また、埋め込み電極22aの材料であるWは、狭い凹部24内にも隙間なく成長させることができる。特に、凹部24では、底面と層間絶縁膜20側の側面との間の角度1が90度より大きく、底面とショットキー電極22b側の側面との間の角度2が90度より大きい。すなわち、凹部24は、上端部の幅が底部の幅より広くなっている。このため、埋め込み電極22aを凹部24内により確実に成長させることができることが可能となっている。したがって、凹部24内に空隙が形成されることが防止される。

20

#### 【0034】

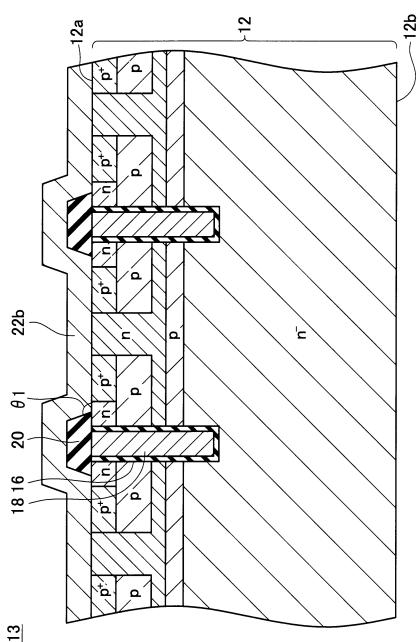

埋め込み電極22aを形成したら、埋め込み電極22aをエッティングする。ここでは、SF6(六フッ化硫黄)をエッティングガスとして用いる。エッティングによって、図10に示すように、埋め込み電極22aの上面を、層間絶縁膜20の上面及びショットキー電極22bの上面より下側まで後退させる。すなわち、層間絶縁膜20の上面及びショットキー電極22bの上面を露出させる。このため、層間絶縁膜20は、凹部24内に残存する。エッティング時には、エッティング後の埋め込み電極22aの上面が、層間絶縁膜20の上面及びショットキー電極22bの上面に近い高さとなるように、エッティング時間を調節する。また、このように埋め込み電極22aをエッティングすると、埋め込み電極22aの上面が略平坦となる。以下、その理由について説明する。

30

#### 【0035】

図11、12は、金属をエッティングする工程の説明図である。図11、12では、2つの凸部102と、2つの凸部102に挟まれた凹部104を有する表面100上に金属層110を形成し、その後、2つの凸部102の上面が露出するまで金属層110をエッティングする工程を表している。図11は、凹部104の幅が広い場合を示しており、図12は、凹部104の幅が狭い場合を示している。エッティングは凹部104の中央部では、凹

40

50

部 104 の端部（すなわち、凸部 102 の近傍）よりも速く進行する。このエッティング速度の差は、凹部 104 の幅が広いほど顕著となる。このため、凹部 104 の幅が広いと、図 11 に示すように、エッティング後に凹部 104 内に残存する金属層 110 の表面は凹状に大きく湾曲した形状となる。これに対し、凹部 104 の幅が狭いと、図 12 に示すように、エッティング後の金属層 110 の表面が湾曲する度合いが小さい。凹部 104 の幅が狭いと、エッティング後の金属層 110 の表面はより平坦となる。

#### 【0036】

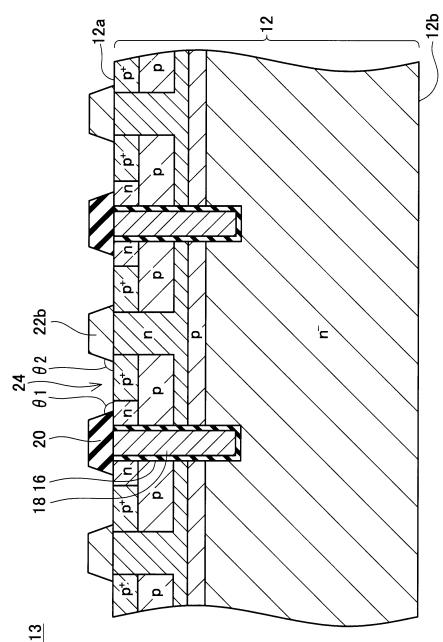

本実施例の製造方法では、図 10 に示すように、凸状の層間絶縁膜 20 から間隔を開けた位置に、凸状のショットキー電極 22b が形成されている。これによって、層間絶縁膜 20 とショットキー電極 22b の間に、幅が狭い凹部 24 が形成されている。このように凹部 24 の幅が狭いため、埋め込み電極 22a のエッティング後に、埋め込み電極 22a の上面を略平坦とすることができます。このため、埋め込み電極 22a のエッティング後に、埋め込み電極 22a の上面、層間絶縁膜 20 の上面及びショットキー電極 22b の上面によって構成されるウエハ 13 の上面が、略平坦となる。

#### 【0037】

次に、図 13 に示すように、ウエハ 13 上に、表面電極 22c（すなわち、A1）を成長させる。表面電極 22c は、層間絶縁膜 20、埋め込み電極 22a 及びショットキー電極 22b の上面の全域を覆うように形成する。上述したように、ウエハ 13 の上面が平坦であるので、表面電極 22c の上面が平坦となる。

#### 【0038】

表面電極 22c を形成したら、裏面側の構造（すなわち、ドレイン領域 40 及びドレン電極 26）を形成する。その後、ウエハ 13 をダイシングすることで、図 1 に示す半導体装置 10 が完成する。

#### 【0039】

以上に説明したように、この製造方法によれば、表面電極 22c の表面を平坦化することができる。

#### 【実施例 2】

#### 【0040】

図 14 に示す実施例 2 の半導体装置 200 では、ソース電極 22 が、バリアメタル層 22d を有する。実施例 2 の半導体装置 200 のその他の構成は、実施例 1 の半導体装置 10 と等しい。

#### 【0041】

バリアメタル層 22d は、TiN（窒化チタン）により構成されている。バリアメタル層 22d の厚みは、層間絶縁膜 20 及びショットキー電極 22b に比べて遥かに薄い。バリアメタル層 22d は、層間絶縁膜 20 の上面と、ショットキー電極 22b の上面と、凹部 24 の内面を覆っている。実施例 2 の半導体装置 200 は、実施例 1 の半導体装置 10 と略同様に動作する。

#### 【0042】

実施例 2 の半導体装置 200 を製造する際には、まず、実施例 1 と同様にして、図 8 に示すようにウエハ 13 を加工する。次に、図 15 に示すように、ウエハ 13 上に、バリアメタル層 22d を成長させる。すなわち、層間絶縁膜 20 の上面と、ショットキー電極 22b の上面と、凹部 24 の内面にバリアメタル層 22d を成長させる。すなわち、実施例 2 では、ゲート電極 18 上の凸部が、層間絶縁膜 20 とバリアメタル層 22d によって構成される。また、ピラー領域 34a 上の凸部が、ショットキー電極 22b とバリアメタル層 22d によって構成される。次に、図 16 に示すように、バリアメタル層 22d 上に、埋め込み電極 22a（すなわち、W）を成長させる。ここでは、実施例 1 と同様にして、埋め込み電極 22a の表面が平坦になり、凹部 24 内に隙間なく埋め込み電極 22a が形成される。

#### 【0043】

次に、埋め込み電極 22a をエッティングする。ここでは、SF6（六フッ化硫黄）を工

10

20

30

40

50

ツチングガスとして用いる。これによって、図17に示すように、埋め込み電極22aの上面を、層間絶縁膜20上のバリアメタル層22dの上面及びショットキー電極22b上のバリアメタル層22dの上面より下側まで後退させる。すなわち、層間絶縁膜20上及びショットキー電極22b上のバリアメタル層22dを露出させる。埋め込み電極22aは、凹部24内に残存させる。本実施例では、層間絶縁膜20とショットキー電極22bがバリアメタル層22dに覆われているので、図17に示すエッチング時に、層間絶縁膜20とショットキー電極22bがエッチングガスに曝されない。また、バリアメタル層22d(TiN)とエッチング対象である埋め込み電極22a(W)のエッチングガス(SF6)に対する選択比は、1対30である。すなわち、バリアメタル層22dは、エッチングガスによるエッチングをほとんど受けない。したがって、バリアメタル層22dによって層間絶縁膜20とショットキー電極22bがエッチングガスから保護される。なお、少なくとも上記選択比が1対5以上となる材料を、バリアメタル層22dとして使用することができる。また、ここでも、実施例1と同様にして、埋め込み電極22aのエッチング後に、ウエハ13の上面が、略平坦となる。

#### 【0044】

埋め込み電極22aをエッチングしたら、図14に示すように、ウエハ13の上面に表面電極22cを成長させる。実施例1と同様に、上面が平坦な表面電極22cを形成することができる。その後、下面側の構造を形成し、ダイシングすることで、図14に示す半導体装置200が完成する。

#### 【0045】

以上に説明したように、実施例2の半導体装置200の製造工程でも、表面電極22cの表面を平坦化することができる。また、実施例2の方法によれば、層間絶縁膜20及びショットキー電極22bをエッチングガスから保護することができる。

#### 【0046】

なお、上述した実施例1、2では、トレンチ型のゲート電極を有するMOSFETとショットキーダイオードを有する半導体装置について説明した。しかしながら、MOSFETの代わりに、トレンチ型のゲート電極を有するIGBTが形成されていてもよい。また、MOSFETの代わりに、トレンチ内に配置された電極を有するpnダイオードが形成されていてもよい。すなわち、トレンチ内に配置された電極を有する素子と、ショットキー電極を有する様々な半導体装置において、本明細書に開示の技術を適用することができる。

#### 【0047】

また、上述した実施例1、2では、ショットキー電極22bと表面電極22cが同じA1によって構成されていたが、これらが異なる材料によって構成されていてもよい。例えば、ショットキー電極22bをPd(パラジウム)により構成されていてもよい。

#### 【0048】

次に、本明細書で開示される構成の例について説明する。本明細書で開示される一例の半導体装置では、埋め込み電極に覆われている範囲において、半導体基板の表面と層間絶縁膜の側面の間の角度が90度より大きい。

#### 【0049】

このような構成によれば、凹部内に埋め込み電極を好適に形成することができる。

#### 【0050】

本明細書で開示される一例の半導体装置では、埋め込み電極に覆われている範囲において、半導体基板の表面とショットキー電極の側面の間の角度が90度より大きい。

#### 【0051】

このような構成によれば、凹部内に埋め込み電極を好適に形成することができる。

#### 【0052】

本明細書で開示される一例の半導体装置では、ショットキー電極と表面電極の間、及び、層間絶縁膜と表面電極の間に、埋め込み電極に対してエッチング選択性を有するバリアメタル層が配置されている。

10

20

30

40

50

**【0053】**

このような構成によれば、ショットキー電極及び層間絶縁膜をエッティング剤から保護することができる。

**【0054】**

本明細書で開示される一例の半導体装置では、埋め込み電極が、半導体基板に対してオーム接觸している。

**【0055】**

これにより、ショットキー電極とオーム接觸を有する半導体装置を製造することができる。

**【0056】**

本明細書で開示される一例の半導体装置の製造方法では、埋め込み電極が、ショットキー電極とは異なる金属により構成される。

10

**【0057】**

以上、実施形態について詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。

本明細書または図面に説明した技術要素は、単独あるいは各種の組み合わせによって技術有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの1つの目的を達成すること自体で技術有用性を持つものである。

20

**【符号の説明】****【0058】**

10 : 半導体装置

12 : 半導体基板

14 : トレンチ

16 : ゲート絶縁膜

18 : ゲート電極

20 : 層間絶縁膜

22 : ソース電極

22 a : 埋め込み電極

30

22 b : ショットキー電極

22 c : 表面電極

22 d : バリアメタル層

24 : 凹部

26 : ドレイン電極

30 : ソース領域

32 : 上部ボディ領域

34 : 中間領域

36 : 下部ボディ領域

38 : ドリフト領域

40 : ドレイン領域

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

## フロントページの続き

| (51)Int.Cl. |                  | F I                                                                                    |

|-------------|------------------|----------------------------------------------------------------------------------------|

| H 01 L      | 27/088 (2006.01) | H 01 L 29/78 6 5 2 E                                                                   |

| H 01 L      | 29/872 (2006.01) | H 01 L 29/78 6 5 2 C                                                                   |

| H 01 L      | 21/329 (2006.01) | H 01 L 27/06 1 0 2 A                                                                   |

| H 01 L      | 29/41 (2006.01)  | H 01 L 27/08 1 0 2 E                                                                   |

| H 01 L      | 21/28 (2006.01)  | H 01 L 29/86 3 0 1 F                                                                   |

| H 01 L      | 29/861 (2006.01) | H 01 L 29/86 3 0 1 P                                                                   |

| H 01 L      | 29/868 (2006.01) | H 01 L 29/44 S<br>H 01 L 21/28 E<br>H 01 L 29/91 K<br>H 01 L 29/91 A<br>H 01 L 29/91 C |

(56)参考文献 特開2004-221218(JP, A)

米国特許出願公開第2014/0231827(US, A1)

特開2011-199060(JP, A)

特開2005-101514(JP, A)

特表2006-501666(JP, A)

特開2011-091283(JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 9 / 7 8     |

| H 01 L | 2 9 / 8 6 1   |

| H 01 L | 2 9 / 8 6 8   |

| H 01 L | 2 9 / 4 1     |

| H 01 L | 2 9 / 4 2 3   |

| H 01 L | 2 1 / 2 8     |

| H 01 L | 2 1 / 3 2 9   |

| H 01 L | 2 1 / 3 3 6   |

| H 01 L | 2 1 / 8 2 3 4 |

| H 01 L | 2 7 / 0 6     |

| H 01 L | 2 7 / 0 8 8   |