(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년09월21일

(11) 등록번호 10-1658437

(24) 등록일자 2016년09월12일

(51) 국제특허분류(Int. Cl.)

*H03H 9/46* (2006.01) *H03H 7/01* (2006.01)

*H03H 9/54* (2006.01)

(21) 출원번호 10-2014-7037102

(22) 출원일자(국제) 2014년03월14일

심사청구일자 2014년12월31일

(85) 번역문제출일자 2014년12월31일

(65) 공개번호 10-2015-0032849

(43) 공개일자 2015년03월30일

(86) 국제출원번호 PCT/US2014/029800

(87) 국제공개번호 WO 2014/145113

국제공개일자 2014년09월18일

(30) 우선권주장

13/838 943 2013년03월15일 미국(US)

(73) 특허권자

**레저넌트 임크.**

미국 93117 캘리포니아주 산타 바바라 스위트 100

캐스틸리안 드라이브 110

(72) 발명자

**터너, 패트릭, 제이.**

미국 93103 캘리포니아주 산타 바바라 노쓰 살리

나스 스트리트 111

**실버, 리차드, 엔.**

미국 94116 캘리포니아주 샌 프란시스코 파체코

스트리트 369

(뒷면에 계속)

(74) 대리인

**양영준, 백만기, 정은진**

(56) 선행기술조사문헌

US20090002102 A1\*

\*는 심사관에 의하여 인용될 문

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 25 항

심사관 : 김재문

(54) 발명의 명칭 마이크로웨이브 음파 필터들의 회로망 합성 설계

## (57) 요약

## 대 표 도

터 회로 설계를 생성하기 위하여 상기 선택된 무순실 회로 응답 변수들에 기초하여 상기 회로 소자들 각각에 대한 값을 선택하는 단계, 음파 필터 회로 설계를 생성하기 위하여 상기 초기 필터 회로 설계의 공진 소자(들) 및 다른 리액티브 회로 소자(들)를 적어도 하나의 음파 공진기 모델로 변환하는 단계, 사전 최적화된 필터 회로 설계를 생성하기 위하여 상기 음파 필터 회로 설계에 기생 효과를 추가하는 단계, 최종 필터 회로 설계를 생성하기 위하여 상기 사전 최적화된 필터 회로 설계를 최적화하는 단계, 및 상기 최종 필터 회로 설계에 기초하여 상기 음파 마이크로웨이브 필터를 구성하는 단계를 포함한다.

(72) 발명자

윌렘센 코르테스, 발람 퀴체 안드레스

미국 02420 매사추세츠주 렉싱턴 매사추세츠 애비뉴 1009

라인, 커트, 에프.

미국 93117 캘리포니아주 골레타 캐논 그린 드라이브 487

팬지, 닐, 오.

미국 93111 캘리포니아주 산타 바바라 버티스 스트리트 650

해먼드, 로버트, 비.

미국 93109 캘리포니아주 산타 바바라 캠페닐 드라이브 3245

## 명세서

### 청구범위

#### 청구항 1

주파수 응답 요건들(단계 52)에 따라서 음파 마이크로웨이브 필터를 설계하는 방법으로서,

복수의 회로 소자들(114-120)을 포함하는 초기 필터 회로 구조(100)를 선택하는 단계(단계 56) - 상기 복수의 회로 소자들(114-120)은 적어도 하나의 공진 소자(114) 및 적어도 하나의 리액티브(reactive) 회로 소자(116-120)를 포함함 -;

상기 주파수 응답 요건들에 기초하여 무손실 회로 응답 변수들을 선택하는 단계(단계 60);

초기 필터 회로 설계를 생성하기 위하여 상기 선택된 무손실 회로 응답 변수들을 기초로 상기 회로 소자들(114-120) 각각에 대한 값을 선택하는 단계(단계 62);

음파 필터 회로 설계를 생성하기 위하여 상기 초기 필터 회로 설계의 상기 적어도 하나의 공진 소자(114) 및 상기 적어도 하나의 리액티브 회로 소자(116-120)를 적어도 하나의 음파 공진기 모델(122)로 변환하는 단계(단계 64);

사전 최적화된 필터 회로 설계를 생성하기 위하여 상기 음파 필터 회로 설계에 기생 효과를 추가하는 단계(단계 68);

최종 필터 회로 설계를 생성하기 위하여 컴퓨터화된 필터 최적화기를 사용하여 상기 사전 최적화된 필터 회로 설계를 최적화하는 단계(단계 70); 및

상기 음파 마이크로웨이브 필터를 구성하는 단계(단계 72) - 상기 음파 마이크로웨이브 필터의 회로 소자 값들 중 적어도 일부는 상기 최종 필터 회로 설계에서의 대응하는 회로 소자 값들에 매칭함 -

를 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

#### 청구항 2

제1항에 있어서, 상기 주파수 응답 요건들은 주파수 종속 복귀 손실, 삽입 손실, 저지(rejection) 및 선형성 중 하나 이상을 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

#### 청구항 3

제1항에 있어서, 상기 주파수 응답 요건들은 500-3500MHz 범위의 통과대역을 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

#### 청구항 4

제1항에 있어서, 상기 주파수 응답 요건들은 통과대역 및 저지대역(stopband)을 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

#### 청구항 5

제1항에 있어서, 상기 적어도 하나의 공진 소자(114) 각각은 커패시터( $C^{R1}$ ) 및 인덕터( $L^{R1}$ )의 병렬 L-C 공진기 조합을 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

#### 청구항 6

제1항에 있어서, 상기 적어도 하나의 리액티브 회로 소자(116)는 커패시터( $C_{11}$ )를 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

#### 청구항 7

제1항에 있어서, 상기 초기 필터 회로 구조(100)는 인-라인 비공진 노드 회로 구조인, 음파 마이크로웨이브 필

터를 설계하는 방법.

### 청구항 8

제1항에 있어서, 상기 무손실 회로 응답 변수들은 송신 제로(zero)들을 정의하는 문자 다항식들과 반사 제로들을 정의하는 분모 다항식들 간의 비와 스케일 팩터(scale factor)를 곱한 형태를 갖는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 9

제8항에 있어서, 송신 제로들의 전체 수는 반사 제로들의 전체 수와 동일하거나 또는 그보다 큼, 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 10

제1항에 있어서, 상기 적어도 하나의 음파 공진기 모델(122)은 각각 적어도 하나의 BVD(Butterworth-Van Dyke) 모델인, 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 11

제10항에 있어서, 상기 적어도 하나의 공진 소자(114) 중 하나는 인-션트 병렬 L-C 공진기 조합( $C^{R1}, L^{R1}$ )을 포함하며, 상기 적어도 하나의 리액티브 회로 소자(116) 중 하나는 상기 인-션트 병렬 L-C 공진기 조합( $C^{R1}, L^{R1}$ )과 직렬인 인-션트 어드미턴스(admittance) 인버터( $J_{11}$ )를 포함하며, 상기 적어도 하나의 리액티브 회로 소자(118) 중 또 다른 하나는 상기 인-션트 병렬 L-C 공진기 조합( $C^{R1}, L^{R1}$ )과 병렬인 인-션트 비공진 서셉턴스(susceptance)( $B^{N1}$ )를 포함하고, 상기 인-션트 병렬 L-C 공진기 조합( $C^{R1}, L^{R1}$ ), 상기 인-션트 어드미턴스 인버터( $J_{11}$ ), 및 상기 인-션트 비공진 서셉턴스( $B^{N1}$ )는 상기 적어도 하나의 BVD 모델(122) 중 하나의 BVD 모델로 변환되는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 12

제11항에 있어서, 상기 인-션트 병렬 L-C 공진기 조합( $C^{R1}, L^{R1}$ ) 및 상기 인-션트 어드미턴스 인버터( $J_{11}$ )는 인-션트 직렬 L-C 공진기 조합(134)으로 변환되고, 상기 인-션트 직렬 L-C 공진기 조합(134) 및 상기 인-션트 비공진 서셉턴스( $B^{N1}$ )는 상기 하나의 BVD 모델(122)로 변환되는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 13

제11항에 있어서, 상기 BVD 모델(122)은 인-션트 BVD 모델인, 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 14

제13항에 있어서, 상기 적어도 하나의 리액티브 회로 소자(120)는 상기 인-션트 병렬 L-C 공진기 조합( $C^{R1}, L^{R1}$ )과 상기 인-션트 비공진 서셉턴스( $B^{N1}$ ) 사이의 노드(1)에 연결된 2개의 인-라인 어드미턴스 인버터들( $J_{S1}, J_{12}$ )을 더 포함하며, 상기 인-션트 BVD 모델(122) 및 상기 2개의 인-라인 어드미턴스 인버터들( $J_{S1}, J_{12}$ )은 인-라인 BVD 모델(122a) 및 상기 인-라인 BVD 모델(122a)과 직렬인 리액턴스( $X_1$ )로 변환되는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 15

제1항에 있어서, 상기 적어도 하나의 공진 소자(114)는 복수의 공진 소자들을 포함하며, 상기 적어도 하나의 리액티브 회로 소자(116-120)는 복수의 리액티브 회로 소자들을 포함하며, 상기 적어도 하나의 음파 공진기 모델(122)은 복수의 공진기 모델들을 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 16

제15항에 있어서, 상기 초기 필터 회로 설계를 복수의 서브셋 회로 설계들(130a, 130b)로 분할하는 단계를 더 포함하며, 상기 복수의 서브셋 회로 설계들 각각은 상기 공진 소자들(114) 중 하나와 상기 복수의 리액티브 회로 소자들(116-120) 중 하나 이상을 포함하고, 각각의 서브셋 회로 설계(130a, 130b)마다, 상기 하나의 공진 소자(114) 및 상기 하나 이상의 리액티브 회로 소자들(116-120)은 상기 음파 공진기 모델들(122) 중 각각의 음파 공진기 모델로 변환되는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 17

제1항에 있어서, SAW(surface acoustic wave) 공진기, BAW(bulk acoustic wave) 공진기, FBAR(flim bulk acoustic resonator), 및 MEMS(microelectromechanical system) 공진기 중 하나로부터 상기 적어도 하나의 공진 소자 각각의 구조적 타입을 선택하는 단계(단계 54)를 더 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 18

제1항에 있어서,

상기 주파수 응답 요건들을 정규화된 설계 공간에 매핑하는 단계 - 상기 회로 소자 값들은 상기 매핑된 주파수 응답 요건들에 기초하여 결정되는 정규화된 값들임-(단계 58); 및

상기 음파 필터 회로 설계의 상기 정규화된 회로 소자 값들을 실제 설계 공간에 언매핑(unmapping)하는 단계(단계 66)를 더 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 19

제1항에 있어서, 상기 적어도 하나의 공진 소자(114)는 복수의 공진 소자들을 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 20

제19항에 있어서,

복수의 필터 솔루션(solution)들을 생성하기 위하여 상기 사전 최적화된 필터 회로 설계에서의 상기 복수의 공진 소자들(114)이 신호 송신 경로를 따라 배치되는 순서를 변경하는 단계;

상기 필터 솔루션들 각각에 대한 성능 파라미터를 계산하는 단계;

상기 성능 파라미터들을 서로 비교하는 단계; 및

상기 계산된 성능 파라미터들의 비교에 기초하여 상기 필터 솔루션들 중 하나를 상기 사전 최적화된 필터 회로 설계로서 선택하는 단계를 더 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 21

제1항에 있어서, 상기 최종 필터 회로 설계를 생성하기 위하여 상기 사전 최적화된 필터 회로 설계의 소자 제거 최적화를 수행하는 단계(단계 70)를 더 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 22

제1항에 있어서, 상기 최종 필터 회로 설계는 복수의 음파 공진기들(Res1-Res8)을 포함하며, 상기 최종 필터 회로 설계에서 상기 복수의 음파 공진기들(Res1-Res8)의 가장 낮은 공진 주파수와 가장 높은 공진 주파수 간의 차이는 상기 복수의 음파 공진기들(Res1-Res8)에서 단일 공진기의 최대 주파수 분리의 적어도 1배인, 음파 마이크로웨이브 필터를 설계하는 방법.

### 청구항 23

제22항에 있어서, 상기 최종 필터 회로 설계에서 복수의 공진기들(Res1-Res8)의 가장 낮은 공진 주파수와 가장 높은 공진 주파수 간의 차이는 상기 복수의 공진기들(Res1-Res8)에서 단일 공진기의 최대 주파수 분리의 적어도 2배인, 음파 마이크로웨이브 필터를 설계하는 방법.

## 청구항 24

제22항에 있어서, 상기 최종 필터 회로 설계에서 복수의 공진기들(Res1-Res8)의 가장 낮은 공진 주파수와 가장 높은 공진 주파수 간의 차이는 상기 복수의 공진기들(Res1-Res8)에서 단일 공진기의 최대 주파수 분리의 적어도 3배인, 음파 마이크로웨이브 필터를 설계하는 방법.

## 청구항 25

제1항에 있어서, 상기 사전 최적화된 필터 회로 설계를 최적화하는 단계는 상기 최종 필터 회로 설계를 생성하기 위하여 상기 사전 최적화된 필터 회로 설계를 필터 최적화기에 입력하는 단계를 포함하는 음파 마이크로웨이브 필터를 설계하는 방법.

### 발명의 설명

### 기술 분야

[0001] 본 발명은 일반적으로 마이크로웨이브 필터에 관한 것으로, 특히 음파 마이크로웨이브 필터에 관한 것이다.

### 배경 기술

[0002] 통신 어플리케이션을 위한 저 손실 주파수 선택성 전기 신호 필터는 전신 및 전화 용도로 1910년경부터 개발이 시작되었고, 특히 장거리 케이블 및 무선 링크들 상에 실리는 통신 신호 채널들의 멀티플렉싱 및 디멀티플렉싱을 위해 개발되었다. "이미지" 또는 "이미지 파라미터" 설계 방법들로 명명된 필터 설계 방법이, 특히 벨 연구소에서 개발되었다(참고, George A. Campbell, Physical Theory of the Electric Wave Filter, The Bell System Technical Journal, Volume I, No. 2 (November 1922); Otto J. Zobel, Theory and Design of Uniform and Composite Electric Wave-Filters, The Bell System Technical Journal, Volume II, No. 1 (January 1923)). 이를 필터 회로는 인덕터, 커패시터 및 변압기를 포함하는 회로 소자들을 활용했다.

[0003] 1920년대에, AW(Acoustic wave) 공진기, 특히 석영 BAW(bulk acoustic wave) 공진기가, 일부 전기 신호 필터에서 사용되기 시작했다. AW 공진기의 등가 회로는 "공진" 주파수 및 "반공진(anti-resonance)" 주파수로 불리는 주파수에서 가깝게 이격된 2개의 공진들을 가진다(참고, K.S. Van Dyke, Piezo-Electric Resonator and its Equivalent Network Proc. IRE, Vol. 16, 1928, pp.742-764). 이미지 필터 설계 방법은 이를 석영 공진기들을 활용하는 필터 회로에 적용되었고, 2개의 AW 필터 회로 타입: "래더(ladder)" 및 "래티스(lattice)" AW 필터 설계들을 가져왔다(참고, L. Espenschied, Electrical Wave Filter, 미국특허번호 제1,795,204호; 및 WP Mason, "Electrical Wave Filters Employing Quartz Crystals as Elements", The Bell System Technical Journal (1934)).

[0004] 1920년 및 1930년대에, "회로망 합성"으로 언급되게 된 다른 접근법이 통신 어플리케이션용의 주파수 선택성 전기 신호 필터의 설계를 위해 개발되었다. 이런 새로운 필터 회로 설계 방법은 특히 미국의 포스터(Foster) 및 달링턴(Darlington)(참고, Ronald M. Foster, "A Reactance Theorem," Bell Syst. Tech. J., Vol 3, 1924, pp. 259-267, and S. Darlington, "Synthesis of Reactance 4-poles which produce prescribed insertion loss characteristics", J. Math Phys, Vol 18, 1939, pp. 257-353.), 및 독일의 카우어(Cauer)(참고, W. Cauer, 미국특허 제1,989,545호, 1935)에 의해 개척되었다.

[0005] "회로망 합성"에서, 회로 소자 타입들과 이들이 상호접속되는 방식을 포함하는 초기 회로 구조가 선택된 후, 원하는 무손실 필터 응답은 산란 파라미터들, 예컨대 S21 및 S11과 같은 복소 주파수 종속 회로 응답 파라미터들의 형태로 복잡한 다항식의 비로 변환된다(translated). S21 산란 파라미터는 다음과 같이 표현될 수 있다:

### 수학식 1

$$H(s) = \frac{N(s)}{D(s)} = K \frac{(s - z_1)(s - z_2) \cdots (s - z_m)}{(s - p_1)(s - p_2) \cdots (s - p_n)}$$

[0007] 여기서, N(s)은 분자 다항식이고, D(s)는 분모 다항식이고,  $z_i$ 들은 방정식  $N(s)=0$ 의 루트(또는 송신 제로(zero)들)이며,  $p_i$ 들은 방정식  $D(s)=0$ 의 루트(또는 반사 제로들)이고,  $m$ 은 송신 제로들의 수이며,  $n$ 은 반사 제로들

의 수이고, K는 스케일 팩터이다(유의: 무손실의 경우에, 송신 제로들은 S21의 제로들이며, 반사 제로들은 S11의 제로들이다. 작지만 유한한 실제 손실들이 회로 설계 프로세스에 후에 부가되는 경우, 이들 제로들은 작지만 더이상 정확히 제로가 안될 수 있고, 최종 필터의 고유 주파수 및 공진에 대응할 수 있다). 필터 회로 소자값들은 그 후 복잡한 다항식의 비로부터 무손실의 경우에 정확히 "합성(계산)"될 수 있다. 실제로 작게 유지되는 손실을 무시하면, "합성" 회로의 응답은 원하는 응답 함수에 매칭한다.

[0008] 1950년 및 1960년대에, 회로망 합성은 통신 및 다른 어플리케이션용의 마이크로웨이브 필터의 설계에 성공적으로 적용되었다. 이들 새로운 필터는 높은 Q(저 손실) 전자기 공진기들과, 회로 소자들로서 이들 공진기들 간의 전자기 결합을 활용한다(참고, George L. Matthaei et al., *Microwave Filters, Impedance-Matching Networks, and Coupling Structures*, McGraw-Hill Book Company, pp. 95-97, 438-440 (1964); and Richard J. Cameron et al., *Microwave Filters for Communication Systems: Fundamentals, Design and Applications*, Wiley-Interscience (2007)..). 회로망 합성은 또한 1960년대에 시작한 통신 및 다른 어플리케이션용의 음파 필터의 설계에 적용되었다(참고, Anatol I. Zverev, *Handbook of Filter Synthesis*, John Wiley & Sons, pp.414-498 (1967); and Robert G. Kinsman, *Crystal Filters: Design, Manufacture, and Application*, John Wiley & Sons, pp. 37-105 and 117-155, (1987)..) 이 논문에서는 초기 회로 구조에 음파 공진기의 공진만이 포함된다. 반공진은 초기 회로의 소자값들이 회로망 합성 방법에 의해 계산된 후 회로에 추가되는 기생 효과로서 취급된다.

[0009] 대략 1992년부터, 박막 SAW(surface acoustic wave) 공진기 및 박막 BAW(bulk acoustic wave) 공진기들이 개발되었고 마이크로웨이브 주파수(> 500MHz)에서 사용되기 시작했다. 에스펜쉬드(Espenschied) 타입 래더 음파 필터 설계의 예인 AW IEF(impedance element filter) 설계가 활용되었다(참고, O. Ikata, et al., *Development of Low-Loss Bandpass Filters Using Saw Resonators for Portable Telephones*, 1992 Ultrasonics Symposium, pp. 111-115; and Ken-ya Hashimoto, *Surface Acoustic Wave Devices in Telecommunications: Modeling and Simulation*, Springer (2000), pp. 149-161). SAW 및 BAW 구현시 이미지 설계 AW IEF 대역 통과 필터는 이동통신 디바이스의 RF(radio frequency) 전단에서 마이크로웨이브 필터링 어플리케이션에 종종 사용되었다. 이동통신 산업에서 특히 중요한 것은 대략 500-3,500MHz의 주파수 범위이다. 미국에서는 셀룰러 통신에 사용되는 다수의 표준 대역들이 존재한다. 이들은 대역 2(~1800-1900MHz), 대역 4(~1700-2100MHz), 대역 5(~800-900MHz), 대역 13(~700-800MHz), 및 대역 17(~700-800MHz)를 포함하고, 다른 대역들이 부상하고 있다.

[0010] 필터의 특수한 종류인 듀플렉서는 이동 디바이스의 전단에서 핵심 구성 요소이다. 현대의 이동 통신 디바이스는 (CDMA(Code Division Multiple Access), WCDMA(Wide Code Division Multiple Access), 또는 LTE(Long Term Evolution)을 사용하여) 동시에 송신 및 수신하고 동일한 안테나를 사용한다. 듀플렉서는 피코 와트(picowatt)만큼 낮을 수 있는 수신 신호로부터 0.5와트까지의 전력일 수 있는 송신 신호를 분리한다. 송신 및 수신 신호들은 듀플렉서가 선택하는 것을 가능케 하는 상이한 주파수들의 반송파들에 변조되는데, 그렇다 할지라도 듀플렉서는 낮은 삽입 손실, 높은 선택성, 작은 회로 면적, 높은 전력 핸들링, 높은 선형성 및 낮은 비용을 제공해야만 한다. 이미지 설계 대역통과 AW IEF 필터는 듀플렉서에서 사용되는 것이 일반적으로 바람직한데, 그 이유는 이것이 이를 요건들을 만족하며, 태핑된 지연 라인(tapped delay line)(이는 더 높은 손실을 가짐), 그리고 공진 단상 단방향 트랜스듀서(SPUDT: single-phase unidirectional transducer) 필터(요구되는 좁은 라인 이 마이크로웨이브 주파수에 대한 스케일링을 막음)와 같은 대안들보다 현저히 양호하기 때문이다; 하지만 이중 모드 SAW(DMS)(종방향 결합 공진기(LCR; longitudinally coupled resonator)라고도 불림) 필터가 그것이 제공하는 밸런싱된 출력에 기인하여 듀플렉서에서의 수신 필터에 때때로 이용되기도 한다(참고, David Morgan, *Surface Acoustic Wave Filters With Applications to Electronic Communications and Signal Processing* Morgan, pp. 335-339, 352-354(2007)).

[0011] 이러한 전통적인 AW IEF 필터 설계에 대한 사소한 변형은 전형적으로 하나 이상의 회로 소자들(예컨대, 커파시터, 인덕터, 또는 AW 공진기)를 IEF 설계에 추가하여 특정 회로 특징을 강화하거나 추가하는 이들 어플리케이션(예컨대, 미국특허 제8,026,776호 및 미국특허 제8,063,717호 참조)에서 고려되었다. 이것은, 최적화된 IEF와 비교했을 때 추가 소자(들)이 부가된 후 현재 사용되는 컴퓨터 최적화 툴이 수렴하여 개선된 설계를 생성할 만큼 AW IEF 회로에 대한 영향이 충분히 작은 경우에 달성될 수 있다. 이것은 가깝게 이격된 공진 및 반공진을 갖는 AW 공진기를 포함하는 임의의 회로에 대한 엄격한 요건이며, 따라서 기본 AW IEF 설계 및 기능에 매우 작은 변동만을 허용하게 된다.

[0012] 개선된 성능, 더 작은 크기 및 더 낮은 비용을 제공할 뿐만 아니라 조정성을 통합하기 위해 개선된 마이크로웨이브 음파 필터들이 요구된다. 회로망 합성은 음파 공진기 필터의 복합 속성이 회로망 합성 프로세스에 직접

통합될 때 길을 제공하는데, 이것이 본 발명의 요지이다.

### 발명의 내용

[0013]

본 발명에 따르면, 주파수 응답 요건들(예컨대, 주파수 종속 복귀 손실, 삽입 손실, 져지(rejection), 선형성 또는 통과 대역(예컨대, 500-3500MHz 범위), 및 저지 대역 중 하나 이상)에 따라서 음파 마이크로웨이브 필터를 설계하는 방법이 제공된다. 이 방법은 적어도 하나의 공진 소자(예컨대, 커패시터 및 인덕터의 병렬 L-C 공진기 조합) 및 적어도 하나의 다른 리액티브(reactive) 회로 소자(예컨대, 커패시터)를 포함하는 복수의 회로 소자들을 포함하는 초기 필터 회로 구조를 선택하는 단계를 포함한다. 초기 필터 회로 구조는 예컨대 인-라인 비공진 노드 회로 구조일 수 있다.

[0014]

선택적인 방법은 SAW(surface acoustic wave) 공진기, BAW(bulk acoustic wave) 공진기, FBAR(film bulk acoustic resonator) 및 MEMS(microelectromechanical system) 공진기 중 하나로부터 공진 소자(들) 각각의 구조적 타입을 선택하는 단계를 더 포함한다. 다른 선택적인 방법은, 주파수 응답 요건을 정규화된 설계 공간에 매핑하는 단계 - 이 경우 회로 소자 값들은 매핑된 주파수 응답 요건들을 기초로 결정된 정규화된 값들임 -, 및 음파 필터 회로 설계의 정규화된 회로 소자 값들을 실제 설계 공간에 언매핑(unmapping)하는 단계를 더 포함한다.

[0015]

이 방법은 주파수 응답 요건들에 기초하여 무손실 회로 응답 변수들을 선택하는 단계(예컨대, 송신 제로들을 정의하는 분자 다항식들과 반사 제로들을 정의하는 분모 다항식들 간의 비와 스케일 팩터를 곱한 형태로), 및 초기 필터 회로 설계를 생성하기 위하여 선택된 회로 응답 변수들에 기초하여 회로 소자들 각각에 대한 값을 선택하는 단계를 더 포함한다.

[0016]

이 방법은 음파 필터 회로 설계를 생성하기 위하여 초기 필터 회로 설계의 리액티브 회로 소자(들) 및 다른 공진 소자(들)를 적어도 하나의 음파 공진기 모델로 변환하는 단계를 더 포함한다. 일 실시예에서, 음파 공진기 모델은 BVD(Butterworth-Van Dyke) 모델이다. 이 경우, 다른 리액티브 회로 소자(들)은 인-션트 병렬 L-C 공진기 조합과 직렬인 인-션트 어드미턴스 인버터(in-shunt admittance inverter), 및 인-션트 병렬 L-C 공진기 조합, 인-션트 어드미턴스 인버터 및 인-션트 비공진 서셉턴스(susceptance)를 포함할 수 있으며, 인-션트 병렬 L-C 공진기 조합과 인-션트 비공진 서셉턴스 사이의 노드에 연결된 2개의 인-라인 어드미턴스 인버터를 더 포함하며, 인-션트 BVD 모델 및 2개의 인-라인 어드미턴스 인버터는 인-라인 BVD 모델 및 인-라인 BVD 모델과 직렬인 리액턴스로 변환될 수 있다.

[0017]

일 실시예에서, 복수의 공진 소자들, 복수의 리액티브 회로 소자들 및 복수의 공진기 모델들이 제공된다. 이 경우, 이 방법은 초기 필터 회로 설계를 복수의 서브셋 회로 설계들로 분할하는 단계를 더 포함할 수 있으며, 복수의 서브셋 회로 설계들 각각은 공진 소자들 중 하나와 복수의 리액티브 회로 소자들 중 하나 이상을 포함하며, 각각의 서브셋 회로 설계마다, 공진 소자 및 리액티브 회로 소자(들)은 음파 공진기 모델들 중 각각의 음파 공진기 모델로 변환된다.

[0018]

이 방법은, 사전 최적화된 필터 회로 설계를 생성하기 위해 음파 필터 회로 설계에 기생 효과를 추가하는 단계, 최종 필터 회로 설계를 생성하기 위하여 사전 최적화된 필터 회로 설계를 최적화하는 단계(예컨대, 최종 필터 회로 설계를 생성하기 위하여 필터 최적화기에 사전 최적화된 필터 회로 설계를 입력함에 의해), 및 최종 필터 회로 설계를 기초로 음파 마이크로웨이브 필터를 구성하는 단계를 더 포함한다. 선택적인 방법은, 최종 필터 회로 설계를 생성하기 위하여 사전 최적화된 필터 회로 설계의 소자 제거 최적화를 수행하는 단계를 더 포함한다.

[0019]

복수의 공진 소자들이 제공된다면, 이 방법은 복수의 필터 솔루션(solution)들을 생성하기 위하여 사전 최적화된 필터 회로 설계에서 복수의 공진 소자들이 신호 송신 경로에 따라 배치되는 순서를 변경하는 단계, 필터 솔루션들 각각에 대한 성능 파라미터를 계산하는 단계, 성능 파라미터들을 서로 비교하는 단계, 및 계산된 성능 파라미터들의 비교에 기초하여 필터 솔루션들 중 하나를 사전 최적화된 회로 설계로서 선택하는 단계를 선택적으로 포함할 수 있다. 하나의 방법에서, 최종 필터 회로 설계는 복수의 음파 공진기들을 포함하며, 최종 필터 회로 설계에서 복수의 음파 공진기들의 가장 낮은 공진 주파수와 가장 높은 공진 주파수 간의 차이는, 복수의

음파 공진기들에서 단일 공진기의 최대 주파수 분리의 적어도 1배이며, 바람직하게는 적어도 2배, 가장 바람직하게는 적어도 3배이다.

[0020] 본 발명의 다른 추가의 양태 및 특징은 후술되는 바람직한 실시예들의 상세한 설명으로부터 명백해질 것이며, 이 실시예들은 본 발명을 예시하는 것이지 한정하는 것은 아니다.

### 도면의 간단한 설명

[0021] 본 발명의 바람직한 실시예들의 설계 및 활용을 도시한 도면에서는 유사한 구성요소가 공통 도면부호로 언급된다. 본 발명의 전술한 또한 다른 이점 및 목적들이 얻어질 수 있는 방법을 잘 이해할 수 있도록, 간략하게 전술한 본 발명의 보다 상세한 설명이, 첨부된 도면에 예시되어 있는 특정 실시예들을 참고하여 설명될 것이다. 이들 도면이 본 발명의 하나의 전형적인 실시예만을 도시하며 이에 따라 본 발명의 범위를 제한하는 것으로 여겨서는 안 되는 것을 이해해야 하며, 본 발명은 첨부 도면을 사용해 보다 상세히 후술될 것이다.

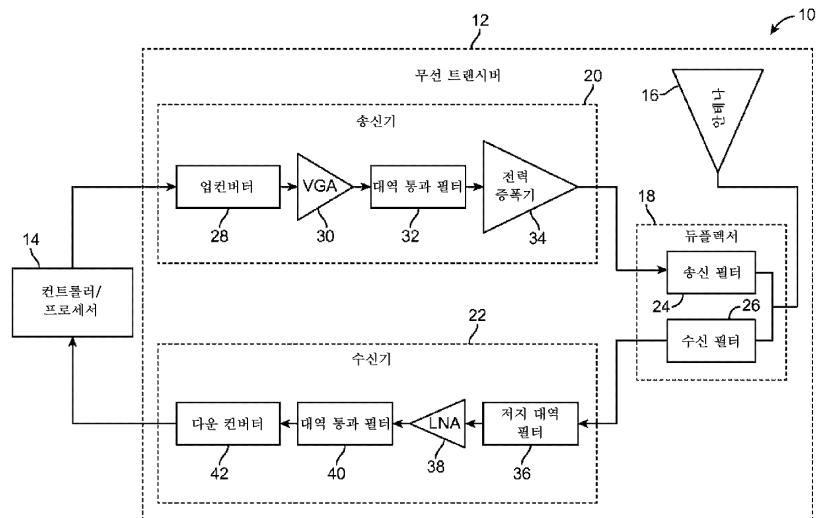

도 1은 무선 통신 시스템의 블록도이다.

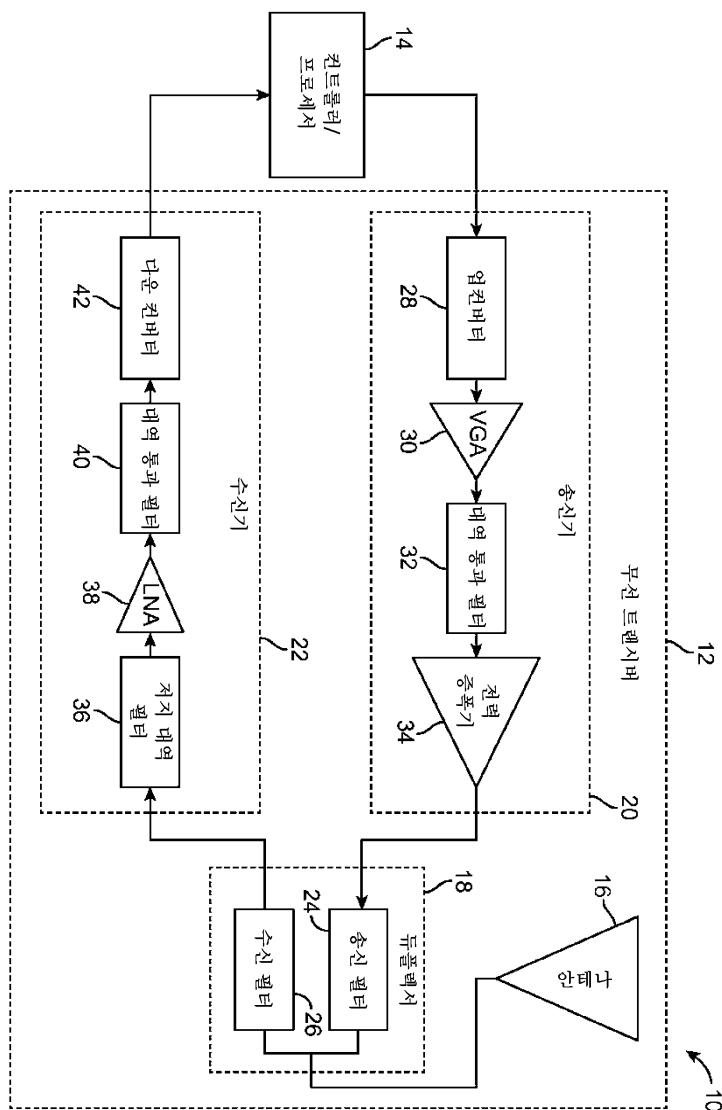

도 2는 본 발명의 일 방법에 따르는 음파 필터를 설계하는 데 사용되는 회로망 합성 기술을 예시하는 흐름도이다.

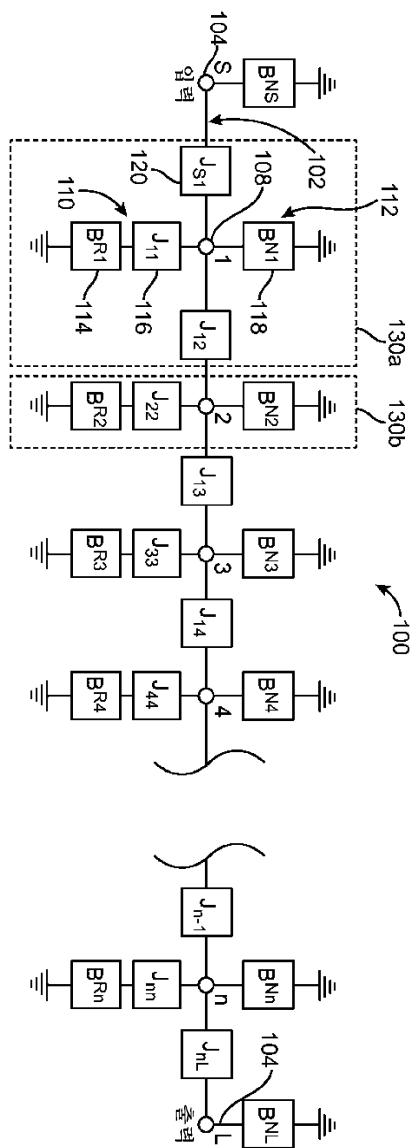

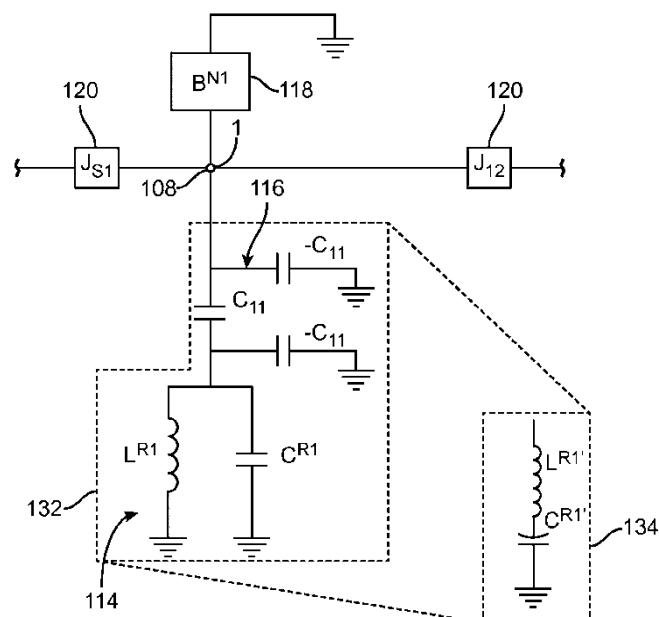

도 3은 도 2의 회로망 합성 기술에 대한 초기 필터 회로 구조로서 사용되는 인-라인 비공진 노드의 개요도이다.

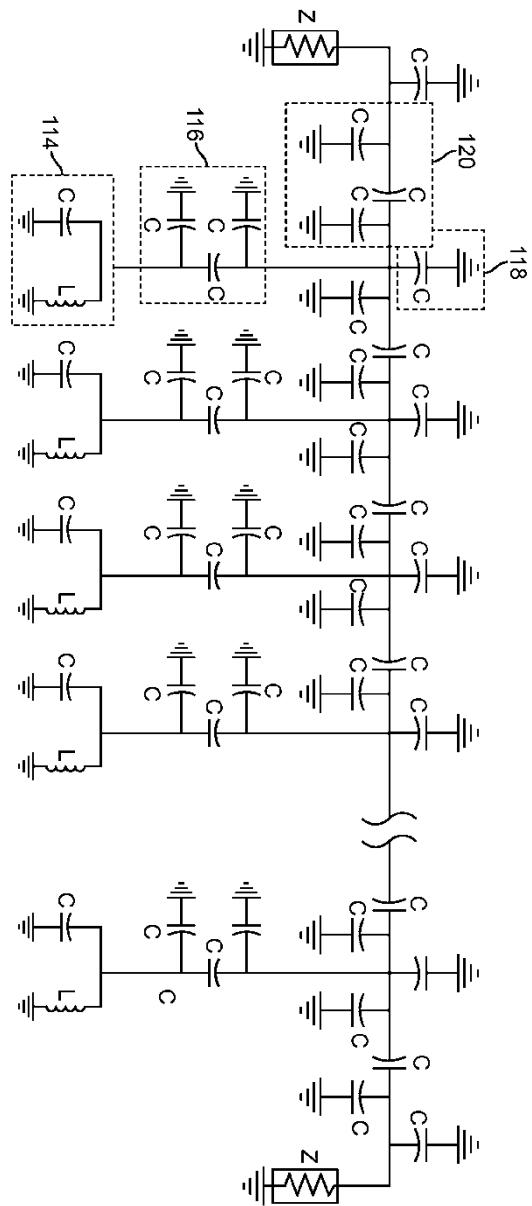

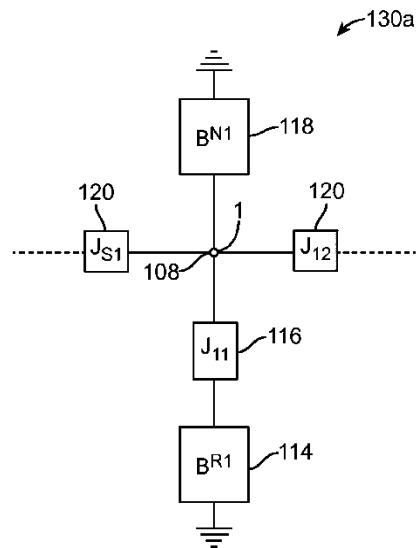

도 4는 도 3의 초기 필터 회로 구조의 병렬 L-C 공진기 조합의 개요도이다.

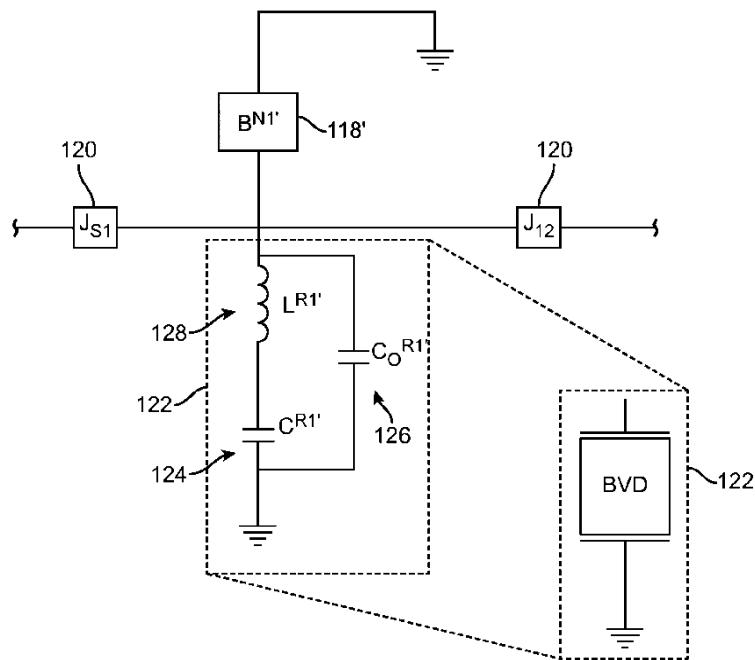

도 5는 BVD(Butterworth-Van Dyke) 음파 공진기 모델에 대한 등가 회로 개요도이다.

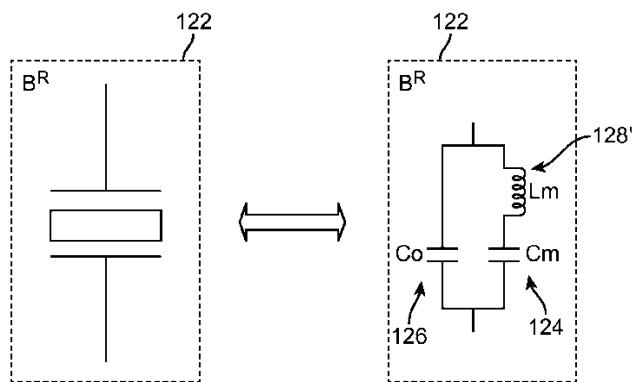

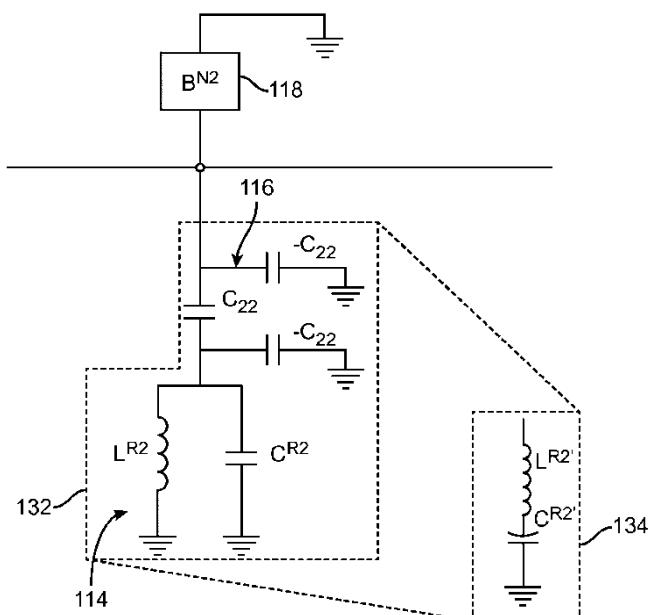

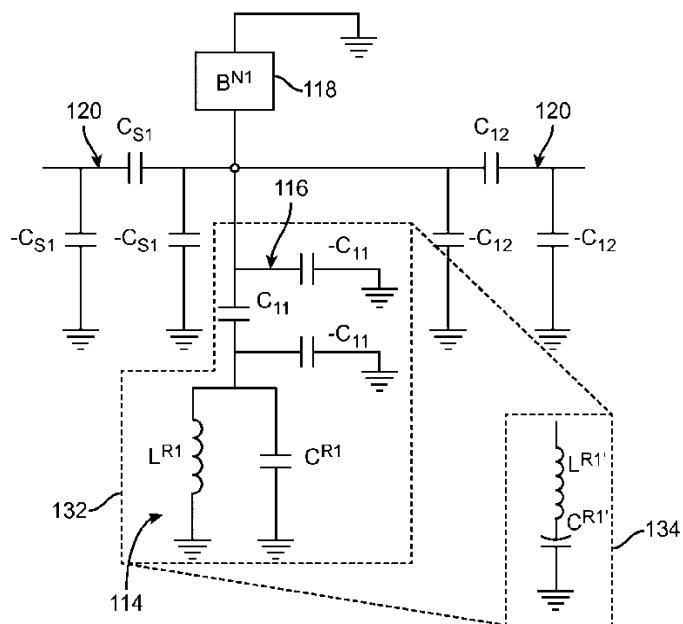

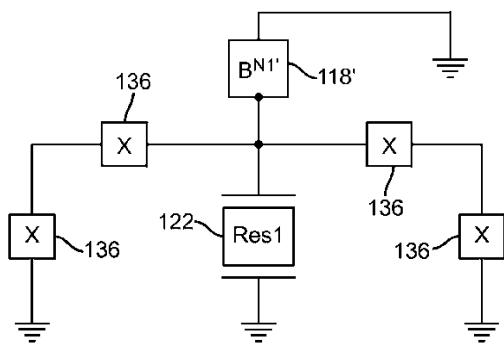

도 6은 도 2의 회로망 합성 기술에 따라서 도 3의 초기 회로 구조(설계)로부터 취해진 서브셋 회로 설계로서, 인-라인 공진기가 도 3의 초기 필터 회로에 통합된다.

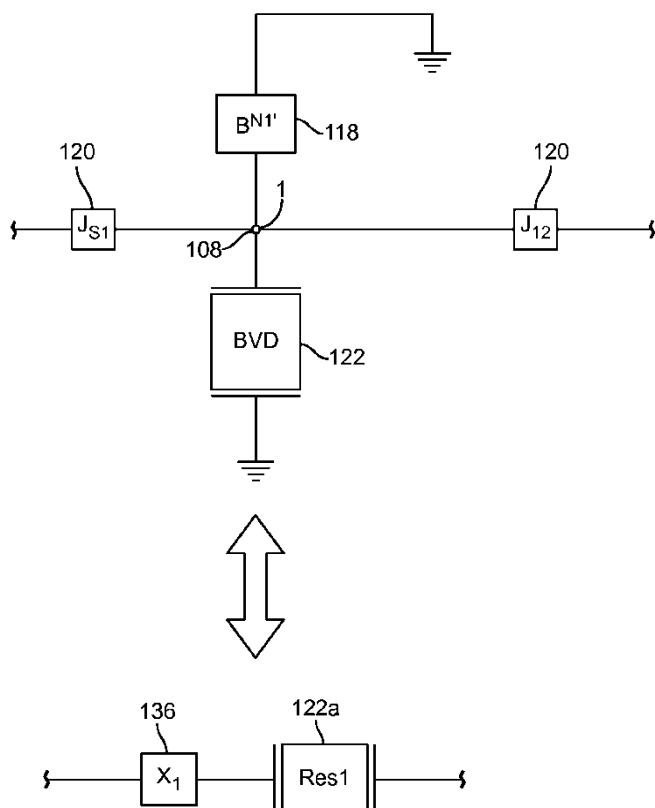

도 7 내지 도 9는 도 2의 회로망 합성 기술에 따라서 도 6의 서브셋 회로 설계에 순차적으로 행해진 회로 변환이다.

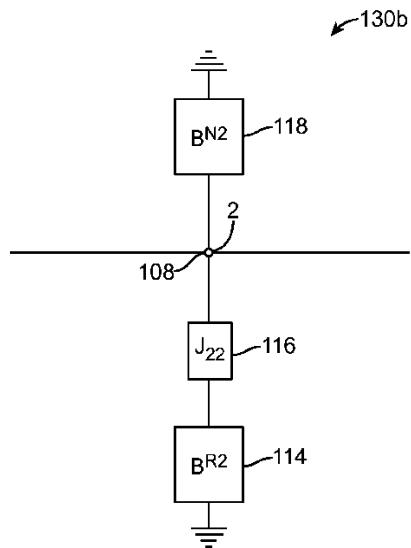

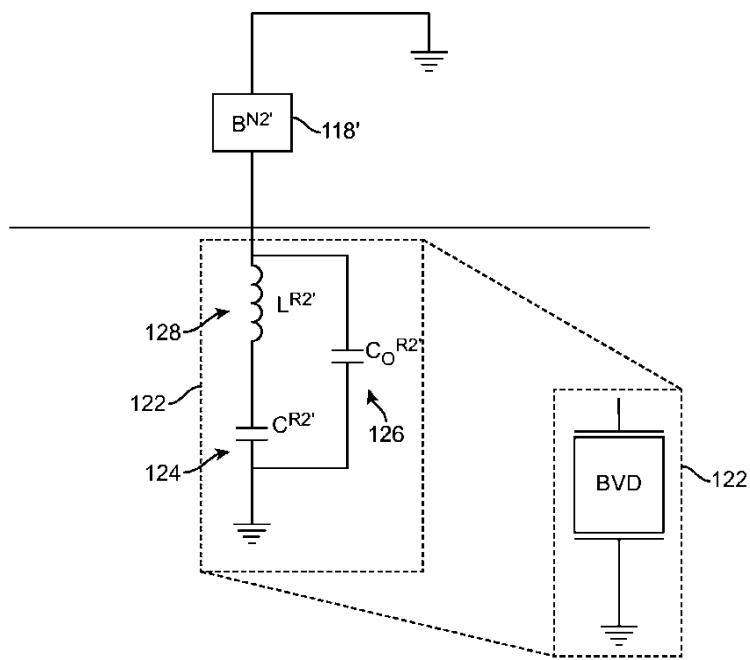

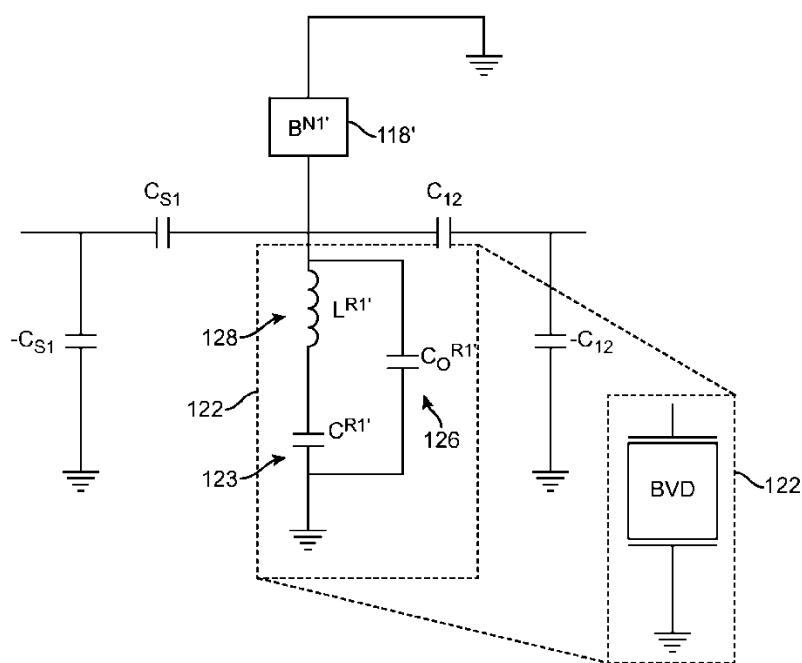

도 10은 도 2의 회로망 합성 기술에 따라서 도 3의 초기 필터 회로 구조로부터 취해진 다른 서브셋 회로 설계이다.

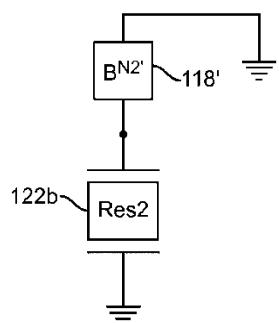

도 11 내지 도 13은 도 2의 회로망 합성 기술에 따라서 도 10의 서브셋 회로 설계에 순차적으로 행해진 회로 변환으로서, 인-센트 음파 공진기가 도 3의 초기 필터 회로 구조에 통합된다.

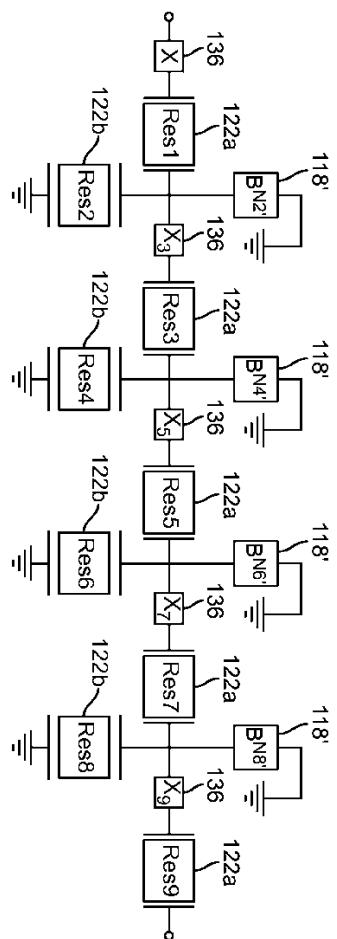

도 14는 도 2의 회로망 합성 기술에 따라서 도 9 및 도 13의 서브셋 음파 회로 설계로부터 발생된 음파 필터 회로 설계의 개요도이다.

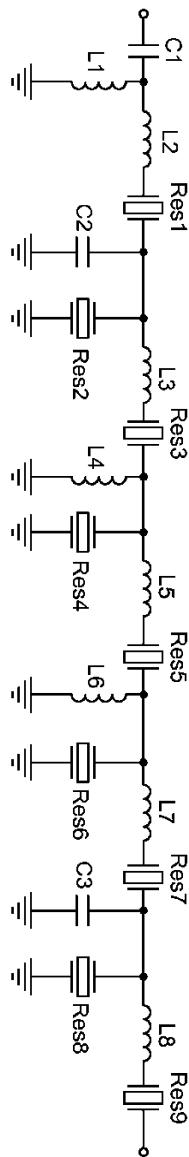

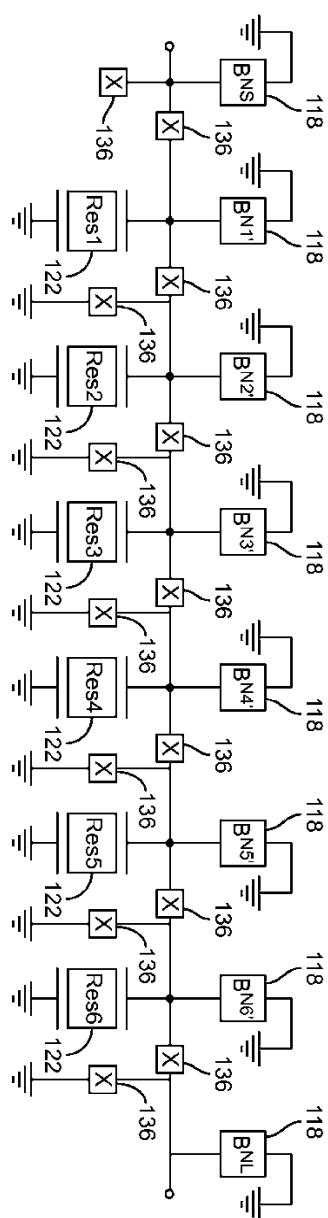

도 15는 도 2의 회로망 합성 기술에 따라서 도 14의 음파 필터 회로 설계로부터 구현되는 사전 최적화된 필터 회로 설계의 개요도이다.

도 16은 도 15의 사전 최적화된 필터 회로 설계의 소자 값들을 나타내는 표이다.

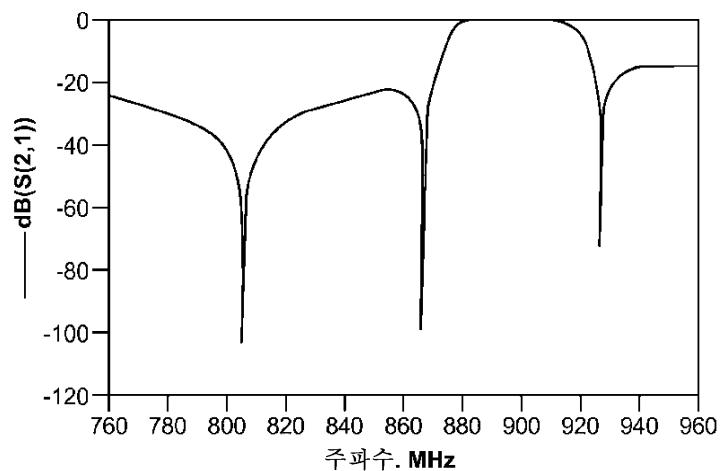

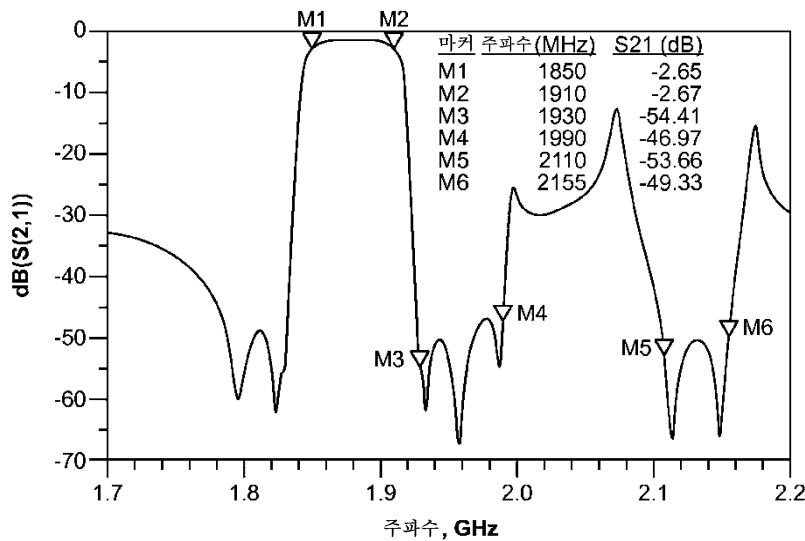

도 17은 도 15의 사전 최적화된 필터 회로 설계의 S21 주파수 응답도이다.

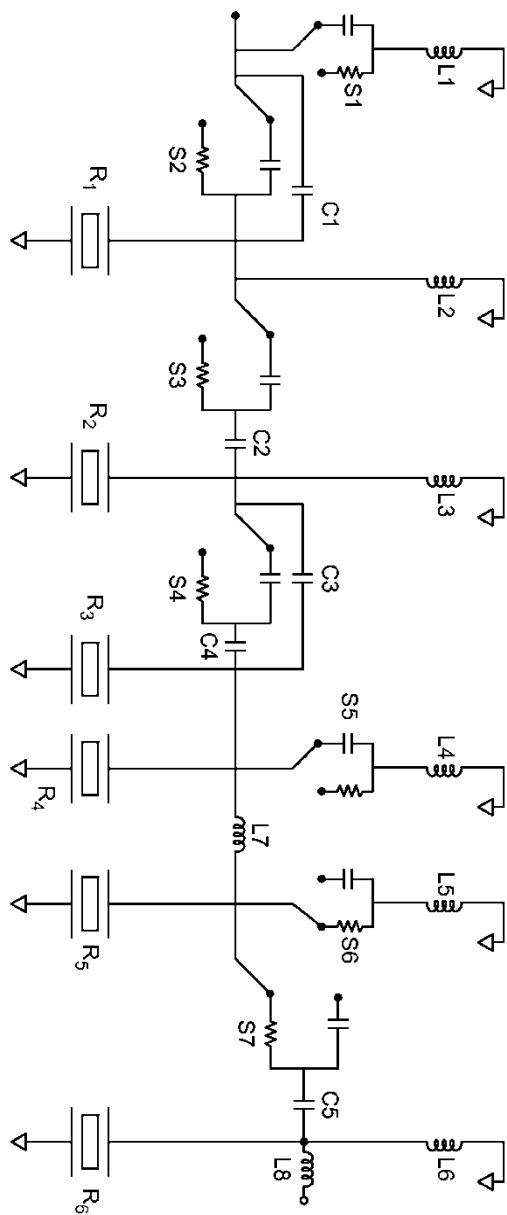

도 18은 도 2의 회로망 합성 기술에 따라서 사전 최적화된 필터 회로 설계를 컴퓨터화된 필터 최적화기에 입력하고, 소자 제거 설계 기술을 수행하여 생성되는 최적화된 필터 회로 설계의 개요도이다.

도 19는 도 18의 최적화된 필터 회로 설계의 소자값들을 나타내는 표이다.

도 20은 도 18의 최적화된 필터 회로 설계의 S21 주파수 응답도이다.

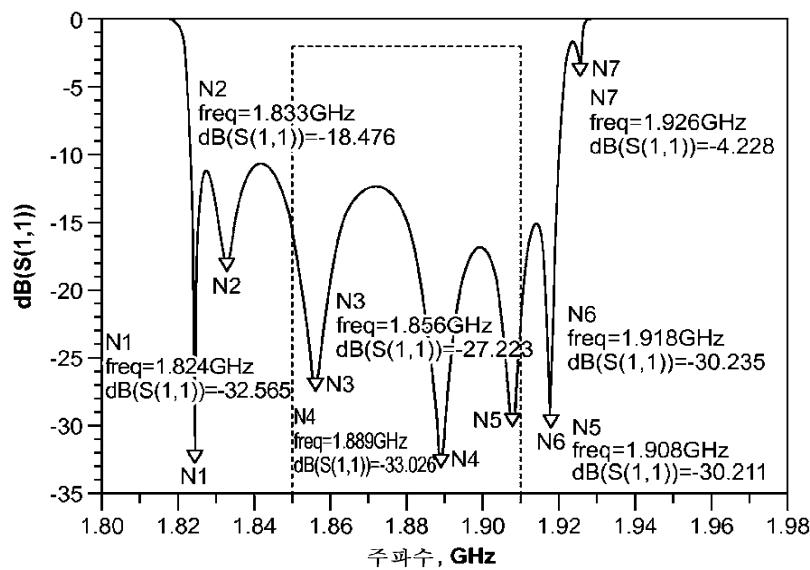

도 21a 및 도 21b는 도 18의 최적화된 필터 회로 설계의 S11 주파수 응답도이다.

도 22 내지 도 24는 도 2의 회로망 합성 기술에 따라서 도 10의 서브셋 회로 설계에 순차적으로 행해진 회로 변환으로서, 인-센트 음파 공진기들이 도 3의 초기 필터 회로 설계의 공진 분기들에 통합된다.

도 25는 도 2의 회로망 합성 기술에 따라서 도 24의 서브셋 음파 회로 설계로부터 생성된 음파 필터 회로 설계의 개요도이다.

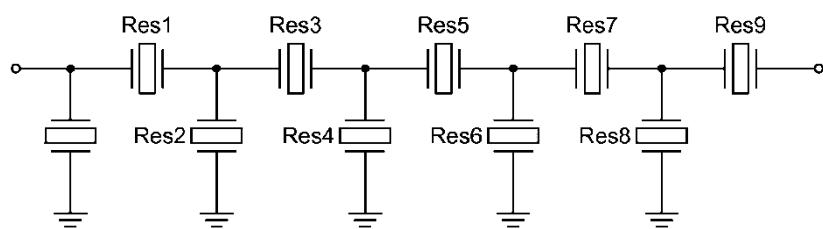

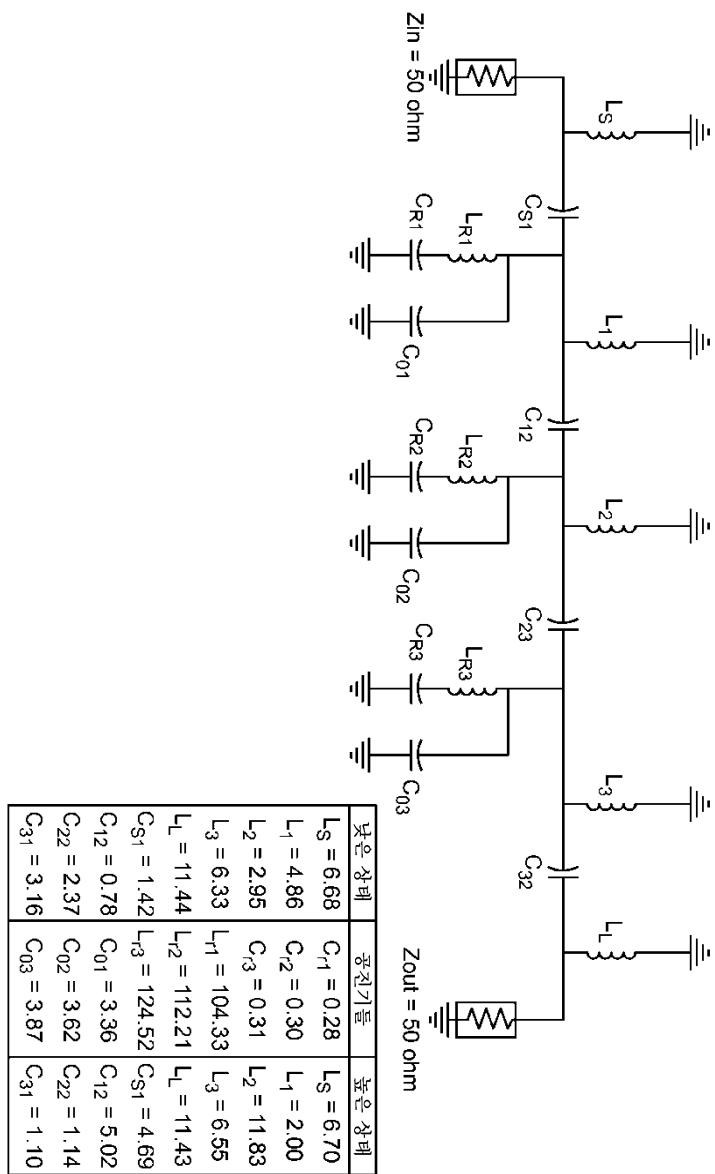

도 26은 도 2의 회로망 합성 기술에 따라서 도 25의 음파 필터 회로 구조로부터 구현된 다른 사전 최적화된 필

터 회로 설계의 개요도이다.

도 27은 도 26의 사전 최적화된 필터 회로 설계의 소자값들을 나타내는 표이다.

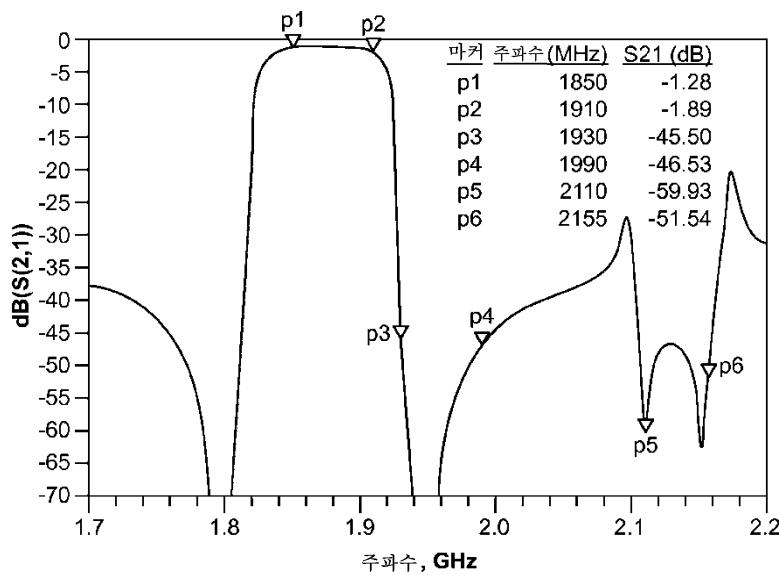

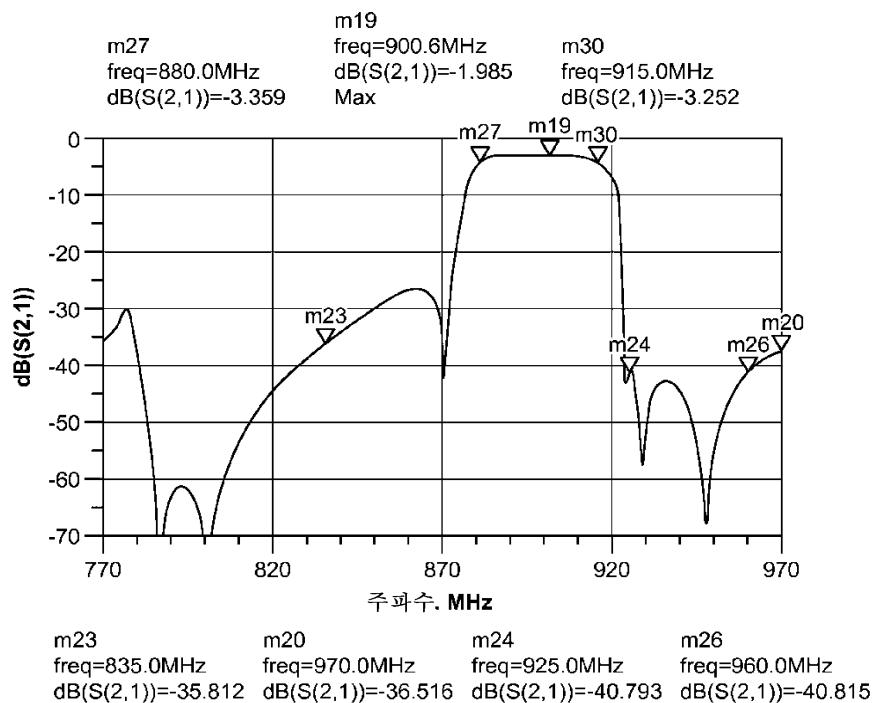

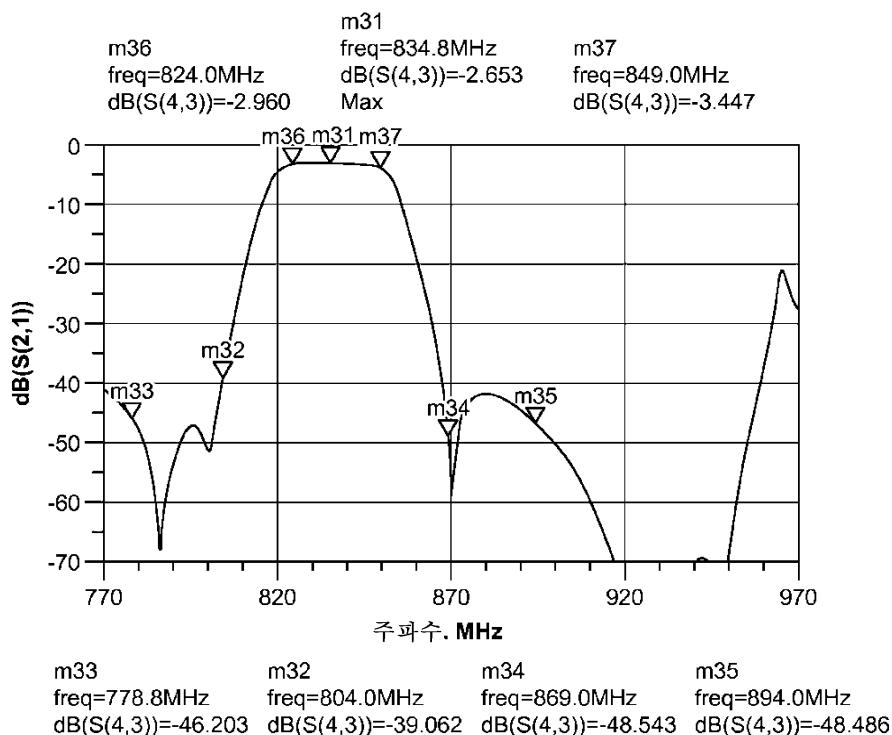

도 28은 최적화 후 도 25의 필터 회로 설계의 S21 대역 5 주파수 응답도이다.

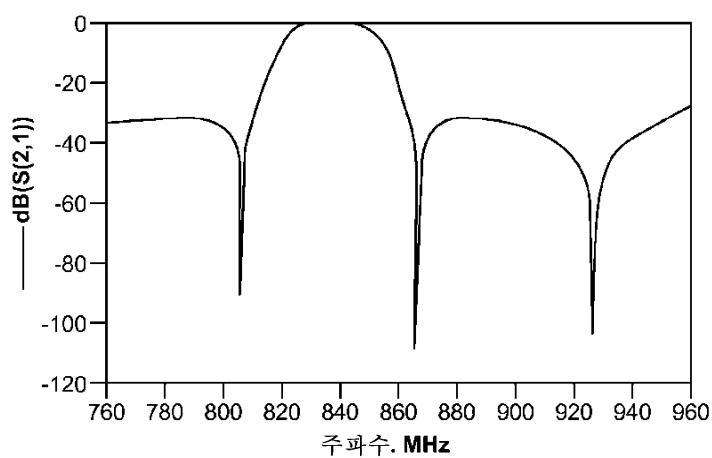

도 29는 최적화 후 도 25의 필터 회로 설계의 S21 대역 8 주파수 응답도이다.

도 30은 도 2의 회로망 합성 기술에 따라서 생성된 또 다른 사전 최적화된 필터 회로 설계의 개요도이다.

도 31은 최적화 후 도 30의 필터 회로 설계의 S21 대역 5 주파수 응답도이다.

도 32는 최적화 후 도 30의 필터 회로 설계의 S21 대역 8 주파수 응답도이다.

### 발명을 실시하기 위한 구체적인 내용

[0022]

본 발명은 AW(acoustic wave) 마이크로웨이브 필터(예컨대, SAW(surface acoustic wave), BAW(bulk acoustic wave), FBAR(film bulk acoustic resonator) 및 MEMS(microelectromechanical system) 필터)를 설계하기 위한 회로망 합성 기술을 설명한다. 이런 회로망 합성 기술은 이전 AW 마이크로웨이브 필터 설계 방법에 비해 (즉, 500MHz 보다 큰 주파수에서) 양호한 수행 및/또는 저 비용의 AW 마이크로웨이브 필터를 가져온다. 이런 AW 마이크로웨이브 필터는 고정 주파수 및/또는 조정가능한 필터들(주파수 및/또는 대역폭, 입력 임피던스 및/또는 출력 임피던스에서 조정가능한) 중 어느 하나일 수 있으며, 단일 대역 또는 다중 대역 대역통과 필터링 및/또는 대역저지에 사용될 수 있다. 이런 AW 마이크로웨이브 필터들은, 셀폰, 스마트폰, 랩톱 컴퓨터, 태블릿 컴퓨터 등을 포함하는 이동 통신 디바이스의 무선 주파수(RF) 전단, 또는 M2M 디바이스, 무선 기지국, 위성 통신 시스템 등을 포함하는 고정 통신 디바이스의 RF 전단에서 발견되는 것들과 같은, 요구가 많은 전기적 및/또는 환경적 성능 요건들 및/또는 엄격한 비용/크기 제약들을 가지고 있는 어플리케이션에서 이점이 있다.

[0023]

이하 설명되는 AW 마이크로웨이브 필터 예(도 28-29)는 가깝게 이격된 저지 대역을 갖는 통과 대역이 요구되는 통신 시스템 듀플렉서에 특히 유용한, 단일 통과 대역 및 단일 저지 대역을 갖는 주파수 응답을 나타낸다. 예컨대, 도 1을 참고하면, 이동 통신 디바이스에 사용하기 위한 통신 시스템(10)은 무선 신호를 송신 및 수신할 수 있는 트랜시버(12), 및 트랜시버(12)의 기능을 제어할 수 있는 컨트롤러/프로세서(14)를 포함한다. 트랜시버(12)는 일반적으로 광대역 안테나(16), 송신 필터(24) 및 수신 필터(26)를 갖는 듀플렉서(18), 듀플렉서(18)의 송신 필터(24)를 통해 안테나(16)에 연결된 송신기(20), 및 듀플렉서(18)의 수신 필터(26)를 통해 안테나(16)에 연결된 수신기(22)를 포함한다.

[0024]

송신기(20)는 컨트롤러/프로세서(14)에 의해 제공되는 기저대역 신호를 RF(radio frequency) 신호로 변환하도록 구성된 업컨버터(28), RF 신호를 증폭하도록 구성된 가변 이득 증폭기(VGA)(30), 컨트롤러/프로세서(14)에 의해 선택된 동작 주파수에서 RF 신호를 출력하도록 구성된 대역 통과 필터(32), 및 듀플렉서(18)의 송신 필터(24)를 통해 안테나(16)에 제공되는 필터링된 RF 신호를 증폭하도록 구성된 전력 증폭기(34)를 포함한다.

[0025]

수신기(22)는 수신 필터(26)를 통해 안테나(16)로부터 입력된 RF 신호로부터 송신 신호 간섭을 소거하도록 구성된 노치 또는 저지 대역 필터(36), 비교적 낮은 잡음을 갖는 저지 대역 필터(36)로부터의 RF 신호를 증폭하도록 구성된 LNA(low noise amplifier)(38), 컨트롤러/프로세서(14)에 의해 선택된 주파수에서 증폭된 RF 신호를 출력하도록 구성된 대역 통과 필터(40), 및 RF 신호를 컨트롤러/프로세서(14)에 제공되는 기저대역 신호로 다운컨버팅하도록 구성된 다운컨버터(42)를 포함한다. 대안적으로, 저지 대역 필터(36)에 의해 수행되는 송신 신호 간섭을 소거하는 기능은 듀플렉서(18)에 의해 대신 수행될 수 있다. 또는 송신기(20)의 전력 증폭기(34)는 송신 신호 간섭을 감소시키도록 설계될 수 있다.

[0026]

도 1에 도시된 블록도는 본질적으로 기능도이며, 여러 기능들이 하나의 전자 컴포넌트에 의해 수행될 수 있거나 하나의 기능이 여러 전자 컴포넌트들에 의해 수행될 수 있음을 이해해야 한다. 예컨대, 업 컨버터(28), VGA(30), 대역통과 필터(40), 다운컨버터(42), 및 컨트롤러/프로세서(14)에 의해 수행되는 기능들은 종종 단일 트랜시버 칩에 의해 수행된다. 대역통과 필터(32)의 기능은 전력 증폭기(34) 및 듀플렉서(18)의 송신 필터(24)에 의해 수행될 수 있다.

[0027]

이하 설명되는 예시적인 회로망 합성 기술은 통신 시스템(10)의 전단용의 음파 마이크로웨이브 필터, 특히 듀플렉서(18)의 송신 필터(24)를 설계하는데 사용되지만, 동일 기술이 듀플렉서(18)의 수신 필터(26) 및 다른 RF 필터용의 음파 마이크로웨이브 필터를 설계하는데 사용될 수도 있다.

[0028]

도 2를 참고하여, AW 마이크로웨이브 필터를 설계하기 위한 하나의 예시적인 회로망 합성 기술(50)을 설명한다.

우선, 주파수 응답 요건들(통과 대역, 복귀 손실, 삽입 손실, 소거, 선형성, 잡음 지수, 입력 및 출력 임피던스 등을 포함) 뿐만 아니라, 크기 및 비용 요건, 및 예컨대 동작 온도 범위, 진동, 실패율 등과 같은 환경 요건을 포함하는 필터 요건들은, 필터의 어플리케이션에 의해 구축된다(단계 52). 예시된 실시예에서, 설계는 다음의 요건들을 목표로 한다: 2dB의 최대 삽입 손실 요건을 갖는 1850MHz-1910MHz의 하나의 통과대역과, 44dB의 최소 저지(rejection)를 갖는 1930MHz-1990MHz의 제1 저지대역, 20dB의 최소 저지를 갖는 2010MHz-2025MHz의 제2 저지대역 및 45dB의 최소 저지를 갖는 2110MHz-2155MHz의 제3 저지대역을 포함하는 3개의 저지대역들.

[0029] 다음에, AW 필터에 사용될 회로 소자들의 구조적 타입이 선택된다. 예컨대, 필터를 제조하기 위한 패키징 및 어셈블리 기술을 포함하여, 공진기의 구조적 타입(SAW, BAW, FBAR, MEMS 등), 및 인더터, 커패시터 및 스위치의 타입과 함께 이들 회로 소자를 제조하는데 사용될 재료가 선택된다(단계 54). 설명되는 특정 예에서, 회로 소자 타입의 선택은 42도 XY 컷의  $\text{LiTaO}_3$ 로 이루어지는 기판 상에 구성된 SAW 공진기 및 커패시터이다.

[0030] 그 후, 초기 회로 구조, 예컨대 인-라인 비공진 노드, 인-라인, 또는 교차 결합들을 가진 인-라인(in-line with cross couplings), 또는 교차 결합들을 갖는 인-라인 비공진 노드 등이 주파수 응답 요건들로부터 획득한 통과 대역(들) 및/또는 저지대역(들)에 기초하여 선택된다(단계 56). 예시된 실시예에서, 선택된 초기 회로 구조는, 미국 특허 제7,719,382호, 제7,639,101호, 제7,863,999호, 제7,924,114호, 제8,063,714호 및 미국 가출원 제61/802,114호(발명의 명칭 "Element Removal Design in Microwave Filters")에 기술된 것들과 같은, 인-라인 비공진 노드 구조이다. 본 명세서에서, 용어 "구조"란 소자들의 값을 고려하지 않는 소자 타입 및 이들의 상호접속을 말한다.

[0031] 도 3을 참고하면, 인-라인 비공진 노드 초기 필터 회로 구조(100)의 이런 일 실시예는 입력(104)(노드 S로 표현됨) 및 출력(106)(노드 L로 표현됨)을 갖는 신호 송신 경로(102), 신호 송신 경로(102)를 따라 배치된 복수의 노드들(108)(노드 S, 1, 2...n으로 표현됨), 노드들(108)을 접지에 각각 연결하는 복수의 공진 분기들(110), 및 공진 분기들(110)에 각각 병렬로 접지에 노드들(108)을 각각 연결하는 복수의 비공진 분기들(112)을 일반적으로 포함한다.

[0032] 초기 필터 회로 구조(100)는 공진 분기들(110)에 각각 위치하는 복수의 인-션트 공진 소자들(114)(서셉턴스  $B^{R1}$ ,  $B^{R2} \dots B^{RN}$ 으로 표현됨) 및 공진 소자(114)와 직렬인 복수의 인-션트 비공진 소자들(116)(어드미턴스 인버터  $J_{11}$ ,  $J_{22} \dots J_{nn}$ 으로 표현됨)을 더 포함한다. 초기 필터 회로 구조(100)는 복수의 인-션트 비공진 소자들(118)을 더 포함하며, 이들 중 둘은 노드 S 및 노드 L을 접지에 연결하며(서셉턴스  $B^{NS}$  및  $B^{NL}$ 로 각각 표현됨), 이들 중 넷은 비공진 분기들(110)에 각각 위치한다( $B^{N1}$ ,  $B^{N2} \dots B^{Nn}$ 으로 표현됨). 초기 필터 회로 구조(100)는 노드들 S, 1, 2...n, L을 함께 각각 연결하는 복수의 인-라인 비공진 소자들(120)(어드미턴스 인버터  $J_{S1}$ ,  $J_{12}$ ,  $J_{23} \dots J_{n-1,n}$ ,  $J_{nL}$ 로 각각 표현됨)을 더 포함한다.

[0033] 초기 필터 회로 구조(100)는 공진 소자들(114)의 주파수들 및/또는 비공진 소자들(120)의 값을 조정하기 위한 복수의 튜닝 소자들(도시 안 됨), 및 비공진 소자들(116-120) 중 선택된 소자들을 변동시킴으로써 초기 필터 회로 구조(100)를 원하는 주파수 범위 내의 선택된 협대역으로 조정하도록 구성된 전기 컨트롤러(도시 안 됨)을 더 포함할 수 있다. 따라서, 초기 필터 회로 구조(100)는, 서셉턴스  $B^R$  값을 구현하는데 사용되는 높은 Q 팩터 공진 소자들(114)이 도 4에 도시된 바와 같이 병렬 L-C 공진기 조합, 즉 탱크 회로로 잘 표현된다면, 재구성 가능한 대역통과 필터들의 회로망 합성에 유용하다.

[0034] 높은 Q 팩터 공진 소자들(114)은 도 5에 예시된 BVD(Butterworth-Van Dyke) 모델(122)을 사용하여 잘 설명된다. BVD 모델(122)은 IDT(interdigital transducer)들을 압전 기판, 예컨대 결정 석영, 니오브산리튬( $\text{LiNbO}_3$ ), 리튬탄탈레이트( $\text{LiTaO}_3$ ) 결정 또는 석영 또는 질화 알루미늄과 같은 물질로 제조되는 BAW(FBAR 포함) 공진기 또는 MEMS 공진기상에 배치함으로써 제조될 수 있는 SAW 공진기를 표현할 수 있다. BVD 모델(122)은 운동 커패시턴스(motional capacitance)  $C_m$ (124), 정적 커패시턴스(static capacitance)  $C_o$ (126) 및 운동 인더턴스  $L_m$ (128)를 포함한다. 운동 커패시턴스  $C_m$ (124) 및 운동 인더턴스  $L_m$ (128)은 전기 음파 행위의 상호작용으로부터 유발될 수 있으며, 그 결과 BVD 모델(122)의 운동 암(arm)으로서 언급될 수 있다. 정적 커패시턴스  $C_o$ (126)는 단독으로 구조(도체, 유전체 및 캡)의 전기 행위로부터 유발될 수 있고, 그 결과 BVD 모델(122)의 정적(비운동) 커패시턴스로서 언급될 수 있다. 파라미터들은 다음의 수학식들과 관련된다:

## 수학식 2

$$\omega_R = \frac{1}{\sqrt{L_m C_m}}$$

[0035]

## 수학식 3

$$\frac{\omega_A}{\omega_R} = \sqrt{1 + \frac{1}{\gamma}}$$

[0036]

[0037] 여기서  $\omega_R$  및  $\omega_A$ 는 어느 주어진 음파 공진기에 대한 각각의 공진 및 반공진 주파수들일 수 있으며, 감마  $\gamma$ 는 다음의 수학식 4에 의해 더 정의될 수 있는 물질 속성에 따라 달라질 수 있다.

## 수학식 4

$$\frac{C_0}{C_m} = \gamma$$

[0038]

[0039] 전형적인  $\gamma$  값은 42도 X Y 컷 LiTaO<sub>3</sub>에 대해 약 12 내지 약 18의 범위에 있을 수 있다. 음파 공진기의 주파수 분리는 그 공진 주파수와 반공진 주파수 간의 차이를 의미한다. 음파 공진기의 분리 퍼센티지는 그 공진 주파수와 반공진 주파수 간의 주파수 분리 퍼센티지이며, 다음과 같이 계산될 수 있다.

## 수학식 8

$$\text{분리 퍼센티지} = \sqrt{1 + \left(\frac{1}{\gamma}\right)} - 1$$

[0040]

[0041] 여기서,  $\gamma$ 는 압전 물질의 물질 속성에 의해 결정되며 디바이스의 기하 형상에 의해 결정되는, 공진기의 정적 커페시턴스와 운동 커페시턴스의 비(수학식 4)이다.

[0042] 음파 공진기의 공진 주파수  $\omega_R$ 은 임피던스의 크기가 국부 최소에 도달하고 임피던스의 위상이 제로 교차하는 주파수를 의미한다. 음파 공진기의 반공진 주파수  $\omega_A$ 는 임피던스의 크기가 국부 최대에 도달하고 임피던스의 위상이 제로 교차하는 주파수를 의미한다.

[0043] 수학식 1로부터 음파 공진기들 각각의 공진 주파수는 BVD 모델(122)의 운동 암에 따라 달라질 것이며, 반면에 필터 특성(예컨대, 대역폭)은 수학식 2에서의  $\gamma$ 에 의해 크게 영향받을 것임을 이해할 수 있다. 음파 공진기 (122)에 대한 품질 팩터(Q)는 필터 내의 소자의 손실과 관련하여, 음파 필터 설계에서 중요한 성능 지수일 수 있다. 희로 소자의 Q는 사이클당 저장된 에너지와 사이클당 소실되는 에너지의 비를 나타낸다. Q 팩터는 각각의 음파 공진기에서의 실제 손실을 모델링하며, 일반적으로 둘 이상의 Q 팩터들이 음파 공진기의 손실을 표현하는데 요구될 수 있다. Q 팩터는 필터 예들에 대해 다음과 같이 정의될 수 있다. 운동 커페시턴스  $C_m$ (124)는  $Q_{cm} = 10^8$ 로서 정의되는 연관된 Q를 가질 수 있으며, 정적 커페시턴스  $C_0$ (126)는  $Q_{co} = 200$ 으로서 정의되는 연관된 Q를 가질 수 있고, 운동 인더턴스  $L_m$ (128)는  $QL_m = 1000$ 로서 정의되는 연관된 Q를 가질 수 있다(이하 간략화를 위해, 운동 공진에서의 손실은 운동 인더턴스로 모아지고(lumped), 운동 커페시턴스는 본질적으로 무손실로 고려된다). 희로 설계자는 전형적으로 SAW 공진기를, 공진 주파수  $\omega_R$ , 정적 커페시턴스  $C_0$ , 감마  $\gamma$  및 품질 팩터  $QL_m$ 으로 특정화할 수 있다. 상용 어플리케이션에서,  $QL_m$ 은 SAW 공진기에서 약 1000이며, BAW 공진기에서 약

3000일 수 있다.

[0044] 도 2를 다시 참조하면, 주파수 응답 요건은 그 후 정규화된 설계 공간에 매핑된다(단계 58). 매핑은 적당한 알고리즘, 예컨대 제곱근/이차 매핑 기법(참고 George L. Matthaei, *Microwave Filters, Impedance-Matching Networks, and Coupling Structures*, McGraw-Hill Book Company, pp. 95-97, 438-440 (1964)), 또는 음파 공진기에 더 적당한 대수/지수 매핑 기법을 이용하여 수행될 수 있다.

[0045] 한가지 흥미로운 대수 매핑 기법은 다음의 수학식을 사용한다.

### 수학식 5

$$\Omega = \ln\left(\frac{\omega^2}{\omega_{p,r}^2}\right) / \ln\left(1 + \frac{1}{\gamma}\right)$$

[0046]

### 수학식 6

$$|\Omega_k - \Omega_l| = 1$$

[0048] 여기서  $\omega_p/2\pi$ 는 통과 대역 또는 저지 대역의 기하학적 중심 주파수이며,  $\omega/2\pi$ 는 실제 주파수이고,  $\Omega$ 는 매핑된 주파수이고,  $\gamma$ 는 공진기의 정적 커패시턴스와 운동 커패시턴스의 비이고,  $\Omega_R$ 은 공진기의 매핑된 공진 주파수이며,  $\Omega_A$ 는 공진기의 매핑된 반공진 주파수이다.

[0049] 다음에, 수학식 1에 제공된 바와 같이 송신 제로들을 정의하는 분자 다항식들과 반사 제로들을 정의하는 분모 다항식 간의 비와 스케일 팩터를 곱한 형태로 무손실 회로 응답 변수들이 제공된다(단계 60). 일반적으로 송신 제로들의 전체 수는 반사 제로들의 전체 수보다 크거나 같고 또는 클 수 있으며, 종종 하나 이상의 반사 제로들은 필터의 임의의 통과대역 외부에 있을 것이다.

[0050] 다음에, 초기 무손실 회로 설계를 생성하기 위하여 이들 다항식으로부터 결합 행렬 또는 파라미터 추출 방법 또는 등가 회로 합성 기술을 이용하여 초기 필터 회로 구조(100)에 대해 매핑되고 정규화된 회로 소자 값들이 계산된다(단계 62). 본 명세서에서, "회로 설계"는 회로 구조를 구성하는 소자들의 값을 고려한 회로 구조를 말할 것이다.

[0051] 다음에, 음파 필터 회로 설계를 생성하기 위하여 회로 소자의 수를 감소시키거나, 또는 회로 소자의 타입, 회로의 크기 또는 개별 회로 소자들의 구현가능성을 변경시키도록 등가 회로 변환이 구현될 수 있다(단계 64). 이들 변환은 초기 무손실 회로 설계의 응답을 실질적으로 변경시키지 않고, J-인버터를 등가 용량성 또는 유도성 PI 또는 T-회로망과 동일시하는 것과 같은 등가 회로 변환을 활용할 수 있다. 예컨대, 션트-공진기/2개의 J-인버터 조합이 단일 직렬 공진기로 변환될 수 있고, 직렬 공진기/2개의 J-인버터 조합이 단일 션트 공진기로 변환될 수 있으며, 다수의 병렬 커패시턴스들이 결합되어 단일 커패시터가 될 수 있고, 또는 그렇지 않다면 커패시터를 제거하기 위해 네가티브(negative) 커패시터들이 포지티브 병렬 커패시터들과 결합함에 의해 제거되어 단일 포지티브(positive) 커패시터를 가져올 수 있고, 다수의 직렬 인덕터들이 결합되어 단일 인덕터가 될 수 있고, 또는 그렇지 않다면 인덕터를 제거하기 위해 네가티브 인덕터들이 포지티브 직렬 인덕터들과 결합함에 의해 제거되어 단일 포지티브 인덕터를 가져올 수 있고, 또는 목표 회로 응답을 가질 수 있으나 초기 무손실 회로 설계보다 더 작은, 덜 비용이 드는 및/또는 더 구현가능한 무손실 회로를 획득하기 위해 다른 등가 회로 변환이 수행될 수 있다.

[0052] 중요한 점으로, 음파 공진 소자들  $B^R$ 이 도 5에 도시된 BVD 모델(122)에 의해 잘 설명된다 할지라도, BVD 모델(122)이 그 추가 정적 커패시턴스  $C_0$ 에 기인하여 도 4에 도시된 L-C 등가 초기 필터 회로 설계(100)에 직접 통합될 수 없기 때문에 문제점이 일어난다. 따라서, 회로 변환의 한 특정 타입은 초기 필터 회로 설계(100)를 음파 공진기 모델, 이 경우 BVD 모델(122)이 통합될 수 있는 적당한 구조로 변환하는 것을 수반한다. 이런 회로 변환은 초기 필터 회로 설계(100)를 공진 소자들(114)의 수와 동일한 다수의 서브셋으로 분할함에 의해 가장 잘 수행될 수 있다. 각각의 서브셋은 공진 분기(110) 및 비공진 분기(112)가 연결되는 각 노드에 연결되는 회로

소자들을 포함한다. 각 서브셋의 본질은 션트 음파 공진기 또는 인-라인 음파 공진기 중 어느 것이 요구되는지에 따라 달라질 것이다.

[0053] 예컨대, 인-라인 음파 공진기를 초기 필터 회로 설계(100)로 통합하는 하나의 변환 기술에서, 특정 서브셋 회로 설계는 각각의 노드(108)로부터 접지에 연결된 공진 소자(114)(서셉턴스  $B^R$ ), 공진 소자(114)와 직렬로 연결된 비공진 소자(116)(어드미턴스 인버터  $J$ ), 공진 소자(114)(서셉턴스  $B^R$ )에 병렬로 각각의 노드(108)로부터 접지에 연결된 비공진 소자(118)(서셉턴스  $B^N$ ), 및 각각의 노드(108)에 일렬(in-line)로 연결된 2개의 비공진 소자(120)(어드미턴스 인버터  $J$ )를 포함한다. 예컨대, 도 6에 도시된 바와 같이, 서브셋(130a)은 노드 1을 포함하며, 그 결과 공진 소자  $B^{R1}$ 은 각각의 노드(108)에서 접지로 연결되고, 어드미턴스 인버터 소자  $J_{11}$ 는 공진 소자  $B^{R1}$ 과 직렬로 연결되며, 비공진 소자  $B^{N1}$ 은 공진 소자  $B^{R1}$ 과 병렬로 각각의 노드(108)로부터 접지에 연결되고, 2개의 어드미턴스 인버터  $J_{S1}$  및  $J_{12}$ 는 각각의 노드(108)와 일렬로 연결된다.

[0054] 도 7에 도시된 바와 같이, 어드미턴스 인버터  $J_{11}$ 은 용량성 PI-회로망(커패시터들  $-C_{11}$ ,  $C_{11}$  및  $-C_{11}$ )으로 대체되고, 공진 소자  $B_1^R$ 은 인덕턴스(인덕터  $L^{R1}$ ) 및 커패시턴스(커패시터  $C^{R1}$ )의 병렬 L-C 공진기 조합으로 대체된다. 커패시터들  $-C_{11}$ ,  $C_{11}$  및  $-C_{11}$ , 및 인덕터  $L^{R1}$  및 커패시터  $C^{R1}$ 의 병렬 L-C 공진기 조합으로 이루어지는 PI-회로망으로 표현되는 회로 서브-구조(132)는 인덕턴스(인덕터  $L^{R1'}$ ) 및 커패시턴스(커패시터  $C^{R1'}$ )의 직렬 L-C 공진기 조합(134)으로 변환될 수 있다. 중요한 점으로, 이런 직렬 L-C 조합(134)은 BVD 모델(122)의 직렬 공진 레그(leg)에 의해 구현될 수 있어, 회로 서브-구조(132)에 더 양호하게 통합될 수 있다.

[0055] BVD 모델(122)을 회로 서브-구조(132)에 통합하기 위하여, BVD 모델(122)의 정적 커패시턴스  $C_0$ 는 수용돼야만 한다. 이는 도 8에 도시된 바와 같이 병렬 서셉턴스  $B_1^N$ 을 커패시턴스( $C_0^{R1'}$  및 서셉턴스  $B^{N1'}$ )로 대체함으로써 달성될 수 있다.  $C_0^{R1'}$ 은 BVD 모델(122)의 정적 커패시턴스를 표현하며,  $B^{N1'}$ 은 관계식  $B^{N1'} - \omega (C_0^{R1'})$ 으로 주어진다. 서셉턴스  $B^{N1'}$ , 2개의 인-라인 어드미턴스  $J_{S1}$  및  $J_{12}$  및 션트 음파 공진기(122)는 그 후 도 9에 도시된 바와 같이 인-라인 음파 공진기(122a) 및 직렬 리액턴스(136)( $X_1$ 로 표시됨)로 변환될 수 있다.

[0056] 인-션트 음파 공진기를 초기 필터 회로 설계(100)에 통합하는 변환 기술에서, 특정 서브셋은 각각의 노드(108)에서 접지로 연결되는 공진 소자(114)(서셉턴스  $B^R$ ), 공진 소자(114)와 직렬로 연결된 비공진 소자(116)(어드미턴스 인버터  $J$ ), 및 공진 소자(114)(서셉턴스  $B^R$ )와 병렬로 각각의 노드(108)에서 접지로 연결된 비공진 소자(118)(서셉턴스  $B^N$ )을 포함한다. 예컨대, 도 10에 도시된 바와 같이, 서브셋(130b)은 노드(2)를 포함하며, 따라서 공진 소자  $B^{R2}$ 는 각각의 노드(108)에서 접지로 연결되며, 어드미턴스 인버터 소자  $J_2$ 는 공진 소자  $B^{R2}$ 와 직렬로 연결되고, 비공진 소자  $B^{N2}$ 는 공진 소자  $B^{R2}$ 와 병렬로 각각의 노드(108)에서 접지로 연결된다.

[0057] 도 11에 도시된 바와 같이, 어드미턴스 인버터  $J_{22}$ 은 용량성 PI-회로망(커패시터들  $-C_{22}$ ,  $C_{22}$  및  $-C_{22}$ )으로 대체되고, 공진 소자  $B^{R2}$ 는 인덕턴스(인덕터  $L^{R2}$ ) 및 커패시턴스(커패시터  $C^{R2}$ )의 병렬 L-C 공진기 조합으로 대체된다. 커패시터들  $-C_{22}$ ,  $C_{22}$  및  $-C_{22}$ , 및 인덕터  $L^{R2}$  및 커패시터  $C^{R2}$ 의 병렬 L-C 공진기 조합으로 이루어지는 PI-회로망으로 표현되는 회로 서브-구조(132)는 인덕턴스(인덕터  $L^{R2'}$ ) 및 커패시턴스(커패시터  $C^{R2'}$ )의 직렬 L-C 공진기 조합(134)으로 변환될 수 있다. 중요한 점으로, 이런 직렬 L-C 조합(134)은 BVD 모델(122)의 직렬 공진 레그에 의해 구현될 수 있어, 회로 서브-구조(132)에 더 양호하게 통합될 수 있다.

[0058] BVD 모델(122)을 회로 서브-구조(132)에 통합하기 위하여, BVD 모델(122)의 정적 커패시턴스  $C_0$ 는 수용돼야만 한다. 이는 도 12에 도시된 바와 같이 병렬 서셉턴스  $B^{2N}$ 을 커패시턴스( $C_0^{R1'}$  및 서셉턴스  $B^{N1'}$ )로 대체함으로써 달성될 수 있다.  $C_0^{R2'}$ 은 BVD 모델(122)의 정적 커패시턴스를 표현하며,  $B^{N2'}$ 은 관계식  $B^{N2'} - \omega (C_0^{R2'})$ 으로

주어진다. 따라서, 인-센트 음파 공진기(122b)는 그 후 도 13에 도시된 바와 같이 구현될 수 있다.

[0059] 초기 필터 회로 설계(100)는 교변하는 인-라인 음파 공진기(122a) 및 인-센트 공진기(122b)를 갖는 필터 회로 설계가 생성될 수 있도록 교변하는 서브셋(130a, 130b)으로 분할될 수 있다. 예컨대, 9개의 공진기들  $B^R$ 을 갖는 초기 필터 회로 설계(100)는 도 14에 도시된 바와 같이 교변하는 형태로 배열된 5개의 인-라인 음파 공진기(122a) 및 4개의 인-센트 음파 공진기(122b)를 갖는 음파 필터 회로 구조(150a)로 변환될 수 있다.

[0060] 회로 변환 단계가 초기 필터 회로 설계(즉, 매핑되고 정규화된 회로 소자값들을 계산한 후)에 수행된다고 설명될지라도, 회로 변환 단계가 음파 필터 회로 구조를 생성하기 위하여 초기 필터 회로 구조(즉, 매핑되고 정규화된 회로 소자값을 계산하기 전)에 수행될 수 있음을 이해해야 하며, 이 경우, 음파 필터 회로 구조에 대해 매핑되고 정규화된 회로 소자값들은 음파 필터 회로 설계를 생성하기 위하여 계산될 수 있다.

[0061] 도 2를 다시 참조하면, 음파 필터 회로 설계(150a)의 회로 소자는, 주파수 응답 요건을 정규화된 설계 공간에 매핑하는데 초기에 사용되는 매핑 기술의 역에 따라서 실제 설계 공간(즉, 실제 주파수를 갖는 무손실 회로 소자들(L들 및 C들)에 업매핑된다(단계 66). 예컨대, 수학식 5의 대수 매핑 기술이 주파수 응답 요건을 정규화된 공간에 매핑하는데 사용된다면, 다음의 대수 언매핑 수학식이 정규화된 회로 소자 값들을 실제 설계 공간에 언매핑하는데 사용될 수 있다:

## 수학식 7

$$\omega = \omega_R \left( 1 + \frac{1}{\gamma} \right)^{\frac{Q}{2}}$$

[0062]

[0063] 특히, 임의의  $B$  값이  $B$ 의 부호에 따라 달라지는  $L$  또는  $C$  중 어느 하나로 구현될 수 있다. 정규화된 회로 값들의 언매핑은, 도 16에 도시된 바와 같이 각각의 공진기에 대한 공진 주파수  $\omega_R$  및 정적 커패시턴스  $C_0$ , 커파시터 및 인덕터의 커패시턴스 및 인덕턴스의 값들과 함께 도 15에 도시된 구현 회로를 가져오고, 이는 시뮬레이션시 도 17에 도시된 주파수 응답을 가져왔다(주의: 인덕터  $L_1$  및 커파시터  $C_1$ 은 회로망의 동일한 입력 및 출력 임피던스를 제공하기 위하여 폴 추출(pole extraction)에 의해 합성의 끝에 추가된다).

[0064] 다음으로, 사전 최적화된 필터 회로 설계에 도달하기 위하여 전자기 시뮬레이터, 예컨대 Sonnet® Software를 이용하고 버스바(busbar)(상호접속) 손실을 추가하여 기생 효과가 음파 필터 회로 설계(150a)에 추가된다(단계 68). 음파 공진기의 손실은 각각의 회로 소자에 대한  $Q$  팩터를 연관시킴으로써 포함될 수 있다. 본 실시예에서, 운동 커패시턴스  $C_m$ (124)은  $Q_{cm}=10^8$ 으로 정의되는 연관된  $Q$ 를 가지며, 정적 커패시턴스  $C_0$ (126)는  $Q_{co}=200$ 으로 정의되는 연관된  $Q$ 를 가지고, 운동 인덕턴스  $L_m$ (128)은  $Q_{lm}=1000$ 으로 정의되는 연관된  $Q$ 를 가진다. 남아있는 인덕터들은  $Q_u=60$ 으로 정의되는 연관된  $Q$ 를 가지며, 남아있는 커파시터들은  $Q_u=200$ 으로 정의되는 연관된  $Q$ 를 가진다.  $R_s=0.5$ 옴의 버스바(상호접속) 저항이 또한 각각의 음파 공진기에 추가된다.

[0065] 그 후 사전 최적화된 필터 회로 설계는 최종 필터 회로 설계를 생성하기 위하여 컴퓨터화된 필터 최적화기에 입력된다(단계 70). 선택적인 방법에서, ERO(element removal optimization) 기술이 최적화 동안 실현된다. 여기서, 불필요한 또는 "사라지는(vanishing)" 회로 소자들은 단순한 회로 소자들로 제거 또는 감소되어, 도 18에 도시된 최종 필터 회로 설계를 가져온다. ERO 기술은 미국 출원 번호 제61/802,114호(발명의 명칭 "Element Removal Design in Microwave Filters")에 기술되어 있다. 최적화 및 ERO 기술은, 도 19에 도시된 바와 같이 각각의 공진기에 대한 공진 주파수  $\omega_R$  및 정전 커패시턴스  $C_0$ , 및 커파시터의 커패시턴스를 가져왔으며, 시뮬레이션시 목표 주파수 응답 요건을 만족시키는 도 20에 도시된 주파수 응답을 가져왔다.

[0066] 특히, 도 2에 도시된 회로망 합성 기술 따라 설계된 다중 대역 필터들은 종래의 이미지 설계 기법들 및 이들의 단순한 확장에 따라 설계된 마이크로웨이브 음파 필터에 비해 비교적 큰 범위에 걸쳐있는 공진 주파수를 갖는 공진들 및 공진기들을 가질 것으로 예상된다.

[0067] 예컨대, 필터 또는 그 공진기의 공진 주파수의 범위(span)와 비교될 수 있는 하나의 척도(measure)는 가장 큰 공진 주파수를 갖는 필터 내의 공진기의 주파수 분리이다. 42도 XY-컷 LiTaO<sub>3</sub> 기판에서,  $\gamma$ 는 약 12보다 크다. 음파 공진기의 구현시 임의의 기생 커패시턴스는  $\gamma$ 를 증가시킬 수 있으며, 따라서 분리 퍼센티지를 감소시키면

서 기생 인더턴스는  $\gamma$ 를 효율적으로 감소시킬 수 있다. 본 예에서,  $\gamma=12$ 에 대해, 분리 퍼센티지는 4.0833%이며, 이에 따라 가장 높은 공진 주파수를 갖는 공진기의 분리는 약 88.1MHz(즉, 2151.57MHz의 공진 주파수에 4.0833%의 분리 퍼센티지를 곱함)이다. 필터 또는 그 공진기의 공진 주파수의 범위와 비교될 수 있는 다른 척도는 그 공진기의 평균 주파수 분리, 이 경우 77.32MHz이다.

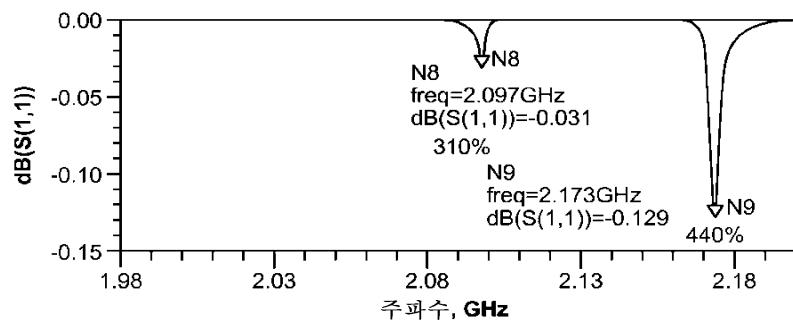

[0068] 음파 공진기의 주파수 분리와는 달리, 2개의 음파 공진기들 간의 "주파수 차이"는 2개의 공진기들의 공진 주파수들 간의 절대 주파수 차를 의미하며, 필터의 2개의 공진들 간의 주파수 차이는 2개의 공진들 간의 절대 주파수 차이이다. 도 21a 및 도 21b는 도 18 및 도 19에 정의된 필터의 복귀 손실(S11)을 도시한다. 복귀 손실 최소들은 필터 회로의 공진들에 대응하며, 초기 필터 회로의 반사 제로들에 또한 대응한다. 도 21a는 필터 통과 대역 N1 내지 N7을 형성하는 데 주로 책임이 있는 필터의 공진들을 도시한다. 도 21a에 도시된 가장 높은 공진과 가장 낮은 공진 간의 주파수 차이는 102MHz이거나 또는 공진기들의 평균 주파수 분리의 약 1.32배이다. 또한, 결합된 도 21a 및 도 21b의 가장 높은 공진과 가장 낮은 공진 간의 주파수 차이는 349MHz(2173-1824MHz)이거나 또는 공진기들의 평균 주파수 분리의 약 4.51배이고, 필터의 가장 높은 공진기와 가장 낮은 공진기 간의 주파수 차이는 459.37MHz(2151.57-1892.2MHz)이거나 또는 공진기들의 평균 주파수 분리의 약 5.94배이다.

[0069] 따라서, 최종 필터 회로 설계에서 통과 대역 공진들의 가장 낮은 공진 주파수와 가장 높은 공진 주파수 간의 차이는 공진기들의 평균 분리의 적어도 1.25배일 것으로 예상된다.

[0070] 도 2에 도시된 회로망 합성 기술에 따라 설계된 다중 대역 필터는, 종래의 이미지 설계 기술에 따라 설계된 필터와 대조되게 통과대역으로부터 비교적 멀리 떨어져 위치하는 반사 제로(zero)들에 대응하는 공진들과 더불어 공진기들을 가질 것임이 예상되며, 여기서 반사 제로들에 대응하는 공진기들 및 공진들은 통과대역에 국한되거나 또는 이에 매우 근접한다.

[0071] 특히, 반사 제로들에 대응하는 공진들은, 국부 복귀 손실(및/또는 S11) 최소들 및 국부 삽입 손실(및/또는 S21) 최대들이 최대 주파수 분리의 약 5% 미만, 본 예에서는 약 4.405MHz 미만 내로 일치하는 주파수들에서 일어난다. 대안적으로, 반사 제로들에 대응하는 공진들은 S11의 지연의 국부 최소 및 국부 최대에서 일어난다(도시 안 됨). 도 21b에서 알 수 있듯이, 반사 제로들에 대응하는 일부 공진들(특히, 마커 N1, N2 및 N6-N9에 대응하는 공진들)은 통과대역(1850MHz 내지 1910MHz) 밖에서 멀리 떨어져 위치한다. 반사 제로에 대응하는 공진과 가장 근접한 통과대역 예지 간의 주파수 차이는 최대 주파수 분리(본 예에서는 약 88.1MHz)의 1배보다 크며, 어쩌면 1.25배보다 클 수 있고, 어쩌면 2배보다 클 수 있다. 본 특정 예에서, 반사 제로들은 통과대역의 예지로부터의 평균 공진기 분리(77.32MHz)의 3.40배까지 위치한다. 통과대역 폭(60MHz)에 관하여, 반사 제로들 N1, N2은 통과대역의 하부 예지의 43.33% 및 28.33% 미만이며, 반사 제로들 N6, N7은 통과대역의 상부 예지를 13.33% 및 26.67% 초과한다. 반사 제로들 N1, N2, N6 및 N7은 서로 인접한다. 통과 대역 저지 제로들 N1, N2, N6, N7과 인접하지 않는 반사 제로들 N8, N9는 통과대역의 상부 예지를 311.67% 및 438.33% 초과한다. 최종 필터 회로 설계의 삽입 손실은 바람직하게 3dB 미만이며, 더 바람직하게는 2dB 미만이다.

[0072] 도 2를 다시 참조하면, 최종 필터 회로 설계가 달성되면, 실제 마이크로웨이브 필터가 최종 필터 회로 설계를 기초로 구성된다(단계 72). 바람직하게, 실제 마이크로웨이브 필터의 회로 소자값들은 최종 필터 회로 설계에서 대응하는 회로 소자 값들과 매칭할 것이다.

[0073] 특히, 다른 주파수 응답들의 조사(survey)가 회로망 합성 기술(50)의 다양한 포인트들에서 분석되고 비교될 수 있다. 일 실시예에서, 단계 70에서 최종 필터 회로 설계를 생성하기 위하여 컴퓨터화된 필터 최적화기에 입력되는 사전 최적화된 회로 설계에 도달하도록 단계 68에서 생성된 음파 필터 회로 설계(150a)의 다른 버전에 기초하여 상이한 주파수 응답들의 조사가 분석되고 비교될 수 있다. 예컨대, 입력과 출력 사이의 상이한 음파 공진기 주파수 순서화(ordering)가 수행될 수 있다. 특히, 음파 공진기가 신호 송신 경로와 함께 배치되는 순서는 다수의 필터 솔루션들을 생성하도록 변경될 수 있으며, 하나 이상의 성능 파라미터들이 필터 솔루션들 각각에 대해 계산될 수 있고, 상이한 필터 솔루션들에 대한 성능(들) 파라미터들이 서로 비교될 수 있고, 이런 비교를 기초로 가장 양호한 필터 솔루션(결국 공진기들의 순서화)이 선택될 수 있다. 이런 조사 프로세스는 실제 필터 회로 설계에서 음파 공진기 주파수들의 순서화의 모든 가능한 순열(permutation)을 다룰 수 있다. 성능 파라미터들은 예컨대 필터 요건에서 원하는 성능 특성들과 대조하여 각 회로 응답을 평가하기 위하여 특정 주파수 또는 다수의 주파수 중 어느 하나에서의 삽입 손실, 복귀 손실, 저지, 그룹 지연, 노드 전압 및 분기 전류 중 하나 이상일 수 있다. 조사 프로세스는 필터 요건과 대비하여 특정 회로가 수행될 수 있는 방법을 나타내는 정량적 또는 정성적 성능 메트릭(quantitative or qualitative performance metric) 값들을 가져올 수 있다.

[0074] 다른 실시예에서, 조사 프로세스는, 공진기의 정적 커패시턴스  $C_0$ 의 모든 실현가능한 값들, J-인버터들의 포지티

브(유도성) 및/또는 네가티브(용량성) 값들(페리티들)의 모든 순열들, 및 그 응답 함수는 변경하지 않을 수 있지만, 실현가능한 저-손실 회로의 응답은 변경할 수 있는 무손실 설계에서 변동될 수 있는 다른 파라미터들도 다를 수 있다. 공진 주파수를 재순서화하는 조사 프로세스를 논의한 추가 상세는 미국 특허 제7,924,114호에 개시된다.

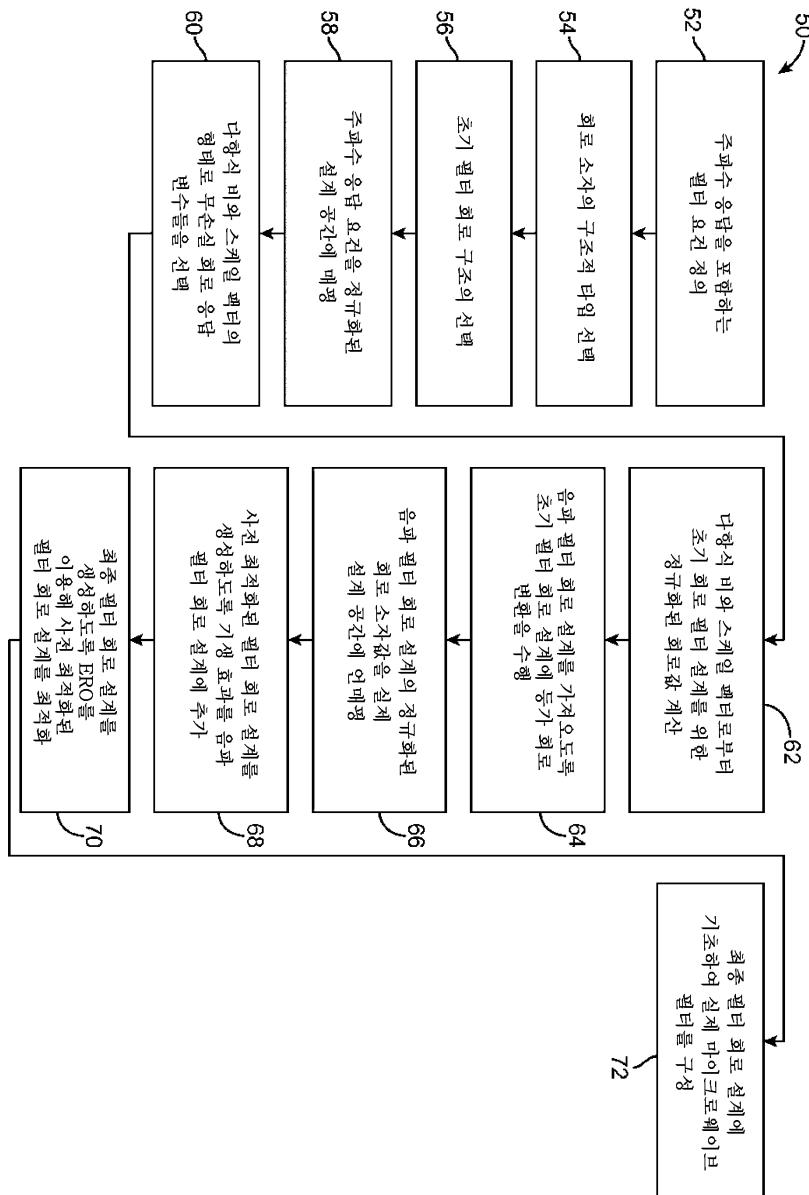

[0075] 필터 요건들이 고정된 통과대역 및 저지대역을 정의하는 것으로 본 실시예에 설명되었다 할지라도, 필터 요건들은 다수의 재구성가능한 통과대역 및/또는 저지대역을 정의할 수 있음을 이해해야 한다. 예컨대, 일 실시예에서, 설계는, 2개의 상태들: 3.5bB 미만의 삽입 손실을 갖는 824MHz와 849MHz 사이의 주파수들을 통과시키며 적어도 40bB 만큼 869MHz와 894MHz 사이의 주파수들을 저지하는 제1 상태(대역 5로 불림), 및 3.5bB 미만의 삽입 손실을 갖는 880MHz와 915MHz 사이의 주파수들을 통과시키며 적어도 40bB 만큼 925MHz와 960MHz 사이의 주파수들을 저지하는 제2 상태(대역 8로 불림) 사이에서 재구성가능할 수 있다(단계 52). 회로 소자 타입은 15도 Y-컷 LiTaO<sub>3</sub> 기판상에 구성된 SAW 공진기들 및 15도 Y-컷 LiTaO<sub>3</sub> 기판상에 집적된 커패시터들로서 선택된다(단계 54).

[0076] 그 후, 도 3에 도시된 초기 필터 회로 구조(100)는 주파수 응답 요건들로부터 획득된 통과대역(들) 및/또는 저지대역(들)에 기초하여 선택된다(단계 56). 이 경우, 공진기들의 수는 6이다. 그 후 주파수 요건들은 정규화된 공간에 매핑되고(단계 58), 무손실 회로 응답이 다항식 비의 형태로 선택되고(단계 60), 그 후 초기 필터 회로 설계를 생성하기 위하여 이를 다항식들로부터 결합 행렬 또는 파라미터 추출 방법 또는 등가회로 합성 기술을 이용하여 초기 필터 회로 구조(100)에서 매핑되고 정규화된 회로 소자 값들이 계산된다(단계 62).

[0077] 다음에, 음파 공진기를 수용하도록 초기 필터 회로 설계(100)에 등가 회로 변환이 수행된다(단계 64). 전술한 것과 동일한 방식으로, 회로 변환은 초기 필터 회로 설계(100)를 공진 소자들(114)의 수(이 경우, 6)와 동일한 다수의 서브셋 회로 설계로 분할하여, 6개의 션트 음파 공진기들을 가져온다.

[0078] 인-션트 음파 공진기를 초기 필터 회로 설계(100)에 통합하는 하나의 변환 기술에서, 도 6에 도시된 서브셋(130)은, 도 22에 도시된 바와 같이, 어드미턴스 인버터 J<sub>S1</sub>을 용량성 PI-회로망(커패시터들 -C<sub>S1</sub>, C<sub>S1</sub> 및 -C<sub>S1</sub>)으로, 어드미턴스 인버터 J<sub>12</sub>를 용량성 PI-회로망(커패시터들 -C<sub>12</sub>, C<sub>12</sub> 및 -C<sub>12</sub>)으로, 어드미턴스 인버터 J<sub>11</sub>을 용량성 PI-회로망(커패시터들 -C<sub>11</sub>, C<sub>11</sub> 및 -C<sub>11</sub>)으로, 그리고 공진 소자 B<sub>1</sub><sup>R1</sup>를 인덕턴스(인덕터 L<sup>R1</sup>) 및 커패시턴스(커패시터 C<sup>R1</sup>)의 병렬 L-C 공진기 조합으로 대체함으로써 변환될 수 있다. 도 7에 관해 전술한 것과 동일한 방식으로, 커패시터들 -C<sub>11</sub>, C<sub>11</sub> 및 -C<sub>11</sub> 및 인덕터 L<sup>R1</sup> 및 커패시터 C<sup>R1</sup>의 병렬 L-C 공진기 조합으로 이루어지는 PI-회로망으로 표현되는 회로 서브-구조(132)는 인덕턴스(인덕터 L<sup>R1'</sup>) 및 커패시턴스(커패시터 C<sup>R1'</sup>)의 직렬 L-C 공진기 조합(134)으로 변환될 수 있다. BVD 모델(122)의 정적 커패시턴스 C<sub>0</sub>를 수용하기 위하여, 3개의 인접 병렬 커패시턴스 및 서셉턴스(-C<sub>S1</sub>, C<sub>12</sub> 및 -B<sub>1</sub><sup>N</sup>)는 도 23에 도시된 커패시턴스(C<sub>0</sub><sup>R1'</sup> 및 서셉턴스 B<sub>1</sub><sup>N'</sup>)로 대체된다. C<sub>0</sub><sup>R1'</sup>은 BVD 모델(122)의 정적 커패시턴스를 표현하며, B<sub>1</sub><sup>N1'</sup>은 관계식 B<sub>1</sub><sup>N1'</sup> = ω(C<sub>S1</sub>+C<sub>12</sub>+C<sub>0</sub><sup>R1'</sup>)으로 주어진다. 따라서, 인-션트 음파 공진기(122)가 도 24에 도시된 바와 같이 구현될 수 있다. 초기 필터 회로 설계(100)의 다른 서브셋(130)은 도 25에 도시된 바와 같이 6개의 인-션트 음파 공진기들(122)을 갖는 음파 필터 회로 구조(150b)에 도달하도록 동일한 방식으로 변환될 수 있다.

[0079] 음파 필터 회로 구조(150b)의 회로 소자는 그 후 실제 공간에 언매핑되고(단계 66), 사전 최적화된 회로 설계에 도달하도록 음파 필터 회로 구조(150b)에 기생 효과가 추가된다(단계 68). 전술한 바와 같이, 회로 소자의 손실은 각각의 회로 소자에 대한 Q 팩터를 연관시킴으로써 포함될 수 있다. 본 실시예에서, 운동 커패시턴스 C<sub>m</sub>은 Q<sub>cm</sub>=10<sup>8</sup>으로 정의되는 연관된 Q를 가지며, 정적 커패시턴스 C<sub>0</sub>는 Q<sub>co</sub>=140으로 정의되는 연관된 Q를 가지고, 운동 인덕턴스 L<sub>m</sub>은 Q<sub>Lm</sub>=3000으로 정의되는 연관된 Q를 가진다. 남아있는 인덕터들은 Q<sub>u</sub>=60으로 정의되는 연관된 Q를 가지며, 남아있는 커패시터들은 Q<sub>u</sub>=200으로 정의되는 연관된 Q를 가진다. R<sub>s</sub>=0.5옴의 버스바(상호접속) 저항이 또한 각각의 음파 공진기에 대해 추가된다. 본 실시예에서, 3pF/(mm 게이트 폭) 및 1.0옴\*(mm 게이트 폭)의 스위치 기생이 또한 추가된다.

[0080] 다음으로, 사전 최적화된 필터 회로 설계는 최종 회로 설계를 생성하기 위하여 선택적인 ERO 기술을 이용하여

컴퓨터 필터 최적화기에 입력된다(단계 70). 최적화 이전에, 도 26에 도시된 바와 같이 임피던스가 2개의 대역들 사이에서 상이한 각각의 분기에 스위치가 추가되어, 그 결과 최적화될 2개의 개별 설계들로부터 단일 회로를 생성한다. 주어진 분기의 임피던스가 일 스위치 상태에서 요구되는 대역 5 임피던스이며, 다른 스위치 상태에서 요구되는 대역 8 임피던스일 수 있도록 각각의 스위치의 게이트 폭, 인덕터 또는 커패시터(필요하다면)의 값 및 분기의 회로 구성이 선택된다. ERO 기술은 그 후 결합 회로상에서 반복된다. 최적화 프로세스는 도 27에 도시된 바와 같이 각각의 공진기에 대한 공진 주파수  $\omega_R$  및 정적 커패시턴스  $C_0$ , 및 커패시터 및 인덕터의 커패시턴스 및 인덕턴스를 가져오고, 시뮬레이션시 도 28에 도시된 대역 5에 대한 주파수 응답 및 도 29에 도시된 대역 8에 대한 주파수 응답을 가져왔다.

[0081] 이전에 논의한 바와 같이, 다른 주파수 응답들의 조사가 회로망 합성 기술(50)의 다양한 포인트들에서 분석 및 비교될 수 있다. 일 실시예에서, 단계 70에서 최종 필터 회로 설계를 생성하기 위하여 컴퓨터화된 필터 최적화기에 입력되는 사전 최적화된 회로 설계에 도달하도록 단계 68에서 생성된 음파 필터 회로 설계(150a)의 다른 버전에 기초하여 상이한 주파수 응답들의 조사가 분석 및 비교될 수 있다. 예컨대, 한 쌍의 회로(하나는 대역 5이고 하나는 대역 8임)가 공진기 주파수들의 각각의 가능한 순서화, J 인버터들(인덕터 또는 용량성)의 각각의 가능한 패리티(parity), 및 공진기들에 대한 정적 커패시턴스  $C_0$  값들의 선택으로 생성된다. 이런 조사 프로세스에서, 공진기 주파수 순서화들의 모든 가능한 순열들, 모든 가능한 패리티들, 및 0.95, 1.9, 3.8 및 7.6 pF의 다양한 실제 정적 커패시턴스  $C_0$  값들이 각각의 설계에 대한 통과대역 중심 주파수에서 삽입 순서를 계산하는데 사용된다. 그 후, 한 쌍의 설계(하나는 대역 5이고 하나는 대역 8이고 공진기 순서 및 정적 커패시턴스  $C_0$  값들이 동일함)가 선택될 수 있다.

[0082] 비록 이전 실시예가 동적으로 재구성가능한 통과대역 및/또는 저지대역을 포함한다 할지라도, 회로망 합성 기술에 따라 구성되는 필터는 필터의 최종 완성 이전에는 재구성가능하지만, 필터의 완성 이후에는 고정될 수 있는 고정 통과대역들 및/또는 저지대역들을 가질 수 있음을 이해해야 한다. 예컨대, 도 30에 도시된 일 실시예에서, 무손실 회로 모델이 836.5MHz(대역 5) 또는 897.5MHz(대역 8)에 중심을 둔 어느 한 통과대역을 갖는 필터를 생성하기 위하여 구현될 수 있다. 이런 무손실 회로는 3개의 SAW 필터들을 이용하는 도 3에 도시된 초기 필터 회로 설계(100)를 변환하여 생성되었다.

[0083] 3개의 인-센트 음파 공진기들을 초기 필터 회로 설계(100)에 통합하는 변환 기술에서, 도 10 내지 도 13에 도시된 변환 기술은 회로 서브셋들(각각의 서브셋은, 각각의 노드(108)에서 접지로 연결되는 공진 소자(114)(서셉턴스  $B^R$ ), 공진 소자(114)와 직렬로 연결된 비공진 소자(116)(어드미턴스 인버터 J), 및 공진 소자(114)(서셉턴스  $B^R$ )와 병렬로 각각의 노드(108)에서 접지로 연결된 비공진 소자(118)(서셉턴스  $B^N$ )을 포함함)을 3개의 인-센트 음파 공진기들로 변환하는데 활용될 수 있다. 회로 소자 타입은 42도 Y-컷  $\text{LiTaO}_3$  기판상에 구성된 SAW 공진기들 및 42도 Y-컷  $\text{LiTaO}_3$  기판상에 접적된 커패시터들로서 선택된다.

[0084] 필터는 공진기들(이 경우,  $C_{S1}$ ,  $C_{12}$ ,  $C_{23}$ ,  $C_{3L}$ ) 및 비공진 센트 소자들(이 경우,  $L_S$ ,  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_L$ ) 사이의 직렬 소자들의 값들을 변경함으로써 완성 전에 재구성될 수 있다. 그 후 필터는 대역 5에 대한 비공진 소자들의 값들 또는 대역 8에 대한 비공진 소자들의 값들 중 어느 하나를 이용하여 구성될 수 있다. 최적화 프로세스는 도 30에 도시된 바와 같이 각각의 공진기에 대한 정적 커패시턴스  $C_0$ , 및 커패시터 및 인덕터의 커패시턴스 및 인덕턴스를 가져오고, 시뮬레이션시 도 31에 도시된 대역 5에 대한 주파수 응답 및 도 32에 도시된 대역 8에 대한 주파수 응답을 가져왔다.

[0085] 비록 본 발명의 특정 실시예가 도시되고 설명되었다 할지라도, 상술한 논의는 본 발명을 이들 실시예들로 제한하고자 하는 것이 아니라는 점을 이해해야 한다. 당업자에게는 본 발명의 정신 및 범위를 벗어남이 없이 다양한 수정 및 변형이 이루어질 수 있음이 자명할 것이다. 예컨대, 본 발명은 단일 입력 및 출력을 갖는 필터를 훨씬 넘어선 어플리케이션을 가지며, 본 발명의 특정한 실시예는 듀플렉서, 멀티플렉서, 채널라이저, 리액티브스위치 등을 형성하는데 사용될 수 있으며, 여기서 저-손실 선택성 회로가 사용될 수 있다. 따라서, 본 발명은 특히 청구범위에 정의된 바와 같이 본 발명의 정신 및 범위 내에 있을 수 있는 대안, 수정 및 균등률들을 커버하는 것을 의도한다.

## 도면

## 도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

| 소자 | 인덕턴스(nH) | 소자 | 커패시턴스(pF) | 소자   | CO(pF) | 주파수(MHz) |

|----|----------|----|-----------|------|--------|----------|

| L1 | 9.05     | C1 | 2.45      | Res1 | 1.96   | 1858.13  |

| L2 | 1.43     | C2 | 0.89      | Res2 | 0.84   | 1825.00  |

| L3 | 0.38     | C3 | 0.14      | Res3 | 0.31   | 1881.19  |

| L4 | 11.93    |    |           | Res4 | 0.61   | 1831.00  |

| L5 | 0.09     |    |           | Res5 | 0.89   | 1910.00  |

| L6 | 63.42    |    |           | Res6 | 0.16   | 2150.00  |

| L7 | 7.18     |    |           | Res7 | 0.54   | 2032.00  |

| L8 | 0.21     |    |           | Res8 | 4.42   | 1797.00  |

|    |          |    |           | Res9 | 4.69   | 1852.36  |

## 도면17

## 도면18

## 도면19

| 소자   | CO(pF) | 주파수(MHz) |

|------|--------|----------|

| Res1 | 6.51   | 1854.78  |

| Res2 | 2.93   | 1792.20  |

| Res3 | 0.81   | 1877.00  |

| Res4 | 3.48   | 1800.00  |

| Res5 | 1.13   | 1866.30  |

| Res6 | 0.61   | 2151.57  |

| Res7 | 6.14   | 2026.79  |

| Res8 | 1.63   | 1806.38  |

| Res9 | 1.74   | 1867.06  |

## 도면20

## 도면21a

## 도면21b

도면22

도면23

## 도면24

## 도면25

도면26

도면27

| 소자 | 인덕턴스 (nH) | 소자 | 커패시턴스 (pF) | 소자   | Co (pF) | 주파수 (MHz) | 소자 | (mm) |

|----|-----------|----|------------|------|---------|-----------|----|------|

| L1 | 8.3       | C1 | 0.85       | Res1 | 0.95    | 929.02    | S1 | 3.3  |

| L2 | 7.9       | C2 | 3.80       | Res2 | 0.95    | 870.21    | S2 | 4.0  |

| L3 | 5.7       | C3 | 0.27       | Res3 | 0.97    | 924.11    | S3 | 4.0  |

| L4 | 2.4       | C4 | 4.60       | Res4 | 1.79    | 787.07    | S4 | 4.0  |

| L5 | 15.3      | C5 | 3.90       | Res5 | 4.51    | 800.95    | S5 | 4.0  |

| L6 | 12.6      |    |            | Res6 | 0.95    | 947.94    | S6 | 4.0  |

| L7 | 13.0      |    |            |      |         |           | S7 | 3.3  |

| L8 | 13.6      |    |            |      |         |           |    |      |

## 도면28

## 도면29

도면30

도면31

도면32