PCT

WELTORGANISATION FÜR GEISTIGES EIGENTUM

Internationales Büro

INTERNATIONALE ANMELDUNG VERÖFFENTLICHT NACH DEM VERTRAG ÜBER DIE

INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT)

|                                                         |                                                                                                                                           |                                                                                                                                                |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| (51) Internationale Patentklassifikation <sup>6</sup> : | A1                                                                                                                                        | (11) Internationale Veröffentlichungsnummer: WO 98/26453<br>(43) Internationales Veröffentlichungsdatum: 18. Juni 1998 (18.06.98)              |

| H01L 23/498, 21/60                                      |                                                                                                                                           |                                                                                                                                                |

| (21) Internationales Aktenzeichen:                      | PCT/DE97/02885                                                                                                                            | (81) Bestimmungsstaaten: AU, CA, CN, JP, KR, SG, US, europäisches Patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE). |

| (22) Internationales Anmeldedatum:                      | 11. Dezember 1997<br>(11.12.97)                                                                                                           |                                                                                                                                                |

| (30) Prioritätsdaten:                                   | 196 51 566.1 11. Dezember 1996 (11.12.96) DE                                                                                              | Veröffentlicht<br><i>Mit internationalem Recherchenbericht.</i>                                                                                |

| (71)(72) Anmelder und Erfinder:                         | FINN, David [IE/DE]; König-Ludwig-Weg 24, D-87459 Pfronten (DE). RIETZLER, Manfred [DE/DE]; Am Alsterberg 10, D-87616 Marktoberdorf (DE). |                                                                                                                                                |

| (74) Anwalt:                                            | TAPPE, Hartmut; Böck + Tappe Kollegen, Egloffsteinstrasse 7, D-97072 Würzburg (DE).                                                       |                                                                                                                                                |

(54) Title: CHIP MODULE AND MANUFACTURE OF SAME

(54) Bezeichnung: CHIP-MODUL SOWIE VERFAHREN ZU DESSEN HERSTELLUNG

(57) Abstract

Disclosed is a chip module (37) with a substrate (12) and, mounted thereon, at least one chip (38) which (11) is contacted through its connecting surfaces with the connecting leads (14, 15) provided on the substrate (12) and presents, following an electrochemical removal of material from the back (39), a reduced thickness d as compared with its original thickness D.

(57) Zusammenfassung

Chip-Modul (37) mit einem Substrat (12) und mindestens einem auf dem Substrat angeordneten Chip (38), wobei der Chip (11) mit seinen Anschlußflächen auf Anschlußleitern (14, 15) des Substrats (12) kontaktiert ist und durch einen Materialabtrag auf seiner Rückseite (39) eine gegenüber seiner ursprünglichen Dicke D reduzierte Dicke d aufweist.

#### **LEDIGLICH ZUR INFORMATION**

Codes zur Identifizierung von PCT-Vertragsstaaten auf den Kopfbögen der Schriften, die internationale Anmeldungen gemäss dem PCT veröffentlichen.

|    |                              |    |                                   |    |                                                 |    |                                |

|----|------------------------------|----|-----------------------------------|----|-------------------------------------------------|----|--------------------------------|

| AL | Albanien                     | ES | Spanien                           | LS | Lesotho                                         | SI | Slowenien                      |

| AM | Armenien                     | FI | Finnland                          | LT | Litauen                                         | SK | Slowakei                       |

| AT | Österreich                   | FR | Frankreich                        | LU | Luxemburg                                       | SN | Senegal                        |

| AU | Australien                   | GA | Gabun                             | LV | Lettland                                        | SZ | Swasiland                      |

| AZ | Aserbaidschan                | GB | Vereinigtes Königreich            | MC | Monaco                                          | TD | Tschad                         |

| BA | Bosnien-Herzegowina          | GE | Georgien                          | MD | Republik Moldau                                 | TG | Togo                           |

| BB | Barbados                     | GH | Ghana                             | MG | Madagaskar                                      | TJ | Tadschikistan                  |

| BE | Belgien                      | GN | Guinea                            | MK | Die ehemalige jugoslawische Republik Mazedonien | TM | Turkmenistan                   |

| BF | Burkina Faso                 | GR | Griechenland                      | ML | Mali                                            | TR | Türkei                         |

| BG | Bulgarien                    | HU | Ungarn                            | MN | Mongolei                                        | TT | Trinidad und Tobago            |

| BJ | Benin                        | IE | Irland                            | MR | Mauretanien                                     | UA | Ukraine                        |

| BR | Brasilien                    | IL | Israel                            | MW | Malawi                                          | UG | Uganda                         |

| BY | Belarus                      | IS | Island                            | MX | Mexiko                                          | US | Vereinigte Staaten von Amerika |

| CA | Kanada                       | IT | Italien                           | NE | Niger                                           | UZ | Usbekistan                     |

| CF | Zentralafrikanische Republik | JP | Japan                             | NL | Niederlande                                     | VN | Vietnam                        |

| CG | Kongo                        | KE | Kenia                             | NO | Norwegen                                        | YU | Jugoslawien                    |

| CH | Schweiz                      | KG | Kirgisistan                       | NZ | Neuseeland                                      | ZW | Zimbabwe                       |

| CI | Côte d'Ivoire                | KP | Demokratische Volksrepublik Korea | PL | Polen                                           |    |                                |

| CM | Kamerun                      | KR | Republik Korea                    | PT | Portugal                                        |    |                                |

| CN | China                        | KZ | Kasachstan                        | RO | Rumänien                                        |    |                                |

| CU | Kuba                         | LC | St. Lucia                         | RU | Russische Föderation                            |    |                                |

| CZ | Tschechische Republik        | LI | Liechtenstein                     | SD | Sudan                                           |    |                                |

| DE | Deutschland                  | LK | Sri Lanka                         | SE | Schweden                                        |    |                                |

| DK | Dänemark                     | LR | Liberia                           | SG | Singapur                                        |    |                                |

5

10

### **CHIP-MODUL SOWIE VERFAHREN ZU DESSEN HERSTELLUNG**

- 15 Die vorliegende Erfindung betrifft ein Chip-Modul mit einem Substrat und mindestens einem auf dem Substrat angeordneten Chip nach dem Oberbegriff des Anspruchs 1. Darüber hinaus betrifft die vorliegende Erfindung ein Verfahren zur Herstellung eines Chip-Moduls gemäß dem Oberbegriff des Anspruchs 7.

- 20 Chip-Module mit einem auf einem Substrat angeordneten Chip werden grundsätzlich überall dort eingesetzt, wo es darauf ankommt, durch die gegenüber den Chipanschlußflächen wesentlich vergrößerten Anschlußleiter des Substrats eine erleichterte elektrische Kontaktierung des Chips zu ermöglichen. So werden derartige Chip-Module beispielsweise in Chip-

- 25 karten eingesetzt und ermöglichen über die freiliegend auf der Kartenoberfläche angeordneten Anschlußleiter des Substrats eine "äußere Kontaktierung" des durch die Anordnung auf der Rückseite des Substrats im Innern der Chipkarte aufgenommenen Chips. Des weiteren werden derartige Chip-Module auch zum Aufbau sogenannter kontaktloser Chip-

- 30 karten verwendet, bei denen die Anschlußleiter des Substrats zur erleichterten Kontaktierung mit einer im Innern des Kartenkörpers angeordneten Antennenspule dienen. Natürlich lassen sich derartige Chip-Module

2

beispielsweise auch zum Aufbau einer sogenannten "Combi-Card" benutzen, bei der über das Substrat sowohl eine äußere Kontaktierung für einen kontaktbehafteten Zugriff auf den Kartenchip als auch eine innere Kontaktierung für einen kontaktlosen Zugriff auf den Chip über die Antennen-spule ermöglicht wird.

Durch die Kombination eines Chips mit dem Substrat zur Ausbildung des Chip-Moduls entsteht ein im Vergleich zur Dicke des Chips bzw. zur Dicke des Substrats relativ dicker Verbund, der in einem hinsichtlich seiner äußereren Abmessungen festgelegten Kartenkörper untergebracht werden muß. Um sich durch die Unterbringung eines Chip-Moduls in einem Kartenkörper hinsichtlich der Möglichkeiten weiterer Bauteilinstal-lationen im Kartenkörper möglichst wenig einzuschränken, erweist es sich daher als wesentlich, das Chip-Modul so dünn wie möglich auszuführen.

Ein Nachteil der bekannten, relativ dick ausgeführten Chip-Module besteht darin, daß sie schon aufgrund ihrer relativ großen Dicke im Vergleich zum flexiblen Kartenkörper eine höhere Biegesteifigkeit aufweisen, so daß es bei einer im Alltagsbetrieb häufig auftretenden Biegebeanspruchung des Kartenkörpers, insbesondere bei Anordnung des Substrats in der Kartenoberfläche, wie es bei einer Kontaktkarte der Fall ist, zu hohen Beanspruchungen der Verbindung zwischen dem Chip-Modul und dem Kartenkörper bis hin zu einer Ablösung des Chip-Moduls vom Kartenkörper kommen kann.

Der vorliegenden Erfahrung liegt die Aufgabe zugrunde, ein Chip-Modul vorzuschlagen, das sich durch eine insgesamt flache Ausbildung auszeichnet.

Diese Aufgabe wird durch ein Chip-Modul mit den Merkmalen des Anspruchs 1 gelöst.

Bei dem erfindungsgemäßen Chip-Modul ist der Chip mit auf seiner Vorderseite angeordneten Anschlußflächen auf Kontaktflächen des Substrats kontaktiert und weist eine infolge eines Materialabtrags auf der

Oberfläche seiner Rückseite gegenüber seiner ursprünglichen Dicke reduzierte Dicke auf.

Bei dem erfindungsgemäßen Chip-Modul wird der Umstand genutzt, daß die elektrischen Schaltungsebenen im Siliciumkörper des Chips benachbart 5 der Vorder- oder Kontaktseite des Chips, die mit den Anschlußflächen versehen ist, angeordnet sind, und der an die Oberfläche der Rückseite angrenzende Bereich des Silicium-Körpers frei von elektrischen Schaltungsebenen ist. Daher ist es ohne Beeinträchtigung der Funktion des Chips möglich, die Oberfläche des Chips von der Rückseite her bis zur 10 Erreichung einer die einwandfreie Funktion des Chips gewährleistenden Mindestdicke des Chipkörpers abzutragen und den Chip hierdurch wesentlich dünner zu gestalten.

Mit der Reduzierung der Dicke des Chips ist nicht nur eine entsprechende Reduzierung der Gesamtdicke des Chip-Moduls möglich, sondern auch 15 eine Beeinflussung des Biegeverhaltens des Chip-Moduls. Durch die Reduzierung der Chipdicke wird der Chip in seinem Biegeverhalten an das Biegeverhalten des Substrats angepaßt, so daß ein insgesamt biegeweicheres, flexibleres Chip-Modul entsteht, das in seinem Biegeverhalten eher dem Biegeverhalten des Kartenkörpers entspricht.

- 20 Bei einer bevorzugten Ausführungsform des Chip-Moduls ragt der Chip zur Ausbildung einer ineinander greifenden Kontaktierung mit auf den Anschlußflächen ausgebildeten Kontakthöckern in Ausnehmungen des Substrats hinein, deren Boden durch die Leiterbahnstruktur gebildet ist. Aufgrund der in die Ausnehmungen des Substrats eingreifenden Anordnung 25 der Kontakthöcker wird eine besonders abscherfeste Verbindung zwischen dem Chip und dem Substrat erreicht. Darüber hinaus ergibt sich aufgrund dieser "Versenkung" der Kontakthöcker in das Substrat schon durch die Konfiguration des Chip-Moduls eine besonders flache Ausbildung des Chip-Moduls.

- 30 Die Kontakthöcker können aus einem beliebigen elektrisch leitenden Material gebildet sein, wie beispielsweise ein elektrisch leitender Kleber

oder eine Kontaktmetallisierung aus einem Lotmaterial oder ähnlichem.

Besonders vorteilhaft ist es, wenn die Kontakthöcker des Chips in ein elektrisch leitendes Verbindungsma

- 5 terial eingebettet sind, das in den Ausnehmungen des Substrats angeordnet ist. Durch dieses Einbetten der

Kontakthöcker in das Verbindungsma

- 10 terial ist es auch leicht möglich, gegebenenfalls vorhandene Toleranzen in der Differenz zwischen der Höhe der Kontakthöcker und der Tiefe der Ausnehmungen durch das Verbindungsma

- 15 terial auszugleichen und unter Aufrechterhaltung einer sicheren, elektrisch leitfähigen Verbindung zwischen den Kontakthöckern des Chips und den Anschlußleitern des Substrats eine flachstmögliche Gesamtanordnung aus Chip und Substrat zu schaffen, bei der die Oberfläche des Chips und die Oberfläche des Substrats unmittelbar benachbart, also ohne Spaltausbildung, aneinanderliegen können. Somit kann bei der Herstellung des erfindungsgemäßen Chip-Moduls auch auf die von der "Underfiller-

Technologie" her bekannte Applikation eines Underfillers verzichtet werden. Auch auf die die Abscherfestigkeit des Chip-Moduls erhöhende, mechanisch stabilisierende Wirkung des Underfillers kann verzichtet werden, da durch die "Einbettung" der Kontakthöcker und die damit verbundene, zumindest in Teilbereichen der Kontaktmetallisierungen

20 allseitige Umhüllung der Kontakthöcker durch das Verbindungsma

- 25 terial eine besonders feste, mechanisch belastbare Verbindung geschaffen wird.

Die vorstehend erörterte Art der ineinander greifenden Kontaktierung zwischen einem Chip und einem Substrat weist auch unabhängig davon, ob es sich bei dem kontaktierten Chip um einen durch Materialabtrag in der Dicke reduzierten Chip oder um einen konventionellen Chip handelt, erhebliche Vorteile auf. Insbesondere, wenn es darum geht, ein mechanisch stabiles Chip-Modul auszubilden.

Zur weiteren Erhöhung der mechanischen Stabilität der bei dem Chip-Modul zwischen dem Chip und dem Substrat geschaffenen Verbindung

30 kann auf der Chip-Oberfläche zusätzlich zu den elektrisch leitend mit der Chipstruktur verbundenen Kontakthöckern mindestens ein weiterer von

5

der Chipstruktur elektrisch unabhängiger Vorsprung vorgesehen sein, der in eine Befestigungsausnehmung des Substrats eingreift. Durch diesen Vorsprung, der identisch mit den elektrischen Anschlüsse bildenden Kontaktköpfen ausgebildet und hergestellt sein kann, wird ein "Kontakt-dummy" geschaffen, der lediglich eine mechanisch stabilisierende Funktion hat.

Falls erwünscht, kann noch eine weitere mechanische Stabilisierung oder eine abdichtende Versiegelung über einen peripheren oder flächigen Kleberauftrag vorgesehen sein.

10 Eine besonders vorteilhafte Verwendung des Chip-Moduls ergibt sich bei dessen Verwendung in einer Chipkarte.

Bei dem erfindungsgemäßen Verfahren zur Herstellung eines Chip-Moduls der vorstehend erläuterten Art erfolgt zunächst die Ausbildung einer, quasi ein Zwischenprodukt bei der Herstellung des endgültigen Chip-15 Moduls darstellenden Handhabungseinheit aus mindestens einem Chip und einem Substrat durch Kontaktierung des bzw. der Chips auf dem mit einer Leiterbahnstruktur versehenen Substrat, derart, daß der Chip bzw. die Chips mit seinen bzw. ihren Anschlußflächen auf Kontaktflächen des Substrats kontaktiert wird bzw. werden, und anschließend eine Bearbeitung des Chips bzw. der Chips durch ein Materialabtragsverfahren auf seiner bzw. ihrer Rückseite erfolgt, wobei das Substrat zur Handhabung und Stabilisierung des bzw. der Chips während des Bearbeitungsverfahrens dient.

Vor der Kontaktierung der Anschlußflächen kann eine selektive Reinigung 25 der zu kontaktierenden Anschlußflächen des Chips und/oder der Kontaktflächen des Substrats bzw. der gegebenenfalls jeweils darauf aufgebrachten Kontaktköpfe oder Verbindungsstoffoberflächen erfolgen.

Bei Durchführung des erfindungsgemäßen Verfahrens kommt dem Substrat also neben seiner ursprünglichen bestimmungsgemäßen Funktion zur 30 Vergrößerung der Anschlußflächen für eine nachfolgende Kontaktierung

die Funktion einer Aufnahmeeinrichtung zur Aufnahme des Chips während der Bearbeitung zu. Erst durch diese Funktion wird eine leichte Handhabung der Chips während der Bearbeitung der auf dem Substrat vereinzelt, also bereits aus einem Wafer-Verbund herausgelösten Chips möglich.

- 5 Gemäß einer vorteilhaften Variante des erfindungsgemäßen Verfahrens wird zur Ausbildung der Handhabungseinheit eine Vielzahl von Chips auf ein kontinuierlich ausgebildetes Substratband kontaktiert und die Separierung des Substratbands zur Ausbildung vereinzelter Chip-Module erfolgt nach der Bearbeitung der einzelnen Chips. Hierdurch wird eine kontinuierliche Bestückung des Substratbands mit Chips sowie eine nachfolgende, kontinuierliche Bearbeitung der einzelnen Chips zur Ausbildung der in ihrer Dicke reduzierten Chip-Module möglich, so daß auch die in ihrer Dicke reduzierten Chip-Module in einer besonders wirtschaftlichen Art und Weise herstellbar sind.

- 10 15 Bei Durchführung der vorgenannten Verfahrensvariante kann die Bearbeitung mehrerer Chips gleichzeitig erfolgen. Zur Bearbeitung der Chips kann ein Werkzeug verwendet werden, das die gleichzeitige Bearbeitung mehrerer Chips ermöglicht, oder es kann auch eine gleichzeitige Bearbeitung der Chips mit verschiedenen Werkzeugen erfolgen.

- 20 25 30 Als besonders vorteilhaft zur Ausbildung der Handhabungseinheit erweist es sich, die Kontaktierung des bzw. der Chips auf dem Substrat derart durchzuführen, daß auf den Anschlußflächen des bzw. der Chips angeordnete Kontakthöcker in ein Verbindungsmaterial eingesetzt werden, das in Ausnehmungen des Substrats angeordnet ist. Hierdurch kann eine Verbindung realisiert werden, die auch höchsten Scherbeanspruchungen standhält, wie sie beispielsweise bei einer Schleifbearbeitung der Rückseite des Chips entstehen, da die durch die Einbettung der Kontakthöcker in das Verbindungsmaterial hergestellte Verbindung noch zusätzlich durch den Eingriff der Kontakthöcker in die Ausnehmungen des Substrats gesichert wird.

Die Bearbeitung des bzw. der Chips kann durch einen Schleif- oder

Läppvorgang erfolgen. Eine weitere Möglichkeit der Bearbeitung des Chips zur Erzielung eines Chip-Moduls mit reduzierter Dicke besteht in der Durchführung eines chemischen Ätzvorgangs auf der Rückseite des Chips.

- 5 Das zur Herstellung der Verbindung benötigte Verbindungsma-

terial kann nach Art und Darreichungsform unterschiedlich beschaffen sein. So kann

das Verbindungsma-

terial vor dem Einsetzen der Kontakthöcker in die

Ausnehmungen durch flächigen Auftrag auf die Oberfläche der Isolations-

schicht und anschließendes Abziehen der Oberfläche in die Ausnehmungen

10 eingebracht werden.

Auch besteht die Möglichkeit, das Verbindungsma-

terial vor oder nach dem

Einsetzen der Kontakthöcker in die Ausnehmungen in einem Dosierverfah-

ren in flüssigem Zustand in die Ausnehmungen einzubringen.

- 15 Eine weitere Möglichkeit der Applikation des Verbindungsma-

terials

besteht darin, vor dem Einsetzen der Kontakthöcker das Verbindungsma-

terial in stückiger Form, etwa als Blei/Zinn-Lotkugeln, in die Ausnehmungen

einzu-

bringen.

- 20 Auch kann das zur Herstellung des Chip-Moduls verwendete Substrat

bereits soweit vorbereitet sein, daß die Kontakthöcker in Ausnehmungen

eingesetzt werden, die im Bereich der Anschlußleiter bereits mit einem

Verbindungsma-

terialauftrag versehen sind. Hierdurch ist es möglich, das

erfindungsgemäße Verfahren zur Herstellung eines Chip-Moduls auch

ausgehend von bereits vom Substrathersteller entsprechend präparierten

Substraten durchzuführen, wodurch eine besonders kostengünstige

25 Durchführung des Verfahrens möglich wird.

- 30 Wenn die Verbindung zwischen dem Verbindungsma-

terial und den Kon-

takthöckern bzw. dem Verbindungsma-

terial und den Anschlußleitern unter

Einwirkung von Druck und Temperatur erfolgt, ist sichergestellt, daß eine

Verbindung zwischen dem Chip und dem Substrat geschaffen wird, bei

dem die benachbarten Oberflächen von Chip und Substrat aneinander

anliegen, wodurch sich bei entsprechender Bemessung der Verbindungs-materialmenge eine zumindest teilweise Einbettung der Kontakthöcker das Verbindungsmaterial auch bei einem Verbindungsmaterial mit hoher Grenzflächenspannung ergibt.

- 5 Die Verbindung zwischen dem Verbindungsmaterial und den Kontakthöckern kann entsprechend dem an sich bekannten "Flip-Chip"-Verfahren erfolgen, bei dem der Chip mit seinen Kontakthöckern unter Temperatureinwirkung gegen das Verbindungsmaterial gedrückt wird. Hierbei erfolgt demnach die zur Herstellung der Verbindung notwendige Erwärmung des Verbindungsmaterials während des Plazierens.

- 10

Die Verbindung kann aber auch so erfolgen, daß erst nach erfolgter Plazierung eine Erwärmung des Verbindungsmaterials und eine Herstellung der Verbindung im sogenannten "Reflow-Verfahren" erfolgt.

- 15 Unabhängig vom Zeitpunkt der Wärmeeinbringung in das Verbindungs-material erweist es sich als besonders vorteilhaft, wenn die Einbringung der Wärme in das Verbindungsmaterial über die Anschlußleiter des Substrats erfolgt. Auf diese Art und Weise bleibt bei Herstellung der Verbindung der Chip im wesentlichen frei von thermischen Belastungen.

- 20 Weiterhin ist es vorteilhaft, wenn nach der Bearbeitung des Chips eine Funktionsprüfung des Chips erfolgt. Hierbei bilden die Anschlußleiter des Substrats die Prüfkontakte. Die Durchführung dieser elektrischen Prüfung, in der Regel eine Durchgangsprüfung, ermöglicht die Detektierung eines möglicherweise infolge der Bearbeitung des Chips oder der Verbindungs-herstellung zwischen Chip und Substrat in der Funktion beeinträchtigten 25 Chip-Moduls.

Nachfolgend wird das erfindungsgemäße Chip-Modul anhand eines Ausführungsbeispiels sowie eines Verfahrens zu dessen Herstellung unter Bezugnahme auf die Zeichnungen näher erläutert. Es zeigen:

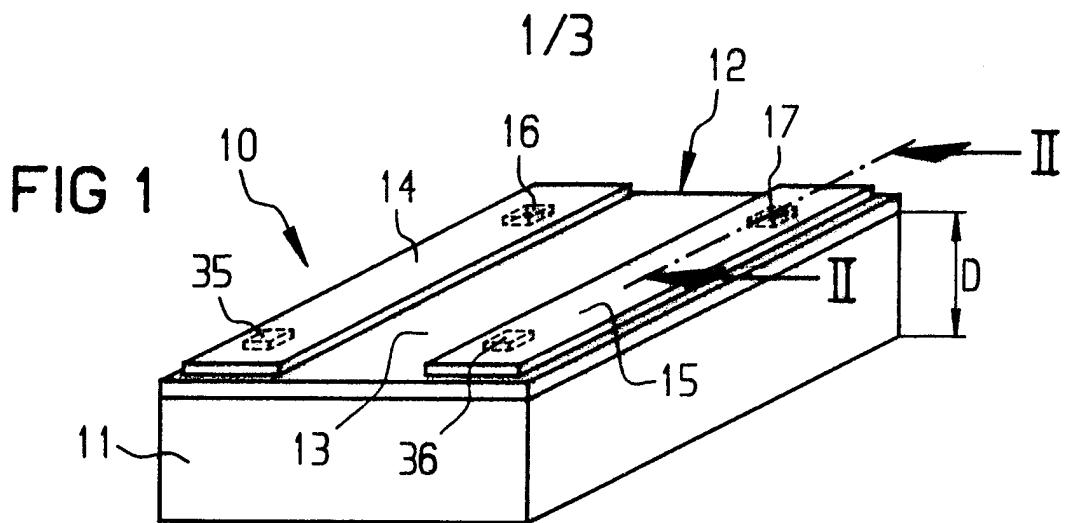

- 30 **Fig. 1** ein Chip-Modul in perspektivischer Darstellung mit einem Chip und einem darauf angeordneten Substrat;

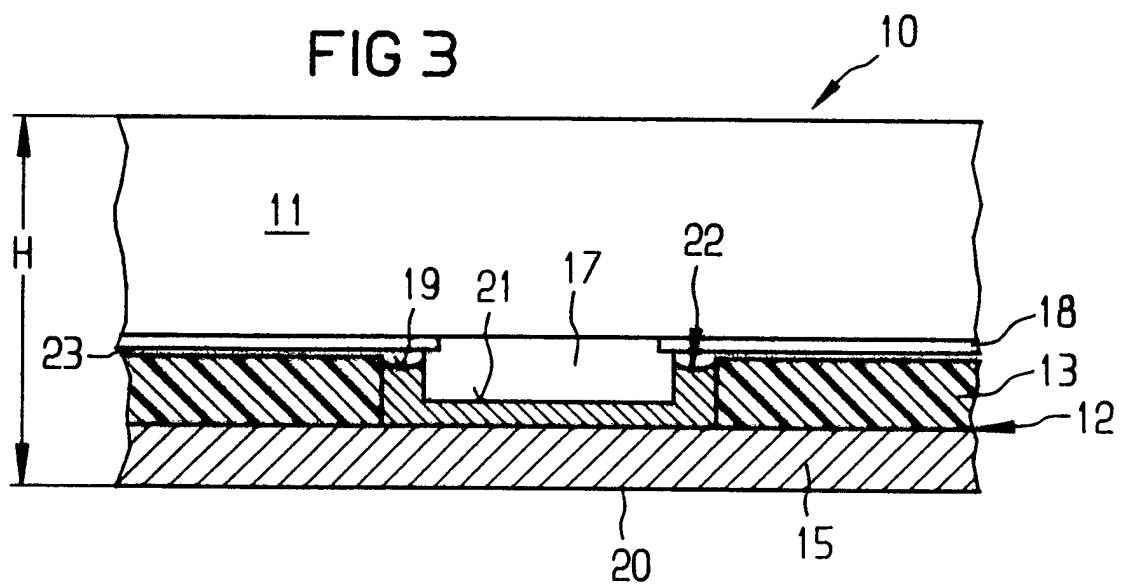

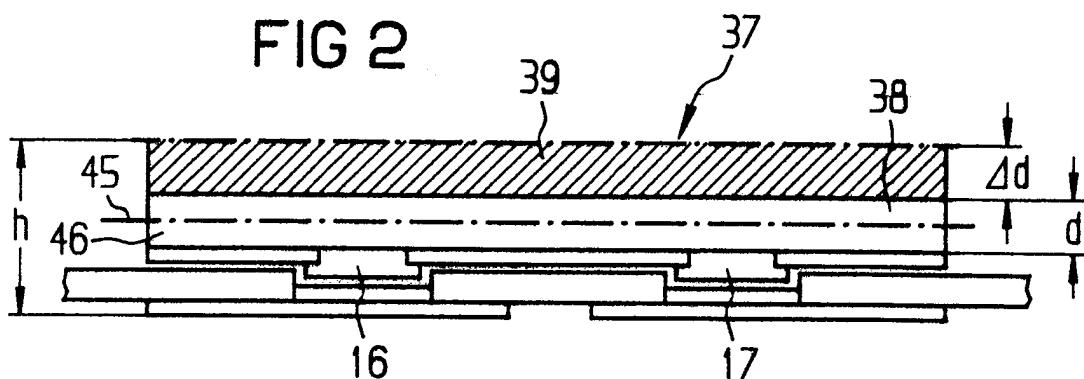

- Fig. 2** eine Seitenansicht des in **Fig. 1** dargestellten Chip-Moduls in vergrößerter Darstellung;

- Fig. 3** das in **Fig. 2** dargestellte Chip-Modul in einer vergrößerten Teildarstellung;

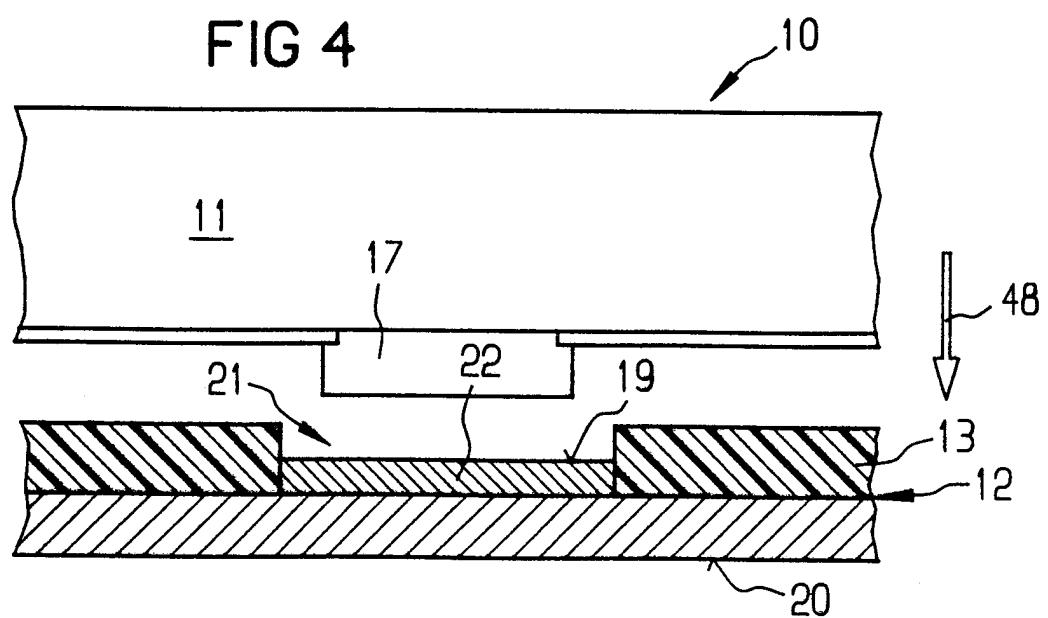

- 5   **Fig. 4** eine in der Darstellung **Fig. 3** entsprechende Darstellung unmittelbar vor der Verbindung des Chips mit dem Substrat zur Ausbildung des Chip-Moduls;

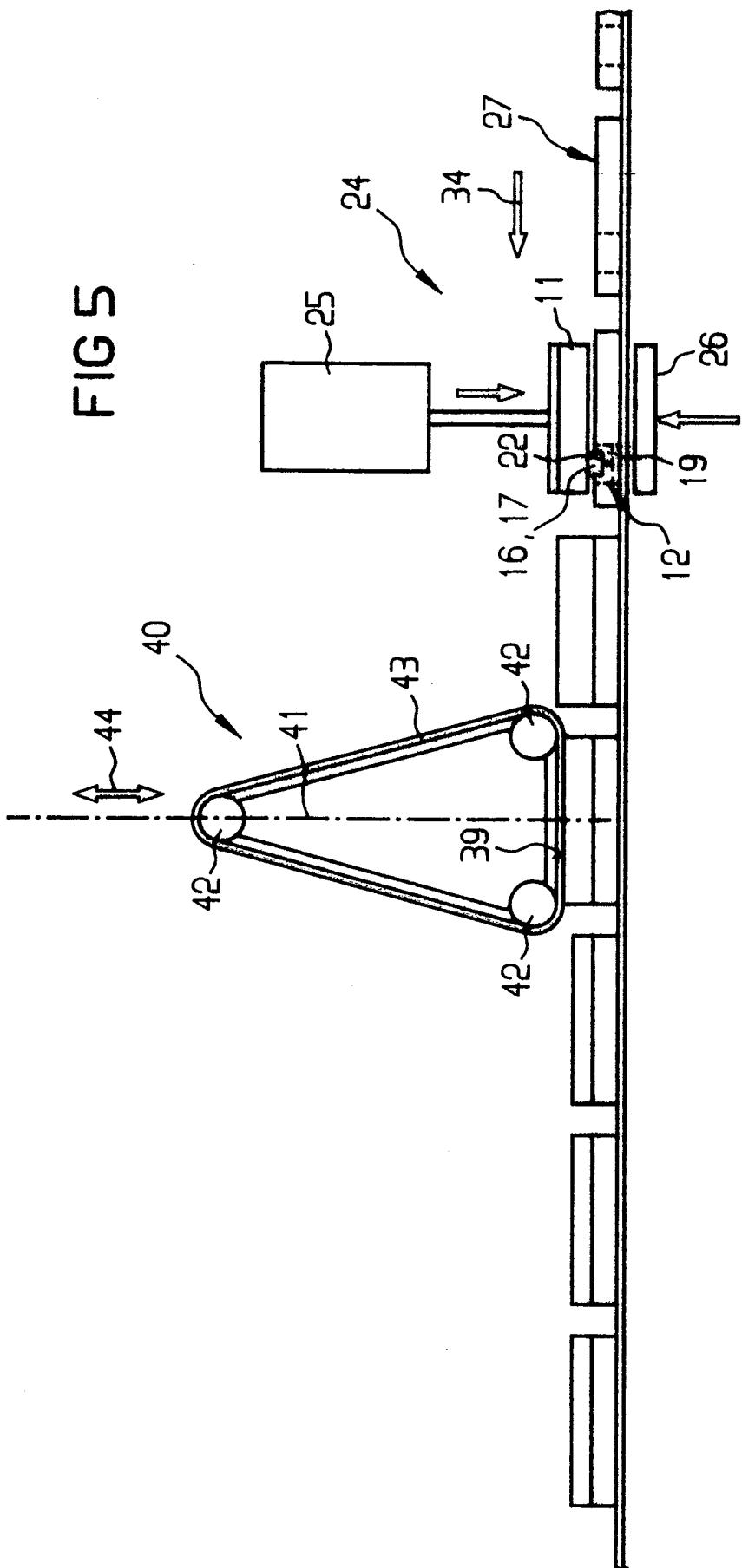

- Fig. 5** eine Vorrichtung zur kontinuierlichen Herstellung des in **Fig. 1** dargestellten Chip-Moduls in einer Schemadarstellung;

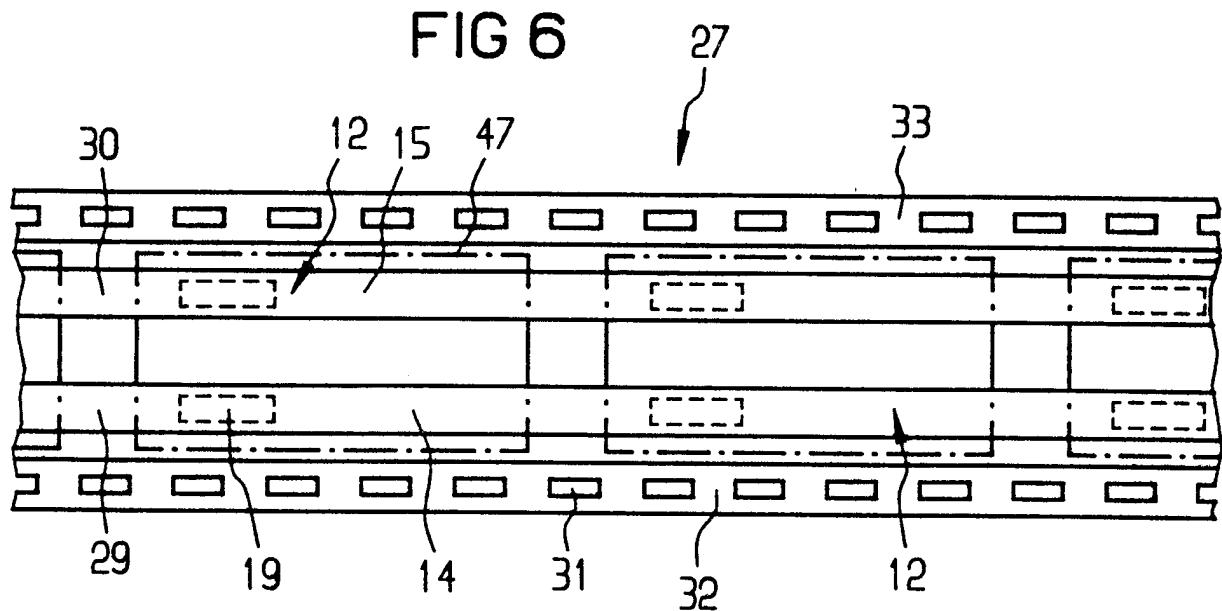

- 10   **Fig. 6** ein Substratband mit einzelnen Substraten in einer Abschnittsdarstellung.

**Fig. 1** zeigt ein Chip-Modul 10 mit einem Chip 11 und einem darauf kontaktierten Substrat 12. Das Substrat 12 weist auf der dem Chip 11 abgewandten Oberseite einer hier als Trägerschicht 13 ausgebildeten 15 Isolationsschicht Anschlußleiter 14, 15 auf, die bei dem hier dargestellten Beispiel in zweifacher Anzahl und sich im wesentlichen längs über die Trägerschicht 13 erstreckend auf dieser angeordnet sind.

Der Chip 11 weist bei dem in **Fig. 1** dargestellten Ausführungsbeispiel zwei in der Fachliteratur unter dem Begriff "Bump" bekannte erhöhte 20 Kontaktmetallisierungen 16, 17 auf, die eine in **Fig. 1** nicht näher dargestellte Passivierungsschicht 18 (**Fig. 3**) des Chips 11 durchdringen und aus dieser hervorragen.

Obwohl **Fig. 1** einen lediglich mit zwei Kontaktmetallisierungen 16, 17 versehenen Chip 11 zeigt, wie er beispielsweise in eine hier nicht näher 25 dargestellte Chipkarte eingesetzt wird, wird betont, daß die nachfolgenden Ausführungen ebenso Chips mit einer hiervon abweichenden Anzahl von Kontaktmetallisierungen, insbesondere solche mit einer Vielzahl von Kontaktmetallisierungen, betreffen, wobei in solchen Fällen auch das mit einem derartigen Chip zu verbindende Substrat in entsprechender Weise

10

mit einer größeren Anzahl von Anschlußleitern ausgeführt ist. Die in **Fig. 1** dargestellte Ausführung wurde aufgrund der damit verbundenen besonders übersichtlichen Darstellungsmöglichkeit gewählt.

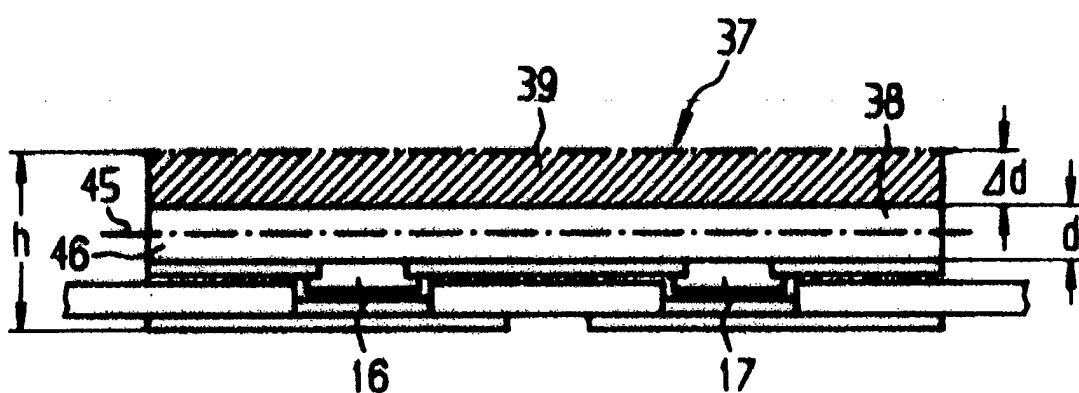

Bei dem in **Fig. 1** dargestellten Chip-Modul 10 weist der auf das Substrat 5 kontaktierte Chip 11 eine reguläre Dicke D auf, die im wesentlichen der Dicke eines hier nicht näher dargestellten Wafers entspricht, aus der der Chip 11 durch Herauslösung aus dem Waferverbund entstanden ist. Die in **Fig. 1** dargestellte Konfiguration des Chip-Moduls 10 bildet, wie nachfolgend noch näher erläutert wird, eine Handhabungseinheit als 10 Ausgangsbasis zur Herstellung eines, hier in **Fig. 2** beispielhaft dargestellten Chip-Moduls 37 mit dem in seiner Dicke reduzierten Chip 38. Gegenüber dem in der **Fig. 1** dargestellten Chip 11 weist, wie durch die schraffierte Teilfläche in **Fig. 2** angedeutet werden soll, der Chip 38 nach einer materialabtragenden Bearbeitung einer den Kontaktmetallisierungen 15 16, 17 gegenüberliegenden, nachfolgend als Rückseite 39 bezeichneten Oberfläche eine um  $\Delta d$  reduzierte Dicke auf, so daß die Dicke d des Chips 38 wesentlich geringer ist als die Dicke D des Chips 11 (**Fig. 1**).

Bei einem Vergleich der **Fig. 2** mit der **Fig. 3**, die das Chip-Modul 10 in einer vergrößerten Teilansicht zeigt, wird deutlich, daß durch die in **Fig. 2** dargestellte Dickenreduzierung  $\Delta d$  gegenüber dem Chip-Modul 10 mit der Gesamtdicke H ein Chip-Modul 37 mit einer wesentlich geringeren Gesamtdicke h möglich wird.

Die **Fig. 3 und 4** verdeutlichen am Beispiel einer Verbindungsstelle die Art und Weise der Ausführung der Verbindung der Kontaktmetallisierung 25 17 mit dem Anschlußleiter 15 des Substrats 12 zur Herstellung des Chip-Moduls 10. Deutlich zu erkennen ist, wie die Kontaktmetallisierung 17 ausgehend von einer Überdeckungslage mit der zugeordneten Ausnehmung 19 in die in der Trägerschicht 13 im Bereich der Kontaktmetallisierung 17 ausgebildete Ausnehmung 19 eingreift. Die Ausnehmung 19 in der Trägerschicht 13 reicht bis zu dem auf der Rückseite der dem Chip 11 zugewandten Trägerschicht 13 angeordneten Anschlußleiter 15 und gibt diesen

im Bereich eines gegenüberliegend einer Außenkontaktseite 20 angeordneten rückwärtigen Chipkontaktebereichs 21 frei.

In der Ausnehmung 19 befindet sich ein Verbindungsmaßmaterial 22, das sowohl zur Herstellung einer elektrisch leitfähigen Verbindung zwischen 5 der Kontaktmetallisierung 17 und dem Chipkontaktebereich 21 des Anschlußleiters 15 als auch zur Herstellung einer mechanisch sicheren Verbindung zwischen dem Chip 11 und dem Substrat 12 dient.

Bei dem in den **Fig. 3** und **4** dargestellten Verbindungsmaßmaterial 22 handelt es sich um einen auf den Chipkontaktebereich 21 des Anschlußleiters 15 10 aufgebrachten Lotauftrag in fester Form. Die für den Lotauftrag gewählte Lotzusammensetzung ist dabei auf die für die Kontaktmetallisierung 17 verwendete Legierung bzw. Materialzusammensetzung abgestimmt. Im Falle der Verwendung von Gold für die Kontaktmetallisierung 17 bietet 15 sich als Verbindungsmaßmaterial ein Blei/Zinn-Lot an. Statt des Lotauftrags kann beispielsweise auch ein elektrisch leitender Kleber auf Epoxidharzbasis oder auch ein thermoplastischer Kleber Verwendung finden.

In jedem Fall wird unabhängig von der Beschaffenheit des Verbindungsmaßmaterials die in **Fig. 3** dargestellte Verbindung zwischen der Kontaktmetallisierung 17 und dem Chip-Kontaktebereich 21 des Anschlußleiters 15 20 durch Einführen (Pfeil 48 in **Fig. 4**) der Kontaktmetallisierung 17 ausgehend von einer Anordnung des Chips 11 oberhalb des Substrats 12 (**Fig. 4**) in die Ausnehmung 19 unter Verdrängung des Verbindungsmaßmaterials 22 ausgeführt. Um bei einer derart hergestellten Verbindung eine wiederholgenuine, gleichbleibende und möglichst geringe Gesamthöhe H des aus dem 25 Chip 11 und dem Substrat 12 gebildeten Chip-Moduls 10 sicherzustellen, ist es ausreichend, die Kontaktmetallisierung 17 bis zur Anlage der Passivierungsschicht 18 des Chips 11 an der dem Chip 11 zugewandten Oberfläche der Trägerschicht 13 in die Ausnehmung 19 einzuführen. Um die über das Verbindungsmaßmaterial 22 erfolgende, in **Fig. 1** am Beispiel der 30 Kontaktmetallisierung 17 dargestellte mechanische Verbindung zwischen dem Chip 11 und dem Substrat 12 noch weiter zu verbessern, ist es

12

möglich, wie in **Fig. 1** angedeutet, neben den Kontaktmetallisierungen 16, 17, die zur elektrischen Kontaktierung des Substrats 12 dienen, weitere Metallisierungsvorsprünge 35, 36 vorzusehen, die entsprechend den Kontaktmetallisierungen 16, 17 ausgebildet sind und in hier nicht näher 5 dargestellte, in der Ausbildung den Ausnehmungen 19 entsprechende Befestigungsausnehmungen eingesetzt sind. Auch hier findet in identischer Weise, wie bei den Kontaktmetallisierungen 16, 17, eine Verbindung der Metallisierungsvorsprünge 35, 36 mit den Anschlußleitern 14, 15 statt, wobei diese Verbindung jedoch lediglich der mechanischen Sicherung des 10 Chips auf dem Substrat dient und keine elektrische Kontaktfunktion hat. Zur Unterstützung der Haftung des Chips 11 auf dem Substrat 12 kann noch eine flächige oder periphere Verklebung des Chips 11 auf dem Substrat 12 vorgesehen werden.

Wie aus **Fig. 3** deutlich hervorgeht, bildet sich auch bei nur teilweiser 15 Versenkung der Kontaktmetallisierung 17 in das Verbindungsmaßaterial 22 eine alle freiliegenden Seiten der hier vereinfacht als Quader dargestellten Kontaktmetallisierung 17 betreffende Benetzung aus. Hieraus resultieren entsprechend geringe elektrische Widerstände im Kontaktbereich der Kontaktmetallisierung 17 und des Verbindungsmaßaterials 22 sowie eine 20 gute mechanische Haftung.

Um insbesondere bei starker Füllung der Ausnehmung 19 mit Verbin- 25 dungsmaterial 22 die Ausbildung von Druckpolstern infolge von Kompre- sionseffekten in der Ausnehmung 19 zu verhindern, kann die Trägerschicht 13 des Substrats 12 auf ihrer dem Chip zugewandten Oberseite mit einem von der Ausnehmung 19 nach außen führenden rillenförmigen Entlüf- tungskanal 23 oder anderen geeigneten Einrichtungen versehen sein.

Neben der in **Fig. 1** dargestellten, als Trägerschicht 13 ausgebildeten Isolationsschicht kann auf den Anschlußleitern noch eine diese zumindest bis auf Kontaktausnehmungen abdeckende, weitere Isolationsschicht 30 angeordnet sein. Darüber hinaus kann das Chip-Modul 10 auch mit einer auf dem Substrat angeordneten Spule zur Ausbildung eines Transponders

versehen sein.

Die zum Versenken der Kontaktmetallisierung 17 in das Verbindungsma-

terial 22 notwendige Erweichung des Verbindungsmaterials bzw. das Auf-

schmelzen des Verbindungsmaterials kann gleichzeitig mit Aufbringen des

5 zum Verdrängen des Verbindungsmaterials notwendigen Drucks erfolgen,

wie beispielsweise in **Fig. 5** dargestellt. **Fig. 5** zeigt eine Chip-Modul-

Herstellungseinrichtung 24 mit zwei in einer stationären Einrichtung

zusammengefaßten Komponenten, nämlich einer Chipplaziereinrichtung 25

und einer Heizeinrichtung 26. Wie **Fig. 5** zeigt, wird der Chip 11 von

10 oben mit seinen nach unten gerichteten Kontaktmetallisierungen 16, 17

gegen das hier in einem Substratband 27 angeordnete Substrat 12 verfah-

ren. Dabei werden die Kontaktmetallisierungen 16, 17 zur Anlage an das

in den Ausnehmungen 19 auf dem Chipkontaktbereich 21 (**Fig. 3**) der

Anschlußleiter 14, 15 angeordnete Verbindungsma-

terial 22 gebracht.

15 Während der Kontaktierung der Kontaktmetallisierungen 16, 17 mit dem

Verbindungsma-

terial 22 kann über die von unterhalb des Substratbands 27

gegen das betreffende Substrat 12 bewegte Heizeinrichtung 26 eine

Kontaktbeheizung der Anschlußleiter 14, 15 erfolgen. Unter dem Druck

der Chipplaziereinrichtung 25 dringen dann die Kontaktmetallisierungen

20 16, 17 in das unter der Temperatureinwirkung erweichende Verbindungs-

material 22 ein.

Alternativ zu der vorstehend beschriebenen Erwärmung des Verbindungs-

materials 22 während der Plazierung des Chips 11, ist es auch möglich,

das Verbindungsma-

terial 22 nachfolgend der Plazierung der Chips 11 in

25 einem Reflow-Verfahren aufzuschmelzen und hierdurch die für die Ver-

bindung des Verbindungsma-

terials 22 mit den Kontaktmetallisierungen 16,

17 notwendige Benetzung der Kontaktmetallisierungen zu bewirken. Je

nach Beschaffenheit des Verbindungsma-

terials kann es dabei notwendig

sein, durch eine zusätzliche, der Chipplaziereinrichtung 25 nachgeordnete

30 Druckeinrichtung durch Druck auf die Kontaktmetallisierungen 16, 17 den

Grenzflächenwiderstand des Verbindungsma-

terials 22 zu überwinden, um

ein Versenken der Kontaktmetallisierungen 16, 17 im Verbindungsma-

terial

14

22 zur Erzielung der beschriebenen Einbettung der Kontaktmetallisierungen 16, 17 im Verbindungsma

5 terial 22 zu ermöglichen.

Fig. 6 zeigt das im Zusammenhang mit der in Fig. 5 dargestellten Chip-Modul-Herstellungseinrichtung 24 bereits erwähnte Substratband 27 in einer Draufsicht. Wie die Draufsicht verdeutlicht, weist das Substratband 27 eine Vielzahl kontinuierlich aufeinanderfolgend ausgebildeter Substrate 12 auf, die über ihre substratübergreifend ausgebildeten Anschlußleiter 14, 15 miteinander verbunden sind. Zur Separierung eines einzelnen Substrats 11, wie es in Fig. 1 dargestellt ist, aus dem Substratband 27 ist lediglich ein Stanzvorgang längs der strichpunktieren in Fig. 5 eingezeichneten Stanzlinien 47 notwendig. Durch den Stanzvorgang werden Verbindungsber

10 eiche 29, 30 der Anschlußleiter 14, 15 sowie mit einer Perforation 31 versehene, als Traktionsräder ausgebildete Außenräder 32, 33 des Substratbands 27 abgetrennt. Eine derartige Ausbildung des Substratbands 15 27 ermöglicht eine kontinuierliche Fertigung von Chip-Modulen 10, wobei, wie in Fig. 5 dargestellt, das Substratband 27 mit den darin vorge-sehenen Substraten 12 in Vorschubrichtung 34 an der Chipplaziereinrich-tung 25 getaktet vorbeigeführt wird.

Die in der Chip-Modul-Herstellungseinrichtung 24 hergestellten Chip-Module 10 bilden jeweils ein Zwischenprodukt bzw. eine Handhabungs-einheit zur nachfolgenden Bearbeitung der Chips 11 mit dem Ziel, Chip-Module 37 mit im Vergleich zu den Chips 11 dünneren Chips 38 herzu-stellen. Durch den durch das Substratband gebildeten Verbund bilden die Chip-Module 10 in ihrer Gesamtheit einen entsprechenden Handhabungs-verbund. Vor der vorstehend erläuterten Separierung der Chip-Module 10 aus dem Substratband 27 erfolgt, wie in Fig. 5 am Beispiel eines kontinuierlichen Herstellungsvorgangs dargestellt, eine materialabtragende Bearbeitung der Chips 11 der Chip-Module 10, nach deren Herstellung in der Chip-Modul-Herstellungseinrichtung 24. Hierzu werden die Chip-Module 10 einer Bearbeitungseinrichtung 40 zugeführt, in der ein Abtrag des Chipkörpermaterials von der Rückseite 39 des Chips 11 erfolgt, wie in Fig. 2 schematisch dargestellt. Bei dem in Fig. 5 beispielhaft dargestellten

15

Bearbeitungsverfahren wird als Bearbeitungseinrichtung eine Bandschleifeinrichtung 40 verwendet, die ein auf einen Geräteträger 41 über Rollen 42 kontinuierlich umlaufendes, endloses Schleifband 43 aufweist. Der Geräteträger 41 ist mit einer hier nicht näher dargestellten Zustelleinrichtung versehen, die eine Auf- und Ab-Bewegung des Geräteträgers 41 in Richtung des Doppelpfeils 44 ermöglicht. Durch eine Überlagerung der umlaufenden Bewegung des Schleifbands 43 mit einer auf die Rückseite 39 des Chips 11 gerichteten Zustellbewegung ist es möglich, den Chip 11 kontinuierlich in seiner Dicke zu reduzieren, bis sich ein Chip 38 mit einer gegenüber dem ursprünglichen Chip 11 reduzierten Dicke  $d$  einstellt (**Fig. 2**). Die mittels dieser Bearbeitung erreichbare Dicke  $d$  ist begrenzt durch die in **Fig. 2** mit strichpunktiertem Linienverlauf angedeuteten Grenzschicht 45, die einen zwischen der Passivierungsschicht 18 und der Grenzschicht 45 liegenden Schaltungsbereich 46 des Chips begrenzt. Bis zum Erreichen der Grenzschicht 45 ist eine Bearbeitung des Chips von dessen Rückseite 39 her möglich, ohne durch ein Eindringen in den Schaltungsbereich 46 die Funktion des Chips zu beeinträchtigen.

Ergebnis der in **Fig. 5** dargestellten Bearbeitung des Chips 11 mit der Bandschleifeinrichtung 40 ist das in **Fig. 2** dargestellte Chip-Modul 37, das gegenüber dem Ausgangs-Chip-Modul 10 eine wesentlich verringerte Gesamthöhe  $h$  aufweist. Die kontinuierlich nach dem in **Fig. 5** dargestellten Verfahren hergestellten, in ihrer Dicke reduzierten Chip-Module 37 können dann wie vorstehend unter Bezugnahme auf die **Fig. 6** beschrieben, aus dem Verbund des Substratbands 27 separiert werden.

16

**Patentansprüche**

1. Chip-Modul mit einem Substrat und mindestens einem auf dem Substrat angeordneten Chip, wobei der Chip über auf seiner Vorderseite angeordnete Anschlußflächen auf Anschlußleitern des mit einer Leiterbahnstruktur versehenen Substrats kontaktiert ist dadurch gekennzeichnet,

daß der Chip (38) durch einen Materialabtrag auf seiner Rückseite (39) eine gegenüber seiner ursprünglichen Dicke reduzierte Dicke aufweist.

2. Chip-Modul nach Anspruch 1,

dadurch gekennzeichnet,

daß der Chip (38) zur Ausbildung einer ineinander greifenden Kontaktierung mit auf den Anschlußflächen ausgebildeten Kontakthöckern (16, 17) in Ausnehmungen (19) des Substrats (12) hinein ragt, deren Boden durch die Anschlußleiter (14, 15) der Leiterbahnstruktur gebildet ist.

3. Chip-Modul nach Anspruch 1 oder 2,

dadurch gekennzeichnet,

daß die Kontakthöcker (16, 17) des Chips (38) in einem elektrisch leitenden Verbindungsmedium (22) eingebettet sind, das in den Ausnehmungen (19) des Substrats (12) angeordnet ist.

4. Chip-Modul nach Anspruch 2 oder 3,

dadurch gekennzeichnet,

daß auf der Vorderseite des Chips (38) neben den elektrisch leitend mit der Leiterbahnstruktur verbundenen, in die Ausnehmungen (19) eingreifenden Kontakthöckern (16, 17) mindestens ein weiterer elektrisch von der Leiterbahnstruktur unabhängiger Vorsprung (35, 36) vorgesehen ist, der in eine Befestigungsausnehmung des Substrats (12) eingreift.

17

5. Chip-Modul nach einem oder mehreren der vorangehenden Ansprüche,

dadurch gekennzeichnet,

daß der Chip (11, 38) peripher oder flächig mit dem Substrat (12)

verklebt ist.

6. Chip-Modul nach einem oder mehreren der vorangehenden Ansprüche,

gekennzeichnet durch

die Verwendung in einer Chipkarte.

- 10 7. Verfahren zur Herstellung eines Chip-Moduls mit einem Substrat und mindestens einem auf dem Substrat angeordneten Chip,

gekennzeichnet durch

die Verfahrensschritte:

- Ausbildung einer Handhabungseinheit (10) aus mindestens einem Chip (11) und einem Substrat (12) durch Kontaktierung des bzw. der Chips auf dem mit einer Leiterbahnstruktur versehenen Substrat, derart, daß der Chip bzw. die Chips mit seinen bzw. ihren Anschlußflächen auf Anschlußleitern (14, 15) des Substrats kontaktiert wird bzw. werden, und

- Bearbeitung des Chips (11) bzw. der Chips durch ein Materialabtragsverfahren auf seiner bzw. ihrer Rückseite (39), wobei das Substrat (12) zur Handhabung und Stabilisierung des bzw. der Chips (11) während der Bearbeitung dient.

- 25 8. Verfahren nach Anspruch 7,

dadurch gekennzeichnet,

daß zur Ausbildung der Handhabungseinheit (10) eine Vielzahl von Chips (11) auf ein kontinuierlich ausgebildetes Substratband (27) kontaktiert wird, und zur Ausbildung einzelner Chip-Module (37) die Separierung des Substratbands (27) nach erfolgter Bearbeitung der Chips (11) erfolgt.

- 30 9. Verfahren nach Anspruch 7 oder 8,

18

dadurch gekennzeichnet,

daß die Bearbeitung mehrerer Chips (11) gleichzeitig erfolgt.

10. Verfahren nach einem oder mehreren der Ansprüche 7 oder 9,

dadurch gekennzeichnet,

daß die Bearbeitung mehrerer Chips (11) mit einem gemeinsamen

Werkzeug erfolgt.

11. Verfahren nach einem oder mehreren der Ansprüche 7 bis 10,

dadurch gekennzeichnet,

daß zur Ausbildung der Handhabungseinheit (10) die Kontaktierung

des bzw. der Chips (11) auf dem Substrat (12, 27) derart erfolgt,

daß auf den Anschlußflächen des bzw. der Chips (11) angeordnete

Kontakthöcker (16, 17) in ein Verbindungsmedium (22) eingesetzt

werden, das in Ausnehmungen (19) des Substrats (12, 27) angeord-

net ist.

- 15 12. Verfahren nach einem oder mehreren der Ansprüche 7 bis 11

dadurch gekennzeichnet,

daß die Bearbeitung des bzw. der Chips (11) durch einen Schleif-

oder Läppvorgang erfolgt.

13. Verfahren nach einem oder mehreren der Ansprüche 7 bis 11

dadurch gekennzeichnet,

daß die Bearbeitung des bzw. der Chips (11) durch einen Ätzvor-

gang erfolgt.

14. Verfahren nach einem oder mehreren der Ansprüche 7 bis 13,

dadurch gekennzeichnet,

daß nach der Bearbeitung des Chips (11) eine Funktionsprüfung des

Chips erfolgt.

2/3

FIG 2

FIG 6

3/3

FIG 5

# INTERNATIONAL SEARCH REPORT

International Application No

PCT/DE 97/02885

**A. CLASSIFICATION OF SUBJECT MATTER**

IPC 6 H01L23/498 H01L21/60

According to International Patent Classification(IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

IPC 6 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                             | Relevant to claim No. |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 5 155 068 A (TADA NOBURU) 13 October 1992                                                                                                   | 1                     |

| A        | see column 2, line 54 - column 3, line 20; claim 1; figures 4C,4D<br>-----                                                                     | 2,6,7,<br>12,13       |

| X        | PATENT ABSTRACTS OF JAPAN<br>vol. 012, no. 407 (E-675), 27 October 1988<br>& JP 63 147352 A (NEC CORP), 20 June 1988,<br>see abstract<br>----- | 1                     |

| A        | EP 0 207 853 A (BULL SA) 7 January 1987<br>see claims 1,15; figures 1,7,8<br>-----                                                             | 5,7,12                |

| A        |                                                                                                                                                | 2-4,6,<br>8-11        |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

<sup>1</sup> Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

1

Date of the actual completion of the international search

Date of mailing of the international search report

16 March 1998

24/03/1998

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl.

Fax: (+31-70) 340-3016

Authorized officer

De Raeve, R

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/DE 97/02885

| Patent document cited in search report | Publication date | Patent family member(s) |            | Publication date |

|----------------------------------------|------------------|-------------------------|------------|------------------|

| US 5155068 A                           | 13-10-92         | JP                      | 3087299 A  | 12-04-91         |

| EP 0207853 A                           | 07-01-87         | FR                      | 2584235 A  | 02-01-87         |

|                                        |                  | CA                      | 1264872 A  | 23-01-90         |

|                                        |                  | HK                      | 84095 A    | 01-06-95         |

|                                        |                  | JP                      | 1905082 C  | 08-02-95         |

|                                        |                  | JP                      | 6030985 B  | 27-04-94         |

|                                        |                  | JP                      | 62050196 A | 04-03-87         |

|                                        |                  | US                      | 4774633 A  | 27-09-88         |

# INTERNATIONALER RECHERCHENBERICHT

Internationales Aktenzeichen

PCT/DE 97/02885

**A. KLASIFIZIERUNG DES ANMELDUNGSGEGENSTANDES**

IPK 6 H01L23/498 H01L21/60

Nach der Internationalen Patentklassifikation (IPK) oder nach der nationalen Klassifikation und der IPK

**B. RECHERCHIERTE GEBIETE**

Recherchierte Mindestprüfstoff (Klassifikationssystem und Klassifikationssymbole)

IPK 6 H01L

Recherchierte aber nicht zum Mindestprüfstoff gehörende Veröffentlichungen, soweit diese unter die recherchierten Gebiete fallen

Während der internationalen Recherche konsultierte elektronische Datenbank (Name der Datenbank und evtl. verwendete Suchbegriffe)

**C. ALS WESENTLICH ANGESEHENE UNTERLAGEN**

| Kategorie | Bezeichnung der Veröffentlichung, soweit erforderlich unter Angabe der in Betracht kommenden Teile                                                         | Betr. Anspruch Nr. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| X         | US 5 155 068 A (TADA NOBURU) 13. Oktober<br>1992                                                                                                           | 1                  |

| A         | siehe Spalte 2, Zeile 54 - Spalte 3, Zeile<br>20; Anspruch 1; Abbildungen 4C, 4D<br>---                                                                    | 2, 6, 7,<br>12, 13 |

| X         | PATENT ABSTRACTS OF JAPAN<br>vol. 012, no. 407 (E-675), 27. Oktober 1988<br>& JP 63 147352 A (NEC CORP), 20. Juni<br>1988,<br>siehe Zusammenfassung<br>--- | 1                  |

| A         | EP 0 207 853 A (BULL SA) 7. Januar 1987<br>siehe Ansprüche 1, 15; Abbildungen 1, 7, 8<br>-----                                                             | 5, 7, 12           |

| A         | EP 0 207 853 A (BULL SA) 7. Januar 1987<br>siehe Ansprüche 1, 15; Abbildungen 1, 7, 8<br>-----                                                             | 2-4, 6,<br>8-11    |

Weitere Veröffentlichungen sind der Fortsetzung von Feld C zu entnehmen

Siehe Anhang Patentfamilie

° Besondere Kategorien von angegebenen Veröffentlichungen :

"A" Veröffentlichung, die den allgemeinen Stand der Technik definiert, aber nicht als besonders bedeutsam anzusehen ist

"E" älteres Dokument, das jedoch erst am oder nach dem internationalen Anmeldedatum veröffentlicht worden ist

"L" Veröffentlichung, die geeignet ist, einen Prioritätsanspruch zweifelhaft erscheinen zu lassen, oder durch die das Veröffentlichungsdatum einer anderen im Recherchenbericht genannten Veröffentlichung belegt werden soll oder die aus einem anderen besonderen Grund angegeben ist (wie ausgeführt)

"O" Veröffentlichung, die sich auf eine mündliche Offenbarung,

eine Benutzung, eine Ausstellung oder andere Maßnahmen bezieht

"P" Veröffentlichung, die vor dem internationalen Anmeldedatum, aber nach dem beanspruchten Prioritätsdatum veröffentlicht worden ist

"T" Spätere Veröffentlichung, die nach dem internationalen Anmeldedatum oder dem Prioritätsdatum veröffentlicht worden ist und mit der Anmeldung nicht kollidiert, sondern nur zum Verständnis des der Erfindung zugrundeliegenden Prinzips oder der ihr zugrundeliegenden Theorie angegeben ist

"X" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann allein aufgrund dieser Veröffentlichung nicht als neu oder auf erforderlicher Tätigkeit beruhend betrachtet werden

"Y" Veröffentlichung von besonderer Bedeutung; die beanspruchte Erfindung kann nicht als auf erforderlicher Tätigkeit beruhend betrachtet werden, wenn die Veröffentlichung mit einer oder mehreren anderen Veröffentlichungen dieser Kategorie in Verbindung gebracht wird und diese Verbindung für einen Fachmann naheliegend ist

"&" Veröffentlichung, die Mitglied derselben Patentfamilie ist

1

Datum des Abschlusses der internationalen Recherche

Absendedatum des internationalen Recherchenberichts

16. März 1998

24/03/1998

Name und Postanschrift der Internationalen Recherchenbehörde

Europäisches Patentamt, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl.

Fax: (+31-70) 340-3016

Bevollmächtigter Bediensteter

De Raeve, R

# INTERNATIONALER RECHERCHENBERICHT

Angaben zu Veröffentlichungen, die zur selben Patentfamilie gehören

Internationales Aktenzeichen

PCT/DE 97/02885

| Im Recherchenbericht angeführtes Patentdokument | Datum der Veröffentlichung | Mitglied(er) der Patentfamilie |            | Datum der Veröffentlichung |

|-------------------------------------------------|----------------------------|--------------------------------|------------|----------------------------|

| US 5155068 A                                    | 13-10-92                   | JP                             | 3087299 A  | 12-04-91                   |

| EP 0207853 A                                    | 07-01-87                   | FR                             | 2584235 A  | 02-01-87                   |

|                                                 |                            | CA                             | 1264872 A  | 23-01-90                   |

|                                                 |                            | HK                             | 84095 A    | 01-06-95                   |

|                                                 |                            | JP                             | 1905082 C  | 08-02-95                   |

|                                                 |                            | JP                             | 6030985 B  | 27-04-94                   |

|                                                 |                            | JP                             | 62050196 A | 04-03-87                   |

|                                                 |                            | US                             | 4774633 A  | 27-09-88                   |