(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7009186号

(P7009186)

(45)発行日 令和4年1月25日(2022.1.25)

(24)登録日 令和4年1月14日(2022.1.14)

(51)国際特許分類

|        |                 |        |       |   |

|--------|-----------------|--------|-------|---|

| H 03 H | 3/02 (2006.01)  | H 03 H | 3/02  | C |

| H 03 H | 9/05 (2006.01)  | H 03 H | 9/05  |   |

| H 03 H | 9/17 (2006.01)  | H 03 H | 9/17  | F |

| H 01 L | 23/02 (2006.01) | H 01 L | 23/02 | C |

請求項の数 22 外国語出願 (全36頁)

(21)出願番号 特願2017-231501(P2017-231501)

(22)出願日 平成29年12月1日(2017.12.1)

(65)公開番号 特開2018-113677(P2018-113677

A)

(43)公開日 平成30年7月19日(2018.7.19)

審査請求日 令和2年11月30日(2020.11.30)

(31)優先権主張番号 62/429,179

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,218

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,223

最終頁に続く

(73)特許権者 503031330

スカイワークス ソリューションズ, イ

ンコーポレイテッド

SKYWORKS SOLUTIONS

, INC.

アメリカ合衆国 92617 カリフォル

ニア州 アーバイン カリフォルニア ア

ベニュー 5260

(74)代理人 100083806

弁理士 三好 秀和

(74)代理人 100095500

弁理士 伊藤 正和

(74)代理人 100111235

弁理士 原 裕子

(72)発明者 鷹野 敦

最終頁に続く

(54)【発明の名称】 キャビティに形成される電子デバイスを製造する方法

## (57)【特許請求の範囲】

## 【請求項1】

電子デバイスを製造する方法であって、

底面の周縁に沿って形成された第1側壁を有する第1基板を与えることであって、前記第1側壁は前記第1基板の底面に配置された電子回路を取り囲み、前記第1側壁は第1金属からなる第1金属層から形成されることと、

第2側壁を有する第2基板を与えることであって、前記第2基板の頂面の周縁に沿って形成された前記第2側壁は第2金属からなる第2金属層と第3金属からなる第3金属層とが順に積層されて形成され、前記第2金属及び前記第3金属は互いに異なりかつ前記第1金属とも異なることと、

前記第1基板の底面、前記第2基板の頂面、前記第1側壁、及び前記第2側壁により内部にキャビティを画定するべく前記第1基板と前記第2基板とを位置合わせすることであって、前記第1側壁は前記第2側壁に対向かつ接触することと、

液相拡散接合により前記第1側壁と前記第2側壁とを互いに接合させるように前記第1基板及び第2基板を加熱することであって、前記第3金属層が溶融することにより前記第1金属層及び前記第2金属層それぞれと第1合金層及び第2合金層を形成することとを含み、

前記第3金属の融点は前記第2金属の融点未満である方法。

## 【請求項2】

前記第1基板を与えることは、圧電体を有する基板を与えることであり、

前記電子回路は、圧電薄膜共振器、バルク弹性波素子、音響多層膜共振器及び弹性表面波素子の少なくとも一つを含む請求項1の方法。

【請求項3】

前記第3金属層は、前記第1合金層及び前記第2合金層が形成されたときになくなっている請求項1の方法。

【請求項4】

前記第2側壁を、前記第1側壁の高さよりも大きな高さを有するように形成することをさらに含む請求項1の方法。

【請求項5】

前記第2側壁を、前記第1側壁の幅よりも大きな幅を有するように形成することをさらに含む請求項1の方法。

10

【請求項6】

前記第3金属層と前記第2金属層との合金形成の開始温度が、前記第3金属層と前記第1金属層との合金形成の開始温度よりも低い請求項1の方法。

【請求項7】

前記第1金属、前記第2金属及び前記第3金属それぞれが、前記液相拡散接合の間に同時に溶融される状態が存在しない請求項6の方法。

【請求項8】

前記第1金属は金を含む請求項1の方法。

【請求項9】

前記第2金属は銅を含む請求項8の方法。

20

【請求項10】

前記第3金属は、錫及びインジウムの少なくとも一方を含む請求項8の方法。

【請求項11】

前記第1基板の厚さは、前記第2基板の厚さとは異なる請求項1の方法。

【請求項12】

前記キャビティの中において前記第1基板の底面と前記第2基板の頂面との間に柱を形成することをさらに含む請求項1の方法。

【請求項13】

前記柱を形成することは、前記柱を、前記第2合金層の上に積層された前記第1合金層から形成することを含む請求項12の方法。

30

【請求項14】

前記柱を形成することは、前記柱を、前記第1合金層がテーパー状となるように形成することを含む請求項13の方法。

【請求項15】

前記第1基板を通過するピアを形成することをさらに含み、

前記ピアの側面の表面粗さが、前記第1基板の底面の表面粗さよりも大きい請求項1の方法。

【請求項16】

前記ピアを形成することは、

40

第1金属を含む第1ストップ層を前記第1基板の底面に形成することと、

第2金属を含む第2ストップ層を前記第1ストップ層に形成することと、

前記ピアを形成するべく前記第1基板をエッティングすることと

を含み、

前記第1基板のエッティングが前記第1ストップ層及び前記第2ストップ層の一方において終わる請求項15の方法。

【請求項17】

前記ピアを貫通する部分と、前記第1基板の上面の上方に延びる上方拡張部分とを有する第1材料層を含む外部電極を形成することをさらに含む請求項15の方法。

【請求項18】

50

前記ピアと前記電子回路との電気接続を形成することをさらに含む請求項1\_5の方法。

【請求項 19】

前記ピアに及び前記第2基板の頂面に結合された柱を形成することをさらに含む請求項1\_5の方法。

【請求項 20】

前記第1基板を与えることは、前記第1基板を、前記第1基板の上面の表面粗さが前記第1基板の底面の表面粗さよりも大きくなるように与えることを含む請求項1の方法。

【請求項 21】

前記第1合金層を形成することは、前記第1合金層を、テーパー状の断面を有するように形成することを含む請求項1の方法。

10

【請求項 22】

前記第1基板及び前記第2基板をプリント基板の頂面に接合することと、

前記プリント基板の頂面を、平均直径を備えた粒子を有するフィラーを含む樹脂によって覆うことと

をさらに含み、

前記第1側壁及び前記第2側壁は、前記第1基板及び前記第2基板それぞれの周縁から内部に、前記フィラーの粒子の平均直径の半分以下となる距離だけ後退する請求項1の方法。

【発明の詳細な説明】

【背景技術】

【0001】

20

従来、携帯電話機のような通信デバイスにおいて、送信信号及び受信信号のような異なる帯域の信号を分離するためのフィルタデバイスが使用されている。圧電薄膜共振器 (F i l m B u l k A c o u s t i c R e s o n a t o r ( F B A R ) ) 及び音響多層膜共振器 ( S o l i d l y M o u n t e d R e s o n a t o r ( S M R ) ) のようなバルク弾性波 ( B u l k A c o u s t i c R e s o n a t o r ( B A W ) ) 共振器を含む電子デバイスが、フィルタデバイスにおいて使用されている。かかる電子デバイスには、電子回路が配置されたデバイス基板、及びキャップ基板が含まれ得る。かかる電子デバイスは、以下のように製造される。すなわち、デバイス基板及びキャップ基板間の接合部分が、金又は銅のような同種の金属で形成され、当該金属部分が高温高圧で共有接合され、その後、デバイス基板及びキャップ基板が一緒に接合される。

30

【0002】

F B A R フィルタ及び弾性表面波 ( S u r f a c e A c o u s t i c W a v e ( S A W ) ) フィルタを記載する背景資料には、非特許文献1が含まれる。

【先行技術文献】

【非特許文献】

【0003】

【文献】F B A R フィルタの開発：S A W フィルタとの比較，電子情報通信学会技術研究報告，E D，電子デバイス103(728)，9-14，2004-03-09

【発明の概要】

【0004】

40

ここに開示される側面及び実施形態は、基板間のキャビティに形成されてピアを含むフィルタのような電子デバイスとその製造方法に関する。

【0005】

電子デバイスを作製するいくつかの従来型の方法には、高温高圧のプロセスを必要とし得る金と金との接合、又は銅と銅との接合が含まれるので、デバイス基板、キャップ基板等の破損が生じたり、製造歩留まりが低下したりすることがある。これらの従来型のプロセスには、常温常圧ステップと高温高圧ステップとの間の繰り返しが含まれるので、サイクルタイムが不必要に長くなることがある。なおもさらに、これらの従来型のプロセスでは、スルーホールの形成プロセスにおけるオーバーエッチングに起因する欠陥が生じ得るので、製造の歩留まりが低下する。

50

## 【 0 0 0 6 】

本開示の複数の側面により、歩留まりを向上させ、サイクルタイムを短縮し、スルーホール形成プロセス中のオーバーエッティング又は上述のすべてによる欠陥を防止するべく使用可能な電子デバイス及び当該電子デバイスの製造方法が得られる。

## 【 0 0 0 7 】

所定の実施形態に係る電子デバイスを製造する方法は、底面の周縁に沿って形成された所定高さの、当該底面に配置された電子回路を取り囲む第1側壁を有する第1基板を与えることであって、第1側壁は第1金属からなる第1金属層により形成されることと、頂面の周縁に沿って形成された所定高さの第2側壁を有する第2基板を与えることであって、第2側壁は第2金属からなる第2金属層と第3金属からなる第3金属層とが順に積層されて形成されることと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁によって内部にキャビティが画定されるように第1基板と第2基板とを位置合わせすることであって、第1側壁は第2側壁に対向かつ接触することと、第1側壁と第2側壁とを互いに接合するべく第1基板及び第2基板を加熱することであって、第1金属層、第2金属層及び第3金属層が液相拡散接合による合金層を形成するべく加熱されることとを含んでよい。第1基板は圧電体からなってよい。電子回路は、圧電薄膜共振器、バルク弾性波素子及び弾性表面波素子の少なくとも一つを含んでよい。

10

## 【 0 0 0 8 】

第3金属の融点は第2金属の融点より低くてよい。第3金属は第2金属とは異なってよい。第1基板及び第2基板を加熱することは、第3金属層を溶融させて第1金属層及び第2金属層それぞれと第1合金層及び第2合金層を形成させることを含んでよい。第1合金層及び第2合金層が形成されるときに第3金属層が消費されてよい。

20

## 【 0 0 0 9 】

第2側壁の高さは、第1側壁の高さよりも大きくてよい。第3金属層と第2金属層との間で合金の形成が開始される温度は、第3金属層と第1金属層との間で合金の形成が開始される温度よりも低くてよい。液相拡散接合の間に、第1金属、第2金属及び第3金属が一緒に溶融する状態が存在しなくともよい。第1基板の厚さは、第2基板の厚さと異なってよい。

## 【 0 0 1 0 】

第1金属は金(Au)を含んでよい。第2金属は銅(Cu)を含んでよい。第3金属は、錫(Sn)及びインジウム(In)の少なくとも一方を含んでよい。

30

## 【 0 0 1 1 】

所定の実施形態によれば、電子デバイスを製造する方法はさらに、プリント基板を与えることを含み、第1側壁及び第2側壁を介して互いに接合された第1基板及び第2基板がプリント基板の頂面に取り付けられ、第1基板及び第2基板が取り付けられたプリント基板の頂面は、所定径のフィラーを含む樹脂で覆われかつ封止され、第1側壁及び第2側壁はそれぞれ、第1基板第2基板の周縁から内側に、当該フィラーの平均径の半分以下である所定距離だけ後退して形成される。

## 【 0 0 1 2 】

所定の実施形態によれば、電子デバイスは、底面の周縁に沿って形成された所定高さの、当該底面に配置された電子回路を取り囲む第1側壁を有する第1基板と、頂面の周縁に沿って形成された所定高さの第2側壁を有する第2基板とを含み、第2側壁は、第1側壁が第2側壁に対向かつ接触して第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により画定されたキャビティが内部に形成されるように、第1側壁に位置合わせされて接合され、第1側壁は、液相拡散接合により第2側壁と接合されてよい。

40

## 【 0 0 1 3 】

所定の実施形態によれば、電子デバイスは、底面及び頂面を有する第1基板と、当該底面に配置された電子回路を取り囲むべく当該底面の周縁に沿って形成された所定高さの第1側壁と、当該頂面に形成された外部電極と、頂面の周縁に沿って形成された所定高さの第2側壁を有する第2基板とを含み、当該外部電極は、当該底面に連通するピアを介して当

50

該電子回路に接続され、第2側壁は、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により画定されたキャビティを内部に形成するべく、第1側壁に位置合わせされて接合されてよい。

【0014】

外部電極は、ビアの直上に配置されてよい。第1基板の厚さは、第2基板の厚さより小さくてよい。第1基板の頂面の表面粗さは、第1基板の底面の表面粗さよりも大きくてよい。ビアの側面の表面粗さは、第1基板の頂面の表面粗さよりも大きくてよい。第1基板は、キャビティを画定する一部分の厚さが周縁部の厚さよりも大きくてよい。

【0015】

所定の実施形態によれば、電子デバイスを製造する方法は、底面及び頂面を有する第1基板の底面の周縁に沿って、当該底面に配置された電子回路を取り囲むべく所定高さの第1側壁を形成することと、当該底面及び当該頂面間を連通させるビアを形成することと、第2基板の頂面の周縁に沿って所定高さの第2側壁を形成することと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁によりキャビティを内部に画定するべく第1側壁及び第2側壁を位置合わせして接合することとを含み、当該ビアを形成することは、当該ビアに対応する第1基板の底面の一部分に第1ストップ層及び第2ストップ層を順に積層することと、当該ビアに対応するスルーホールを形成するべく第1基板をエッチングすることとを含み、第1基板をエッチングする速度は第1ストップ層をエッチングする速度よりも大きく、第1ストップ層をエッチングする速度は第2ストップ層をエッチングする速度よりも大きくてよい。

10

【0016】

第1基板の頂面に、ビアに接続された外部電極を配置してよい。第1基板のエッチングは、ドライエッチングにより行われてよい。第1ストップ層はチタン(Ti)及びクロム(Cr)の少なくとも一方を含んでよく、第2ストップ層は金(Au)を含んでよい。第2ストップ層の厚さは、第1ストップ層の厚さよりも大きくてよい。電子回路は配線パッド及び第1ストップ層を含んでよく、第2ストップ層は、配線パッドの上まで拡張されるように形成されてよい。

20

【0017】

所定の実施形態によれば、電子デバイスを製造する方法は、底面及び頂面を有する第1基板を与えることであって、所定高さの第1側壁が第1基板の底面の周縁に沿って形成されて当該底面に配置された電子回路を取り囲み、当該底面及び当該頂面間を連通させるビアが形成され、当該底面において当該ビアの直下には当該ビアよりも直径が大きい所定高さの第1柱が配置され、第1側壁及び第1柱は第1金属からなる第1金属層により形成されることと、頂面を有する第2基板を与えることであって、所定高さの第2側壁が第2基板の頂面の周縁に沿って形成され、第1基板の底面に形成された第1柱に対応する位置において所定高さの第2柱が当該頂面に形成され、第2側壁及び第2柱は、第2金属からなる第2金属層と第3金属からなる第3金属層とが順に積層されることにより形成されることと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁によりキャビティを内部に画定するべく第1側壁が第2側壁に対向かつ接触し、第1柱が第2柱に対向かつ接触するように第1側壁を第2側壁に位置合わせすることと、第1柱及び第2柱が溶融して互いに接合されるように第1基板及び第2基板を加熱することであって、第1金属層、第2金属層及び第3金属層が加熱されて液相拡散接合により合金層を形成することとを含んでよい。

30

【0018】

所定の実施形態において、電子デバイスは、底面及び頂面を有する第1基板と、頂面を有する第2基板とを含み、当該底面に配置された電子回路を取り囲むように第1基板の底面の周縁に沿って所定高さの第1側壁が形成され、当該底面及び当該頂面間を連通させるようにビアが形成され、当該ビアよりも直径が大きい所定高さの第1柱が当該底面において当該ビアの直下に配置され、所定高さの第2側壁が第2基板の頂面の周縁に沿って形成され、第1基板の底面に形成された第1柱に対応する位置において当該頂面に所定高さの第

40

50

2柱が形成され、第2側壁及び第2柱が、第1側壁が第2側壁に対向かつ接触して第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により画定されたキャビティが内部に形成されるように、第1側壁及び第1柱に位置合わせされて接合され、第1側壁及び第1柱は、液相拡散接合により第2側壁及び第2柱それぞれと接合されてよい。

【0019】

圧電体は、タンタル酸リチウム及びニオブ酸リチウムの少なくとも一方を含んでよい。ピアは、ドライエッキングにより形成されたスルーホールを含んでよい。第1基板の頂面には、ピアに接続された外部電極がさらに配置されてよい。第1柱の直径は、第2柱の直径よりも大きくてよい。第2基板の頂面には他の電子回路が配置されてよく、第2側壁は当該他の電子回路を取り囲むように形成されてよい。第2基板は圧電体からなってよい。第2基板の頂面に配置された電子回路は、圧電薄膜共振器、バルク弾性波素子及び弾性表面波素子の少なくとも一つを含んでよい。

10

【0020】

所定の実施形態によれば、電子デバイスは、底面の周縁に沿って形成された所定高さの、当該底面に配置された電子回路を取り囲む第1側壁を有する第1基板と、頂面の周縁に沿って形成された所定高さの第2側壁を有する第2基板とを含み、第2側壁は、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁によりキャビティを内部に画定するべく、第1側壁に位置合わせされて接合され、当該キャビティは、1気圧よりも低い圧力の雰囲気を含んでよい。

20

【0021】

所定の実施形態において、電子デバイスを製造する方法は、底面の周縁に沿って形成された所定高さの、当該底面に配置された電子回路を取り囲む第1側壁を有する第1基板を与えることと、所定高さの第2側壁を有して平坦な頂面の周縁に沿って形成された第2基板を与えることと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するように第1基板と第2基板とを位置合わせすることであって、第1側壁は第2側壁に対向かつ接触することと、第1側壁と第2側壁とを互いに接合するべく第1基板及び第2基板を加熱することであって、当該加熱は真空中で行われることとを含んでよい。

【0022】

加熱における真空中度は、コントロールバルブによって制御されてよい。第1基板及び第2基板は、加熱の前に大気圧下かつ温度100℃以下で予備加熱されてよい。

30

【0023】

所定の実施形態によれば、電子デバイスを製造する方法は、底面及び頂面を有する第1基板の当該底面の周縁に沿って所定高さの第1側壁を形成し、当該底面に配置された電子回路を取り囲むことと、当該底面及び当該頂面間を連通させるピアと当該頂面の外部電極とを形成することと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するべく第1側壁及び第2側壁を位置合わせして接合することとを含み、当該ピア及び当該外部電極を形成することは、第1基板において当該ピアに対応するスルーホールを形成することと、第1基板の頂面にスパッタ膜を形成することと、当該外部電極に対応するパターンをフォトリソグラフィーにより当該スパッタ膜上に形成することと、金属をメッキして当該スルーホール内に充填することにより当該ピア及び当該外部電極を同時に形成することとを含んでよい。フォトリソグラフィーには、ネガ型液体レジストを使用してよい。

40

【0024】

所定の実施形態によれば、電子デバイスを製造する方法が与えられ、当該電子デバイスは、底面に配置された電子回路を取り囲むように周縁に沿って形成された所定高さの第1側壁を有する第1基板と、頂面の周縁に沿って形成された所定高さの第2側壁を有する第2基板とを含み、第1側壁は、第1基板の底面として第1ウェハの底面に形成され、所定高さの第1封止部が当該周縁に沿って形成され、第2側壁は、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁によりキャビティを内部に画定するべく、第1側壁に位置

50

合わせされて接合されてよい。方法は、第1基板の底面としての第1ウェハの底面に第1側壁を形成するとともに周縁に沿って所定高さを有する第1封止部を形成することと、第2基板の頂面としての第2ウェハの頂面に第2側壁を形成するとともに当該周縁に沿って所定高さの第2封止部を形成することと、第1ウェハの底面、第2ウェハの頂面、第1封止部、及び第2封止部により内部にキャビティを画定するべく第1ウェハと第2ウェハとを互いに位置合わせして接合することとを含み、第1封止部及び第1側壁はそれぞれが、液相拡散接合により第2封止部及び第2側壁と接合されてよい。

#### 【 0 0 2 5 】

第1ウェハ及び第2ウェハはそれぞれが、実質的に円板形状を有してよい。方法はさらに、第1ウェハ及び第2ウェハにおいて、第1封止部及び第2封止部の外側エッジをトリミングすることを含んでよい。トリミングすることは、第1封止部及び／又は第2封止部を、第1ウェハ及び第2ウェハの周縁に露出させてよい。トリミングすることは、第1ウェハ及び第2ウェハにおいて、第1ウェハの底面又は第2ウェハの頂面に対して所定角度をなす封止部を形成してよい。第1ウェハの頂面及び第2ウェハの底面それを、所定深さまで研磨してよい。電子デバイスは、第1ウェハ及び第2ウェハをダイシングにより個片化して形成してよい。第1側壁及び第2側壁並びに第1封止部及び第2封止部は、液相拡散接合により接合された第1合金層及び第2合金層を含んでよい。

10

#### 【 0 0 2 6 】

所定の実施形態によれば、電子デバイスを製造する方法が与えられ、当該電子デバイスは、底面に配置された電子回路を取り囲む周縁に沿って形成された所定高さの第1側壁を有する第1基板と、頂面の周縁に沿って形成された所定高さの第2側壁を有する第2基板とを含み、第2側壁は、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するべく、液相拡散接合により第1側壁と位置合わせされて接合されてよい。方法は、第1基板の底面としての第1ウェハの底面に第1側壁を形成するとともに周縁に沿って所定高さの第1封止部を形成することと、第2基板の頂面としての第2ウェハの頂面に第2側壁を形成することと、周縁に沿って所定高さの第2封止部を形成し、第1ウェハの底面、第2ウェハの頂面、第1封止部、及び第2封止部により内部にキャビティを画定するべく、第1ウェハと第2ウェハとを互いに位置合わせして接合することと、第1封止部と第2封止部とを接合することにより、第1ウェハ及び第2ウェハの周縁に沿って第1ウェハの底面と第2ウェハの頂面との間に封止部を形成することと、当該封止部により画定された内部領域において第1ウェハ及び第2ウェハをプラズマにより適切に切り離して個片化することとを含んでよい。封止部は、リング形状を有してよい。

20

#### 【 0 0 2 7 】

ここに記載される複数の側面及び実施形態によれば、液相拡散接合を使用することにより、電子デバイスのデバイス基板とキャップ基板とを、高温高压プロセスを必要とすることなく接合することができる。ひいては、電子デバイスを製造するサイクルタイムを低減することができる。さらに、スルーホールを形成するプロセスにおけるオーバーエッティングゆえに生じる欠陥を防止し、ひいては歩留まりを向上させることができる。

30

#### 【 0 0 2 8 】

所定の実施形態によれば、電子デバイスを製造する方法は、底面の周縁に沿って形成された第1側壁を有する第1基板を与えることであって、第1側壁は第1基板の底面に配置された電子回路を取り囲み、第1側壁は第1金属からなる第1金属層から形成されることと、頂面の周縁に沿って形成された第2側壁を有する第2基板を与えることであって、第2側壁は、第2金属からなる第2金属層と第3金属からなる第3金属層とが順に積層されることにより形成され、第2金属及び第3金属は互いに異なりかつ第1金属と異なることと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するべく、第1基板と第2基板とを位置合わせすることであって、第1側壁は第2側壁に対向かつ接触することと、液相拡散接合により第1側壁と第2側壁とを互いに接合させるべく第1基板及び第2基板を加熱することであって、第3金属層が溶融されて第1金属層及び第2金属層それぞれと第1合金層及び第2合金層を形成することとを含んでよい。

40

50

## 【0029】

所定の実施形態によれば、電子デバイスを製造する方法は、第1基板の底面の周縁に沿って第1側壁を形成して第1基板の底面に配置された電子回路を取り囲むことと、第1基板の底面と第1基板の頂面とを連通させるピアを形成することと、第2基板の頂面において周縁に沿って第2側壁を形成することと、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するべく第1側壁と第2側壁とを位置決めして接合することとを含み、当該ピアを形成することは、当該ピアに対応する第1基板の底面の一部分に第1ストップ層及び第2ストップ層を順に積層することと、当該ピアに対応するスルーホールを形成するべく第1基板をエッティングすることとを含み、第1基板をエッティングする速度は第1ストップ層をエッティングする速度よりも大きく、第1ストップ層をエッティングする速度は第2ストップ層をエッティングする速度よりも大きくてよい。

10

## 【0030】

所定の実施形態によれば、底面に配置された電子回路を取り囲むように周縁に沿って形成された第1側壁を有する第1基板と、頂面において周縁に沿って形成された第2側壁を有する第2基板とを含む電子デバイスであって、第2側壁は、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するべく、第1側壁と位置合わせされて接合される電子デバイスを製造する方法は、第1基板の底面としての第1ウェハの底面に第1側壁を形成するとともに第1ウェハの底面の周縁まわりに第1封止部を形成することと、第2基板の頂面としての第2ウェハの頂面に第2側壁を形成するとともに第2ウェハの頂面の周縁まわりに第2封止部を形成することと、第1ウェハの底面、第2ウェハの頂面、第1封止部、及び第2封止部により内部にキャビティを画定するべく、第1ウェハと第2ウェハとを互いに位置合わせして接合することとを含み、第1封止部及び第1側壁はそれぞれが、液相拡散接合により第2封止部及び第2側壁と接合されてよい。

20

## 【0031】

所定の実施形態によれば、電子デバイスは、底面の周縁に沿って形成されて当該底面に配置された電子回路を取り囲む第1側壁を有する第1基板であって、外部電極が第1基板の頂面に形成され、当該外部電極は、第1基板の底面と連通するピアを介して当該電子回路に接続される第1基板と、頂面の周縁に沿って形成された第2側壁を有する第2基板とを含み、第2側壁は、第1基板の底面、第2基板の頂面、第1側壁、及び第2側壁により内部にキャビティを画定するべく、第1側壁と位置合わせされて接合され、第1側壁は第1金属と第3金属との第1合金を含み、第2側壁は第2金属と第3金属との第2合金を含み、第1金属は、第2金属と異なりかつ第3金属とも異なってよい。

30

## 【図面の簡単な説明】

## 【0032】

少なくとも一つの実施形態の様々な側面が、縮尺どおりであることを意図しない添付図面を参照して以下に説明される。図面は、様々な側面及び実施形態の例示及びさらなる理解を与えるべく含められ、本明細書に組み入れられかつその一部を構成するが、本発明の限界を定めることは意図しない。図面において、様々な図面に例示される同一又はほぼ同一の構成要素はそれぞれが、同じ番号で表される。明確性を目的として、すべての図面においてすべての構成要素が標識されているわけではない。

40

## 【0033】

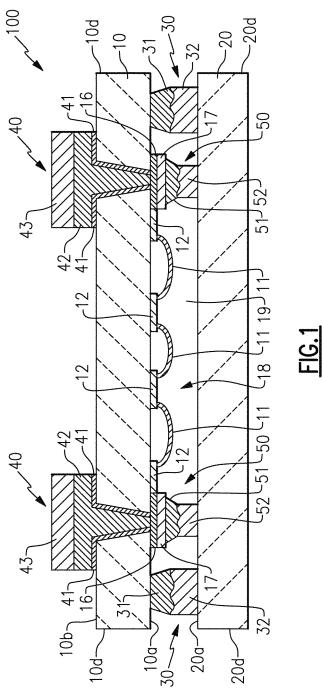

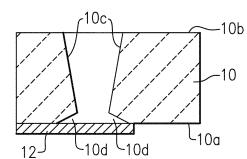

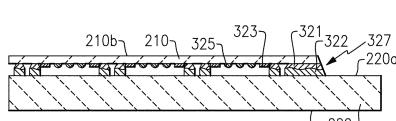

【図1】一実施形態に係る電子デバイスの模式的構成を示す断面図である。

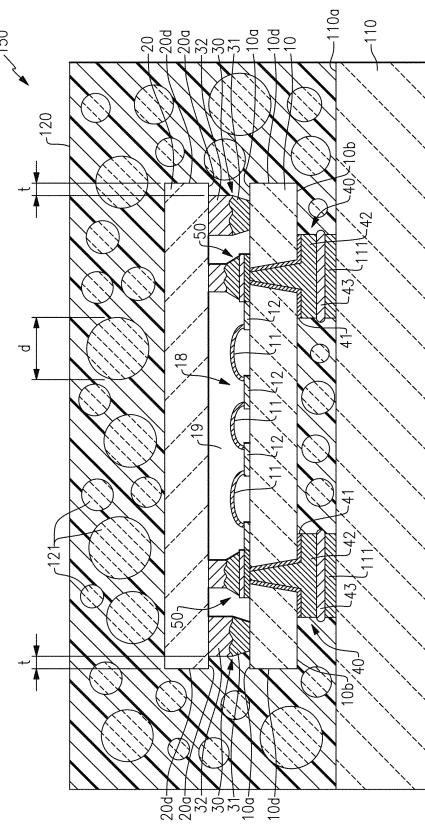

【図2】ここに記載の実施形態に係る電子デバイスがプリント基板に実装された一構造を示す断面図である。

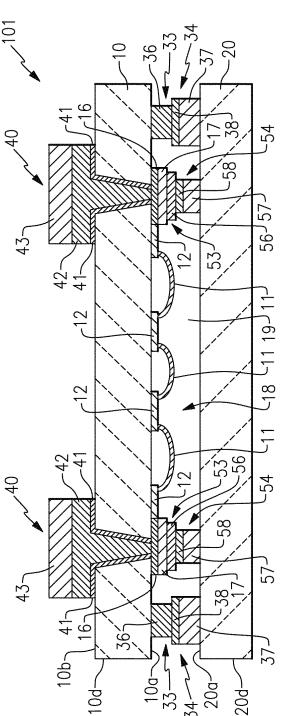

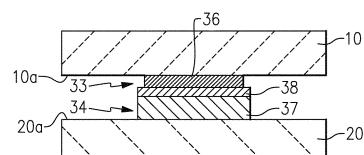

【図3】第1基板と第2基板との位置合わせを示す断面図である。

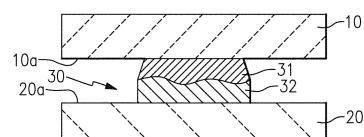

【図4】図4A～4Cは、液相拡散接合を説明する断面図である。

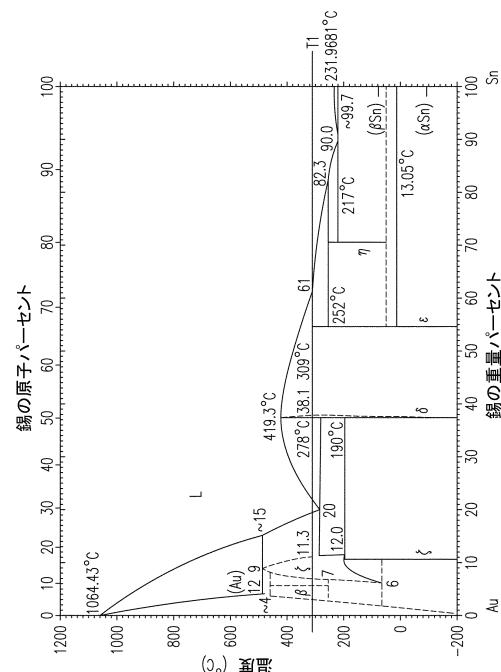

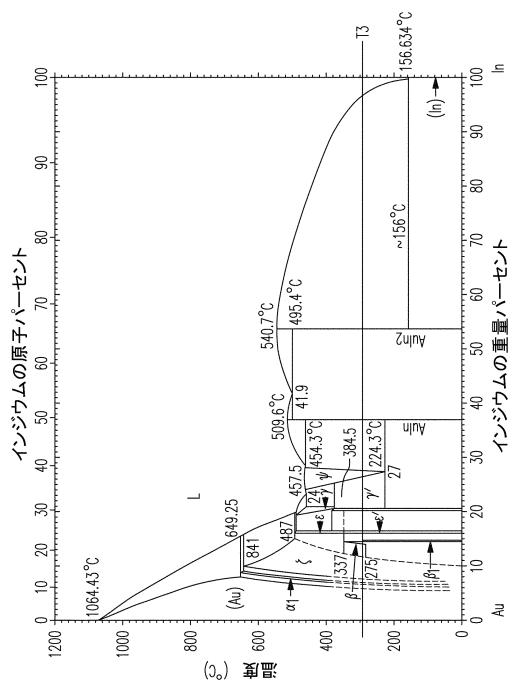

【図5A】金及び錫(Au-Sn)の状態図である。

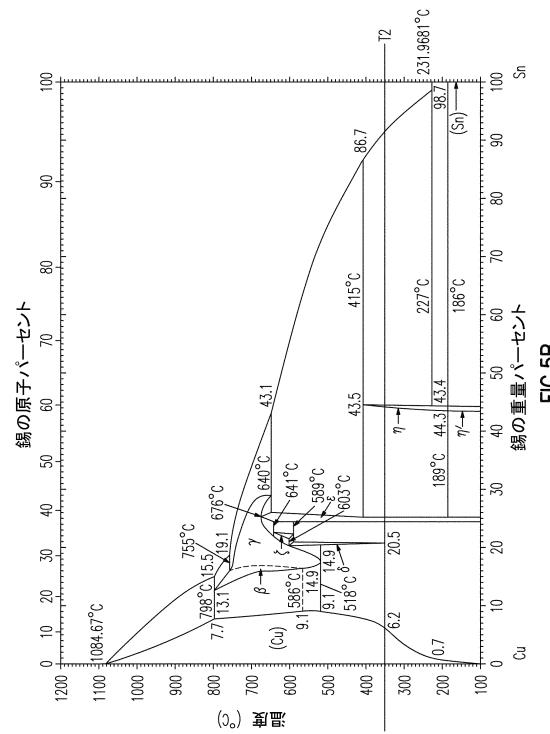

【図5B】銅及び錫(Cu-Sn)の状態図である。

【図6A】金及びインジウム(Au-In)の状態図である。

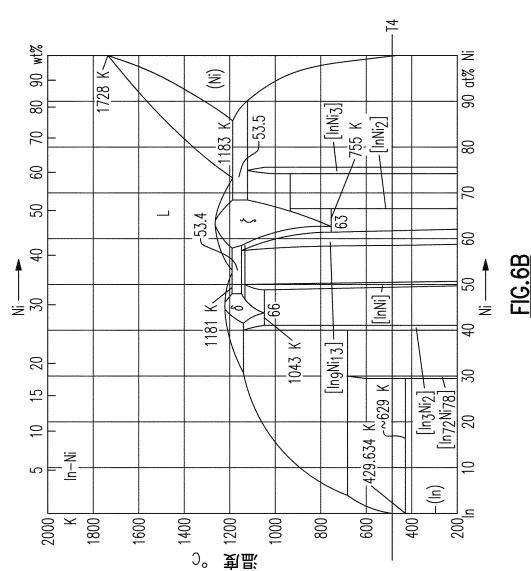

【図6B】銅及びインジウム(Cu-In)の状態図である。

50

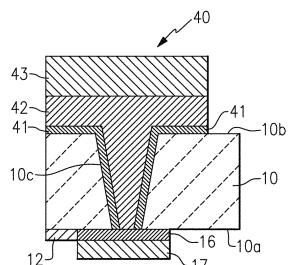

【図 7】一実施形態に係るビアのストップ層を説明する一部拡大断面図である。

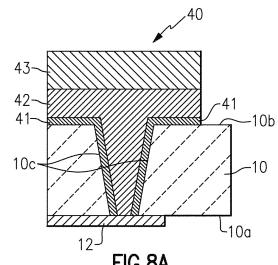

【図 8】図 8 A ~ 8 C は、従来型のビアを説明する一部拡大断面図である。

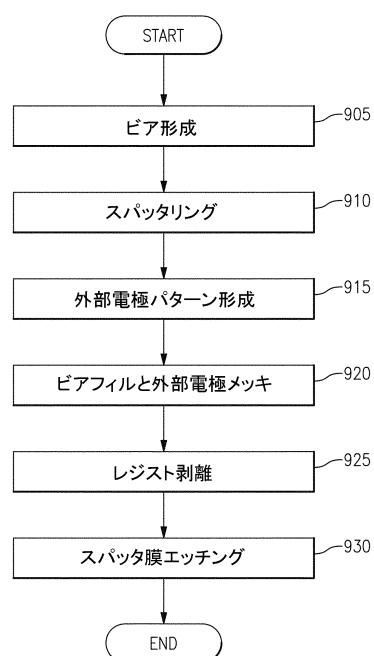

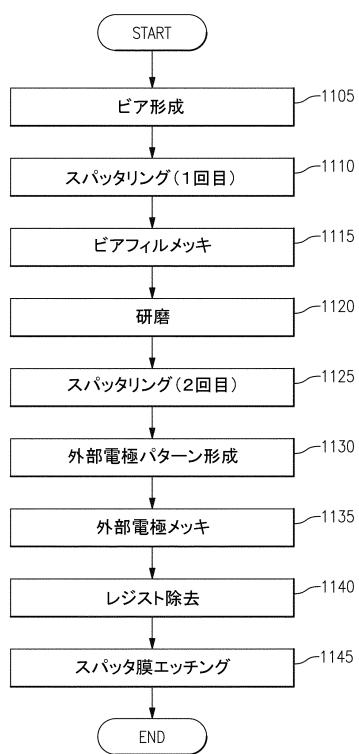

【図 9】一実施形態に係るビア及び外部電極を形成するプロセスのフローチャートである。

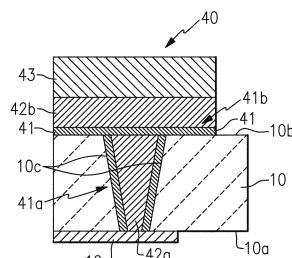

【図 10】従来型のビア及び外部電極の一構造を説明する一部拡大断面図である。

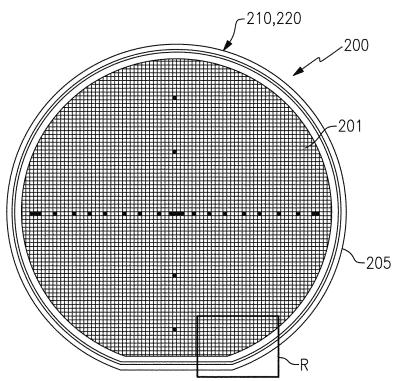

【図 11】従来型のビア及び外部電極を形成するプロセスのフローチャートである。

【図 12】図 12 A 及び 12 B は、ここに記載の実施形態に係る電子デバイスを製造する方法を説明する。

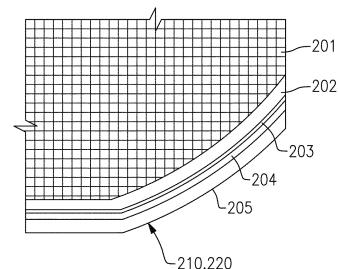

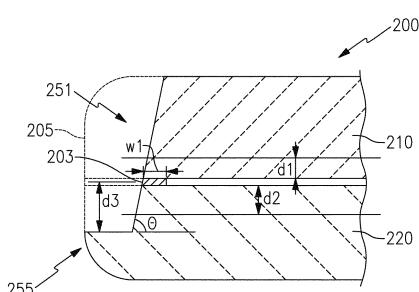

【図 13】図 13 A 及び 13 B は、エッジがトリミングされた第 1 ウェハ及び第 2 ウェハを示す断面図である。

【図 14】図 14 A 及び 14 B は、ここに記載の実施形態に係る電子デバイスを製造する方法を説明する。

10

【図 15 - 1】図 15 A ~ 15 I は、電子デバイスを製造する方法の一連のステップを説明する第 1 セットの模式図である。

【図 15 - 2】図 15 A ~ 15 I は、電子デバイスを製造する方法の一連のステップを説明する第 1 セットの模式図である。

【図 16】図 16 A ~ 16 E は、電子デバイスを製造する方法一連のステップを説明する第 2 セットの模式図である。

【図 17】図 17 A ~ 17 E は、電子デバイスを製造する方法の一連のステップを説明する第 3 セットの模式図である。

【図 18 - 1】図 18 A ~ 18 G は、電子デバイスを製造する方法の一連のステップを説明する第 4 セットの模式図である。

20

【図 18 - 2】図 18 A ~ 18 G は、電子デバイスを製造する方法の一連のステップを説明する第 4 セットの模式図である。

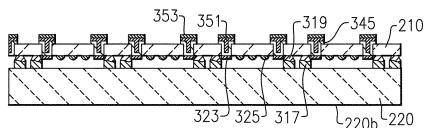

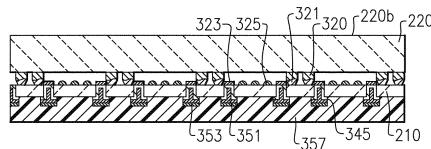

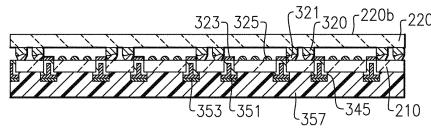

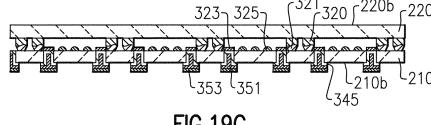

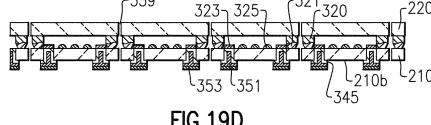

【図 19】図 19 A ~ 19 D は、電子デバイスを製造する方法の一連のステップを説明する第 5 セットの模式図である。

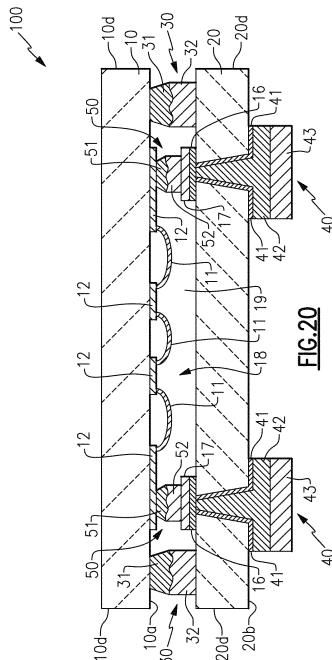

【図 20】本開示の複数の側面に係る電子デバイスの第 1 変形例の模式的構成を示す断面図である。

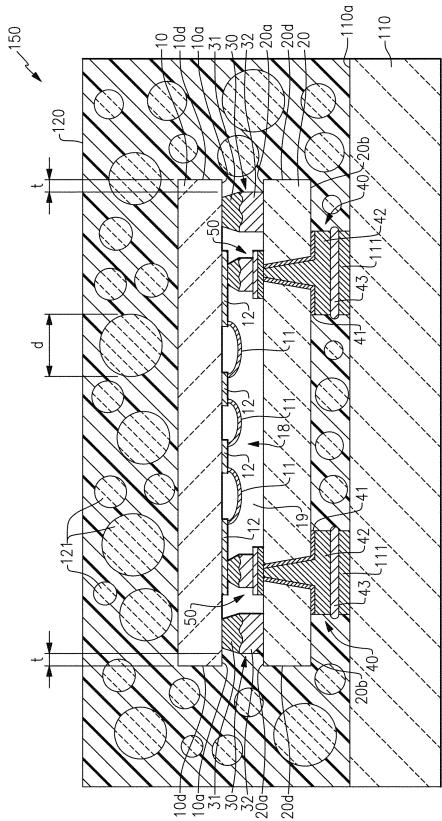

【図 21】第 1 変形例の電子デバイスがプリント基板に実装された一構造を示す断面図である。

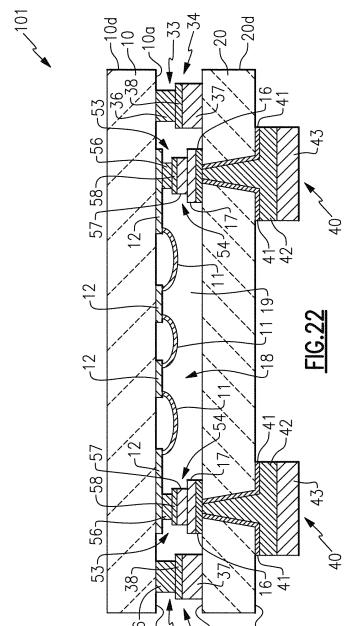

【図 22】第 1 変形例に係る第 1 基板と第 2 基板との位置合わせを示す断面図である。

30

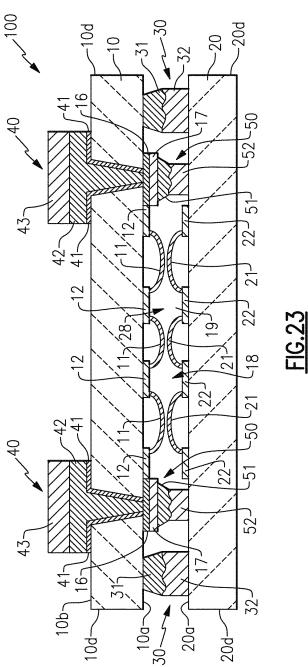

【図 23】本開示の複数の側面に係る電子デバイスの第 2 変形例の模式的構成を示す断面図である。

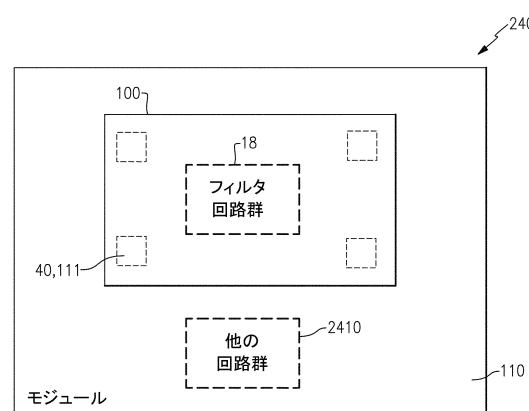

【図 24】様々な実施形態に係るフィルタ回路群を含むパッケージモジュールの一例のブロック図である。

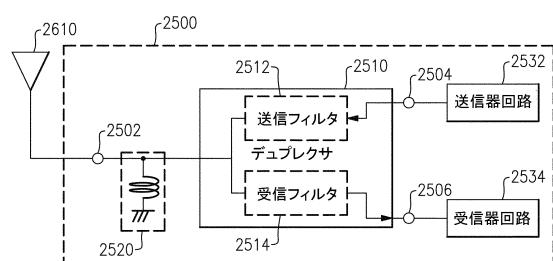

【図 25】所定の実施形態に係るフィルタ回路群の複数の例を使用して実装されたアンテナデュプレクサを含むフロントエンドモジュールの一例のブロック図である。

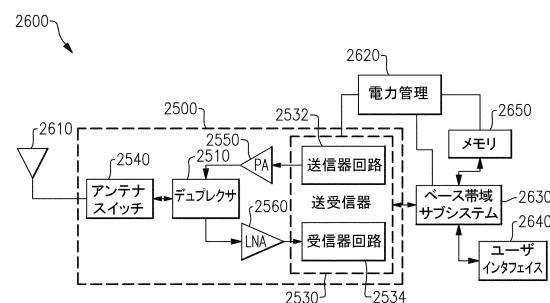

【図 26】フィルタ回路群の複数の例が様々な実施形態により使用可能な無線デバイスの一例のブロック図である。

【発明を実施するための形態】

【0034】

40

理解するべきことだが、ここで述べられた方法及び装置の実施形態は、以下の明細書に記載され又は添付図面に例示された構成要素の構造及び配列の詳細への適用に限られない。方法及び装置は、他の実施形態で実装し、様々な態様で実施又は実行することができる。特定の実装例は、例示のみを目的としてここに与えられ、限定されることを意図しない。また、ここで使用される表現及び用語は、説明目的であって、限定としてみなすべきではない。ここでの「含む」、「備える」、「有する」、「包含する」及びこれらの変形の使用は、以降に列挙される項目及びその均等物並びに付加項目の包括を意味する。「又は(若しくは)」の言及は、「又は(若しくは)」を使用して記載される任意の用語が、当該記載の用語の一つの、一つを超える、及びすべてのものを示すように解釈され得る。前後左右、頂底上下、及び横縦への言及はいずれも、記載の便宜を意図しており、本システム

50

及び方法又はこれらの構成要素がいずれか一つの位置的又は空間的配向に限られるものではない。

【 0 0 3 5 】

以下、本開示の複数の側面に係る電子デバイス及びその製造方法について図面を参照して詳細に説明する。図1は、一実施形態に係る電子デバイスの模式的構成を示す断面図である。図2は、一実施形態に係る電子デバイスがプリント基板に実装された一構造を示す断面図である。

【 0 0 3 6 】

図1に示すように、一実施形態によれば、電子デバイス100は、所定厚さを有する第1基板10と、所定厚さを有して第1基板10と所定間隔で対向する第2基板20とを含む。第1基板10はデバイス基板と称してよい。第1基板10の底面10aは第2基板20に対向し、圧電薄膜共振器(FBAR)11を含む電子回路18が設けられる。第2基板20はキャップ基板と称してよい。第2基板20の頂面20aと第1基板10の底面10aとの間には側壁30が形成されて所定間隔が画定される。第1基板10の底面10a、第2基板20の頂面20a、及び側壁30により、第1基板10の底面10aに配置された電子回路18が内部に含まれるキャビティ19が画定される。

10

【 0 0 3 7 】

電子デバイス100がプリント基板110に実装された構造150を示す図2を参照すると、図1の電子デバイス100が、ここでは上下を反転されてプリント基板110の頂面110aに配置される。プリント基板110の頂面110aには、電子デバイス100を覆う樹脂層120が配置される。この構造150において、第2基板20は、電子デバイス100の上にある樹脂層120を支持してキャビティ19を保護するキャップの役割を果たす。

20

【 0 0 3 8 】

詳しくは、第1基板10は、窒化アルミニウム(AlN)及び酸化亜鉛(ZnO)のような圧電体からなる。第1基板10の底面10aには、圧電体の薄膜により複数の圧電薄膜共振器11が形成される。圧電薄膜共振器11は配線パッド12により互いに適切に接続され、フィルタ及びフィルタデバイスのような電子回路18を形成する。なお、電子回路18が圧電薄膜共振器11を含むにもかかわらず、圧電薄膜共振器11とともに、又は圧電薄膜共振器11に代えて、弹性表面波(SAW)素子、又は音響多層膜共振器(SMR)のようなバルク弹性波(BAW)素子を使用することもできる。

30

【 0 0 3 9 】

第2基板20は、例えばシリコン又は同様の材料からなる。第2基板20は、第1基板10の底面10aと第2基板20の頂面20aとが所定間隔を介して離間されるように、第1基板10上の側壁30によって支持される。側壁30は、第1基板10の底面10aに配置された電子回路18を取り囲むように、かつ、第1基板10の周縁10d及び第2基板20の周縁20dに沿って延びるように形成される。側壁30は、第1基板10の底面10aと第2基板20の頂面20aとの間に、金(Au)及び錫(Sn)の合金からなる第1合金層31と、錫(Sn)及び銅(Cu)の合金からなり第1合金層31に積層された第2合金層32とを含む。

40

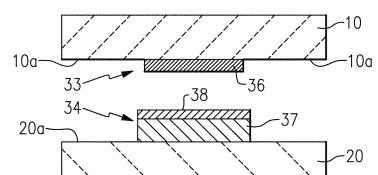

【 0 0 4 0 】

図3は、第1基板10と第2基板20との位置合わせを示す断面図である。この断面図は、第1基板10と第2基板20とが側壁30によって接合される前の状態を示す。第1基板10の底面10aにはその周縁10dに沿って第1側壁33が形成され、第2基板20の頂面20aにはその周縁20dに沿って第2側壁34が形成される。第1側壁33は、所定高さを有し、第1基板10の周縁10dから内側に所定距離だけ後退して配置される。第1側壁33は、第1厚さを有して第1金属としての金(Au)からなる第1金属層36により形成される。第2側壁34は、所定高さを有し、第2基板20の周縁20dから内側に所定距離だけ後退して配置される。第2側壁34は、第2厚さを有して第2金属としての銅(Cu)からなる第2金属層37と、第3厚さを有して第3金属としての錫(Sn)からなる第3金属層38とを含む。

50

n) からなる第3金属層38とにより形成され、第3金属層38が第2金属層37上に積層される。ここで、第1側壁33の幅は、第2側壁34の幅よりも小さい。

【0041】

第1基板10は、第1基板10の底面10a、第2基板20の頂面20a、第1側壁33、及び第2側壁34が内部にキャビティ19を画定するように、及び第1側壁33が第2側壁34に対向かつ接触するように、第2基板20に位置合わせされる。すなわち、第1側壁33の底面が第2側壁34の頂面に当接する。本開示の一側面によれば、第1基板10及び第2基板20は、位置合わせされた状態が維持されて加熱され、第1側壁33及び第2側壁34が互いに液相拡散(TLP)接合により接合されて単一の側壁30が形成される。

10

【0042】

図4A~4Cは、TLP接合を説明する一部拡大断面図である。図4A~4Cは特に、図3に示した第1基板10及び第2基板20において、第1側壁33及び第2側壁34を含む一部分を示す。図4Aは、位置合わせ前の第1基板10及び第2基板20を示す。第1基板10の底面10aには、第1厚さを有して第1金属としての金(Au)からなる第1金属層36が配置されて第1側壁33が形成される。第2基板20の頂面20aには、第2厚さを有して第2金属としての銅(Cu)からなる第2金属層37が配置され、第2金属層37には、第3厚さを有して第3金属としての錫(Sn)からなる第3金属層38が積層され、第2金属層37と第3金属層38とにより第2側壁34が形成される。

【0043】

図4Bは、第1基板10及び第2基板20が互いに位置決めされ、第1側壁33の底面と第2側壁34の頂面とが対向かつ接触することを示す。すなわち、第1側壁33の底面が第2側壁34の頂面に当接する。

20

【0044】

本開示の一側面によれば、第1側壁33及び第2側壁34が、図4Bに示すように、第1側壁33の底面と第2側壁34の頂面とが接觸した状態で加熱され、ひいてはTLP接合により互いに接合され、第1合金層31及び第2合金層32からなる側壁30が形成される。この加熱プロセスは、第1基板10及び第2基板20を240から260の温度範囲で5分から10分にわたり低圧の雰囲気に維持している間に行われる。このプロセスにより、第1側壁33の第1金属層36の第1金属としての金と、第2側壁34の第3金属層38の第3金属としての錫とに由来する金及び錫の第1合金からなる第1合金層31がもたらされる。このプロセスにより、第2金属層37の第2金属としての銅と、第2側壁34の第3金属層38の第3金属としての錫とに由来する銅及び錫の第2合金からなる第2合金層32も、もたらされる。

30

【0045】

図4Cは、第1側壁33及び第2側壁34がTLP接合によって互いに接合された状態を示す。第1側壁33及び第2側壁34はTLP接合によって接合され、第1基板10の底面10aと第2基板20の頂面20aとの間に第1合金層31及び第2合金層32が順に積層される。第1合金層31は、第1金属層36の第1金属としての金と、第3金属層38の第3金属としての錫とに由来する金及び錫の第1合金からなる。第2合金層32は、第2金属層37の第2金属としての銅と、第3金属層38の第3金属としての錫とに由来する銅及び錫の第2合金からなる。

40

【0046】

本開示の一側面によれば、第2側壁34を形成する第3金属層38の第3金属の融点は、第2金属層37の第2金属の融点よりも低い。実際のところ、第3金属としての錫の融点は、第2金属としての銅の融点よりも低い。このように、第3金属の融点を第2金属の融点よりも低くすることにより、第1側壁33と第2側壁34とを低温かつ短時間で接合することができる。ここで、低温で接合することにより、第1基板10及び第2基板20の内部に累積される加工歪み等が、望ましくない程度に高くなることが回避されるので、接合を安定して行うことができる。さらに、接合が短時間で行うことができるので、生産性

50

が向上する。

【 0 0 4 7 】

加えて、本開示によれば、第2側壁34において、第2金属層37の第2金属と第3金属層38の第3金属とが異なる。第2金属は銅でよく、第3金属は錫でよい。すなわち、第2側壁34が異なる金属からなるように構成され、第2金属層37及び第3金属層38がそれぞれ第2金属及び第3金属からなるので、合金形成開始温度及び合金形成速度が第2金属層37と第3金属層38とで異なる。したがって、第3金属層38の第3金属が、第2金属層37の第2金属よりも融点が低いことに起因して流れ出すことを抑制することができる。

【 0 0 4 8 】

さらに、本開示の複数の側面によれば、図4A及び4Bに示すように、第1金属としての金の第1金属層36により形成された第1側壁33の幅は、第2金属としての銅の第2金属層37と、第3金属としての錫の第3金属層38とにより形成された第2側壁34の幅よりも小さくなるように構成される。これにより、第1側壁33の第1金属層36において使用され得る第1金属としての高価な金の使用量が少なくなるとともに、第2側壁34の大きな幅により側壁30の強度を確保することができる。

10

【 0 0 4 9 】

図5A及び5Bは、金及び錫(Au-Sn)、並びに銅及び錫(Cu-Sn)それぞれの状態図である。これらの状態図からわかるように、第1金属としての金、第2金属としての銅、及び第3金属としての錫は融点が異なり、第3金属としての錫の融点が当該3つの金属中、最も低い。したがって、加熱により周囲温度が上昇すると、第3金属としての錫が溶融を開始し、第1金属としての金と金-錫の第1合金を形成し、その後、第2金属としての銅と銅-錫の第2合金を形成する。

20

【 0 0 5 0 】

図5Aに示す温度T1、及び図5Bに示す温度T2は、加熱の工程で予測される温度の上限を示す。これらの温度T1及びT2を上限とする領域では、所定の構成成分を有する合金の融点が一意に決まるので、合金の形成を容易に管理することができる。さらに、図5A及び5Bからわかるように、合金の形成開始温度、又は合金形成温度が、金及び錫(Au-Sn)の第1合金と、銅及び錫(Cu-Sn)の第2合金とでは異なる。したがって、3元系の溶融状態ではなく、実質的に2元系の溶融状態が重なった状態となり、合金の形成を容易に管理することができる。

30

【 0 0 5 1 】

図4Cに示すように、TLP接合により形成された側壁30は、第1合金層31及び第2合金層32を含むので、第3金属としての錫からなる第3金属層38は消費されて第1合金層31及び第2合金層32に組み入れられている。ここで、融点が低い第3金属としての錫を含まない側壁30は、300°Cを超える再溶融温度を有している。したがって、側壁30を含む電子デバイス100は、リフロー及び実装時に求められる耐熱基準を満たすことができる。

30

【 0 0 5 2 】

図3、4A又は4Bに示すように、第2側壁34の高さは、第1側壁33の高さよりも大きくなるように構成される。すなわち、第2側壁34に含まれる第2金属層37の第2厚さと第3金属層38の第3厚さとの合計が、第1側壁33に含まれる第1金属層36の第1厚さよりも大きくなるように構成される。さらに、合金形成が開始されるときの温度について、第3金属としての錫の融点は銅又は金よりも低く、第2側壁34を形成する第2金属層37の第2金属としての銅の融点は、第1側壁33を形成する第1金属層36の第1金属としての金よりも高い。したがって、第3金属層38の、融点が低い第3金属としての錫は、当該融点に到達する前に、厚さが大きく第2側壁34を形成する第2金属層37の第2金属としての銅との合金形成を開始する。加えて、第3金属層38の厚さが小さくなるように構成することで、第3金属層38の、接合中に溶融して側方に流れる第3金属としての錫の量を、第3金属としての錫が融点に到達するときの適切な温度プロファイ

40

50

ルに従って制御することができる。

【0053】

図6A及び6Bは、金及びインジウム(Au-In)、並びに銅及びインジウム(Cu-In)それぞれの状態図である。図1~5に示す実施形態において、第2側壁34を形成する第3金属層の第3金属として錫が例示されるが、インジウム(In)も第3金属として代替的に使用することができる。図6A及び6Bの状態図からわかるように、インジウムが第3金属として使用される場合、第1金属としての金、第2金属としての銅、及び第3金属としてのインジウムの融点は異なり、第3金属としてのインジウムの融点が最も低い。したがって、加熱により周囲温度が上昇すると、第3金属としてのインジウムが溶融し、第1金属としての金と金-インジウムの第1合金を形成し、その後、第2金属としての銅と銅-インジウムの第2合金を形成する。

10

【0054】

インジウムが第3金属として使用される場合、加熱プロセスは、第1基板10及び第2基板20が、170から200の温度範囲で5分から10分にわたり低圧の雰囲気に維持されている間に行われる。図6Aに示す温度T3、及び図6Bに示す温度T4は、加熱の工程で予測される温度の上限を示す。加熱された周囲温度等を除き、インジウムが第3金属層38の第3金属として使用される場合も、錫が第3金属層38の第3金属として使用された実施形態と同様である。

20

【0055】

本開示の一側面によれば、第1基板10の厚さは、第2基板20の厚さと異なる。例えば、第1基板10の厚さは第2基板20の厚さよりも大きくてよく、さらには第1基板10の厚さは第2基板20の厚さよりも小さくてよい。第1基板10の厚さは第2基板20の厚さと異なるので、図3に示すように第1側壁33及び第2側壁34が互いに位置決めされて接触した場合、第3金属層38に接触する第1金属層36の温度は、熱伝導の差に起因して、第3金属層38が積層された第2金属層37の温度とは異なる。本開示の一側面によれば、第3金属層38の第3金属としての錫は、第1金属層36の第1金属としての金、及び第2金属層37の第2金属としての銅それぞれとの合金形成の開始温度が異なるので、当該開始温度の差は、第1基板10と第2基板20との厚さの差に由来する温度の差よりも大きい。したがって、第1基板10と第2基板20との厚さの差の影響を受けることなく接合を行うことができる。

30

【0056】

図2に示すように電子デバイス100がプリント基板110に実装された構造150において、樹脂層120は、それぞれが所定の直径を有するフィラー121を含む。ここで、樹脂層120は、例えば、エポキシ樹脂からなり、フィラー121はシリカからなる。本開示の一側面によれば、第1基板10の周縁10d及び第2基板20の周縁20dから内部に後退した側壁30により画定される距離tと、フィラー121の粒径dとの間には以下の関係が存在する。

$$t = (d \text{ の平均}) / 2$$

【0057】

すなわち、第1基板10の周縁10d及び第2基板20の周縁20dから内部に後退した側壁30が画定する距離tは、樹脂層120に含まれるフィラー121の粒径の平均の半分以下である。

40

【0058】

本開示の一側面によれば、第1基板10の周縁10d及び第2基板20の周縁20dから内部に後退した側壁30が画定する距離tが、上述したフィラー121の粒径dとの関係を満たす場合、フィラー121は、第1基板10の底面10aと第2基板20の頂面20aとの間に画定された間隙内に侵入することが防止される。したがって、この間隙は、弾性率の高いフィラー121ではなく、弾性率の低い樹脂層120によって充填されるので、電子デバイス100がプリント基板110に実装された構造150の耐ヒートサイクル性を向上させることができる。さらに、本開示によれば、側壁30が第1基板10の周縁

50

10 d 及び第 2 基板 20 の周縁 20 d から所定距離 t だけ内部に後退しているので、ウェハから第 1 基板 10 及び第 2 基板 20 を個片化するダイシングプロセスにおいて金属からなる側壁 30 を切断する必要がなく、当該ダイシングプロセスを容易に行うことができる。例えば、ウェハ切断用のダイシングブレードは、金属側壁 30 を切断する必要がないので、厚さを大きく構成する必要がない。

#### 【 0 0 5 9 】

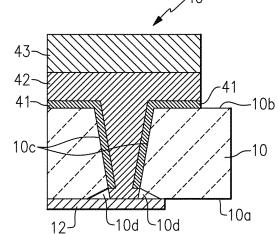

図 1 に示すように、本開示によれば、外部電極 40 が、電子デバイス 100 におけるデバイス基板として構成された第 1 基板 10 の頂面 10 b に形成される。外部電極 40 は、ビア 42 を介して第 1 基板 10 の底面 10 a に配置された電子回路 18 の配線パッド 12 に接続される。ビア 42 は、頂面 10 b 及び底面 10 a 間で第 1 基板 10 を貫通するスルーホール 10 c (図 7 参照) に形成される。外部電極 40 は、ビア 42 と、ビア 42 の頂面に配置された外部電極層 43 とを含む。本開示の一側面によれば、ビア 42 は、スルーホール 10 c に充填される金属のみで形成されるわけではなく、頂面 10 b においてスルーホール 10 c まわりの所定領域に所定厚さを有するように形成された金属層とも一体となって形成される。ここで、ビア 42 は銅メッキにより形成され、外部電極層 43 は半田メッキにより形成される。ビア 42 の一部分は、下地処理を目的として成膜されたスパッタ膜 41 の上に形成される。

#### 【 0 0 6 0 】

一実施形態によれば、外部電極 40 は、電子回路 18 が配置されるデバイス基板として構成された第 1 基板 10 に配置される。さらに、外部電極 40 は、頂面 10 b のレベルにおいてスルーホール 10 c (図 7 参照) の直上に配置される。したがって、電子回路 18 から外部電極 40 まで延びる配線の距離が短くなるように構成されるので、接続点数を減らすことができる。ひいては、フィルタ特性の挿入損失のような電子デバイスの特性を向上させることができる。

#### 【 0 0 6 1 】

さらに、図 2 に示すように電子デバイス 100 がプリント基板 110 に実装された構造 150において、電子デバイス 100 は、デバイス基板として構成された第 1 基板 10 の頂面 10 b に配置された外部電極 40 を介して電極 111 に接続される。この電極 111 は、プリント基板 110 の頂面 110 a に配置される。したがって、プリント基板 110 及び第 1 基板 10 間の距離、すなわちプリント基板 110 の頂面 110 a と第 1 基板 10 の頂面 10 b との間の距離を最小限にすることができるので、プリント基板 110 と第 1 基板 10 又はキャップ基板として構成された第 2 基板 20 との線膨張係数の差に起因して作用する応力を低減することができる。ひいては、信頼性試験における周波数変動を低減することができる。

#### 【 0 0 6 2 】

さらに、本開示に係る電子デバイスは、第 1 基板 10 を第 2 基板 20 よりも薄く構成することができる。一実施形態によれば、電子回路 18 は、スルーホール 10 c 及び外部電極 40 を含むデバイス基板として構成された第 1 基板の底面 10 a に配置されるので、図 2 に示すように実装された後の第 1 基板 10 における応力を低減することができる。その結果、第 1 基板 10 の厚さを低減するように構成することができる。第 1 基板 10 の厚さが小さくなればなるほど、スルーホール 10 c のアスペクト比も小さくなる。したがって、スルーホール 10 c に充填したビア 42 の金属と第 1 基板 10 との線膨張係数の差に由来する応力を低減し、ひいては耐ヒートサイクル性を向上させることができる。

#### 【 0 0 6 3 】

図 1 に示す実施形態の電子デバイス 100において、外部電極 40 が配置される第 1 基板 10 の頂面 10 b は、電子回路 18 が配置される底面 10 a よりも粗くなるように構成される。さらに、外部電極 40 と第 1 基板 10 の頂面 10 b との密着性を確保するために、スパッタ膜 41 が配置される。このため、第 1 基板 10 の頂面 10 b が粗く構成されるので、スパッタ膜 41 との接触面積が増えて密着強度が向上される。

#### 【 0 0 6 4 】

10

20

30

40

50

さらに、本開示の電子デバイス 100において、第1基板 10に形成されたスルーホール 10cの側面の粗さは、電子回路 18が配置された第1基板の底面 10aの粗さよりも大きい。スルーホール 10cにはビア 42を形成する金属が充填されるが、スルーホール 10cの側面が斜行するように構成されるので、成膜エネルギーが分散されて密着強度が低下することがある。本開示によれば、スルーホール 10cの粗い側面にスパッタ膜 41が成膜されるので、スパッタ膜 41とスルーホール 10cの側面との密着強度が、スパッタ膜 41と頂面 10bとの密着強度と同様に確保される。

#### 【0065】

図 1 に示す実施形態の電子デバイス 100において、第1基板 10の厚さは、電子回路 18を含んでキャビティ 19を画定する部分が、第1基板 10の底面 10aと第2基板 20の頂面 20aとが側壁 30により接続される部分よりも厚くなるように勾配がつけられてよい。勾配のついた厚さにより、第1基板 10の電子回路 18を含んでキャビティ 19を画定する部分が、プリント基板 110が実装された構造 150において、基板撓み試験等で生じる引っ張り応力に耐えることができる。

10

#### 【0066】

図 7 は、ビアのストップ層を説明する一部拡大断面図である。図 1 に示すように、電子デバイス 100において、第1基板 10の底面 10aには、ビア 42の直下に第1ストップ層 16及び第2ストップ層 17が順に積層される。第1基板 10、第1ストップ層 16及び第2ストップ層間でエッチング速度が異なる。特に、第1基板 10のエッチング速度が第1ストップ層 16のエッチング速度よりも大きい一方、第1ストップ層 16のエッチング速度は第2ストップ層 17のエッチング速度よりも大きい。

20

#### 【0067】

本開示の電子デバイス 100は、第1基板 10においてビア 42の直下に第1ストップ層 16及び第2ストップ層 17が順に積層されるように構成されるとともに、第1基板 10のエッチング速度が第1ストップ層 16のエッチング速度よりも大きく、かつ、第1ストップ層 16のエッチング速度が第2ストップ層 17のエッチング速度よりも大きくなるように構成される。その結果、ビア 42の底部において、すなわち、スルーホール 10cの側面が第1基板 10の底面 10aと交差する部分において、スルーホール 10cの形成時にオーバーエッチングによるノッチの発生を抑制することができる。これにより、ビア 42の形成時に欠陥を有することなくスルーホール 10cに金属を充填することができるの

30

#### 【0068】

ここに開示の実施形態によれば、第1基板 10のスルーホール 10cは、ドライエッチングプロセスにより形成することができる。第1基板 10のエッチング速度を第1ストップ層 16のエッチング速度よりも大きくなるように構成し、かつ、第1ストップ層 16のエッチング速度を第2ストップ層 17のエッチング速度よりも大きくなるように構成することにより、材料の広範な選択肢によるドライエッチングが可能となる。対照的に、スルーホール 10cがウェットエッチングプロセスにより形成される場合、第1基板 10のエッチング速度を第1ストップ層 16のエッチング速度よりも大きくなり、かつ、第1ストップ層 16のエッチング速度を第2ストップ層 17のエッチング速度よりも大きくなるような材料の選択は困難となる。

40

#### 【0069】

本開示によれば、第1ストップ層 16のためにチタン (Ti)、クロム (Cr) 等が使用され、第2ストップ層 17のために金 (Au) 等が使用される。これらの種類の金属を使用すると、第1基板 10のエッチング速度が第1ストップ層 16のエッチング速度よりも大きく、かつ、第1ストップ層 16のエッチング速度が第2ストップ層 17のエッチング速度よりも大きい関係を達成することができるので、ビア 42の底部におけるノッチ発生を抑制することができる。

#### 【0070】

本開示の一側面によれば、チタン又はクロムからなる第1ストップ層 16が与えられるの

50

で、第2ストップ層17を密着させるための密着層が不要となる。かかる密着層は通常、当該面と蒸着又はスパッタリングで成膜された膜との密着を目的として使用されてきたが、チタン又はクロムからなる第1ストップ層16は、密着層として機能することができる。

【0071】

本開示の一側面によれば、第1ストップ層16は第2ストップ層17よりも薄い。第1ストップ層16の厚さを低減することにより、第1ストップ層16をエッティングするときのエッティング速度の低下に起因する面内でのエッティング状態のばらつきを防止することができる。すなわち、第1ストップ層16がエッティングによりスルーホール10cの底面から完全に除去され得ることを保証することができるので、第1ストップ層16が部分的に残存することがなくなる。さらに、第2ストップ層17の厚さを大きくすることにより、エッティング後に第2ストップ層17の強度を確保することができる。エッティングが完了すると、スルーホール10cの底面には、薄くなつた第2ストップ層17が残存する。

【0072】

図1及び7に示すように、第1ストップ層16及び第2ストップ層17が第1基板10の底面10aにおいてビア42の直下に配置されるが、第1ストップ層16及び第2ストップ層17は、第1基板10の底面10aに配置された電子回路18の配線パッド12を覆うように拡張されてよい。さらに、第1ストップ層16及び第2ストップ層17は、電子回路18の配線パッド12の代替として、使用することができる。第1ストップ層16及び第2ストップ層17は、配線パッド12よりも厚さが大きいので、配線抵抗を下げることができる。したがって、第1ストップ層16及び第2ストップ層17を配線パッド12の上まで拡張したり配線パッド12のために使用することができるので、電子デバイス100の挿入損失を低減することができる。

【0073】

図8A～8Cは、比較例として、底にストップ層が存在しない従来型のビアを説明する一部拡大断面図である。図8Aに示すように、電子回路18の配線パッド12は、ビア42の直下の位置まで延ばされ、ストップ層の介在なしにビア42に接続される。図8Bに示すこのような従来型の構成によれば、エッティングにより第1基板10にスルーホール10cが形成されるとき、スルーホール10cの側面が底面10aと交差する部分において、オーバーエッティングによりノッチ10dが発生することがある。図8Cに示すように、底部に生じたノッチ10dを含むスルーホール10cに金属を充填してビア42を形成すると、金属がノッチ10dの部分に入らずに不十分な金属の欠陥がもたらされる場合があり、ひいては電子デバイス100の歩留まりが低下することができる。

【0074】

図1に示す実施形態の電子デバイス100は、第1基板10の底面10aと第2基板20の頂面20aとの間ににおいてビア42の直下に形成された柱50を含む。柱50の直径は、ビア42の直径よりも大きくなるように構成される。第1基板10の底面10aと柱50との間には、第1ストップ層16及び第2ストップ層17が介在される。側壁30と同様、柱50も、金-錫の合金からなる第1合金層51と、錫-銅の合金からなる第2合金層52とが順に積層されることにより形成される。

【0075】

図3に示すように第1基板10及び第2基板20が位置合わせされると、第1基板10の底面10aにはビア42の直下に第1柱53が配置され、第1基板10の頂面20aには第1柱53に対応する箇所に第2柱54が配置される。第1柱53は、第1金属としての金からなる第1厚さを有する第1金属層56によって形成される。第2柱54は、第2金属層57及び第3金属層58が順に積層されることによって形成される。第2金属層57は、第2金属としての銅からなり、第2厚さを有する。第3金属層58は、第3金属としての錫からなり、第3厚さを有する。ここで、第1柱53の直径は、第2柱54の直径よりも大きい。

【0076】

図3に示すように、第1基板10及び第2基板20が互いに位置合わせされ、第1基板1

10

20

30

40

50

0 の底面 10 a、第 2 基板 20 の頂面 20 a、第 2 側壁 34、及び第 1 側壁 33 が内部にキャビティ 19 を画定する。第 1 側壁 33 及び第 2 側壁 34 が互いに対向かつ接触する一方、第 1 柱 53 及び第 2 柱 54 が互いに対向かつ接触する。すなわち、第 1 柱 53 の底面と第 2 柱 54 の頂面とが当接する。本開示の一側面によれば、第 1 基板 10 及び第 2 基板 20 は、位置合わせされかつ加熱された状態に維持され、液相拡散 (TLP) 接合により第 1 側壁 33 及び第 2 側壁 34 が互いに接合されて単一の側壁 30 となり、第 1 柱 53 及び第 2 柱 54 も TLP 接合により互いに接合されて単一の柱 50 となる。第 1 柱 53 及び第 2 柱 54 に適用される TLP 接合プロセスは、図 4 に示す第 1 側壁 33 及び第 2 側壁 34 の TLP 接合プロセスと同様である。

## 【0077】

10

図 2 に示すように電子デバイス 100 がプリント基板 110 に実装された構造 150 によれば、プリント基板 110 の頂面 110 a と電子デバイス 100 との間に樹脂層 120 が介在される。構造 150 に対してヒートサイクル試験が行われると、プリント基板 110 と電子デバイス 100 との間に介在する樹脂層 120 が膨張及び収縮することによりビア 42 に対する引っ張り応力が発生する。本開示によれば、ビア 42 よりも直径が大きい柱 50 が、ビア 42 の直下に配置される。したがって、かかる引っ張り応力及びヒートサイクルによりもたらされるビア 42 への影響に耐える強度が確保され、信頼性を向上させることができる。例えば、ビア 42 と第 1 ストップ層 16、第 2 ストップ層 17 又は配線パッド 12 の間の金属疲労による断線を防止することができる。

## 【0078】

20

さらに、本開示によれば、第 1 金属としての金からなる第 1 金属層 56 により形成された第 1 柱 53 の直径は、第 2 金属としての銅からなる第 2 金属層 57 と、第 3 金属としての錫からなる第 3 金属層 58 とにより形成された第 2 柱 54 の直径よりも大きい。TLP 接合により、融点の低い第 3 金属層 58 の第 3 金属としての錫が、第 1 金属層 56 の第 1 金属としての金の側に濡れ広がり、金 - 錫合金からなる第 1 合金層 51 の断面が、なだらかなテーパー状になる。したがって、第 1 基板 10 の底面 10 a と柱 50 とが交差する部分における応力集中を回避することができるので、さらに信頼性を向上させることができる。

## 【0079】

さらに、本開示の複数の側面によれば、スルーホール 10 c は、レーザによって第 1 基板 10 に形成することができる。図 1 に示すように、一実施形態によれば、柱 50 は、第 1 ストップ層 16 及び第 2 ストップ層 17 が介在されてスルーホール 10 c の底部に配置される。したがって、スルーホール 10 c がレーザにより形成されるときに第 1 ストップ層 16 及び第 2 ストップ層 17 がスルーホール 10 c の底部から加熱されても、第 1 ストップ層 16 及び第 2 ストップ層 17 の直下に接続された柱 50 によって熱が速やかに散逸されるので、第 1 ストップ層 16 及び第 2 ストップ層 17 は熱から保護される。したがって、スルーホール 10 c を形成するときにウェットエッチング又はドライエッチングによつては加工が困難なタンタル酸リチウム、ニオブ酸リチウム、サファイア、ガラス等も、レーザにより加工される第 1 基板 10 の材料として使用することができる。

## 【0080】

30

図 1 に示すように、電子デバイス 100 は、第 1 基板 10 の底面 10 a、第 2 基板 20 の頂面 20 a、及び側壁 30 により内部に画定されたキャビティ 19 を有する。本開示の一側面によれば、キャビティ 19 は、窒素又は空気が充填されて 1 気圧よりも低い圧力の雰囲気に維持される。キャビティ 19 を 1 気圧よりも低い気圧の雰囲気に維持することにより、電子回路 18 の圧電薄膜共振器 11 がキャビティ 19 内で振動するときに作用する空気抵抗を低減することができるので、Q 値を確保して良好な特性を実現することができる。

## 【0081】

本開示の一側面によれば、第 1 基板 10 及び第 2 基板 20 が図 3 に示すように位置合わせされた状態のまま、第 1 側壁 33 及び第 2 側壁 34 は、真空下で TLP 接合により接合される。したがって、TLP 接合プロセス中に第 1 側壁 33 及び第 2 側壁 34 が加熱されても、第 1 側壁 33 を形成する第 1 金属層 36 の第 1 金属としての金、並びに第 2 側壁 34

40

50

を形成する第2金属層37の第2金属としての銅、及び第3金属層38の第3金属としてのインジウムの、酸化及び窒化を防止することができる。酸化防止が本開示のTLP接合にとって有利なのは、第2金属層37の第2金属としての銅が酸化されると、図1に示す側壁30の第2合金層32に、銅及び錫からなる第2合金が形成できなくなるからである。

#### 【0082】

なおもさらに、本開示の複数の側面によれば、図3に示すように位置合わせされた第1基板10及び第2基板20は、低圧コントロールバルブにより適切な真空度に維持され得る適切なチャンバに格納してもよい。これにより、電子デバイス100のキャビティ19の内部を、適切な真空度に設定することができ、ひいては第1基板10と第2基板20とのTLP接合を確実に実現することができる。またなおもさらに、図3Aに示す位置合わせ状態にある第1基板10と第2基板20とのTLP接合に先立って、100以下10

の温度で予備加熱プロセスが行われる。予備加熱プロセスは、予備加熱温度が100以下に設定されるので、第2側壁34を形成する第3金属層38の第3金属としての低融点のインジウムでさえ溶融させることができない。加えて、第2側壁34における第2金属層37の第2金属としての銅もまた、酸化が防止され得る。したがって、図1に示す側壁30の第2合金層32の銅-錫からなる第2合金の形成が阻害されることはない。

#### 【0083】

図1に示すように、電子デバイス100は、互いに一体に形成された外部電極40及びビア42を有する。ビア42は、第1基板10の頂面10b及び底面10a間を貫通するスルーホール10cに充填された金属によるのみでなく、スルーホール10cまわりの所定領域において頂面10bに所定厚さを有するように形成された金属層によっても一体に形成される。外部電極層43はビア42上に配置される。20

#### 【0084】

図9は、本開示に係るビア及び外部電極を形成する一連のステップを示すフローチャートである。ステップ905において、第1基板10の底面10a及び頂面10b間を貫通するようにスルーホール10cが形成される。スルーホール10cの形成は、例えば、レーザ、ドライエッチング、又はウェットエッチングによってもよい。ステップ910において、第1基板10の頂面10b及びスルーホール10cの側面にスパッタ膜41が形成される。ここで、スパッタ膜41は、メッキによる金属の密着を可能にする。ステップ915において、ネガ型液体レジストが使用されて外部電極40のレジストパターンが形成される。30

#### 【0085】

ステップ920において、スパッタ膜41に銅がメッキされる。これにより、銅が、スルーホール10cの中に充填されるとともに、第1基板10の頂面10bにおけるスルーホール10cまわりの所定領域に金属層としてもメッキされ、ビア42が形成される。さらに、ビア42の頂面には、外部電極層43が半田メッキにより所定厚さを有するように形成される。ビア42及び外部電極層43によって外部電極40が構成される。ステップ925において、ステップ915で形成されたレジストが除去される。ステップ930において、外部電極40が形成された領域を除き、第1基板10の頂面10bからスパッタ膜41が除去される。40

#### 【0086】

一実施形態によれば、第1基板10のスルーホール10cに充填された金属と、外部電極層43を支持するべく第1基板10の頂面10bでスルーホール10cまわりの所定領域に形成された金属層とが一体となってビア42を形成する。したがって、ビア42が、第1基板10の頂面10bに配置された外部電極40の外部電極層43と、第1基板10の底面10aに配置された第1ストップ層16、第2ストップ層17又は配線パッド12とを直接的に接続するので、電子デバイスの接続抵抗ひいては挿入損失を低下させることができる。

#### 【0087】

さらに、本開示の一側面によれば、ネガ型液体レジストを使用して外部電極40のパター

10

20

30

40

50

ンが形成される。したがって、スルーホール 10c の中へのレジストの流れ込みを防止することにより、外部電極 40 をパターニングすることができる。この防止は、スルーホール 10 の直径及び深さ、すなわちビア 42 の体積、レジストの粘度、並びに / 又はレジストのプリベーカー時間を制御することによって達成することができる。

#### 【0088】

図 10 は、比較例としての従来型のビア及び外部電極の一構造を説明する一部拡大断面図である。従来型のビアは、第 1 スパッタ膜 41a が介在されて第 1 基板 10 のスルーホール 10c に形成された金属充填部 42a を含む。従来型の外部電極 40 は、外部電極支持層 42b 及び外部電極層 43 を含む。第 1 基板 10 の頂面 10b には、第 2 スパッタ膜 41b が介在されて外部電極支持層 42b が形成される。外部電極支持層 42b には外部電極層 43 が形成される。従来型のビアの金属充填部 42a と、外部電極 40 の外部電極支持層 42b とは、既に述べた実施形態にかかる外部電極 40 のビア 42 と同様に銅メッキによって形成されるが、金属充填部 42a と外部電極支持層 42b との間に第 2 スパッタ膜 41b が介在される点が異なる。

#### 【0089】

図 11 は、従来型のビア及び外部電極を形成する一連のステップを示すフローチャートである。ステップ 1105 において、第 1 基板 10 にスルーホール 10c が形成される。ステップ 1110 において、1 回目のスパッタリングにより、スルーホール 10c の側面を含む領域を覆うように第 1 スパッタ膜 41a が形成される。ステップ 1115 において、スルーホール 10c の第 1 スパッタ膜 41a には、銅メッキにより金属充填部 42a が形成される。ステップ 1120 において、第 1 基板 10 の頂面 10b が研磨され、頂面 10b に形成された銅メッキ部分及び第 1 スパッタ膜 41a が除去される。

#### 【0090】

ステップ 1125 において、2 回目のスパッタリングにより、金属充填部 42a を含む第 1 基板 10 の頂面 10b に第 2 スパッタ膜 41b が形成される。ステップ 1130 において、フォトリソグラフィーにより外部電極 40 のレジストパターンが形成される。ステップ 1135 において、銅メッキにより外部電極支持層 42b が形成され、半田メッキにより外部電極層 43 が形成される。ステップ 1140 において、レジストが除去される。ステップ 1145 において、外部電極 40 が形成された部分を除き、第 1 基板 10 の頂面 10b から第 2 スパッタ膜 41b が除去される。

#### 【0091】

図 10 に示す従来型のビア及び外部電極 40 、並びに図 11 に示す従来型のビア及び外部電極 40 を製造する方法によれば、金属充填部 42a 及び外部電極支持層 42b が別個のステップにより形成されるので、金属充填部 42a と外部電極支持層 42b との間に第 2 スパッタ膜 41b が介在される。このため、工数が増加するとともに、第 2 スパッタ膜 41b が介在することにより金属充填部 42a と外部電極層 43 との間の接続抵抗が増加する。

#### 【0092】

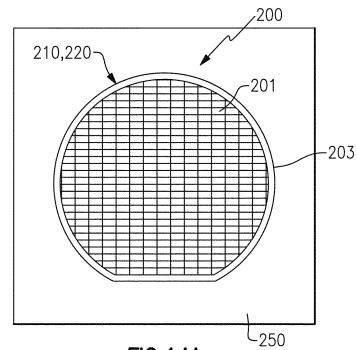

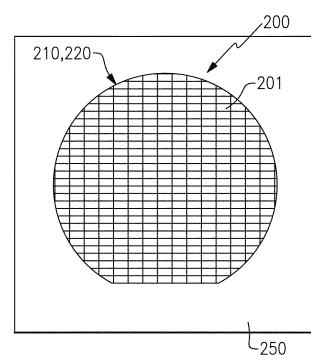

図 1 及び 2 への参照、並びに図 13A 及び 13B への参照に引き続き、図 12A 及び 12B は、本開示に係る電子デバイスを製造する方法を例示する。図 12A は、電子デバイス 100 を形成するべく配列された複数の第 1 基板 10 を有する第 1 ウェハ 210 と、同じ電子デバイス 100 を形成するべく配列された複数の第 2 基板 20 を有する第 2 ウェハ 220 とを含む構造 200 を示し、第 1 ウェハ 210 と第 2 ウェハ 220 とは互いに位置合わせされて TLP 接合により接合される。換言すれば、図 12A は、図 1 に示す電子デバイス 100 が、第 1 ウェハ 210 及び第 2 ウェハ 220 から未だ個片化されておらず、複数の電子デバイス 100 が互いに結合されている状態を示す。

#### 【0093】

図 12B は、実質的に円形状の第 1 ウェハ 210 及び第 2 ウェハ 220 を含む構造 200 を示す図 12A におけるボックス領域 R の一部拡大図である。図 12A 及び 12B に示すように、電子デバイス 100 の構成が形成された部分が有効エリア 201 に対応する。有

10

20

30

40

50

効エリア 201 から外側において周縁 205 に沿って所定幅の無効エリア 202、リング状の封止部 203、及びメッキ給電部 204 が順に形成される。

【0094】

本開示によれば、封止部 203 は、第 1 基板 10 の底面 10a に配置された第 1 側壁 33、及び第 2 基板 20 の頂面 20a に配置された第 2 側壁 34 と同様に構成される。すなわち、第 1 ウェハの底面 210 には周縁 205 に沿って第 1 封止部が形成され、第 2 ウェハの頂面 220 において第 1 封止部に対応する部分には第 2 封止部が形成される。第 1 封止部は、第 1 金属としての金からなり第 1 厚さを有する第 1 金属層を含む。第 2 封止部は、第 2 金属としての銅からなり第 2 厚さを有する第 2 金属層と、第 3 金属としての錫からなり第 3 厚さを有する第 3 金属層とが、順に積層されて構成される。

10

【0095】

第 1 ウェハ 210 と第 2 ウェハ 220 とを互いに位置合わせして TLP 接合により接合するとき、図 3 に示すように第 1 基板 10 及び第 2 基板 20 が位置合わせされる場合と同様、第 1 側壁 33 及び第 2 側壁 34 が互いに対向かつ接触するように位置合わせされる一方、第 1 封止部及び第 2 封止部は互いに対向かつ接触するように位置合わせされ、第 1 ウェハ 210 に形成された第 1 側壁 33 と第 2 ウェハ 220 に形成された第 2 側壁 34 によりキャビティ 19 が内部に画定される。すなわち、第 1 封止部の底面と第 2 封止部の頂面とが当接する。第 1 ウェハ 210 及び第 2 ウェハ 220 はその後、位置合わせされた状態で加熱されると、第 1 側壁 33 及び第 2 側壁 34 が TLP 接合により接合されて单一の側壁 30 を形成する一方、第 1 封止部及び第 2 封止部が TLP 接合により接合されて单一の封止部 203 を形成する。第 1 封止部及び第 2 封止部の TLP 接合プロセスは、図 4A～4C に示す第 1 側壁 33 及び第 2 側壁 34 の TLP 接合プロセスと同様である。

20

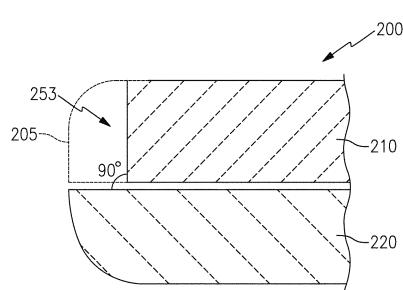

【0096】

図 13A は、第 1 ウェハ 210 及び第 2 ウェハ 220 が互いに接合された構造 00 にエッジトリミングが施された状態を説明する断面図である。図 13A に示すように、第 1 ウェハ 210 及び第 2 ウェハ 220 が互いに接合された構造 200 は、周縁 205 から、リング状の封止部 203 が形成された位置まで研削される。ここで、封止部 203 は、第 1 ウェハの底面 210 又は第 2 ウェハの頂面 220 に沿って、例えば 150 μm の長さ w1 が確保されるように加工される。研削により加工された斜面 251 は、第 1 ウェハの底面 210 又は第 2 ウェハの頂面 220 に対して、例えば 60 度の角度をなす。さらに、エッジトリミングによる斜面 251 は、第 2 ウェハの頂面 220 から深さ d3 まで形成され、深さ d3 を超えるフランジ部 255 は残される。深さ d3 は、例えば 210 μm である。

30

【0097】

図 13A に示すように、第 1 ウェハ 210 及び第 2 ウェハ 220 が接合されて構造 200 となるが、構成 200 がエッジトリミングされて斜面 251 が形成された後、第 1 ウェハ 210 は、厚さ d1 が達成されるまで頂面から研磨される。厚さ d1 は、例えば 70 μm である。第 2 ウェハ 220 は、厚さ d2 が達成されるまで底面から研磨される。厚さ d2 は、例えば 110 μm である。この研磨加工の間にフランジ部 255 は、研削されて除去される。

40

【0098】

上述した製造方法により、第 1 ウェハ 210 及び第 2 ウェハ 220 が互いに接合された構造 200 は、周縁 205 からリング状の封止部 203 まで研削によりエッジトリミングされる。第 1 ウェハ 210 及び第 2 ウェハ 220 は封止部 203 により支持されるので、第 1 ウェハ 210 及び第 2 ウェハ 220 が薄くなるように研磨されるときでも、第 1 ウェハ 210 及び第 2 ウェハ 220 が破壊されることがない。

【0099】

さらに、上述した製造方法によれば、第 1 ウェハ 210 及び第 2 ウェハ 220 が互いに接合された構造 200 は、エッジトリミングにより形成されて、第 1 ウェハの底面 210 又は第 2 ウェハの頂面 220 に対し、例えば 60 度の角度を有する斜面 251 を含む。封止部 203 が斜面 251 で露出するので、メッキ用のシード層を、斜面 251 に沿って周

50

縁 2 0 5 から第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 の中心まで連続して、低抵抗で成膜することができる。

#### 【 0 1 0 0 】

ここで、角度  $\theta$  を 90 度未満に構成することにより、斜面 2 5 1 上の封止部 2 0 3 の露出面積が大きくなるので、当該低抵抗に寄与し得る。しかしながら、角度  $\theta$  が小さくなりすぎると、封止部 2 0 3 がウェハの中に入り込むので有効エリア 2 0 1 が狭まり、結果的に、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 からダイシングして取り出せる電子デバイスの数が減少し得る。したがって、ダイシングして取り出せる電子デバイスの数の低下を防止し、かつ、メッキ用のシード層の低抵抗を確保するべく、角度  $\theta$  は  $60 \pm 20$  度又は  $60 \pm 10$  度とすることができる。

10

#### 【 0 1 0 1 】

さらに、上述した製造方法によれば、エッジトリミングにより形成された斜面 2 5 1 は、封止部 2 0 3 を含む。したがって、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が薄くなるように研磨するか又はウェットプロセスに投入するとき、封止部 2 0 3 は、第 1 ウエハの底面 2 1 0 と第 2 ウエハの頂面 2 2 0 とにより画定されるキャビティへの水の侵入を阻止することができる。なおもさらに、第 2 ウエハの底面 2 2 0 が研磨されるとき、第 2 ウエハ 2 2 0 の周縁 2 0 5 に沿って形成されたフランジ部 2 5 5 を、同時に研削して除去することができる。

#### 【 0 1 0 2 】

図 1 3 B は、比較例として、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が互いに接合された構造 2 0 0 が、従来型の製造方法によりエッジトリミングが施された状態を説明する断面図である。従来型の製造方法では、第 1 ウエハ 2 1 0 はエッジトリミングにより研削され、第 1 ウエハの底面 2 1 0 又は第 2 ウエハの頂面 2 2 0 に対して 90 度をなす垂直面 2 5 3 が形成される。第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が互いに接合されてエッジトリミングされた構造 2 0 0 は、第 1 ウエハの底面 2 1 0 と第 2 ウエハの頂面 2 2 0 との間に封止部 2 0 3 を含まない。このため、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が互いに接合された構造では、第 1 ウエハの頂面 2 1 0 又は第 2 ウエハの底面 2 2 0 を研磨するか又はウェットプロセスに投入するとき、第 1 ウエハの底面 2 1 0 と第 2 ウエハの頂面 2 2 0 との間のギャップに水が浸入することがある。

20

#### 【 0 1 0 3 】

図 1 4 A 及び 1 4 B は、本開示のさらなる側面に係る電子デバイスを製造する方法を説明する。図 1 4 A に示すように、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が位置合わせされて接合された構造 2 0 0 は、裏面研削保護テープ 2 5 0 に貼り付けられて固定される。ここで、構造 2 0 0 は図 1 2 A に示すようになる。詳しくは、電子デバイス 1 0 0 を形成するべく配列された複数の第 1 基板 1 0 を有する第 1 ウエハ 2 1 0 と、同じ電子デバイス 1 0 0 を形成するべく配列された複数の第 2 基板 2 0 を有する第 2 ウエハ 2 2 0 とが、互いに位置合わせされて接合される。第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 は、周縁 2 0 5 に沿ってリング状の封止部 2 0 3 により接合される。この接合は T L P 接合により行われるが、適切な接合を達成するべく他のオプションを使用することもできる。例えば、有機樹脂による接着を使用することができる。

30

#### 【 0 1 0 4 】

本開示によれば、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が封止部 2 0 3 で接合された構造 2 0 0 が、プラズマダイシングビフォアグラインディング (Dicing - Before - Grinding (DBG)) 技術を使用してダイシングされ、別個の電子デバイス 1 0 0 のチップに個片化される。詳しくは、第 1 ウエハ 2 1 0 及び第 2 ウエハ 2 2 0 が封止部 2 0 3 で接合された構造 2 0 0 に電子デバイス 1 0 0 の複数のチップが形成された有効エリア 2 0 1 が、第 1 ウエハの頂面 2 1 0 から適切な深さまで、プラズマによりダイシングされる。その後、裏面研削保護テープ 2 5 0 が剥離され、他の裏面研削保護テープが第 1 ウエハの頂面 2 1 0 に貼り付けられる。引き続き、第 2 ウエハの底面 2 2 0 が適切な深さまで研磨されて別個のチップが形成される。当該頂面から裏面研削保護テープが剥離

40

50

されて構造 200 が分離されて個片化されることにより、最終製品としての電子デバイス 100 を得ることができる。

【0105】

本開示の一側面によれば、第 2 ウェハの底面 220 が研磨された後であっても、リング状の封止部 203 の剛性ゆえに、第 1 ウェハ 210 及び第 2 ウェハ 220 の形状を維持することができる。したがって、研磨プロセス中にチップが研磨抵抗を受けて動くことが防止されるので、互いに隣接して配列されたチップが、チッピングを引き起こすことがなくなり、ひいては損傷なく電子デバイス 100 を分離することができる。したがって、ダイシングされる隣接チップ同士間の幅を狭くすることができるので、有効エリア 201 内で得られるチップの数を最大化することができる。

10

【0106】

図 14B は、比較例として、従来型のダイシングプロセスを説明する。従来、周縁 205 に沿って封止部 203 を固定することなく第 1 ウェハ 210 及び第 2 ウェハ 220 を含む構造 200 は、裏面研削保護テープ 250 に接着され、電子デバイス 100 の複数のチップが有効エリア 201 から切り出されていた。ウェハは、ダイヤモンド砥石を使用したメカニカルな研磨及びダイシング技術によって薄膜化されていた。かかる従来型のメカニカルな研磨及びダイシング技術は、チッピング、チップ割れ及びウェア割れを引き起こし、歩留まり及び生産性が低下し得る。

20

【0107】

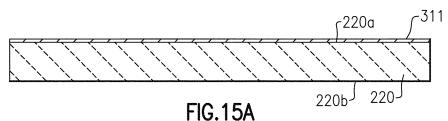

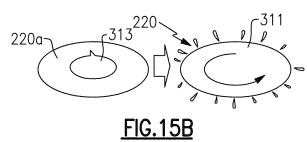

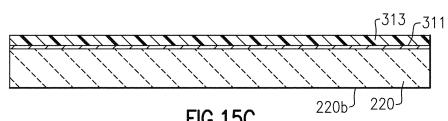

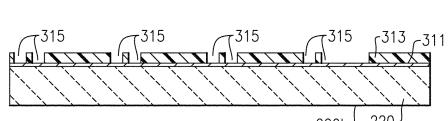

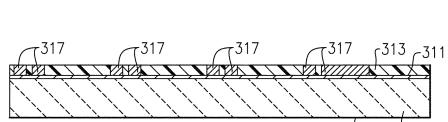

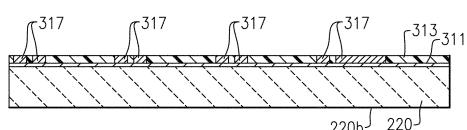

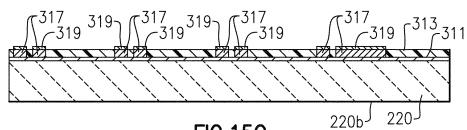

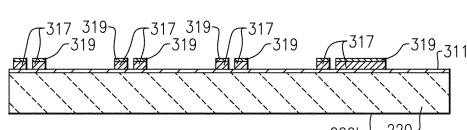

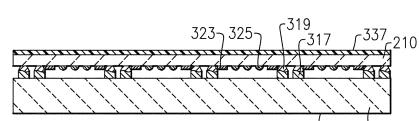

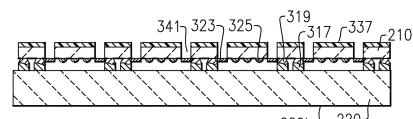

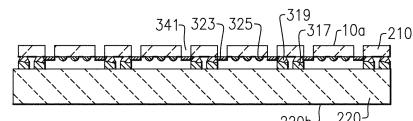

図 15A～15I は、本開示の複数の側面に係る電子デバイスを製造する方法の一連のステップを説明する。図 15A に示すように、第 2 ウェハ 220 が用意され、第 2 ウェハ 220 の頂面 220a にスパッタ膜 311 が形成される。図 15B に示すように、第 2 ウェハ 220 上に形成されたスパッタ膜 311 に、スピンドルコーティングによりレジスト 313 が塗布される。図 15C に示すように、レジスト 313 が塗布された第 2 ウェハ 220 は、露光されて所定パターンが転写される。図 15D に示すように、露光された第 2 ウェハ 220 に露光後ベーク (PEB) 及び現像が施される。これにより、レジスト 313 から所定部分が除去され、凹部 315 が形成される。図 15E に示すように、凹部 315 には銅メッキ 317 が形成される。図 15F に示すように、レジスト 313 及び銅メッキ 317 が研磨されて表面が平坦にされる。図 15G に示すように、銅メッキ 317 の上には錫メッキ 319 が施される。図 15H に示すように、レジスト 313 が除去される。図 15I に示すように、さらにスパッタ膜 311 が除去される。図 15I からわかるように、第 2 金属としての銅からなる第 2 金属層と、第 3 金属としての錫からなる第 3 金属層とが順に、第 2 ウェハ 220 の頂面 220a に積層される。

30

【0108】

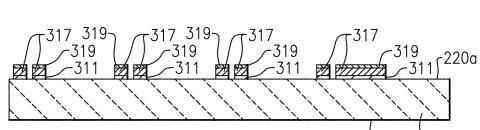

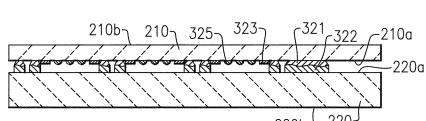

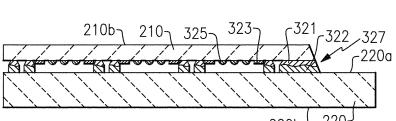

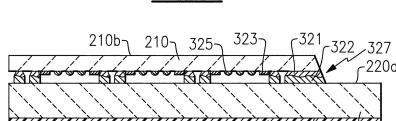

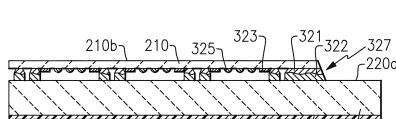

図 16A～16E は、図 15A～15I のステップに引き続いての、本開示の複数の側面に係る電子デバイスを製造する方法の一連のステップを説明する。図 16A に示すように、圧電薄膜共振器 325 と、ストップ層 323 と、及び底面 210a に適切に形成された第 1 金属としての金からなる第 1 金属層 36 (図 3 及び 4 を参照) とを含む第 1 ウェハ 210 が、図 15I に示す第 2 ウェハ 220 と位置合わせされる。その後、第 2 ウェハ 220 の頂面 220a に順に積層された第 2 金属層及び第 3 金属層と、第 1 ウェハ 210 の底面 210a に形成された第 1 金属層とが、TLP 接合により接合される。この接合により、金-錫の合金からなる第 1 合金層 321 と、銅-錫の合金からなる第 2 合金層 322 とが、第 1 ウェハ 210 の底面 210a と第 2 ウェハ 220 の頂面 220a との間に順に積層される。図 16B に示すように、第 1 ウェハ 210 がその周縁に沿って研削され、第 1 合金層 321 及び第 2 合金層 322 が露出する斜面 327 が形成される。図 16C に示すように、第 2 ウェハ 220 の底面 220b には裏面研削保護テープ 329 が貼り付けられる。図 16D に示すように、第 1 ウェハ 210 が所定厚さになるように、第 1 ウェハ 210 が頂面 210b から研磨される。図 16E に示すように、第 2 ウェハ 220 の底面 220b から裏面研削保護テープ 329 が剥離される。

40

【0109】

50

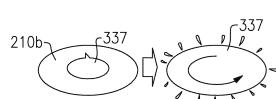

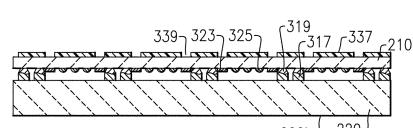

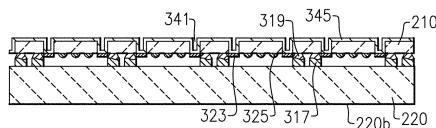

図17A～17Eは、図16A～16Eのステップに引き続いての、本開示の複数の側面に係る電子デバイスを製造する方法の一連のステップを説明する。図17Aに示すように、第1ウェハ210の頂面210bにはスピンドルコーティングによりレジスト337が塗布される。図17Bに示すように、レジスト337が塗布された第1ウェハ210は、露光されて所定パターンが転写される。図17Cに示すように、露光された第1ウェハ210にPEB及び現像が施される。これにより、レジスト337から所定部分が除去され、凹部339が形成される。図17Dに示すように、第1ウェハ210が加工されるように凹部339を介するドライエッティングが行われ、頂面210bが底面210aと連通し、スルーホール341が、底面210aに形成されたストップ層323に到達するようになる。図17Eに示すように、レジスト337が除去される。

10

#### 【0110】

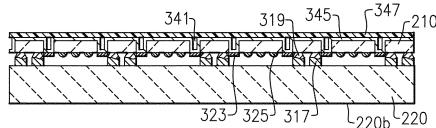

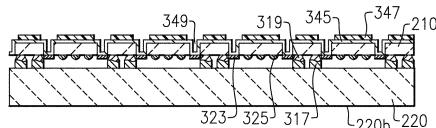

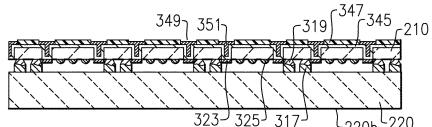

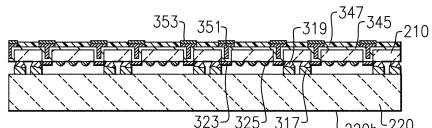

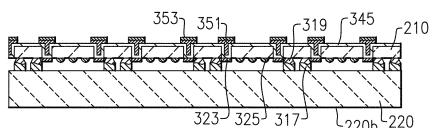

図18A～18Gは、図17A～17Eのステップに引き続いての、本開示の一側面に係る電子デバイスを製造する方法の一連のステップを説明する。図18Aに示すように、第1ウェハ210の頂面210bと、スルーホール341の側面及び底面とが覆われるよう にスパッタ膜345が形成される。図18Bに示すように、第1ウェハ210の頂面210bには、スピンドルコーティングによりレジスト347が、スパッタ膜345が介在されて塗布される。図18Cに示すように、露光、PEB及び現像により、スルーホール341の頂部のレジスト347が除去され、凹部349が形成される。図18Dに示すように、スルーホール341及び凹部349に銅メッキ351が形成される。図18Eに示すように、銅メッキ351に半田メッキ353が施される。図18Fに示すように、レジスト347が除去される。図18Gに示すように、スパッタ膜345が除去される。

20

#### 【0111】

図19A～19Dは、図18A～18Gのステップに引き続いての、本開示の一側面に係る電子デバイスを製造する方法の一連のステップを説明する。図19Aに示すように、第1ウェハ210及び第2ウェハ220が上下に反転され、ここで下側になった第1ウェハ210の頂面210bに裏面研削保護テープ357が貼り付けられる。図19Bに示すように、ここで上側になった第2ウェハ220の底面220bが、第2ウェハ220所定厚さを有するまで研磨される。図19Cに示すように、ここで下側になった第1ウェハ210の頂面210bから、裏面研削保護テープ357が剥離される。図19Dに示すように、構造200はプラズマDBGによりダイシングされて電子デバイス100の別個のチップに個片化される。すなわち、構造200は、第1ウェハ210の頂面210bから適切な深さまでプラズマによりダイシングされ、切目359が形成される。引き続き、第1ウェハ210の頂面210bに裏面研削保護テープが貼り付けられ、第2ウェハ220の底面220bが研磨されて電子デバイス100の複数のチップが分離され、個片化される。

30

#### 【0112】

図20は、本開示のさらなる側面に係る電子デバイスの第1変形例を示す断面図である。図21は、電子デバイスの第1変形例がプリント基板に実装された一構造を示す断面図である。第2基板20の底面20bに外部電極40が配置された第1変形例は、図1に示すように第1基板10の頂面10bに外部電極40が配置された既に述べた実施形態の電子デバイスとは異なる。第1変形例の他の構成は、既に述べた実施形態の電子デバイスのものと同様である。

40

#### 【0113】

図22は、第1変形例に係る電子デバイスの第1基板と第2基板との位置合わせを示す断面図である。第1変形例においてはまた、図3に示す電子デバイスと同様、第1基板10の底面10a、第2基板20の頂面20a、第1側壁33及び第2側壁34により内部にキャビティ19が形成されて第1側壁33が第2側壁34に対向かつ接触するように、第1基板10と第2基板20とが位置合わせされる。第1基板10及び第2基板20が、位置合わせされた状態で維持されて加熱され、第1側壁33及び第2側壁34は互いにTCP接合により接合されて单一の側壁30となる。

#### 【0114】

50

圧電薄膜共振器 11 を含む図 1 及び図 2 に例示される電子回路 18 は、第 1 基板 10 に配置されるが、第 1 変形例の電子デバイスにおいて外部電極 40 は第 2 基板 20 に配置される。これにより、電子回路 18 を第 1 基板 10 に配置するプロセスを、外部電極 40 を第 2 基板 20 に配置するプロセスから分離することができるので、各基板を個別に加工することができる。したがって、第 1 基板 10 及び第 2 基板 20 について各プロセスの工数を低減するとともに、当該プロセスを容易に行うことができる。

【 0115 】

図 23 は、本開示のなおもさらなる側面に係る電子デバイスの第 2 変形例を示す断面図である。図 1 に示す電子デバイス 100 と比べると、第 2 変形例においては、第 2 基板 20 の頂面 20a にも圧電薄膜共振器 21 を含む電子回路 28 が配置される。電子回路 28 は、配線パッド 22 により互いに適切に接続された圧電薄膜共振器 21 を有し、第 1 基板 10 の底面 10a に配置された電子回路 18 とともにフィルタ、フィルタデバイス等を形成する。第 2 変形例によれば、第 2 基板 20 にも電子回路 28 が配置されるので、電子デバイス 100 における集積度を向上させて電子デバイス 100 の小型化とともに高機能化を図ることができる。

10

【 0116 】

フィルタ回路群 18 の複数の実施形態は、例えば無線通信デバイスのような電子デバイスにおいて究極的に使用されるモジュールに組み入れられて当該モジュールとしてパッケージ化され得る。図 24 は、フィルタ回路群 18 を含むモジュール 2400 の一例を説明するブロック図である。フィルタ回路群 18 は、一以上の接続パッド、例えば図 1 に示す外部電極 40、を含む一以上のダイ 100 に実装することができる。例えば、フィルタ回路群 18 は、フィルタ回路群 18 の入力接触部に対応する接続パッド 40 と、フィルタ回路群 18 の出力接触部に対応する他の接続パッド 40 を含んでよい。パッケージ状モジュール 2400 は、例えば、図 2 に示すプリント基板 110 のような、ダイ 100 を含む複数の構成要素を受容するように構成されたパッケージ基板を含む。例えば、図 2 に示す電極 111 のような複数の接続パッドを、パッケージ基板 110 に配置することができ、様々なフィルタ回路群 18 の様々な接続パッド 40 を、当該フィルタ回路群 18 への及びフィルタ回路群 18 からの様々な信号を通過させるべく、パッケージ基板 110 上の電極 111 に接続することができる。図 24 には、接続パッド 40 及び電極 111 が重なるように例示される。モジュール 2400 はさらに、オプションとして、ここでの開示に鑑みて半導体製作の当業者に知られているような、例えば一以上の付加フィルタ、増幅器、前置フィルタ、変調器、復調器、ダウンコンバータ等のような、他の回路群ダイ 2410 を含む。いくつかの実施形態において、モジュール 2400 はまた、例えば、モジュール 2400 の保護を与えてその取り扱いを容易にする一以上のパッケージ構造を含み得る。かかるパッケージ構造は、パッケージ基板 110 を覆うように形成されてその上に様々な回路及び構成要素を実質的にカプセル化する寸法とされたオーバーモールドを含み得る。オーバーモールドは、例えば、図 2 に示す樹脂 120 を含み得る。

20

30

【 0117 】

上述したように、フィルタ回路群 18 の様々な例及び実施形態を、多様な電子デバイスに使用することができる。例えば、フィルタ回路群 18 は、アンテナデュプレクサにおいて使用することができる。アンテナデュプレクサは、それ自体が、RF フロントエンドモジュール及び通信機器のような様々な電子機器に組み入れ可能である。

40

【 0118 】

図 25 を参照すると、例えば、無線通信デバイス（例えば携帯電話機）のような電子デバイスにおいて使用され得るフロントエンドモジュール 2500 の一例のブロック図が示される。フロントエンドモジュール 2500 は、共通ノード 2502、入力ノード 2504 及び出力ノード 2506 を有するアンテナデュプレクサ 2510 を含む。共通ノード 2502 にはアンテナ 2610 が接続される。

【 0119 】

アンテナデュプレクサ 2510 は、入力ノード 2504 及び共通ノード 2502 間に接続

50

された一以上の送信フィルタ 2512 と、共通ノード 2502 及び出力ノード 2506 間に接続された一以上の受信フィルタ 2514 とを含んでよい。送信フィルタの通過帯域は、受信フィルタの通過帯域とは異なる。フィルタ回路 18 の実施形態は、一以上の送信フィルタ 2512 又は一以上の受信フィルタ 2514 に含まれ得る。インダクタ又は他の整合要素 2520 を共通ノード 2502 に接続することができる。

#### 【0120】

フロントエンドモジュール 2500 はさらに、デュプレクサ 2510 の入力ノード 2504 に接続された送信器回路 2532 と、デュプレクサ 2510 の出力ノード 2506 に接続された受信器回路 2534 とを含む。送信器回路 2532 は、アンテナ 2610 を介して送信される信号を生成し、受信器回路 2534 は、アンテナ 2610 を介して信号を受信して処理することができる。いくつかの実施形態において、受信器回路及び送信器回路は、図 25 に示すように別個の構成要素として実装されるが、他の実施形態において、これらの構成要素は共通の送受信器回路又はモジュールに組み入れることができる。当業者にわかることだが、フロントエンドモジュール 2500 は、図 25 に示されないスイッチ、電磁カプラ、増幅器、プロセッサ等を含むがこれらに限られない他の構成要素も含み得る。

10

#### 【0121】

図 26 は、図 25 に示すアンテナデュプレクサ 2510 を含む無線デバイス 2600 の一例のブロック図である。無線デバイス 2600 は、音声又はデータ通信のために構成されたセルラー電話機、スマートフォン、タブレット、モ뎀、通信ネットワーク、又は任意の他のポータブル若しくは非ポータブルデバイスであってよい。無線デバイス 2600 は、アンテナ 2610 から信号を送受信することができる。無線デバイスは、図 25 を参照して上述したものと同様にフロントエンドモジュール 2500 の一実施形態を含む。フロントエンドモジュール 2500 は、上述したように、デュプレクサ 2510 を含む。図 26 に示される例において、フロントエンドモジュール 2500 はさらに、アンテナスイッチ 2540 を含む。これは、例えば送信モード及び受信モードのような異なる周波数帯域又はモードで切り替わるように構成することができる。図 26 に示される例において、アンテナスイッチ 2540 は、デュプレクサ 2510 及びアンテナ 2610 間に位置決めされる。しかしながら、他例において、デュプレクサ 2510 は、アンテナスイッチ 2540 及びアンテナ 2610 間に位置決めされてよい。他例において、アンテナスイッチ 2540 及びデュプレクサ 2510 は単一の構成要素に統合することができる。

20

#### 【0122】

フロントエンドモジュール 2500 は、送信用の信号を生成し、又は受信された信号を処理するように構成された送受信器 2530 を含む。送受信器 2530 は、図 25 の例に示すように、デュプレクサ 2510 の入力ノード 2504 に接続することができる送信器回路 2532 と、デュプレクサ 2510 の出力ノード 2506 に接続することができる受信器回路 2534 とを含み得る。

30

#### 【0123】

送信器回路 2532 による送信のために生成された信号が、電力増幅器 (PA) モジュール 2550 によって受信される。PA モジュール 2550 は、送受信器 2530 の送信器回路 2532 からの生成信号を増幅する。電力増幅器モジュール 2550 は一以上の電力増幅器を含み得る。電力増幅器モジュール 2550 は、多様な RF 又は他の周波数帯域の送信信号を増幅するべく使用することができる。例えば、電力増幅器モジュール 2550 は、無線ローカルエリアネットワーク (WLAN) 信号又は任意の他の適切なパルス信号を送信する補助となるように、電力増幅器の出力をパルス化するべく使用可能なイネーブル信号を受信することができる。電力増幅器モジュール 2550 は、例えば、GSM (Global System for Mobile) (登録商標) 信号、符号分割多元接続 (CDMA) 信号、広帯域符号分割多元接続 (W-CDMA) 信号、ロングタームエボリューション (LTE) 信号又はEDGE 信号を含む様々なタイプの信号のいずれかを増幅するように構成することができる。所定の実施形態において、スイッチ等を含む電力増幅

40

50

器モジュール 2550 及び関連構成要素は、例えば高電子移動度トランジスタ ( pHEMT ) 若しくは絶縁ゲートバイポーラトランジスタ ( BiFET ) を使用してガリウム砒素 ( GaAs ) 基板に、又は相補型金属酸化物半導体 ( CMOS ) 電界効果トランジスタを使用してシリコン基板に作製することができる。

【 0124 】

なおも図 26 を参照すると、フロントエンドモジュール 2500 はさらに、アンテナ 2610 からの受信信号を増幅して当該増幅信号を送受信器 2530 の受信回路 2534 に与える低雑音増幅器モジュール 2560 を含む。

【 0125 】

図 26 の無線デバイス 2600 はさらに、送受信器 2530 に接続されて無線デバイス 2600 の動作のための電力を管理する電力管理サブシステム 2620 を含む。電力管理システム 2620 はまた、ベース帯域サブシステム 2630 、及び無線デバイス 2600 の様々な他の構成要素の動作を制御することができる。電力管理システム 2620 はまた、無線デバイス 2600 の様々な構成要素のために電力を供給する電池 ( 図示せず ) を含み又は当該電池に接続されてよい。電力管理システム 2620 はさらに、例えば信号の送信を制御することができる一以上のプロセッサ又はコントローラを含み得る。一実施形態において、ベース帯域サブシステム 2630 は、ユーザとの間でやりとりされる音声又はデータの様々な入力及び出力を容易にするべくユーザインターフェイス 2640 に接続される。ベース帯域サブシステム 2630 はまた、無線デバイスの動作を容易にし及び / 又はユーザのための情報を格納するべく、データ及び / 又は命令を格納するように構成されたメモリ 2650 に接続することができる。

10

20

30

【 0126 】

少なくとも一つの実施形態のいくつかの側面を上述したが、様々な改変、修正及び改善が当業者にとって容易に想起されることを理解されたい。かかる改変、修正及び改善は、本開示の一部となることが意図され、かつ、本発明の範囲内にあることが意図される。理解するべきことだが、ここで述べられた方法及び装置の実施形態は、本明細書に記載され又は添付図面に例示された構成要素の構造及び配列の詳細への適用に限られない。方法及び装置は、他の実施形態で実装し、様々な態様で実施又は実行することができる。特定の実装例は、例示のみを目的としてここに与えられ、限定されることを意図しない。また、ここで使用される表現及び用語は、説明目的であって、限定としてみなすべきではない。ここでの「含む」、「備える」、「有する」、「包含する」及びこれらの変形の使用は、以降に列挙される項目及びその均等物並びに付加項目の包括を意味する。「又は ( 若しくは ) 」の言及は、「又は ( 若しくは ) 」を使用して記載される任意の用語が、当該記載の用語の一つの、一つを超える、及びすべてのものを示すように解釈され得る。前後左右、頂底上下、及び横縦への言及はいずれも、記載の便宜を意図しており、本システム及び方法又はこれらの構成要素がいずれか一つの位置的又は空間的配向に限られるものではない。したがって、上記説明及び図面は例示にすぎず、本発明の範囲は、添付の特許請求の範囲の適切な構造及びその均等物から決定されるべきである。

40

50

【図面】

【図 1】

1

【图2】

**FIG. 2**

【 図 3 】

**FIG. 3**

【 図 4 】

FIG.4A

FIG.4B

FIG.4C

10

20

30

40

50

【図 5 A】

【図 5 B】

10

20

30

40

【図 6 A】

FIG.6A

【図 6 B】

FIG.6B

50

【図 7】

FIG.7

【図 8】

FIG.8A

10

FIG.8B

20

FIG.8C

【図 9】

【図 10】

FIG.10

30

40

50

【図 1 1】

FIG.11

【図 1 2】

FIG.12A

10

FIG.12B

20

【図 1 3】

FIG.13A

【図 1 4】

FIG.14A

30

FIG.13B

FIG.14B

40

50

【図15-1】

FIG.15A

FIG.15B

FIG.15C

FIG.15D

FIG.15E

【図15-2】

FIG.15F

FIG.15G

FIG.15H

FIG.15I

10

20

30

40

【図16】

FIG.16A

FIG.16B

FIG.16C

FIG.16D

FIG.16E

【図17】

FIG.17A

FIG.17B

FIG.17C

FIG.17D

FIG.17E

50

【 図 1 8 - 1 】

FIG.18A

FIG.18B

FIG. 18C

### 【図 18-2】

FIG.18D

FIG. 18E

FIG.18F

FIG.18G

【図19】

FIG.19A

FIG.19B

110.150

110.100

【図20】

FIG.20

## 【図21】

【図22】

### 【図23】

### 【図24】

【図 2 5】

FIG.25

【図 2 6】

FIG.26

10

20

30

40

50

---

フロントページの続き

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,226

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,183

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,186

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,188

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/429,190

(32)優先日 平成28年12月2日(2016.12.2)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/539,863

(32)優先日 平成29年8月1日(2017.8.1)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/539,861

(32)優先日 平成29年8月1日(2017.8.1)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/539,871

(32)優先日 平成29年8月1日(2017.8.1)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/539,873

(32)優先日 平成29年8月1日(2017.8.1)

(33)優先権主張国・地域又は機関

米国(US)

大阪府門真市大字門真1006番地 スカイワークスフィルターソリューションズジャパン株式会

社内

審査官 橋本 和志

(56)参考文献 特開2015-091065(JP,A)

特開2015-024443(JP,A)

国際公開第2010/021267(WO,A1)

国際公開第2010/005061(WO,A1)

(58)調査した分野 (Int.Cl., DB名)

H03H 3/02

H 0 3 H 9 / 0 5

H 0 3 H 9 / 1 7

H 0 1 L 2 3 / 0 2