(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7114244号

(P7114244)

(45)発行日 令和4年8月8日(2022.8.8)

(24)登録日 令和4年7月29日(2022.7.29)

(51)国際特許分類

|        |                  |        |        |   |

|--------|------------------|--------|--------|---|

| H 01 L | 27/146 (2006.01) | H 01 L | 27/146 | A |

| H 04 N | 5/369 (2011.01)  | H 04 N | 5/369  |   |

| H 01 L | 31/107 (2006.01) | H 01 L | 27/146 | F |

|        |                  | H 01 L | 31/10  | B |

請求項の数 14 (全27頁)

(21)出願番号 特願2017-230987(P2017-230987)

(22)出願日 平成29年11月30日(2017.11.30)

(65)公開番号 特開2019-102618(P2019-102618)

A)

(43)公開日 令和1年6月24日(2019.6.24)

審査請求日 令和2年11月20日(2020.11.20)

前置審査

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

(74)代理人 100124442

弁理士 黒岩 創吾

(72)発明者 岩田 旬史

東京都大田区下丸子3丁目30番2号キ

ャノン株式会社内

審査官 柴山 将隆

最終頁に続く

(54)【発明の名称】 光検出装置、光検出システム、及び移動体

## (57)【特許請求の範囲】

## 【請求項1】

アバランシェダイオードを含む画素が配され、第1面と、前記第1面と対向する第2面とを有する半導体基板を有する光検出装置であって、

前記アバランシェダイオードは、

前記半導体基板の第1の深さにおいて、信号電荷と同じ第1導電型の第1半導体領域と、前記第1導電型とは極性の異なる第2導電型の第2半導体領域と、を有し、

前記半導体基板の、前記第1面からの深さが前記第1の深さよりも深い第2の深さにおいて、前記第1半導体領域と接して配され、前記第1半導体領域よりも前記第1導電型の不純物濃度が低い前記第1導電型の第3半導体領域と、前記第2半導体領域及び前記第3半導体領域と接して配され、前記第2半導体領域よりも前記第2導電型の不純物濃度が低い前記第2導電型の第4半導体領域と、を有し、

前記半導体基板の、前記第1面からの深さが前記第2の深さよりも深い第3の深さにおいて、前記第3半導体領域及び前記第4半導体領域と接して配され、前記第1導電型の不純物濃度が前記第3半導体領域より低い前記第1導電型の第5半導体領域と、を有し、

前記第1半導体領域は前記半導体基板の前記第1面の一部を構成し、

平面視において、

前記第1半導体領域のすべての領域が前記第3半導体領域に重なり、

前記第2半導体領域は前記第4半導体領域の少なくとも一部と重なり、

前記第3半導体領域及び前記第4半導体領域は前記第5半導体領域と重なり、

前記第1半導体領域から前記第3半導体領域において、アバランシェ増幅が生じることを特徴とする光検出装置。

【請求項2】

前記第1半導体領域と前記第2半導体領域の間に第6半導体領域を有し、前記第6半導体領域は、前記第1導電型の不純物濃度が前記第1半導体領域よりも低い、あるいは、前記第2導電型の不純物濃度が前記第2半導体領域よりも低いことを特徴とする請求項1に記載の光検出装置。

【請求項3】

アバランシェダイオードを含む画素が配され、第1面と、前記第1面と対向する第2面とを有する半導体基板を有する光検出装置であって、

前記アバランシェダイオードは、

前記半導体基板の第1の深さにおいて、信号電荷と同じ第1導電型の第1半導体領域と、前記第1導電型とは極性の異なる第2導電型の第2半導体領域と、を有し、

前記半導体基板の、前記第1面からの深さが前記第1の深さより深い第2の深さにおいて、前記第1半導体領域と接して配された第3半導体領域と、前記第2半導体領域及び前記第3半導体領域と接して配され、前記第2半導体領域よりも前記第2導電型の不純物濃度が低い前記第2導電型の第4半導体領域と、を有し、

前記半導体基板の、前記第1面からの深さが前記第2の深さよりも深い第3の深さにおいて、前記第3半導体領域及び前記第4半導体領域と接して配された第5半導体領域を有し、

前記第1半導体領域と前記第2半導体領域の間に第6半導体領域を有し、

平面視において、

前記第1半導体領域のすべての領域が前記第3半導体領域に重なり、

前記第2半導体領域は前記第4半導体領域の少なくとも一部と重なり、

前記第3半導体領域及び前記第4半導体領域は前記第5半導体領域と重なり、

前記第3半導体領域の信号電荷に対するポテンシャルの高さが、前記第4半導体領域の前記信号電荷に対するポテンシャルの高さよりも低く、

前記第4半導体領域の前記信号電荷に対するポテンシャルの高さが、前記第5半導体領域の前記信号電荷に対するポテンシャルの高さよりも高く、

前記第1半導体領域の前記信号電荷に対するポテンシャルの高さが、前記第3半導体領域の前記信号電荷に対するポテンシャルの高さよりも低く、

前記第3半導体領域の前記信号電荷に対するポテンシャルの高さが、前記第5半導体領域の前記信号電荷に対するポテンシャルの高さよりも低く、

前記第1半導体領域から前記第3半導体領域において、アバランシェ増幅が生じることを特徴とする光検出装置。

【請求項4】

前記第6半導体領域は、前記第1導電型の不純物濃度が前記第1半導体領域よりも低い、あるいは、前記第2導電型の不純物濃度が前記第2半導体領域よりも低いことを特徴とする請求項3に記載の光検出装置。

【請求項5】

前記平面視において、前記第1半導体領域は前記第2半導体領域に内包されることを特徴とする請求項1乃至4のいずれか1項に記載の光検出装置。

【請求項6】

前記平面視において、前記第3半導体領域は前記第4半導体領域に内包されることを特徴とする請求項1乃至5のいずれか1項に記載の光検出装置。

【請求項7】

前記画素を複数有し、

前記複数の画素の各々を分離する分離部を有し、

前記分離部は、前記平面視において前記第2半導体領域を内包して前記第2半導体領域と接し、前記第2半導体領域よりも前記第2導電型の不純物濃度の高い前記第2導電型の

10

20

30

40

50

第7半導体領域を有することを特徴とする請求項1乃至6のいずれか1項に記載の光検出装置。

【請求項8】

前記分離部は、前記平面視において前記第4半導体領域を内包して前記第4半導体領域と接し、前記第7半導体領域よりも前記第2導電型の不純物濃度の低い前記第2導電型の第8半導体領域を有することを特徴とする請求項7に記載の光検出装置。

【請求項9】

前記半導体基板は、前記第1面から前記第5半導体領域よりも深い第4の深さにおいて、前記第2導電型の第9半導体領域を有し、前記第9半導体領域と前記分離部に含まれる前記第2導電型の半導体領域とが電気的に接続していることを特徴とする請求項7または8に記載の光検出装置。

10

【請求項10】

前記分離部は、前記半導体基板の深さ方向において、前記第7半導体領域と前記第8半導体領域の間に、前記第7半導体領域よりも前記第2導電型の不純物濃度が低く、前記第2半導体領域、及び前記第8半導体領域よりも前記第2導電型の不純物濃度が高い、前記第2導電型の第10半導体領域を有することを特徴とする請求項8に記載の光検出装置。

【請求項11】

前記第3半導体領域と前記第4半導体領域とが、PN接合を構成し、

前記第3半導体領域の不純物濃度は、前記PN接合に逆バイアスとなる電位を供給した際に、前記第3半導体領域のすべての領域が空乏化する不純物濃度であることを特徴とする請求項1乃至10のいずれか1項に記載の光検出装置。

20

【請求項12】

前記半導体基板とは異なる半導体基板を有し、

前記異なる半導体基板には、前記第1半導体領域に供給される電位を制御する制御部が配され、

前記半導体基板と、前記異なる半導体基板とが積層され、

前記第1半導体領域と、前記制御部とが、配線を介して電気的に接続していることを特徴とする請求項1乃至11のいずれか1項に記載の光検出装置。

【請求項13】

請求項1から12のいずれか1項に記載の光検出装置を複数有する光検出システムであつて、

30

前記光検出装置によって検出される光を発光する発光部と、

前記光検出装置に保持されたデジタル信号を用いて距離算出を行う距離算出手段と、を有することを特徴とする光検出システム。

【請求項14】

移動体であつて、

請求項1から13のいずれか1項に記載の光検出装置と、

前記光検出装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と、を有することを特徴とする移動体。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光検出装置、光検出システム、及び移動体の少なくとも1つに関する。

【背景技術】

【0002】

従来、アバランシェ（電子なだれ）增幅を利用し、単一光子レベルの微弱光を検出可能な光検出装置が知られている。

【0003】

50

特許文献1では、光電変換部を構成する半導体領域のPN接合領域において、単一光子に起因する光電荷がアバランシェ増幅を起こすSPAD (Single Photon Avalanche Diode)を開示している。

【0004】

また、特許文献1のSPADは、半導体基板の表面に高い不純物濃度のP型半導体領域が配され、P型半導体領域の下部にはN型半導体領域が配されている。N型半導体領域はN型のエピタキシャル層に含まれるように配される。P型半導体領域とN型半導体領域とはPN接合を構成し、PN接合には高い逆バイアス電圧が印加されている。

【先行技術文献】

【特許文献】

10

【0005】

【文献】米国特許第9209336号

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1に記載のSPADにおいて、電荷検出領域はPN接合領域となる。電荷検出領域には、強電界が生じているため、強電界によってPN接合間にトンネル効果が生じるおそれがある。トンネル効果によって生じた電荷は、電荷検出領域で偽信号として検出され、ノイズとなるおそれがある。このトンネル効果によって生じる電荷は、電荷検出領域の面積に比例して多くなる。

20

【0007】

一方で、電荷検出領域の面積を小さくした場合には、トンネル効果によって生じる電荷を抑制することが可能である。しかし、電荷検出領域の面積を小さくすると、光検出効率が下がってしまうおそれがある。

【0008】

そこで、ノイズを抑制しつつ、光検出効率の低下を抑制することができる光検出装置を提供する。

【課題を解決するための手段】

【0009】

本発明の一様態は、アバランシェダイオードを含む画素が配され、第1面と、前記第1面と対向する第2面とを有する半導体基板を有する光検出装置であって、前記アバランシェダイオードは、前記半導体基板の第1の深さにおいて、信号電荷と同じ第1導電型の第1半導体領域と、前記第1導電型とは極性の異なる第2導電型の第2半導体領域と、を有し、前記半導体基板の、前記第1面からの深さが前記第1の深さよりも深い第2の深さにおいて、前記第1半導体領域と接して配され、前記第1半導体領域よりも前記第1導電型の不純物濃度が低い前記第1導電型の第3半導体領域と、前記第2半導体領域及び前記第3半導体領域と接して配され、前記第2半導体領域よりも前記第2導電型の不純物濃度が低い前記第2導電型の第4半導体領域と、を有し、前記半導体基板の、前記第1面からの深さが前記第2の深さよりも深い第3の深さにおいて、前記第3半導体領域及び前記第4半導体領域と接して配され、前記第1導電型の不純物濃度が前記第3半導体領域よりも低い前記第1導電型の第5半導体領域と、を有し、前記第1半導体領域は前記半導体基板の前記第1面の一部を構成し、平面視において、前記第1半導体領域のすべての領域が前記第3半導体領域に重なり、前記第2半導体領域は前記第4半導体領域の少なくとも一部と重なり、前記第3半導体領域及び前記第4半導体領域は前記第5半導体領域と重なり、前記第1半導体領域から前記第3半導体領域において、アバランシェ増幅が生じることを特徴とする光検出装置に関する。

30

【0010】

アバランシェダイオードを含む画素が配され、第1面と、前記第1面と対向する第2面とを有する半導体基板を有する光検出装置であって、前記アバランシェダイオードは、前記半導体基板の第1の深さにおいて、信号電荷と同じ第1導電型の第1半導体領域と、前

40

50

記第1導電型とは極性の異なる第2導電型の第2半導体領域と、を有し、前記半導体基板の、前記第1面からの深さが前記第1の深さより深い第2の深さにおいて、前記第1半導体領域と接して配された第3半導体領域と、前記第2半導体領域及び前記第3半導体領域と接して配され、前記第2半導体領域よりも前記第2導電型の不純物濃度が低い前記第2導電型の第4半導体領域と、を有し、前記半導体基板の、前記第1面からの深さが前記第2の深さよりも深い第3の深さにおいて、前記第3半導体領域及び前記第4半導体領域と接して配された第5半導体領域を有し、前記第1半導体領域と前記第2半導体領域の間に第6半導体領域を有し、平面視において、前記第1半導体領域のすべての領域が前記第3半導体領域に重なり、前記第2半導体領域は前記第4半導体領域の少なくとも一部と重なり、前記第3半導体領域及び前記第4半導体領域は前記第5半導体領域と重なり、前記第3半導体領域の信号電荷に対するポテンシャルの高さが、前記第4半導体領域の前記信号電荷に対するポテンシャルの高さよりも低く、前記第4半導体領域の前記信号電荷に対するポテンシャルの高さが、前記第5半導体領域の前記信号電荷に対するポテンシャルの高さよりも高く、前記第1半導体領域の前記信号電荷に対するポテンシャルの高さが、前記第3半導体領域の前記信号電荷に対するポテンシャルの高さよりも低く、前記第1半導体領域から前記第3半導体領域において、アバランシェ増幅が生じることを特徴とする光検出装置に関する。 10

【発明の効果】

【0011】

ノイズを抑制しつつ、光検出効率の低下を抑制することが可能な光検出装置を実現できる。 20

【図面の簡単な説明】

【0012】

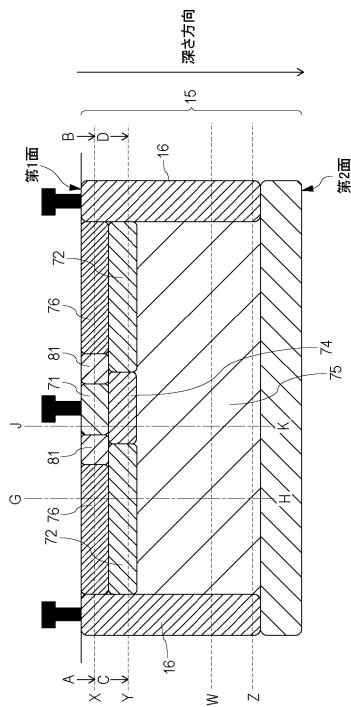

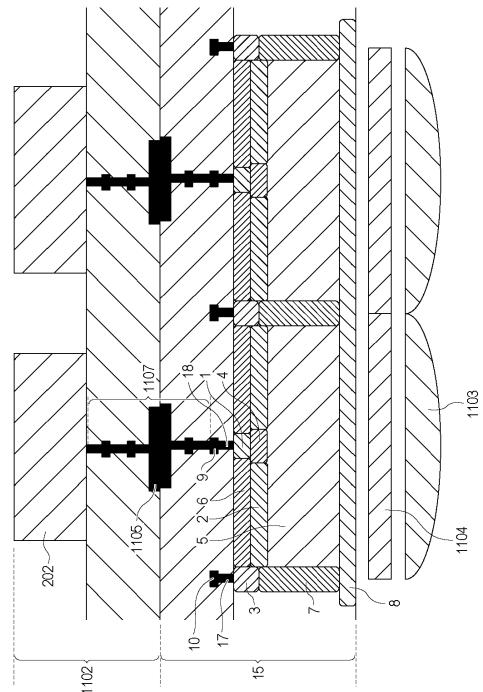

【図1】アバランシェダイオードの断面模式図

【図2】アバランシェダイオードの平面模式図

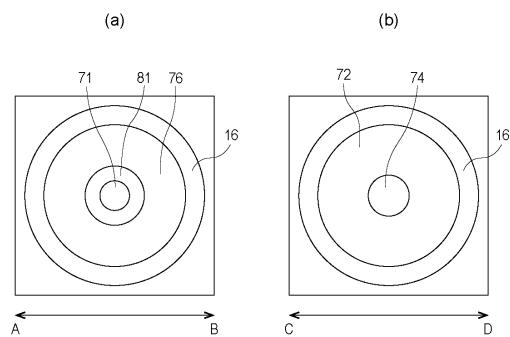

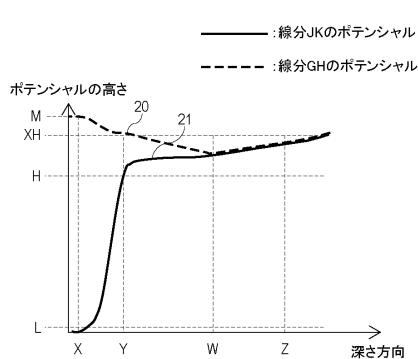

【図3】アバランシェダイオードのポテンシャル図

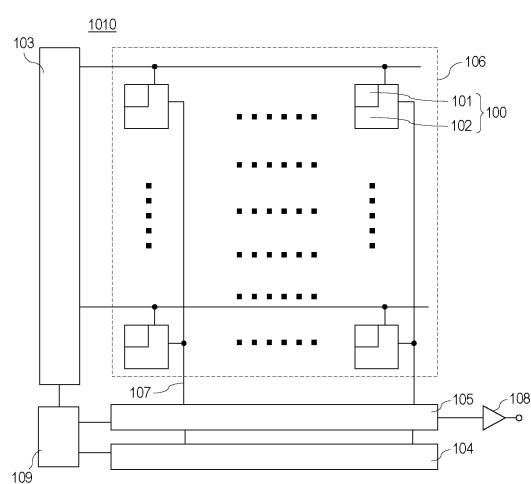

【図4】光検出装置のブロック図

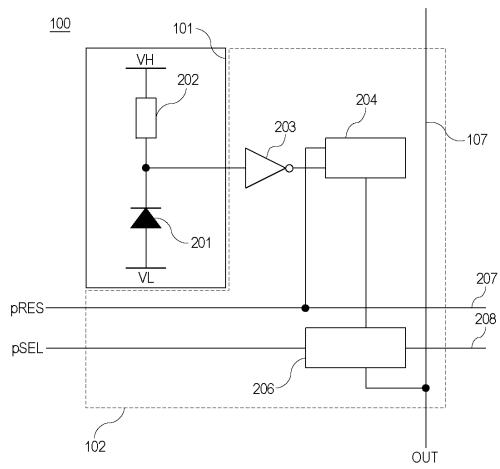

【図5】等価回路を含む画素のブロック図

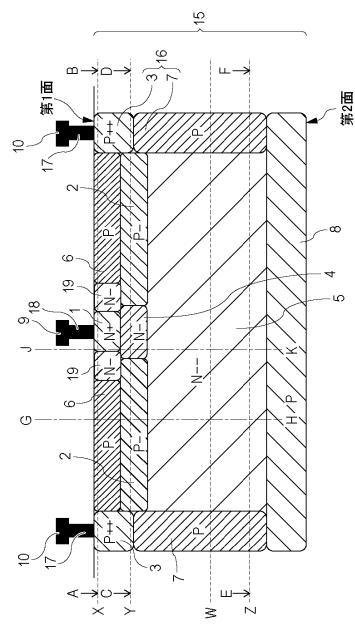

【図6】実施例1に係る断面模式図

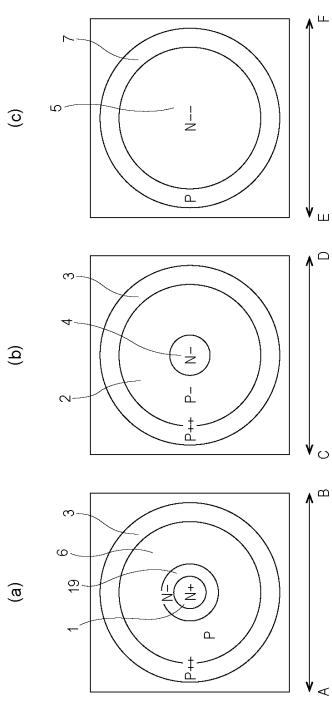

【図7】実施例1に係る平面模式図

【図8】実施例1に係る製造方法

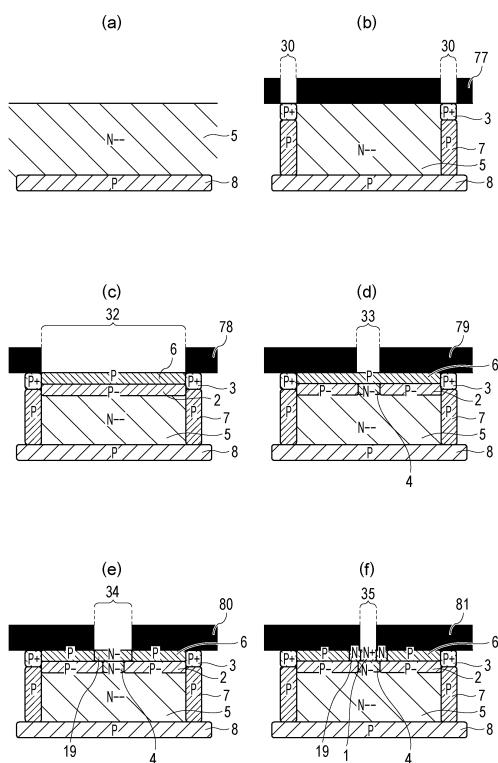

【図9】等価回路図

【図10】実施例2に係る断面模式図

【図11】実施例3に係る断面模式図

【図12】アバランシェダイオードの断面模式図

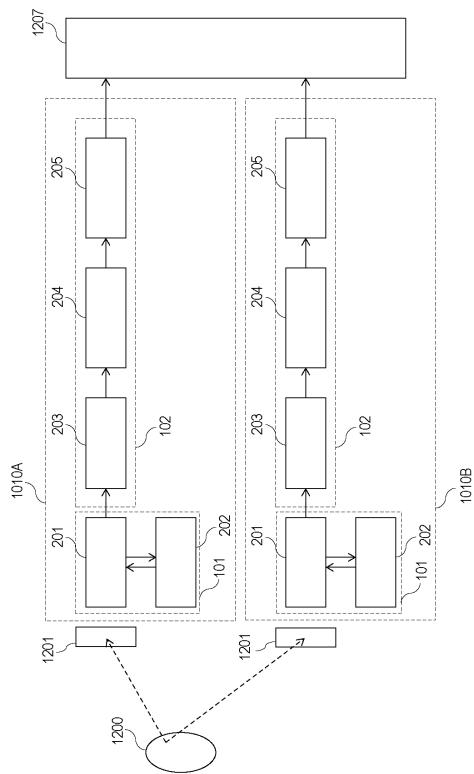

【図13】光検出システムのブロック図

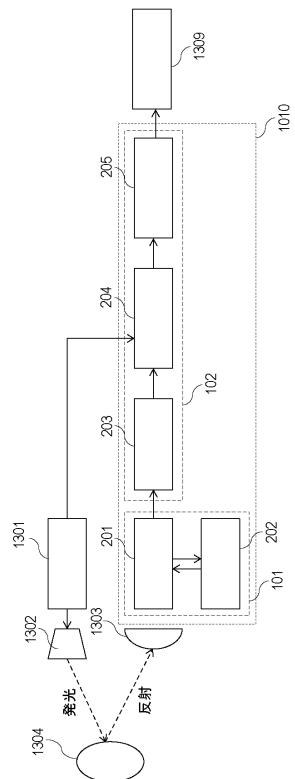

【図14】光検出システムのブロック図

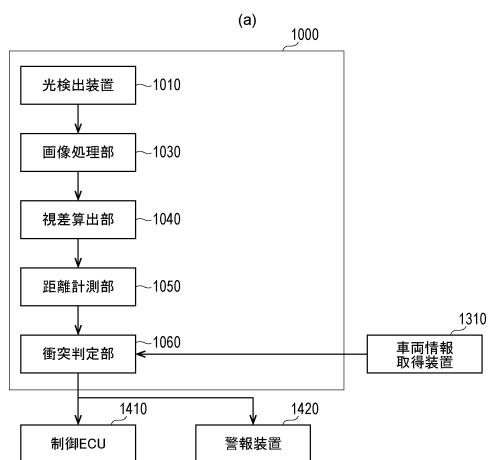

【図15】光検出システムのブロック図

【発明を実施するための形態】

【0013】

図1～図3を用いて本実施形態における光検出装置について説明する。本実施形態の光検出装置はアバランシェダイオードを含む画素を有する。アバランシェダイオードで生じる電荷対のうち信号電荷として用いられる電荷の導電型を第1導電型と呼ぶ。また、第1導電型と反対導電型を第2導電型と呼ぶ。 40

【0014】

図1は、本実施形態におけるアバランシェダイオードの断面模式図である。本実施形態のアバランシェダイオードは、半導体基板15に配される。半導体基板15は第1面と、第1面に対向する第2面を有する。例えば、第1面は半導体基板15の表面であり、第2面は半導体基板15の裏面である。本実施形態では、第1面から第2面へ向かって深さ方

10

20

30

40

50

向とする。半導体基板 15 の第 1 面側（表面側）には、トランジスタのゲート電極や多層配線構造が配される。

【 0 0 1 5 】

図 1 において、分離部 16 に挟まれた領域に、第 1 導電型の第 1 半導体領域 71、第 3 半導体領域 74、第 5 半導体領域 75、第 6 半導体領域 81 が配される。また、分離部 16 に挟まれた領域に、第 2 導電型の第 2 半導体領域 76、第 4 半導体領域 72 が配される。

【 0 0 1 6 】

半導体基板 15 において、第 1 の深さ X に、第 1 半導体領域 71、第 2 半導体領域 76、及び第 6 半導体領域 81 が配される。第 1 半導体領域 71 と第 6 半導体領域 81、及び第 6 半導体領域 81 と第 2 半導体領域 76 は、平面視において接している。ここで、第 1 半導体領域 71 及び第 2 半導体領域 76 が第 1 の深さ X に配されるとは、例えば、深さ X における断面に、第 1 半導体領域 71 及び第 2 半導体領域 76 が存在することを指す。なお、平面視とは、第 1 面に対する平面視である。また、所定領域の所定不純物の不純物濃度とは、該所定の不純物の正味の不純物濃度のことであり、所謂 N E T 不純物濃度を指す。

10

【 0 0 1 7 】

半導体基板 15 において、第 1 面に対して第 1 の深さ X よりも深い第 2 の深さ Y に、第 3 半導体領域 74 及び第 4 半導体領域 72 が配される。第 3 半導体領域 74 と第 4 半導体領域 72 は、平面視において互いに接している。第 4 半導体領域 72 は、第 3 半導体領域 74 と分離部 16 との間に配される。

20

【 0 0 1 8 】

半導体基板 15 において、第 1 面に対して第 2 の深さ Y よりも深い第 3 の深さ Z に、第 5 半導体領域 75 が配される。

【 0 0 1 9 】

図 2 は平面模式図であり、図 2 ( a ) は第 1 の深さ X における点線 A - B に沿った平面模式図、図 2 ( b ) は第 2 の深さ Y における点線 C - D に沿った平面模式図を示す。

【 0 0 2 0 】

図 2 ( a ) に示すように、第 1 の深さ X において、第 1 半導体領域 71 は第 6 半導体領域 81 に内包され、第 6 半導体領域 81 は第 2 半導体領域 76 に内包される。すなわち、第 1 半導体領域 71 は、第 2 半導体領域 76 に内包される。また、第 2 半導体領域 76 は分離部 16 に内包される。

30

【 0 0 2 1 】

図 2 ( b ) に示すように、第 2 の深さ Y において、第 3 半導体領域 74 は第 4 半導体領域 72 に内包される。そして、第 4 半導体領域 72 は分離部 16 に内包される。図 1、2 から明らかなように、平面視において、第 1 半導体領域 71 は第 3 半導体領域 74 の少なくとも一部と重なり、第 3 半導体領域 74 及び第 4 半導体領域 72 は第 5 半導体領域 75 と重なる。さらに、第 2 半導体領域 76 は第 4 半導体領域 72 の少なくとも一部と重なる。

【 0 0 2 2 】

図 3 にアバランシェダイオードのポテンシャル図を示す。図 3 は、図 1 に示される断面図の線分 G H 及び線分 J K のポテンシャル分布の一例を示す。点線 20 は、線分 G H のポテンシャル分布を示し、実線 21 は、線分 J K のポテンシャル分布を示す。ここでは、信号電荷である電子からみたポテンシャルを示す。なお、信号電荷が正孔である場合にはポテンシャルの高低の関係が逆になる。

40

【 0 0 2 3 】

また図 3 において、深さ X、Y、W、及び Z は、図 1 に示した各深さに対応しており、深さ W は深さ Y と深さ Z との間の任意の深さである。

【 0 0 2 4 】

ポテンシャルの高さ X H は、第 4 半導体領域 72 のポテンシャルの高さを示す。ポテンシャルの高さ H は、第 3 半導体領域 74 のポテンシャルの高さを示す。ポテンシャルの高さ M は、第 2 半導体領域 76 のポテンシャルの高さを示す。ポテンシャルの高さ L は、第 1 半導体領域 71 のポテンシャルの高さを示す。

50

## 【0025】

図3の点線20より、深さZにおける線分GHのポテンシャルの高さは、XHレベルとHレベルの間のポテンシャルの高さである。深さZから深さWに近づくと徐々にポテンシャルが下がる。そして、深さWから深さYに近づくと徐々にポテンシャルが上がり、深さYではXHレベルとなる。深さYから深さXに近づくと徐々にポテンシャルが上がる。深さXにおいて、Mレベルのポテンシャルとなる。

## 【0026】

図3の実線21より、深さZにおける線分JKのポテンシャルの高さは、XHレベルとHレベルの間のポテンシャルの高さである。深さZから深さYに近づくまで徐々にポテンシャルが下がる。深さYに近づくと、ポテンシャルの高さが、急峻に下がり始め、深さYのときに、Hレベルのポテンシャルの高さとなる。深さYから深さXに近づくまで、ポテンシャルの高さは急峻に下がる。そして、深さXにおいてLレベルのポテンシャルの高さとなる。

10

## 【0027】

深さZにおいて、点線20と実線21で表されるポテンシャルはほぼ同じ高さとなっている。図3において、深さYより深さZに近い深さでは、線分GH及び線分JKで示す領域において半導体基板15の第1面の側に向かって緩やかに低くなるポテンシャル勾配をもつ。そのため光検出装置において生じた電荷は、緩やかなポテンシャル勾配によって、第2面側から第1面側に移動する。

## 【0028】

20

図3において、深さWから深さYに近づくにつれて、実線21では、緩やかに低くなるポテンシャル勾配をもち、電荷が第1面の側に移動する。一方で点線20では、第1面に向かう電荷に対して、ポテンシャル障壁となるポテンシャル勾配が形成されている。このポテンシャル障壁が、第5半導体領域75から第2半導体領域76に電荷が移動することを抑制する。このポテンシャル障壁に対して、線分GHの領域から線分JKの領域に移動する方向のポテンシャルが低いため、深さWから深さYにおいて、線分GHの領域に存在する電荷は、第1面に移動する過程で線分JKの領域付近に移動しやすくなる。

## 【0029】

線分JKの領域付近に移動した電荷は、深さYから深さXにかけて、急峻なポテンシャル勾配、すなわち強電界によって加速され、加速された電荷が第1半導体領域71に到達する。深さYからXの領域においてアバランシェ増幅が生じる。これに対し、線分GHで示した領域においては、アバランシェ降伏を起こさない、もしくは線分JKで示した領域、特に線分JKの深さYからXの領域よりもアバランシェ降伏が起きにくいポテンシャル分布となっている。

30

## 【0030】

このようなポテンシャル構造とすることにより、特許文献1に示すようなフォトダイオード全体でアバランシェ降伏が起こる構成に比べて、上述したトンネル効果により生じるノイズ電荷を低減させることが可能となる。加えて、本実施形態のアバランシェダイオードによれば、主に波長の長い光の感度の低下を招くことはない。それは、第5半導体領域75のうち第4半導体領域72に重なる領域に存在する信号電荷が、第3半導体領域74を介して第1半導体領域に移動しやすいポテンシャル構造となっているためである。

40

## 【0031】

具体的には、第3半導体領域74のポテンシャルの高さが、第4半導体領域72のポテンシャルの高さよりも低いためである。つまり、第4半導体領域72が第5半導体領域75に存在する信号電荷に対するポテンシャルバリアとして機能し、結果として、第3半導体領域74を介して、第1半導体領域71に電荷が移動しやすくなるのである。

## 【0032】

一方、第2半導体領域76、及び第4半導体領域72で光電変換された電荷は、点線20の深さXから深さWにかけてのポテンシャル勾配により、第5半導体領域75に流れ込む。第5半導体領域75内の電荷は、上述の理由により第3半導体領域74に移動しやす

50

い構造となっている。結果として、第2半導体領域76、及び第4半導体領域72で光電変換された電荷は、第3半導体領域74を介して第1半導体領域に移動し、アバランシェ増幅によって信号電荷として検出される。従って、第2半導体領域76、及び第4半導体領域72で光電変換された電荷を、感度として検出することが可能となる。すなわち、波長の短い光についても、感度を向上することができる。

#### 【0033】

なお、平面視において第1半導体領域71のすべての領域が、第3半導体領域74に重なる方がよい。このような構成によれば、第1半導体領域71と第4半導体領域72とのPN接合が形成されない。そのため、第1半導体領域71と第4半導体領域72とのPN接合においてアバランシェ増幅が生じ、トンネル効果によるノイズが生じることを抑制することが可能となる。

10

#### 【0034】

上記のポテンシャルの関係を実現するための不純物領域の構成の例について図1を用いて説明する。ここでは、信号電荷が電子である場合について説明する。信号電荷が正孔である場合には、不純物の導電型は逆となる。

#### 【0035】

図1において、半導体基板15が、第1面と、第1面と反対に位置する第2面を有し、信号電荷が第1面側に接続された電極を介して取り出される構成を例として説明する。

20

#### 【0036】

半導体基板15は、第1面からの深さXにおいて、信号電荷が取り出される電極が接続されるN型の第1半導体領域71と、第1半導体領域と極性が異なる、P型の第2半導体領域76を有する。また、半導体基板15は、第1面からの深さYにおいて、N型を付与する不純物(N型の不純物)の濃度が第1半導体領域71より低い第3半導体領域74と、P型の第4半導体領域72を有する。第4半導体領域72の第2導電型の不純物濃度は、第2半導体領域76の第2導電型の不純物濃度より低い。また、深さYは深さXより第1面からの深さが深い。

20

#### 【0037】

なお、第3半導体領域は、N型の不純物濃度が第1半導体領域71より低ければよく、N型半導体領域であっても、P型半導体領域であっても良い。例えば、第3半導体領域は、N型半導体領域であり第4半導体領域72と接続しても良く、また、第4半導体領域72の不純物の拡散等により、第4半導体領域から連続するP型半導体領域となっていてもよい。この場合、第3半導体領域の第2導電型の不純物濃度は、第4半導体領域72の第2導電型の不純物濃度より低い。いずれの場合でも、第3半導体領域のN型の不純物濃度は、第1半導体領域より低い。これにより、第1半導体領域71の電子に対するポテンシャルが、第3半導体領域74の電子に対するポテンシャルより低くなる。よって、第3半導体領域74の電子は、第1半導体領域71に収集されやすくなる。

30

#### 【0038】

更に、半導体基板15は、第1面からの深さWにおいて、N型の不純物濃度が第3半導体領域より低い第5半導体領域75を有する。深さWは、第1面からの深さが深さYより深い。これにより、電子に対するポテンシャルは、第3半導体領域74が第5半導体領域75より低くなる。よって、第5半導体領域75で発生した電子は、第3半導体領域74に移動しやすくなる。なお、第5半導体領域75は、N型の不純物濃度が第3半導体領域74より低ければよく、N型半導体領域であっても、P型半導体領域であっても良い。

40

#### 【0039】

また、半導体基板15は、第1半導体領域71と第2半導体領域76との間に、電界緩和層として機能する第6半導体領域を有する。第6半導体領域は、第1半導体領域71と第2半導体領域76との間の電界を緩和して、これらの間でPN接合が生成することで発生する暗電流などのノイズを抑制することができる濃度、幅とすることができます。第6半導体領域は、該機能を満たせば、N型半導体領域であってもP型半導体領域であっても良い。

50

## 【0040】

第1面に対する平面視において、第1半導体領域71は、第3半導体領域74の少なくともと重なり、第2半導体領域76は、第4半導体領域72の少なくとも一部と重なる。また、該平面視において、第3半導体領域74及び第4半導体領域72は、第5半導体領域75と重なる。

## 【0041】

このような構成とすることで、上述のようなポテンシャル構造を有するアバランシェダイオードを構成することができる。

## 【0042】

よって、電荷検出領域の面積が最小化され、かつ、波長の短い光を含む光の光電変換により生成された電荷の電荷検出領域への収集量を向上した光検出装置を実現できる。

10

## 【0043】

以下、本発明の実施形態を具体的な実施例を用いて説明する。各実施例では、信号電荷が電子である構成について説明するが、信号電荷が正孔である場合にも適用可能である。その場合には、各半導体領域及びポテンシャル関係が逆になる。

## 【0044】

## (実施例1)

図4から図9を用いて、本発明に適用可能な光検出装置の実施例を説明する。また、図1～図3と同様の機能を有する部分には同様の符号を付し、詳細な説明を省略する。

## 【0045】

図4は、本実施例の光検出装置1010のブロック図である。光検出装置1010は、画素部106、制御パルス生成部109、水平走査回路部104、列回路105、信号線107、垂直走査回路部103を有している。

20

## 【0046】

画素部106には、画素100が行列状に複数配されている。一つの画素100は、光電変換素子101および画素信号処理部102から構成される。光電変換素子101は光を電気信号へ変換する。画素信号処理部102は、変換した電気信号を列回路105に出力する。

## 【0047】

垂直走査回路部103は、制御パルス生成部109から供給された制御パルスを受け、各画素100に制御パルスを供給する。垂直走査回路部103にはシフトレジスタやアドレスデコーダといった論理回路が用いられる。

30

## 【0048】

信号線107は、垂直走査回路部103により選択された画素100から出力された信号を電位信号として画素100の後段の回路に供給する。

## 【0049】

列回路105は、信号線107を介して各画素100の信号が入力され、所定の処理を行う。所定の処理とは入力された信号のノイズ除去や増幅などを行い、センサ外部に出力する形に変換する処理である。例えば列回路には、パラレル・シリアル変換回路を有する。

40

## 【0050】

水平走査回路部104は、列回路105で処理された後の信号を出回路108へ順次出力するための制御パルスを列回路105に供給する。

## 【0051】

出回路108は、バッファアンプ、差動増幅器などから構成され、列回路105から出力された信号を光検出装置1010の外部の記録部または信号処理部に出力する。

## 【0052】

図4において画素部106における画素100の配列は1次元状に配されていてもよいし、単一画素のみから構成されていてもよい。また、垂直走査回路部103、水平走査回路部104、列回路105は、画素部106を複数の画素列をブロックに分けて、ブロック毎に配置してもよい。また、各画素列に配してもよい。

50

## 【0053】

画素信号処理部102の機能は、必ずしも全ての画素100に1つずつ設けられる必要はなく、例えば複数の画素100によって1つの画素信号処理部102が共有され、順次信号処理が行われてもよい。また、画素信号処理部102は、光電変換素子101の開口率を高めるために、光電変換素子101と異なる半導体基板に設けられていてもよい。この場合、光電変換素子101と画素信号処理部102は、画素毎に設けられた接続配線を介して電気的に接続される。垂直走査回路部103、水平走査回路部104、信号線107および列回路105も上記のように異なる半導体基板に設けられていてもよい。

## 【0054】

図5に本実施例における等価回路を含む画素100のブロック図の一例を示す。図5において、一つの画素100は光電変換素子101および画素信号処理部102を有する。

10

## 【0055】

光電変換素子101は、光電変換部201と制御部202を有する。

## 【0056】

光電変換部201は、光電変換により入射光に応じた電荷対を生成する。光電変換部201には、アバランシェダイオードが用いられる。

20

## 【0057】

光電変換部201のカソードにはアノードに供給される電位VLよりも高い電位VHに基づく電位が供給される。そして光電変換部201のアノードとカソードには、光電変換部201がアバランシェダイオードとなるような逆バイアスがかかるように電位が供給される。このような逆バイアスの電位を供給した状態で光電変換することで、入射光によって生じた電荷がアバランシェ増幅を起こしアバランシェ電流が発生する。

20

## 【0058】

なお、逆バイアスの電位が供給される場合において、アノードおよびカソードの電位差が降伏電圧より大きいときには、アバランシェダイオードはガイガーモード動作となる。ガイガーモード動作を用いて单一光子レベルの微弱信号を高速検出するフォトダイオードがSPADである。

30

## 【0059】

また、光電変換部201のアノードおよびカソードの電位差が、光電変換部201に生じた電荷がアバランシェ増幅を起こす電位差以上であって降伏電圧以下の電位差である場合には、アバランシェダイオードは線形モードになる。線形モードにおいて光検出を行うアバランシェダイオードをアバランシェダイオード(APD)と呼ぶ。本実施例において、光電変換部201はどちらのアバランシェダイオードとして動作してもよい。なお、アバランシェ増幅を起こす電位差については後述する。

30

## 【0060】

制御部202は、高い電位VHを供給する電源電圧と光電変換部201に接続される。制御部202は、光電変換部201で生じたアバランシェ電流の変化を電圧信号に置き換える機能を有する。さらに制御部202は、アバランシェ増幅による信号増幅時に負荷回路(クエンチ回路)として機能し、光電変換部201に供給する電圧を抑制して、アバランシェ増幅を抑制する働きを持つ(クエンチ動作)。制御部202としては、例えば抵抗素子や、アバランシェ電流の増加を検出してフィードバック制御を行うことによりアバランシェ増幅を能動的に抑制する能動クエンチ回路を用いる。

40

## 【0061】

画素信号処理部102は、波形整形部203、カウンタ回路209、選択回路206を有する。波形整形部203は、光子レベルの信号の検出時に得られる電圧変化を整形して、パルス信号を出力する。波形整形部203としては、例えばインバータ回路が用いられる。また、波形整形部203として、インバータを一つ用いた例を示したが、複数のインバータを直列接続した回路を用いてもよいし、波形整形効果があるその他の回路を用いてもよい。

## 【0062】

50

波形整形部 203 から出力されたパルス信号は、カウンタ回路 209 によってカウントされる。カウンタ回路 209 には、例えば  $N - b i t$  カウンタ ( $N$  : 正の整数) の場合、单一光子によるパルス信号を最大で約 2 の  $N$  乗個までカウントすることが可能である。カウントした信号は、検出した信号として保持される。また、駆動線 207 を介して制御パルス p R E S が供給されたとき、カウンタ回路 209 に保持された検出した信号がリセットされる。

#### 【0063】

選択回路 206 には、図 4 の垂直走査回路部 103 から駆動線 208 を介して制御パルス p S E L が供給され、カウンタ回路 209 と信号線 107 との電気的な接続、非接続を切り替える。選択回路 206 には、例えばトランジスタや、画素外に信号を出力するためのバッファ回路などを用いる。

10

#### 【0064】

なお、制御部 202 と光電変換部 201 との間や、光電変換素子 101 と画素信号処理部 102 との間にトランジスタ等のスイッチを配して、電気的な接続を切り替えてよい。同様に、制御部 202 に供給される高い電位 V H または光電変換素子 101 に供給される低い電位 V L の電位の供給をトランジスタ等のスイッチを用いて電気的に切り替えてよい。

#### 【0065】

複数の画素 100 が行列状に配された画素部 106 において、カウンタ回路 209 のカウントを行ごとに順次リセットし、カウンタ回路 209 に保持された検出した信号を行ごとに順次出力するローリングシャッタ動作によって撮像画像を取得してもよい。

20

#### 【0066】

または、全画素行のカウンタ回路 209 のカウントを同時にリセットし、カウンタ回路 209 に保持された検出した信号を行ごとに順次出力するグローバル電子シャッタ動作によって撮像画像を取得してもよい。なお、グローバル電子シャッタ動作を行う場合には、カウンタ回路 209 のカウントを行う場合と、行わない場合を切り替える手段を設けた方がよい。切り替える手段とは、例えば前述したスイッチである。

#### 【0067】

本実施例では、カウンタ回路 209 を用いて撮像画像を取得する構成を示した。しかし、カウンタ回路 209 の代わりに、時間・デジタル変換回路 ( Time to Digit a l C onverter : 以下、 T D C ) 、メモリを用いて、パルス検出タイミングを取得する光検出装置 1010 としてもよい。

30

#### 【0068】

このとき、波形整形部 203 から出力されたパルス信号の発生タイミングは、 T D C によってデジタル信号に変換される。 T D C には、パルス信号のタイミングの測定に、図 4 の垂直走査回路部 103 から駆動線を介して、制御パルス p R E F ( 参照信号 ) が供給される。 T D C は、制御パルス p R E F を基準として、波形整形部 203 を介して各画素から出力された信号の入力タイミングを相対的な時間としたときの信号をデジタル信号として取得する。

#### 【0069】

T D C の回路には、例えばバッファ回路を直列接続して遅延をつくる D e l a y L i n e 方式、 D e l a y L i n e をループ状につないだ L o o p e d T D C 方式などを用いる。その他の方式を用いてよいが、光電変換部 201 の時間分解能と同等以上の時間分解能を達成できる回路方式である方がよい。

40

#### 【0070】

T D C で得られたパルス検出タイミングを表すデジタル信号は、1つまたは複数のメモリに保持される。メモリが複数配された場合には、選択回路 206 に複数の信号を供給することで、メモリにおいて保持したデジタル信号を信号線 107 に出力する際に、メモリ毎に信号線 107 への出力を制御することが可能である。

#### 【0071】

50

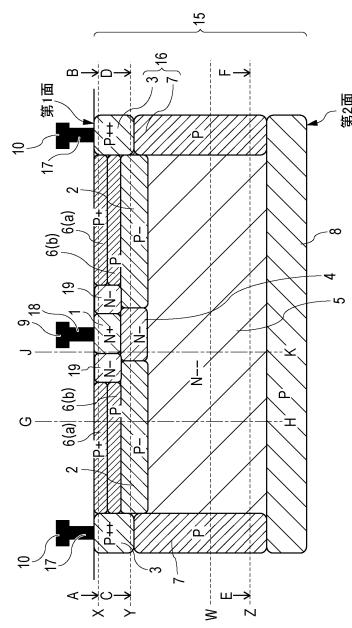

図6、図7を用いて、本アイデアの第1の実施形態の断面模式図及び平面模式図を説明する。なお、図6において、図1の第1半導体領域71が配される領域には、N型半導体領域1が配され、図1の第2半導体領域76が配される領域には、P型半導体領域6が配される。図6において、図1の第3半導体領域74が配される領域には、N型半導体領域4が配され、図1の第4半導体領域72が配される領域には、P型半導体領域2が配される。図6において、図1の第5半導体領域75が配される領域には、N型半導体領域5が配される。

#### 【0072】

まず図6を用いて、分離部16及び分離部16に挟まれた光電変換領域の断面構造について説明する。

10

#### 【0073】

分離部16は第1面から深さ方向に向かって配されたP型の半導体領域によって構成されている。具体的には、分離部16として、P型半導体領域3と、P型半導体領域7と、が、第1面から深さ方向にこの順に配され、接している。なお、P型半導体領域3は、P型半導体領域7、P型半導体領域8、P型半導体領域2、及びP型半導体領域6と電気的に接続されている。

#### 【0074】

P型半導体領域3の不純物濃度は、P型半導体領域6、P型半導体領域7、P型半導体領域8、及びP型半導体領域2の各々の不純物濃度よりも高い。これにより、P型半導体領域7とコンタクトプラグ17を接続するよりも、P型半導体領域3とコンタクトプラグ17を接続する方が接触抵抗を低くすることが可能となる。例えば、P型半導体領域3の不純物濃度は $1 \times 10^{19} \sim 10^{20} \text{ cm}^{-3}$ 程度とすることができます。

20

#### 【0075】

N型半導体領域1は、N型半導体領域4、後述のN型半導体領域5よりも不純物濃度の高い領域である。例えば、N型半導体領域1の不純物濃度は、 $6 \times 10^{18}$ 以上であり、N型半導体領域1には、分離部16に対して逆バイアスとなる電位が供給される。

#### 【0076】

N型半導体領域4の不純物濃度は、N型半導体領域1の不純物濃度よりも低い。例えば、N型半導体領域4の不純物濃度は、 $1 \times 10^{17}$ 以下でとすることができます。これにより、N型半導体領域4の付近の電荷がN型半導体領域1に移動しやすくなる。

30

#### 【0077】

P型半導体領域6の不純物濃度は、P型半導体領域2の不純物濃度よりも高い。例えば、P型半導体領域6の不純物濃度は、 $1 \times 10^{18} \sim 5 \times 10^{18} \text{ cm}^{-3}$ 程度であり、P型半導体領域2の不純物濃度は、 $5 \times 10^{17} \sim 1 \times 10^{18} \text{ cm}^{-3}$ 程度とすることができます。これにより、P型半導体領域6で光電変換された電荷が、P型半導体領域2を通って、N型半導体領域5に移動しやすくなる。

#### 【0078】

N型半導体領域19は、N型半導体領域1よりも不純物濃度が低い。例えば、N型半導体領域19の不純物濃度は、 $1 \times 10^{17} \sim 10^{18} \text{ cm}^{-3}$ 程度とすることができます。これにより、N型半導体領域1とP型半導体領域6の間で発生する高電界を緩和することができる。N型半導体領域1とP型半導体領域6の間で電荷がアバランシェ増幅されることを抑制することができる。

40

#### 【0079】

P型半導体領域2の不純物濃度は、P型半導体領域7の不純物濃度より低い。P型半導体領域2とN型半導体領域4とは、PN接合を形成する。このPN接合によって、N型半導体領域4のすべての領域が空乏層領域となる。さらに、この空乏層領域がN型半導体領域1の一部の領域まで延在する。延在した空乏層領域に強電界が誘起される。この強電界により、N型半導体領域1の一部の領域まで延びた空乏層領域に電子が移動すると、アバランシェ増幅が生じ、増幅された電荷に基づく電流がコンタクトプラグ18を介して配線9から出力される。つまり、本実施例において光検出領域は、N型半導体領域1の一部の

50

領域における空乏層領域となる。

【0080】

なお、本実施例において、N型半導体領域4をP型の領域ではなく、N型の領域で構成しているのは、空乏層をよりN型半導体領域5の深部までより深く広げることにより、より深部からの電荷取得を可能とするためである。

【0081】

さらに、N型半導体領域1、N型半導体領域4、P型半導体領域2の不純物濃度は、N型半導体領域1の一部に生じる空乏層領域においてアバランシェ増幅を起こす電位差を供給した際に、N型半導体領域1のすべての領域が空乏化しない不純物濃度に設定する。これは、半導体基板15の第1面に接するほど空乏層領域が広がると、半導体基板15の第1面にノイズが生じるおそれがあるからである。一方で、N型半導体領域4のすべての領域は空乏化するような不純物濃度に設定する。

【0082】

N型半導体領域4のすべての領域が空乏化する条件を式1に示す。ここでは、N型半導体領域4の不純物濃度を不純物濃度Ndとし、P型半導体領域2の不純物濃度を不純物濃度Naとし、電気素量を電気素量qとする。さらに、半導体の誘電率を誘電率εとし、N型半導体領域4とP型半導体領域2のPN接合間の電位差を電位差Vとし、P型半導体領域2に挟まれたN型半導体領域4の長さを長さDとする。

【0083】

【数1】

$$2 \times \sqrt{\frac{2\epsilon NaV}{qNd(Nd+Na)}} > D \quad \cdots \text{ (式1) }$$

【0084】

N型半導体領域1のすべての領域が空乏化しない不純物濃度を例えばN型半導体領域1の不純物濃度は $6.0 \times 10^{18}$  [atms/cm<sup>3</sup>]以上とする。その場合に、これらの空乏化条件を満たすような不純物濃度とは、P型半導体領域2の不純物濃度は $1.0 \times 10^{16}$  [atms/cm<sup>3</sup>]以上である。また、N型半導体領域4の不純物濃度は、 $1.0 \times 10^{17}$  [atms/cm<sup>3</sup>]以下である。ただし、これらの不純物濃度に限られない。

【0085】

そして、空乏層に誘起される深さ方向の電界が充分大きくなるように、N型半導体領域1及び分離部16の電位差を設定する。ここで、充分大きくなる電位差とは、電界の影響を受けた電荷がアバランシェ増幅を起こす電位差である。つまり、本構造の光検出素子がアバランシェダイオード(APDまたはSPAD)としての動作を実現するN型半導体領域1及びP型半導体領域3の電位差である。

【0086】

具体的には、N型半導体領域1及びP型半導体領域2の電位差は6V以上である。このとき、上述したように、N型半導体領域1と電気的に接続されたN型半導体領域4のすべての領域が、空乏層領域となり、且つN型半導体領域1の一部の領域まで延在した空乏層領域に、アバランシェ増幅が生じるような強電界が生じる。

【0087】

また、より好ましくは、N型半導体領域1及びP型半導体領域3の電位差は10V以上であり、30V以下である。このとき、例えば、N型半導体領域1には、10V以上の電位が供給され、P型半導体領域3には0V以下の電位が供給される。ただし、電位差が6V以上となれば、これらの電位の値には限られない。

【0088】

10

20

30

40

50

ところで、本実施例は、電荷をN型半導体領域5で発生させ、N型半導体領域1で収集して読み出す。すなわち、第1導電型の半導体領域で発生した電荷を、第1導電型の半導体領域から読み出している。

【0089】

また、P型半導体領域6やP型半導体領域2で光電変換により発生した電荷も、N型半導体領域5及びN型半導体領域4を介してN型半導体領域1で収集して読み出すことができる。

【0090】

これに対して、米国特許第9209336号明細書に記載のデバイスは、N型のエピタキシャル層2で発生した電荷をN型のエピタキシャル層2とp型のアノード領域14との界面でアバランシェ増幅させ、p型のアノード領域14から電荷を読み出している。すなわち、第1導電型の半導体領域で発生した電荷を、第2導電型の半導体領域から読み出している。この点においても、本実施形態は米国特許第9209336号明細書に記載されたデバイスとは異なる。

10

【0091】

図6において、P型半導体領域2とN型半導体領域4を設けずに、不純物濃度が濃いN型半導体領域1のすぐ下部に、N型半導体領域1よりも不純物濃度の低いN型半導体領域5を配することを想定する。この場合、N型半導体領域5で電荷を発生させ、N型半導体領域1から電荷を読み出すことは可能であるが、本実施例と同等の電圧条件下でアバランシェ増幅させることは難しい。これは、N型半導体領域1及びP型半導体領域3の間に印加した電位差の大部分がN型半導体領域5の空乏層領域にかかることにより、N型半導体領域1近傍のアバランシェ増幅領域にかかる電位差が小さくなってしまうためである。他方、本実施例では、N型半導体領域5はN型半導体領域4と接する箇所を除いた各方面でP型半導体領域に囲まれるため、N型半導体領域5のポテンシャルはN型半導体領域1よりも、周囲のP型半導体領域に近いレベルとなる。すなわち、P型半導体領域2で基板深部への空乏層の過度な広がりを抑制することで、上記の印加する電位差の大部分をN型半導体領域1近傍のアバランシェ増幅領域に集中させることができる。この結果、より低電圧で光電荷をアバランシェ増幅させることができる。

20

【0092】

N型半導体領域5の不純物濃度は、N型半導体領域4の不純物濃度以下、もしくは同等の不純物濃度である。少なくとも、N型半導体領域5の不純物濃度はN型半導体領域1の不純物濃度よりも少なければよい。

30

【0093】

図6では、N型半導体領域5は一例として同一の不純物濃度からなる領域を示した。しかし、N型半導体領域5は、半導体基板15の第1面の側に電荷が移動するようなポテンシャル構造になるように不純物濃度の勾配を有していた方がよい。そのような不純物濃度の勾配とすることで、N型半導体領域1に電荷を移動しやすくすることが可能である。

【0094】

また、半導体基板15の第1面の側に電荷が移動するようなポテンシャル構造になるように不純物濃度の勾配を有する場合に、N型半導体領域5が配された領域において第1面の側がN型半導体領域であり、第2面の側がP型半導体領域となってもよい。

40

【0095】

もしくは、P型半導体領域2の不純物濃度よりも不純物濃度が低いP型半導体領域が、N型半導体領域5の代わりに配されてもよい。その場合においても半導体基板15の第1面の側に電荷が移動するようなポテンシャル構造になるように不純物濃度の勾配を有していることが好ましい。

【0096】

例えば、このP型半導体領域は、第1領域と、第1面に対して第1領域よりも深い位置に配された第2領域と、第1面に対して第2領域よりも深い位置に配された第3領域とを有する。そして、第1領域を第1不純物濃度、第2領域を第2不純物濃度、第3領域を第

50

3不純物濃度とした時に、第1不純物濃度 < 第2不純物濃度 < 第3不純物濃度としてもよい。なお、第1不純物濃度は、P型半導体領域2の不純物濃度よりも低くなる。ここでは、N型半導体領域5の代わりに配したP型半導体領域を3つの領域に分けたが、この限りではない。

#### 【0097】

P型半導体領域8は、N型半導体領域5よりも深い位置に配されており、光電変換領域の深さを定義する。N型半導体領域5は、P型半導体領域2とP型半導体領域7とP型半導体領域8との各々とPN接合を形成する。P型半導体領域8の不純物濃度は、P型半導体領域2の不純物濃度よりも高くする。これにより、P型半導体領域8の付近で生じた電荷は、第1面方向に移動しやすくなる。

10

#### 【0098】

N型半導体領域1にはコンタクトプラグ18が接続され、コンタクトプラグ18には配線9が接続される。また、P型半導体領域3にはコンタクトプラグ17が接続され、コンタクトプラグ17には配線10が接続される。配線9または配線10は、クエンチ動作を行うための抵抗素子などの制御部202に接続される。以下では、制御部202が配線9に接続されるものとして説明する。

#### 【0099】

図6では、コンタクトプラグ17及び配線10が第1面の側に配されるものとして説明した。しかし、コンタクトプラグ17及び配線10が第2面の側に配されてもよい。

20

#### 【0100】

コンタクトプラグ17及び配線10が第2面の側に配される場合において、P型半導体領域8のうちコンタクトプラグ17が配される領域の不純物濃度は、P型半導体領域7の不純物濃度よりも高い方がよい。つまりP型半導体領域3となる。このとき、第1面側に配されているP型半導体領域3には、コンタクトプラグ17が接続されなくなる。よって、P型不純物の黄土が、P型半導体領域7の方がP型半導体領域6より高い場合には、P型半導体領域3の不純物濃度をP型半導体領域7と同程度としてもよい。

#### 【0101】

また、分離部16が第1面側に絶縁分離部を有する場合においても、コンタクトプラグ17及び10は、第2面側に配される。このとき、分離部16は、第1面から深さ方向に絶縁分離部、P型半導体領域7、P型半導体領域3の順に重なるように接して配される。

30

#### 【0102】

次に、図7を用いて、図6の断面構造の任意の深さにおける分離部16及び分離部16に挟まれた光電変換領域の平面構造について説明する。図7では各半導体領域の境界を円形で描いているが、これに限られない。

#### 【0103】

図7(a)は、図6の深さXにおける線分ABの平面模式図を示す。N型半導体領域1は、N型半導体領域19に内包される。また、N型半導体領域19は、P型半導体領域6に内包され、P型半導体領域6は、P型半導体領域3に内包される。また、P型半導体領域6の面積は、N型半導体領域1の面積よりも大きい。

#### 【0104】

図7(b)は、図6の深さYにおける線分CDの平面模式図を示す。N型半導体領域4は、P型半導体領域2に内包される。P型半導体領域2は、P型半導体領域3に内包される。

40

#### 【0105】

図7(c)は、図6の深さZにおける線分EFの平面模式図を示す。N型半導体領域5は、P型半導体領域7に内包される。なお、図7(b)と図7(c)を重ねたとき、平面視においてN型半導体領域4及びP型半導体領域2は、N型半導体領域5と重なる。

#### 【0106】

また、図7(a)と図7(b)を重ねたとき、平面視においてN型半導体領域1は、N型半導体領域4の少なくとも一部の領域と重なり、P型半導体領域6はP型半導体領域2

50

の少なくとも一部と重なる。

【0107】

このような構成とすることで、電荷検出領域の面積が最小化され、かつ、波長の短い光を含む光の光電変換により生成された電荷の電荷検出領域への収集量を向上した光検出装置を実現できる。

【0108】

次に、図8を用いて、図6に示した断面模式図における、アバランシェダイオードの製造方法を説明する。特に順番に関して説明のない工程に関しては適宜順序を入れ替えてよい。また、図8にて説明を省略する工程に関しては、周知の製造方法を適用することが可能である。

10

【0109】

図8(a)に示すように、半導体基板15の第1面に対する法線方向から、N型半導体領域5となる領域にP型の不純物イオン注入(以下、イオン注入)を行う。これにより、半導体基板15の第1面に対して深い位置にP型半導体領域8を形成する。

【0110】

次に図8(b)に示すように、半導体基板15の第1面にマスク77を形成する。マスク77には、開口部30を有する。そして、半導体基板15の第1面に対して法線方向から、P型のイオン注入を行うことでP型半導体領域3及びP型半導体領域7を、第1面からこの順に配されるように形成する。このとき、P型半導体領域7とP型半導体領域8の一部が接続する。また、P型半導体領域7の不純物濃度よりもP型半導体領域3の不純物濃度が高くなるようにする。具体的には、異なるイオン注入エネルギーで複数回イオン注入を行うなどの方法がある。

20

【0111】

次にマスク77を除去し、マスク78を配する。マスク78は、開口部32を有する。そして、図8(c)に示すように、半導体基板15の第1面に対して法線方向に平行な方向から、P型のイオン注入を行うことでP型半導体領域2となる領域を形成する。その後、P型半導体領域2となる領域を形成するために行ったP型のイオン注入を行った位置よりも第1面に対して浅い位置に、同じくP型のイオン注入を行いP型半導体領域6となる領域を形成する。ここでは、P型半導体領域2となる領域を形成した後に、P型半導体領域6となる領域を形成したが逆でもよい。

30

【0112】

次にマスク78を除去し、マスク79を配する。マスク79は開口部33を有する。図8(d)に示すように、半導体基板15の第1面に対する法線方向に平行な方向から、P型半導体領域2となる領域が配される深さにN型のイオン注入を行うことで、P型半導体領域2となる領域の一部にN型半導体領域4を形成する。

【0113】

次にマスク79を除去し、マスク80を配する。マスク80は開口部34を有する。半導体基板15の第1面に対して法線方向に平行な方向から、半導体基板15の第1面の側にN型のイオン注入を行うことでN型半導体領域19を形成する。ここでは、N型半導体領域4を先に形成したが、N型半導体領域19を先に形成してもよい。

40

【0114】

次にマスク80を除去し、マスク81を配する。マスク81は開口部35を有する。半導体基板15の第1面に対して法線方向に平行な方向から、半導体基板15の第1面の側にN型のイオン注入を行うことでN型半導体領域1を形成する。ここでは、N型半導体領域19を先に形成したが、N型半導体領域1を先に形成してもよい。

【0115】

なお、N型半導体領域1、N型半導体領域4、及びN型半導体領域19を形成するために入れる不純物イオンとして、異なる熱拡散係数を有する不純物イオンを用いてよい。このような構成によれば、N型半導体領域1、N型半導体領域4、及びN型半導体領域19が配される領域における、ポテンシャル設計の自由度が向上する。

50

## 【0116】

また、図8(d)の工程を経ずに、図8(f)の工程でN型半導体領域4を形成してもよい。その場合、入射面である第1面に対して浅い位置へのイオン注入であるN型半導体領域1よりも、第1面に対して深い位置へのイオン注入であるN型半導体領域4の方が、第1面に対する平行な方向への不純物イオンの拡散が大きくなる。結果として、N型半導体領域1は平面視でN型半導体領域4に内包される。また、同一マスクを用いてN型半導体領域1及びN型半導体領域4を形成するため、両半導体領域の位置ズレを抑制することが可能であり、位置ズレにより生じ得るトンネル効果を抑制することが可能となる。

## 【0117】

このような構造により、特許文献1に示すようなアバランシェダイオード全体でアバランシェ降伏が起こる構成に比べて、感度特性を悪化させることなく、トンネル効果により生じるノイズ電荷を低減させることが可能となる。さらに、深さX~Yにおいて光電変換された電荷は、ポテンシャル勾配によりN型半導体領域5に流れ込み、N型半導体領域4を通じてN型半導体領域1の近傍でアバランシェ増幅され、信号としてカウントすることが可能となる。すなわち、基板浅部で光電変換された電荷も感度として検出することができる。

10

## 【0118】

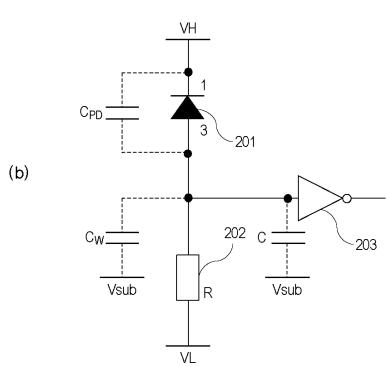

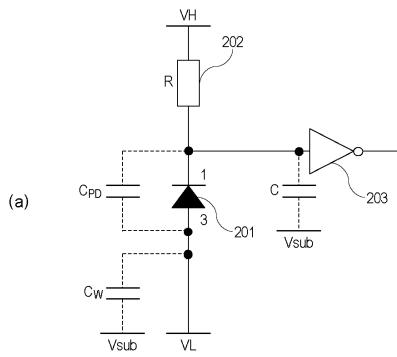

次に図9を用いて、本実施例の制御部202について説明する。本実施例において制御部202は、二つの構成を有する。一つ目の構成は図9(a)に示すように光電変換部201の高い電位VHが供給されるカソードの側に制御部202が配される構成である。二つ目の構成は、図9(b)に示すように光電変換部201の低い電位VLが供給されるアノードの側に制御部202が配される構成である。

20

## 【0119】

図9(a)および図9(b)の構成において、アバランシェ電流により波形整形部203の入力電位が変化してから、制御部202による電圧降下によって光電変換部201の初期状態のバイアスに復帰するまでには一定の時間が必要である。このように、一度電荷を検出してから、次に電荷を検出することが可能なバイアス状態に戻るまでの期間をDead timeという。このDead timeが短いほど、時間あたりにカウントできる電荷の数が増加し、光検出装置としてのダイナミックレンジが大きくなる。

30

## 【0120】

例として、制御部202が抵抗素子である場合には、本実施例のアバランシェダイオードのDead time(d[s])は抵抗(R[ ])と、入力端子の容量(C[F])、の積で決まる。以下の式で、光電変換部201のPN接合容量はCpd、光電変換部201のウエルの容量はCw、配線・拡散層の寄生容量はCで示す。

## 【0121】

図9(a)の場合には、Dead timeは、式2で求められる。

$$d = R(C_{pd} + C) \quad \dots \text{ (式2)}$$

## 【0122】

図9(b)の場合には、Dead timeは、式3で求められる。

$$d = R(C_{pd} + C_w + C) \quad \dots \text{ (式3)}$$

40

## 【0123】

光電変換部201のPN接合容量Cpdは、アバランシェ増幅を生じさせるために強電界を誘起する光検出領域のPN接合容量である。そのため、PN接合容量Cpdは、光検出領域の面積に比例して変化する。つまり、光検出効率をあげるために光検出領域の面積が大きくなると、PN接合容量Cpdが大きくなり、Dead timeが増加する。その結果、ダイナミックレンジが低下してしまう。

## 【0124】

すなわち、光検出効率とダイナミックレンジはトレードオフ関係となっている。一方、本実施例の構造によれば、光電変換領域の面積を大きく確保しながら、光検出領域の面積を小さくすることができる。そのため、Cpdを低減し、Dead timeを低減

50

することができる。結果として、高い光検出効率と高いダイナミックレンジを両立することができる。

【0125】

本実施例の画素構造によるダイナミックレンジの向上効果は、図9の(b)よりも図9(a)の構成の方が顕著にあらわれる。例えば、従来のS P A D構造に対する本実施例のS P A D構造のC p dの比をA( $0 < A < 1$ )とすると、図9(a)と図9(b)のそれぞれの回路方式におけるダイナミックレンジの向上率はそれぞれ数式4、数式5で表される。

$$1 = (1 - A) C p d / (A C p d + C) \quad \dots \text{ (数式4)}$$

$$2 = (1 - A) C p d / (A C p d + C w + C) \quad \dots \text{ (数式5)}$$

【0126】

数式4および数式5において、ダイナミックレンジがDead timeに反比例することを利用して計算した。上式から、常に $1 > 2$ が満たされることがわかる。

【0127】

以上のことから、本実施例の構成において図9(a)、図9(b)を適応した際にダイナミックレンジの向上率は、図9(a)の方が図9(b)より原理的に高くなる。

【0128】

ここまででは制御部202を抵抗素子として説明したが、能動クエンチ回路の場合でも、同様である。

【0129】

以上から、本実施例の画素に対する制御部202は、光電変換部201のアノードの側に配する場合よりもカソードの側に配する場合の方がダイナミックレンジの向上効果を大きくすることが可能である。

【0130】

本実施例の構成によれば、電荷が移動する経路を形成することで光検出効率の低下を抑制することが可能となる。つまり、光検出効率の低下を抑制しながら、ノイズを低減することが可能となる。

【0131】

(実施例2)

図10は、本アイデアにおける第2の実施形態の断面図である。図1～図8と同様の機能を有する部分には同様の符号を付し、詳細な説明を省略する。図10は、図6のP型半導体領域6に関して、不純物濃度の異なるP型半導体領域6(a)とP型半導体領域6(b)で構成されている点で異なる。

【0132】

図10において、P型半導体領域6(a)はP型半導体領域6(b)よりも不純物濃度が高い(N型の不純物濃度が低い)。また、P型半導体領域6(b)はP型半導体領域2よりも不純物濃度が高い(N型の不純物濃度が低い)。これにより、図3に記載する線分GHの深さX-Yにかけてのポテンシャル勾配が大きくなり、深さX-Yの間で光電変換された電荷がN型半導体領域5に流れ込みやすくなる。その結果、実施例1の構造と比較して、短波長側の感度が向上する。

【0133】

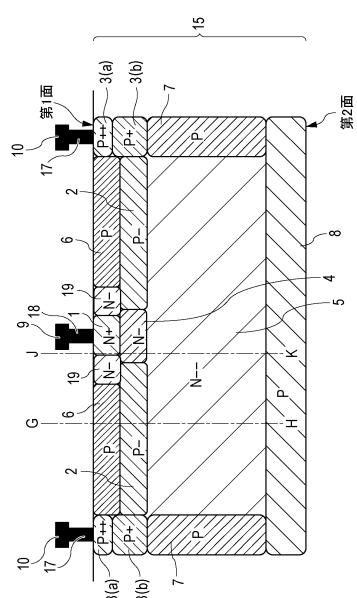

(実施例3)

図11は、本アイデアにおける第3の実施形態の断面図である。図1～図8と同様の機能を有する部分には同様の符号を付し、詳細な説明を省略する。図11は、図6のP型半導体領域3に関して、不純物濃度の異なるP型半導体領域3(a)とP型半導体領域3(b)で構成されている点で異なる。

【0134】

図11において、P型半導体領域3(a)はP型半導体領域3(b)よりも不純物濃度が高いことを特徴とする。図6において、P型半導体領域3は、コンタクトプラグ17と基板との間のコンタクト抵抗を下げるために必要であり、同時に、P型半導体領域6で光

10

20

30

40

50

電変換された電荷の隣接画素への混入を防止するために必要である。しかし、P型半導体領域3が深く配置されると、P型半導体領域3の領域内で発生した発生電荷が、N型半導体領域5に流れ込みやすくなり、ノイズ特性が悪化する。従って、P型半導体領域3は、前記目的を満たす範囲であれば浅い方がよい。その場合、P型半導体領域3の浅化に伴ってP型半導体領域7を第1面側へ延在させると、P型半導体領域6とP型半導体領域7が近接する。P型半導体領域6とP型半導体領域7の不純物濃度が同等である場合、P型半導体領域6の領域内で光電変換された電荷がP型半導体領域7を通過して隣接画素へ漏れこみやすくなり、混色成分が増加する。

#### 【0135】

前記課題を解決するため、隣接画素間に第1面側から深さ方向へ順に、P型半導体領域3(a)、P型半導体領域3(a)より低濃度のP型半導体領域3(b)、P型半導体領域3(b)より低濃度のP型半導体領域7を形成する。その際、P型半導体領域3(b)はP型半導体領域6より不純物濃度が高く、P型半導体領域7はP型半導体領域2より不純物濃度が高いことを特徴とする。これらの構成により、コンタクトプラグ17と基板との間のコンタクト抵抗低減、隣接画素への混色防止、ノイズ特性の悪化防止を両立することができる。

10

#### 【0136】

##### (実施例4)

図12は、本実施例におけるアバランシェダイオードおよび制御部の断面模式図である。図1～図15と同様の機能を有する部分には同様の符号を付し、詳細な説明を省略する。

20

#### 【0137】

図12では、光電変換部201と制御部202とが異なる半導体基板に配されている。光電変換部201を構成するアバランシェダイオードの構成は実施例1と同様である。半導体基板15には、光電変換部201が複数配され、ここでは例として2つのアバランシェダイオードが配された構成を示す。半導体基板1102には、制御部202と、制御部202に接続された配線1107が配される。ここでは、半導体基板1102に、制御部202および配線1107が配される構成を示したが、その他の回路が配されていてもよい。

#### 【0138】

本実施例のアバランシェダイオードは、裏面照射型の構成である。また、光はN型半導体領域5からN型半導体領域1に向かう方向に入射される。このとき、光はマイクロレンズ1103、カラーフィルタ1104を通ってN型半導体領域5に入射される。

30

#### 【0139】

前述したようにN型半導体領域5で光電変換され、生じた電荷は、N型半導体領域4を通り、N型半導体領域1に移動する。N型半導体領域1と、P型半導体領域2とN型半導体領域4との間に生じる空乏層との間の電界によって、アバランシェ増幅が生じ、配線9に電流が流れる。

#### 【0140】

配線9は、接続部1105を介して、別途作成した半導体基板1102に設けられた制御部202に接続される。

40

#### 【0141】

アバランシェダイオードごとに検出した信号は、半導体基板1102の画素部の周辺に設けられた走査回路などによって信号の処理が行われる。なお、走査回路は、半導体基板15および半導体基板1102と異なる半導体基板に配されてもよい。

#### 【0142】

本実施例の構成によれば、アバランシェダイオードが配された半導体基板15に対して異なる半導体基板1102を積層している。そして積層した半導体基板1102に、制御部202などの処理回路を配することによって、アバランシェダイオードの開口率を高め、光検出効率を向上することが可能となる。

#### 【0143】

50

なお、本実施例において、各アバランシェダイオードにマイクロレンズ 1103 を配する場合、マイクロレンズ 1103 の光軸が、平面視で N 型半導体領域 4 に内包されるような位置関係とする方がよい。例えば光電変換素子 101 の中央部において垂直光が入射する場合、N 型半導体領域 5 の内部での信号電荷の発生確率の分布は、マイクロレンズ 1103 の光軸付近で最大となる。ここで、マイクロレンズの光軸とは、平面視でマイクロレンズの中心を通る、半導体基板 15 に垂直な軸である。

【0144】

本実施例の構成により、マイクロレンズ 1103 の光軸が N 型半導体領域 4 に平面的に内包されれば、N 型半導体領域 5 において、平面視で N 型半導体領域 4 に近い位置で電荷が生じやすくなる。そして、平面的に遠い位置で生じる電荷の発生確率を低減することが可能となり、半導体基板 15 の第 1 面に対して浅い位置で生じた電荷と、深い位置で生じた電荷とで、光検出領域で電荷検出するまでの時間分解能の低下を抑制することが可能となる。

10

【0145】

なお、本実施例では裏面照射型のフォトダイオード構成をとるが、表面照射型であっても本実施例による効果、すなわち高光検出効率と低 DCR の両立を実現することができる。ただし、本実施例では、光電変換部を裏面の側に形成する構成をとるため、表面照射型の場合と比べ裏面照射型の場合の方が、基板の最表面付近（光入射の側）で発生した電荷を高効率で検出できる。すなわち、短波長から長波長までプロードな波長帯で高い光検出効率を実現できるという点から、本実施例の光電変換部 201 は裏面照射型とする方が好みしい。

20

【0146】

本実施例は、すべての実施例に適用可能である。

【0147】

（実施例 5）

本実施例では、各実施例の光検出装置 1010 を用いた光検出システムの一例を説明する。図 13 を用いて光検出システムの一例である不可視光検出システムおよび PET 等の医療診断システムについて説明する。図 1 ~ 図 12 と同様の機能を有する部分には同様の符号を付し、詳細な説明を省略する。なお、本実施例の画素 100 は、図 5 のカウンタ回路 209 の代わりに TDC とメモリを有する。ここでは、TDC を TDC 204 とし、メモリをメモリ 205 として説明する。

30

【0148】

図 13 は、不可視光検出システムの構成を説明するブロック図である。不可視光検出システムは、波長変換部 1201、データ処理部 1207 を有し、光検出装置 1010 を複数有する。

【0149】

照射物 1200 は、不可視光となる波長帯の光を照射する。波長変換部 1201 は、照射物 1200 から照射された不可視光となる波長帯の光を受光し、可視光を照射する。

【0150】

波長変換部 1201 から照射された可視光が入射された光電変換部 201 は光電変換し、制御部 202、波形整形部 203、TDC 204 を介して、光検出装置 1010 は光電変換した電荷に基づく信号に基づくデジタル信号をメモリ 205 に保持する。複数の光検出装置 1010 は、一つの装置として形成されていてもよいし複数の装置が配列することで形成されてもよい。

40

【0151】

複数の光検出装置 1010 のメモリ 205 で保持された複数のデジタル信号は、データ処理部 1207 によって信号処理が行われる。ここでは、信号処理手段として複数のデジタル信号から得られる複数の画像の合成処理を行う。

【0152】

次に不可視光検出システムの具体的な例として PET 等の医療診断システムの構成につ

50

いて説明する。

【0153】

照射物1200である被験者は、生体内から放射線対を放出する。波長変換部1201は、シンチレータを構成し、シンチレータは、被験者から放出された放射線対が入射すると可視光を照射する。

【0154】

シンチレータから照射された可視光が入射された光電変換部201は光電変換し、制御部202、波形整形部203、TDC204を介して、光検出装置1010は光電変換した電荷に基づく信号に基づくデジタル信号をメモリ205に保持する。つまり、光検出装置1010は、被験者から放出された放射線対の到達時間を検出するために配され、シンチレータから照射された可視光を検出し、デジタル信号をメモリ205に保持する。

10

【0155】

複数の光検出装置1010のメモリ205で保持されたデジタル信号は、データ処理部1207において信号処理される。ここでは、信号処理手段として複数のデジタル信号から得られる複数の画像を用いて画像再構成などの合成処理を行い、被験者の生体内の画像の形成を行う。

【0156】

(実施例6)

本実施例では、各実施例の光検出装置1010を用いた光検出システムの一例を説明する。図1～図12と同様の機能を有する部分には同様の符号を付し、詳細な説明を省略する。

20

【0157】

図14では、光検出システムの一例である距離検出システムについて説明する。なお、本実施例の画素100は、図5のカウンタ回路209の代わりにTDCとメモリを有する。ここでは、TDCをTDC204とし、メモリをメモリ205として説明する。

【0158】

図14を用いて、本実施例の距離検出システムのブロック図の一例を説明する。距離検出システムは、光源制御部1301、発光部1302、光学部材1303、光検出装置1010、距離算出部1309を有している。

30

【0159】

光源制御部1301は発光部1302の駆動を制御する。発光部1302は、光源制御部1301から信号を受けた際に、撮影方向に対して短パルス(列)の光を照射する。

【0160】

発光部1302から照射された光は、被写体1304に反射する。反射光は光学部材1303を通して、光検出装置1010の光電変換部201で受光し、光電変換された電荷に基づく信号が波形整形部203を介してTDC204に入力される。

【0161】

TDC204は、光源制御部1301から得られる信号と、波形整形部203から入力された信号とを比較する。そして、発光部1302がパルス光を発光してから被写体1304を反射した反射光を受光するまでの時間を高精度にデジタル変換する。TDC204から出力されたデジタル信号は、メモリ205に保持される。

40

【0162】

距離算出部1309は、メモリ205に保持された複数回測定分のデジタル信号を元に、光検出装置から被写体までの距離を算出する。この距離検出システムは例えば車載に適用することができる。

【0163】

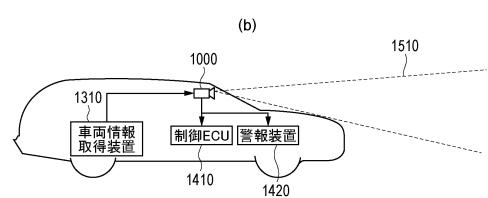

次に、図5のカウンタ回路209を用いた場合の光検出システムの一例を図15に示す。図15(a)及び(b)では、光検出システムの一例である車載カメラに関する光検出システムについて説明する。

【0164】

50

光検出システム 1000 は、本発明に係る測距画素および撮像画素を含む光検出システムである。光検出システム 1000 は、光検出装置 1010 により取得した複数のデジタル信号に対し、画像処理を行う画像処理部 1030 を有する。さらに、光検出システム 1000 は、画像処理部 1030 により取得した複数の画像データから視差（視差画像の位相差）の算出を行う視差算出部 1040 を有する。

【0165】

また、光検出システム 1000 は、算出された視差に基づいて対象物までの距離を算出する距離計測部 1050 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 1060 と、を有する。ここで、視差算出部 1040 や距離計測部 1050 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。

10

【0166】

衝突判定部 1060 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されてもよい。また、FPGA (Field Programmable Gate Array) やASIC (Application Specific Integrated Circuit) などによって実現されてもよい。さらに、これらの組合せによって実現されてもよい。

20

【0167】

光検出システム 1000 は車両情報取得装置 1310 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、光検出システム 1000 は、衝突判定部 1060 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 1410 と接続されている。

【0168】

また、光検出システム 1000 は、衝突判定部 1060 での判定結果に基づいて、ドライバーへ警報を発する警報装置 1420 とも接続されている。例えば、衝突判定部 1060 の判定結果として衝突可能性が高い場合、制御 ECU 1410 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 1420 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

30

【0169】

本実施例では車両の周囲、例えば前方または後方を光検出システム 1000 で撮像する。図 15 (b) に、車両前方を撮像する場合の光検出システムを示した。また、上記では、他の車両と衝突しない制御を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、光検出システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム (ITS) 等、広く物体認識を利用する機器に適用することができる。

40

【符号の説明】

【0170】

- 7 1 第 1 半導体領域

- 7 2 第 4 半導体領域

- 7 4 第 3 半導体領域

- 7 5 第 5 半導体領域

- 7 6 第 2 半導体領域

50

【四面】

【 四 1 】

【 図 2 】

【 义 3 】

〔 4 〕

【図5】

【図6】

【図7】

【図8】

10

20

30

40

50

【図 9】

【図 10】

10

20

【図 11】

【図 12】

30

40

50

【図13】

【図14】

10

20

【図15】

30

40

50

---

フロントページの続き

(56)参考文献

米国特許出願公開第2005/0258449(US, A1)

米国特許出願公開第2013/0099091(US, A1)

特開2016-009691(JP, A)

米国特許出願公開第2017/0186798(US, A1)

特開2017-112169(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H04N 5/369

H01L 31/107