**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| (51) Int. Cl. <sup>6</sup><br>G11C 16/00                                                                                                                                                                                                                                                                                                                                                                                                     | (11) 공개번호      특 1995-0006866<br>(43) 공개일자      1995년03월21일 |

| (21) 출원번호      특 1994-0020700<br>(22) 출원일자      1994년08월22일                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

| (30) 우선권주장      8/109,886 1993년08월23일 미국(US)<br>(71) 출원인      어드밴스드 마이크로 디바이시즈, 인코포레이티드 미키오 이시마루<br>미합중국 캘리포니아 서니베일 원 에이엠디 플레이스 (우편번호 : 94088)<br>(72) 발명자      청 케이. 창<br>미합중국 캘리포니아 서니베일 산 후안 드라이브 627 #4 (우편번호 : 94086)<br>자니 씨. 첸<br>미합중국 캘리포니아 쿠퍼ти노 웨스틀린 웨이 1038 (우편번호 : 95104)<br>マイ클 애이. 반 버스커크<br>미합중국 캘리포니아 산 호세 페이비언 드라이브 1742 (우편번호 : 95124)<br>리 이. 클리브랜드<br>미합중국 캘리포니아 산타 클라라 라센 플레이스 1870 (우편번호 : 95051)<br>(74) 대리인      박장원 |                                                             |

**심사청구 : 없음****(54) 고 내구성을 갖는 플래시 이이피롬 어레이****요약**

개선된 종복 - 소거된 비트 정정 구조는 고 내구성을 제공하도록 소거 동작 후에, 플래시 EEPROM 메모리 셀의 어레이에서 종복 - 소거된 메모리 셀 상의 정정 동작을 실행하도록 제공된다. 감지 회로소자(20)는 APDE 동작동안 종복 - 소거된 비트를 나타내는 열 누설 전류를 검출하고, 메모리 셀내에 저장된 데이터를 나타내는 논리 신호를 발생시키도록 사용된다. 데이터 입력 버퍼 회로(26)는 논리 신호 및 메모리 셀내에 프로그램된 데이터를 나타내는 데이터 신호를 비교함으로서 비트 정합 신호를 발생시킨다. 펄스 카운터(30)는 데이터 입력 버퍼 회로에 접속되어 제공되어진 다수의 프로그래밍 펄스를 계수한다. 데이터 입력 버퍼 회로는 비트 정합 신호가 하이 논리 레벨에 있는 펄스 카운터에 대한 비트 라인의 열중 특정 하나에만 선택적으로 접속되어짐으로써 비트 라인의 열중 특정 하나에만 접속된 종복 - 소거된 메모리 셀을 재 프로그램하게 된다.

**대표도****도 1****명세서**

[발명의 명칭]

고 내구성을 갖는 플래시 이이피롬 어레이

[도면의 간단한 설명]

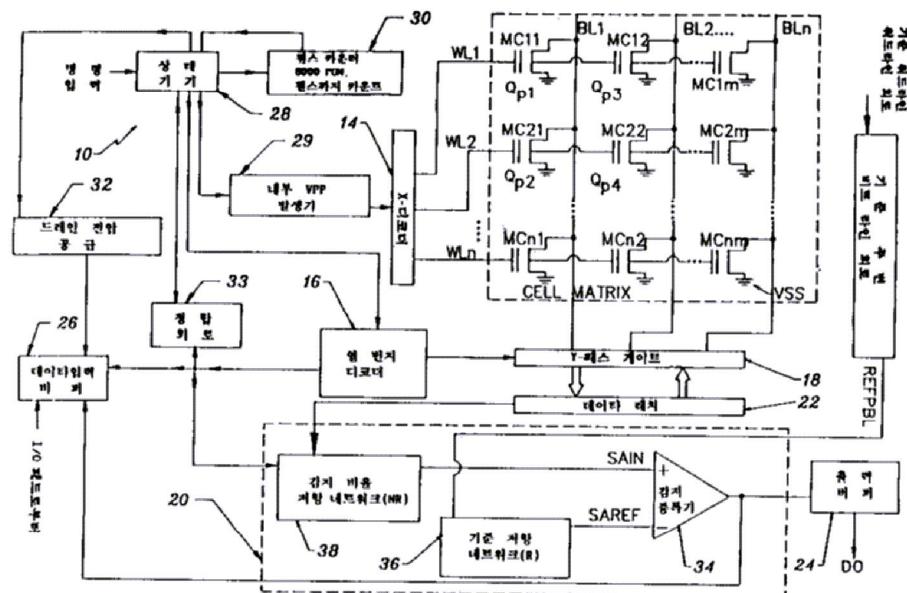

제1도는 본 발명에 따라 개선된 종복 - 소거(over - erased)비트 정정 구조를 갖는 반도체 집적 회로 메모리 소자의 블록도.

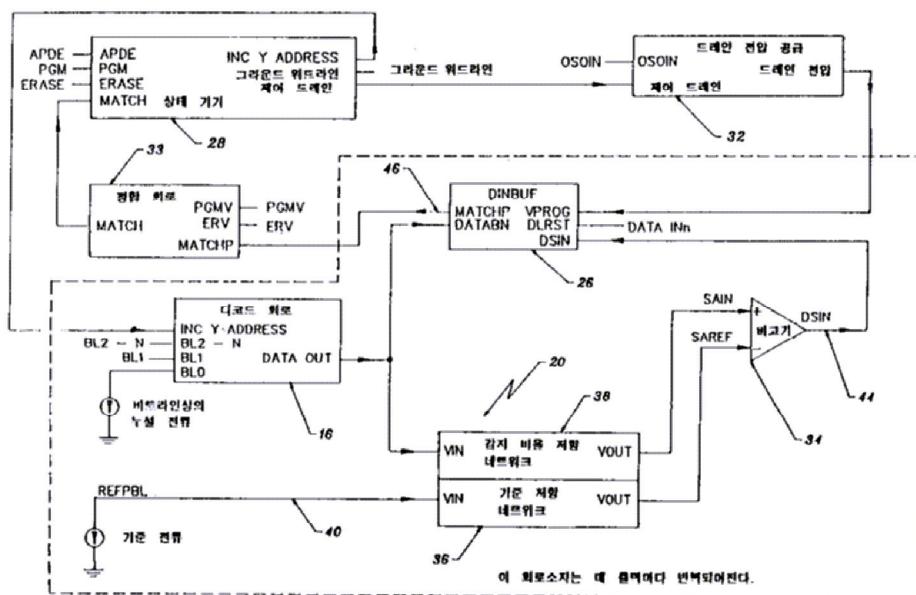

제2도는 제1도의 종복 - 소거 비트 정정의 단순 블럭도.

본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음.

**(57) 청구의 범위****청구항 1**

메모리 소자내의 종복 - 소거된 메모리 셀상의 정정 동작을 실행하는 종복 - 소거된 비트 정정 구조를 구비한 반도체 집적 회로 메모리 소자로서, 상기 정정 구조는, 워드 라인의 행 및 상기 워드 라인의 행과

교차되는 비트 라인의 열로 배열되고, 그 게이트가 상기 워드 라인의 행 중 하나에 접속되고, 그 드레인이 상기 비트 라인의 열중 하나에 접속되고, 그 소오스가 접지 전위에 접속되는 부동 게이트 어레이 트랜지스터를 각각 포함하는 다수의 메모리 셀을 갖는 셀 매트릭스(12)와, 행 번지신호에 응답하고, 상기 셀 매트릭스에 운용적으로 접속되어 상기 워드라인의 열중 하나를 선택하는 행 디코더 수단(14)과, 열 번지 신호에 응답하고, 상기 셀 매트릭스에 운용적으로 접속되어 상기 비트라인의 열중 하나를 선택하는 열 디코더 수단(16)과, 상기 비트라인의 열에 대한 기준 전류를 제공하는 기준 주변 비트 라인회로 수단(42)과, APDE 모드 동작동안, 상기 비트라인의 열중 선택된 하나에서의 누설 전류 및 상기 비트 라인의 열중 선택된 하나와 관련된 기준 전류를 비교하여, 상기 비트 라인 누설 전류가 상기 기준 전류보다 크면 중복-소거된 메모리 셀을 나타내는 하이 논리 레벨에 있고 상기 비트 하인 누설 전류가 상기 기준 전류보다 작으면 적정 프로그램된 메모리 셀을 나타내는 로우 논리 레벨에 있는 메모리 셀내에 저장된 데이터를 나타내는 논리 신호를 발생시키는 감지회로 수단(20)과, 상기 논리신호 및 메모리 셀내에 프로그램된 데이터를 나타내는 데이터 신호를 비교하여 상기 논리신호 및 상기 데이터신호가 동일할 때 하이 논리 레벨에 있는 비트 정합 신호를 발생시키는 데이터 입력버퍼회로 수단(26)과, 상기 데이터 입력 버퍼 회로 수단에 접속되어 제공되어진 다수의 프로그래밍 펄스를 계수하는 펄스 카운터 수단(30)으로 구성되고, 상기 데이터 입력회로 수단이 상기 비트 정합 신호가 하이 논리 레벨에 있는 상기 펄스 카운터 수단에 대해서 상기 비트 라인의 열 중 특정 하나에만 선택적으로 접속되어 상기 비트 라인의 열중 특정 하나에만 접속된 중복-소거된 메모리 셀을 재프로그래ム하도록 하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 2

제1항에 있어서, 상기 다수의 프로그래밍 펄스는 중복-소거된 메모리 셀에서 어레이 트랜지스터의 네가티브 문턱값을 파지티브 문턱 전압으로 변경시키도록 제공되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 3

제1항에 있어서, 상기 감지회로 소자는, 상기 비트 라인의 열에 운용적으로 접속되어 상기 비트 라인의 열중 선택된 하나에 누설 전류에 부합하는 제1저항 값을 발생시키는 감지 비율 저항 네트워크(38)와, 상기 기준 주변 비트 라인회로에 운용적으로 접속되어 기준 전류에 부합하는 제2저항 값을 발생시키는 기준 전항 네트워크 수단(36)과, 감지 비율 저항 네트워크 수단에 접속된 제1입력 및 상기 기준 저항 네트워크 수단에 접속된 제2입력을 구비하여 열 누설전류 및 기준전류를 비교하는 비교기 수단(34)으로 구성되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 4

제3항에 있어서, 상기 제2저항값에 대한 상기 제1저항값의 비은 메모리 소자의 내구성을 향상시키기 위해서 APDE 모드 동작동안 약 12 : 1까지 증가하는 감지 비율로 정의되어지는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 5

제1항에 있어서, 상기 기준 주변 비트 라인회로 수단은 각각의 출력 라인에 대해서 부합하는 기준 전류를 발생시키는 미니-어레이로 구성되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 6

제5항에 있어서, 상기 기준 주변 비트 라인회로 수단은 상기 감지 회로 수단의 감지 비율을 배로 하는 수단(302)을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 7

제1항에 있어서, 여덟 개의 데이터 입력 버퍼 수단으로부터의 비트 정합신호에 응답하여 각각의 정합신호가 하이일 때만 하이 논리 레벨에 있는 바이트 정합신호를 발생시키는 정합회로 수단(33)을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 8

제7항에 있어서, 상기 펄스 카운터 수단은 바이트 정합신호가 어레이로부터의 바이트 데이터 및 프로그램되어질 데이터사이에 완전한 정합이 존재함을 가리키는 하이 논리 레벨에 있을 때만, 상기 다수의 펄스를 종료하는 것을 특징으로 하는 집적회로 메모리 소자.

## 청구항 9

제8항에 있어서, 상기 바이트 정합 회로에 응답하여 프로그램되어질 어레이내에서 다음 바이트를 선택하는 수단(28)을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

## 청구항 10

메모리 소자내의 중복-소거된 메모리 셀상의 정정 동작을 실행하는 중복-소거된 비트 정정 구조를 구비한 반도체 집적회로 메모리 소자로서, 상기 정정 구조는, 워드 라인의 행 및 상기 워드 라인의 행과 교차되는 비트 라인의 열로 배열되고, 그 게이트가 상기 워드 라인의 행중 하나에 접속되고, 그 드레인이 상기 비트 라인의 열중 하나에 접속되고, 그 소오스가 접지 전위에 접속되는 부동 게이트 어레이 트랜지스터를 각각 포함하는 다수의 메모리 셀을 갖는 셀 트릭스(12)와, 행 번지 신호에 응답하고, 상기 셀 매트릭스에 운용적으로 접속되어 상기 워드 라인의 행중 하나를 선택하는 행 디코더 수단(14)과, 열 번지 신호에 응답하고, 상기 셀 매트릭스에 운용적으로 접속되어 상기 비트 라인의 열중 하나를 선택하

는 열 디코더 수단(16)과, 상기 비트 라인의 열중 하나에 각각 관련된 다중 기준 전류를 발생시키는 기준 주변 비트 라인 회로 수단(44)과, APDE 모드 동작동안, 상기 비트 라인의 열중 선택된 하나에서의 누설 전류 및 상기 비트 라인의 열중 선택된 하나와 관련된 기준 전류를 비교하여, 상기 비트라인 누설 전류가 상기 기준 전류보다 크면 중복 - 소거된 메모리 셀을 나타내는 하이 논리 레벨에 있고 상기 비트 하인 누설 전류가 상기 기준 전류보다 작으면 적정 프로그램된 메모리 셀을 나타내는 로우 논리 레벨에 있는 메모리 셀내에 저장된 데이터를 나타내는 논리 신호를 발생시키는 감지회로 수단(20)과, 상기 논리 신호 및 메모리 셀내에 프로그램된 데이터를 나타내는 데이터 신호를 비교하여 상기 논리신호 및 상기 데이터 신호가 동일할 때 하이 논리 레벨에 있는 비트 정합 신호를 발생시키는 데이터 입력 버퍼회로 수단(26)과, 상기 데이터 입력 버퍼 회로 수단에 접속되어 제공되어진 다수의 프로그래밍 펄스를 계수하는 펄스 카운터 수단(30)으로 구성되고, 상기 데이터 입력회로 수단이 상기 비트 정합 신호가 하이 논리 레벨에 있는 상기 펄스 카운터 수단에 대해서 상기 비트 라인의 열중 특정 하나에만 선택적으로 접속되어 상기 비트 라인의 열중 특정 하나에만 접속된 중복 - 소거된 메모리 셀을 재 프로그램하도록 하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 11

제10항에 있어서, 상기 다수의 프로그래밍 펄스는 종복 - 소거된 메모리 셀에서 어레이 트랜지스터의 네 가타브 문턱값을 파지티브 문턱 전압으로 변경시키도록 제공되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 12

제10항에 있어서, 상기 감지회로 소자는, 상기 비트 라인의 열에 운용적으로 접속되어 상기 비트 라인의 열중 선택된 하나에 누설 전류에 부합하는 제1저항 값을 발생시키는 감지 비율 저항 네트워크(38)와, 상기 기준 주변 비트 라인 회로에 운용적으로 접속되어 기준 전류에 부합하는 제2저항 값을 발생시키는 기준 저항 네트워크 수단(36)과, 감지 비율 저항 네트워크 수단에 접속된 제1입력 및 상기 기준 저항 네트워크 수단에 접속된 제2입력을 구비하여 열 누설 전류 및 기준 전류를 비교하는 비교기 수단(34)으로 구성되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 13

제12항에 있어서, 상기 제2저항 값에 대한 상기 제1저항 값의 비는 메모리 소자의 고 내구성을 향상시키기 위해서 APDE 모드 동작동안 약 12 : 1까지 증가하는 감지 비율로 정의되어지는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 14

제10항에 있어서, 상기 기준 주변 비트 라인회로 수단은 각각의 출력 라인에 대해서 부합하는 기준 전류를 발생시키는 미니 - 어레이로 구성되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 15

제14항에 있어서, 상기 기준 주변 비트 라인회로 수단은 상기 감지회로 수단의 감지 비율을 배로 하는 수단(302)을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 16

제10항에 있어서, 여덟 개의 데이터 입력 및 버퍼 수단으로부터의 비트 정합 신호에 응답하여 각각의 정합 신호가 하이일 때만 하이 논리 레벨에 있는 바이트 정합 신호를 발생시키는 정합 회로 수단(33)을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 17

제16항에 있어서, 상기 펄스 카운터 수단은 바이트 정합신호가 어레이로부터 바이트 데이터 및 프로그램되어질 바이트 데이터 사이에 완전한 정합이 존재함을 가리키는 하이 논리 레벨에 있을 때만, 상기 다수의 펄스를 종료하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 18

제17항에 있어서, 상기 바이트 정합 회로에 응답하여 프로그램되어질 어레이내에서 다음 바이트를 선택하는 수단(28)을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 19

고 내구성을 제공하도록 소거 동작 후에, 플래시 EEPROM 메모리 셀의 어레이에 있어서 종복 - 소거된 메모리 셀을 정정하는 종복 - 소거된 비트 정정 구조로서, 상기 정정 구조는 APDE 모드 동작동안, 상기 비트 라인의 열중 선택된 하나에서의 누설 전류 및 상기 비트 라인의 열중 선택된 하나의 관련된 기준 전류를 비교하여, 상기 비트 라인 누설 전류가 상기 기준 전류보다 크면 종복 - 소거된 메모리 셀을 나타내는 하이 논리 레벨에 있고 상기 비트 하인 누설 전류가 상기 기준 전류보다 작으면 적정 프로그램된 메모리 셀을 나타내는 로우 논리 레벨에 있는 메모리 셀내에 저장된 데이터를 나타내는 논리 신호를 발생시키는 감지 회로 수단(20)과, 상기 논리 신호 및 메모리 셀내에 프로그램된 데이터를 나타내는 데이터 신호를 비교하여 상기 논리 신호 및 상기 데이터 신호가 동일할 때 하이 논리 레벨에 있는 비트 정합 신호를 발생시키는 데이터 입력버퍼회로 수단(26)과, 상기 데이터 입력 버퍼 회로 수단에 접속되어 제공되어진 다수의 프로그래밍 펄스를 계수하는 펄스 카운터 수단(30)으로 구성되고, 상기 데이터 입력회로 수단이 상기 비트 정합 신호가 하이 논리 레벨에 있는 상기 펄스 카운터 수단에 대해서 상기 비트 라인의 열 중 특정 하나에만 선택적으로 접속되어 상기 비트 라인의 열중 특정 하나에만 접속된 종복 - 소거된

메모리 셀을 재 프로그램하도록 하는 것을 특징으로 하는 중복 - 소거된 비트 정정 구조.

청구항 20

제19항에 있어서, 상기 다수의 프로그래밍 펄스는 중복-소거된 메모리 셀에서 어레이 트랜지스터의 네 가이트브 문턱값을 파지티브 문턱 전압으로 변경시키도록 제공되는 것을 특징으로 하는 중복-소거된 비트 정정 구조.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

도연

도면 1

도면2