(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5586361号

(P5586361)

(45) 発行日 平成26年9月10日(2014.9.10)

(24) 登録日 平成26年8月1日(2014.8.1)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 616T |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 618B |

| HO1L 21/316 | (2006.01) | HO1L 29/78 | 618C |

| HO1L 21/318 | (2006.01) | HO1L 29/78 | 617K |

| HO1L 21/203 | (2006.01) | HO1L 29/78 | 619A |

請求項の数 3 (全 72 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2010-167799 (P2010-167799) |

| (22) 出願日     | 平成22年7月27日 (2010.7.27)       |

| (65) 公開番号    | 特開2011-49540 (P2011-49540A)  |

| (43) 公開日     | 平成23年3月10日 (2011.3.10)       |

| 審査請求日        | 平成25年6月14日 (2013.6.14)       |

| (31) 優先権主張番号 | 特願2009-179773 (P2009-179773) |

| (32) 優先日     | 平成21年7月31日 (2009.7.31)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 大原 宏樹<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 佐々木 俊成<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (72) 発明者  | 野田 耕生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のゲート電極層と、

前記第1のゲート電極層上にゲート絶縁層と、

前記ゲート絶縁層上に酸化物半導体層と、

前記酸化物半導体層上に酸化物絶縁層と、

前記酸化物絶縁層上にソース電極層またはドレイン電極層と、

前記ソース電極層または前記ドレイン電極層上に絶縁層と、

前記絶縁層上に第2のゲート電極層と、を有し、

前記酸化物半導体層は、前記酸化物絶縁層と接する第1の領域と、前記ソース電極層または前記ドレイン電極層と接する第2の領域とを有し、

前記第1の領域は、前記第1のゲート電極層と前記ゲート絶縁層を介して重なるチャネル形成領域と、前記酸化物半導体層の周縁及び側面を覆う前記酸化物絶縁層と重なる領域とを有し、

前記酸化物半導体層の端面は、前記酸化物絶縁層を介して前記ソース電極層または前記ドレイン電極層と重なる領域を有し、

前記第1のゲート電極層のチャネル長方向の幅は、前記酸化物半導体層のチャネル長方向の幅よりも広く、前記第1のゲート電極層の端面は、前記ゲート絶縁層及び前記酸化物絶縁層を介して前記ソース電極層または前記ドレイン電極層と重なることを特徴とする半導体装置。

**【請求項 2】**

請求項 1 において、同一基板上に前記ゲート電極層と同じ電位のゲート配線層と、前記ソース電極層と同じ電位のソース配線層との配線交差部を有し、

前記配線交差部において、前記ゲート配線層と前記ソース配線層との間には、前記ゲート絶縁層と前記酸化物絶縁層とを有することを特徴とする半導体装置。

**【請求項 3】**

請求項 1 または請求項 2 において、さらに同一基板上に容量部を有し、

前記容量部は、容量配線及び該容量配線と重なる容量電極を有し、

前記容量部の誘電体は、前記ゲート絶縁層であり、

前記容量配線及び前記容量電極は前記ゲート絶縁層と接することを特徴とする半導体装置。10

**【発明の詳細な説明】****【技術分野】****【0001】**

酸化物半導体を用いる半導体装置及びその作製方法に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、表示装置などの電気光学装置、半導体回路及び電子機器は全て半導体装置である。

**【背景技術】****【0003】**

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。金属酸化物は多様に存在しさまざまな用途に用いられている。酸化インジウムはよく知られた材料であり、液晶ディスプレイなどで必要とされる透明電極材料として用いられている。

**【0004】**

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては、例えば、酸化タンゲステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような半導体特性を示す金属酸化物をチャネル形成領域とする薄膜トランジスタが既に知られている（特許文献1及び特許文献2）。

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

絶縁表面上に複数の薄膜トランジスタを作製する場合、例えばゲート配線とソース配線とで交差する部分がある。交差する部分には、ゲート配線と、該ゲート配線と電位が異なるソース配線の間に絶縁層が設けられ、該絶縁層が誘電体となって容量が形成される。この容量は、配線間の寄生容量とも呼ばれ、信号波形のなまりが生じる恐れがある。また、寄生容量が大きいと信号の伝達が遅くなる恐れがある。

**【0007】**

また、寄生容量の増加は、配線間で電気信号が漏れてしまうクロストーク現象や、消費電力の増大に繋がる。

**【0008】**

また、アクティブマトリクス型の表示装置において、特に映像信号を供給する信号配線と40

また、アクティブマトリクス型の表示装置において、特に映像信号を供給する信号配線と50

、他の配線または電極との間に大きな寄生容量が形成されると、表示品質が低下する恐れがある。

【0009】

また、回路の微細化を図る場合においても、配線間隔が狭くなり、配線間の寄生容量が増加する恐れがある。

【0010】

本発明の一態様は、配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【0011】

また、絶縁表面上に駆動回路を形成する場合、駆動回路に用いる薄膜トランジスタの動作速度は、速い方が好ましい。

【0012】

例えば、薄膜トランジスタのチャネル長( $L$ )を短くする、またはチャネル幅 $W$ を広くすると動作速度が高速化される。しかし、チャネル長を短くすると、スイッチング特性、例えばオンオフ比が小さくなる問題がある。また、チャネル幅 $W$ を広くすると薄膜トランジスタ自身の容量負荷を上昇させる問題がある。

【0013】

また、チャネル長が短くとも、安定した電気特性を有する薄膜トランジスタを備えた半導体装置を提供することも課題の一とする。

【0014】

また、絶縁表面上に複数の異なる回路を形成する場合、例えば、画素部と駆動回路を同一基板上に形成する場合には、画素部に用いる薄膜トランジスタは、優れたスイッチング特性、例えばオンオフ比が大きいことが要求され、駆動回路に用いる薄膜トランジスタには動作速度が速いことが要求される。特に、表示装置の精細度が高精細であればあるほど、表示画像の書き込み時間が短くなるため、駆動回路に用いる薄膜トランジスタは速い動作速度とすることが好ましい。

【0015】

また、同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えた半導体装置を提供することも課題の一とする。

【課題を解決するための手段】

【0016】

ボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部にチャネル保護層となる酸化物絶縁層を形成し、その酸化物絶縁層の形成時に酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

【0017】

酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層は、ゲート電極層と、その上方または周辺に形成される配線層(ソース配線層や容量配線層など)との距離を大きくし、寄生容量の低減を図る。酸化物半導体層の周縁部を覆う酸化物絶縁層は、チャネル保護層と同一工程で形成されるため、工程数の増加なく、寄生容量を低減できる。

【0018】

酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層は、寄生容量を低減することができ、信号波形のなまりを抑制することができる。

【0019】

なお、寄生容量を低減するためには配線間に挟む酸化物絶縁層として、誘電率の小さな絶縁材料を用いることが好ましい。

【0020】

酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層を設けることにより、寄生容量をできる限り小さくし、薄膜トランジスタの高速動作を実現できる。また、動作速度の速い薄膜トランジスタを用いることで回路の集積度が向上する。

【0021】

10

20

30

40

50

本明細書で開示する本発明の一態様は、ゲート電極層と、前記ゲート電極層上にゲート絶縁層と、前記ゲート絶縁層上に酸化物半導体層と、前記酸化物半導体層上に酸化物絶縁層と、前記酸化物絶縁層上にソース電極層またはドレイン電極層とを有し、前記酸化物半導体層は、前記酸化物絶縁層と接する第1の領域と、前記ソース電極層または前記ドレイン層と接する第2の領域とを有し、前記第1の領域は、前記ゲート電極層と前記ゲート絶縁層を介して重なるチャネル形成領域と、前記酸化物半導体層の周縁及び側面を覆う前記酸化物絶縁層と重なる領域とを有し、前記酸化物半導体層の端面は、前記酸化物絶縁層を介して前記ソース電極層または前記ドレイン電極層と重なる半導体装置である。

## 【0022】

上記構成は、上記課題の少なくとも一つを解決する。

10

## 【0023】

また、上記構造を実現するための本発明の一態様は、ゲート電極層と、前記ゲート電極層上にゲート絶縁層と、前記ゲート絶縁層上に酸化物半導体層と、前記酸化物半導体層上に酸化物絶縁層と、前記酸化物絶縁層上にソース電極層またはドレイン電極層と、前記ソース電極層または前記ドレイン電極層上に保護絶縁層とを有し、前記酸化物半導体層は、前記酸化物絶縁層と接する第1の領域と、前記ソース電極層または前記ドレイン層と接する第2の領域と、前記保護絶縁層と接する第3の領域と、を有し、前記第1の領域のうち、前記ゲート電極層と前記ゲート絶縁層を介して重なる領域がチャネル形成領域であり、前記チャネル形成領域と前記第2の領域との間に前記第3の領域を有する半導体装置である。

20

## 【0024】

また、本明細書で用いる酸化物半導体は、例えば、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記される薄膜を形成し、その薄膜を酸化物半導体層として用いた薄膜トランジスタを作製する。なお、Mは、Ga、Fe、Ni、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。例えばMとして、Gaの場合があることの他、GaとNiまたはGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、または該遷移金属の酸化物が含まれているものがある。本明細書においては、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記される構造の酸化物半導体層のうち、MとしてGaを含む構造の酸化物半導体をIn-Ga-Zn-O系酸化物半導体とよび、その薄膜をIn-Ga-Zn-O系非単結晶膜とも呼ぶ。

30

## 【0025】

また、酸化物半導体層に適用する金属酸化物として上記の他にも、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の金属酸化物を適用することができる。また上記金属酸化物からなる酸化物半導体層に酸化珪素を含ませてもよい。

## 【0026】

窒素、または希ガス（アルゴン、ヘリウムなど）の不活性気体雰囲気下での加熱処理を行った場合、酸化物半導体層は加熱処理により酸素欠乏型となって低抵抗化、即ちN型化（N<sup>-</sup>化など）させ、その後、酸化物半導体層に接する酸化物絶縁膜の形成や、形成後に加熱処理を行うことにより酸化物半導体層を酸素過剰な状態とすることで高抵抗化、即ちI型化させているとも言える。また、酸化物半導体層を酸素過剰な状態とする固相酸化を行っているとも呼べる。これにより、電気特性が良好で信頼性のよい薄膜トランジスタを有する半導体装置を作製し、提供することが可能となる。

40

## 【0027】

脱水化または脱水素化は、窒素、または希ガス（アルゴン、ヘリウムなど）の不活性気体雰囲気下での400以上基板の歪み点未満、好ましくは420以上570以下の加熱処理を行い、酸化物半導体層の含有水分などの不純物を低減する。

## 【0028】

50

脱水化または脱水素化を行った酸化物半導体層は、脱水化または脱水素化後の酸化物半導体層に対してTDSで450まで測定を行っても水の2つのピーク、少なくとも300

付近に現れる1つのピークは検出されない程度の熱処理条件とする。従って、脱水化または脱水素化が行われた酸化物半導体層を用いた薄膜トランジスタに対してTDSで450まで測定を行っても少なくとも300付近に現れる水のピークは検出されない。

#### 【0029】

そして、酸化物半導体層に対して脱水化または脱水素化を行う加熱温度Tから温度を下げる際、脱水化または脱水素化を行った同じ炉を用いて大気に触れさせないことで、水または水素が再び混入させないことが重要である。脱水化または脱水素化を行い、酸化物半導体層を低抵抗化、即ちN型化(N<sup>-</sup>など)させた後、高抵抗化させてI型とした酸化物半導体層を用いて薄膜トランジスタを作製すると、薄膜トランジスタのしきい値電圧値をプラスとすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。薄膜トランジスタのゲート電圧が0Vにできるだけ近い正のしきい値電圧でチャネルが形成されることが半導体装置(表示装置)には望ましい。なお、薄膜トランジスタのしきい値電圧値がマイナスであると、ゲート電圧が0Vでもソース電極とドレイン電極の間に電流が流れ、所謂ノーマリーオンとなりやすい。アクティブマトリクス型の表示装置においては、回路を構成する薄膜トランジスタの電気特性が重要であり、この電気特性が表示装置の性能を左右する。特に、薄膜トランジスタの電気特性のうち、しきい値電圧(V<sub>th</sub>)が重要である。電界効果移動度が高くともしきい値電圧値が高い、或いはしきい値電圧値がマイナスであると、回路として制御することが困難である。しきい値電圧値が高く、しきい値電圧の絶対値が大きい薄膜トランジスタの場合には、駆動電圧が低い状態ではTFTとしてのスイッチング機能を果たすことができず、負荷となる恐れがある。nチャネル型の薄膜トランジスタの場合、ゲート電圧に正の電圧を印加してはじめてチャネルが形成されて、ドレイン電流が流れ出すトランジスタが望ましい。駆動電圧を高くしないとチャネルが形成されないトランジスタや、負の電圧状態でもチャネルが形成されてドレイン電流が流れるトランジスタは、回路に用いる薄膜トランジスタとしては不向きである。

#### 【0030】

また、加熱温度Tから下げるガス雰囲気は、加熱温度Tまで昇温したガス雰囲気と異なるガス雰囲気に切り替えてよい。例えば、脱水化または脱水素化を行った同じ炉で大気に触れさせることなく、炉の中を高純度の酸素ガスまたはN<sub>2</sub>Oガス、超乾燥エア(露点が-40以下、好ましくは-60以下)で満たして冷却を行う。

#### 【0031】

脱水化または脱水素化を行う加熱処理によって膜中の含有水分を低減させた後、水分を含まない雰囲気(露点が-40以下、好ましくは-60以下)下で徐冷(または冷却)した酸化物半導体膜を用いて、薄膜トランジスタの電気特性を向上させるとともに、量産性と高性能の両方を備えた薄膜トランジスタを実現する。

#### 【0032】

本明細書では、窒素、または希ガス(アルゴン、ヘリウムなど)の不活性気体雰囲気下での加熱処理を脱水化または脱水素化のための加熱処理と呼ぶ。本明細書では、この加熱処理によってH<sub>2</sub>として脱離させていることのみを脱水素化と呼んでいるわけではなく、H、OHなどを脱離することを含めて脱水化または脱水素化と便宜上呼ぶこととする。

#### 【0033】

窒素、または希ガス(アルゴン、ヘリウムなど)の不活性気体雰囲気下での加熱処理を行った場合、酸化物半導体層は加熱処理により酸素欠乏型となって低抵抗化、即ちN型化(N<sup>-</sup>化など)させる。

#### 【0034】

また、ドレイン電極層と重なる酸素欠乏型である高抵抗ドレイン領域(HRD(High Resistance Drain)領域とも呼ぶ)が形成される。また、ソース電極層と重なる酸素欠乏型である高抵抗ソース領域(HRS(High Resistance Source)領域とも呼ぶ)が形成される。

10

20

30

40

50

## 【0035】

具体的には、高抵抗ドレン領域のキャリア濃度は、 $1 \times 10^{18} / \text{cm}^3$  以上の範囲内であり、少なくともチャネル形成領域のキャリア濃度 ( $1 \times 10^{18} / \text{cm}^3$  未満) よりも高い領域である。なお、本明細書のキャリア濃度は、室温にて Hall 効果測定から求めたキャリア濃度の値を指す。

## 【0036】

そして、脱水化または脱水素化した酸化物半導体層の少なくとも一部を酸素過剰な状態とすることで、さらに高抵抗化、即ち I 型化させてチャネル形成領域を形成する。なお、脱水化または脱水素化した酸化物半導体層を酸素過剰な状態とする処理としては、脱水化または脱水素化した酸化物半導体層に接する酸化物絶縁膜のスパッタ法の成膜、または酸化物絶縁膜成膜後の加熱処理、または酸素を含む雰囲気での加熱処理、または不活性ガス雰囲気下で加熱した後に酸素雰囲気で冷却する処理、超乾燥エア（露点が -40 以下、好みしくは -60 以下）で冷却する処理などによって行う。10

## 【0037】

また、脱水化または脱水素化した酸化物半導体層の少なくとも一部（ゲート電極層と重なる部分）をチャネル形成領域とするため、選択的に酸素過剰な状態とすることで、高抵抗化、即ち I 型化させることもできる。

## 【0038】

これにより、電気特性が良好で信頼性のよい薄膜トランジスタを有する半導体装置を作製し、提供することが可能となる。20

## 【0039】

なお、ドレン電極層と重畳した酸化物半導体層において高抵抗ドレン領域を形成することにより、駆動回路を形成した際の信頼性の向上を図ることができる。具体的には、高抵抗ドレン領域を形成することで、ドレン電極層から高抵抗ドレン領域、チャネル形成領域にかけて、導電性を段階的に変化させうるような構造とすることができます。そのため、ドレン電極層に高電源電位 VDD を供給する配線に接続して動作させる場合、ゲート電極層とドレン電極層との間に高電界が印加されても高抵抗ドレン領域がバッファとなり局所的な高電界が印加されず、トランジスタの耐圧を向上させた構成とすることができます。

## 【0040】

また、ドレン電極層（及びソース電極層）と重畳した酸化物半導体層において高抵抗ドレン領域を形成することにより、駆動回路を形成した際のチャネル形成領域でのリーク電流の低減を図ることができる。具体的には、高抵抗ドレン領域を形成することで、ドレン電極層とソース電極層との間に流れるトランジスタのリーク電流の経路として、ドレン電極層、ドレン電極層側の高抵抗ドレン領域、チャネル形成領域、ソース電極層側の高抵抗ソース領域、ソース電極層の順となる。このときチャネル形成領域では、ドレン電極層側の高抵抗ドレン領域よりチャネル領域に流れるリーク電流を、トランジスタがオフ時に高抵抗となるゲート絶縁層とチャネル形成領域の界面近傍に集中させることができ、バックチャネル部（ゲート電極層から離れているチャネル形成領域の表面の一部）でのリーク電流を低減することができる。30

## 【0041】

また、ソース電極層に重なる高抵抗ソース領域と、ドレン電極層に重なる高抵抗ドレン領域は、ゲート電極層の幅にもよるが、ゲート電極層の一部とゲート絶縁層を介して重なり、より効果的にドレン電極層の端部近傍の電界強度を緩和させることができる。

## 【0042】

また、駆動回路を有する表示装置としては、液晶表示装置の他に、発光素子を用いた発光表示装置や、電気泳動表示素子を用いた電子ペーパーとも称される表示装置が挙げられる。

## 【0043】

発光素子を用いた発光表示装置においては、画素部に複数の薄膜トランジスタを有し、画

10

20

30

40

50

素部においてもある薄膜トランジスタのゲート電極と他のトランジスタのソース配線、或いはドレイン配線を接続させる箇所を有している。また、発光素子を用いた発光表示装置の駆動回路においては、薄膜トランジスタのゲート電極とその薄膜トランジスタのソース配線、或いはドレイン配線を接続させる箇所を有している。

## 【0044】

また、薄膜トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース線に対して、画素部の薄膜トランジスタの保護用の保護回路を同一基板上に設けることが好ましい。保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することが好ましい。

## 【0045】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

## 【発明の効果】

## 【0046】

寄生容量を十分に低減し、チャネル長が短くとも、安定した電気特性を有する薄膜トランジスタを備えた半導体装置を実現する。

## 【図面の簡単な説明】

## 【0047】

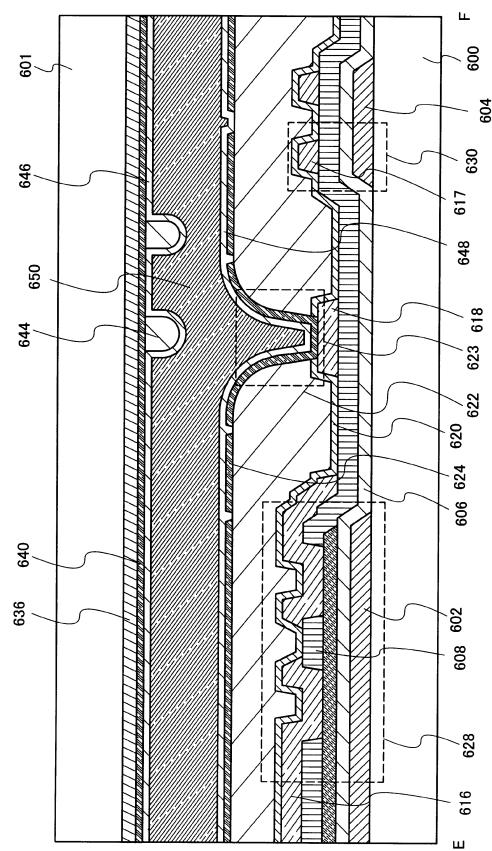

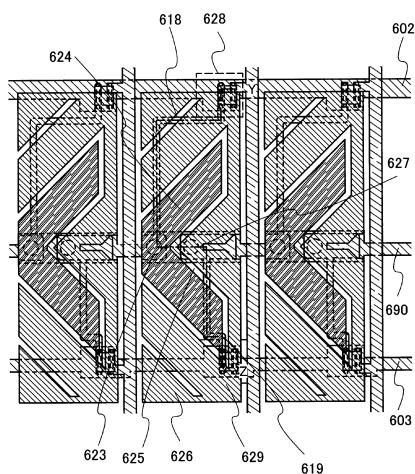

【図1】本発明の一態様を示す平面図及び断面図である。

【図2】本発明の一態様を示す工程断面図である。

【図3】本発明の一態様を示す断面図である。

【図4】本発明の一態様を示す平面図及び断面図である。

【図5】本発明の一態様を示す平面図及び断面図である。

【図6】本発明の一態様を示す断面図である。

【図7】本発明の一態様を示す平面図及び断面図である。

【図8】本発明の一態様を示す工程断面図である。

【図9】半導体装置を説明する図。

【図10】半導体装置を説明する図。

【図11】半導体装置を説明する図。

【図12】半導体装置の画素等価回路を説明する図。

【図13】半導体装置を説明する図。

【図14】半導体装置のブロック図を説明する図。

【図15】信号線駆動回路の構成を説明する図および動作を説明するタイミングチャート。

。

【図16】シフトレジスタの構成を示す回路図。

【図17】シフトレジスタの構成を説明する図および動作を説明するタイミングチャート。

。

【図18】半導体装置を説明する図。

【図19】半導体装置を説明する図。

【図20】電子書籍の一例を示す外観図。

【図21】テレビジョン装置およびデジタルフォトフレームの例を示す外観図。

【図22】遊技機の例を示す外観図。

【図23】携帯型のコンピュータ及び携帯電話機の一例を示す外観図。

【図24】半導体装置を説明する図。

【図25】半導体装置を説明する図。

【図26】半導体装置を説明する図。

【図27】半導体装置を説明する図。

【図28】半導体装置を説明する図。

【図29】半導体装置を説明する図。

10

20

30

40

50

【図30】半導体装置を説明する図。

【図31】半導体装置を説明する図。

【図32】半導体装置を説明する図。

【図33】半導体装置を説明する図。

【図34】半導体装置を説明する図。

【図35】半導体装置を説明する図。

【図36】半導体装置を説明する図。

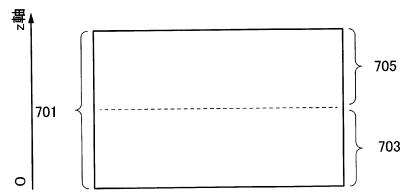

【図37】計算で用いた酸化物半導体層の構造を説明する図である。

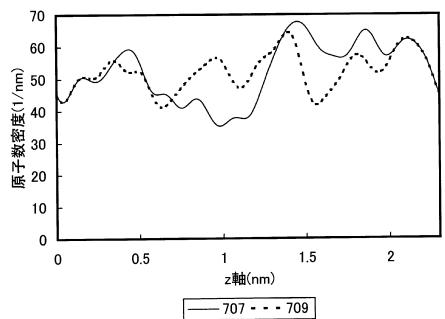

【図38】酸化物半導体層の酸素密度の計算結果を説明する図である。

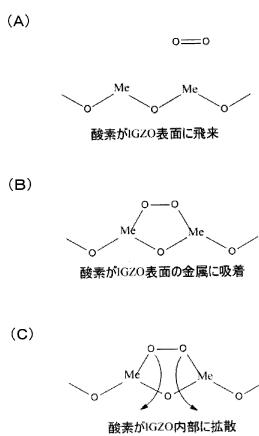

【図39】酸素と酸化物半導体膜表面の相互作用を説明する図である。

10

【発明を実施するための形態】

【0048】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0049】

(実施の形態1)

本実施の形態では、半導体装置及び半導体装置の作製方法の一形態を図1、図2、図3、及び図4を用いて説明する。

20

【0050】

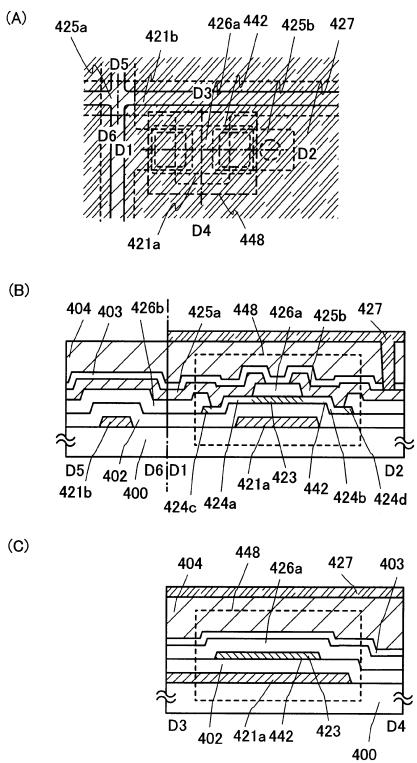

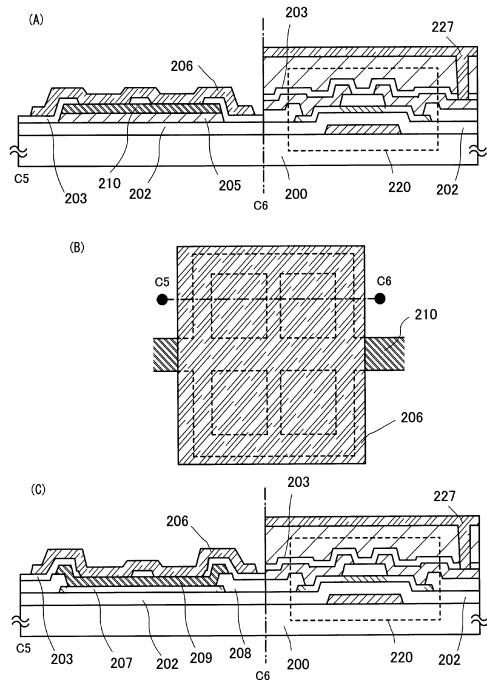

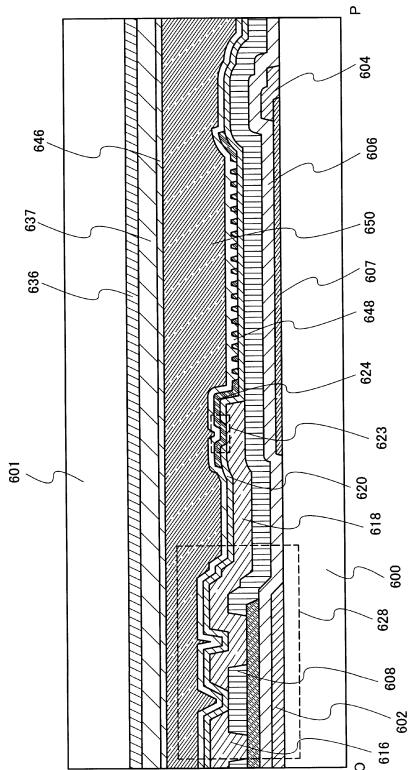

また、図1(A)は画素に配置されるチャネル保護型の薄膜トランジスタ448の平面図であり、図1(B)は図1(A)の線D1-D2における断面図及び図1(A)の線D5-D6における断面図である。また、図1(C)は、図1(A)の線D3-D4における断面図である。なお、図2(E)は図1(B)と同一である。

【0051】

画素に配置される薄膜トランジスタ448はチャネル保護型(チャネルトップ型ともいう)の薄膜トランジスタであり、絶縁表面を有する基板400上に、ゲート電極層421a、ゲート絶縁層402、チャネル形成領域423を含む酸化物半導体層442、チャネル保護層として機能する酸化物絶縁層426a、ソース電極層425a、及びドレイン電極層425bを含む。また、薄膜トランジスタ448を覆い、酸化物絶縁層426a、ソース電極層425a、及びドレイン電極層425bに接して保護絶縁層403、及び平坦化絶縁層404が積層して設けられている。平坦化絶縁層404上にはドレイン電極層425bと接する画素電極層427が設けられており、薄膜トランジスタ448と電気的に接続している。

30

【0052】

画素用の薄膜トランジスタ448は、高抵抗ソース領域424a、高抵抗ドレイン領域424b、及びチャネル形成領域423を含む酸化物半導体層442を有し、ソース電極層425aの下面に接して高抵抗ソース領域424aが形成されている。また、ドレイン電極層425bの下面に接して高抵抗ドレイン領域424bが形成されている。薄膜トランジスタ448は、高電界が印加されても高抵抗ドレイン領域または高抵抗ソース領域がバッファとなり局所的な高電界が印加されず、トランジスタの耐圧を向上させた構成となっている。

40

【0053】

画素に配置される薄膜トランジスタ448のチャネル形成領域は、酸化物半導体層442のうち、チャネル保護層である酸化物絶縁層426aに接し、且つゲート電極層421aと重なる領域である。薄膜トランジスタ448は、酸化物絶縁層426aによって保護されるため、ソース電極層425a、ドレイン電極層425bを形成するエッチング工程で、酸化物半導体層442がエッチングされるのを防ぐことができる。

50

## 【0054】

また、薄膜トランジスタ448は透光性を有する薄膜トランジスタとして高開口率を有する表示装置を実現するためにソース電極層425a、ドレイン電極層425bは、透光性を有する導電膜を用いる。

## 【0055】

また、薄膜トランジスタ448のゲート電極層421aも透光性を有する導電膜を用いる。

## 【0056】

また、薄膜トランジスタ448が配置される画素には、画素電極層427、または他の電極層（容量電極層など）や、容量配線層などの他の配線層に可視光に対して透光性を有する導電膜を用い、高開口率を有する表示装置を実現する。勿論、ゲート絶縁層402、酸化物絶縁層426aも可視光に対して透光性を有する膜を用いることが好ましい。

10

## 【0057】

本明細書において、可視光に対して透光性を有する膜とは可視光の透過率が75～100%である膜厚を有する膜を指し、その膜が導電性を有する場合は透明の導電膜とも呼ぶ。また、ゲート電極層、ソース電極層、ドレイン電極層、画素電極層、または他の電極層や、他の配線層に適用する金属酸化物として、可視光に対して半透明の導電膜を用いてもよい。可視光に対して半透明とは可視光の透過率が50～75%であることを指す。

20

## 【0058】

また、ゲート配線とソース配線の交差する配線交差部は、寄生容量の低減を図るため、ゲート電極層421bとソース電極層425aとの間にゲート絶縁層402と酸化物絶縁層426bが設けられている。なお、チャネル形成領域423と重なる領域の酸化物絶縁層426aと、チャネル形成領域423と重ならない領域の酸化物絶縁層426bとを異なる符号で示しているが、同じ材料、同じ工程で形成される層である。

## 【0059】

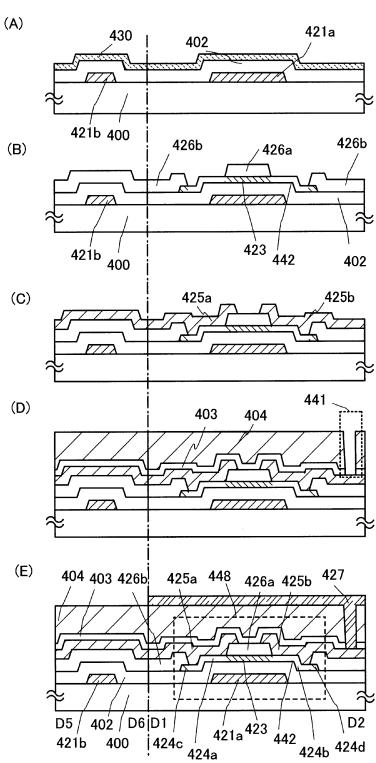

以下、図2(A)乃至図2(E)を用い、同一基板上に薄膜トランジスタ448と配線交差部を作製する工程を説明する。また、画素部だけでなく駆動回路の薄膜トランジスタを形成してもよく、同じ工程で同一基板上に作製することもできる。

## 【0060】

30

まず、絶縁表面を有する基板400上に透光性を有する導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層421a、421bを形成する。また、画素部にはゲート電極層421a、421bと同じ透光性を有する材料、同じ第1のフォトリソグラフィ工程により容量配線層を形成する。また、画素部だけでなく駆動回路も形成する場合、駆動回路に容量が必要な場合には、駆動回路にも容量配線層を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0061】

絶縁表面を有する基板400に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。絶縁表面を有する基板400にはガラス基板を用いることができる。

40

## 【0062】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、B<sub>2</sub>O<sub>3</sub>よりBaOを多く含むガラス基板を用いることが好ましい。

## 【0063】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶

50

縁体でなる基板を用いても良い。他にも、結晶化ガラスなどを用いることができる。

【0064】

また、下地膜となる絶縁膜を基板400とゲート電極層421a、421bの間に設けてもよい。下地膜は、基板400からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた一又は複数の膜による積層構造により形成することができる。

【0065】

ゲート電極層421a、421bの材料は、可視光に対して透光性を有する導電材料、例えばIn-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の金属酸化物を適用することができ、膜厚は50nm以上300nm以下の範囲内で適宜選択する。ゲート電極層421a、421bに用いる金属酸化物の成膜方法は、スパッタ法や真空蒸着法（電子ビーム蒸着法など）や、アーク放電イオンプレーティング法や、スプレー法を用いる。また、スパッタ法を用いる場合、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて成膜を行い、透光性を有する導電膜に結晶化を阻害するSiO<sub>X</sub>(X>0)を含ませ、後の工程で行う脱水化または脱水素化のための加熱処理の際に結晶化してしまうのを抑制することが好ましい。

【0066】

酸化物半導体は、好ましくはInを含有する酸化物半導体、さらに好ましくは、In、及びGaを含有する酸化物半導体である。酸化物半導体層をI型（真性）とするため、脱水化または脱水素化の工程を経ることは有効である。

【0067】

次いで、ゲート電極層421a、421b上にゲート絶縁層402を形成する。

【0068】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化珪素層、窒化珪素層、酸化窒化珪素層、窒化酸化珪素層、又は酸化アルミニウム層を単層で又は積層して形成することができる。例えば、成膜ガスとして、SiH<sub>4</sub>、酸素及び窒素を用いてプラズマCVD法により酸化窒化珪素層を形成すればよい。ゲート絶縁層402の膜厚は、100nm以上500nm以下とし、積層の場合は、例えば、膜厚50nm以上200nm以下の第1のゲート絶縁層と、第1のゲート絶縁層上に膜厚5nm以上300nm以下の第2のゲート絶縁層の積層とする。

【0069】

本実施の形態では、プラズマCVD法により窒化珪素層である膜厚200nm以下のゲート絶縁層402とする。

【0070】

次いで、ゲート絶縁層402上に、膜厚2nm以上200nm以下の酸化物半導体膜430を形成する（図2（A）参照。）。酸化物半導体膜430の形成後に脱水化または脱水素化のための加熱処理を行っても酸化物半導体膜を非晶質な状態とするため、膜厚を50nm以下と薄くすることが好ましい。酸化物半導体膜の膜厚を薄くすることで酸化物半導体層の形成後に加熱処理した場合に、結晶化してしまうのを抑制することができる。

【0071】

酸化物半導体膜430は、In-Ga-Zn-O系非単結晶膜、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いる。本実施の形態では、In-Ga-Zn-O系酸化物半導体ターゲットを用いてスパッタ法により成膜する。また、酸化物半導体膜430は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（代表的にはアルゴン）及び酸素雰囲気下においてスパッタ法により形成することができる。また、スパッタ法を用いる場合、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲ

10

20

30

40

50

ットを用いて成膜を行い、酸化物半導体膜430に結晶化を阻害する $\text{SiO}_x$ ( $X > 0$ )を含ませ、後の工程で行う脱水化または脱水素化のための加熱処理の際に結晶化してしまうのを抑制することが好ましい。

【0072】

ここでは、 $\text{In}$ 、 $\text{Ga}$ 、及び $\text{Zn}$ を含む酸化物半導体ターゲット( $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 1$  [mol数比])を用いて、基板とターゲットの間との距離を100mm、圧力0.2Pa、直流(DC)電源0.5kW、アルゴン及び酸素(アルゴン:酸素=30sccm:20sccm 酸素流量比率40%)雰囲気下で成膜する。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均一となるために好ましい。 $\text{In-Ga-Zn-O}$ 系非単結晶膜の膜厚は、5nm~200nmとする。本実施の形態では、酸化物半導体膜として、 $\text{In-Ga-Zn-O}$ 系酸化物半導体ターゲットを用いてスパッタ法により膜厚20nmの $\text{In-Ga-Zn-O}$ 系非単結晶膜を成膜する。

10

【0073】

スパッタ法にはスパッタ用電源に高周波電源を用いるRFスパッタ法と、DCスパッタ法があり、さらにパルス的にバイアスを与えるパルスDCスパッタ法もある。RFスパッタ法は主に絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に金属膜を成膜する場合に用いられる。

【0074】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

20

【0075】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ法を用いるスパッタ装置がある。

【0076】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてこれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法もある。

30

【0077】

次いで、酸化物半導体膜430を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0078】

次いで、酸化物半導体層の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上基板の歪み点未満、好ましくは425以上とする。なお、425以上であれば熱処理時間は1時間以下でよいが、425未満であれば加熱処理時間は、1時間よりも長時間行うこととする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。本実施の形態では、酸化物半導体層の脱水化または脱水素化を行う加熱温度Tから、再び水が入らないような十分な温度まで同じ炉を用い、具体的には加熱温度Tよりも100以上下がるまで窒素雰囲気下で徐冷する。また、窒素雰囲気に限定されず、ヘリウム、ネオン、アルゴン等の希ガス雰囲気下において脱水化または脱水素化を行う。

40

【0079】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、

50

またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0080】

また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、結晶化し、微結晶膜または多結晶膜となる場合もある。

【0081】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜430に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

10

【0082】

また、酸化物半導体膜430の成膜前に、不活性ガス雰囲気(窒素、またはヘリウム、ネオン、アルゴン等)下、酸素雰囲気下において加熱処理(400以上基板の歪み点未満)を行い、ゲート絶縁層内に含まれる水素及び水などの不純物を除去してもよい。

【0083】

次いで、ゲート絶縁層402、及び酸化物半導体層上に、スパッタ法で酸化物絶縁膜を形成した後、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行って酸化物絶縁層426a、426bを形成し、その後レジストマスクを除去する。この段階で、酸化物半導体層は、酸化物絶縁層と接する領域が形成され、この領域のうち、ゲート電極層とゲート絶縁層を介して重なり且つ酸化物絶縁層426aと重なる領域がチャネル形成領域となる。また、酸化物半導体層の周縁及び側面を覆う酸化物絶縁層426bと重なる領域も形成される。

20

【0084】

酸化物絶縁膜は、少なくとも1nm以上の膜厚とし、スパッタリング法など、酸化物絶縁膜に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。本実施の形態では、酸化物絶縁膜として膜厚300nmの酸化珪素膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では室温とする。酸化珪素膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において行うことができる。また、ターゲットとして酸化珪素ターゲットまたは珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び窒素雰囲気下でスパッタリング法により酸化珪素膜を形成することができる。低抵抗化した酸化物半導体層に接して形成する酸化物絶縁膜は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

30

【0085】

次いで、不活性ガス雰囲気下、または窒素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う(図2(B)参照)。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物絶縁層426bと重なる酸化物半導体層442の端部と、酸化物絶縁層426aと重なる酸化物半導体層442の一部が酸化物絶縁層と接した状態で加熱される。なお、第2の加熱処理を行うと、酸化物絶縁層と重ならない酸化物半導体層442の一部は露出した状態で加熱される。酸化物半導体層442が露出している状態で、窒素、または不活性ガス雰囲気下で加熱処理を行うと、酸化物半導体層442において露出している高抵抗化された(I型化された)領域を低抵抗化することができる。また、酸化物絶縁層426aは酸化物半導体層442のチャネル形成領域となる領域上に接して設けられ、チャネル保護層として機能する。

40

【0086】

次いで、ゲート絶縁層402、酸化物絶縁層426a、426b、及び酸化物半導体層4

50

42上に、透光性を有する導電膜を形成した後、第4のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってソース電極層425a、及びドレイン電極層425bを形成する(図2(C)参照)。透光性を有する導電膜の成膜方法は、スパッタ法や真空蒸着法(電子ビーム蒸着法など)や、アーク放電イオンプレーティング法や、スプレー法を用いる。導電膜の材料としては、可視光に対して透光性を有する導電材料、例えばIn-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の金属酸化物を適用することができ、膜厚は50nm以上300nm以下の範囲内で適宜選択する。また、スパッタ法を用いる場合、 $SiO_2$ を2重量%以上10重量%以下含むターゲットを用いて成膜を行い、透光性を有する導電膜に結晶化を阻害する $SiO_x$ ( $X > 0$ )を含ませ、後の工程で行う脱水化または脱水素化のための加熱処理の際に結晶化してしまうのを抑制することが好ましい。

#### 【0087】

なお、ソース電極層425a、ドレイン電極層425bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0088】

次いで、酸化物絶縁層426a、426b、ソース電極層425a、ドレイン電極層425b上に保護絶縁層403を形成する。本実施の形態では、RFスパッタ法を用いて窒化珪素膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層403の成膜方法として好ましい。保護絶縁層403は、水分や、水素イオンや、 $OH^-$ などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化珪素膜、窒化アルミニウム膜、窒化酸化珪素膜、酸化窒化アルミニウム膜などを用いる。勿論、保護絶縁層403は透光性を有する絶縁膜である。

#### 【0089】

次いで、保護絶縁層403上に平坦化絶縁層404を形成する。平坦化絶縁層404としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(10w-k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、平坦化絶縁層404を形成してもよい。

#### 【0090】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成された $Si-O-Si$ 結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有しても良い。

#### 【0091】

平坦化絶縁層404の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピニコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

#### 【0092】

次に、第5のフォトリソグラフィ工程を行い、レジストマスクを形成し、平坦化絶縁層404、及び保護絶縁層403のエッチングによりドレイン電極層425bに達するコンタクトホール441を形成し、レジストマスクを除去する(図2(D)参照)。図2(D)に示すようにコンタクトホールの下方には酸化物絶縁層426bが設けられており、コンタクトホールの下方に酸化物絶縁層が設けられていない場合に比べて除去する平坦化絶縁層の膜厚を薄くでき、エッチング時間を短くすることができる。また、コンタクトホールの下方に酸化物絶縁層が設けられていない場合に比べてコンタクトホール441の深さ

10

20

30

40

50

を浅くすることができ、コンタクトホール 441 と重なる領域において、後の工程で形成する透光性を有する導電膜のカバレッジを良好なものとすることができます。また、ここでのエッティングによりゲート電極層 421b に達するコンタクトホールも形成する。また、ドレイン電極層 425b に達するコンタクトホールを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0093】

次いで、透光性を有する導電膜を成膜する。透光性を有する導電膜の材料としては、酸化インジウム ( $In_2O_3$ ) や酸化インジウム酸化スズ合金 ( $In_2O_3 - SnO_2$ 、ITO と略記する)などをスパッタ法や真空蒸着法などを用いて形成する。透光性を有する導電膜の他の材料として、窒素を含ませた  $Al - Zn - O$  系非単結晶膜、即ち  $Al - Zn - O - N$  系非単結晶膜や、 $Zn - O - N$  系非単結晶膜や、 $Sn - Zn - O - N$  系非単結晶膜を用いてもよい。なお、 $Al - Zn - O - N$  系非単結晶膜の亜鉛の組成比(原子%)は、47原子%以下とし、非単結晶膜中のアルミニウムの組成比(原子%)より大きく、非単結晶膜中のアルミニウムの組成比(原子%)は、非単結晶膜中の窒素の組成比(原子%)より大きい。このような材料のエッティング処理は塩酸系の溶液により行う。しかし、特に ITO のエッティングは残渣が発生しやすいので、エッティング加工性を改善するために酸化インジウム酸化亜鉛合金 ( $In_2O_3 - ZnO$ ) を用いても良い。

#### 【0094】

なお、透光性を有する導電膜の組成比の単位は原子%とし、電子線マイクロアナライザー (EPMA: Electron Probe X-ray Micro Analyzer) を用いた分析により評価するものとする。

#### 【0095】

次に、第6のフォトリソグラフィ工程を行い、レジストマスクを形成し、エッティングにより不要な部分を除去して画素電極層 427 を形成し、レジストマスクを除去する(図2(E)参照。)。

#### 【0096】

以上の工程により、6枚のマスクを用いて、同一基板上に薄膜トランジスタ 448 と、寄生容量の低減された配線交差部を作製することができる。画素用の薄膜トランジスタ 448 は、高抵抗ソース領域 424a、高抵抗ドレイン領域 424b、及びチャネル形成領域 423 を含む酸化物半導体層 442 を含むチャネル保護型薄膜トランジスタである。よって、薄膜トランジスタ 448 は、高電界が印加されても高抵抗ドレイン領域 424b または高抵抗ソース領域 424a がバッファとなり局所的な高電界が印加されず、トランジスタの耐圧を向上させた構成となっている。

#### 【0097】

また、ゲート絶縁層 402 を誘電体とし容量配線層と容量電極とで形成される保持容量も同一基板上に形成することができる。薄膜トランジスタ 448 と保持容量を個々の画素に対応してマトリクス状に配置して画素部を構成し、アクティブマトリクス型の表示装置を作製するための一方の基板とすることができる。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

#### 【0098】

また、同一基板上に駆動回路の薄膜トランジスタを設けることもできる。同一基板上に駆動回路と画素部を形成することによって、駆動回路と外部信号との接続配線が短縮でき、半導体装置の小型化、低コスト化が可能である。

#### 【0099】

また、図1(B)に示す画素用の薄膜トランジスタ 448 の酸化物半導体層 442 は、酸化物絶縁層 426b と重なる第1領域 424c、第2領域 424d を周縁部に有している。酸化物半導体層 442 の周縁部である第1領域 424c、及び第2領域 424d は、チャネル形成領域 423 と同じ酸素過剰な状態であり、近くに電位の異なる配線や酸化物半導体層が配置された場合にリーク電流の低減や、寄生容量の低減を実現できる。

10

20

30

40

50

## 【0100】

特に駆動回路においては、高集積化のため、複数の配線や複数の酸化物半導体層の間隔を狭めて配置することが好ましく、酸化物絶縁層426bと重ねることで第1領域424c、及び第2領域424dを設け、リーク電流の低減や、寄生容量の低減を行うことは有効である。また、複数の薄膜トランジスタを直列または並列に配置する場合、複数の薄膜トランジスタの酸化物半導体層を一つのアイランドとし、それぞれの素子分離を酸化物絶縁層426bと重ねることで行い、酸化物絶縁層426bと重なる領域を素子分離領域とすることができる。このようにすることで、狭い面積に複数の薄膜トランジスタを配置することができるため、駆動回路の高集積化を図ることができる。

## 【0101】

10

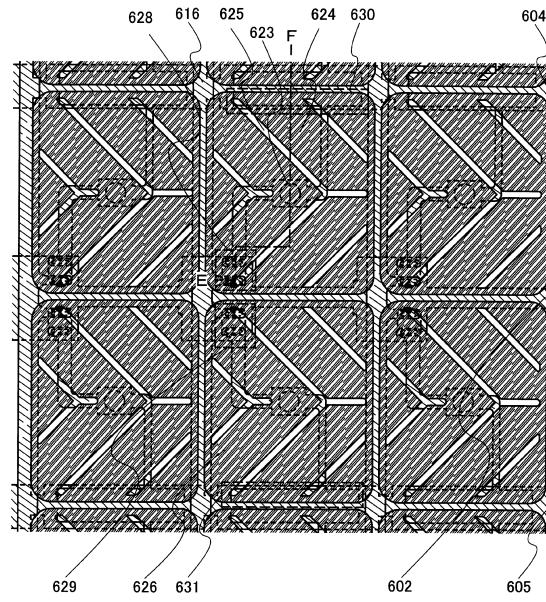

## (実施の形態2)

本実施の形態では、実施の形態1に示した薄膜トランジスタを用いて、同一基板上に画素部と駆動回路を形成し、アクティブマトリクス型の液晶表示装置を作製する一例を示す。

## 【0102】

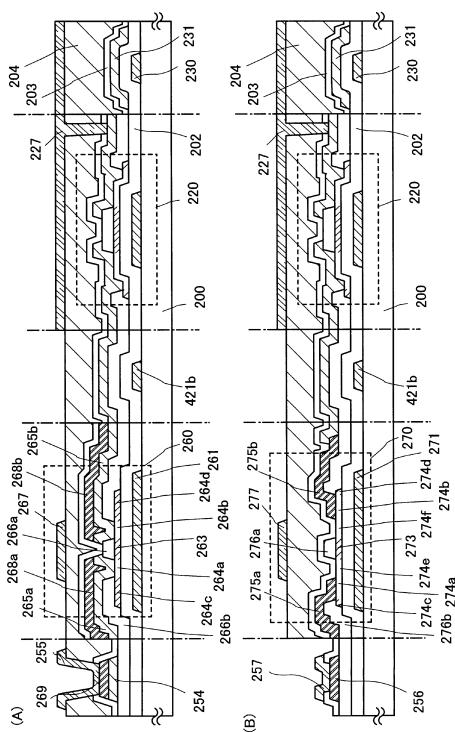

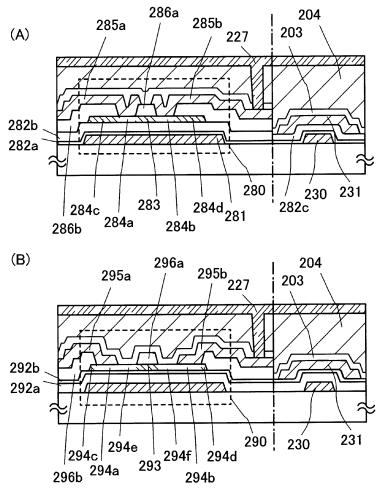

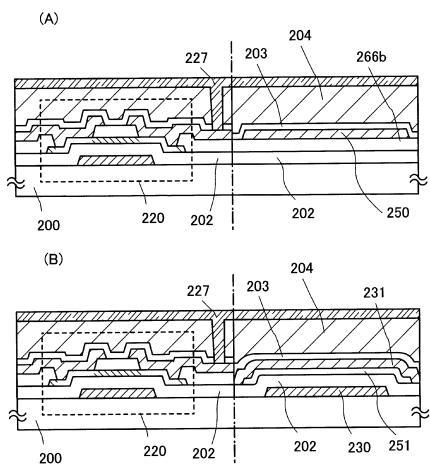

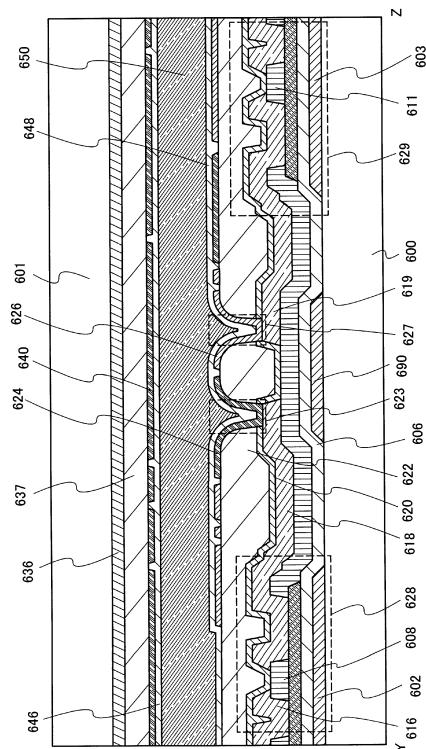

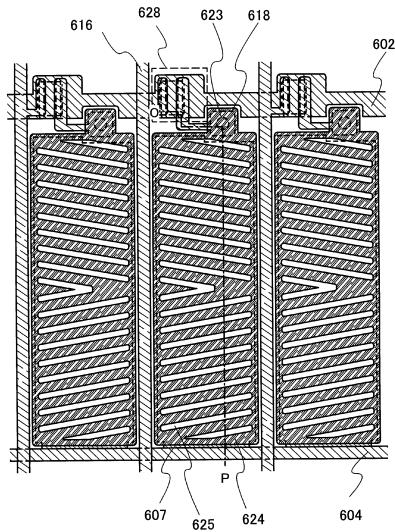

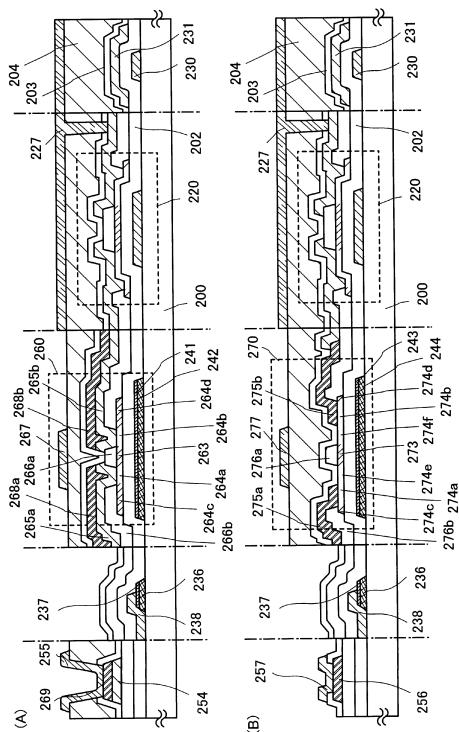

アクティブマトリクス基板の断面構造の一例を図3(A)に示す。

## 【0103】

実施の形態1では、画素部の薄膜トランジスタ及び配線交差部を図示したが、本実施の形態では、薄膜トランジスタ及び配線交差部に加え、駆動回路の薄膜トランジスタ、保持容量、ゲート配線、ソース配線の端子部も図示して説明する。容量、ゲート配線、ソース配線の端子部は、実施の形態1に示す作製工程と同じ工程で形成することができる。また、画素部の表示領域となる部分においては、ゲート配線、ソース配線、及び容量配線層は全て透光性を有する導電膜で形成されており、高い開口率を実現している。

20

## 【0104】

図3(A)において、画素電極層227と電気的に接続する薄膜トランジスタ220は、画素部に設けられるチャネル保護型の薄膜トランジスタであり、本実施の形態では、実施の形態1の薄膜トランジスタ448と同じ構造を用いる。また、薄膜トランジスタ220のゲート電極層のチャネル長方向の幅は薄膜トランジスタ220の酸化物半導体層のチャネル長方向の幅よりも狭い。

## 【0105】

30

薄膜トランジスタ220のゲート電極層と同じ透光性を有する材料、及び同じ工程で形成される容量配線層230は、誘電体となるゲート絶縁層202を介して容量電極231と重なり、保持容量を形成する。なお、容量電極231は、薄膜トランジスタ220のソース電極層またはドレイン電極層と同じ透光性を有する材料、及び同じ工程で形成される。従って、薄膜トランジスタ220が透光性を有していることに加え、それぞれの保持容量も透光性を有するため、開口率を向上させることができる。

## 【0106】

保持容量が透光性を有することは、開口率を向上させる上で重要である。特に10インチ以下の小型の液晶表示パネルにおいて、ゲート配線の本数を増やすなどして表示画像の高精細化を図るため、画素寸法を微細化しても、高い開口率を実現することができる。また、薄膜トランジスタ220及び保持容量の構成部材に透光性を有する膜を用いることで、広視野角を実現するため、1画素を複数のサブピクセルに分割しても高い開口率を実現することができる。即ち、高密度の薄膜トランジスタ群を配置しても開口率を大きくとることができ、表示領域の面積を十分に確保することができる。例えば、一つの画素内に2~4個のサブピクセル及び保持容量を有する場合、薄膜トランジスタが透光性を有していることに加え、それぞれの保持容量も透光性を有するため、開口率を向上させることができる。

40

## 【0107】

なお、保持容量は、画素電極層227の下方に設けられ、容量電極231が画素電極層227と電気的に接続される。

## 【0108】

50

本実施の形態では、容量電極 231、及び容量配線層 230 を用いて保持容量を形成する例を示したが、保持容量を形成する構造については特に限定されない。例えば、容量配線層を設けず、画素電極層を隣り合う画素のゲート配線と平坦化絶縁層、保護絶縁層、及びゲート絶縁層を介して重ねて保持容量を形成してもよい。

【0109】

また、図3(A)において保持容量は、大きな容量を形成するため、容量配線層と容量電極の間にゲート絶縁層 202 のみとしており、配線交差部は、寄生容量を低減するためにゲート電極層 421b とその上方に形成される配線の間にゲート絶縁層 202 と酸化物絶縁層 266b とを設けている。保持容量において、容量配線層と容量電極の間にゲート絶縁層 202 のみとする場合、酸化物絶縁層 266b を除去するエッチングの際に、選択的にゲート絶縁層 202 のみを残すようなエッチング条件またはゲート絶縁層の材料を選択する。本実施の形態では、酸化物絶縁層 266b がスパッタ法で得られる酸化珪素膜、ゲート絶縁層 202 がプラズマCVD法で得られる窒化珪素膜であるため、選択的に除去することができる。なお、酸化物絶縁層 266b とゲート絶縁層 202 が同じエッチング条件で除去される材料を用いる場合には、エッチングによりゲート絶縁層の一部が薄膜化されてもゲート絶縁層が少なくとも残存し、容量を形成することができる膜厚とすることが好み。保持容量を大きくするためには、ゲート絶縁層の膜厚を薄くすることが好みいため、酸化物絶縁層 266b の選択的なエッチングの際に容量配線上のゲート絶縁層を薄膜化させた構成としてもよい。

【0110】

また、薄膜トランジスタ 260 は、駆動回路に設けられるチャネル保護型の薄膜トランジスタであり、薄膜トランジスタ 220 に比べチャネル長 L を短くして、動作速度を高速化したものである。駆動回路に設けられるチャネル保護型の薄膜トランジスタのチャネル長 L は、0.1 μm 以上 2 μm 以下とすることが好み。薄膜トランジスタ 260 のゲート電極層 261 のチャネル長方向の幅は薄膜トランジスタ 260 の酸化物半導体層のチャネル長方向の幅よりも広く、ゲート電極層 261 の端面は、ゲート絶縁層 202 及び酸化物絶縁層 266b を介してソース電極層 265a、又はドレイン電極層 265b と重なる。

【0111】

薄膜トランジスタ 260 は、絶縁表面を有する基板 200 上に、ゲート電極層 261、ゲート絶縁層 202、少なくともチャネル形成領域 263、高抵抗ソース領域 264a、及び高抵抗ドレイン領域 264b を有する酸化物半導体層、ソース電極層 265a、及びドレイン電極層 265b を含む。また、チャネル形成領域 263 に接する酸化物絶縁層 266a が設けられている。

【0112】

また、駆動回路の薄膜トランジスタ 260 のゲート電極層は、酸化物半導体層の上方に設けられた導電層 267 と電気的に接続させる構造としてもよい。その場合には、薄膜トランジスタ 220 のドレイン電極層と、画素電極層 227 とを電気的に接続するためのコンタクトホールと同じフォトマスクを用い、平坦化絶縁層 204、保護絶縁層 203、酸化物絶縁層 266b、ゲート絶縁層 202 を選択的にエッチングしてコンタクトホールを形成する。このコンタクトホールを介して導電層 267 と駆動回路の薄膜トランジスタ 260 のゲート電極層 261 とを電気的に接続する。

【0113】

保護絶縁層 203 は、無機絶縁膜を用い、窒化珪素膜、窒化アルミニウム膜、窒化酸化珪素膜、酸化窒化アルミニウム膜などを用いる。本実施の形態では窒化珪素膜を用いる。

【0114】

また、薄膜トランジスタ 260 は、ゲート電極層 261 の幅が酸化物半導体層の幅よりも広い構造となっている。また、酸化物絶縁層 266b は、酸化物半導体層の周縁部と重なっており、さらにゲート電極層 261 とも重なっている。酸化物絶縁層 266b は、ドレイン電極層 265b とゲート電極層 261 との間隔を広げ、ドレイン電極層 265b とゲ

10

20

30

40

50

ート電極層 261との間に形成される寄生容量を低減する機能を果たしている。また、酸化物絶縁層 266bと重なる酸化物半導体層の第1領域 264c、第2領域 264dは、チャネル形成領域 263と同じ酸素過剰な状態であり、リーク電流の低減や、寄生容量を低減する機能も果たしている。

【0115】

また、液晶表示パネルのサイズが 10 インチを超える場合、さらには 120 インチとする場合には透光性を有する配線の配線抵抗が問題となる恐れがあるため、配線の一部を金属配線として配線抵抗を低減することが好ましい。例えば、ソース電極層 265a、及びドレイン電極層 265bを Ti などの金属配線とする。金属配線を形成するため、実施の形態 1 に比べ、フォトマスクの数は 1 枚増える。

10

【0116】

その場合、脱水化または脱水素化した酸化物半導体層上に接して Ti などの金属電極からなるソース電極層やドレイン電極層を形成し、ソース電極層に重なる高抵抗ソース領域と、ドレイン電極層に重なる高抵抗ドレイン領域とが形成され、高抵抗ソース領域と高抵抗ドレイン領域との間の領域がチャネル形成領域となる。

【0117】

また、配線抵抗を低減するために図 3 (A) のように、ソース電極層 265a、及びドレイン電極層 265b 上により低抵抗な金属電極を用いた補助電極層 268a、268b を形成する。この場合も金属配線 (金属電極) を形成するため、実施の形態 1 に比べ、さらにフォトマスクの数は 1 枚増える。透光性のソース電極層及びドレイン電極層のみの構造としてもよいが、ソース電極層及びドレイン電極層上に金属電極を用いた補助電極層を設けると配線抵抗を低減することができる。

20

【0118】

ソース電極層 265a、ドレイン電極層 265b、補助電極層 268a、268b、薄膜トランジスタ 220 のソース電極層及びドレイン電極層は、透光性を有する導電膜及び金属導電膜を積層し、フォトリソグラフィ工程により選択的にエッチングして形成する。薄膜トランジスタ 220 のソース電極層及びドレイン電極層上の金属導電膜は除去する。

【0119】

なお、金属導電膜のエッチングの際に、薄膜トランジスタ 220 のソース電極層及びドレイン電極層も除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

30

【0120】

例えば、金属導電膜を選択的にエッチングするため、アルカリ性のエッチャントを用いる。金属導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、金属導電膜は、単層構造でも、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する 2 層構造、Ti 膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する 3 層構造などが挙げられる。また、Al に、チタン (Ti)、タンタル (Ta)、タングステン (W)、モリブデン (Mo)、クロム (Cr)、ネオジム (Nd)、スカンジウム (Sc) から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、もしくは窒化膜を用いてもよい。

40

【0121】

本実施の形態では、金属導電膜として Ti 膜を用いて、ソース電極層及びドレイン電極層には In-Sn-O 系酸化物を用いて、エッチャントとして過水アンモニア水 (アンモニア、水、過酸化水素水の混合液) を用いる。

【0122】

酸化物半導体層と金属材料からなる補助電極層 268b の間に設けられるドレイン電極層 265b は低抵抗ドレイン領域 (L R N (Low Resistance N-type conductivity) 領域、L R D (Low Resistance Drain) 領域とも呼ぶ) としても機能する。酸化物半導体層、低抵抗ドレイン領域、金属電極

50

である補助電極層 268b の構成とすることによって、よりトランジスタの耐圧を向上させることができる。具体的には、低抵抗ドレイン領域のキャリア濃度は、高抵抗ドレイン領域 (H R D 領域) よりも大きく、例えば  $1 \times 10^{20} / \text{cm}^3$  以上  $1 \times 10^{21} / \text{cm}^3$  以下の範囲内であると好ましい。

【 0 1 2 3 】

また、ゲート配線、ソース配線、及び容量配線層は画素密度に応じて複数本設けられるものである。また、端子部においては、ゲート配線と同電位の第1の端子電極、ソース配線と同電位の第2の端子電極、容量配線層と同電位の第3の端子電極などが複数並べられて配置される。それぞれの端子電極の数は、それぞれ任意な数で設ければ良いものとし、実施者が適宜決定すれば良い。

10

【 0 1 2 4 】

端子部において、ゲート配線と同電位の第1の端子電極は、画素電極層 227 と同じ透光性を有する材料で形成することができる。第1の端子電極は、ゲート配線に達するコンタクトホールを介してゲート配線と電気的に接続される。ゲート配線に達するコンタクトホールは、薄膜トランジスタ 220 のドレイン電極層と、画素電極層 227 とを電気的に接続するためのコンタクトホールと同じフォトマスクを用い、平坦化絶縁層 204、保護絶縁層 203、酸化物絶縁層 266b、ゲート絶縁層 202 を選択的にエッチングして形成する。

【 0 1 2 5 】

また、端子部のソース配線 254 と同電位の第2の端子電極 255 は、画素電極層 227 と同じ透光性を有する材料で形成することができる。第2の端子電極 255 は、ソース配線 254 に達するコンタクトホールを介してソース配線と電気的に接続される。ソース配線は金属配線であり、薄膜トランジスタ 260 のソース電極層 265a と同じ材料、同じ工程で形成され、同電位である。

20

【 0 1 2 6 】

また、容量配線層 230 と同電位の第3の端子電極は、画素電極層 227 と同じ透光性を有する材料で形成することができる。また、容量配線層 230 に達するコンタクトホールは、容量電極 231 が画素電極層 227 と電気的に接続するためのコンタクトホールと同じフォトマスク、同じ工程で形成することができる。

【 0 1 2 7 】

30

また、アクティブマトリクス型の液晶表示装置を作製する場合には、アクティブマトリクス基板と、対向電極が設けられた対向基板との間に液晶層を設け、アクティブマトリクス基板と対向基板とを固定する。なお、対向基板に設けられた対向電極と電気的に接続する共通電極をアクティブマトリクス基板上に設け、共通電極と電気的に接続する第4の端子電極を端子部に設ける。この第4の端子電極は、共通電極を固定電位、例えば GND、0V などに設定するための端子である。第4の端子電極は、画素電極層 227 と同じ透光性を有する材料で形成することができる。

【 0 1 2 8 】

また、ゲート電極層、ソース電極層、ドレイン電極層、画素電極層、またはその他の電極層や、その他の配線層に同じ材料を用いれば共通のスペッターゲットや共通の製造装置を用いることができ、その材料コスト及びエッチング時に使用するエッチャント（またはエッチングガス）に要するコストを低減することができ、結果として製造コストを削減することができる。

40

【 0 1 2 9 】

また、図 3 (A) の構造において、平坦化絶縁層 204 として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

【 0 1 3 0 】

また、図 3 (B) に、図 3 (A) とは一部異なる断面構造を示す。図 3 (B) は、図 3 (A) と平坦化絶縁層 204 が端子部で存在しない点と駆動回路の薄膜トランジスタの構造が異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明

50

は省略する。図3(B)では、金属配線を用いる薄膜トランジスタ270を配置する。また、端子電極も金属配線と同じ材料、同じ工程で形成する。

【0131】

また、図3(B)の構造においては、平坦化絶縁層204として感光性の樹脂材料を用い、レジストマスクを形成する工程を省略する。従って、レジストマスクを用いることなく、平坦化絶縁層204が端子部で存在しない構成とすることができる。端子部において、平坦化絶縁層が存在しないと、FPCとの良好な接続を行いやさい。

【0132】

薄膜トランジスタ270は、絶縁表面を有する基板200上に、ゲート電極層271、ゲート絶縁層202、少なくともチャネル形成領域273、高抵抗ソース領域274a、及び高抵抗ドレイン領域274bを有する酸化物半導体層、ソース電極層275a、及びドレイン電極層275bを含む。また、チャネル形成領域273に接する酸化物絶縁層276aが設けられている。

【0133】

また、酸化物絶縁層276bと重なる酸化物半導体層の第1領域274c、第2領域274dは、チャネル形成領域273と同じ酸素過剰な状態であり、リーク電流の低減や、寄生容量を低減する機能も果たしている。また、保護絶縁層203と接する酸化物半導体層の第3領域274eは、チャネル形成領域273と高抵抗ソース領域274aの間に設けられる。また、保護絶縁層203と接する酸化物半導体層の第4領域274fは、チャネル形成領域273と高抵抗ドレイン領域274bの間に設けられる。保護絶縁層203と接する酸化物半導体層の第3領域274e、及び第4領域274fはオフ電流の低減を図ることができる。

【0134】

また、チャネル保護型の薄膜トランジスタは、チャネル形成領域のチャネル長Lを短くするため酸化物絶縁層の幅を狭くして、幅の狭い酸化物絶縁層上にソース電極層及びドレイン電極層を設けると酸化物絶縁層上で短絡する恐れがある。そのため、幅の狭い酸化物絶縁層276aから端部を離してソース電極層275a及びドレイン電極層275bを設ける構成である。

【0135】

なお、金属導電膜のエッティングの際に、薄膜トランジスタ270の酸化物半導体層も除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

【0136】

本実施の形態では、金属導電膜としてTi膜を用いて、酸化物半導体層にはIn-Ga-Zn-O系酸化物を用いて、エッチャントとして過水アンモニア水(アンモニア水、水、過酸化水素水の混合液)を用いる。

【0137】

また、駆動回路の薄膜トランジスタ270のゲート電極層は、酸化物半導体層の上方に設けられた導電層277と電気的に接続させる構造としてもよい。

【0138】

また、端子部のソース配線256と同電位の第2の端子電極257は、画素電極層227と同じ透光性を有する材料で形成することができる。ソース配線は金属配線であり、薄膜トランジスタ270のソース電極層275aと同じ材料、同じ工程で形成され、同電位である。

【0139】

また、薄膜トランジスタは静電気などにより破壊されやすいため、画素部または駆動回路と同一基板上に保護回路を設けることが好ましい。保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することができる。例えば、保護回路は画素部と、走査線入力端子及び信号線入力端子との間に配設されている。本実施の形態では複数の保護回路を配設して、走査線、信号線及び容量バス線に静電気等によりサージ電圧が印加され、画素トランジスタなどが破壊されないように構成されている。そのため、保護回路にはサージ電

10

20

30

40

50

圧が印加されたときに、共通配線に電荷を逃がすように構成する。また、保護回路は、走査線に対して並列に配置された非線形素子によって構成されている。非線形素子は、ダイオードのような二端子素子又はトランジスタのような三端子素子で構成される。例えば、画素部の薄膜トランジスタ 220 と同じ工程で形成することも可能であり、例えばゲート端子とドレイン端子を接続することによりダイオードと同様の特性を持たせることができる。

【0140】

なお、平坦化絶縁層 204 の形成工程を省略し、平坦化絶縁層 204 を設けない構造としてもよい。この場合、導電層 267、導電層 277、画素電極層 227、第 2 の端子電極 255、257 は保護絶縁層 203 上に接して設けられる。

10

【0141】

本実施の形態は実施の形態 1 と自由に組み合わせることができる。

【0142】

(実施の形態 3)

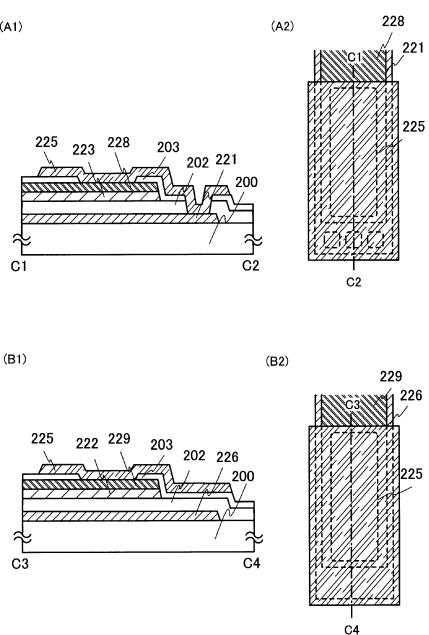

また、本実施の形態では、薄膜トランジスタと同一基板上に設けられる端子部の構成の一例を示す。なお、実施の形態 2 ではソース配線の端子部の一例を示したが、本実施の形態では実施の形態 2 とは異なる構成のソース配線の端子部と、ゲート配線の端子部を図示する。なお、図 4 において、図 3 (A) または図 3 (B) と同じ箇所には同じ符号を用いて説明する。

【0143】

図 4 (A1)、図 4 (A2) は、ゲート配線端子部の上面図及び断面図をそれぞれ図示している。図 4 (A1) は図 4 (A2) 中の C1 - C2 線に沿った断面図に相当する。図 4 (A1) において、保護絶縁層 203 上に形成される導電層 225 は、入力端子として機能する接続用の端子電極である。また、図 4 (A1) において、端子部では、ゲート電極層 421b と同じ材料で形成される第 1 の端子 221 と、ソース配線と同じ材料で形成される接続電極層 223、228 とがゲート絶縁層 202 を介して重なり、導電層 225 で導通させている。また、第 1 の端子 221 は、図 3 (B) に示す構成とする場合には金属配線材料を用いることができる。

20

【0144】

また、図 4 (B1)、及び図 4 (B2) は、図 3 (B) に示すソース配線端子部とは異なるソース配線端子部の上面図及び断面図をそれぞれ図示している。また、図 4 (B1) は図 4 (B2) 中の C3 - C4 線に沿った断面図に相当する。図 4 (B1) において、保護絶縁層 203 上に形成される導電層 225 は、入力端子として機能する接続用の端子電極である。また、図 4 (B1) において、端子部では、ゲート配線と同じ材料で形成される電極層 226 が、ソース配線と電気的に接続される第 2 の端子 222、229 の下方にゲート絶縁層 202 を介して重なる。電極層 226 は第 2 の端子 222、229 とは電気的に接続しておらず、電極層 226 を第 2 の端子 222、229 と異なる電位、例えばフローティング、GND、0V などに設定すれば、ノイズ対策のための容量または静電気対策のための容量を形成することができる。また、第 2 の端子 222、229 は、保護絶縁層 203 を介して導電層 225 と電気的に接続している。また、導電材料の積層である第 2 の端子 222、229 は、図 3 (B) に示す構成とする場合には金属配線材料の単層を用いることができる。

30

【0145】

ゲート配線、ソース配線、及び容量配線は画素密度に応じて複数本設けられるものである。また、端子部においては、ゲート配線と同電位の第 1 の端子、ソース配線と同電位の第 2 の端子、容量配線と同電位の第 3 の端子などが複数並べられて配置される。それぞれの端子の数は、それぞれ任意な数で設ければ良いものとし、実施者が適宣決定すれば良い。

40

【0146】

本実施の形態は実施の形態 1 または実施の形態 2 と自由に組み合わせることができる。

【0147】

50

## (実施の形態 4 )

ここでは、第1の基板と第2の基板の間に液晶層を封入する液晶表示装置において、第2の基板に設けられた対向電極と電気的に接続するための共通接続部を第1の基板上に形成する例を示す。なお、第1の基板にはスイッチング素子として薄膜トランジスタが形成されており、共通接続部の作製工程を画素部のスイッチング素子の作製工程と共通化させることで工程を複雑にすることなく形成する。

## 【0148】

共通接続部は、第1の基板と第2の基板とを接着するためのシール材と重なる位置に配置され、シール材に含まれる導電性粒子を介して対向電極と電気的な接続が行われる。或いは、シール材と重ならない箇所（ただし画素部を除く）に共通接続部を設け、共通接続部に重なるように導電性粒子を含むペーストをシール材とは別途設けて、対向電極と電気的な接続が行われる。

10

## 【0149】

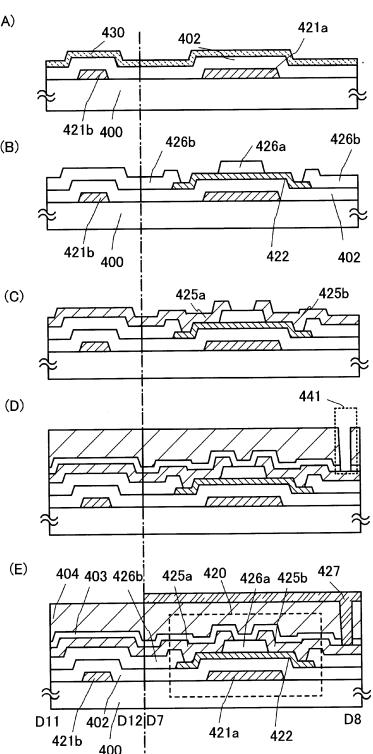

図5(A)は薄膜トランジスタと共に接続部とを同一基板上に作製する半導体装置の断面構造図を示す図である。

## 【0150】

図5(A)において、画素電極層227と電気的に接続する薄膜トランジスタ220は、画素部に設けられるチャネル保護型の薄膜トランジスタであり、本実施の形態では、実施の形態1の薄膜トランジスタ448と同じ構造を用いる。

20

## 【0151】

また、図5(B)は共通接続部の上面図の一例を示す図であり、図中の鎖線C5-C6に沿った共通接続部の断面図が図5(A)に相当する。なお、図5(B)において図5(A)と同一の部分には同じ符号を用いて説明する。

## 【0152】

共通電位線205、210は、ゲート絶縁層202上に設けられ、薄膜トランジスタ220のソース電極層及びドレイン電極層と同じ材料及び同じ工程で作製される。

## 【0153】

また、共通電位線205、210は、保護絶縁層203で覆われ、保護絶縁層203は、共通電位線205、210と重なる位置に複数の開口部を有している。この開口部は、薄膜トランジスタ220のドレイン電極層と画素電極層227とを接続するコンタクトホールと同じ工程で作製される。

30

## 【0154】

なお、ここでは面積サイズが大きく異なるため、画素部におけるコンタクトホールと、共通接続部の開口部と使い分けて呼ぶこととする。また、図5(A)では、画素部と共に接続部とで同じ縮尺で図示しておらず、例えば共通接続部の鎖線C5-C6の長さが500μm程度であるのに対して、薄膜トランジスタの幅は50μm未満であり、実際には10倍以上面積サイズが大きいが、分かりやすくするため、図5(A)に画素部と共に接続部の縮尺をそれぞれ変えて図示している。

## 【0155】

また、共通電極層206は、保護絶縁層203上に設けられ、画素部の画素電極層227と同じ材料及び同じ工程で作製される。

40

## 【0156】

このように、画素部のスイッチング素子の作製工程と共にさせて共通接続部の作製工程を行う。

## 【0157】

そして画素部と共に接続部が設けられた第1の基板と、対向電極を有する第2の基板とをシール材を用いて固定する。

## 【0158】

シール材に導電性粒子を含ませる場合は、シール材と共に接続部が重なるように一対の基板の位置合わせが行われる。例えば、小型の液晶パネルにおいては、画素部の対角などに

50

2個の共通接続部がシール材と重ねて配置される。また、大型の液晶パネルにおいては、4個以上の共通接続部がシール材と重ねて配置される。

【0159】

なお、共通電極層206は、シール材に含まれる導電性粒子と接触する電極であり、第2の基板の対向電極と電気的に接続が行われる。

【0160】

液晶注入法を用いる場合は、シール材で一対の基板を固定した後、液晶を一対の基板間に注入する。また、液晶滴下法を用いる場合は、第2の基板或いは第1の基板上にシール材を描画し、液晶を滴下させた後、減圧下で一対の基板を貼り合わせる。

【0161】

なお、本実施の形態では、対向電極と電気的に接続する共通接続部の例を示したが、特に限定されず、他の配線と接続する接続部や、外部接続端子などと接続する接続部に用いることができる。

【0162】

また、図5(C)に、図5(A)とは一部異なる断面構造を示す。図5(C)は、図5(A)と共に電極層206と重なる酸化物半導体層及び端部を覆う酸化物絶縁層が存在する点と、共通電位線として金属配線を用いる点以外の構成は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。

【0163】

酸化物半導体層207は、ゲート絶縁層202上に設けられ、薄膜トランジスタ220の酸化物半導体層と同じ材料及び同じ工程で作製される。また、酸化物半導体層207を覆う酸化物絶縁層208を形成する。そして、酸化物半導体層207上に金属配線からなる共通電位線209を形成する。この金属配線からなる共通電位線209は、実施の形態2の図3(B)に示したように、駆動回路の薄膜トランジスタのソース電極層またはドレイン電極層と同じ工程で形成する。

【0164】

また、共通電位線209は、保護絶縁層203で覆われ、保護絶縁層203は、共通電位線209と重なる位置に複数の開口部を有している。この開口部は、薄膜トランジスタ220のドレイン電極層と画素電極層227とを接続するコンタクトホールと同じ工程で作製される。

【0165】

また、共通電極層206は、保護絶縁層203上に設けられ、画素部の画素電極層227と同じ材料及び同じ工程で作製される。

【0166】

このように、画素部のスイッチング素子の作製工程と共に接続部の作製工程を行い、共通電位線を金属配線として配線抵抗の低減を図る構成としてもよい。

【0167】

本実施の形態は実施の形態1乃至3のいずれか一と自由に組み合わせることができる。

【0168】

(実施の形態5)

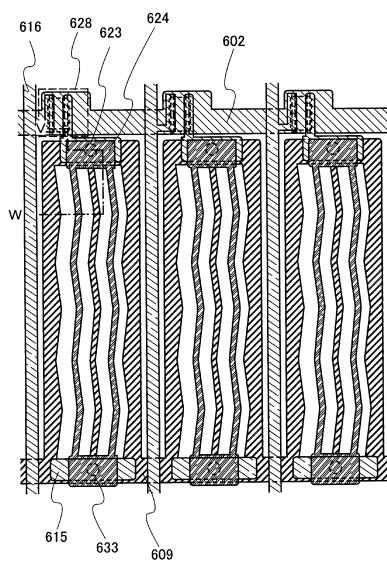

実施の形態1または実施の形態2ではゲート絶縁層が単層の例を示したが、本実施の形態では、積層の例を示す。なお、図6において、図3(A)または図3(B)と同じ箇所には同じ符号を用いて説明する。

【0169】

図6(A)において、薄膜トランジスタ280は、画素部に設けられるチャネル保護型の薄膜トランジスタであり、ゲート絶縁層が2層の例である。

【0170】

本実施の形態では、膜厚50nm以上200nm以下の第1のゲート絶縁層282aと、膜厚50nm以上300nm以下の第2のゲート絶縁層282bの積層のゲート絶縁層とする。第1のゲート絶縁層282aとしては膜厚100nmの窒化珪素膜または窒化酸化

10

20

30

40

50

珪素膜を用いる。また、第2のゲート絶縁層282bとしては、膜厚100nmの酸化珪素膜を用いる。

【0171】

また、薄膜トランジスタ280は、絶縁表面を有する基板上に、ゲート電極層281、第1のゲート絶縁層282a、第2のゲート絶縁層282b、少なくともチャネル形成領域283、高抵抗ソース領域284a、及び高抵抗ドレイン領域284b、ソース領域284c、ドレイン領域284dを有する酸化物半導体層、ソース電極層285a、及びドレイン電極層285bを含む。また、チャネル形成領域283に接する酸化物絶縁層286aが設けられている。また、画素電極層227はドレイン電極層285bと電気的に接続されている。

10

【0172】

なお、保持容量は、画素電極層227の下方に設けられ、容量電極231が画素電極層227と電気的に接続される。

【0173】

本実施の形態では、容量電極231、及び容量配線層230を用いて保持容量を形成する。

【0174】

また、図6(A)において保持容量は、大きな容量を形成するため、容量配線と容量電極の間にゲート絶縁層のみとしている。

【0175】

本実施の形態では酸化物絶縁層286bとしてスパッタ法で得られる酸化珪素膜を用い、容量配線層230と重なる酸化物絶縁層を除去する際に、酸化珪素膜である第2のゲート絶縁層もエッチングして薄膜化して第3のゲート絶縁層282cとする例である。なお、第1のゲート絶縁層282aは、窒化珪素膜または窒化酸化珪素膜であり、エッチングストッパーとして機能し、ゲート電極層や基板へのエッチングダメージを防ぐ。

20

【0176】

膜厚の薄い第3のゲート絶縁層282cとすることによって保持容量を増大させることができる。

【0177】

また、図6(B)に、図6(A)とは一部異なる断面構造を示す。

30

【0178】

図6(B)に示す薄膜トランジスタ290では、膜厚50nm以上200nm以下の第1のゲート絶縁層292aと、膜厚1nm以上50nm以下の第2のゲート絶縁層292bの積層のゲート絶縁層とする。第1のゲート絶縁層292aとしては膜厚100nmの酸化珪素膜を用いる。また、第2のゲート絶縁層292bとしては、膜厚10nmの窒化珪素膜または窒化酸化珪素膜を用いる。

【0179】

薄膜トランジスタ290は、絶縁表面を有する基板200上に、ゲート電極層291、第1のゲート絶縁層292a、第2のゲート絶縁層292b、少なくともチャネル形成領域293、高抵抗ソース領域294a、及び高抵抗ドレイン領域294bを有する酸化物半導体層、ソース電極層295a、及びドレイン電極層295bを含む。また、チャネル形成領域293に接する酸化物絶縁層296aが設けられている。

40

【0180】

また、酸化物絶縁層296bと重なる酸化物半導体層の第1領域294c、第2領域294dは、チャネル形成領域293と同じ酸素過剰な状態であり、リーク電流の低減や、寄生容量を低減する機能も果たしている。また、保護絶縁層203と接する酸化物半導体層の第3領域294eは、チャネル形成領域293と高抵抗ソース領域294aの間に設けられる。また、保護絶縁層203と接する酸化物半導体層の第4領域294fは、チャネル形成領域293と高抵抗ドレイン領域294bの間に設けられる。保護絶縁層203と接する酸化物半導体層の第3領域294e、及び第4領域294fはオフ電流の低減を図

50

ることができる。

【0181】

また、酸化物半導体層の第3領域294e、及び第4領域294fは窒化珪素膜または窒化酸化珪素膜である第2のゲート絶縁層292bとも接する。保護絶縁層203は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化珪素膜、窒化アルミニウム膜、窒化酸化珪素膜、酸化窒化アルミニウム膜などを用いる。

【0182】

また、本実施の形態では酸化物絶縁層296bとしてスパッタ法で得られる酸化珪素膜を用い、容量配線層230と重なる酸化物絶縁層を除去する際に、窒化珪素膜または窒化酸化珪素膜である第2のゲート絶縁層をエッチングストッパーとして酸化物絶縁層をエッチングする例である。

10

【0183】

また、チャネル保護型の薄膜トランジスタは、チャネル形成領域のチャネル長Lを短くするため酸化物絶縁層の幅を狭くして、幅の狭い酸化物絶縁層上にソース電極層及びドレイン電極層を設けると酸化物絶縁層上で短絡する恐れがある。そのため、幅の狭い酸化物絶縁層296aから端部を離してソース電極層295a及びドレイン電極層295bを設ける構成である。

【0184】

本実施の形態は実施の形態1乃至4のいずれか一と自由に組み合わせることができる。

20

【0185】

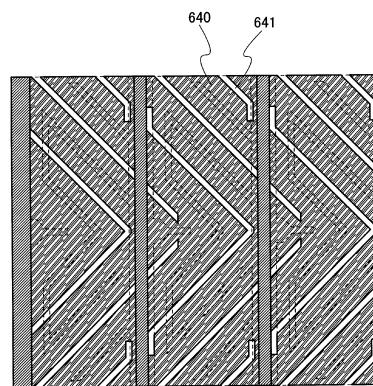

(実施の形態6)

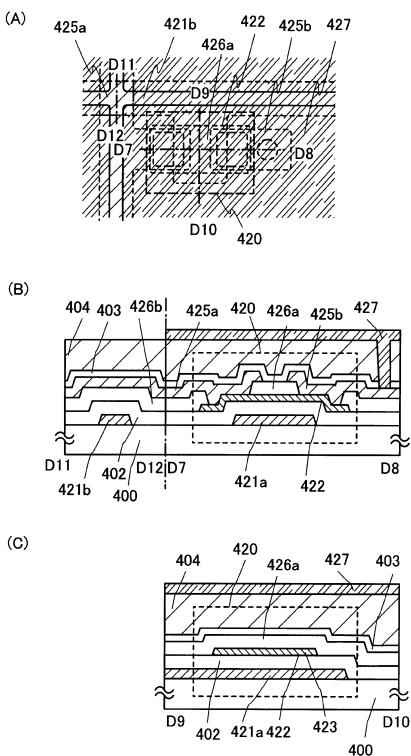

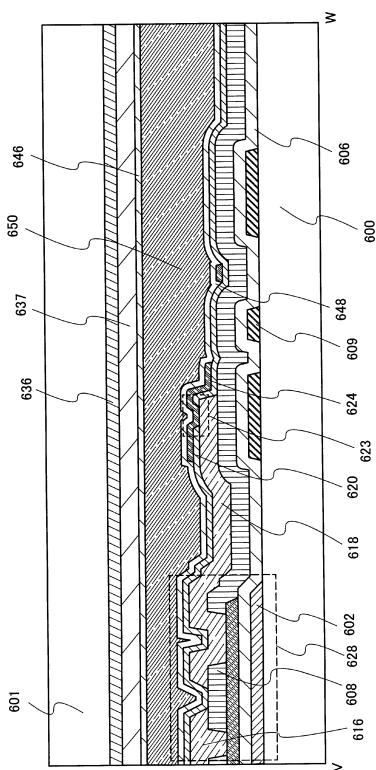

本実施の形態では、薄膜トランジスタの作製工程の一部が実施の形態1と異なる例を図7及び図8に示す。図7及び図8は、図1及び図2と工程が一部異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。

【0186】

まず、実施の形態1に従って、基板上にゲート電極層、ゲート絶縁層、及び酸化物半導体膜430の形成を行い、実施の形態1における図2(A)の工程まで行う。図2(A)は図8(A)と同一である。

【0187】

30

そして、酸化物半導体膜430を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。

【0188】

次いで、酸化物半導体層の脱水化または脱水素化を行う。脱水化または脱水素化を行う第1の加熱処理の温度は、400以上基板の歪み点未満、好ましくは425以上とする。なお、425以上であれば熱処理時間は1時間以下でよいが、425未満であれば加熱処理時間は、1時間よりも長時間行うこととする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。その後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥工業(露点が-40以下、好ましくは-60以下)を導入して冷却を行う。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

40

【0189】

また、脱水化または脱水素化を行う第1の加熱処理後に200以上400以下、好ましくは200以上300以下の温度で酸素ガスまたはN<sub>2</sub>Oガス雰囲気下での加熱処理を行ってもよい。

【0190】

50

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜430に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0191】

以上の工程を経ることによって酸化物半導体膜全体を酸素過剰な状態とすることで、高抵抗化、即ちI型化させる。

【0192】

次いで、ゲート絶縁層402、及び酸化物半導体層上に、スパッタ法で酸化物絶縁膜を形成した後、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行って酸化物絶縁層426a、426bを形成し、その後レジストマスクを除去する(図8(B)参照)。

10

【0193】

次いで、ゲート絶縁層402、酸化物絶縁層426a、426b、及び酸化物半導体層422上に、透光性を有する導電膜を形成した後、第4のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってソース電極層425a、及びドレイン電極層425bを形成する(図8(C)参照)。

【0194】

次いで、薄膜トランジスタの電気的特性のばらつきを軽減するため、不活性ガス雰囲気下、または窒素ガス雰囲気下で加熱処理(好ましくは150以上350未満)を行ってもよい。例えば、窒素雰囲気下で250、1時間の加熱処理を行う。

20

【0195】

次いで、酸化物絶縁層426a、426b、ソース電極層425a、ドレイン電極層425b上に保護絶縁層403を形成する。

【0196】

次いで、保護絶縁層403上に平坦化絶縁層404を形成する。

【0197】

次に、第5のフォトリソグラフィ工程を行い、レジストマスクを形成し、平坦化絶縁層404、及び保護絶縁層403のエッチングによりドレイン電極層425bに達するコンタクトホール441を形成し、レジストマスクを除去する(図8(D)参照)。

30

【0198】

次いで、透光性を有する導電膜を成膜する。

【0199】

次に、第6のフォトリソグラフィ工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して画素電極層427を形成し、レジストマスクを除去する(図8(E)参照)。

【0200】

以上の工程により、6枚のマスクを用いて、同一基板上に薄膜トランジスタ420と、寄生容量の低減された配線交差部を作製することができる。

【0201】

画素用の薄膜トランジスタ420は、チャネル形成領域を含む酸化物半導体層422を含むチャネル保護型薄膜トランジスタである。

40

【0202】

また、図7(A)は、画素に配置されるチャネル保護型の薄膜トランジスタ420の平面図であり、図7(B)は図7(A)の線D7-D8における断面図及び図7(A)の線D11-D12における断面図である。また、図7(C)は、図7(A)の線D9-D10における断面図である。なお、図8(E)は図7(B)と同一である。

【0203】

本実施の形態は実施の形態1乃至5のいずれか一と自由に組み合わせることができる。

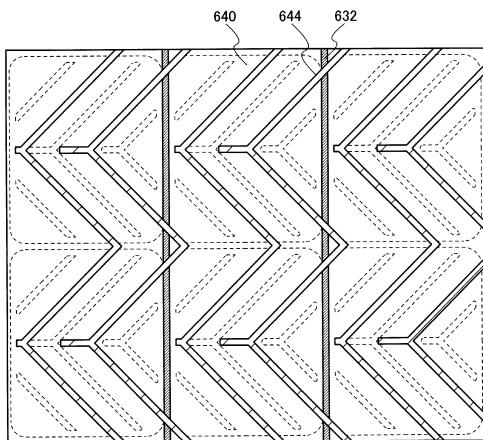

【0204】

(実施の形態7)

50

本実施の形態では、保持容量の構成について、実施の形態2と異なる例を図9(A)及び図9(B)に示す。図9(A)は、図3(A)と保持容量の構成が異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。なお、図9(A)では画素部の薄膜トランジスタ220と保持容量の断面構造を示す。

【0205】

図9(A)は、誘電体を保護絶縁層203、及び平坦化絶縁層204とし、画素電極層227と、該画素電極層227と重なる容量配線層250とで保持容量を形成する例である。容量配線層250は、画素部の薄膜トランジスタ220のソース電極層と同じ透光性を有する材料、及び同じ工程で形成されるため、薄膜トランジスタ220のソース配線層と重ならないようにレイアウトされる。

10

【0206】

図9(A)に示す保持容量は、一対の電極及び誘電体が透光性を有しており、保持容量全体として透光性を有する。

【0207】

また、図9(B)は、図9(A)と異なる保持容量の構成の例である。図9(B)も、図3(A)と保持容量の構成が異なる点以外は同じであるため、同じ箇所には同じ符号を用い、同じ箇所の詳細な説明は省略する。

【0208】

図9(B)は、誘電体をゲート絶縁層202とし、容量配線層230と、該容量配線層230と重なる酸化物半導体層251と容量電極231との積層で保持容量を形成する例である。また、酸化物半導体層251上に容量電極231は接して積層されており、保持容量の一方の電極として機能する。なお、酸化物半導体層251は、薄膜トランジスタ220の酸化物半導体層と同じ透光性を有する材料、同じ工程で形成する。また、容量配線層230は、薄膜トランジスタ220のゲート電極層と同じ透光性を有する材料、同じ工程で形成されるため、薄膜トランジスタ220のゲート配線層と重ならないようにレイアウトされる。また、容量電極231は画素電極層227と電気的に接続されている。

20

【0209】

図9(B)に示す保持容量も、一対の電極及び誘電体が透光性を有しており、保持容量全体として透光性を有する。

【0210】

図9(A)及び図9(B)に示す保持容量は、透光性を有しており、ゲート配線の本数を増やすなどして表示画像の高精細化を図るため、画素寸法を微細化しても、十分な容量を得ることができ、且つ、高い開口率を実現することができる。

30

【0211】

本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0212】

(実施の形態8)

本実施の形態では、同一基板上に少なくとも駆動回路の一部と、画素部に配置する薄膜トランジスタを作製する例について以下に説明する。

【0213】

画素部に配置する薄膜トランジスタは、実施の形態1、2、5、6に従って形成する。また、実施の形態1、2、5、6に示す薄膜トランジスタはnチャネル型TFTであるため、駆動回路のうち、nチャネル型TFTで構成することができる駆動回路の一部を画素部の薄膜トランジスタと同一基板上に形成する。

40

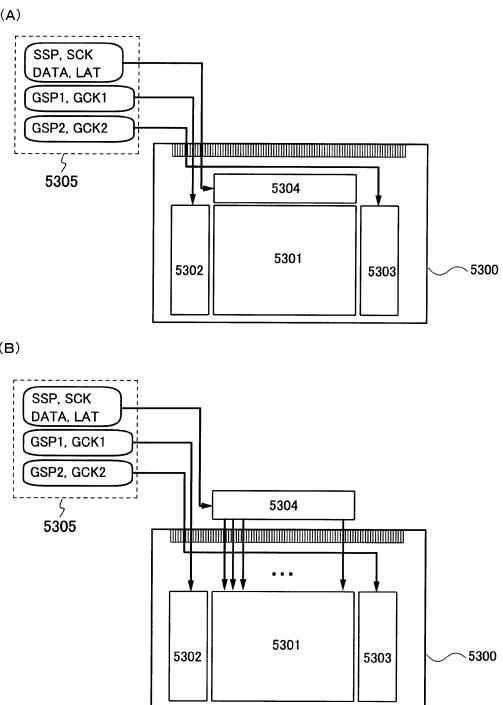

【0214】

アクティブマトリクス型表示装置のブロック図の一例を図14(A)に示す。表示装置の基板5300上には、画素部5301、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304を有する。画素部5301には、複数の信号線が信号線駆動回路5304から延伸して配置され、複数の走査線が第1の走査線駆動回路5302、及び走査線駆動回路5303から延伸して配置されている。なお走査線と信号

50

線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板 5300 は FPC (Flexible Printed Circuit) 等の接続部を介して、タイミング制御回路 5305 (コントローラ、制御 I C ともいう) に接続されている。

【0215】

図 14 (A) では、第 1 の走査線駆動回路 5302、第 2 の走査線駆動回路 5303、信号線駆動回路 5304 は、画素部 5301 と同じ基板 5300 上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板 5300 外部に駆動回路を設けた場合の配線を延伸させることによる接続部での接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

10

【0216】

なお、タイミング制御回路 5305 は、第 1 の走査線駆動回路 5302 に対し、一例として、第 1 の走査線駆動回路用スタート信号 (GSP1)、走査線駆動回路用クロック信号 (GCK1) を供給する。また、タイミング制御回路 5305 は、第 2 の走査線駆動回路 5303 に対し、一例として、第 2 の走査線駆動回路用スタート信号 (GSP2) (スタートパルスともいう)、走査線駆動回路用クロック信号 (GCK2) を供給する。信号線駆動回路 5304 に、信号線駆動回路用スタート信号 (SSP)、信号線駆動回路用クロック信号 (SCK)、ビデオ信号用データ (DATA) (単にビデオ信号ともいう)、ラッチ信号 (LAT) を供給するものとする。なお各クロック信号は、周期のずれた複数のクロック信号でもよいし、クロック信号を反転させた信号 (CKB) とともに供給されるものであってもよい。なお、第 1 の走査線駆動回路 5302 と第 2 の走査線駆動回路 5303 との一方を省略することが可能である。

20

【0217】

図 14 (B) では、駆動周波数が低い回路 (例えば、第 1 の走査線駆動回路 5302、第 2 の走査線駆動回路 5303) を画素部 5301 と同じ基板 5300 に形成し、信号線駆動回路 5304 を画素部 5301 とは別の基板に形成する構成について示している。当該構成により、単結晶半導体を用いたトランジスタと比較すると電界効果移動度が小さい薄膜トランジスタによって、基板 5300 に形成する駆動回路を構成することができる。したがって、表示装置の大型化、コストの低減、又は歩留まりの向上などを図ることができる。

30

【0218】

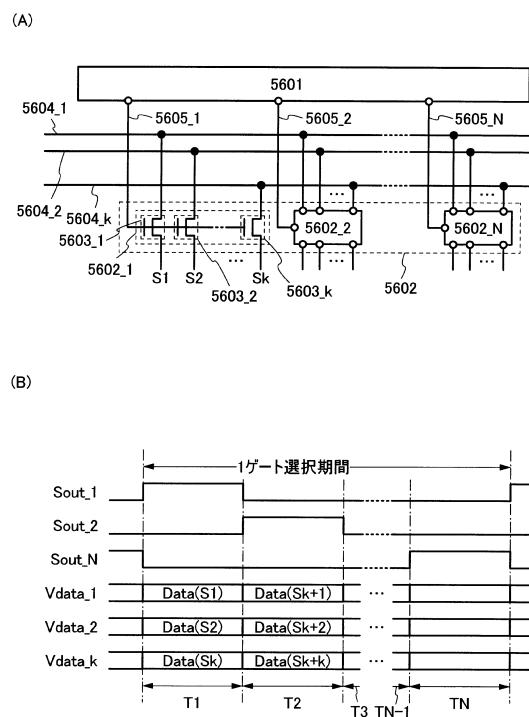

また、実施の形態 1、2、5、6 に示す薄膜トランジスタは、n チャネル型 TFT である。図 15 (A)、図 15 (B) では n チャネル型 TFT で構成する信号線駆動回路の構成、動作について一例を示し説明する。

【0219】

信号線駆動回路は、シフトレジスタ 5601、及びスイッチング回路 5602 を有する。スイッチング回路 5602 は、スイッチング回路 5602\_1 ~ 5602\_N (N は自然数) という複数の回路を有する。スイッチング回路 5602\_1 ~ 5602\_N は、各々、薄膜トランジスタ 5603\_1 ~ 5603\_k (k は自然数) という複数のトランジスタを有する。薄膜トランジスタ 5603\_1 ~ 5603\_k が、N チャネル型 TFT である例を説明する。

40

【0220】

信号線駆動回路の接続関係について、スイッチング回路 5602\_1 を例にして説明する。薄膜トランジスタ 5603\_1 ~ 5603\_k の第 1 端子は、各々、配線 5604\_1 ~ 5604\_k と接続される。薄膜トランジスタ 5603\_1 ~ 5603\_k の第 2 端子は、各々、信号線 S1 ~ Sk と接続される。薄膜トランジスタ 5603\_1 ~ 5603\_k のゲートは、配線 5605\_1 と接続される。

【0221】

シフトレジスタ 5601 は、配線 5605\_1 ~ 5605\_N に順番に H レベル (H 信号、高電源電位レベル、ともいう) の信号を出力し、スイッチング回路 5602\_1 ~ 56

50

02\_Nを順番に選択する機能を有する。

【0222】

スイッチング回路5602\_1は、配線5604\_1～5604\_kと信号線S1～Skとの導通状態（第1端子と第2端子との間の導通）に制御する機能、即ち配線5604\_1～5604\_kの電位を信号線S1～Skに供給するか否かを制御する機能を有する。このように、スイッチング回路5602\_1は、セレクタとしての機能を有する。また薄膜トランジスタ5603\_1～5603\_kは、各々、配線5604\_1～5604\_kと信号線S1～Skとの導通状態を制御する機能、即ち配線5604\_1～5604\_kの電位を信号線S1～Skに供給する機能を有する。このように、薄膜トランジスタ5603\_1～5603\_kは、各々、スイッチとしての機能を有する。

10

【0223】

なお、配線5604\_1～5604\_kには、各々、ビデオ信号用データ（DATA）が入力される。ビデオ信号用データ（DATA）は、画像情報又は画像信号に応じたアナログ信号である場合が多い。

【0224】

次に、図15（A）の信号線駆動回路の動作について、図15（B）のタイミングチャートを参照して説明する。図15（B）には、信号Sout\_1～Sout\_N、及び信号Vdata\_1～Vdata\_kの一例を示す。信号Sout\_1～Sout\_Nは、各々、シフトレジスタ5601の出力信号の一例であり、信号Vdata\_1～Vdata\_kは、各々、配線5604\_1～5604\_kに入力される信号の一例である。なお、信号線駆動回路の1動作期間は、表示装置における1ゲート選択期間に対応する。1ゲート選択期間は、一例として、期間T1～期間TNに分割される。期間T1～TNは、各々、選択された行に属する画素にビデオ信号用データ（DATA）を書き込むための期間である。

20

【0225】

なお、本実施の形態の図面等において示す各構成の、信号波形のなまり等は、明瞭化のために誇張して表記している場合がある。よって、必ずしもそのスケールに限定されないものであることを付記する。

【0226】

期間T1～期間TNにおいて、シフトレジスタ5601は、Hレベルの信号を配線5605\_1～5605\_Nに順番に出力する。例えば、期間T1において、シフトレジスタ5601は、ハイレベルの信号を配線5605\_1に出力する。すると、薄膜トランジスタ5603\_1～5603\_kはオンになるので、配線5604\_1～5604\_kと、信号線S1～Skとが導通状態になる。このとき、配線5604\_1～5604\_kには、Data(S1)～Data(Sk)が入力される。Data(S1)～Data(Sk)は、各々、薄膜トランジスタ5603\_1～5603\_kを介して、選択される行に属する画素のうち、1列目～k列目の画素に書き込まれる。こうして、期間T1～TNにおいて、選択された行に属する画素に、k列ずつ順番にビデオ信号用データ（DATA）が書き込まれる。

30

【0227】

以上のように、ビデオ信号用データ（DATA）が複数の列ずつ画素に書き込まれることによって、ビデオ信号用データ（DATA）の数、又は配線の数を減らすことができる。よって、外部回路との接続数を減らすことができる。また、ビデオ信号が複数の列ずつ画素に書き込まれることによって、書き込み時間を長くすることができ、ビデオ信号の書き込み不足を防止することができる。

40

【0228】

なお、シフトレジスタ5601及びスイッチング回路5602としては、実施の形態1、2、5、6に示す薄膜トランジスタで構成される回路を用いることが可能である。この場合、シフトレジスタ5601が有する全てのトランジスタの極性をNチャネル型、又はPチャネル型のいずれかの極性のみで構成することができる。

50

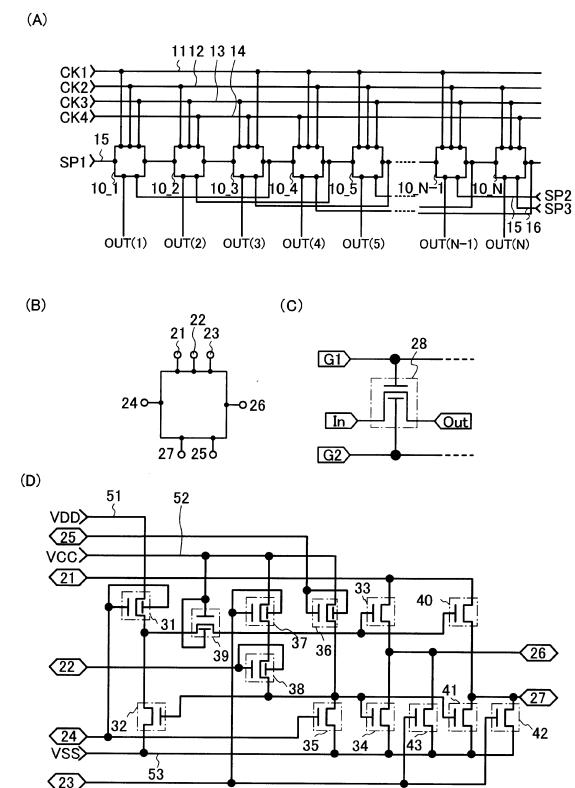

## 【0229】

走査線駆動回路及び／または信号線駆動回路の一部に用いるシフトレジスタの一形態について図16及び図17を用いて説明する。

## 【0230】

走査線駆動回路は、シフトレジスタを有している。また場合によってはレベルシフタやバッファなどを有していても良い。走査線駆動回路において、シフトレジスタにクロック信号（C L K）及びスタートパルス信号（S P）が入力されることによって、選択信号が生成される。生成された選択信号はバッファにおいて緩衝増幅され、対応する走査線に供給される。走査線には、1ライン分の画素のトランジスタのゲート電極が接続されている。そして、1ライン分の画素のトランジスタを一齊にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

10

## 【0231】

走査線駆動回路、信号線駆動回路のシフトレジスタについて、図16及び図17を参照して説明する。シフトレジスタは、第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_N（Nは3以上の自然数）を有している（図16（A）参照）。図16（A）に示すシフトレジスタの第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_Nには、第1の配線1\_1より第1のクロック信号CK1、第2の配線1\_2より第2のクロック信号CK2、第3の配線1\_3より第3のクロック信号CK3、第4の配線1\_4より第4のクロック信号CK4が供給される。また第1のパルス出力回路10\_1では、第5の配線1\_5からのスタートパルスS P 1（第1のスタートパルス）が入力される。また2段目以降の第nのパルス出力回路10\_n（nは、2以上N以下の自然数）では、一段前段のパルス出力回路からの信号（前段信号OUT（n-1）という）が入力される。また第1のパルス出力回路10\_1では、2段後段の第3のパルス出力回路10\_3からの信号が入力される。同様に、または2段目以降の第nのパルス出力回路10\_nでは、2段後段の第（n+2）のパルス出力回路10\_（n+2）からの信号（後段信号OUT（n+2）という）が入力される。従って、また各段のパルス出力回路からは、後段及び／または二つ前段のパルス出力回路に入力するための第1の出力信号（OUT（1）（S R）～OUT（N）（S R））及び別の回路等に入力される第2の出力信号（OUT（1）～OUT（N））が出力される。なお、図16（A）に示すように、シフトレジスタの最終段の2つの段には、後段信号OUT（n+2）が入力されないため、一例としては、別途第2のスタートパルスS P 2、第3のスタートパルスS P 3をそれぞれ入力する構成とすればよい。

20

## 【0232】

なお、クロック信号（C K）は、一定の間隔でHレベルとLレベル（L信号、低電源電位レベル、ともいう）を繰り返す信号である。ここで、第1のクロック信号（C K 1）～第4のクロック信号（C K 4）は、順に1/4周期分遅延している。本実施の形態では、第1のクロック信号（C K 1）～第4のクロック信号（C K 4）を利用して、パルス出力回路の駆動の制御等を行う。なお、クロック信号は、入力される駆動回路に応じて、G C K、S C Kということもあるが、ここではC Kとして説明を行う

30

## 【0233】

第1の入力端子2\_1、第2の入力端子2\_2及び第3の入力端子2\_3は、第1の配線1\_1～第4の配線1\_4のいずれかと電気的に接続されている。例えば、図16（A）において、第1のパルス出力回路10\_1は、第1の入力端子2\_1が第1の配線1\_1と電気的に接続され、第2の入力端子2\_2が第2の配線1\_2と電気的に接続され、第3の入力端子2\_3が第3の配線1\_3と電気的に接続されている。また、第2のパルス出力回路10\_2は、第1の入力端子2\_1が第2の配線1\_2と電気的に接続され、第2の入力端子2\_2が第3の配線1\_3と電気的に接続され、第3の入力端子2\_3が第4の配線1\_4と電気的に接続されている。

40

## 【0234】

第1のパルス出力回路10\_1～第Nのパルス出力回路10\_Nの各々は、第1の入力端

50

子 2 1、第 2 の入力端子 2 2、第 3 の入力端子 2 3、第 4 の入力端子 2 4、第 5 の入力端子 2 5、第 1 の出力端子 2 6、第 2 の出力端子 2 7 を有しているとする(図 16 (B) 参照)。第 1 のパルス出力回路 10\_1 において、第 1 の入力端子 2 1 に第 1 のクロック信号 C K 1 が入力され、第 2 の入力端子 2 2 に第 2 のクロック信号 C K 2 が入力され、第 3 の入力端子 2 3 に第 3 のクロック信号 C K 3 が入力され、第 4 の入力端子 2 4 にスタートパルスが入力され、第 5 の入力端子 2 5 に後段信号 O U T (3) が入力され、第 1 の出力端子 2 6 より第 1 の出力信号 O U T (1) (S R) が出力され、第 2 の出力端子 2 7 より第 2 の出力信号 O U T (1) が出力されていることとなる。

【 0 2 3 5 】

なお第 1 のパルス出力回路 10\_1 ~ 第 N のパルス出力回路 10\_N は、3 端子の薄膜トランジスタ(TFT: Thin Film Transistorともいう)の他に、上記実施の形態で説明した 4 端子の薄膜トランジスタを用いることができる。図 16 (C) に上記実施の形態で説明した 4 端子の薄膜トランジスタ 28 のシンボルについて示す。図 16 (C) に示す薄膜トランジスタ 28 のシンボルは、上記実施の形態 1、2、5、6 のいずれか一で説明した 4 端子の薄膜トランジスタを意味し、図面等で以下用いることとする。なお、本明細書において、薄膜トランジスタが半導体層を介して二つのゲート電極を有する場合、半導体層より下方のゲート電極を下方のゲート電極、半導体層に対して上方のゲート電極を上方のゲート電極とも呼ぶ。薄膜トランジスタ 28 は、下方のゲート電極に入力される第 1 の制御信号 G 1 及び上方のゲート電極に入力される第 2 の制御信号 G 2 によって、In 端子と Out 端子間の電気的な制御を行うことのできる素子である。

【 0 2 3 6 】

酸化物半導体を薄膜トランジスタのチャネル形成領域を含む半導体層に用いた場合、製造工程により、しきい値電圧がマイナス側、或いはプラス側にシフトすることがある。そのため、チャネル形成領域を含む半導体層に酸化物半導体を用いた薄膜トランジスタでは、しきい値電圧の制御を行うことのできる構成が好適である。図 16 (C) に示す 4 端子の薄膜トランジスタ 28 のしきい値電圧は、薄膜トランジスタ 28 のチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設け、上方及び / または下方のゲート電極の電位を制御することにより所望の値に制御することができる。

【 0 2 3 7 】

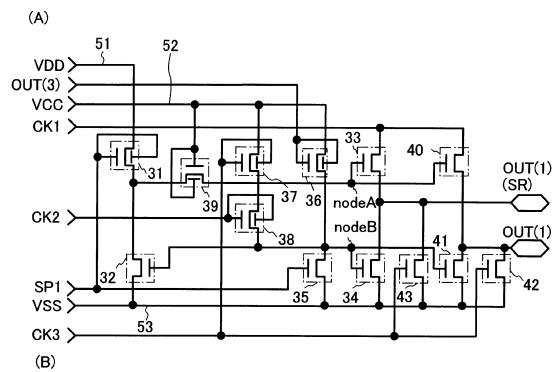

次に、図 16 (B) に示したパルス出力回路の具体的な回路構成の一例について、図 16 (D) で説明する。

【 0 2 3 8 】

図 16 (D) に示した第 1 のパルス出力回路 10\_1 は、第 1 のトランジスタ 31 ~ 第 13 のトランジスタ 43 を有している。また、上述した第 1 の入力端子 2 1 ~ 第 5 の入力端子 2 5、及び第 1 の出力端子 2 6、第 2 の出力端子 2 7 に加え、第 1 の高電源電位 V D D が供給される電源線 5 1、第 2 の高電源電位 V C C が供給される電源線 5 2、低電源電位 V S S が供給される電源線 5 3 から、第 1 のトランジスタ 31 ~ 第 13 のトランジスタ 43 に信号、または電源電位が供給される。ここで図 16 (D) における各電源線の電源電位の大小関係は、第 1 の電源電位 V D D は第 2 の電源電位 V C C 以上の電位とし、第 2 の電源電位 V C C は、第 3 の電源電位 V S S より大きい電位とする。なお、第 1 のクロック信号 (C K 1) ~ 第 4 のクロック信号 (C K 4) は、一定の間隔で H レベルと L レベルを繰り返す信号であるが、H レベルのとき V D D、L レベルのとき V S S であるとする。なお電源線 5 1 の電位 V D D を、電源線 5 2 の電位 V C C より高くすることにより、動作に影響を与えることなく、トランジスタのゲート電極に印加される電位を低く抑えることができ、トランジスタのしきい値のシフトを低減し、劣化を抑制することができる。なお図 16 (D) に図示するように、第 1 のトランジスタ 31 ~ 第 13 のトランジスタ 43 のうち、第 1 のトランジスタ 31、第 6 のトランジスタ 36 乃至第 9 のトランジスタ 39 には、図 16 (C) で示した 4 端子の薄膜トランジスタ 28 を用いることが好ましい。第 1 のトランジスタ 31、第 6 のトランジスタ 36 乃至第 9 のトランジスタ 39 の動作は、ソースまたはドレインとなる電極の一方が接続されたノードの電位を、ゲート電極の制御信号

10

20

30

40

50

によって切り替えることが求められるトランジスタであり、ゲート電極に入力される制御信号に対する応答が速い（オン電流の立ち上がりが急峻）ことでよりパルス出力回路の誤動作を低減することができるトランジスタである。そのため、図16（C）で示した4端子の薄膜トランジスタ28を用いることによりしきい値電圧を制御することができ、誤動作がより低減できるパルス出力回路とすることができる。なお図16（D）では第1の制御信号G1及び第2の制御信号G2が同じ制御信号としたが、異なる制御信号が入力される構成としてもよい。

### 【0239】

図16（D）において第1のトランジスタ31は、第1端子が電源線51に電気的に接続され、第2端子が第9のトランジスタ39の第1端子に電気的に接続され、ゲート電極（下方のゲート電極及び上方のゲート電極）が第4の入力端子24に電気的に接続されている。第2のトランジスタ32は、第1端子が電源線53に電気的に接続され、第2端子が第9のトランジスタ39の第1端子に電気的に接続され、ゲート電極が第4のトランジスタ34のゲート電極に電気的に接続されている。第3のトランジスタ33は、第1端子が第1の入力端子21に電気的に接続され、第2端子が第1の出力端子26に電気的に接続されている。第4のトランジスタ34は、第1端子が電源線53に電気的に接続され、第2端子が第1の出力端子26に電気的に接続されている。第5のトランジスタ35は、第1端子が電源線53に電気的に接続され、第2端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極が第4の入力端子24に電気的に接続されている。第6のトランジスタ36は、第1端子が電源線52に電気的に接続され、第2端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極（下方のゲート電極及び上方のゲート電極）が第5の入力端子25に電気的に接続されている。第7のトランジスタ37は、第1端子が電源線52に電気的に接続され、第2端子が第8のトランジスタ38の第2端子に電気的に接続され、ゲート電極（下方のゲート電極及び上方のゲート電極）が第3の入力端子23に電気的に接続されている。第8のトランジスタ38は、第1端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極（下方のゲート電極及び上方のゲート電極）が第2の入力端子22に電気的に接続されている。第9のトランジスタ39は、第1端子が第1のトランジスタ31の第2端子及び第2のトランジスタ32の第2端子に電気的に接続され、第2端子が第3のトランジスタ33のゲート電極及び第10のトランジスタ40のゲート電極に電気的に接続され、ゲート電極（下方のゲート電極及び上方のゲート電極）が電源線52に電気的に接続されている。第10のトランジスタ40は、第1端子が第1の入力端子21に電気的に接続され、第2端子が第2の出力端子27に電気的に接続され、ゲート電極が第9のトランジスタ39の第2端子に電気的に接続されている。第11のトランジスタ41は、第1端子が電源線53に電気的に接続され、第2端子が第2の出力端子27に電気的に接続され、ゲート電極が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続されている。第12のトランジスタ42は、第1端子が電源線53に電気的に接続され、第2端子が第2の出力端子27に電気的に接続され、ゲート電極が第7のトランジスタ37のゲート電極（下方のゲート電極及び上方のゲート電極）に電気的に接続されている。第13のトランジスタ43は、第1端子が電源線53に電気的に接続され、第2端子が第1の出力端子26に電気的に接続され、ゲート電極が第7のトランジスタ37のゲート電極（下方のゲート電極及び上方のゲート電極）に電気的に接続されている。

### 【0240】

図16（D）において、第3のトランジスタ33のゲート電極、第10のトランジスタ40のゲート電極、及び第9のトランジスタ39の第2端子の接続箇所をノードAとする。また、第2のトランジスタ32のゲート電極、第4のトランジスタ34のゲート電極、第5のトランジスタ35の第2端子、第6のトランジスタ36の第2端子、第8のトランジスタ38の第1端子、及び第11のトランジスタ41のゲート電極の接続箇所をノード

10

20

30

40

50

Bとする。

【0241】

図17(A)に、図16(D)で説明したパルス出力回路を第1のパルス出力回路10\_1に適用した場合に、第1の入力端子21乃至第5の入力端子25と第1の出力端子26及び第2の出力端子27に入力または出力される信号を示している。

【0242】

具体的には、第1の入力端子21に第1のクロック信号CK1が入力され、第2の入力端子22に第2のクロック信号CK2が入力され、第3の入力端子23に第3のクロック信号CK3が入力され、第4の入力端子24にスタートパルスが入力され、第5の入力端子25に後段信号OUT(3)が入力され、第1の出力端子26より第1の出力信号OUT(1)(SR)が出力され、第2の出力端子27より第2の出力信号OUT(1)が出力される。

10

【0243】

なお、薄膜トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。また、ゲートと重畠した領域にチャネル領域が形成される半導体を有しており、ゲートの電位を制御することでチャネル領域を介してドレインとソースの間に流れる電流を制御することが出来る。ここで、ソースとドレインとは、薄膜トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。

20

【0244】

なお図16(D)、図17(A)において、ノードAを浮遊状態とすることによりブートストラップ動作を行うための、容量素子を別途設けても良い。またノードBの電位を保持するため、一方の電極をノードBに電気的に接続した容量素子を別途設けてもよい。

【0245】

ここで、図17(A)に示したパルス出力回路を複数具備するシフトレジスタのタイミングチャートについて図17(B)に示す。なおシフトレジスタが走査線駆動回路である場合、図17(B)中の期間61は垂直帰線期間であり、期間62はゲート選択期間に相当する。

30

【0246】

なお、図17(A)に示すように、ゲートに第2の電源電位VCCが印加される第9のトランジスタ39を設けておくことにより、ブートストラップ動作の前後において、以下のような利点がある。

【0247】

ゲート電極に第2の電位VCCが印加される第9のトランジスタ39がない場合、ブートストラップ動作によりノードAの電位が上昇すると、第1のトランジスタ31の第2端子であるソースの電位が上昇していき、第1の電源電位VDDより大きくなる。そして、第1のトランジスタ31のソースが第1端子側、即ち電源線51側に切り替わる。そのため、第1のトランジスタ31においては、ゲートとソースの間、ゲートとドレインの間ともに、大きなバイアス電圧が印加されるために大きなストレスがかかり、トランジスタの劣化の要因となりうる。そこで、ゲート電極に第2の電源電位VCCが印加される第9のトランジスタ39を設けておくことにより、ブートストラップ動作によりノードAの電位は上昇するものの、第1のトランジスタ31の第2端子の電位の上昇を生じないようにすることができる。つまり、第9のトランジスタ39を設けることにより、第1のトランジスタ31のゲートとソースの間に印加される負のバイアス電圧の値を小さくすることができる。よって、本実施の形態の回路構成とすることにより、第1のトランジスタ31のゲートとソースの間に印加される負のバイアス電圧も小さくできるため、ストレスによる第1のトランジスタ31の劣化を抑制することができる。

40

【0248】

50

なお、第9のトランジスタ39を設ける箇所については、第1のトランジスタ31の第2端子と第3のトランジスタ33のゲートとの間に第1端子と第2端子を介して接続されるように設ける構成であればよい。なお、本実施形態でのパルス出力回路を複数具備するシフトレジスタの場合、走査線駆動回路より段数の多い信号線駆動回路では、第9のトランジスタ39を省略してもよく、トランジスタ数を削減することが利点である。

【0249】

なお第1のトランジスタ31乃至第13のトランジスタ43の半導体層として、酸化物半導体を用いることにより、薄膜トランジスタのオフ電流を低減すると共に、オン電流及び電界効果移動度を高めることが出来ると共に、劣化の度合いを低減することが出来るため、回路内の誤動作を低減することができる。また酸化物半導体を用いたトランジスタ、アモルファスシリコンを用いたトランジスタに比べ、ゲート電極に高電位が印加されることによるトランジスタの劣化の程度が小さい。そのため、第2の電源電位VCCを供給する電源線に、第1の電源電位VDDを供給しても同様の動作が得られ、且つ回路間を引き回す電源線の数を低減することができるため、回路の小型化を図ることが出来る。

10

【0250】

なお、第7のトランジスタ37のゲート電極（下方のゲート電極及び上方のゲート電極）に第3の入力端子23によって供給されるクロック信号、第8のトランジスタ38のゲート電極（下方のゲート電極及び上方のゲート電極）に第2の入力端子22によって供給されるクロック信号は、第7のトランジスタ37のゲート電極（下方のゲート電極及び上方のゲート電極）に第2の入力端子22によって供給されるクロック信号、第8のトランジスタ38ゲート電極（下方のゲート電極及び上方のゲート電極）に第3の入力端子23によって供給されるクロック信号となるように、結線関係を入れ替えると同様の作用を奏する。この時、図17（A）に示すシフトレジスタにおいて、第7のトランジスタ37及び第8のトランジスタ38が共にオンの状態から、第7のトランジスタ37がオフ、第8のトランジスタ38がオフの状態となることによって、第2の入力端子22及び第3の入力端子23の電位が低下することで生じる、ノードBの電位の低下が第7のトランジスタ37のゲート電極の電位の低下、及び第8のトランジスタ38のゲート電極の電位の低下に起因して2回生じることとなる。一方、第7のトランジスタ37及び第8のトランジスタ38が共にオンの状態から、第7のトランジスタ37がオン、第8のトランジスタ38がオフの状態、次いで、第7のトランジスタ37がオフ、第8のトランジスタ38がオフの状態とすることによって、第2の入力端子22及び第3の入力端子23の電位が低下することで生じるノードBの電位の低下を、第8のトランジスタ38のゲート電極の電位の低下による一回に低減することができる。そのため、第7のトランジスタ37のゲート電極（下方のゲート電極及び上方のゲート電極）に第3の入力端子23からクロック信号が供給され、第8のトランジスタ38のゲート電極（下方のゲート電極及び上方のゲート電極）に第2の入力端子22からクロック信号が供給される結線関係とすることが好適である。なぜなら、ノードBの電位の変動回数が低減され、またノイズを低減することができるからである。

20

【0251】

30

このように、第1の出力端子26及び第2の出力端子27の電位をLレベルに保持する期間に、ノードBに定期的にHレベルの信号が供給されることにより、パルス出力回路の誤動作を抑制することができる。

40

【0252】

（実施の形態9）

薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置（表示装置ともいう）を作製することができる。また、薄膜トランジスタを駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

【0253】

50

表示装置は表示素子を含む。表示素子としては液晶素子（液晶表示素子ともいう）、発光素子（発光表示素子ともいう）を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL（Electro Luminescence）素子、有機EL素子等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

#### 【0254】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに、該表示装置を作製する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッティングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

10

#### 【0255】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えばFPC（Flexible printed circuit）もしくはTAB（Tape Automated Bonding）テープもしくはTCP（Tape Carrier Package）が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG（Chip On Glass）方式によりIC（集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。

20

#### 【0256】

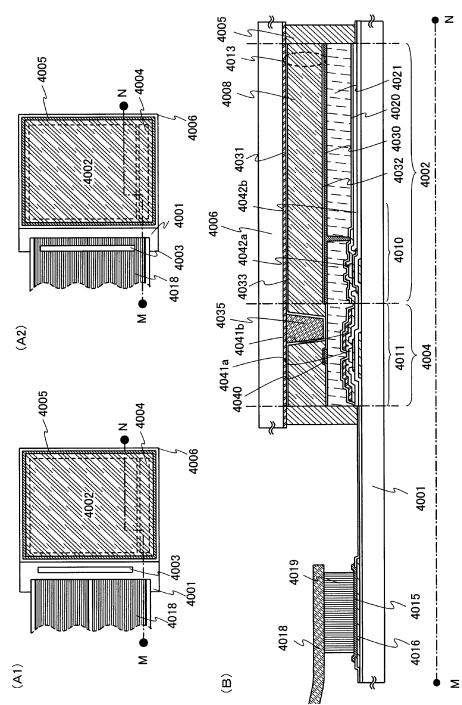

半導体装置の一形態に相当する液晶表示パネルの外観及び断面について、図10を用いて説明する。図10(A1)(A2)は、薄膜トランジスタ4010、4011、及び液晶素子4013を、第1の基板4001と第2の基板4006との間にシール材4005によって封止した、パネルの平面図であり、図10(B)は、図10(A1)(A2)のM-Nにおける断面図に相当する。

#### 【0257】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。また第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003が実装されている。

30

#### 【0258】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG方法、ワイヤボンディング方法、或いはTAB方法などを用いることができる。図10(A1)は、COG方法により信号線駆動回路4003を実装する例であり、図10(A2)は、TAB方法により信号線駆動回路4003を実装する例である。

40

#### 【0259】

また第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、薄膜トランジスタを複数有しており、図10(B)では、画素部4002に含まれる薄膜トランジスタ4010と、走査線駆動回路4004に含まれる薄膜トランジスタ4011とを例示している。薄膜トランジスタ4010、4011上には絶縁層4041a、4041b、4042a、4042b、4020、4021が設けられている。

#### 【0260】

薄膜トランジスタ4010、4011は、実施の形態1、2、5、6で示した酸化物半導体層を含む信頼性の高い薄膜トランジスタを適用することができる。駆動回路用の薄膜トランジスタ4011としては、実施の形態1、2、5、6で示した薄膜トランジスタ26

50

0、270、画素用の薄膜トランジスタ4010としては、薄膜トランジスタ420、448、220、280、290を用いることができる。本実施の形態において、薄膜トランジスタ4010、4011はnチャネル型薄膜トランジスタである。

【0261】

絶縁層4021上において、駆動回路用の薄膜トランジスタ4011の酸化物半導体層のチャネル形成領域と重なる位置に導電層4040が設けられている。導電層4040を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、BT試験前後における薄膜トランジスタ4011のしきい値電圧の変化量を低減することができる。また、導電層4040は、電位が薄膜トランジスタ4011のゲート電極層と同じでもよいし、異なるってても良く、第2のゲート電極層として機能させることもできる。また、導電層4040の電位がGND、0V、或いはフローティング状態であってもよい。

10

【0262】

また、液晶素子4013が有する画素電極層4030は、薄膜トランジスタ4010と電気的に接続されている。そして液晶素子4013の対向電極層4031は第2の基板4006上に形成されている。画素電極層4030と対向電極層4031と液晶層4008とが重なっている部分が、液晶素子4013に相当する。なお、画素電極層4030、対向電極層4031はそれぞれ配向膜として機能する絶縁層4032、4033が設けられ、絶縁層4032、4033を介して液晶層4008を挟持している。

【0263】

なお、第1の基板4001、第2の基板4006としては、透光性基板を用いることができる、ガラス、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエチルフィルムまたはアクリル樹脂フィルムを用いることができる。

20

【0264】

また4035は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、画素電極層4030と対向電極層4031との間の距離(セルギャップ)を制御するためには設けられている。なお球状のスペーサを用いていても良い。また、対向電極層4031は、薄膜トランジスタ4010と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極層4031と共通電位線とを電気的に接続することができる。なお、導電性粒子はシール材4005に含有させる。

30

【0265】

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために5重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層4008に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1ms以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

【0266】

40

なお透過型液晶表示装置の他に、半透過型液晶表示装置でも適用できる。

【0267】

また、液晶表示装置では、基板の外側(視認側)に偏光板を設け、内側に着色層(カラーフィルタ)、表示素子に用いる電極層という順に設ける例を示すが、偏光板は基板の内側に設けてもよい。また、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、表示部以外にブラックマトリクスとして機能する遮光膜を設けてもよい。

【0268】

薄膜トランジスタ4011は、チャネル保護層として機能する絶縁層4041aと、酸化物半導体層の積層の周縁部(側面を含む)を覆う絶縁層4041bとが形成されている。

50

同様に薄膜トランジスタ4010は、チャネル保護層として機能する絶縁層4042aと、酸化物半導体層の積層の周縁部（側面を含む）を覆う絶縁層4042bとが形成されている。

【0269】

酸化物半導体層の積層の周縁部（側面を含む）を覆う酸化物絶縁層である絶縁層4041b、4042bは、ゲート電極層と、その上方または周辺に形成される配線層（ソース配線層や容量配線層など）との距離を大きくし、寄生容量の低減を図ることができる。絶縁層4041a、4041b、4042a、4042bは実施の形態1で示した酸化物絶縁層426a、426bと同様な材料及び方法で形成すればよい。また、薄膜トランジスタの表面凹凸を低減するため平坦化絶縁膜として機能する絶縁層4021で覆う構成となっている。ここでは、絶縁層4041a、4041b、4042a、4042bとして、実施の形態1を用いてスパッタ法により酸化珪素膜を形成する。

10

【0270】

また、絶縁層4041a、4041b、4042a、4042b上に絶縁層4020が形成されている。絶縁層4020は実施の形態1で示した保護絶縁層403と同様な材料及び方法で形成すればよい。ここでは、絶縁層4020として、RFスパッタ法により窒化珪素膜を形成する。

【0271】

また、平坦化絶縁膜として絶縁層4021を形成する。絶縁層4021としては、実施の形態1で示した平坦化絶縁層404と同様な材料及び方法で形成すればよく、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（LOW-K材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、絶縁層4021を形成してもよい。

20

【0272】

本実施の形態では、画素部の複数の薄膜トランジスタをまとめて窒化物絶縁膜で囲む構成としてもよい。絶縁層4020とゲート絶縁層とに窒化物絶縁膜を用いて、図10に示すように少なくともアクティブマトリクス基板の画素部の周縁を囲むように絶縁層4020とゲート絶縁層とが接する領域を設ける構成とすればよい。このような構成により、外部からの水分の侵入を防ぐことができる。また、半導体装置、例えば表示装置としてデバイスが完成した後にも長期的に、外部からの水分の侵入を防ぐことができデバイスの長期信頼性を向上することができる。

30

【0273】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

【0274】

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。絶縁層4021の焼成工程と半導体層のアニールを兼ねることで効率よく半導体装置を作製することが可能となる。

40

【0275】

画素電極層4030、対向電極層4031は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

50

## 【0276】

また、画素電極層4030、対向電極層4031として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

## 【0277】

導電性高分子としては、いわゆる 電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

10

## 【0278】

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC4018から供給されている。

## 【0279】

接続端子電極4015が、液晶素子4013が有する画素電極層4030と同じ導電膜から形成され、端子電極4016は、薄膜トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

## 【0280】

接続端子電極4015は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

20

## 【0281】

また図10においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているがこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

## 【0282】

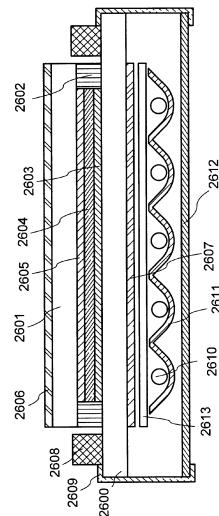

図19は、本明細書に開示する作製方法により作製されるTFT基板2600を用いて半導体装置として液晶表示モジュールを構成する一例を示している。

## 【0283】

図19は液晶表示モジュールの一例であり、TFT基板2600と対向基板2601がシール材2602により固着され、その間にTFT等を含む画素部2603、液晶層を含む表示素子2604、着色層2605が設けられ表示領域を形成している。着色層2605はカラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。TFT基板2600と対向基板2601の外側には偏光板2606、偏光板2607、拡散板2613が配設されている。光源は冷陰極管2610と反射板2611により構成され、回路基板2612は、フレキシブル配線基板2609によりTFT基板2600の配線回路部2608と接続され、コントローラ回路や電源回路などの外部回路が組みこまれている。また偏光板と、液晶層との間に位相差板を有した状態で積層してもよい。

30

## 【0284】

液晶表示モジュールには、TN(Twisted Nematic)モード、IPS( In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi-domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optical Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モードなどを用いることができる。

## 【0285】

50

以上の工程により、半導体装置として信頼性の高い液晶表示パネルを作製することができる。

【0286】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

【0287】

(実施の形態10)

半導体装置の一形態として電子ペーパーの例を示す。

【0288】

スイッチング素子と電気的に接続する素子を利用して電子インクを駆動させる電子ペーパーに用いてもよい。電子ペーパーは、電気泳動表示装置（電気泳動ディスプレイ）も呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。 10

【0289】

電気泳動ディスプレイは、様々な形態が考えられ得るが、プラスの電荷を有する第1の粒子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒または溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第1の粒子または第2の粒子は染料を含み、電界がない場合において移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの（無色を含む）とする。 20

【0290】

このように、電気泳動ディスプレイは、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動的効果を利用したディスプレイである。

【0291】

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

【0292】

また、アクティブマトリクス基板上に適宜、二つの電極の間に挟まれるように上記マイクロカプセルを複数配置すればアクティブマトリクス型の表示装置が完成し、マイクロカプセルに電界を印加すれば表示を行うことができる。例えば、実施の形態1、2、5、6の薄膜トランジスタによって得られるアクティブマトリクス基板を用いることができる。 30

【0293】

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を用いればよい。

【0294】

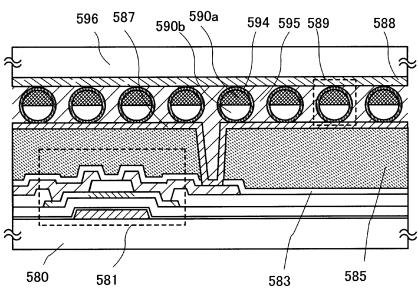

図18は、半導体装置の例としてアクティブマトリクス型の電子ペーパーを示す。半導体装置に用いられる薄膜トランジスタ581としては、実施の形態1で示す薄膜トランジスタと同様に作製でき、酸化物半導体層を含む信頼性の高い薄膜トランジスタである。また、実施の形態2、5、6で示す薄膜トランジスタも本実施の薄膜トランジスタ581として適用することもできる。 40

【0295】

図18の電子ペーパーは、ツイストボール表示方式を用いた表示装置の例である。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせての球形粒子の向きを制御することにより、表示を行う方法である。

【0296】

50

基板 580 上に形成された薄膜トランジスタ 581 はボトムゲート構造の薄膜トランジスタであり、半導体層と接する絶縁膜 583 に覆われている。薄膜トランジスタ 581 のソース電極層又はドレイン電極層によって第 1 の電極層 587 と、絶縁層 585 に形成する開口で接しており電気的に接続している。第 1 の電極層 587 と基板 596 上に形成された第 2 の電極層 588 との間には、黒色領域 590a 及び白色領域 590b を有し、周りに液体で満たされているキャビティ 594 を含む球形粒子 589 が設けられており、球形粒子 589 の周囲は樹脂等の充填材 595 で充填されている。第 1 の電極層 587 が画素電極に相当し、第 2 の電極層 588 が共通電極に相当する。第 2 の電極層 588 は、薄膜トランジスタ 581 と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して第 2 の電極層 588 と共通電位線とを電気的に接続することができる。10

#### 【 0297 】

また、ツイストボールの代わりに、電気泳動素子を用いることも可能である。透明な液体と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径  $10 \mu\text{m} \sim 200 \mu\text{m}$  程度のマイクロカプセルを用いる。第 1 の電極層と第 2 の電極層との間に設けられるマイクロカプセルは、第 1 の電極層と第 2 の電極層によって、電場が与えられると、白い微粒子と、黒い微粒子が逆の方向に移動し、白または黒を表示することができる。この原理を応用した表示素子が電気泳動表示素子であり、一般的に電子ペーパーとよばれている。電気泳動表示素子は、液晶表示素子に比べて反射率が高いため、補助ライトは不要であり、また消費電力が小さく、薄暗い場所でも表示部を認識することが可能である。また、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能であるため、電波発信源から表示機能付き半導体装置（単に表示装置、又は表示装置を具備する半導体装置ともいう）を遠ざけた場合であっても、表示された像を保存しておくことが可能となる。20

#### 【 0298 】

以上の工程により、半導体装置として信頼性の高い電子ペーパーを作製することができる。。

#### 【 0299 】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。30

#### 【 0300 】

##### （実施の形態 11）

半導体装置として発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機 EL 素子、後者は無機 EL 素子と呼ばれている。

#### 【 0301 】

有機 EL 素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。40

#### 【 0302 】

無機 EL 素子は、その素子構成により、分散型無機 EL 素子と薄膜型無機 EL 素子とに分類される。分散型無機 EL 素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー - アクセプター再結合型発光である。薄膜型無機 EL 素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機 EL 素子を用いて説明する。50

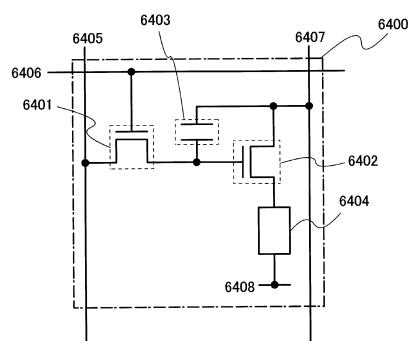

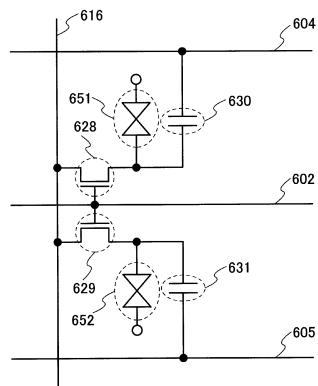

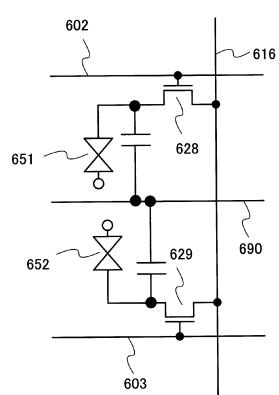

## 【0303】

図12は、半導体装置の例としてデジタル時間階調駆動を適用可能な画素構成の一例を示す図である。

## 【0304】

デジタル時間階調駆動を適用可能な画素の構成及び画素の動作について説明する。ここでは酸化物半導体層をチャネル形成領域に用いるnチャネル型のトランジスタを1つの画素に2つ用いる例を示す。

## 【0305】

画素6400は、スイッチング用トランジスタ6401、発光素子駆動用トランジスタ6402、発光素子6404及び容量素子6403を有している。スイッチング用トランジスタ6401はゲートが走査線6406に接続され、第1電極（ソース電極及びドレイン電極の一方）が信号線6405に接続され、第2電極（ソース電極及びドレイン電極の他方）が発光素子駆動用トランジスタ6402のゲートに接続されている。発光素子駆動用トランジスタ6402は、ゲートが容量素子6403を介して電源線6407に接続され、第1電極が電源線6407に接続され、第2電極が発光素子6404の第1電極（画素電極）に接続されている。発光素子6404の第2電極は共通電極6408に相当する。共通電極6408は、同一基板上に形成される共通電位線と電気的に接続される。

10

## 【0306】

なお、発光素子6404の第2電極（共通電極6408）には低電源電位が設定されている。なお、低電源電位とは、電源線6407に設定される高電源電位を基準にして低電源電位 < 高電源電位を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子6404に印加して、発光素子6404に電流を流して発光素子6404を発光させるため、高電源電位と低電源電位との電位差が発光素子6404の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

20

## 【0307】

なお、容量素子6403は発光素子駆動用トランジスタ6402のゲート容量を代用して省略することも可能である。発光素子駆動用トランジスタ6402のゲート容量については、チャネル領域とゲート電極との間で容量が形成されていてもよい。

## 【0308】

30

ここで、電圧入力電圧駆動方式の場合には、発光素子駆動用トランジスタ6402のゲートには、発光素子駆動用トランジスタ6402が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。つまり、発光素子駆動用トランジスタ6402は線形領域で動作させる。発光素子駆動用トランジスタ6402は線形領域で動作させるため、電源線6407の電圧よりも高い電圧を発光素子駆動用トランジスタ6402のゲートにかける。なお、信号線6405には、（電源線電圧 + 発光素子駆動用トランジスタ6402のVth）以上の電圧をかける。

## 【0309】

また、デジタル時間階調駆動に代えて、アナログ階調駆動を行う場合、信号の入力を異ならせてことで、図12と同じ画素構成を用いることができる。

40

## 【0310】

アナログ階調駆動を行う場合、発光素子駆動用トランジスタ6402のゲートに発光素子6404の順方向電圧 + 発光素子駆動用トランジスタ6402のVth以上の電圧をかける。発光素子6404の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。なお、発光素子駆動用トランジスタ6402が飽和領域で動作するようなビデオ信号を入力することで、発光素子6404に電流を流すことができる。発光素子駆動用トランジスタ6402を飽和領域で動作させるため、電源線6407の電位は、発光素子駆動用トランジスタ6402のゲート電位よりも高くする。ビデオ信号をアナログとすることで、発光素子6404にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

50

## 【0311】

なお、図12に示す画素構成は、これに限定されない。例えば、図12に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ又は論理回路などを追加してもよい。

## 【0312】

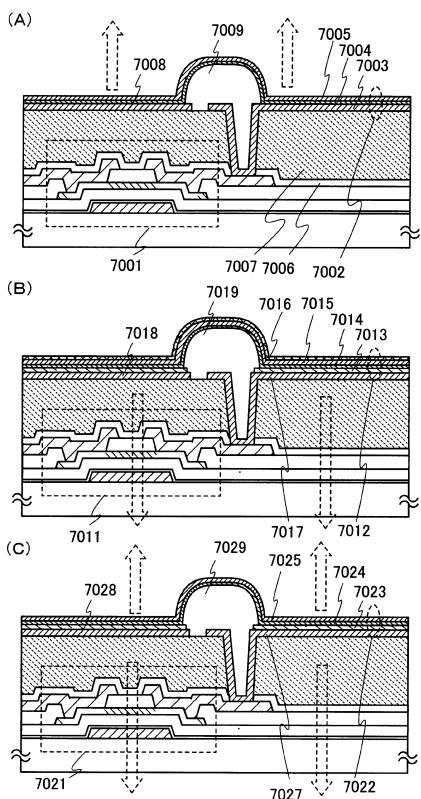

次に、発光素子の構成について、図13を用いて説明する。ここでは、発光素子駆動用TFTがn型の場合を例に挙げて、画素の断面構造について説明する。図13(A)(B)(C)の半導体装置に用いられる発光素子駆動用TFTであるTFT7001、7011、7021は、実施の形態1で示す画素に配置される薄膜トランジスタと同様に作製でき、酸化物半導体層を含む信頼性の高い薄膜トランジスタである。また、実施の形態2、5、6で示す画素に配置される薄膜トランジスタをTFT7001、7011、7021として適用することもできる。 10

## 【0313】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に薄膜トランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、画素構成はどの射出構造の発光素子にも適用することができる。

## 【0314】

上面射出構造の発光素子について図13(A)を用いて説明する。 20

## 【0315】

図13(A)に、発光素子駆動用TFTであるTFT7001がn型で、発光素子7002から発せられる光が陽極7005側に抜ける場合の、画素の断面図を示す。図13(A)では、発光素子7002の陰極7003と発光素子駆動用TFTであるTFT7001が電気的に接続されており、陰極7003上に発光層7004、陽極7005が順に積層されている。陰極7003は仕事関数が小さく、なおかつ光を反射する導電膜であれば様々な材料を用いることができる。例えば、Ca、Al、MgAg、AlLi等が望ましい。そして発光層7004は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、陰極7003上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。陽極7005は光を透過する透光性を有する導電性材料を用いて形成し、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性導電膜を用いても良い。 30

## 【0316】

また、陰極7003と隣り合う画素の陰極7008の間に、それぞれの端部を覆って隔壁7009を設ける。隔壁7009は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁7009は、特に感光性の樹脂材料を用い、隔壁7009の側面が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。隔壁7009として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。 40

## 【0317】

陰極7003及び陽極7005で発光層7004を挟んでいる領域が発光素子7002に相当する。図13(A)に示した画素の場合、発光素子7002から発せられる光は、矢印で示すように陽極7005側に射出する。

## 【0318】

次に、下面射出構造の発光素子について図13(B)を用いて説明する。発光素子駆動用TFT7011がn型で、発光素子7012から発せられる光が陰極7013側に射出する場合の、画素の断面図を示す。図13(B)では、発光素子駆動用TFT7011と電 50

気的に接続された透光性を有する導電膜 7017 上に、発光素子 7012 の陰極 7013 が成膜されており、陰極 7013 上に発光層 7014、陽極 7015 が順に積層されている。なお、陽極 7015 が透光性を有する場合、陽極上を覆うように、光を反射または遮蔽するための遮蔽膜 7016 が成膜されていてもよい。陰極 7013 は、図 13 (A) の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度（好ましくは、5 nm ~ 30 nm 程度）とする。例えば 20 nm の膜厚を有するアルミニウム膜を、陰極 7013 として用いることができる。そして発光層 7014 は、図 13 (A) と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極 7015 は光を透過する必要はないが、図 13 (A) と同様に、透光性を有する導電性材料を用いて形成することができる。そして遮蔽膜 7016 は、例えば光を反射する金属等を用いることができるが、金属膜に限定されない。例えば黒の顔料を添加した樹脂等を用いることもできる。

### 【0319】

また、導電膜 7017 と隣り合う画素の導電膜 7018 の間に、それぞれの端部を覆って隔壁 7019 を設ける。隔壁 7019 は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁 7019 は、特に感光性の樹脂材料を用い、隔壁 7019 の側面が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。隔壁 7019 として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

### 【0320】

陰極 7013 及び陽極 7015 で、発光層 7014 を挟んでいる領域が発光素子 7012 に相当する。図 13 (B) に示した画素の場合、発光素子 7012 から発せられる光は、矢印で示すように陰極 7013 側に射出する。

### 【0321】

次に、両面射出構造の発光素子について、図 13 (C) を用いて説明する。図 13 (C) では、発光素子駆動用 TFT 7021 と電気的に接続された透光性を有する導電膜 7027 上に、発光素子 7022 の陰極 7023 が成膜されており、陰極 7023 上に発光層 7024、陽極 7025 が順に積層されている。陰極 7023 は、図 13 (A) の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば 20 nm の膜厚を有する Al を、陰極 7023 として用いることができる。そして発光層 7024 は、図 13 (A) と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極 7025 は、図 13 (A) と同様に、光を透過する透光性を有する導電性材料を用いて形成することができる。

### 【0322】

また、導電膜 7027 と隣り合う画素の導電膜 7028 の間に、それぞれの端部を覆って隔壁 7029 を設ける。隔壁 7029 は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁 7029 は、特に感光性の樹脂材料を用い、隔壁 7029 の側面が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。隔壁 7029 として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

### 【0323】

陰極 7023 と、発光層 7024 と、陽極 7025 とが重なっている部分が発光素子 7022 に相当する。図 13 (C) に示した画素の場合、発光素子 7022 から発せられる光は、矢印で示すように陽極 7025 側と陰極 7023 側の両方に射出する。

### 【0324】

なお、ここでは、発光素子として有機 EL 素子について述べたが、発光素子として無機 EL 素子を設けることも可能である。

### 【0325】

なお、発光素子の駆動を制御する薄膜トランジスタ（発光素子駆動用 TFT）と発光素子

10

20

30

40

50

が電気的に接続されている例を示したが、発光素子駆動用 TFT と発光素子との間に電流制御用 TFT が接続されている構成であってもよい。

【0326】

なお半導体装置は、図 13 に示した構成に限定されるものではなく、本明細書に開示する技術的思想に基づく各種の変形が可能である。

【0327】

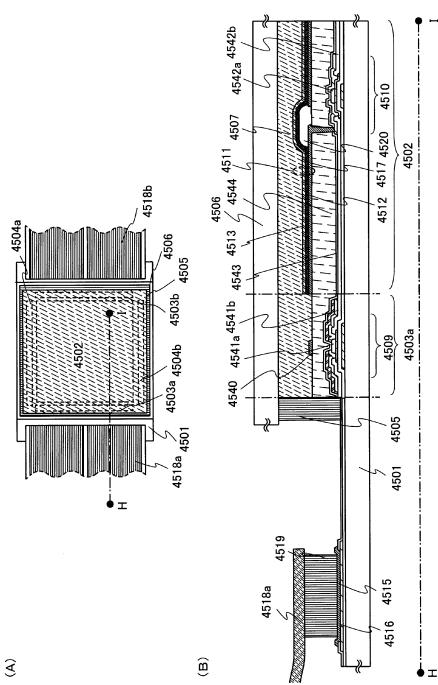

次に、半導体装置の一形態に相当する発光表示パネル（発光パネルともいう）の外観及び断面について、図 11 を用いて説明する。図 11 (A) は、第 1 の基板上に形成された薄膜トランジスタ及び発光素子を、第 2 の基板との間にシール材によって封止した、パネルの平面図であり、図 11 (B) は、図 11 (A) の H - I における断面図に相当する。

10

【0328】

第 1 の基板 4501 上に設けられた画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b を囲むようにして、シール材 4505 が設けられている。また画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b の上に第 2 の基板 4506 が設けられている。よって画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b は、第 1 の基板 4501 とシール材 4505 と第 2 の基板 4506 とによって、充填材 4507 と共に密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好ましい。

20

【0329】

また第 1 の基板 4501 上に設けられた画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b は、薄膜トランジスタを複数有しており、図 11 (B) では、画素部 4502 に含まれる薄膜トランジスタ 4510 と、信号線駆動回路 4503a に含まれる薄膜トランジスタ 4509 とを例示している。

【0330】

薄膜トランジスタ 4509、4510 は、実施の形態 1、2、5、6 で示した酸化物半導体層を含む信頼性の高い薄膜トランジスタを適用することができる。駆動回路に配置される薄膜トランジスタ 4509 としては、実施の形態 1、2、5、6 で示した薄膜トランジスタ 260、270、画素に配置される薄膜トランジスタ 4510 としては、薄膜トランジスタ 420、448、220、280、290 を用いることができる。本実施の形態において、薄膜トランジスタ 4509、4510 は n チャネル型薄膜トランジスタである。

30

【0331】

絶縁層 4544 上において駆動回路用の薄膜トランジスタ 4509 の酸化物半導体層のチャネル形成領域と重なる位置に導電層 4540 が設けられている。導電層 4540 を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、BT 試験前後における薄膜トランジスタ 4509 のしきい値電圧の変化量を低減することができる。また、導電層 4540 は、電位が薄膜トランジスタ 4509 のゲート電極層と同じでもよいし、異なっていても良く、第 2 のゲート電極層として機能させることもできる。また、導電層 4540 の電位が GND、0V、或いはフローティング状態であってもよい。

40

【0332】

薄膜トランジスタ 4509 上には、チャネル保護層として機能する絶縁層 4541a と、酸化物半導体層の周縁部（側面を含む）を覆う絶縁層 4541b とが形成されている。同様に薄膜トランジスタ 4510 は、チャネル保護層として機能する絶縁層 4542a と、酸化物半導体層の周縁部（側面を含む）を覆う絶縁層 4542b とが形成されている。

【0333】

酸化物半導体層の周縁部（側面を含む）を覆う酸化物絶縁層である絶縁層 4541b、4542b は、ゲート電極層と、その上方または周辺に形成される配線層（ソース配線層や容量配線層など）との距離を大きくし、寄生容量の低減を図ることができる。絶縁層 4541a、4541b、4542a、4542b は実施の形態 1 で示した酸化物絶縁層 42

50

6 a、426 b と同様な材料及び方法で形成すればよい。また、薄膜トランジスタの表面凹凸を低減するため平坦化絶縁膜として機能する絶縁層4543で覆う構成となっている。ここでは、絶縁層4541a、4541b、4542a、4542bとして、実施の形態1を用いてスパッタ法により酸化珪素膜を形成する。

【0334】

また、絶縁層4541a、4541b、4542a、4542b上に絶縁層4543が形成されている。絶縁層4543は実施の形態1で示した保護絶縁層403と同様な材料及び方法で形成すればよい。ここでは、絶縁層4543として、RFスパッタ法により窒化珪素膜を形成する。

【0335】

また、平坦化絶縁膜として絶縁層4544を形成する。絶縁層4544としては、実施の形態1で示した平坦化絶縁層404と同様な材料及び方法で形成すればよい。ここでは、絶縁層4544としてアクリルを用いる。

【0336】

本実施の形態では、画素部の複数の薄膜トランジスタをまとめて窒化物絶縁膜で囲む構成としてもよい。絶縁層4543とゲート絶縁層とに窒化物絶縁膜を用いて、図11に示すように少なくともアクティブマトリクス基板の画素部の周縁を囲むように絶縁層4543とゲート絶縁層とが接する領域を設ける構成とすればよい。この製造プロセスでは、外部からの水分の侵入を防ぐことができる。また、半導体装置、例えば表示装置としてデバイスが完成した後にも長期的に、外部からの水分の侵入を防ぐことができデバイスの長期信頼性を向上することができる。

【0337】

また4511は発光素子に相当し、発光素子4511が有する画素電極である第1の電極層4517は、薄膜トランジスタ4510のソース電極層またはドレイン電極層と電気的に接続されている。なお発光素子4511の構成は、第1の電極層4517、電界発光層4512、第2の電極層4513の積層構造であるが、示した構成に限定されない。発光素子4511から取り出す光の方向などに合わせて、発光素子4511の構成は適宜変えることができる。

【0338】

隔壁4520は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、第1の電極層4517上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0339】

電界発光層4512は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0340】

発光素子4511に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4513及び隔壁4520上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC膜等を形成することができる。

【0341】

また、信号線駆動回路4503a、4503b、走査線駆動回路4504a、4504b、または画素部4502に与えられる各種信号及び電位は、FPC4518a、4518bから供給されている。

【0342】

接続端子電極4515が、発光素子4511が有する第1の電極層4517と同じ導電膜から形成され、端子電極4516は、薄膜トランジスタ4509、4510が有するソース電極層及びドレイン電極層と同じ導電膜から形成されている。

【0343】

接続端子電極4515は、FPC4518aが有する端子と、異方性導電膜4519を介して電気的に接続されている。

10

20

30

40

50

## 【0344】

発光素子4511からの光の取り出し方向に位置する第2の基板は透光性でなければならない。その場合には、ガラス板、プラスチック板、ポリエスチルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

## 【0345】

また、充填材4507としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。例えば充填材として窒素を用いればよい。

10

## 【0346】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

## 【0347】

信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bは、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜によって形成された駆動回路で実装されていてよい。また、信号線駆動回路のみ、或いは一部、又は走査線駆動回路のみ、或いは一部のみを別途形成して実装しても良く、図11の構成に限定されない。

20

## 【0348】

以上の工程により、半導体装置として信頼性の高い発光表示装置(表示パネル)を作製することができる。

## 【0349】

本実施の形態は、実施の形態1乃至4、及び6乃至8に記載した構成と適宜組み合わせて実施することが可能である。

## 【0350】

## (実施の形態12)

本明細書に開示する半導体装置は、電子ペーパーとして適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図20に示す。

30

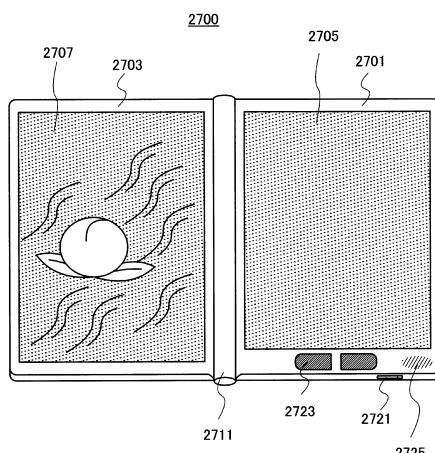

## 【0351】

図20は、電子書籍2700の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

40

## 【0352】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、継ぎ画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部(図20では表示部2705)に文章を表示し、左側の表示部(図20では表示部2707)に画像を表示することができる。

## 【0353】

また、図20では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側

50

面に、外部接続用端子（イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

【0354】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0355】