(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년01월16일

(11) 등록번호 10-1222401

(24) 등록일자 2013년01월08일

- (51) 국제특허분류(Int. Cl.)

*B06B 1/06* (2006.01) *G06T 7/00* (2006.01)

(21) 출원번호 10-2007-7012161

(22) 출원일자(국제) 2005년08월25일

심사청구일자 2010년08월25일

(85) 번역문제출일자 2007년05월29일

(65) 공개번호 10-2007-0106687

(43) 공개일자 2007년11월05일

(86) 국제출원번호 PCT/US2005/030237

(87) 국제공개번호 WO 2007/086817

국제공개일자 2007년08월02일

(30) 우선권주장

10/978,175 2004년10월29일 미국(US)

## (56) 선행기술조사문헌

JP평성09185649 A

JP평성05160263 A

전체 청구항 수 : 총 22 항

심사관 : 황동율

## (54) 발명의 명칭 스위칭 구성 구현 방법 및 초음파 이미징 시스템 동작 방법

**(57) 요약**

본 명세서에 개시되는 재구성 가능한 초음파 어레이에는 서브 소자 그룹이 동적으로 함께 접속되어 최종 소자의 형상이 과정 전면의 형상과 일치하도록 구성될 수 있다. 이것은 개선된 성능 및/또는 감소된 채널 카운트를 유도 할 수 있다. 재구성 가능성은 스위칭 네트워크를 사용하여 성취될 수 있다. 스위칭 네트워크의 구성을 적합하게 선택하여 이 스위칭 네트워크의 성능이 개선되게 하는 방법 및 알고리즘이 개시된다.

**대 표 도**

(72) 발명자

피셔 레이예트 앤

미국 뉴욕주 12309 니스카유나 버클리 애비뉴 2305

토메니우스 카이 이

미국 뉴욕주 12065 클립톤 파크 반 브란肯 로드 74

스미스 로웰 스코트

미국 뉴욕주 12309 니스카유나 채쉐어 플레이스 24

밀스 레이비드 마틴

미국 뉴욕주 12309 니스카유나 헤리티지 로드 1915

**특허청구의 범위**

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

**청구항 16**

재구성 가능한 센서 소자 어레이의 제어 중에 스위치 네트워크에 의해 개입되는 에러를 최소화하는 스위칭 구성 구현 방법에 있어서,

- (a) 초기 스위칭 구성을 생성하는 단계와,

- (b) 반복적 알고리즘을 수행하는 단계로서, 상기 반복적 알고리즘은,

- (i) 스위치 구성을 시스템 내로 입력하는 단계 - 상기 초기 스위칭 구성은 시작시에 입력되고 연속적으로 유도되는 수정된 스위칭 구성은 이후 연속적으로 입력됨 - 와,

- (ii) 상기 입력된 스위치 구성으로 상기 시스템의 성능을 판정하는 단계와,

- (iii) 상기 시스템의 판정된 성능을 표현하는 데이터에 적어도 부분적으로 근거해서 비용 함수에 대한 값을 계산하는 단계와,

- (iv) 상기 계산된 값이 상기 비용 함수에 대한 최소 값을 실질적으로 표현하는지를 판정하는 단계와,

- (v) 상기 계산된 값이 상기 비용 함수에 대한 최소값이 아닌 경우, 현재 스위칭 구성은 상기 값 계산 결과의 함수로서 수정하여 수정된 스위칭 구성에 도달하게 하는 단계를 포함하되, 상기 단계 (i) 내지 (v)는 각 스위칭 구성에 대해 반복되는 단계와,

- (c) 상기 계산된 값이 상기 비용 함수에 대한 최소값인 경우, 상기 비용 함수 값이 최소화되도록 하는 상기 수정된 스위칭 구성으로 상기 스위칭 네트워크를 구성하는 단계를 포함하는

스위칭 구성 구현 방법.

**청구항 17**

제 16 항에 있어서,

상기 구성 단계는 상기 스위치의 상태를 제어하는 제어 회로를 프로그래밍하는 단계를 포함하는

스위칭 구성 구현 방법.

**청구항 18**

제 16 항에 있어서,

상기 계산된 값이 상기 비용 함수에 대한 최소값을 실질적으로 표현하는지를 판정하는 상기 단계는, 시뮬레이팅된 어닐링 타입 알고리즘(simulated annealing type of algorithm)을 사용하여 수행되는

스위칭 구성 구현 방법.

**청구항 19**

제 16 항에 있어서,

사용되는 상기 비용 함수는 사전 결정되는 임계값보다 큰 스위치 거리를 갖는 센서 소자의 수인

스위칭 구성 구현 방법.

**청구항 20**

제 16 항에 있어서,

상기 단계(b)(ii)는 상기 시스템의 복사 패턴을 계산하는 단계를 포함하는

스위칭 구성 구현 방법.

### 청구항 21

제 16 항에 있어서,

상기 단계(b)(i)는 상기 시스템에 의해 생성되는 이미지를 평가하는 단계를 포함하는 스위칭 구성 구현 방법.

### 청구항 22

제 16 항에 있어서,

상기 단계(b)(i)는 상기 시스템의 전기 측정을 이루는 단계를 포함하는 스위칭 구성 구현 방법.

### 청구항 23

제 16 항에 있어서,

각 센서 소자는 각 초음파 변환기 소자이고, 상기 단계(b)(ii)는 상기 스위치의 저항에 관한 측정 및 상기 초음파 변환기 소자의 캐패시턴스를 측정하는 단계를 포함하는 스위칭 구성 구현 방법.

### 청구항 24

제 16 항에 있어서,

사용되는 상기 비용 함수는 애플리케이션에 따라 변하는 스위칭 구성 구현 방법.

### 청구항 25

제 24 항에 있어서,

제 1 비용 함수는 상기 센서 소자 어레이가 송신 모드에서 동작할 때 사용되는 제 1 스위칭 구성을 최적화하는 데 사용되고,

제 2 비용 함수는 상기 센서 소자 어레이가 수신 모드에서 동작할 때 사용되는 제 2 스위칭 구성을 최적화하는 데 사용되는

스위칭 구성 구현 방법.

### 청구항 26

제 24 항에 있어서,

제 1 비용 함수는 상기 센서 소자 어레이가 제 1 시스템 파라미터 세트에 따라 동작될 때 사용되는 제 1 스위칭 구성을 최적화하는 데 사용되고,

제 2 비용 함수는 상기 센서 소자 어레이가 제 2 시스템 파라미터 세트에 따라 동작할 때 제 2 스위칭 구성 사용을 최적화하는 데 사용되는

스위칭 구성 구현 방법.

### 청구항 27

제 16 항에 있어서,

상기 방법은 상기 센서 소자 어레이의 구성이 변할 때마다 수행되는 스위칭 구성 구현 방법.

### 청구항 28

제 16 항에 있어서,

상기 방법은 상기 센서 소자 어레이의 동작 환경의 사전 결정된 온도 변경이 검출될 때마다 수행되는 스위칭 구성 구현 방법.

### 청구항 29

제 16 항에 있어서,

상기 센서 소자 어레이는 이미징 시스템에 결합되고, 상기 방법은 상기 이미징 시스템이 턴 온(turn on)될 때마다 수행되는

스위칭 구성 구현 방법.

### 청구항 30

제 16 항에 있어서,

상기 센서 소자 어레이는 이미징 시스템에 결합될 수 있는 프로브에 포함되고, 상기 비용 함수가 최소화되게 하는 상기 수정된 스위칭 구성을 표현하는 데이터는 상기 프로브의 메모리에 저장되는

스위칭 구성 구현 방법.

### 청구항 31

제 16 항에 있어서,

상기 센서 소자 어레이는 이미징 시스템에 결합될 수 있는 프로브에 포함되고, 상기 비용 함수 값이 최소화되게 하는 상기 수정된 스위칭 구성을 표현하는 데이터는 상기 이미징 시스템의 메모리에 저장되어 추후에 상기 프로브의 로컬 메모리에 다운로드되는

스위칭 구성 구현 방법.

### 청구항 32

제 16 항에 있어서,

상기 센서 소자 어레이는 이미징 시스템에 결합될 수 있는 프로브에 포함되고, 상기 비용 함수 값이 최소화되게 하는 상기 수정된 스위칭 구성을 표현하는 데이터는 스캐닝 중에 상기 프로브의 로컬 메모리로부터 판독되는

스위칭 구성 구현 방법.

### 청구항 33

제 16 항에 있어서,

각 센서 소자는 개개의 초음파 변환기 소자이고, 상기 방법은 수신 모드 중에 다수의 초점 존(focal zone)에서

의 재구성을 위해 다수의 개구 구성 각각에 대해 수행되는

스위칭 구성 구현 방법.

#### 청구항 34

네트워크 스위치의 개개의 상태를 제어하여 재구성 가능한 초음파 변환기 소자 어레이를 구비한 초음파 이미징 시스템의 동작 방법에 있어서,

- (a) 상기 초음파 이미징 시스템의 제 1 동작 상태에서 사용하기 위한 제 1 스위칭 구성을 최적화하는 단계와,

- (b) 상기 초음파 이미징 시스템의 제 2 동작 상태에서 사용하기 위한 제 2 스위칭 구성을 최적화하는 단계를 포함하되,

상기 최적화 단계는 반복적 알고리즘을 사용하여 비용 함수를 최소화하는 단계를 포함하는

초음파 이미징 시스템 동작 방법.

#### 청구항 35

제 34 항에 있어서,

상기 초음파 변환기 소자 어레이는 상기 제 1 개구 상태의 제 1 개구 구성 및 상기 제 1 개구 구성과 상이한 상기 제 2 동작 상태의 제 2 개구 구성을 갖는

초음파 이미징 시스템 동작 방법.

#### 청구항 36

제 34 항에 있어서,

상기 초음파 변환기 소자 어레이는 상기 제 1 동작 상태에서는 송신 모드로 동작하고 상기 제 2 동작 상태에서는 수신 모드로 동작하는

초음파 이미징 시스템 동작 방법.

#### 청구항 37

제 34 항에 있어서,

사용되는 상기 비용 함수는 사전 결정되는 임계값보다 큰 스위치 거리를 갖는 센서 소자의 수인

초음파 이미징 시스템 동작 방법.

#### 청구항 38

삭제

#### 청구항 39

삭제

#### 청구항 40

삭제

#### 청구항 41

작제

## 명세서

[0001] [연방 정부 보증 연구 개발에 관한 주장]

[0002] 미국 정부는 미 육군에 의해 수여되는 미국 정부 계약 번호 DAMD17-02-1-0181에 따라 이 발명에 대한 소정 권리 를 가질 수 있다.

[0003] [관련 특허 출원]

[0004] 본 출원은 2003년 3월 6일에 출원된 "Mosaic Arrays Using Micromachined Ultrasound Transducer"란 명칭의 미국 특허 출원 제 10/383,990의 일부 계속 출원이며 이로부터 우선권을 주장한다.

## 기술 분야

[0005] 본 발명은 전반적으로 재구성 가능한 센서 어레이(예를 들어, 광, 열, 압력, 초음파)에 관한 것이다. 특히, 본 발명은 재구성 가능한 마이크로머신 초음파 변환기(MUT) 어레이에 관한 것이다. MUT용의 한 특정 애플리케이션은 의료 진단 초음파 이미징 시스템이다. 다른 특정 예는 캐스팅(castings), 포징(forging) 또는 파이프 라인과 같은 비-파괴적인 물질 평가를 위한 것이다.

## 배경 기술

[0006] 종래 초음파 이미징 시스템은 초음파 빔을 송신하고 관측할 피검체로부터 반사되는 빔을 수신하는 데 사용되는 초음파 변환기 어레이를 포함한다. 이러한 스캐닝은 초점을 맞춘 초음파가 전송되는 일련의 측정을 포함하고, 이 시스템은 짧은 시간 간격 후에 수신 모드로 전환하며, 반사된 초음파가 수신되고 빔 형성되어 디스플레이를 위해 처리된다. 통상적으로, 각 측정 동안 동일 방향으로 송신 및 수신이 초점이 맞추어 져서 음향 빔 또는 스캔 라인을 따라 일련의 포인트로부터 데이터를 수집한다. 수신기는 반사된 초음파가 수신됨에 따라 스캔 라인을 따라 연속적으로 다시 초점이 맞추어 진다.

[0007] 초음파 이미징에 있어서, 통상적으로 어레이는 하나 이상의 행으로 배열되어 송신 시에 개별 전압으로 구동되는 복수의 변환기를 갖는다. 시간 지연(또는 위상) 및 인가 전압의 크기를 선택하여, 개별 변환기는 원하는 벡터 방향을 따라 이동하고 빔을 따라 선택된 영역에서 초점이 맞추어지는 순수 초음파(a net ultrasonic wave)를 형성하기 위해 결합되는 초음파를 발생시키도록 제어될 수 있다.

[0008] 수신 모드에서 반사된 음향을 수신하기 위해 변환기 프로브가 사용될 때 동일한 원리를 적용한다. 수신 변환기에서 발생되는 전압은 합산되어, 순수 신호는 피검체의 단일 초점 영역으로부터 반사되는 초음파를 표시한다. 송신 모드에서, 이 초음파 에너지의 초점 수신은 각 수신 변환기로부터의 신호에 개별 시간 지연(및/또는 위상 시프트) 및 이득을 부과함으로써 달성된다. 시간 지연은 복귀되는 신호의 증가하는 깊이로 조절되어 수신에 대해 동적으로 초점을 맞춘다.

[0009] 형성되는 이미지의 화질 또는 해상도는 부분적으로, 변환기 어레이의 송신 및 수신 개구를 각각 구성하는 변환기의 수의 함수이다. 따라서, 고화질을 달성하기 위해, 2차원 및 3차원 이미징 애플리케이션 모두에 대해 많은 수의 변환기가 바람직하다. 통상적으로 초음파 변환기는, 변환기 신호를 처리하고 초음파 이미지를 생성하는 전자 유닛에 유연한 케이블에 의해 접속되는 소형 변환기 프로브에 위치된다. 변환기 프로브는 초음파 송신 회로 및 초음파 수신 회로 모두를 지닐 수 있다.

[0010] 재구성 가능한 초음파 어레이는 서브 소자 그룹을 동적으로 함께 접속되게 하여 최종 요소의 형상이 파형 전면의 형상화 일치하게 할 수 있는 것이다. 이는 성능 향상 및/또는 채널 수 감소를 유도할 수 있다. 재구성 가능성을 스위칭 네트워크를 사용하여 달성될 수 있다.

[0011] 빔 형성을 위해 요구되는 스위칭 네트워크의 성능을 개선하기 위한 알고리즘으로 가는 작업은 거의 없다. 하지만, 스위칭 또는 멀티플렉싱은 매우 많은 제한된 재구성 가능성을 위한 여러 경우에서 사용되어 왔다. 이것의

예로는 개구 사이즈를 증가시키기 위한 합성 개구를 사용하여 멀티플렉싱하고, 다수의 행 어레이와, 선형 어레이의 스캐닝을 위해 사용되는 멀티플렉싱을 포함한다. 모든 이러한 경우에, 재구성 가능성은 극단적으로 제한되고 스위칭 네트워크를 최적화할 필요성이 방지된다.

[0012] 최근 반도체 공정이 사용되어 마이크로기계 초음파 변환기(MUT)로 알려진 유형의 초음파 변환기를 제조하여 왔으며, 용량성(MUT) 또는 압전기(pMUT) 변형으로 구성될 수 있다. MUT는 적극을 갖는 작은 칸막이(diaphragm) 형상 장치이며 수신된 초음파 신호의 음파 진동을 변조된 캐페시턴스로 변환한다. 전송을 위해, 용량성 전하가 변조되어 디바이스의 칸막이를 진동시켜서 음파를 전달한다. MUT의 한 가지 장점은 표제 "마이크로머시닝(micromachining)" 하에서 그룹화되는 마이크로제조 공정과 같은 반도체 제조 공정을 사용하여 구성될 수 있다 는 점이다. 이러한 마이크로머시닝 공정으로부터 유도되는 시스템은 통상적으로 "마이크로머신 전기-기계 시스템(MEMS)"로 지칭된다.

[0013] cMUT는 통상적으로 이들 사이에 펼쳐지는 막(membrane)을 갖는 육각형 구조이다. 이 막은 인가 바이어스 전압에 의해 기판 표면에 근접하게 유지된다. 이미 바이어싱된 cMUT에 진동 신호를 인가하여, 막은 진동하도록 구성될 수 있어서, 음향 에너지를 방출하게 한다. 유사하게, 음파가 막에 입사하면, 최종 진동은 cMUT상의 전압 변동으로서 검출될 수 있다. cMUT 셀은 이들 육각형 "드럼" 구조 중 하나를 묘사하기 위해 사용되는 용어이다. cMUT 셀은 매우 작은 구조일 수 있다. 통상적 셀 치수는 육각형의 평평한 에지로부터 평평한 에지로 25-50마이크로이다. 셀의 치수는 설계되는 음향 응답에 의해 지시되는 많은 방식으로 존재한다. 주파수 응답 및 원하는 감도의 관점에서 여전히 잘 동작하면서 더 큰 셀을 구성하는 것이 불가능할 수 있다.

[0014] 불행히도, 이러한 소형 셀을 개별적으로 제어할 수 있는 전자소자를 제조하는 것은 난해하다. 전체로서 어레이의 음향 성능의 관점에서, 소형 셀 크기는 우수하며 현저한 유연성을 유도하지만, 제어는 더 큰 구조에 한정된다. 복수의 셀을 함께 그룹화하고 서로 전기적으로 접속하는 것은 더 큰 서브 소자를 구성할 수 있게 하고, 개별적으로 제어하면서 원하는 음향 응답을 유지할 수 있다. 그래서, 서브 소자는 재구성될 수 없는 전기적으로 접속되는 셀 그룹이다. 본 명세서에서의 설명 목적을 위해, 서브 소자는 최소의 독립적으로 제어되는 음향 단위이다. 스위칭 네트워크를 사용하여 서브 소자를 함께 접속함으로써 링 또는 소자를 형성할 수 있다. 소자는 스위칭 네트워크의 상태를 변경하여 재구성될 수 있다. 그러나, 서브 소자는 접속 해제로 스위칭 가능하지 않은 접속되는 셀을 포함하기 때문에 재구성될 수 없다. 또한, 어레이가 PZT 또는 어떤 다른 더 공통적 또는 장래 변환기 기술로 구성되는 경우에 이하의 모든 분석이 유효하다.

[0015] 실리콘-기반 초음파 변환기 서브 소자를 사용하는 재구성 가능성은 미국 특허 NO. 10/383,990에 개시되어 있다. 재구성 가능성의 한 형태는 모자이크 환상(annular) 어레이이며, 상술한 특허 출원에 또한 개시되어 있다. 모자이크 환상 어레이 개념은 재구성 가능한 전자 스위칭 네트워크를 사용하여 서브 소자를 함께 그룹화하여 환상 소자를 구성하는 단계를 포함한다. 목표는 빔 형성 채널의 수를 감소시키며 화질을 유지하고 슬라이스 두께를 개선하는 것이다. 시스템 채널을 감소시키기 위해, 모자이크 환상 어레이는 모자이크 환상 어레이는 조정되지 않는(unsteered) 빔에 있어서 하위 2차원 변환기 어레이 표면상의 지연 등고선(delay contours)이 원형이라는 사실을 이용한다. 다시 말해, 등지연 곡선(iso-delay curves)은 빔 중심에 대해 고리 모양(annuli)이다. 지연의 원형 대칭은 공통 지연을 갖는 서브 소자의 분명한 그룹화를 유도하고 원형 어레이 개념을 유도한다. 재구성 가능성은 스캔 또는 이미지를 형성하기 위해 더 큰 하위 2차원 변환기를 따라 빔을 스텝(step)하는 데 사용될 수 있다. 또한, 재구성 가능성은 더 많은 채널을 인접 필드의 더 작은 액티브 개구에 할당하여 다수 전송 애플리케이션을 위해 성능을 개선하는 데 사용될 수 있다. 재구성 가능성이 유용한 것으로 증명된 많은 다른 애플리케이션이 존재한다.

[0016] 재구성 가능한 초음파 어레이는 현재 이용 가능한 전자 소자를 사용하여 구현하기 난해하거나 불가능할 수 있는 복잡한 스위칭 네트워크를 요구한다. 스위칭 구성을 주의 깊게 선택하여 최적 성능을 유지하는 간단한 스위칭 네트워크가 필요하다.

### 발명의 상세한 설명

[0017] 본 발명은 재구성 가능한 센서 어레이 및 그러한 어레이를 위한 스위칭 구성을 최적화하는 방법에 관한 것이다. 센서는 광, 열 또는 압력 센서 또는 초음파 변환기일 수 있다. 본 명세서에 개시된 실시예는 더 큰 소자가 설치되는 하위 그리드로서 용량성 마이크로머신 초음파 변환기(cMUT)의 2차원 어레이를 사용한다. 하지만, 본 발명은 cMUT에 한정되지 않으며 다른 종래 또는 미래 변환기 기술에도 마찬가지로 적용될 수 있다.

[0018]

본 발명의 한 측면은 재구성 가능한 센서 소자 어레이의 제어 중에 스위치 네트워크에 의해 도입되는 에러를 최소화하는 스위칭 구성을 구현하는 방법으로서, 이 방법은 (a) 초기 스위칭 구성을 생성하는 단계와, (b) 반복적 알고리즘을 수행하는 단계로서, 이 반복적 알고리즘은, (i) 모든 스위칭 네트워크 에러를 고려하여, 스위치 구성을 시스템 응답을 계산하는 시스템 모델로 입력하는 단계 - 초기 스위칭 구성을 시작시에 입력되고 연속적으로 유도되는 수정된 스위칭 구성을 이후 연속적으로 입력됨 - 와, (ii) 입력된 스위치 구성을 모델을 사용하여 이미지 또는 복사 패턴을 생성하는 단계와, (iii) 생성된 패턴을 표현하는 데이터에 적어도 부분적으로 근거해서 비용 함수에 대한 값을 계산하는 단계와, (iv) 계산된 값이 비용 함수에 대한 최소 값을 실질적으로 표현하는지를 판정하는 단계와, (v) 계산된 값이 비용 함수에 대한 최소값이 아닌 경우, 현재 스위치 구성을 값 계산 결과의 함수로서 수정하여 수정된 스위칭 구성을 도달하게 하는 단계를 포함하고, 단계 (i) 내지 (v)는 각 스위칭 구성을 대해 반복되는 알고리즘 수행 단계와, (c) 계산된 값이 비용 함수에 대한 최소값인 경우, 비용 함수 값이 최소화되도록 하는 수정된 스위칭 구성을 시스템으로 구성하는 단계를 포함한다.

[0019]

본 발명의 다른 측면은 재구성 가능한 센서 어레이의 제어 중에 스위치 네트워크에 의해 도입되는 에러를 최소화하는 스위칭 구성을 구현 방법으로서, 이 방법은, (a) 초기 스위칭 구성을 생성하는 단계와, (b) 반복적 알고리즘을 수행하는 단계로서, 반복적 알고리즘은, (i) 스위치 구성을 시스템으로 입력하는 단계 - 초기 스위칭 구성을 시작시에 입력되고 연속적으로 유도되는 수정된 스위칭 구성을 이후 연속적으로 입력됨 - 와, (ii) 입력된 스위치 구성을 시스템의 성능을 판정하는 단계와, (iii) 시스템의 판정된 성능을 표현하는 데이터에 적어도 부분적으로 근거해서 비용 함수에 대한 값을 계산하는 단계와, (iv) 계산된 값이 비용 함수에 대한 최소 값을 실질적으로 표현하는지를 판정하는 단계와, (v) 계산된 값이 비용 함수에 대한 최소값이 아닌 경우, 현재 스위치 구성을 값 계산 결과의 함수로서 수정하여 수정된 스위칭 구성을 도달하게 하는 단계를 포함하고, 단계 (i) 내지 (v)는 각 스위칭 구성을 대해 반복되는 알고리즘 수행 단계와, (c) 계산된 값이 비용 함수에 대한 최소값인 경우, 상기 비용 함수 값이 최소화되도록 하는 수정된 스위칭 구성을 시스템으로 구성하는 단계를 포함한다.

[0020]

본 발명의 또 다른 양태는 스위치 네트워크의 각 상태를 제어하여 재구성 가능한 초음파 변환기 소자 어레이를 갖는 초음파 이미징 시스템을 동작하는 방법으로서, 이 방법은, (a) 초음파 이미징 시스템의 제 1 동작 상태에서 사용하기 위해 제 1 스위칭 구성을 최적화하는 단계와, (b) 초음파 이미징 시스템의 제 2 동작 상태에서 사용하기 위해 제 2 스위칭 구성을 최적화하는 단계를 포함하는데, 최적화 단계는 반복적 알고리즘을 사용하여 비용 함수를 최소화하는 단계를 포함한다.

[0021]

본 발명의 또 다른 양태는 스위치 네트워크의 각 상태를 제어하여 재구성 가능한 초음파 변환기 소자 어레이를 갖는 초음파 이미징 시스템을 동작하는 방법으로서, 이 방법은, (a) 초음파 이미징 시스템의 제 1 동작 상태에서 사용하기 위해 제 1 반복적 알고리즘을 사용하여 제 1 비용 함수를 최소화하여 제 1 스위칭 구성을 최적화하는 단계와, (b) 초음파 이미징 시스템의 제 2 동작 상태에서 사용하기 위해 제 2 반복적 알고리즘을 사용하여 제 2 비용 함수를 최소화하여 제 2 스위칭 구성을 최적화하는 단계를 포함하는데, 제 2 비용 함수는 제 1 비용 함수와 상이하다.

[0022]

본 발명의 또 다른 양태는 스위치 네트워크의 각 상태를 제어하여 재구성 가능한 초음파 변환기 소자 어레이를 갖는 초음파 이미징 시스템을 동작하는 방법으로서, 이 방법은, (a) 제 1 선택된 초음파 변환기 소자 세트를 포함하는 제 1 개구를 설치하는 제 1 스위칭 구성을 최적화하는 단계와, (b) 제 1 선택된 초음파 변환기 소자 세트를 포함하는 제 2 개구를 설치하는 제 2 스위칭 구성을 최적화하는 단계를 포함하는데, 제 2 개구의 빔 중심은 제 1 개구의 빔 중심에 대해 초음파 변환기 소자의 비율만큼 스텝된다.

[0023]

본 발명의 다른 측면도 이하 개시된다.

## 실시예

[0053]

본 발명은 재구성 가능한 스위칭 매트릭스 및 그러한 매트릭스와 그 관련 센서 소자 어레이에 대한 스위칭 구성을 최적화하는 방법에 관한 것이다. 설명의 목적을 위해, 재구성 가능한 어레이 및 최적화 방법을 용량성 마이크로머신 초음파 변환기(cMUT)를 참조하여 설명할 것이다. 하지만, 여기에 개시되는 본 발명의 관점은 cMUT를 사용하는 프로브에 한정되어 적용되는 것이 아니며, 오히려 pMUT를 사용하는 프로브, 나아가 입방체 서브 소자 각각이 상호 접속 수단에 의해 하위 스위칭 층에 접속되는 입방체 압전기 어레이에도 적용될 수 있다는 것을 이해해야 한다. 또한, 본 발명의 동일한 관점은 재구성 가능한 광, 열 또는 압력 센서 어레이에도 적용된다.

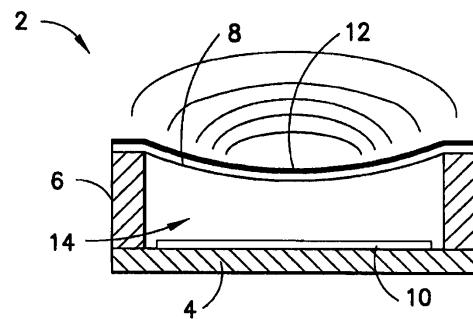

- [0054] 도 1을 참조하면, 통상적 cMUT 변환기 셀(2)의 단면이 도시되어 있다. 이러한 cMUT 변환기 셀의 어레이에는 통상적으로 질게 도핑된 실리콘(따라서, 반도전성) 웨이퍼와 같은 기판(4)상에 제조된다. 각 cMUT 변환기 셀에 대해, 실리콘 니트라이드로 구성될 수 있는 얇은 막(membrane or diaphragm, 8)이 기판(4) 위에 매달린다. 막(8)은 절연 지지부(6)에 의해 그 주변이 지지되고, 지지부는 실리콘 옥사이드 또는 실리콘 니트라이드로 구성될 수 있다. 막(8)과 기판(4) 사이의 캐비티(14)는 공기 또는 가스로 채워지거나 전체적으로 또는 부분적으로 진공일 수 있다. 통상적으로, cMUT는 공정이 허용하는 한 완전히 진공이다. 알루미늄 합금 또는 기타 적합한 전도성 재료와 같은 전도 재료 필름 또는 층은 막(8)상에 전극(12)을 형성하고, 전도성 재료로 구성되는 다른 필름 또는 층은 기판(4)상에 전극(10)을 형성한다. 다른 방법으로, 반도체성 기판(4)의 적절한 도핑에 의해 하부 전극이 형성될 수 있다.

- [0055] 캐비티(14)에 의해 분리되는 2개의 전극(10 및 12)는 캐패시턴스를 형성한다. 총돌 음향 신호가 막(8)을 진동시키면, 캐패시턴스의 진동은 관련 전자 소자를 사용하여 검출될 수 있으며(도 1에는 도시되지 않음), 이로써 음향 신호를 전기 신호로 변환한다. 반대로, 전극 중 하나에 인가되는 AC 신호는 전극 상의 전하를 변조시키며, 이것은 결국 전극들 사이의 용량적 힘의 변조를 야기하고, 후자는 막을 이동하게 하여 음향 신호를 전송한다.

- [0056] 개별 셀은 원형, 직사각형, 육각형 또는 기타 주변 형상을 가질 수 있다. 육각형 형상은 변환기 서브 소자의 cMUT 셀의 조밀한 패킹을 제공한다. cMUT 셀은 상이한 치수를 가질 수 있어서 변환기 서브 소자는 상이한 셀 사이즈의 복합 특성을 가지고 변환기에 광대역 특성을 제공할 것이다.

- [0057] 불행하게도, 이러한 소형 셀에 대한 개별 제어를 허용할 전자 소자를 제공하는 것은 난해하다. 전체로서 어레이의 음향 성능의 관점에서 소형 셀 사이즈는 우수하며 현저한 유연성을 제공하지만, 제어는 더 큰 구조로 제한된다. 다수 셀을 함께 그룹화하고 그들을 전기적으로 접속하는 것은 한 셀이 더 큰 서브 소자를 생성하게 허용하며, 원하는 음향 응답을 유지하면서 개별 제어를 가질 수 있게 한다. 한 셀은 스위칭 네트워크를 사용하여 서브 소자를 함께 접속함으로써 링 또는 소자를 형성할 수 있다. 소자들은 스위칭 네트워크의 상태를 변경하여 재구성될 수 있다. 그러나, 개별 서브 소자는 상이한 서브 소자를 형성하기 위해 재구성될 수 없다.

- [0058] MUT 셀은 서브 소자를 형성하기 위해 마이크로머신 공정에서 (스위치를 개입하기 않고) 함께 접속될 수 있다. 용어 "음향 서브 소자"는 그러한 클러스터를 기술하기 위해 이하에서 사용될 것이다. 이들 음향 서브 소자는 실리콘층 내의 그러한 스위치 또는 변환기 어레이에 직접적으로 인접하여 위치되는 상이한 기판상에 그러한 스위치를 배치하여 더 큰 소자를 형성하기 위해 마이크로전자 스위치에 의해 상호접속될 것이다.

- [0059] 여기에서 사용되는 바와 같이, 용어 "음향 서브 소자"는 단일 셀 또는 재구성될 수 없는 전기적으로 접속되는 셀의 그룹인데, 즉, 서브 소자는 독립적으로 제어되는 최소 음향 단위이다. 용어 "서브 소자들"은 음향 소자 및 그 관련 접속 전자 소자를 의미한다. "소자"는 스위칭 네트워크를 사용하여 함께 서브 소자를 접속하여 형성된다. 소자들은 스위칭 네트워크의 상태를 변경하여 재구성될 수 있다. 스위칭 네트워크에 포함되는 스위치의 적어도 일부는 "관련 접속 전자소자"의 부분이고, 이를 이후에 설명할 것이다.

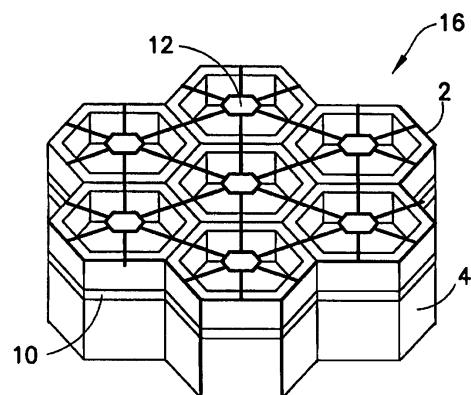

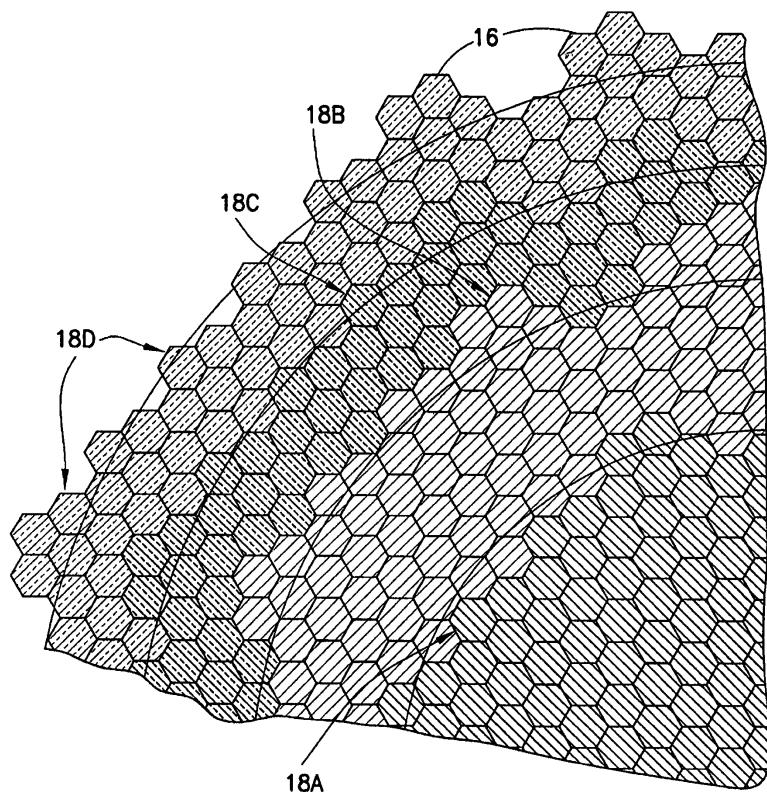

- [0060] 예시적 목적을 위해, 도 2는 7개의 육각형 cMUT 셀(2)로 구성되는 "데이지(daisy)" 변환기 서브 소자(16)를 도시하고 있다. 5개의 셀 링에 의해 하나의 중심 셀이 둘러싸이고, 링의 각 셀은 중심 셀의 각 사이드 및 링의 인접 셀과 접촉한다.

- [0061] 각 cMUT 셀(2)의 상부 전극(12)은 스위칭 가능하게 접속 해제될 수 있지 않은 접속에 의해 함께 전기적으로 결합된다. 육각형 어레이의 경우, 6개의 도전체는 상부 전극(12)으로부터 바깥쪽으로 복사하고, 인접 cMUT 셀의 상부전극에 각각 접속된다(6개가 아닌 3개의 다른 셀에 접속되는 주변의 셀의 경우는 예외). 유사하게, 각 셀(2)의 하부 전극(10)은 스위칭 가능하게 접속 해제 가능하지 않은 접속에 의해 함께 전기적으로 결합되어서, 7 배 더 큰 용량성 변환기 서브 소자(16)를 형성한다.

- [0062] 도 2에 도시된 종류의 서브 소자는 반도체성(가령, 실리콘) 기판상에 2차원 어레이를 형성하도록 배열될 수 있다. 이 서브 소자들은 스위칭 네트워크를 사용하여 환상 링과 같은 소자들을 형성하도록 재구성될 수 있다. 실리콘 기반 초음파 변환기 서브 소자를 사용하는 재구성 가능성은 미국 특허 출원 No. 10/383,990에 개시되어 있다. 재구성 가능성의 한 형태는 모자이크 환상 어레이이며, 이 또한 상술한 특허 출원에 개시되어 있다. 모자이크 환상 어레이 개념은 재구성 가능한 전자 스위칭 네트워크를 사용하여 서브 소자를 함께 그룹화함으로써 환상 소자를 구성하는 단계를 포함한다. 그 목적은 화질을 유지하고 슬라이스 두께를 개선하면서 빔형성 채널의 수를 감소시키는 것이다. 시스템 채널을 감소시키기 위해, 모자이크 환상 어레이에는 조정되지 않는 빔에 대

하여 하위 2차원 변환기 어레이의 표면상의 지연 등고선은 원형이라는 사실을 이용한다. 다시 말해, 등-지연 곡선은 빔 중심에 대해 환형이다. 지연의 원형 대칭성은 공통 지연을 갖는 서브 소자의 명백한 그룹화를 유도한다. 재구성 가능성은 스캔 또는 이미지를 형성하기 위해 더 큰 하위 2차원 변환기 어레이를 따라 빔을 스텝하는 데 사용될 수 있다.

[0063] MUT 셀 및 음향 서브 소자를 사용하여 변환기 어레이를 형성하는 많은 방식이 존재한다. 도 3은 모자이크 어레이를 형성하는 음향 서브 소자의 모자이크 세공을 도시하고 있다. 도 3의 실시예에서, 4개의 거의 환형인 소자(18A 내지 18D로 각각 표시됨)는, 각각 "데이지" 음향 서브 소자의 모자이크 세공(서브 소자당 함께 접속되는 7개의 MUT 셀)7개의 MUT 셀을 포함하고, 소자당 거의 동일한 면적을 갖도록 구성된다. 각 경우에 모자이크 세공은 다수의 서브 소자 유형으로 구성될 수 있다. 어레이 패턴은 모자이크 세공일 필요는 없지만, 음향 서브 소자 없는 면적을 가질 수 있다. 예를 들어, 음향 서브 소자 또는 어레이 아래의 셀을 상부 전극 접속을 가져오는 비아(vias)가 존재할 수 있다.

[0064] 본 발명의 구성은 빔폭, 사이드 로브 레벨(side lobe level) 또는 초점 깊이와 같은 다양한 음향 수치를 최적화하도록 변경될 수 있다. 다른 방법으로, 음향 서브 소자는 송신 동작을 위해 하나의 개구를 형성하고 수신부를 위해 다른 개구로 즉시 스위칭되도록 그룹화될 수 있다. 도 3은 거의 환형인 소자의 각 부분을 도시하고 있지만, 가령, 비연속 링, 광학 링 또는 원호(arcs)와 같은 다른 구성이 구현될 수 있다. 패턴 선택은 애플리케이션 요구에 의존할 수 있다.

[0065] 대부분이 개구는 하나의 더 큰 소자를 형성하기 위해 상호접속되는 접촉하는 그룹화된 서브 소자로 구성될 것이다. 이 경우, 모든 서브 소자를 그 개별 버스 라인에 직접적으로 접속하는 것이 필요치 않다. 소정 그룹 내의 제한된 수의 서브 소자를 접속시키고 나머지 서브 소자를 서로 접속시키는 것으로 충분하다. 이 방식에서, 송신 신호는 버스 라인을 따라 시스템으로부터 진행하여 제한된 수의 액세스 포인트의 제한된 수를 따라 소자로 진행한다. 이곳으로부터 로컬 접속부를 통해 소자 내에서 신호가 확산된다.

[0066] 소정의 특정 구조에서, 재구성 가능한 어레이는 음향 서브 소자를 시스템 채널로 매핑된다(maps). 이 매핑은 개선된 성능을 제공하도록 설계된다. 매핑은 스위칭 네트워크를 통해 수행되고, cMUT 셀이 구성되는 기판에 직접적으로 배치되는 것이 이상적이지만, 변환기 기판에 인접하여 접속되는 상이한 기판에도 존재할 수 있다. cMUT 어레이가 실리콘 기판의 상부에 직접적으로 구성되므로, 스위칭 전자소자는 그 기판으로 포함될 수 있다. PZT 또는 종래 구현에 있어서, 스위칭 네트워크는 분리된 실리콘 기판에서 간단히 제조되어 PZT 어레이에 부착될 것이다.

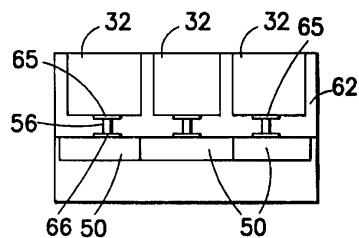

[0067] 도 4에 도시된 공동 접속된 cMUT 및ASIC 어레이의 단면도가 도시되어 있으며, ASIC로부터 어떻게 cMUT로 구성되는지를 도시하고 있다. 도시된 바처럼, 단일 비아(56)가 각 cMUT 서브 소자(32)를 그 대응 CMOS 서브 소자(또는 "셀", 50)에 접속하기 위해 사용된다. 신호 전극을 스위칭 ASIC에 형성되는 각 도전 패드(66)에 접속시키는 비아(56)는 음향 백킹층(acoustic backing layer, 62)에 매립될 수 있다.

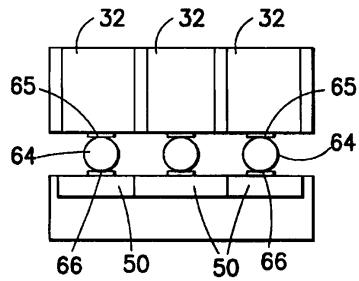

[0068] 또한, 개별 웨이퍼상의 cMUT를 구성하고 그들을 ASIC 스위치 매트릭스에 개별적으로 접속시키는 것도 가능하며, 이것은 도 5에 도시되어 있다. 여기서 예를 들어, 솔더 범프(solder bump, 64) 및 도전 패드(66)가 사용되어 개별 cMUT 서브 소자(32)를 그들의 스위치 전자 소자 대응 부분(50)에 접속하는 데 사용된다. ACF(Anisotropic Conductive Film) 또는 유연한 상호접속부와 같은 다른 패키징 기술도 사용될 수 있다.

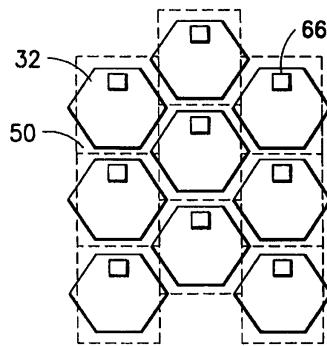

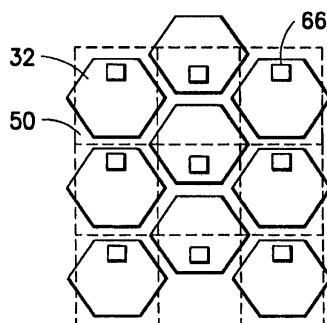

[0069] 최적 패키징 밀도를 위해, 도 6에 도시된 바와 같이 cMUT 서브 소자(32) 및관련 전자소자를 육각형 그리드에 타일(tile)하는 것이 유용하고, 도 6은 ASIC 스위치 매트릭스의 평면도를 도시하고 있다. 여기서, CMOS 유닛 스위치 셀(50)은 모든 두번째 열이 셀 높이 절반만큼 상쇄되는 열로 배치된다. 셀 치수의 올바른 선택에 관하여, 이는 도시된 바와 같은 완벽한 육각형 패드(66) 어레이를 산출할 것이다. 그리고, 비아(56)(또한 육각형 어레이로 배열됨)는 상술한 변환기층으로의 접속의 기반을 형성하는 각 패드(도 4에서는 생략)로 접속되고, 육각형 서브 소자 어레이를 포함한다. 더 간단한 ASIC 구현이 도 7에 도시되어 있다. 여기서, CMOS 유닛 스위치 셀(50)은 직사각형 그리드를 형성하기 위해 수평 행 및 수직 열로 배열되고, 그 위의 육각형 서브 소자들(32)은 육각형 그리드를 형성한다. 도 7에 도시된 바와 같이, 직사각형 어레이를 형성하기 위해 행과 열로 배열되는 단위 스위치 셀 패드(66)는 여전히 적합하게 라인 업되어 단위 스위치 셀(50)들이 각 육각형 서브 소자들(32)에 전기적으로 접속되도록 접속을 형성한다. 어느 경우에도, 서브 소자들의 육각형 그리드 패턴은 도 3에 도시된 바와 같은 모자이크 환상 어레이를 구현할 수 있게 한다.

[0070] 통상적인 동작에서, 재구성 가능한 어레이는 도 3에 도시된 것과 유사한 초기 개구 패턴으로 프로그램된다. 이

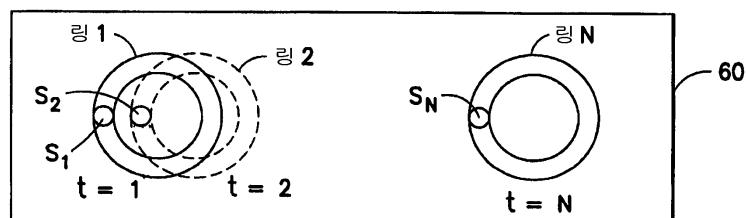

패턴은 빔형성기가 어레이 전면의 빔을 생성하게 한다. 이미징 동안, 개구는 도 8에 도시된 바와 같은 어레이를 지나서 스캔되고, 링은  $t=1$ 에서 링 1로부터  $t=2$ 에서 링2 최종적으로  $t=N$ 에서 링 N이며,  $t=$ 는 시각이고 N은 2보다 큰 양의 정수이다. 이 방식에서, 빔은 어레이 전면의 공간에서 스위핑되고(swept) 빔형성되는 애코가 사용되어 이미지의 연속적인 라인을 구성한다. 재구성 가능한 어레이의 목적은 임의적인 복합 어레이 패턴을 위해 도 8에 도시된 이미징 동작을 전자적으로 완수할 수 있다. 이전 초음파 스캐너는 전자적 스캐닝을 완수할 수 있지만 상승 방향 및 고정된 구조의 미세한 센서 서브 소자의 결여로 인해 개구의 복잡도에서 제한된다.

[0071] 도 8에 도시된 바와 같은 완전히 재구성 가능한 어레이는 구현의 많은 협력한 시도를 제공한다. 센서 어레이는 수만 개의 서브 소자로 세부 분할된다. 빔 패턴은 유한 개의 시스템 송신/수신 및 빔형성 채널로 그들의 접속의 서브 소자들을 그룹화하여 구성된다. 모자이크 환상 어레이 개념을 구현하기 위해 사용되는 경우, 재구성 가능한 어레이는 어레이를 지나 전자적으로 이동되는 다수의 링을 형성할 것이다. 각각의 새로운 이동 스텝핑에서, 전체 링 패턴은 새로운 구성을 생성하기 위해 어레이로 재프로그래밍된다. 또한, 송신과 수신 사이에서 링 패턴을 갱신하고 수신 등에 다수의 간격으로 형성되는 입의 왜곡을 감소시켜, 화질을 개선한다.

[0072] 통상적인 시스템에서, 128개 또는 이상의 빔 형성 채널이 사용된다. 현재의 초음파 시스템은 128개 시스템 채널을 고정된 수의 변환기 소자로 루팅할 수 있는 멀티플렉싱 아키텍처를 사용한다. 이러한 멀티플렉서 네트워크의 현명한 설계를 사용하면, 제한된 양의 전자소자를 갖는 표준 스캐닝 패턴을 생성할 수 있다. 하지만, 대부분의 경우에, 네트워크 제한으로 인하여 스캐닝 패턴은 고정되며 재구성 가능하지 않다. 전체적으로 재구성 가능한 어레이는 이러한 제한을 받지 않는다. 그러나, 그것을 구현하기 위해 매우 밀집한 스위칭 매트릭스를 요구한다.

[0073] 도 8에 도시된 바와 같이, 재구성 가능한 어레이의 기본적 성질은 어떤 서브 소자도 어떤 시스템 채널로 임의적으로 접속될 수 있다는 것을 요구한다. 가령, 개구는 첫 번째 위치로부터 다음 위치로 스캐닝되므로, 서브 소자(S2)는 우선 내부 링(도시되지 않음)의 부분이어야 하며 링 2의 부분이어야 한다. 이것은 단기단에 첫 번째 시스템 채널에 접속되는 것으로부터 상이한 시스템 채널로 접속되는 것으로 스위칭되어야 한다는 것을 의미한다. 이것은 일반적으로 스캐닝 동작 중의 어레이의 많은 수의 서브 소자에 관해 사실이다.

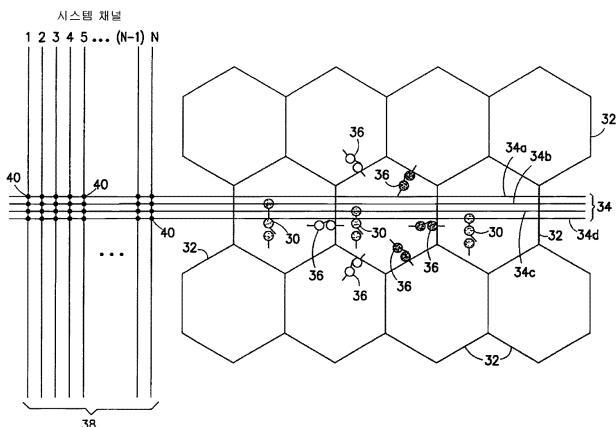

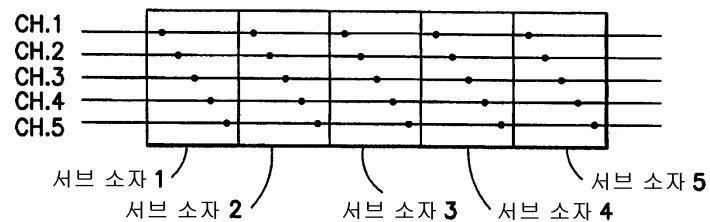

[0074] 이 요구 조건을 구현하는 가장 간단한 방식은 각 서브 소자가 모든 시스템 채널로 액세스를 가지도록 어레이를 통해 모든 시스템 채널을 분배하는 것이다. 이 아키텍처가 도 9에 도시되어 있다. 여기서는 단지 5개의 시스템 채널이 예시를 위해 도시된다. 각 시스템 채널은 어느 시스템이 어느 서브 소자에 의해 꾹눌되는지를 선택하는 데 사용되는 로컬 스위치를 갖는 모든 서브 소자를 통해 버스된다(bussed).

[0075] 매트릭스 전자소자가 변환기 어레이 바로 뒤에 존재하는 시스템에서는, 각 서브 소자의 스위칭 전자소자에 대해 공간은 서브 소자의 사이즈로 감소된다. 통상적인 초음파 시스템에서 이 사이즈는 대략 수백 마이크로이지만 이보다 작을 수도 있다. 스위치의 사이즈는 그 저항에 대해 역으로 변하므로, 저항이 더 높고 스위치가 더 많거나 저항이 더 낮고 스위치가 더 적은 것 중 절충해야 한다. 하지만, 스위치가 최대로 작을 수 있는 극단적인 경우를 취하더라도, 현재의 반도체 기술을 사용하여 16개보다 많은 스위치는 할당된 공간에 쉽게 맞을 수 없다는 것이 곧 명백해질 것이다. 실제 어레이에 있어서 도 9의 전체적으로 거주되는 아키텍처는 더 많은 스위치를 포함할 것이고, 이는 현재 기술 수준으로는 곤란한 것으로 보인다.

[0076] 미래 기술은 더 많은 스위치를 동일한 공간에 접속할 수 있을 것이지만, 이미지의 과장에 관련되는 것이기 때문에 초음파의 진보는 할당된 셀 사이즈를 감소시키는 경향일 것이며, 개선된 화질을 위해 축소되어야 한다. 또한, 더 많은 부품, 가령 디지털 제어 및 송신/수신 회로는 이 동일한 제한된 면적으로 이주할 것이다. 따라서, 단순성이 유리하지만 전체적으로 거주되는 아키텍처는 유지되거나 실용적이지 않다.

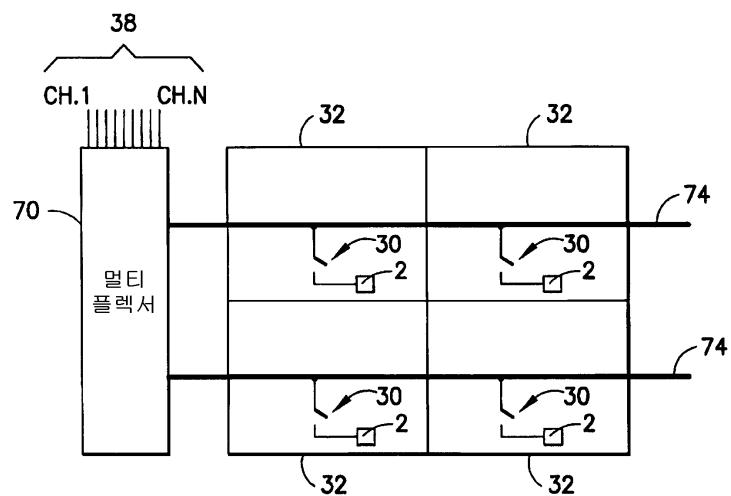

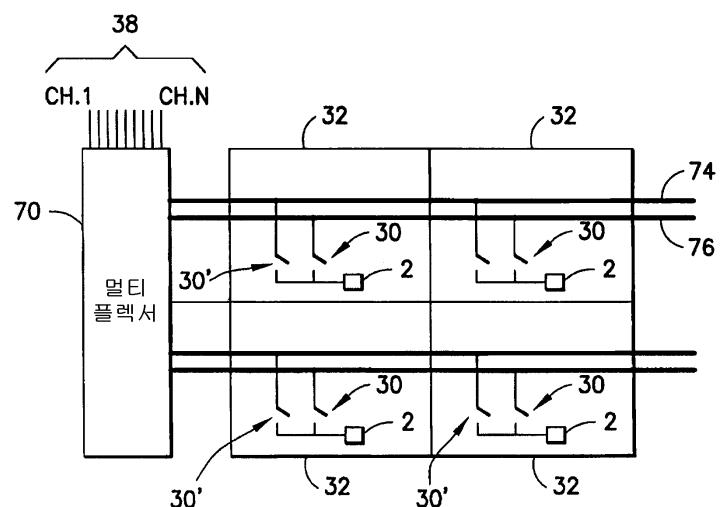

[0077] 상술한 상호 접속 문제에 대한 보다 나은 해결 방안은 각 서브 소자의 스위치의 수를 제한하여 동시에 재구성 가능한 어레이에서 요구되는 유연성을 제공한다. 이는, 도 10에 도시된 바와 같이, 제한된 수의 버스 라인을 사용하고 그들을 재구성 가능하게 하여 수행될 수 있다. 여기서 멀티플렉서(70)는, 오직 하나의 버스 라인에 의해 서브 소자(32)의 각 행이 제공되며, 버스 라인(74) 중 하나에 시스템 채널(38)(CH.1 내지 CH.N) 중 하나가 접속되게 임의로 선택하는 데 사용된다. 각 서브 소자의 cMUT 셀(2) (오직 하나의 cMUT 셀이 각 서브 소자에 대해 도시됨)은 개별 액세스 스위치(30)에 의해 버스 라인에 접속된다. 이 아키텍처의 핵심 특징은 많은 스위치가 어레이 외부에 위치되어서 변환기의 구조에 의해 제한되지 않는다는 것이다. 1차원적 패턴은 서브 소자의 어느 행이 어느 시스템 채널에 접속되는지를 연속적으로 선택하여 이 아키텍처를 사용함으로써 어레이를 지나 스캔될 수 있다. 이 아키텍처에 대한 추가적인 개선점이 도 11에 도시되어 있다. 여기서, 다수의 버스 라인(74, 76)은 서브 소자(32)의 각 행 아래로 루팅된다. 각 서브 소자(32)의 cMUT 셀(2)은 액세스 스위치(30')을

통한 버스 라인(74) 또는 액세스 스위치(30)를 통한 버스 라인(76)에 접속될 수 있다. 이 아키텍처는 동일한 행 내의 상이한 시스템 채널상의 소자를 그룹화할 수 있기 때문에 수평 방향으로 유연성을 제공한다.

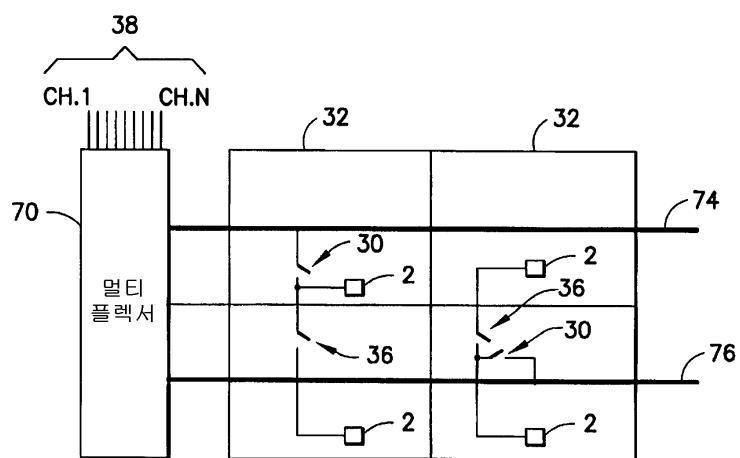

[0078] 상술한 아키텍처에 대한 추가적인 개선점은, 단일의 더 큰 소자를 형성하기 위해 접속되는 그룹화된 서브 소자들로 대부분의 개구가 구성될 것이라는 점을 실현하여 이루어질 수 있다. 이 경우엔, 모든 서브 소자를 그 개별 서브 라인으로 직접 접속할 필요가 없다. 주어진 그룹 내의 제한된 수의 서브 소자를 접속하고 서로에 대하여 나머지 서브 소자를 접속하는 것으로 충분하다. 이 방식에서, 이 방식에서, 송신 신호는 버스 라인을 따라 시스템으로부터 진행되어 제한된 수의 액세스 포인트를 따라 소자로 진행한다. 그곳에서부터 신호는 로컬 접속을 통해 소자 내에서 확산된다. 이 아키텍처는 도 12에 도시되어 있다. 여기서 개개의 서브 소자(32)는 액세스 스위치(30)에 의해 그들의 행과 관련되는 버스 라인에 접속할 수 있고, 매트릭스 스위치(36)에 의해 인접 행과 관련되는 버스 라인에 접속할 수 있으며, 이들은 하나의 서브 소자를 인접 서브 소자에 접속한다.

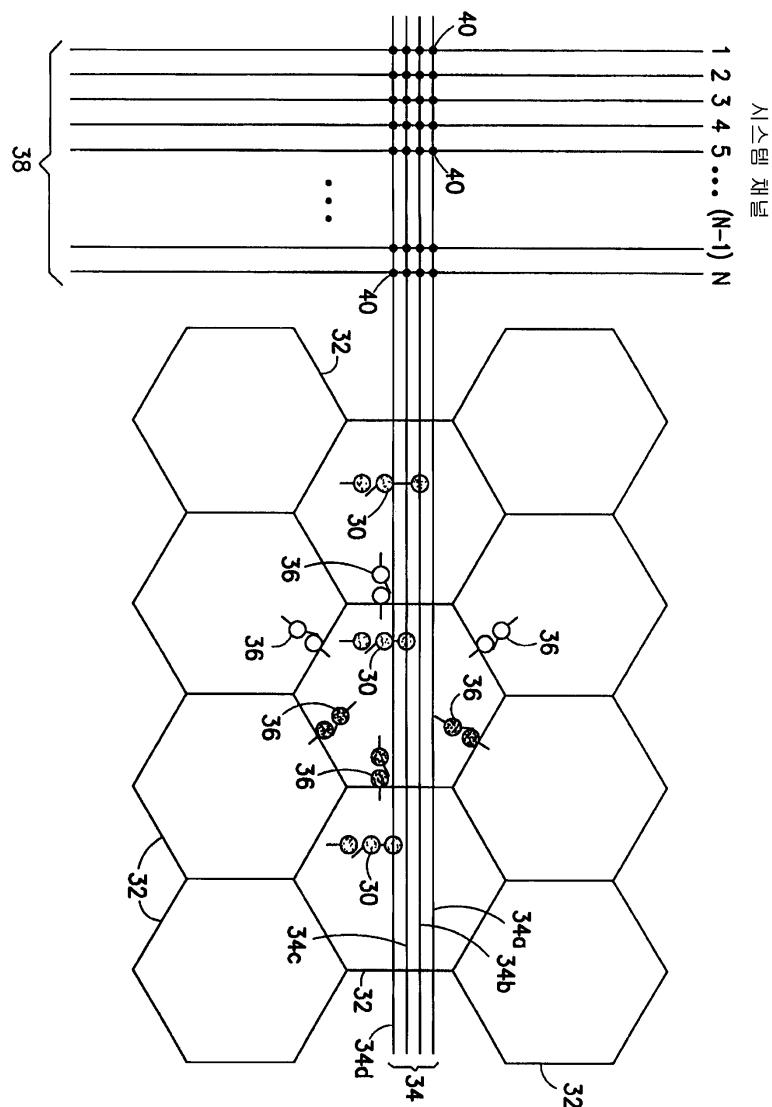

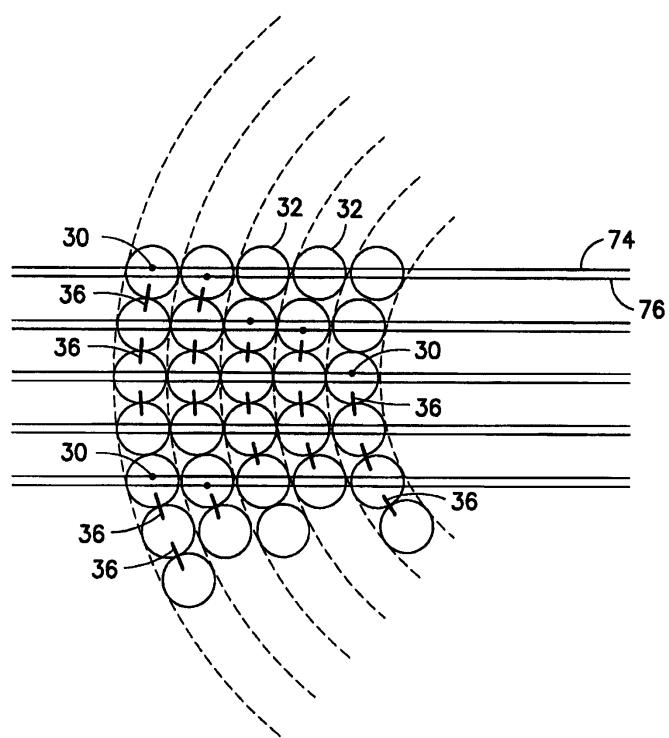

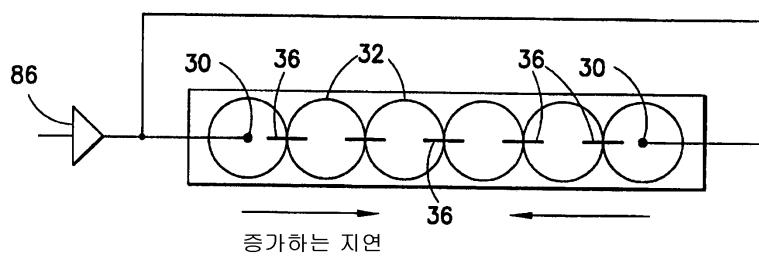

[0079] 도 13에 도시된 본 발명의 일실시예는 상술한 모든 개선점을 함께 포함한다. 여기서 액세스 스위치(30)는 소정 서브 소자(32)를 버스(34)의 행 버스 라인에 접속하는 데 사용된다. 이 아키텍처는 직접적으로 모자이크 환상 어레이에 적용 가능하다. 이러한 디바이스에서 다수의 링은 본 아키텍처를 사용하여 형성될 수 있는데, 여기서 각 링은 하나 이상의 액세스 스위치를 사용하여 단일 시스템 채널에 접속되고 이를 각각은 버스 라인에 접속되며 결국 시스템 채널에 접속된다.

[0080] 액세스 스위치는 도 13에 도시된 바와 같이 소정 수의 버스 라인을 위해 요구되는 수를 감소시키기 위해 엇갈리며(staggered), 이하에서 추가적으로 설명한다. 또한, 버스 라인(도시되지 않음)에 대한 액세스 스위치의 랜덤 정렬이 반복 패턴으로 인한 일그러짐(artifacts)을 감소시키기 위해 사용된다. 어레이의 유연성을 개선하기 위해 각 서브 소자의 하나 이상의 액세스 스위치가 사용될 수 있다. 이러한 아키텍처에서, 개수가 버스 라인과 시스템 채널의 수보다 훨씬 작은 경우에 유연성과 서브 소자당 액세스 스위치의 수 사이에 균형을 맞추어질 것이다. 또한, 각 소자에서 버스 라인당 하나 이상의 액세스 스위치를 사용하는 것도 가능하다. 중복 액세스 스위치를 사용하여 기능하지 않은 액세스 스위치가 바이패싱될 수 있기 때문에 디바이스의 산출량을 개선할 것이다.

[0081] 행 버스 라인은 도 13에 도시된 바와 같은 교차점 매트릭스를 사용하여 시스템 채널에 접속된다. 더 적은 멀티플렉서 스위치가 요구되는 경우에는 산재하는(sparse) 교차점 스위치도 사용될 수 있다. 이러한 아키텍처는 공간 사용에 더 효율적이지만 모든 버스 라인이 올바르게 접속되는 것을 보장하기 위해 현명한 스위치 구성 선택을 요구할 것이다. 도 12에 도시된 바처럼, 행당 다수 버스 라인이 사용될 수 있다. 더 많은 버스 라인은 더 많은 멀티플렉서 스위치의 비용으로 어레이의 유연성 및 어레이 내부의 더 많은 루팅 면적을 개선한다. 행을 스kip하거나 상이한 행의 버스 라인의 상이한 수를 사용할 수 있다. 예컨대, 면적을 보존하기 위해 인접 서브 소자 행의 모든 쌍 사이의 버스 라인 그룹을 공유하는 것이 유리할 수 있다.

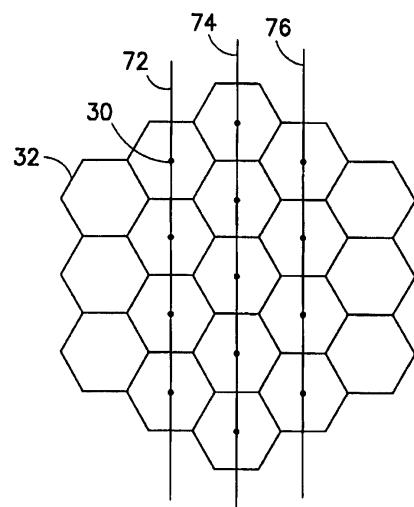

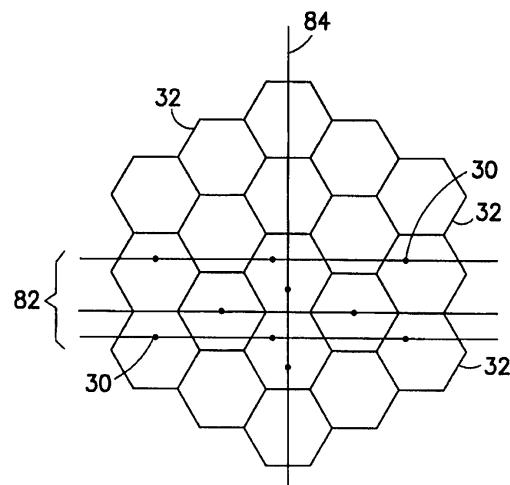

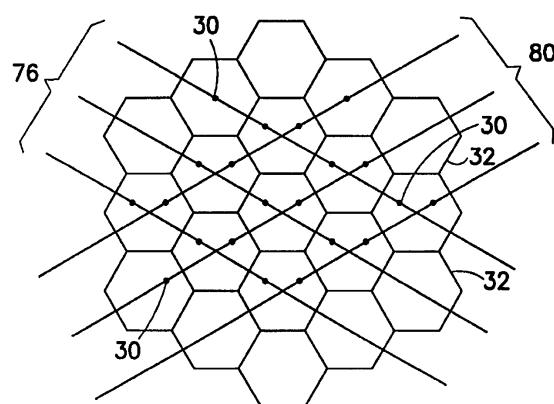

[0082] 지금까지 오직 수평 버스 라인을 설명하였지만, 어레이 내에 수직 및 수평 이동 버스를 배치하는 것도 가능하다. 버스 라인은 도 14에 도시된 바와 같이 (버스 라인 72, 74, 76을 참조) 수직으로 배치될 수 있다. 도 15를 참조하면, 하나의 버스 라인 세트(82)가 수평적으로 배치되고 다른 한 세트(84)가 수직으로 배치될 수 있다. 이 경우에 각 서브 소자 또는 서브 소자 그룹은 하나의 액세스 스위치를 통해 수직 버스 라인에 접속 가능할 것이고 다른 액세스 스위치를 통해 수평 버스 라인에도 접속 가능할 것이다. 하지만, 버스 라인을 위해 이용 가능한 전자적인 예산(electronic real estate)이 낮고 더 많은 버스 라인이 필요하기 때문에 2방향으로 버스 라인이 이어지지만 서브 소자에 여전히 오직 하나의 액세스 스위치가 존재하는 경우, 각 서브 소자의 액세스 스위치는 수평 버스 라인 또는 수직 버스 라인에 접속될 수 있지만 양쪽 모두에는 접속될 수 없다. 최종적으로, 버스 라인은 도 16에 도시된 바와 같이 대각선으로 배치될 수도 있다. 이러한 라인(76, 80)은 육각형 어레이의 자연축의 두 개를 따라 각각 이어지므로 서브 소자 지정을 단순화할 것이다.

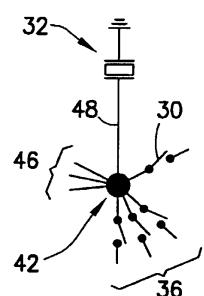

[0083] 액세스 스위치와 행 버스 라인의 수는 사이즈 제한 및 애플리케이션에 의해 결정된다. 한 예시적인 구현(도 13에 도시됨)을 개시할 목적으로, 각 서브 소자(32)에 대한 단일 액세스 스위치(30) 및 어레이 각 행에 대한 4개의 행 버스 라인(34a-34d)를 가정할 것이다. 두 번째 종류의 스위치는 매트릭스 스위치(36)이며, 이 스위치는 한 서브 소자의 접속점(42)을 이웃 서브 소자의 접속점에 접속하는 데 사용된다(도 17을 참조). 이것은 음향 서브 소자가 이웃 음향 서브 소자와 관련되는 접적 전자소자를 통해 시스템 채널에 접속되게 한다. 또한, 음향 서브 소자가 액세스 스위치를 통해 직접적으로 접속되지 않더라도 시스템 채널에 접속될 수 있게 한다. 도 13은 서브 소자당 3개의 매트릭스 스위치를 도시하고 있지만, 면적을 보존하기 위해 3개보다 적게 갖거나, 저항이

낮아서 더 큰 면적을 가지는 스위치가 가능하다. 게다가, 매트릭스 스위치는 소정 어레이에 대해 알려진 악성 서브 소자 주위를 루팅하는 데 사용될 수 있다. 최종적으로, 육각형 서브 소자가 도시되어 있지만, 직사각형 서브 소자도 가능하다.

[0084] 도 17을 참조하면, 서브 소자 각각은 음향 서브 소자(32)와 관련되는 전자소자의 공통 접속점(42)에 접속된다. 이 공통 접속점(42)은 각 서브 소자의 8개의 부품을 전기적으로 접속한다. 공통 접속점(42)은 그 서브 소자에 대한 액세스 스위치(30)에, 그 서브 소자와 관련되는 세개의 매트릭스 스위치(36)에, 접속부(46)를 통한 세 개의 이웃 서브 소자와 관련되는 세 개의 매트릭스 스위치에 음향 서브 소자 또는 변환기(32)를 접속한다. 매트릭스 스위치를 통해 이동하는 신호는 이웃 서브 소자의 공통 접속점에 접속되게 된다.

[0085] 도 13은 스위칭 네트워크가 특정 서브 소자를 위해 어떻게 동작할 수 있는지를 도시한다. 이는 오직 예시적인 배열이다. 네 개의 행 버스 라인(34a 내지 34d)을 포함하는 버스(34)는 서브 소자(32)의 행 아래로 이어진다. 도 13은 이 행의 오직 세 개의 서브 소자를 도시하고 있지만, 이 행의 다른 서브 소자가 도시되지 않았다는 것을 이해해야 한다. 버스(34)의 행 버스 라인은 행의 끝부분에서 멀티플렉싱 스위치(40)에 의해 시스템 채널 버스(38)의 시스템 채널 버스 라인으로 멀티플렉싱되고, 교차점 스위칭 매트릭스를 형성한다. 도 13에 도시된 바와 같이, 각 행 버스 라인(34a-34d)은 적합한 멀티플렉싱 스위치(40)를 턴 온하고 특정 행 버스 라인을 다른 시스템 채널 버스 라인에 접속하는 멀티플렉싱 스위치를 턴 오프함으로써 버스(38)의 시스템 채널 버스 라인 중 하나에 접속될 수 있다. 이러한 멀티플렉싱 전자소자는 측면을 벗어날 수 있으므로(be off to the side) 사이즈가 제한되지 않는다. 도 13은 전체적으로 거주되는 교차점 스위치를 도시하고 있다. 그러나, 모든 버스 라인이 모든 시스템 채널에 접속되게 하는 스위치를 가질 필요가 없는 경우에는, 시스템 채널의 오직 작은 서브 세트가 소정 버스 라인에 접속될 수 있는 산재하는 교차점 스위치가 사용될 수 있고, 이 경우에는 도 13에 도시된 오직 일부의 스위치만이 존재할 것이다.

[0086] 액세스 스위치는 버스 라인으로의 서브 소자 직접 액세스를 제공하기 때문에 그렇게 명명된다. 도 13에 도시된 예시적 구현에서, 여섯 개의 다른 스위치 접속이 각 서브 소자에 대해 존재한다. 이러한 접속은 매트릭스 스위치(36)의 형태를 취한다. 매트릭스 스위치는 이웃 서브 소자에 서브 소자가 접속되게 한다. 이 육각형 패턴의 각 서브 소자에 대해 이웃 서브 소자에 여섯 개의 접속이 존재하지만, 오직 세 개의 스위치가 각 서브 소자에 상주하고, 다른 세 개의 접속은 이웃 서브 소자의 스위치에 의해 제어된다. 그러므로, 각 서브 소자에는 도합 네 개의 스위치와 관련 디지털 로직이 존재한다. 이것은 단지 하나의 예시적 구현이다. 버스 라인 수, 액세스 스위치 수, 매트릭스 스위치의 수 및 형태는 모두 상이할 수 있지만, 전체적인 원리는 유지될 것이다.

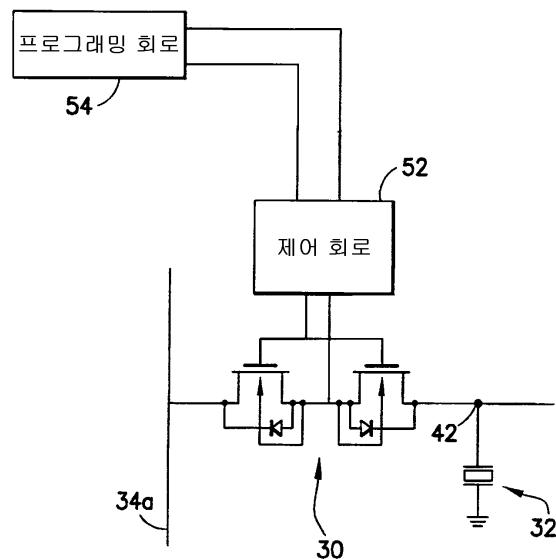

[0087] 액세스 및 매트릭스 스위치는 개별적으로 패키징되는 부품일 수 있지만, MUT 어레이가 제조될 동일한 반도체 기판 내에 스위치를 제조할 수도 있다. 이러한 스위치는 미국 특허 출원 No. 10/248,968 "Integrated High-Voltage Switching Circuit for Ultrasound Transducer Array"에 개시된 유형의 고전압 스위칭 회로를 포함할 수 있다. 각 스위치는 바이폴라 동작을 허용하기 위해 연속적으로(back to back) 접속되는(소스 노드가 함께 단락됨) 두 개의 DMOS FET를 포함한다. 양쪽 FET가 턴 온될 때마다 스위치 단말을 통해 전류가 흐른다. 스위치의 상태는 개개의 스위치 제어 회로에 의해 제어된다. 스위치 제어 회로의 상태는 결국 프로그래밍 회로로부터의 출력에 의해 지시되는데, 이것은 여기에 개시된 알고리즘을 사용하여 유도되는 최적 스위칭 구성에 따라 스위치 제어 회로를 프로그램한다. 스캔 제어기는 최적 스위칭 구성을 프로그래밍 회로로 로딩한다. CMOS 고전압 스위치의 사용은 하나의 바람직한 실시예이지만, 여기에 개시되는 본 발명은 다른 스위칭 기술, 가령 저전압 스위치, MEMS 스위치 및 개발 중인 기타 미래 스위치 기술에 직접적으로 적용 가능하다.

[0088] 도 18는 공통 접속점(42)을 통해 액세스 스위치(30)에 접속되는 음향 서브 소자를 도시하고 있다. 접속점에 접속하는 여섯 개의 다른 라인은 도시되지 않는다. 이 예를 위해, 액세스 스위치(30)는 상술한 연속 DMOS FET 쌍을 포함한다. 제어 회로(52)는 프로그래밍 회로(54)에 의해 송신되는 제어 신호의 함수로서 스위치(30)를 온 또는 오프한다. 액세스 스위치(30)가 턴 온되면, 음향 서브 소자(32)(즉, 상호 접속되는 cMUT 셀의 서브 어레이)는 행 버스 라인(34a)에 접속된다. 이 구성에 있어서, 각 음향 서브 소자와 관련되는 전자소자는 하나의 액세스 스위치, 세 개의 매트릭스 스위치, 이러한 네 개의 스위치 각각에 대한 개개의 제어 회로 및 세 개의 이웃 서브 소자(도시되지 않음)의 매트릭스 스위치에 공통 접속점을 접속하는 개개의 도전체를 포함할 것이다.

[0089] 서브 소자로부터 행 버스 라인으로 이동하는 신호는 전기 수신 신호이다. 여기서 수신 신호는 사운드 압력 파가 변환기와 상호 작용할 때 음향 서브 소자에 의해 발생되는 전기 응답이다. 전기적 펄스가 초음파 시스템에 의해 발생되는 송신 신호는 행 버스 라인으로부터 매트릭스 스위치로 이동한다. 소정 채널에 있어서, 이 전기적 여기 펄스는 시스템 채널 버스 라인을 통해 행 버스 라인으로 이동한다. 신호는 행 버스 라인으로부터 음향

서브 소자로 액세스 스위치를 통해 이동하고 매트릭스 스위치를 통해 다른 서브 소자로도 이동한다.

[0090] 음향 서브 소자 뒤에 적합한 스위치의 수는 제한된다. 스위치의 사이즈는 스위치의 온 저항(on resistance)을 결정하고 스위치가 작을수록 온 저항은 커진다. 스위칭에 의해 유발되는 지연 및 왜곡은 스위치 온 저항이 증가함에 따라 증가한다. 이는 음향 서브 소자 뒤의 스위치의 수와 이러한 스위치에 의해 도입되는 지연 사이에 균형이 존재한다는 것을 의미한다. 균형에 대한 한 가지 해결방안은 유연성을 최대한 유지하면서 작은 수로 스위치의 수를 감소시키는 것을 포함한다. 이 감소는, 다른 서브 소자를 통해 음향 서브 소자가 시스템 채널에 부착되도록 매트릭스 스위치를 사용하고 액세스 스위치의 수를 작은 수로 제한하여 완수된다.

[0091] 액세스 스위치를 시스템 채널에 접속하는 버스 라인은 전자 소자층에도 공간을 차지하여 버스 라인의 수를 최소화하는 것도 유리하다. 동일한 행에서 음향 서브 소자에 직접적으로 접속될 수 있는 고유 채널의 수는 버스 라인의 수에 의해 결정된다. 하지만, 매트릭스 스위치는 한 행의 서브 소자가 다른 행의 서브 소자에 접속되게 하기 때문에, 한 행의 채널의 수는 매트릭스 스위치에 의해 증가된다. 이는 버스 라인의 수가 작게 유지되게 하며, 여전히 더 많은 채널을 제공한다. 물론, 더 많은 버스 라인을 갖는 것은 유연성을 증가시키지만 더 많은 공간을 요구한다.

[0092] 매트릭스 스위치의 사용은 각 서브 소자 뒤의 액세스 스위치의 수가 감소될 수 있다는 것을 의미한다. 극단적인 경우에 각 서브 소자에 대해 오직 하나의 액세스 스위치가 존재한다. 하지만, 하나 이상의 버스 라인이 존재하는 경우, 어떤 버스 라인에 각 액세스 스위치가 접속되어야 하는지에 관해 결정해야 한다. 한 가지 해결방안은 접속을 엇갈리게 하여 접속되는 버스 라인이 행의 모든 N 서브 소자를 반복하게 하는 것이며, 여기서 N은 이하 설명하는 바와 같은 최소 신호 왜곡 요구 사항에 의해 결정되는 수이다. 도 13을 참조하면, 행의 각 서브 소자(32)는 개개의 액세스 스위치(30)를 통해 행 버스(34)의 행 버스 라인 중 하나에 접속된다. 엇갈린 접속의 패턴은 네 개의 서브 소자마다 반복한다. 엇갈림은 더 많은 버스 라인이 더 적은 액세스 스위치를 갖고 매트릭스 스위치와 결합되게 하며, 여전히 어떤 시스템 채널이 각 서브 소자에 접속될 수 있는지에 관한 상당한 유연성을 허용한다. 물론, 셀당 하나 이상의 액세스 스위치를 가지는 것은 접속의 유연성을 증가시키나 더 높은 온 저항을 갖는 더 적은 스위치를 요구한다.

[0093] 일반적으로, 여전히 적합한 신호 무결성을 유지하면서 패턴이 반복된 후 함께 배열될 수 있는 최대 매트릭스 스위치 수에 의해 행(N)의 수가 결정된다. 이 수는, 매트릭스 스위치 저항 및 cMUT 캐페시턴스가 시리즈 텁(N)의 수와 지수적으로 변하는 지연의 시간 상수를 갖는 RC 지연 라인을 형성한다는 이해를 바탕으로 한다. 다수 행 버스 라인의 액세스 스위치를 엇갈리게 하는 것은 지원될 수 있는 소자의 수가 지연 라인의 소정 제한으로 증가되게 한다. 도 20에 도시된 바와 같이, 설계에 대한 최악의 경우는 단일 서브 소자 너비를 갖는 링(그 일부가 점선 호에 의해 표시됨)이 함께 근접하여 밀집되는 경우에 발생한다. 링의 수직 단면은 이 설계의 버스 라인(74, 76)이 수평으로 이어지기 때문에 최악의 경우를 만든다. 링의 수평 단면에서, 서브 소자는 버스 라인이 링에 평행하게 이어지기 때문에 모두 동일할 것이므로 모든 서브 소자에서 오직 하나의 액세스 스위치를 사용할 수 있다. 하지만, 수직 단면에서, 서브 소자(32)의 모든 행은 상이한 시스템 채널에 접속되는 상이한 버스 라인과 관련된다. 그러므로, 이 영역에서 수직하게 공간을 갖는 서브 소자는 매트릭스 스위치를 사용하여 오직 지지될 수 있고, 점선으로 표시된다. 도 20에서, 해당 2개의 버스 라인이 존재하며, 액세스 스위치(30)(점으로 표시)의 패턴은 네 개의 행마다 반복한다. 각 행에서, 두 개의 링은 두 개의 액세스 스위치 및 매트릭스 스위치와 그룹화되는 서브 소자의 관련 열(string)에 의해 지지된다. 패턴은 네 개 행 후에 반복되므로, 이 특정 아키텍처는 최대  $2 \times 4 = 8$  링을 지지할 것이다. 일반적으로, 각 행의 M 버스 라인 및 각 서브 소자 스트링에 대한 N 텁에 있어, 최대 K개의 시스템 채널이 지지될 수 있고,  $K = M \times N$ 이다. 물론, 링의 대부분의 단면은 수평으로도 수직으로도 완전치 않다. 따라서, 시스템 설계자의 작업은 아키텍처 제한 하에서 개구의 모든 지점에서 어레이 구성을 최적화하는 것이다.

[0094] 서브 소자와 시스템 채널 사이의 특정 원하는 매핑이 주어지면, 그 매핑을 제공하거나 거의 제공하는 최적 스위칭 네트워크 구성을 결정하는 것이 목적이다. 원하는 매핑과 정확히 일치하는 구성이 존재하지 않을 수 있다. 이것은 소정 설계의 유연성에 의존하며, 유연성은 버스 라인의 수 및 액세스 스위치의 수에 의해 제어된다. 원하는 매핑이 구성될 수 없는 경우에, 근접 추정치가 선택되어야 한다. 재구성 가능성의 모자이크 환상 버전에 있어서, 더 가능한 상황은 원하는 서브 소자 대 채널 매핑을 제공하는 다수 구성이 존재할 것이라는 것이다. 또한, 원하는 매핑이 정확히 구성될 수 없는 경우를 위한 다수 근사 구성이 존재할 수 있다. 이러한 경우, 다수 구성이 동일한 서브 소자 대 시스템 채널 매핑을 제공하며, 지연 및 크기 성능의 관점에서 다른 것보다 바람직할 것이다. 여기에 제공되는 본 발명의 한 측면은 더 나은 성능을 갖는 구성을 선택하여 이미징 시스템의 성

능을 개선하기 위해 최적화 절차를 사용하는 것을 포함한다.

[0095] 시스템 채널과 소정 서브 소자 사이의 접속은 복잡할 수 있다. 스위치 네트워크 구성은 서브 소자와 시스템 채널들 사이의 복잡한 접속망을 규정한다. 그 결과는 서브 소자로부터 시스템 채널로 간단한 저속이 존재하지 않으나 복잡한 지연 라인 구조를 구성하는 일련의 스위치(액세스 및 매트릭스 양자)를 통한 접속이 존재한다는 것이다. 송신시, 동일한 시스템 채널에 접속되는 신호는 동일한 송신 펄스를 동시에 참조하여야 한다. 하지만, 실제로는 스위치 네트워크는 신호를 지연시키고 각 서브 소자의 펄스의 크기 및 형상을 변경하고, 각 서브 소자는 시스템 송신기로의 상이한 경로를 참조한다.

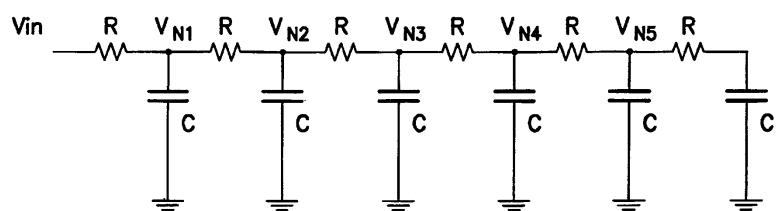

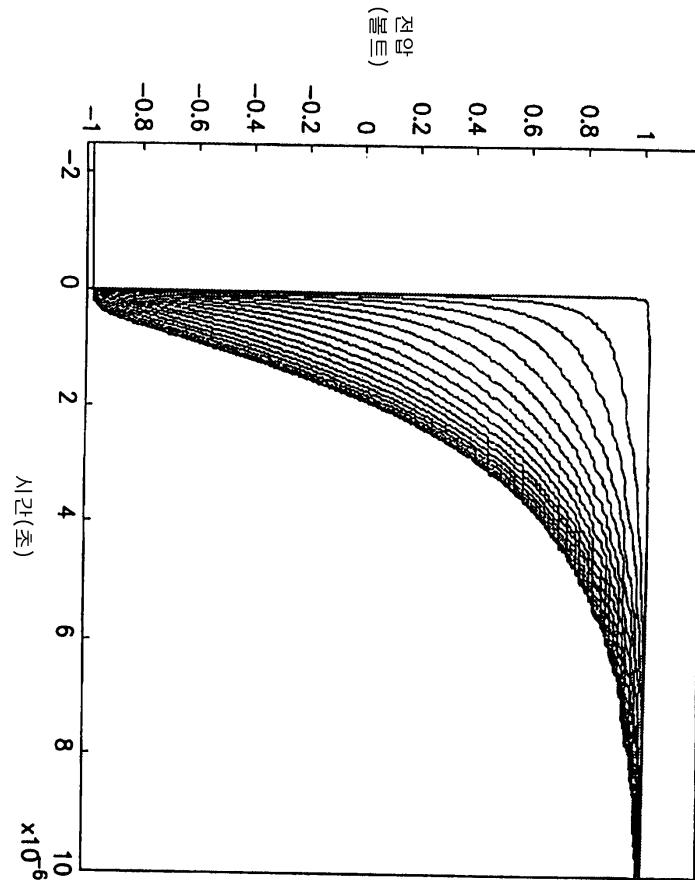

[0096] 지연 라인의 간단한 시뮬레이션은 얼마만큼 지연이 제공될 것이며 어떻게 펄스가 왜곡될지에 관한 사상을 얻는데 사용될 수 있다. 변환기 어레이 및 그 관련 스위치 매트릭스는 분배형 저항 및 캐패시턴스 네트워크로서 모델될 수 있다. 신호는 네트워크의 단위 저항 및 캐패시턴스에 관련되는 지연 시간으로 이 네트워크를 통해 전파된다. 이러한 네트워크의 간단한 예는 도 20에 도시된 바와 같은 1차원 RC 지연 라인이다. 이 네트워크에서, 입력부로부터 전파되는 신호는 도시된 바와 같은 저항 R과 캐패시턴스 C의 함수인 지연을 초래한다. 네트워크의 각 노드 또는 템에서 과형은 상이하게 형성되는데, 입력 신호에 대한 상이한 양의 지연을 초래했기 때문이다. 유한 RC 지연 라인의 최악의 경우 지연은  $RCN^2/2$ 로 변하도록 도시되는데, 여기서 N은 지연 하인의 템 수이다. 도 21은 도 20에 도시된 네트워크에 유사한 20-템 RC 지연 라인에 대해 측정되는 데이터를 도시하고 있다. 그레프는 좌측에서 우측으로 증가하는 템 번호를 갖는 지연 라인의 각 템에서 측정되는 곡선 부류를 도시한다. 이 그레프는 네트워크를 통하여 진행하는 전압 과형의 왜곡을 분명히 도시하고 있다. 최악의 경우 지연(스테핑 입력으로부터 출력 중간점으로부터의 시간으로 정의됨)은  $RCN^2/2$ 에 의해 근사하게 보여지는데, 이 실험에서는 대략 23マイ크로초이다. 따라서, 재구성 가능한 초음파 어레이의 설계를 위한 우수한 규칙은,  $RCN^2/2$ 가 시스템에서 허용될 수 있는 최악의 경우 지연보다 항상 작게 변환기 캐패시턴스 및 스위치 온 저항을 설계하는 것이다. 이 경우, 임의의 소정 결오에서 허용되는 템(또는 스위치)의 수 N은 시스템 이미징 요구 사항 및 네트워크의 RC 시간 상수에 의해 제한된다.

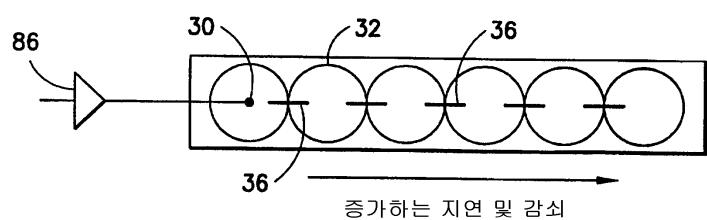

[0097] 상술한 결과는 특정 서브 소자의 지연은 신호가 얼마나 많은 수의 스위치를 통과하고 얼마나 많은 수의 경로를 이동해야 하며 어떻게 다수 접속이 분배되는지에 의존한다는 것을 증명한다. 사용되는 특정 개구에 의존하여 상이한 지연 패턴을 참조하는 것을 예상할 수 있다. 추가적으로, 시뮬레이션 및 연속적인 근사값을 통해 감소된 지연을 위한 개선된 액세스 스위치 배치에 도달할 수 있다. 도 22는 어떻게 지연이 서브 소자 형태에 따라 변하는가를 도시한다. 이 예의 아이템(86)은 구동기를 표현하지만, 도면의 나머지는 개개의 매트릭스 스위치(36)에 의해 (선형 소자를 형성하기 위한) 직렬로 접속되는 서브 소자(32) 행을 도시한다. 행의 제 1 서브 소자는 구동기(86)에 접속된다. 첫 번째 순서를 위해, 지연 라인의 신호 전파는 점 열원으로부터 열 확산으로서 고려될 수 있다. 이 분석을 염두에 두고, 도 22는 지연 및 감쇠가 강제 노드 또는 액세스 스위치(30)로부터의 거리가 증가함에 따라 2차원으로 증가하는 것을 도시하고 있다.

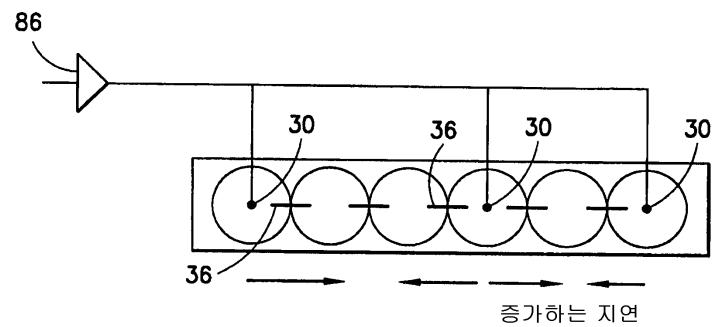

[0098] 개구의 모든 서브 소자에 대해 신호 왜곡을 감소시키기 위해, 최대한 균일하고 최대한 조밀하게 액세스 스위치를 분배하는 것이 최선이라는 것이 명백하다. 구체적으로, 스위치는, 도 23에 도시된 바와 같은 장기간 매트릭스 스위치 접속의 양쪽 끝부분에 접속되는 개개의 상이한 액세스 스위치(30)가 존재하는 것을 보장하도록 구성될 수 있다. 도시된 선형 소자를 사용하여, 선형 소자의 양쪽 끝부분에 액세스 스위치(30)를 배치하여 상당한 개선점을 달성할 수 있는데, 특히 선형 소자를 따라 매트릭스 스위치에 의해 모든 서브 소자가 접속되어 선형 소자의 한쪽 끝부분으로부터 다른 소자로의 연속적인 경로가 존재하는 경우에 탁월하다. 연속적으로 접속되는 선형 소자의 양쪽 끝부분을 접속하여 달성되는 개선점은 동일한 소자를 고유 액세스 스위치 접속을 갖는 2개의 더 짧은 소자로 분할하여 달성될 개선점보다 크다. 도 24에 도시된 바와 같이, 액세스 스위치(30)가 소자 내에서 분배될 때 더 개선된다.

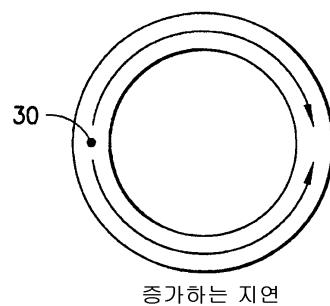

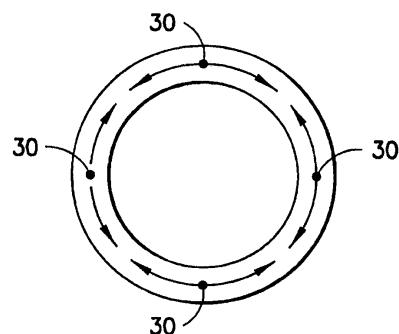

[0099] 환상 어레이의 경우, 가장 간단한 아키텍처는 도 25에 도시된 것일 것이다. 여기서, 단일 액세스 스위치(30)는 서브 소자의 전체 링에 접속되고(개개의 서브 소자는 도시되지 않음), 각 서브 소자는 매트릭스 스위치(도시 생략)에 의해 함께 접속된다. 단 하나의 액세스 스위치를 요구하기 때문에 구현하기 간단하지만, 이 아키텍처는 매트릭스 스위치의 사이즈에 의존하여 상당한 지연을 초래한다. 따라서, 다수 액세스 스위치가 도 26에 도시된 바와 같이 전체 링에 접속될 수 있고, 개개의 링 단면을 구성하기 위해 액세스 스위치(30)를 구비하는 서브 소자(도시 생략됨) 사이의 매트릭스 스위치를 구비한다. 이러한 액세스 스위치는 스위치들 사이의 서브 소자에 대한 신호 지연을 감소시키기 위해 링 주위에 거리를 두고 동일한 거리로 분배될 것이다. 이 방식에서, 다수 중복 매트릭스 스위치 접속은 직렬 저항을 감소시켜서 지연을 감소시키기 위해 단일 링을 구성하도록 사용될 수

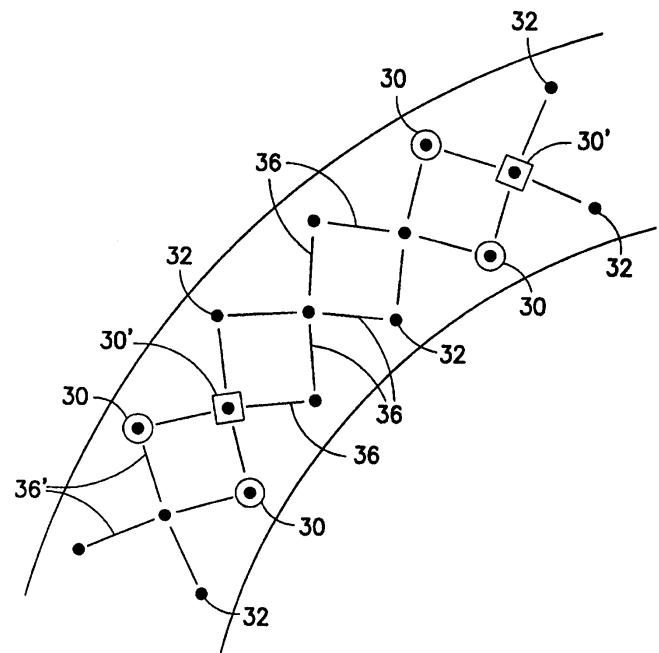

있다. 도 27에 도시된 바와 같이, 액세스 스위치는 오직 하나의 액세스 스위치가 사용되는 경우에는 링 내부의 지연을 최소화하고자 링의 양쪽 에지로부터 등거리에 존재하도록 선택될 수 있다. 링의 에지는 링의 내측 및 외측 주변 경계 부근의 서브 소자를 지칭한다. 이 방식에서, 링 내부의 지연 패턴이 개선된다. 다수 액세스 스위치가 링의 폭에 걸쳐 사용되는 경우, 2차원 스위치 거리를 최소화하여 지연 패턴을 개선하기 위해 링의 내측 및 외측 주변에 배치되어야 한다. 도 28은 이러한 경우를 도시한다. 원으로 둘러싸인 점들(30)은 서브 소자(개개의 서브 소자는 도시되지 않음)의 각 링의 내측 및 외측 주변 부근에 쌍으로 배열되는 액세스 스위치를 표현한다. 링의 에지에 위치되는 액세스 스위치(30)를 사용하여 신호는 양방향으로 구동되고 전체 에러는 감소된다. 또한, 도 28은 링의 중심(즉, 링의 내측 및 외측 주변 경계 사이의 중간지점)에 위치되는 정사각형 내의 액세스 스위치(30)를 도시한다. 이것은 액세스 스위치가 양쪽 에지로부터 링을 구동하지 않기 때문에 더 큰 에러를 초래한다.

[0100] 본 아키텍처는 모자이크 환상 어레이 개념을 목표로 하지만, 링이 아닌 패턴도 여전히 지연을 최소화하는 액세스 스위치 배치를 선택하여 구성될 수 있다는 것이 당업자에게 자명할 것이다. 따라서, 여기서 설명되는 발명은 페이즈드(phased) 어레이, 선형 및 2차원 어레이를 포함하는 다른 유형의 이미징에 직접적으로 적용 가능하다.

[0101] 본 발명의 방법은 복잡한 스위칭 네트워크에 의해 도입되는 에러를 최소화하는 스위칭 구성을 선택하기 위해 사용될 수 있다. 목적은 빔형성이 최소로 손상되는 방식으로 에러를 감소시키는 것이다. 이것이 완수될 수 있는 여러 방식이 존재한다. 이 목적을 완수하려는 알고리즘의 몇몇 특정 구현이 이하 제공된다. 이러한 구현은 본 발명을 제한하는 것이 아니라 이러한 알고리즘의 잠재성을 예시하기 위해 사용된다.

[0102] 가령, 시스템의 전체 모델이 사용 가능한 경우, 그 모델은 스위치 네트워크에 대한 최선의 구성을 결정하기 위해 사용될 수 있다. 이것은 어떤 랜덤 또는 세미랜덤 프로세스를 통해 스위칭 구성을 생성함으로써 완수될 수 있다. 스위치 구성을 모델로의 입력이다. 모델은 모든 스위칭 네트워크 에러를 고려하여 시스템의 응답을 계산한다. 이미지 또는 복사 패턴의 일부는 모델을 사용하여 생성될 수 있고 어떤 기준 또는 비용 함수가 이 데이터에 근거하여 계산된다. 비용 함수의 결과는 구성을 수정하는 데 사용된다. 반복적 알고리즘이 생성되고, 비용 함수를 시험하고 최소화하기 위해 시뮬레이션된 어닐링 또는 어떤 다른 계산 방법이 사용된다.

[0103] 계산된 수치는 선택된 모델의 복잡도와 최소화되도록 선택된 특정 비용 함수에 의존한다. 완전한 모델은 소정 특정 스위칭 구성 및 입력 여기의 정면에서 음향 출력(공간과 시간의 함수로서의 압력)을 계산할 수 있을 것이다. 이러한 모델은 스위칭 네트워크의 효과와 개개의 변환기 셀의 응답을 포함할 필요가 있을 것이다. 음향 출력이 제공되면, 평가될 수 있는 많은 비용 함수가 존재한다. 예컨대 최종 복사 패턴의 빔폭은 최소화되는 동시에 패턴의 사이드로브 레벨을 최소화한다. 이 경우, 모델은 빔폭 및 사이드로브 레벨을 계산할 필요가 있을 것이다.

[0104] 다른 방법으로, 하드웨어가 이용 가능한 경우, 이 최소화 프로세스는 실제 하드웨어를 사용하여 행해질 수 있다. 이 경우에 구성이 생성되어 시스템 제어기에 응용될 것이다. 이미지가 구성되거나 간단한 데이터가 얻어질 것이다. 다시 비용 함수는 이 데이터에 근거하고 구성을 수정하는 데 사용될 것이다. 하지만, 이 경우에 모델링은 포함되지 않는다. 또한, 스위칭 어레이를 일치시키도록 설계되는 프로브 어레이를 사용하여 하위 CMOS 전자 소자에 직접적으로 전압 측정하여 성능을 평가할 수 있다. 여기서 스위칭 네트워크가 프로그램될 수 있는 속도와 데이터가 수집되고 처리될 수 있는 속도는 관찰될 수 있는 구성의 수를 제한한다. 하지만, 이 수는 아마도 상당히 클 것이고 이것은 이미지 형성 없이 실제 응답을 결정하는 좋은 방법일 수 있다.

[0105] 어떤 경우에는, 스위칭 형태 에러 모두를 포함하는 시스템의 음향 응답의 전체 모델링은 난해하며 계산적으로 비싸다. 또한, 동작 하드웨어 원형은 구성에 데이터를 수집하는 데 사용하기 위해 이용 가능할 수 있다. 하드웨어가 이용 가능한 경우, 많은 구성을 위해 데이터를 수집하고 처리하기 위해 요구되는 시간이 클 것이다. 그래서, 이 유형의 알고리즘을 사용하는 효율성을 결정하기 위해, 네트워크가 어떻게 음향 응답에 영향을 미칠 수 있는지에 대한 직감과 이해에 근거하여, 매우 신속하게 많은 구성을 평가하게 하는 더 간단한 모델이 채택될 수 있다. 예컨대, 신호가 통과해야 하는 스위치 수가 많은 수록 도입될 지연 및 왜곡이 많다.

[0106] 첫 번째 순서로, 스위칭 네트워크를 시험하고 배열하는 좋은 방법은 접속과 서브 소자 사이의 거리가 최대한 작도록 하는 것이다. 여기서, 접속은 액세스 스위치로서 규정되고, 스위치를 갖는 서브 소자를 특정 채널에 대한 행 버스 라인에 직접적으로 접속시킨다. 그리고 거리는 음향 서브 소자로부터 행 버스 라인으로 얻기 위해 신호가 통과해야 하는 스위치의 수를 지칭한다. 게다가, 접속되는 액세스 스위치는 어떤 서브 소자에 대해 매우 장기간을 희생하여 로컬 짧은 거리를 방지하기 위해 최대한 많이 확산되어야 한다. 그래서 단순화된 모델은 구

성의 성능에 대한 메트릭(metrics)으로서 신호가 이동해야 하는 매트릭스 스위치의 수를 사용한다. 이것은 전체적으로 정확하지 않지만, 이 간단한 모델은 시뮬레이션에서 스위칭 네트워크 성능을 개선하는 것으로 보여졌다. 이것은 2차원 현상이 1차원 메트릭으로 모델링된다는 사실을 무시한다.

- [0107] 여기에 개시된 특정 재구성 가능성 구현에 있어, 전자소자에 의하여 부과되는 제한이 존재한다. 시스템에 대한 스위칭 구성을 관리하는 규칙 세트가 있다. 하드 규칙 외에도, 음향 서브 소자와 접속점 사이의 거리를 감소시키는 것과 같은 지도 원리가 있다. 이 규칙은 준수되어야 하며 지도 원리는 성능을 개선하기 위해 사용될 수 있다. 규칙은 이하와 같다.

- [0108] [1] 각 행은 "n" 행 버스 라인을 가진다. 여기에 개시된 예에 있어서,  $n=4$ 이다. 이는 전체 행에 대해 액세스 스위치가 접속할 수 있는 오직 네 개의 시스템 채널 버스 라인이 존재한다는 것을 의미한다.

- [0109] [2] 행의 각 서브 소자는  $n$  행 버스 라인 중 오직 하나에만 접속한다. 이것은 서브 소자에 오직 하나의 액세스 스위치가 존재한다는 사실로부터 이어진다. 또한, 이것은 소정 서브 소자가 단일 시스템 채널에만 직접적으로 접속될 수 있고, 시스템 채널 버스 라인과 행 버스 라인 사이의 멀티플렉서에 의해 채널이 결정된다는 것을 의미한다.

- [0110] [3] 각 행 버스 라인은 단일 시스템 채널 버스 라인에 접속된다. 시스템 채널 버스 라인은 행 버스 라인으로 멀티플렉싱되고, 이 접속은 소정 구성에 대해 변경될 수 없다.

- [0111] [4] 어떤 행 버스 라인이 소정 액세스 스위치에 접속되는 패턴은 행에 걸쳐 반복된다. 여기에 설명한 경우에 있어서, 패턴은 네 개의 서브 소자마다 반복한다.

- [0112] [5] 소정 회로 구현에 있어서, 동일한 행 버스 라인에 접속되는 액세스 스위치의 총 수는 작은 유한 수이다. 이 명세서에서 추후에 설명할 특별한 경우, 제한은 4이다. 이것은 행 버스 라인의 제한된 사이즈에 의해 부과되는 현재 도면 제한으로부터 얻어진다. 이 제한은 시뮬레이션에 근거하며 행 버스 라인의 사이즈를 증가하여 증가될 수 있고 더 큰 현재 도면이 가능하지만 이것은 더 큰 서브 소자를 요구할 수 있다.

- [0113] 지도 원리를 상술하였지만, 보다 구체적으로 이하 설명할 것이다. 본 발명의 일실시예에 따라, 스위칭 네트워크에 의해 도입되는 지역 예러를 최소화하는 것이 목적이다. 이것은 접속점으로부터 서브 소자로 최대한 작은 거리를 유지하여 수행될 수 있다. 그와 관련하여, 접속점은 액세스 스위치가 턴 온되는 서브 소자이다. 게다가, 접속점은 균등하게 분배되는 것이 더 양호하다.

- [0114] 스위칭 네트워크 구성을 결정하는 단계는 어떤 액세스 스위치가 턴 온되고 행 버스 라인들 사이의 멀티플렉서 (도 13에 부분적으로 도시된 멀티플렉서 스위치의 뱅크를 의미함) 및 시스템 채널 버스 라인이 설정되는지를 결정하는 단계를 수반한다. 일단 원하는 패턴이 알려지면 매트릭스 스위치 상태는 쉽게 결정한다. 매트릭스 스위치는 스위치가 접속할 이웃 서브 소자가 동일한 시스템 채널상에 존재해야 하는지를 간단히 결정하여 설정된다. 그래서, 그 작업은 시스템 채널을 멀티플렉싱된 행 버스 라인에 어떻게 접속할지를 결정한다. 일단 이것이 알려지면, 액세스 스위치도 할당하기 쉽다.

- [0115] 최적 스위치 구성을 결정하는 것은 더욱 난해하다. 시작을 위해, 스위치 할당을 위한 간단한 알고리즘 접근 방안이 개발되었다. 알고리즘은 생각 속의 규칙의 일부와 지도 원리를 사용하여 설계되었지만 최적의 해결 방안은 아니고, 기준을 정하기 위한 해결 방안일 뿐이다. 구해진 해결 방안은 특정 원하는 구성에 근거한다. 한 예에서는, 원하는 구성은 20-링, 동일 폭 환상 어레이였다. 알고리즘은 이하와 같다.

- [0116] 어레이의 한 예지에서 시작하여, 어레이를 거쳐 행으로부터 행으로 동작한다. 각 행과 그 행의 각 버스 라인에 대해 동작한다.

- [0117] [1] 소정 행 버스 라인에 대해 어떤 링(즉, 어떤 시스템 채널)이 가능한가를 결정한다. 가령, 어레이의 상부 부근에는 오직 외측 소자가 제공될 수 있다. 그 경우에 오직 하나의 링만 가능하다. 중심으로 이동함에 따라 링의 모두가 제공되나, 소정 행 버스에 대해 오직 링 일부가 가능할 것이다.

- [0118] [2] 각 링에 대해, 멀티플렉서가 행 버스 라인을 그 링에 대응하는 시스템 채널로 설정하는 경우, 많은 액세스 스위치가 어떻게 소정 행 버스 라인에 대해 턴 온될 수 있는지를 결정한다.

- [0119] [3] 행 버스 라인을 최대 액세스 스위치가 턴 온되게 하는 링으로 행 버스 라인을 할당한다. 하지만, 이것은 이하의 제한을 따라 행해져야 한다.

- [0120] [a] 동일한 링은 한 행의 하나 이상의 버스 라인에 할당될 수 없다.

- [0121] [b] 동일한 링은 과거 네 개의 행에 이미 할당된 경우에는 할당될 수 없다.

- [0122] 어떤 경우에 조건 [b]를 충족할 수 없고 여전히 링을 특정 행 버스 라인에 할당한다. 가령, 오직 세 개의 링이 특정 행 버스 라인에 할당될 후보이지만 이 세 개의 링은 이전 세 개의 행 버스 라인에 할당된 경우, 이 특정 행 버스 라인에 할당될 수 있는 링은 존재하지 않을 것이다. 이 경우 및 조건 [b]가 행 버스 라인이 임의의 링으로 할당되는 것을 막는 모든 경우, 제한 조건은 제거되어야 한다. 이 알고리즘에 있어, 제한 조건은 알고리즘의 의도가 최소로 방해하는 방식으로 제거될 수 있다. 그래서 조건 [b]가 충족될 수 없는 경우, 가장 먼 행으로부터 시작해서 하나씩 행의 제한을 제거한다. 그래서 [b]가 충족될 수 없으면, 네 번째 이전 행 버스 라인에 할당된 동일한 링으로 행 버스 라인 할당을 허용한다. 이것이 여전히 할당을 허용하지 않는 경우, 세 번째 이전 행 버스와 동일한 것에 행 버스 라인 할당을 허용하며, 행 버스 라인이 할당될 수 있을 때까지 행해진다.

- [0123] 상술한 알고리즘은 특정 원하는 링 구조에 대해 멀티플렉서 및 액세스 스위치 세팅을 할당하는 데 사용될 수 있다. 액티브 액세스 스위치의 수를 최소화 하기 때문에, 접속점과 서브 소자 사이의 거리를 감소시키는 것을 돋는다. 이 알고리즘은 유용한 기준이다.

- [0124] 소정 스위칭 네트워크 구성에서, 그 구성이 이미징 상황에서 어떻게 효율적으로 존재하는지를 결정하는 것은 사소한 것이 아니다. 하나의 구성이 다른 것보다 우수한지를 결정하는 데 사용되어야 하는 궁극적인 황금 표준은 그러한 구성이 생성하는 화질이다. 하지만, 동작 원형의 부재 시, 이것은 거의 불가능하다. 또한, 화질을 결정하는 것은 동작 원형을 사용하더라도 난해한 메트릭이고, 이것은 이것이 요구할 수 있는 시간 및 노력으로 인해 모든 가능한 구성을 스크린 아웃하는 데 사용될 수 없다. 소정 특정 구성에서, 전자소자의 완전한 컴퓨터 모델을 사용하여 빔 프로파일을 시뮬레이션할 수 있다. 하지만, 이 시뮬레이션은 매우 시간 소모적이며 큰 스크린 프로세스가 아닌 오직 소수의 구성을 위해 보존되어야 한다. 또한, 단순화된 전기적 모델을 사용하여 오직 지연 및 크기 변경만을 시뮬레이션할 수 있으나 이것은 다시 요구되는 입력의 큰 수를 스크린하기 위해 원하는 것보다 많은 시간이 소모된다. 약간 빠른 방법은 지연을 추정하기 위해 단순화된 식을 사용하고 더 간단한 빔형성기 모델을 사용하는 것이나, 이것은 여전히 많은 가능한 구성의 상당한 스크린을 허용할 매우 빠른 시뮬레이션이다.

- [0125] 많은 구성의 매우 신속한 평가를 허용하는 방법은 서브 소자로부터 접속점으로의 거리로부터의 지연 결과에 관한 주요 효과를 가정하는 것이다. 각 서브 소자부터 가장 근접한 접속점으로의 거리를 계산하는 것은 루프 테이블을 사용하여 매우 신속하게 구성될 수 있다. 이것은 반복적 알고리즘이 다수의 구성을 통해 검색할 수 있도록 설계되게 한다. 본 발명은 이 구현에 제한되지 않으며, 이 평가 속도는 최적화의 실제적 사용을 허용하는 중요한 장점이다.

- [0126] 이미 설명한 스위치 구성을 결정하는 간단한 방법에 비해 지연 예상의 현저한 개선을 유도하는 반복적 알고리즘이 개발되었다. 알고리즘은 이하와 같이 동작한다.

- [0127] [1] 초기 구성이 주어진다. 한 경우에, 간단한 알고리즘의 출력이 사용되었다. 이것은 또한 랜덤 구성일 수 있다.

- [0128] [2] 특정 구조를 위해, 루프 테이블(LUT)이 생성된다. 이 LUT는 링의 임의의 서브 소자로부터 그 링의 임의의 다른 서브 소자로의 스위치의 거리를 제공한다. LUT의 계산 속도를 개선하기 위해 최대 거리보다 큰 임의의 거리가 임계값보다 크게 표시되도록 어떤 최대 거리가 사용되며 계산되지 않는다.

- [0129] [3] 지금의 구성에 있어, 알고리즘은 이하를 행한다.

- [0130] [a] LUT을 사용하여, 각 서브 소자로부터 가장 근접한 접속점으로 거리(스위치의 수)를 계산한다.

- [0131] [b] 거리를 분류하고 M개의 최악의 거리(즉, 가장 먼 거리)를 갖는 서브 소자를 유지한다. 한 경우에, M=10이고, 열 개의 최악 거리가 보유되었다.

- [0132] [c] M개의 최악의 거리 중 하나를 갖는 서브 소자들 중 하나를 랜덤 선택한다. 이 경우에, 1과 10 사이의 랜덤 정수가 서브 소자 선택을 위해 생성되었다.

- [0133] [d] 랜덤 선택된 서브 소자에 대한 액세스 스위치를 턴 온한다. 이것은 다른 액세스 스위치를 턴 오프하고 시스템 채널 버스 라인과 그 서브 소자의 행의 행 버스 라인 사이의 멀티플렉서를 변경하는 것을 포함할 것이다.

- [0134] [e] 이 새로운 생성된 구성을 위해 전체적 비용 함수를 평가한다. 사용된 특정 비용 함수는 임계값보다 큰 스위치 거리를 갖는 서브 소자의 수이다. 스위치의 단일 하인을 갖는 어떤 시뮬레이션에 근거하여, 사용된 임계

값은 4이다.

[0135] [f] 비용 함수가 변경되지 않는 구성의 비용 함수보다 작은 경우, 새로운 구성이 지금의 최선으로서 채택된다.

[0136] [g] 비용 함수가 변경된 스위치와 더 큰 경우, 그것은 여전히 유지될 수 있다. 이것은 시뮬레이션된 어닐링 유형의 알고리즘이다. 온도 함수가 규정되고 느린 많은 반복을 걸쳐 온도가 감소된다. 최초로, 온도 함수는 높고 더 큰 비용 함수에도 불구하고 구성의 유지하려는 가능성이 더 커진다. 반복 회수에 증가함에 따라, 온도가 낮춰지고 열등한 구성의 유지할 확률이 감소된다. 이 유형의 알고리즘은 시스템이 로컬 최소값을 점프 아웃하게 하고 보다 우수한(아마도 전체적이지 않음) 최소값을 발견할 기회를 제공한다.

[0137] [h] 이 과정은 어떤 소정 반복 횟수 또는 모든 거리가 임계값 아래가 될 때까지 반복된다.

[0138] 시뮬레이션된 어닐링은 가능한 세팅의 소모적인 검색이 가능하지 않을 때 수치 선택을 최적화하는 잘 알려진 계산적인 방법이다. 어닐링은 금속 결정이 냉각되는 물리적 과정을 지칭한다. 이 냉각 과정의 마지막 상태는 사물이 냉각되는 속도에 의존한다. 냉각이 매우 느린 속도로 발생하는 경우 시스템은 최소 에너지 상태에 도달할 수 있다. 사물은 매우 신속히 냉각되며, 에너지의 오직 부분적 최소값만 완수된다. 시뮬레이션된 어닐링은 냉각 과정을 모방하는 수학적 알고리즘이다. 연구하고자 하는 과정에 대한 비용 함수가 규정되고 시뮬레이션된 어닐링 알고리즘은 이 비용 함수를 최소화하려 한다. 여기서 비용 함수는 어닐링의 물리적 과정의 에너지와 유사하다. 시뮬레이션된 어닐링 알고리즘은 특정 구성으로 시작한다. 구성에 대한 랜덤 변경이 가해진다(즉, 수치의 랜덤 변경이 가해진다). 이러한 변경은 어떤 법칙 또는 규칙을 따를 필요가 있을 수 있다. 구성에서 변경이 가해진 후, 비용 함수가 다시 평가된다. 비용 함수가 감소되는 경우, 구성은 새로운 구성으로 변경된다. 비용 함수가 더 높은 경우, 구성은 어떤 랜덤 변수의 값에 의존하여 변경되거나 되지 않을 수 있다. 알고리즘이 진행됨에 따라 더 높은 비용 구성이 유지될 가능성이 감소된다. 하지만 더 높은 비용 구성이 발생하게 하여, 알고리즘은 부분적 최소값을 피하고 더 절대 최소값에 근접할 수 있다. 더 높은 비용 구성이 유지될 확률은 최초에 높으며 알고리즘이 진행함에 따라 감소된다. 이 확률은 물리적 어닐링의 온도에 유사하다. 확률이 떨어지는 비율은 알고리즘의 속도를 결정한다. 비율이 높으면 응답은 신속히 오지만 참 최소값 부근이 아닐 수 있다. 비율이 낮으면 응답은 오래 걸리지만 최소값에 더 가깝다.

[0139] 스위칭 구성은 모자이크 환상 어레이에 대한 간단한 알고리즘을 사용하여 결정되었다. 간단한 알고리즘에 있어, 7015 서브 소자 중 172가 네 개의 스위치보다 큰 거리를 갖는다. 이것은 서브 소자의 97.5%이 상이 임계값 미만임을 의미한다. 이 구성은 반복적 알고리즘으로의 입력으로 사용하여, 새로운 스위칭 구성이 결정되었다. 이 경우에 7015 서브 소자 중 오직 12만이 접속점으로 이동하는 네 개의 스위치를 가졌는데, 즉, 소자의 99.8% 이상이 임계값 미만이었다. 임계값 기준을 충족하지 못한 12 서브 소자는 모두 다섯 개의 스위치 거리에 존재하였다. 이것은 172로부터 12로의 임계값 기준을 충족하지 않는 서브 소자를 감소시켜서 간단한 알고리즘에 대한 개선점을 보여준다. 하지만, 반복적 알고리즘은 시스템을 행 버스 라인당 네 개의 액티브 액세스 스위치로 제한하는 규칙을 고려하지 않는다. 추가적 처리 스템은 추가 스위치를 제거하는 데 사용되었다. 이 과정은 평균 거리의 증가를 최소화하려는 방식으로 그들을 제거한다. 추가 스위치가 제거된 결과는 간단한 알고리즘에 비한 상당한 개선점이었다. 추가 스위치의 대부분은 상부 및 하부 부근에서 제거되었는데, 접속 밀도가 크고 손실이 거의 없는 곳이다.

[0140] 거리는 전자소자 시뮬레이션으로부터 유도되는 실제 지연에 비교되었다. 반복적 알고리즘을 사용하여 스위칭 구성을 생성하고, 단순화된 모델 및 전자소자 시뮬레이션 소프트웨어(가령, HSPICE)를 사용하여 지연을 시뮬레이션할 수 있다. 이것은 지연 문제의 2차원 성질을 더 정확하게 반영하며, 계산 속도를 위해 단일 스칼라(scalar)로 감소되었다. 상업용 전자소자 시뮬레이션 패키지를 사용하는 동일한 스위치 구성에 대한 지연의 시뮬레이션의 결과는 실제 지연의 피크가 (최적화를 위해 사용된) 거리 메트릭의 피크에서 항상 발생했다는 것이다. 이것은 거리 메트릭이 최적화를 위해 사용하기에 우수한 메트릭이라는 사실을 증명한다. 하지만, 지연에 대응 피크를 갖지 않은 거리 메트릭의 어떤 피크가 존재하였다. 이것은 지연의 2차원 성질 대 거리 메트릭의 1차원 성질에 관한 문제이다.

[0141] 상술한 스위치 매트릭 구현은 반복적 알고리즘의 출력이었다. 하지만, 결과는 상이한 실행에 대래 상이할 수 있고 또한 사용되는 온도 수치 및 임계값과 비용함수에도 의존한다. 더 긴 최적화 시간으로 지금의 설계를 개선할 수 있다. 또한, 이것은 에러를 최소화하기 위한 오직 예시적 알고리즘이라는 것을 주목해야 한다. 성능 개선을 위하여 다른 것들도 사용될 수 있다.

[0142] 선형 스캔을 구성하기 위해, 모자이크 환상 어레이의 액티브 개구는 하위 2차원 어레이를 지나 스템되어야 한

다. 이 스텝핑 단계는 스위칭 네트워크가 재구성될 것을 요구한다. 이 스텝핑 단계가 수행될 수 있는 여러 방식이 존재한다. 어레이 해상도 및 준비된 애플리케이션의 요구사항에 의해 결정되는 바와 같이, 요구되는 빔 스페이싱이 전체 서브 소자가 수용 가능하도록 되면, 스위치 구성으로부터 알고리즘적으로 유도되는 것과 동일한 것이 각 빔을 위해 사용될 수 있다. 이 경우 스위칭 구성은 각 빔에 대하여 하나 또는 여러 서브 소자에 걸쳐 간단히 스텝핑한다. 재프로그래밍 및 재구성을 위해 시스템에 의해 사용되는 전력을 최소화하기 위하여, 한 서브 소자로부터 이웃 서브 소자로 직접적으로 스위치 상태를 전달하여 전체 어레이를 외부적으로 재프로그래밍하는 것을 피할 수 있을 것이다. 하지만, 액세스 및 매트릭스 스위치 패턴을 이동하는 것에 더하여, 행 버스 라인을 시스템 채널 버스 라인에 접속하는 멀티플렉서도 변경되어야 한다. 행 버스 라인의 방향으로 전체 서브 소자에 의해 빔을 스텝핑할 때, 이 변경은 단순히 채널의 회전이다. 예컨대, 각기 A,B,C,D로 지정되는 네 개의 시스템 채널이 특정 구성에 대한 특정 행의 네 개의 행 버스 라인에 접속되면, 스위칭 패턴이 다음 빔 위치로 스캔될 때, 시스템 채널/행 멀티플렉서의 상태는, 가령, 시스템 채널 B,C,D 및 A가 동일한 네 개의 행 버스 라인에 이 순서로 각기 접속되도록 시스템 채널이 네 개의 버스 라인들 사이에서 회전하게 조절되어야 한다. 다른 방법으로, 시스템 채널과 행 버스 라인 사이의 멀티플렉싱을 변경하지 않고, 시스템 빔형성기가 구조의 변경을 직접적으로 고려하므로 네 개의 채널상의 지연을 조절하여 새로운 지연을 고려할 수 있다.

[0143] 상술한 바와 같이, 환상 링이 이동이 서브 소자의 정수 곱이 되도록 스텝핑되면, 각 빔에 대해 다시 최적화할 필요가 없다(하위 스위치 매트릭스가 전체 하위 2차원 어레이에 걸쳐 균일한 전기적 특성을 갖는다고 가정). 하지만, 원하는 빔 밀도가 단일 서브 소자보다 근접하여 함께 존재할 것을 요구하는 경우가 존재할 수 있다. 이 경우에, 빔 중심은 서브 소자의 일부 스텝핑할 수 있는데, 가령, 개구는 개구의 전체 스텝핑들 사이의 절반 스텝핑을 효율적으로 조정하기 위해 변형되어서, 이미지의 해상도를 증가시킨다. 이러한 경우에 있어서, 최적화는 간단히 이동하지 않고 새로운 최적화가 각 비율적 스텝핑에 대해 이루어져야 한다. 하지만, 이러한 비율적 스텝핑 구성은 환상 어레이가 선형 스캔을 구성하기 위해 하위 2차원 어레이에 걸쳐 스텝핑되기 때문에 재발생할 수 있다. 이러한 경우, 동일한 비율적 스텝핑이 요구될 때마다, 최적화는 동일할 것이고 재사용될 수 있다. 그래서 비유적 스텝핑의 경우 조차도, 적은 수의 최적화가 요구될 것이다. 이러한 경우, 프로그래밍 시간 및 전력 소비를 절약하기 위해, 특정 구성에 대한 모든 빔을 발사(fire)하고 조합한 빔 스페이싱으로 어레이에 걸쳐 그 구성을 스텝핑할 수 있을 것이다. 이 경우 서브 소자로부터 이웃 서브 소자로 직접적으로 구성의 전달 할 수 있을 것이다. 조합한 스캔을 완료한 후, 이전 구성으로부터의 비율적 스텝핑을 표현하는 새로운 구성이 프로그램되고 어레이에 걸쳐 스텝핑될 수 있다. 이것은 각 비율적 스텝핑에 대해 반복될 수 있다. 각 구성으로부터 결과적인 조합하게 스페이싱된 빔은 원하는 미세한 빔 스페이싱을 제공하기 위해 스캔 컨버터에 의해 개재(interleave)될 수 있다. 또한, 상이한 구성으로부터의 빔을 혼합할 때, 빔형성 이득 차이를 보상하고 이러한 상이한 구성으로부터의 라인을 섞기 위해 빔들간의 이득을 조절할 필요가 있을 것이다.

[0144] 상술한 수적인 최적화 알고리즘은 재구성 가능한 어레이의 빔형성 성능을 개선한다. 해결되는 문제점은, 재구성 가능한 어레이에 대한 단순화된 스위칭 네트워크의 경우에, 지연, 크기 변경 및 파형 왜곡이 모두 단순화된 스위칭 네트워크로 인해 발생한다는 것이다. 수적인 최적화의 사용은 에러를 최소화하고 적합한 빔형성 성능을 유지하는 것을 돋는다. 간단한 메트릭이 규정되고 다양한 구성의 성능을 특징짓는 데 사용되는 최적화의 특정 예가 연구되었다. 이 예에서 사용되는 간단한 메트릭은 소정 서브 소자와 접속된 가장 근접한 액세스 스위치 사이의 스위치 수이었다. 얻어진 결과는 이 간단한 메트릭이 만들어진 조합한 근사값에도 불구하고 스위칭 네트워크의 성능을 개선할 수 있다는 것을 보여준다. 간단한 메트릭은 또한 많은 구성이 조사될 수 있게 하는데, 이것은 성공 기회를 높인다.

[0145] 여기에 개시되는 최적화 기술은 재구성 가능한 어레이에 대한 단순화된 스위칭 네트워크를 갖는 개선된 이미징 성능을 제공한다. 지연 에러 및 왜곡의 감소는 개선된 해상도 및 콘트라스트를 포함하는 개선된 빔형성을 직접 유도한다.

[0146] 최적화 알고리즘은 충만한 또는 산재한 멀티플렉서와 사용될 수 있다. 알고리즘은 저장 시간 이전에 그 데이터를 생성하여 추후에 사용할 수 있거나 어레이 저항의 변경으로 인한 증가 개선점을 위해 이미징 중에 부분적으로 생성될 수 있다. 알고리즘은 측정되는 값으로 실제 저항 값을 사용하여 제조 시점에 이상적 저항 값을 가정하는 설계 단계에서 수행되거나 또는 시스템 연령으로서 사용되는 교정 스텝핑 또는 온도로 인한 변동을 보상하기 위해 현장에서 정기적으로(가령, 초음파 이미징 머신이 턴 온 되거나 사용 중인 모든 시점에, 교정이 필요하거나 어레이 구성이 변경될 때마다) 행해질 수 있다. 가령, 이 시스템은 온도의 소정 변경의 검출에 응답하여 자동적으로 교정될 수 있다. 또한, 제조된 cMUT 캐페시턴스의 변동도 어레이 성능에 영향을 줄 것이다. 이러한 변동은, 제조된 어레이의 모든 서브 소자에 개한 정확한 cMUT 캐페시턴스가 측정된 후에 최적화 절차를 반복

하여 계산될 수 있다.

[0147] 교정 데이터는 각 프로브에 고유하며 ROM 또는 EEPROM의 각 프로브에 저장될 수 있거나, 케이블의 데이터 링크를 통해 프로브에 다운로드되는 파일로서 이미징 시스템에 저장되어서, 프로브 자체의 RAM, EEPROM, FRAM 등에 부분적으로 저장된다. 이 데이터는 새로운 요구되는 구성 데이터를 관리하는 각 새로운 스캔으로 스캔 중에 로컬(프로브) 메모리로부터 관리될 것이다. 다른 방법으로, 교정 데이터는 시스템 사용 중에 계산되고 프로브로 다운로드될 수 있다.

[0148] 센서 소자를 버스 라인에 접속하는 액세스 및 매트릭스 스위치의 합체는 상당한 유연성을 제공한다. 본 발명의 다양한 실시예에 따라, 하나 이상의 다음 특징이 사용될 수 있다.

[0149] (1) 액세스 스위치는 소정 수의 버스 라인을 위해 요구되는 액세스 스위치의 수를 감소시키기 위해 엇갈릴 수 있다.

[0150] (2) 단일 스위치가 엇갈린 패턴의 서브 소자를 위해 사용될 수 있다.

[0151] (3) 반복 패턴으로 인한 일그러짐을 감소시키기 위해 버스 라인 매핑에 대한 액세스 스위치의 랜덤 정렬이 사용될 수 있다.

[0152] (4) 하나 이상의 액세스 스위치가 각 서브 소자에 사용될 수 있지만, 버스 라인 및 시스템 채널 수보다 적다.

[0153] (5) 교차점 스위칭 매트릭스를 사용하여 시스템 채널에 버스 라인이 접속될 수 있다.

[0154] (6) 희박한 교차점 스위치가 버스 라인을 시스템 채널에 접속하기 위해 사용될 수 있다.

[0155] (7) 장기간 매트릭스 스위치 접속의 양단에 접속되는 개개의 상이한 액세스 스위치가 존재하는 것을 보장하도록 스위치가 구성될 수 있고, 이러한 액세스 스위치는 동일한 버스 라인에 접속되어 지연을 감소시킨다.

[0156] (8) 매트릭스 스위치 세트 및 제한된 수의 액세스 스위치가 존재하는 스위칭 구성이 사용될 수 있다. 매트릭스 스위치는 이웃 서브 소자를 동적으로 접속한다. 액세스 스위치는 시스템 채널에 멀티플렉싱되는 버스 라인을 접속한다.

[0157] 본 발명의 다양한 실시예에 따라, 이하의 추가적인 특징 중 하나 이상의 시스템에 제공될 수 있다.

[0158] (1) 버스 라인당 하나의 액세스 스위치가 각 서브 소자에 사용된다.

[0159] (2) 다수의 버스 라인이 행당 사용될 수 있다.

[0160] (3) 버스 라인이 어레이 내에서 수직 및 수평적으로 배치될 수 있다. 일실시예에 따라, 버스 라인 중 한 세트가 수평적으로 배치되고 다른 세트는 수직적으로 배치되는 경우, 각 서브 소자 또는 서브 소자 그룹은 수직 버스 라인에 상이한 액세스 스위치를 통해 접속 가능할 것이고 상이한 액세스 스위치를 통해 수평적으로 버스 라인에도 접속 가능할 것이다. 하지만, 버스 라인을 위해 이용 가능한 전자적 예산이 낮게 이어지고 더 많은 버스 라인이 필요하나 서브 소자에 여전히 오직 하나의 스위치가 존재하기 때문에 버스 라인이 양방향으로 이어지는 경우에 각 서브 소자의 액세스 스위치는 수평적 버스 또는 수직적 버스에 접속되거나 어디에도 접속되지 않는다. 또한, 소정 버스 라인을 위해 턴 온될 수 있는 스위치의 수가 현재 도면 및 라인 사이즈에 의해 제한될 때 예상되는 결과를 갖는다.

[0161] (4) 액세스 스위치는 링 내부의 지연을 최소화하기 위해 링의 양쪽 에지로부터 등거리에 존재하도록 선택될 수 있다. "링의 에지"는 재구성 가능성이 환상 어레이를 균접하게 하기 위해 사용되는 경우를 지칭한다. 이 경우에 서브 소자를 접속하여 모방하기 원하는 어떤 원하는 환상 어레이 또는 링 구조가 존재한다. 링의 에지는 균접하기 원하는 링의 경계 부근의 서브 소자를 지칭하는데, 즉, 서브 소자를 접속하여 형성되는 더 큰 소자의 에지이다. 액세스 스위치는 소자의 한쪽에 모두 존재하면 안 되며 양쪽상에 존재하도록 선택되어야 한다. 형상은 링이 아닐 수 있고 다른 형상이 사용될 수 있으며 서브 소자를 접속하여 균접하게 되는 형상의 양쪽 에지상에 액세스 스위치를 가는 것이 최선이다.

[0162] (5) 버스 라인당 하나 이상의 액세스 스위치가 각 서브 소자에 사용될 수 있다. 이 중복 접속은 디바이스 산출량을 개선한다.

[0163] (6) 수신 중에 다수의 간격으로 송신 및 수신 사이의 링 패턴을 업데이트하는 기능을 제공할 수 있다.

[0164] (7) 단일 액세스 스위치가 전체 서브 소자 링에 접속될 수 있고, 각 서브 소자는 결국 매트릭스 스위치에 의해

함께 접속된다.

[0165] (8) 다수의 액세스 스위치가 전체 링에 접속될 수 있고, 서브 소자들 사이의 매트릭스 스위치는 개개의 링 단면을 형성하기 위해 액세스 스위치를 가진다.

[0166] (9) 다수의 액세스 스위치가 전체 링에 접속될 수 있고, 스위치는 스위치들 사이의 이러한 서브 소자에 대한 신호 지연을 감소시키기 위해 동일한 거리로 링 주위에 분배된다.

[0167] (10) 다수 링이 형성될 수 있고, 각 링은 하나 이상의 액세스 스위치를 사용하여 단일 시스템 채널에 접속되며, 그 각각은 버스 라인에 접속되며, 시스템 채널에 접속된다.

[0168] (11) 직렬 저항을 감소시키고 그에 의해 지연을 감소시키기 위하여 다수의 중복 매트릭스 스위치 접속이 단일 링을 구성하도록 채택될 수 있다.

[0169] (12) 매트릭스 스위치는 소정 어레이에 대한 공지의 악성 하위 소자 주위를 루팅하는 데 사용될 수 있다.

[0170] (13) 링 이외의 패턴이 구성될 수 있고 지연을 최소화하기 위해 여전히 액세스 스위치 패턴을 선택한다.

[0171] (14) 전체 링 패턴이 각 새로운 이동 스텝에서 최소 지연 알고리즘을 반복 사용하여 이동 범위 생성하기 위해 이동될 수 있다.

[0172] (15) 소자의 중심은 소자의 형상을 변경하여 전체 하위 소자보다 적은 증가량만큼 스텝될 수 있다.

[0173] 스위칭 전자소자는 아직 정의되지 않은 스위칭 기술로서 CMOS 또는 BiCMOS 또는 SOI 또는 MEMS 또는 기타를 사용하여 구성될 수 있다.

[0174] 바람직한 실시예를 참조하여 본 발명을 설명하였으나, 본 발명을 범주를 벗어나지 않고 여러 변경이 가능하며 등가물이 대체될 수 있다는 것은 당업자에게 자명하다. 게다가, 본 발명의 핵심적 범주를 벗어나지 않고 본 발명의 교시에 특정 상황을 적용시키기 위해 많은 수정이 가능할 수 있다. 따라서, 본 발명은 이를 실시하기 위한 최적 모드로 개시된 특정 실시예에 한정되는 것이 아니라 첨부된 청구범위의 범주 내의 모든 실시예를 포함하는 것으로 의도된다.

### 도면의 간단한 설명

[0024] 도 1은 통상적 cMUT 셀의 단면도를 도시하는 도면이다.

[0025] 도 2는 간접 스위치 없이 함께 각각 접속되는 상부 전극 및 하부 전극을 구비한 7개의 육각형 MUT로부터 형성되는 "데이지" 서브 소자를 도시하는 도면이다. 이 도면은 미국 특허 No. 10/383,990로부터 얻어진다. 제 1 선택된 초음파 변환기 소자 세트를 포함하는 제 1 개구를 설치하는 제 1 스위칭 구성을 최적화하는 단계와,

[0026] 도 3은 미국 특허 No. 10/383,990에 개시된 4개의 환상 소자를 포함하는 모자이크 어레이 섹터를 도시하는 도면으로서, 각 소자는 대략 동일한 소자당 면적을 갖도록 구성되는 "데이지" 서브 소자의 모자이크 세공으로 구성된다.

[0027] 도 4는 함께 접적되는 cMUT 및 주문형 접적 회로(ASIC) 어레이의 단면도를 도시하는 도면이다.

[0028] 도 5는 ASIC 스위치 매트릭스에 접속되는 cMUT 웨이퍼의 단면도를 도시하는 도면이다.

[0029] 도 6은 관련 단위 스위치 셀의 육각형 어레이 꼭대기의 육각형 cMUT 어레이의 평면도를 도시하는 도면이다.

[0030] 도 7은 관련 단위 스위치 셀의 직사각형 어레이 꼭대기의 육각형 cMUT 서브 소자 어레이의 평면도를 도시하는 도면이다.

[0031] 도 8은 어레이를 지나는 환상 변환기 소자의 이동을 도시하는 도면이다.

[0032] 도 9는 모든 시스템 채널이 어레이 전체에 분배되어 각 변환기 서브 소자가 모든 시스템 채널로 액세스를 갖는 아키텍처를 도시하는 도면이다.

[0033] 도 10은 각 서브 소자의 스위치 수가 서브 소자 행당 하나의 버스를 갖는 것으로 제한되고, 버스 라인은 멀티플렉서를 통해 시스템 채널에 접속되는 아키텍처를 도시하는 도면이다.

[0034] 도 11은 서브 소자당 다수 버스 라인을 구비하여 동일 행 내의 여러 시스템 채널상의 서브 소자를 그룹화할 수 있게 하는 아키텍처를 도시하는 도면이다.

- [0035] 도 12는 제 1 행의 서브 소자의 매트릭스 스위치를 통해 제 2 행의 인접 서브 소자의 액세스 스위치에 접속하여 서브 소자의 제 2 행에 대한 버스 라인에 접속하는 제 1 행의 서브 소자를 허용하는 본 발명의 일실시예에 따른 아키텍처를 도시하는 도면이다.

- [0036] 도 13은 cMUT 어레이의 특정 행의 특정 서브 소자가 다수의 시스템 채널 버스 라인 중 임의의 하나에 접속되게 하는 본 발명의 다른 실시예에 따른 아키텍처를 도시하는 도면이다.

- [0037] 도 14는 (실선으로 표시되는) 액세스 스위치를 통해 각 서브 소자 옆에 접속되는 버스 라인을 갖는 육각형 서브 소자 어레이를 도시하는 도면이다.

- [0038] 도 15는 (실선으로 표시되는) 각 액세스 스위치를 통해 수직 및 수형 버스 라인에 접속되는 몇몇 서브 소자를 갖는 육각형 서브 소자 어레이를 도시하는 도면이다.

- [0039] 도 16은 육각형 어레이의 자연축을 따라 대각선으로 배치되는 버스 라인을 갖는 육각형 서브 소자 어레이를 도시하는 도면이다. 액세스 스위치는 실선으로 표시된다.

- [0040] 도 17은 도 13에 도시된 실시예에 따른 특정 음향 서브 소자와 관련되는 전자 소자의 공통 접속점으로의 접속을 도시하는 도면이다.

- [0041] 도 18은 이전에 미국 특허 출원 No. 10/248,968에 개시된 바와 같은 액세스 스위치 및 그 액세스 스위치의 상태를 제어하는 회로를 도시하는 도면이다.

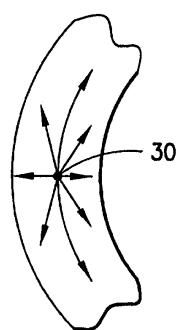

- [0042] 도 19는 단일 서브 소자 폭을 갖는 링(그 일부가 점선 원호로 도시됨)과 사용하기 위한 액세스 배열 및 매트릭스 스위치가 근접하게 함께 밀집되는 것을 도시하는 도면이다. 액세스 스위치는 실선에 의해 표시되고 매트릭스 스위치는 점선에 의해 표시된다.

- [0043] 도 20은 분배형 RC 지연 라인을 표현하는 회로도이다.

- [0044] 도 21은 20-탭 RC 지연 라인에 대해 측정된 지연 데이터의 그래프이다.

- [0045] 도 22는 행의 한쪽 끝부분의 서브 소자가 액세스 스위치에 의해 버스 라인에 접속되는 매트릭스 스위치에 의해 직렬로 접속되는 서브 소자 행을 도시하는 도면이다.

- [0046] 도 23은 행의 끝부분의 서브 소자가 개개의 액세스 스위치에 의해 버스 라인에 접속되고 나머지 서브 소자는 매트릭스 스위치를 통해 하나 또는 다른 액세스 스위치에 접속되는 서브 소자 행을 도시하는 도면이다.

- [0047] 도 24는 행의 끝부분의 서브 소자 및 행의 중간부분 부근의 한 서브 소자가 개개의 액세스 스위치에 의해 버스 라인에 접속되고 나머지 서브 소자는 매트릭스 스위치를 통해 개개의 액세스 스위치에 접속되는 서브 소자 행을 도시하는 도면이다.

- [0048] 도 25는 분리된 액세스 스위치로부터 거리가 증가하는 환상 서브 소자 링 주위의 지연을 증가시키는 것을 도시하는 도면이다.

- [0049] 도 26은 각 사분원에 배치되는 개개의 액세스 스위치로부터 거리가 증가하는 환상 서브 소자 링 주위의 지연을 증가시키는 것을 도시하는 도면이다.

- [0050] 도 27은 액세스 스위치로부터 거리가 증가하는 환상 서브 소자 링의 지연을 증가시키는 것을 도시하는 도면이다. 환상 링은 한 서브 소자보다 큰 폭을 갖는다.

- [0051] 도 28은 다스 액세스 스위치가 환상 링의 폭에 걸쳐 사용되는 경우를 도시하는 도면이다. 점들은 음향 서브 소자를 표시하고, 원은 한 설계에 따른 액세스 스위치의 배치를 도시하며, 정사각형은 다른 설계에 따른 액세스 스위치의 배치를 도시한다.

- [0052] 이하, 상이한 도면에서 유사한 소자는 동일 참조 부호를 갖는 도면을 참조할 것이다.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

## 도면18

### 도면19

### 도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

## 도면28