(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294549

(P2005-294549A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

**H01L 29/78**

**H01L 21/8238**

**H01L 27/092**

F 1

H01L 29/78    301G

H01L 29/78    301H

H01L 27/08    321D

H01L 27/08    321C

テーマコード(参考)

5FO48

5F140

審査請求 未請求 請求項の数 5 O L (全 10 頁)

(21) 出願番号

(22) 出願日特願2004-107809 (P2004-107809)

平成16年3月31日 (2004.3.31)

(71) 出願人 302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100110928

弁理士 速水 進治

(72) 発明者 君塚 直彦

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社

(72) 発明者 今井 清隆

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社

(72) 発明者 益岡 有里

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社

最終頁に続く

(54) 【発明の名称】MOS型トランジスタ

## (57) 【要約】

【課題】 高誘電率材料からなるゲート絶縁膜、多結晶シリコンからなるゲート電極を備えるPチャネルMOS型トランジスタにおいて、フェルミピニングを解消し、閾値電圧の安定的な低下を提供する技術を提供する。

【解決手段】 MOS型トランジスタは、チャネル領域105にP型不純物であるInを注入することにより、埋め込みチャネルトランジスタとしている。また、ゲート電極はN型不純物によりドープされた多結晶シリコン膜106により構成されている。このため、フェルミピニングによるゲート空乏化を効果的に抑制することができる。したがって、ゲート電極の空乏化および閾値電圧を安定的に低下させることができる。ここで、閾値電圧を安定的に低下させることができるのは、一定の電圧をゲート電極に印加することにより、電荷が誘起されるからである。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

N型の導電型を有する半導体基板領域と、

前記半導体基板領域内に設けられたP型の導電型を有する第1拡散層と、

前記半導体基板領域内に設けられたP型の導電型を有する第2拡散層と、

前記半導体基板領域の内部にあって、前記第1拡散層と前記第2拡散層との間に設けられたチャネル領域と、

前記チャネル領域上に設けられた、酸化シリコンよりも誘電率が高い高誘電率膜を含むゲート絶縁膜と、

前記ゲート絶縁膜上に設けられ、N型不純物を含む多結晶シリコンからなるゲート電極と、

を含むことを特徴とするMOS型トランジスタ。10

**【請求項 2】**

請求項1に記載のMOS型トランジスタにおいて、

前記高誘電率膜は、Hf、Zr、Al、LaおよびYからなる群から選択される一または二以上の元素を含むことを特徴とするMOS型トランジスタ。20

**【請求項 3】**

請求項1または2に記載のMOS型トランジスタにおいて、

前記チャネル領域に、P型不純物が導入されていることを特徴とするMOS型トランジスタ。20

**【請求項 4】**

請求項1乃至3いずれかに記載のMOS型トランジスタにおいて、

前記チャネル領域の下方に、N型不純物が導入された、N型不純物領域を有することを特徴とするMOS型トランジスタ。30

**【請求項 5】**

請求項1乃至4いずれかに記載のMOS型トランジスタにおいて、

前記ゲート絶縁膜は、シリコン酸化膜と、その上に設けられた前記高誘電率膜とを含み、

前記高誘電率膜と前記ゲート電極とが接していることを特徴とするMOS型トランジスタ。30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、高誘電率膜を含むゲート絶縁膜と多結晶シリコンからなるゲート電極とを備えるMOS型トランジスタに関する。40

**【背景技術】****【0002】**

近年、半導体素子の構成材料として、high-kとよばれる高誘電率薄膜の利用が検討され始めている。high-k材料の代表的なものとしては、Zr、Hf等を含む酸化物が挙げられる。こうした材料をMOSFETのゲート絶縁膜に用いることにより、ゲート絶縁膜の厚みをある程度厚くしてもシリコン酸化膜換算膜厚は薄くなり、物理的・構造的に安定なゲート絶縁膜を実現することができる。40

**【0003】**

特許文献1には、こうしたhigh-k材料を用いたMOSFETが開示されている。この文献には、表面チャネル型のNチャネルMOSFETが記載されている。ゲート絶縁膜として、金属シリケート膜が用いられている。ゲート電極は、N型の多結晶シリコンにより構成されている。

**【0004】**

ところが、最近の研究によれば、ゲート絶縁膜をhigh-k膜で構成し、ゲート電極を多結晶シリコンで構成した場合、フェルミピニングとよばれる現象が起こるとの知見が50

得られている（非特許文献1）。フェルミピニングは、ゲート電極中のゲート絶縁膜側界面近傍において、 $h_{igh-k}$ 膜を構成する金属がゲートを構成する多結晶シリコン中を拡散し、シリコンと上記金属との結合に基づく準位が形成されることによると考えられている。同文献には、多結晶シリコンに接して $HfO_2$ や $Al_2O_3$ 等の $h_{igh-k}$ 膜を設けるとフェルミピニングが起こることが報告されている。

#### 【0005】

MOSFETのゲート多結晶シリコン中でフェルミピニングが起こると、ゲート絶縁膜との界面近傍においてゲート多結晶シリコン中に空乏層が発生する。このような状態になると、ゲート電圧を充分に印加してもゲート絶縁膜に充分な電圧が印加されず、チャネル領域に充分なキャリアを誘起することが困難となる。この結果、閾値電圧が上昇する上、閾値電圧のばらつきが大きくなるという課題を有していた。特に、P型不純物を含んでいるゲート多結晶シリコンからなるゲート電極を有するPチャネルMOS型トランジスタにおいて、顕著にこの現象が現れていた。10

#### 【0006】

【特許文献1】特開2003-289140号公報

【非特許文献1】2003 Symposium on VLSI Technology Digest of Technical Papers

"Fermi Level Pinning at the PolySi/Metal Oxide Interface" C.Hobbs et al,

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

本発明は、こうした事情に鑑みてなされたものであり、その目的とするところは、多結晶シリコンからなるゲート電極を備えるPチャネルMOS型トランジスタにおいて、フェルミピニングによるゲート空乏化を解消し、閾値電圧を安定的に低下させることを目的とする。20

#### 【課題を解決するための手段】

#### 【0008】

本発明によれば、N型の導電型を有する半導体基板領域と、半導体基板領域内に設けられたP型の導電型を有する第1拡散層と、半導体基板領域内に設けられたP型の導電型を有する第2拡散層と、半導体基板領域の内部にあって、第1拡散層と第2拡散層との間に設けられたチャネル領域と、チャネル領域上に設けられた、酸化シリコンよりも誘電率が高い高誘電率膜を含むゲート絶縁膜と、ゲート絶縁膜上に設けられ、N型不純物を含む多結晶シリコンからなるゲート電極とを含むことを特徴とするMOS型トランジスタが提供される。30

#### 【0009】

本発明に係るトランジスタは、高誘電率膜を含むゲート絶縁膜上に形成される多結晶シリコンゲート電極が、N型不純物を含んでいる。このため、フェルミピニングによるゲートの空乏化を効果的に抑制することができる。

#### 【0010】

また、高誘電率膜は、Hf、Zr、Al、LaおよびYからなる群から選択される一または二以上の元素を含んでいてもよい。40

#### 【0011】

また、チャネル領域に、P型不純物が導入されていてもよい。

#### 【0012】

また、チャネル領域の下方に、N型不純物が導入された、N型不純物領域を有してもよい。

#### 【0013】

また、ゲート絶縁膜は、シリコン酸化膜と、その上に設けられた高誘電率膜とを含み、高誘電率膜とゲート電極とが接していてもよい。

#### 【発明の効果】

#### 【0014】

10

20

30

40

50

本発明によれば、PチャネルMOS型トランジスタにおいて、高誘電率膜を含むゲート絶縁膜上に形成される多結晶シリコンゲート電極がN型不純物を含む構成としているため、フェルミピニングによるゲートの空乏化が効果的に抑制される。

**【発明を実施するための最良の形態】**

**【0015】**

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

**【0016】**

**第一の実施の形態**

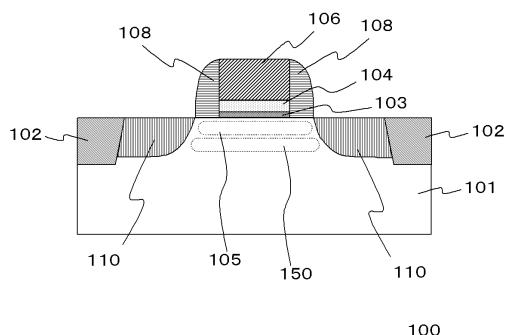

図1は、本実施形態に係るMOS型トランジスタ100の一例を示す図である。このMOSFETは、埋め込みチャネル型の構造を有している。シリコン基板(不図示)に設けられたN型の導電型を有する半導体基板領域としてのNウエル101内に、一対の不純物拡散領域110が設けられ、これらの間にチャネル領域105が形成されている。このチャネル領域105の下にN型不純物領域であるパンチスルーストッパー領域150が形成されている。また、チャネル領域105上に、シリコン熱酸化膜103および高誘電率膜104がこの順で積層した構造のゲート絶縁膜が設けられ、さらにその上に多結晶シリコン膜106が形成されており、これらによりゲート電極が構成されている。

**【0017】**

Nウエル101は、たとえばリンを150KeV、 $1 \times 10^{13} \text{ cm}^{-2} \sim 5 \times 10^{13} \text{ cm}^{-2}$ の条件で注入し、その後、非酸化雰囲気中で熱処理しN型不純物を活性化することにより形成できる。

**【0018】**

シリコン熱酸化膜103は、Nウエル101の表面を熱酸化することにより形成される。膜厚はたとえば、1.2nmとする。

**【0019】**

高誘電率膜104は、酸化シリコンよりも比誘電率の高い膜であり、好ましくは比誘電率10以上の膜とする。いわゆるhigh-k膜とよばれるものを用いることができる。高誘電率膜104の好ましい例としては、Hf、Zr、Al、LaおよびYからなる群から選択される—または二以上の元素を含むものが挙げられ、これらのいずれかの元素を含む酸化膜、シリケート膜等が好ましく用いられる。上記金属元素を含む酸化膜等は、高い比誘電率を有するとともに良好な耐熱性を有するため、MOSFETのサイズ縮小化、信頼性向上に寄与する。こうした材料を用いた場合、このような利点が得られる反面、フェルミピニングによるゲート空乏化が問題となるところ、本実施形態で述べた構成によれば、こうした問題を効果的に解決することができ、上記元素を含む高誘電率膜の利点を充分に生かすことができる。

**【0020】**

また、高誘電率膜104は、窒素やアンモニア等の窒素含有化合物の雰囲気化でアニールし、膜中に窒素を導入してもよい。窒素アニールにより、高誘電率膜104の結晶化が抑制される。本実施形態では、後述の製造方法において説明するように、高誘電率膜104として、ハフニウムシリケートを用いる。

**【0021】**

なお、本実施形態では、上記シリコン熱酸化膜103と高誘電率膜104との積層膜がゲート絶縁膜として機能する。

**【0022】**

チャネル領域105は、Nウエル101表面にInなどのP型不純物をイオン注入することにより形成される。このように、チャネル領域105にP型不純物がドープされることにより、閾値電圧の上昇を抑制することができる。

**【0023】**

パンチスルーストッパー領域150は、Nウエル101内にAsなどのN型不純物をイオン注入することにより、チャネル領域105の下方に形成される。パンチスルーストッ

10

20

30

40

50

パー領域 150 が、チャネル領域 105 の下方に形成されることにより、短チャネル効果を抑制することができる。

#### 【0024】

多結晶シリコン膜 106 は、As などのN型不純物がドープされた多結晶シリコンであり、ゲート電極としての実質的な機能を有する。N型にドープされた多結晶シリコン膜を用いることにより、フェルミピニングによるゲートの空乏化を効果的に抑制することができる。

#### 【0025】

不純物拡散領域 110 は、N ウエル 101 表面に P 型不純物がドープされ、表面から浅く導入された拡散層である。一方がソース領域、他方がドレイン領域となる。

10

#### 【0026】

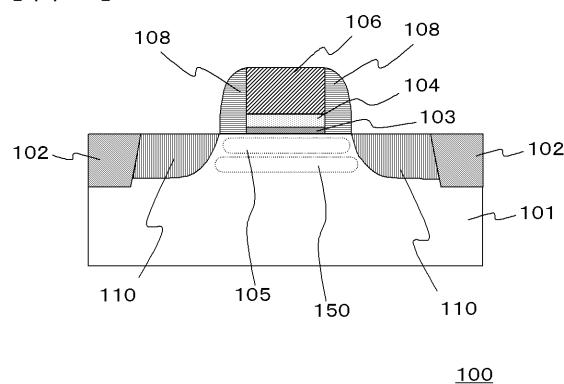

以下、図1のMOS型トランジスタ 100 の製造方法について説明する。まず、図2(a)に示すように、たとえば、(100)面を正面とするシリコン基板にSTI(Shallow Trench Isolation)による素子分離領域 102 を形成した後、As などのN型不純物をイオン注入してN ウエル 101 を形成する。素子分離方法は公知の他の素子分離法を用いてもよく、例えばLOCOS法により素子分離を行ってもよい。

#### 【0027】

つづいて、シリコン基板表面に犠牲酸化膜 107 を形成する。犠牲酸化膜 107 は、熱処理によりN ウエル 101 の表面を酸化することにより得ることができる。熱処理の条件としては、たとえば、処理温度 900 、処理時間 40 秒～50 秒程度が用いられる。

20

#### 【0028】

次に、犠牲酸化膜 107 の上から、たとえば、As などのN型不純物をイオン注入する。このイオン注入により、パンチスルーストップバー領域 150 が形成され、短チャネル特性の劣化を抑制する。パンチスルーストップバー領域 150 を形成する際のイオン注入条件は、たとえば、150 keV、 $5 \times 10^{12} \text{ cm}^{-2}$  とする。

#### 【0029】

つづいて、たとえば、In などのP型不純物をイオン注入してチャネル領域 105 をN ウエル 101 の表層付近に形成する。イオン注入条件としては、たとえば、In の場合、60 keV、 $2 \times 10^{13} \text{ cm}^{-2}$  などが用いられる。

30

#### 【0030】

次に、図2(b)に示すように、N ウエル 101 上に形成されている犠牲酸化膜 107 を除去する。具体的には、犠牲酸化膜 107 を希釈フッ酸(例えは、HF:H<sub>2</sub>O=1:200)を用いてエッティング除去した後、純水を用いて水洗し、窒素ブローなどにより乾燥させる。

#### 【0031】

つづいて、N ウエル 101 表面を熱酸化することにより、シリコン熱酸化膜 103 を形成する。熱酸化の条件としては、たとえば、処理温度 950 、処理時間 40 秒程度とする。また、シリコン熱酸化膜 103 の膜厚としては、たとえば、1.5 nm 程度とする。

#### 【0032】

次に、図2(c)に示すように、シリコン熱酸化膜 103 上に高誘電率膜 104 を成膜する。高誘電率膜 104 は、CVD法やALD法(原子層堆積法)などにより成膜する。本実施形態では、高誘電率膜 104 としてハフニウム膜を採用する。この成膜は、有機ハフニウム原料ガス、酸化性ガスおよびシリコン含有ガスを用いて行う。ここで、酸化性ガスとして酸素等、シリコン含有ガスとしてモノシラン(SiH<sub>4</sub>)等を用いることができる。高誘電率膜 104 の膜厚は、1.5 nm 程度とする。シリコン熱酸化膜 103 および高誘電率膜 104 を成膜した後、窒素アニールを行う。窒素アニールは、窒素あるいはアンモニアなどの窒素含有物を用いて行い、アニール条件としては、たとえば、アンモニアを用いた場合、処理温度 850～1000 、処理時間 40 秒等とする。窒素アニールを行うことにより、ハフニウムシリケートの結晶化を抑制することができる。

40

#### 【0033】

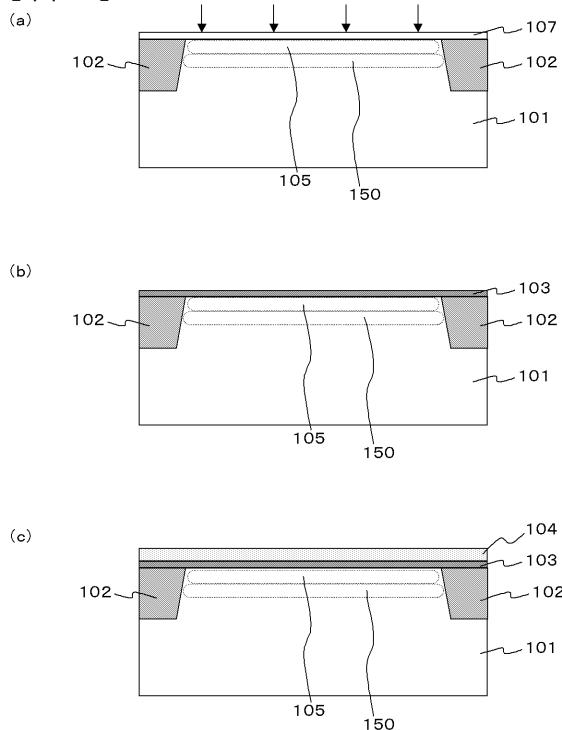

つぎに、図3(a)に示すように、高誘電率膜 104 上に多結晶シリコン膜 106 を成

50

膜し、その後、多結晶シリコン膜106全面にN型不純物をイオン注入する。多結晶シリコン膜の厚さは、たとえば130nm程度とする。N型不純物として、ここではリンを10keV、 $4 \times 10^{15} \text{ cm}^{-2}$ の条件で注入する。その後、図3(b)に示すように、シリコン熱酸化膜103、高誘電率膜104および多結晶シリコン膜106を選択的にドライエッチングし、ゲート電極の形状に加工する。なお、この工程において、シリコン熱酸化膜103、高誘電率膜104を全面に残しておく構成にしてもよい。

#### 【0034】

つぎに、チャネル領域105と後述する不純物拡散領域110との電気的接続部であるS/Dエクステンション領域を形成するため、ここでは、BF<sub>2</sub>を2.5keV、 $5 \times 10^{14} \text{ cm}^{-2}$ の条件で注入する。つづいて、図3(c)に示すように、シリコン熱酸化膜103、高誘電率膜104および多結晶シリコン膜106からなるゲート電極の側壁に側壁絶縁膜108を形成する。具体的には、シリコン熱酸化膜103、高誘電率膜104および多結晶シリコン膜106の側壁のみに側壁絶縁膜108が残るように、たとえば、フルオロカーボンガスなどを用いて異方性エッチングを行う。次に、ゲート電極および側壁絶縁膜108をマスクとして、Nウエル101の表層にP型不純物をドープして不純物拡散領域110を形成する。P型不純物として、ここではボロンを用いる。注入条件は、たとえば、2keV、 $5 \times 10^{14} \text{ cm}^{-2} \sim 2 \times 10^{15} \text{ cm}^{-2}$ とする。その後、非酸化雰囲気中で熱処理を行うことにより、不純物の活性化を行う。熱処理の条件としては、たとえば、1030～1050の範囲でスパイクアニールとする。以上のプロセスにより、MOS型トランジスタが形成される。

#### 【0035】

以下、MOS型トランジスタ100の効果について説明する。

#### 【0036】

本実施形態において、MOS型トランジスタは、チャネル領域105にP型不純物であるInを注入することにより、埋め込みチャネルトランジスタとしている。また、ゲート電極はN型不純物によりドープされた多結晶シリコン膜106により構成されている。このため、ハフニウムの拡散によってフェルミピニングが生じても、これに起因するゲート空乏化を効果的に抑制することができる。したがって、MOS型トランジスタの閾値電圧を安定的に低下させ、製品適用が可能なレベルに調整することができる(閾値電圧約0.5V)。

#### 【0037】

また、本実施形態においては、チャネル領域105の下部に、パンチスルーストッパー領域150が設けられている。これにより、短チャネル効果を抑制することができる。本実施形態のような埋め込みチャネル型のMOSトランジスタでは短チャネル効果が生じやすいところ、パンチスルーストッパー領域150を設けることにより、かかる問題を解消することができる。

#### 【0038】

##### 第二の実施の形態

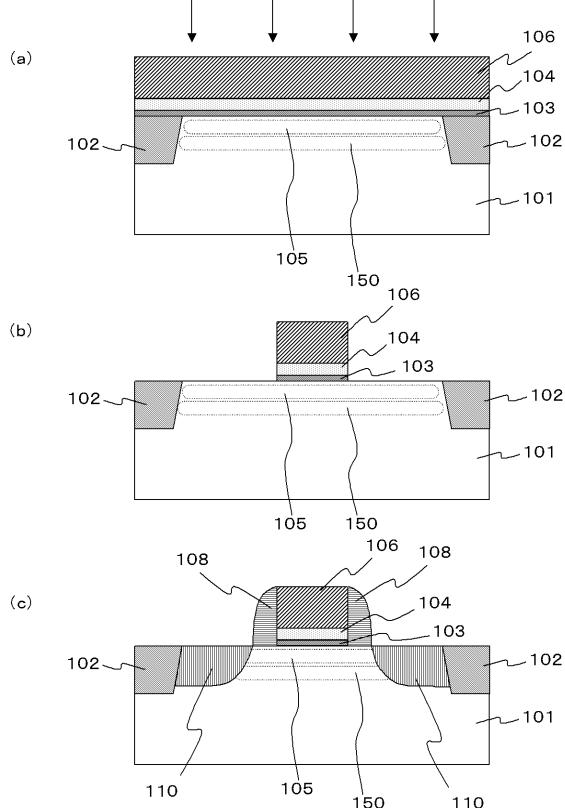

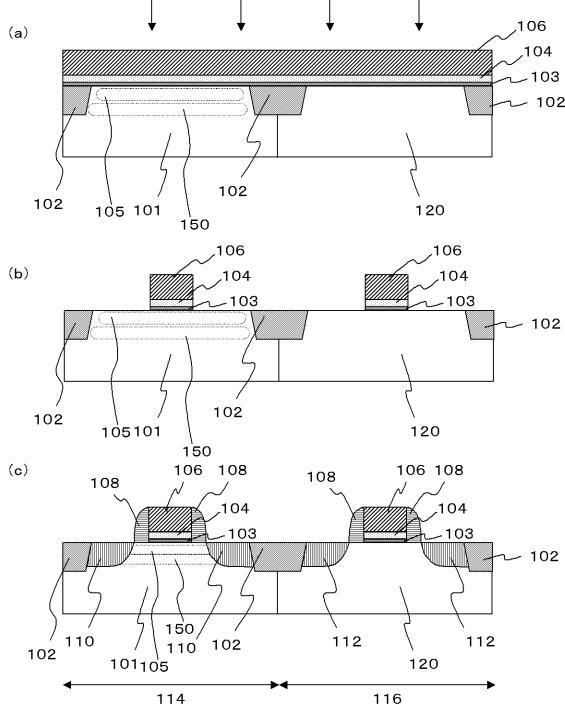

本実施形態は、本発明をCMOSに適用した例に関するものである。図4は、本実施形態に係るCMOSの製造方法を示す工程断面図である。

#### 【0039】

まず、図4(a)に示す構造体を得る。まず、シリコン基板中に素子分離領域102を形成した後、PMOS領域にNウエル101を形成し、NMOS領域にPウエル120を形成する。次いで、基板表面にシリコン熱酸化膜103、高誘電率膜104および多結晶シリコン膜106をこの順で成膜する。これらの膜の成膜方法は、第一の実施の形態で述べたのと同様である。その後、多結晶シリコン膜106の全面にN型不純物をイオン注入する。ここでは、リンを10keV、 $4 \times 10^{15} \text{ cm}^{-2}$ の条件で注入する。

#### 【0040】

次に、図4(b)に示すように、シリコン熱酸化膜103、高誘電率膜104および多結晶シリコン膜106からなる積層膜上に所定の形状にパターニングされたレジストマス

10

20

30

40

50

クを設け、上記積層膜を選択的にドライエッティングし、ゲート電極の形状に加工する。なお、第一の実施の形態と同様に、この工程において、シリコン熱酸化膜 103、高誘電率膜 104 を全面に残しておく構成にしてもよい。

#### 【0041】

つづいて、図 4 (c) に示すように、たとえば、第一の実施の形態と同様の方法を用いて、シリコン熱酸化膜 103、高誘電率膜 104 および多結晶シリコン膜 106 からなるゲート電極の側壁に側壁絶縁膜 108 を形成する。次に、ゲート電極をマスクとして PMOS 領域に P 型不純物をドープし、不純物拡散領域 110 を形成する。次に、NMOS 領域に N 型不純物をドープし、不純物拡散領域 112 を形成する。P 型不純物としては、たとえばボロンを  $2 \text{ keV}$ 、 $5 \times 10^{14} \text{ cm}^{-2}$  ~  $2 \times 10^{15} \text{ cm}^{-2}$  程度の条件で注入し、N 型不純物としては、たとえば、As を  $30 \text{ keV}$ 、 $3 \times 10^{15} \text{ cm}^{-2}$  程度の条件で注入する。以上により、N ウエル 101 を有する PMOS 型トランジスタ 114 と P ウエル 120 を有する NMOS 型トランジスタとを備える CMOS トランジスタが形成される。

#### 【0042】

本実施形態によれば、多結晶シリコン膜 106 を形成した後に、PMOS 型トランジスタ 114 と NMOS 型トランジスタ 116 の多結晶シリコン膜 106 に対して、単一のリソグラフィー工程でリンなどの N 型不純物を注入することができる。このため、製造プロセスの簡略化を図ることができる。

#### 【0043】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

#### 【0044】

たとえば、上記実施形態においては、CVD 法を用いて高誘電率膜 104 を成膜する形態について説明したが、ALD 法など、他の成膜方法を用いてもよい。

#### 【0045】

また、上記実施形態においては、high-k 膜として、ハフニウムシリケート膜を用いる形態について説明したが、Hf、Zr、Al、La、Y などの酸化膜、シリケート膜、酸窒化膜などを用いてもよい。ここで、非特許文献 1 に、多結晶シリコンに接して HfO<sub>2</sub> や Al<sub>2</sub>O<sub>3</sub> 等の high-k 膜を設けるとフェルミビニングが起こることが報告されている。そこで、HfO<sub>2</sub> や Al<sub>2</sub>O<sub>3</sub> など以外にも、HfO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub> と同じような性質を有する、Zr、La、Y の酸化膜、シリケート膜、酸窒化膜などについても同様の現象が起こることが考えられる。したがって、上記 high-k 膜を用いることによりフェルミビニングが発生したとしても、ゲート電極が N 型不純物によりドープされた多結晶シリコン膜 106 により構成されることで、ゲート空乏化を効果的に抑制することができる。この結果、MOS 型トランジスタの閾値電圧を安定的に低下させ、製品適用が可能なレベルに調整することができる。

#### 【0046】

また、上記実施形態においては、P 型不純物として In をイオン注入してチャネル領域 105 を N ウエル 101 の表層付近に形成する形態について説明したが、ボロンなどの他の P 型不純物をイオン注入してチャネル領域を N ウエルの表層付近に形成してもよい。こうすることにより、閾値電圧の上昇を抑制することができる。

#### 【0047】

また、上記実施形態においては、N 型不純物として As をイオン注入してパンチスルーストッパー領域 150 を形成する形態について説明したが、リンなどの他の N 型不純物をイオン注入してパンチスルーストッパー領域を形成してもよい。こうすることにより、短チャネル特性の劣化を抑制することができる。

#### 【図面の簡単な説明】

#### 【0048】

【図 1】本発明の実施の形態に係るトランジスタを模式的に示した断面図である。

10

20

30

40

50

【図2】本発明の実施の形態に係るトランジスタの製造工程を模式的に示した断面図である。

【図3】本発明の実施の形態に係るトランジスタの製造工程を模式的に示した断面図である。

【図4】本発明の実施の形態に係るトランジスタの製造工程を模式的に示した断面図である。

【符号の説明】

【0049】

|     |              |    |

|-----|--------------|----|

| 100 | MOS型トランジスタ   | 10 |

| 101 | Nウェル         |    |

| 102 | 素子分離領域       |    |

| 103 | シリコン熱酸化膜     |    |

| 104 | 高誘電率膜        |    |

| 105 | チャネル領域       |    |

| 106 | 多結晶シリコン膜     |    |

| 107 | 犠牲酸化膜        |    |

| 108 | 側壁絶縁膜        |    |

| 110 | 不純物拡散領域      | 20 |

| 112 | 不純物拡散領域      |    |

| 114 | PMOS型トランジスタ  |    |

| 116 | NMOS型トランジスタ  |    |

| 120 | Pウェル         |    |

| 150 | パンチスルーストップ領域 |    |

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

F ターム(参考) 5F048 AA07 AC01 AC03 BA01 BB06 BB11 BB14 BB18 BC15 BD04

BE03 BG13 DA23

5F140 AA06 AA21 AB03 AC01 BA01 BA20 BB06 BB15 BC06 BD01

BD11 BD13 BE03 BE07 BE10 BE17 BF01 BF04 BG08 BG32

BG38 BG53 BH14 BH39 BK02 BK10 BK13 BK21 CB01 CB04

CB08