(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4881256号

(P4881256)

(45) 発行日 平成24年2月22日(2012.2.22)

(24) 登録日 平成23年12月9日(2011.12.9)

(51) Int.Cl.

F 1

H01L 23/48 (2006.01)

H01L 23/48

G

H01L 25/07 (2006.01)

H01L 25/04

C

H01L 25/18 (2006.01)

請求項の数 9 (全 23 頁)

(21) 出願番号 特願2007-212307 (P2007-212307)

(73) 特許権者 000003078

(22) 出願日 平成19年8月16日 (2007.8.16)

株式会社東芝

(65) 公開番号 特開2009-49104 (P2009-49104A)

東京都港区芝浦一丁目1番1号

(43) 公開日 平成21年3月5日 (2009.3.5)

(74) 代理人 100091351

審査請求日 平成21年9月25日 (2009.9.25)

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100084618

弁理士 村松 貞男

最終頁に続く

(54) 【発明の名称】パワー半導体モジュール

## (57) 【特許請求の範囲】

## 【請求項1】

パワー半導体素子、このパワー半導体素子の一面に設けられる第1電極板、前記パワー半導体素子の他面に設けられる第2電極板および、前記パワー半導体素子と前記第1電極板との間に設けられ絶縁基板とからなる半導体装置と、

この半導体装置を構成する前記第1電極板の主面に、第1のはんだ部材を介してはんだ付け接合される導電部材である第1のバスバーと、

前記半導体装置を構成する前記第2電極板の主面に、第2のはんだ部材を介してはんだ付け接合される導電部材である第2のバスバーと、

前記第1のバスバーにおける第1電極板がはんだ付けされる主面および、前記第2のバスバーにおける第2電極板がはんだ付けされる主面のそれぞれに設けられ、前記第1のはんだ部材および第2のはんだ部材のはんだ接合厚さを規制するはんだ付け制御手段とを具備することを特徴とするパワー半導体モジュール。

## 【請求項2】

前記はんだ付け制御手段は、

前記第1のバスバーにおける前記第1電極板がはんだ付けされる主面を覆うとともに、第1電極板がはんだ付けされる位置に、第1電極板の主面よりも大きな面積の取付け部を形成するソルダーレジスト膜であり、

前記第2のバスバーにおける前記第2電極板がはんだ付けされる主面を覆うとともに、第2電極板がはんだ付けされる位置に、第2電極板の主面よりも大きな面積の取付け部を

10

20

形成するソルダーレジスト膜であることを特徴とする請求項1記載のパワー半導体モジュール。

**【請求項3】**

前記はんだ付け制御手段は、

前記第1のバスバーにおける前記第1電極板がはんだ付けされる主面を覆うとともに、第1電極板がはんだ付けされる位置に、第1電極板の主面よりも大きな面積の取付け領域を区画するとともに、前記取付け領域が複数に区画されるように仕切り領域を有するソルダーレジスト膜であり、

前記第2のバスバーにおける前記第2電極板がはんだ付けされる主面を覆うとともに、第2電極板がはんだ付けされる位置に、第2電極板の主面よりも大きな面積の取付け領域を区画するとともに、前記取付け領域が複数に区画されるように仕切り領域を有するソルダーレジスト膜であることを特徴とする請求項1記載のパワー半導体モジュール。10

**【請求項4】**

前記はんだ付け制御手段は、

前記第1のバスバーにおける前記第1電極板がはんだ付けされる主面の一端部に設けられ、前記第1電極板の一端が載る第1の突条部であり、前記主面の端縁から前記第1の突条部までの長さ寸法( $L_a$ )と、第1電極板の一端縁から他端縁までの長さ寸法( $L$ )とが略同一に設定され、

前記第2のバスバーにおける前記第2電極板がはんだ付けされる主面の一端部に設けられ、前記第2電極板の一端が載る第2の突条部であり、前記主面の端縁から前記第2の突条部までの長さ寸法( $L_b$ )と、第2電極板の一端縁から他端縁までの長さ寸法( $L$ )とが略同一に設定されることを特徴とする請求項1記載のパワー半導体モジュール。20

**【請求項5】**

パワー半導体素子、このパワー半導体素子の一面に設けられる第1電極板、前記パワー半導体素子の他面に設けられる第2電極板および、前記パワー半導体素子と前記第1電極板との間に設けられ、一部が前記第1電極板および第2電極板の外周縁より外側に突出する引出し部を備え、この引出し部に前記パワー半導体素子の制御電極と接続する外部接続端子を備えた絶縁基板からなる半導体装置と、

この半導体装置を構成する第1電極板の主面の前記外周縁と端縁を位置合せされ、第1電極板の主面に、第1のはんだ部材を介してはんだ付け接合される導電部材である第1のバスバーと。30

前記半導体装置を構成する第2電極板の主面の前記外周縁と端縁を位置合せされ、第2電極板の主面に、第2のはんだ部材を介してはんだ付け接合される導電部材である第2のバスバーと、

前記半導体装置に設けられ、前記第1のはんだ部材および第2のはんだ部材のはんだ接合厚さを規制するはんだ付け制御手段と

を具備することを特徴とするパワー半導体モジュール。

**【請求項6】**

半導体装置を構成する第1電極板と、第2電極板および絶縁基板は、第1のバスバーと第2のバスバーの端縁と位置合せされる前記外周縁から、前記引出し部の突出方向と逆方向に形成される加工用辺部を備えていて。40

前記はんだ付け制御手段は、前記加工用辺部の前記外周縁から所定距離に亘って設けられる切欠部であることを特徴とする請求項5記載のパワー半導体モジュール。

**【請求項7】**

半導体装置を構成する第1電極板と、第2電極板および絶縁基板は、第1のバスバーと第2のバスバーの端縁と位置合せされる外周縁から前記引出し部の突出方向と逆方向に形成される加工用辺部を備えていて、

前記はんだ付け制御手段は、前記加工用辺部の前記外周縁から互いに同一の間隔を存して設けられる複数の切欠部であり、これら切欠部の切欠面積は、前記外周縁から漸次小さく形成されることを特徴とする請求項5記載のパワー半導体モジュール。50

**【請求項 8】**

パワー半導体素子、このパワー半導体素子の一面に設けられる第1電極板、前記パワー半導体素子の他面に設けられる第2電極板および、前記パワー半導体素子と前記第1電極板との間に設けられ絶縁基板とからなる半導体装置と、

この半導体装置を構成する第1電極板主面に、第1のはんだ部材を介してはんだ付け接合される導電部材である第1のバスバーと、

前記半導体装置を構成する第2電極板主面に、第2のはんだ部材を介してはんだ付け接合される導電部材である第2のバスバーとを具備し、

前記第1のはんだ部材および第2のはんだ部材は、はんだ接合厚さと同一直径で、かつはんだ成分に固溶しない金属ボールが混入されることを特徴とするパワー半導体モジュール。

**【請求項 9】**

前記第1のバスバーにおける前記第1電極板がはんだ付けされる主面は、ソルダーレジスト膜で覆われるとともに、このソルダーレジスト膜の第1電極板がはんだ付けされる位置に、第1電極板の取付け部が形成され、

前記第2のバスバーにおける前記第2電極板がはんだ付けされる主面は、ソルダーレジスト膜で覆われるとともに、このソルダーレジスト膜の第2電極板がはんだ付けされる位置に、第2電極板の取付け部が形成されることを特徴とする請求項 5ないし請求項 8のいずれかに記載のパワー半導体モジュール。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、たとえばIGBT等のパワー半導体素子を備えた片状の半導体装置の両面に、導電部材であるバスバーをはんだ付け接合してなるパワー半導体モジュールに関する。

**【背景技術】**

**【0002】**

電力用半導体素子として、IGBT(Insulate Gate Bipolar Transistor)、IGET(Injection Enhanced Transistor)、MOS-FETなどが多用されている。前記電力用半導体素子は片状に形成されていて、この主面に第1電力端子および制御端子を備え、主面に対向する裏面に第2電力端子を備えている。前記電力用半導体素子がIGBT素子である場合には、第1電力端子がエミッタ電極であり、第2電力端子がコレクタ電極であり、制御端子はゲート電極となる。

**【0003】**

このような電力用半導体素子を基板に実装して半導体装置化する場合には、[特許文献1]もしくは[特許文献2]に記載されるように、半導体素子の第2電力端子をはんだ接合により基板表面側の電極に接続し、アルミニウムワイヤを用いたワイヤボンディングにより、半導体素子の第1電力端子および制御端子を基板表面側の電極に接続している。

**【0004】**

ところが、ワイヤボンディングは、ワイヤを1本ずつボンディングするために、ボンディング時間が長いことと、ワイヤがループ形状を描くためにワイヤ長が長くなり、配線インダクタンスが大きくなる。ワイヤ自体が振動に弱く、切断や隣接間ショートが生じる可能性が高いこと等の、技術的な課題が多い。

**【0005】**

そのため、半導体素子の第1電力端子にアルミニウム薄板をボンディングする方法や、平板やリードをはんだ接合し電極として引き出す方法が採用される傾向にある。特に、半導体素子の第1電力端子にはんだ接合が可能な材質を選定し、平板やリードをはんだ接合により接続する方法は、最近注目されている技術である。ただし、制御端子からの引出線には、ワイヤボンディングにボンディングされたワイヤが使用される。

**【0006】**

前記半導体装置(以下、「半導体パッケージ」と呼ぶ)を複数個備えた半導体モジュー

10

20

30

40

50

ルにおいては、複数の半導体パッケージを放熱板であるベース基板上に一列に並べ、半導体パッケージの基板裏面がベース基板上に接合される。このような半導体モジュールが、インバータやコンバータ等の電力制御器に搭載されている。

【特許文献1】特開2003-110064号公報

【特許文献2】特開2002-164485号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、前述の半導体モジュールでは、各半導体パッケージの片面だけがベース基板に接触している状態なので、放熱性が充分でない。また、各半導体パッケージの基板裏面がベース基板上に接合して設けられているため、ベース基板に対する半導体パッケージの設置面積が大きくなり、半導体モジュールが大型化してしまう。10

【0008】

これらの不利条件を克服するためには、各半導体パッケージを一列に並べ、半導体パッケージの正面と、この正面と対向する面である裏面のそれぞれに導電部材であるバスバーを取付けて挿持状態となし、これらをベース基板上に設けるようにすればよい。

なお説明すると、半導体パッケージ正面もしくは裏面、バスバーの半導体パッケージ取付け面の少なくともいずれか一方に、はんだ部材をコーティングする。片状に形成される半導体パッケージを立てて垂直姿勢とし、この正面と裏面にバスバーの側面をあてがって仮保持し加熱炉に収容して加熱する。はんだ部材は溶融して、半導体パッケージとバスバーを互いにはんだ接合する。20

【0009】

問題は、半導体パッケージとバスバーをはんだ部材を介してはんだ付け加工する際にある。すなわち、片状の半導体パッケージを立てて垂直姿勢とすると、この半導体パッケージの正面と裏面および、はんだ接合するバスバーの側面も垂直面となる。そのため、加熱炉で加熱され溶融したはんだ部材の一部が重力の影響を受けて、半導体パッケージ下端からバスバーの下端を介して流れ落ち、あるいは半導体パッケージ下端周辺に濡れ拡がり易い。

【0010】

上述のはんだの流出等を無くすために、予め、はんだ部材の量を少なくすることが考えられる。しかしながら、この場合は、半導体パッケージとバスバーとの間に形成されるはんだ層に気泡ができ易く、確実で信頼性の高いはんだ接合を得ることができない。30

このように半導体パッケージを垂直姿勢にして、バスバーとはんだ付け接合するにあたって、半導体パッケージとバスバーとの最適なはんだ接合厚さを得るのが困難であり、はんだ継手構造に対する信頼性が低いものである。

【0011】

本発明は前記事情にもとづきなされたものであり、その目的とするところは、半導体装置とバスバーとをはんだ付け接合するにあたって、はんだ接合厚さを最適化し、はんだ継手構造の信頼性を向上させたパワー半導体モジュールを提供しようとするものである。

【課題を解決するための手段】

【0012】

前記目的を満足するため本発明の半導体モジュールは、パワー半導体素子、このパワー半導体素子の一面に設けられる第1の電極板、パワー半導体素子の他面に設けられる第2の電極板およびパワー半導体素子と第1電極板との間に設けられる絶縁基板とからなる半導体装置と、この半導体装置を構成する第1電極板の正面に第1のはんだ部材を介してはんだ付け接合される導電部材である第1のバスバーと、半導体装置を構成する第2電極板の正面に第2のはんだ部材を介してはんだ付け接合される導電部材である第2のバスバーと、第1のバスバーにおける第1電極板がはんだ付けされる正面および第2のバスバーにおける第2電極板がはんだ付けされる正面のそれぞれに設けられ第1のはんだ部材および第2のはんだ部材のはんだ接合厚さを規制するはんだ付け制御手段とを具備する。4050

**【発明の効果】****【0013】**

本発明によれば、半導体装置と導電部材であるバスバーとのはんだ付けにあたって、はんだ接合厚さを最適化し、はんだ継手構造の信頼性向上を得るという効果を奏する。

**【発明を実施するための最良の形態】****【0014】**

以下、本発明の実施の形態を、図面にもとづいて説明する。（なお、説明をしても符号を付していない構成部品については、図示していない。）

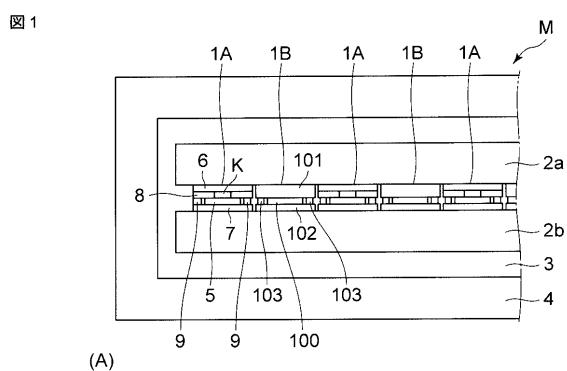

図1（A）はパワー半導体モジュールMの一部省略した平面図であり、図1（B）はパワー半導体モジュールMの一部省略した正面図である。10

このパワー半導体モジュールMは、複数の電力用半導体装置（以下、「電力用半導体パッケージ」と呼ぶ）1Aと、複数の整流用半導体装置（以下、「整流用半導体パッケージ」と呼ぶ）1Bと、これら半導体パッケージ1A、1Bを挟持し、かつ電気的に接続される導電部材である第1のバスバー2aおよび第2のバスバー2bと、これら第1、第2のバスバー2a、2bを支持する絶縁シートや絶縁板等の絶縁体3と、この絶縁体3に重ね合わせて設けられる放熱板4とから構成される。

**【0015】**

電力用半導体パッケージ1Aと整流用半導体パッケージ1Bは、第1、第2のバスバー2a、2bの長手方向に沿って交互に、一直線上に並べられ、後述するように、第1のバスバー2aの一側面に第1のはんだ部材を介してはんだ接合されるとともに、第2バスバー2bの一側面に第2のはんだ部材を介してはんだ接合されている。20

**【0016】**

前記電力用半導体パッケージ1Aは、IGBT素子等の電力用パワー半導体素子5と、このパワー半導体素子5の表面である主面に設けられる第1電極板6と、パワー半導体素子5の主面と対向する裏面に設けられる第2電極板7と、パワー半導体素子5と第1電極板6との間に設けられる絶縁基板8とを積層することにより構成されている。

**【0017】**

前記パワー半導体素子5は、板状小片の半導体チップに、たとえばIGBTが搭載されたIGBT素子であり、外周縁が第1電極板6、第2電極板7および絶縁基板8の各外周縁より内側になるよう形成されている。パワー半導体素子5の主面には、エミッタ電極である第1電力端子と、ゲート電極である制御端子が設けられ、主面と対向する裏面にはコレクタ電極である第2電力端子が設けられている。30

**【0018】**

前記絶縁基板8は一部に、パワー半導体素子5や、第1、第2電極板6、7の外周縁よりも外側に突出する引出し部Kが設けられている。この引出し部Kには外部接続端子が設けられていて、前記半導体素子5に備えられる制御端子と配線を介して接続される。

すなわち、半導体パッケージ1Aを第1、第2のバスバー2a、2b間に挟持しはんだ接合した状態で、引出し部Kが第1、第2電極板6、7と絶縁基板8の外周縁と、第1、第2のバスバー2a、2bの上端縁から上方へ突出する。このことから、ワイヤボンディングを用いることなく、制御配線をパッケージ外に引出すことができる。40

**【0019】**

前記第2電極板7と絶縁基板8との間には、これらの離間距離を一定に保持するスペーサ9が設けられている。このスペーサ9はたとえば4つ設けられていて、パワー半導体素子5の外周縁より外側の4つの角部に位置付けられている。

前記スペーサ9を備えることによって、第2電極板7と絶縁基板8との間が一定に保持されて、外力によるパワー半導体素子5の破損を確実に防止することができ、その結果、半導体パッケージ1Aの部品信頼性を向上させることができる。

**【0020】**

前記整流用半導体パッケージ1Bは、ダイオード素子等の整流用半導体素子100と、この整流用半導体素子100を挟持し電気的に接続される第1電極板101および第2電50

極板 102 と、これら第 1、第 2 電極板 101, 102 との間の軸間距離を一定に保持するスペーサ 103 を備えて、片状に形成される。前記スペーサ 103 は、整流用半導体素子 100 の外周縁より外側で、第 1 電極板 101 の 4 つの角部に位置付けられている。

#### 【0021】

前記第 1、第 2 のバスバー 2a, 2b は、銅材など極めて導電性のよい部材からなり、角柱状をなす。電力用半導体パッケージ 1A と整流用半導体パッケージ 1B の共通の電極部材としてそれぞれ機能するとともに、熱伝導性を有していて、放熱部材としても機能する。

#### 【0022】

ここでは、前記第 1 のバスバー 2a は、電力用半導体パッケージ 1A を構成する第 1 電極板 6 と第 1 のはんだ部材を介してはんだ接合されることで電気的に接続され、エミッタ電極プロックとして機能する。また、前記第 2 のバスバー 2b は、電力用半導体パッケージ 1A を構成する第 2 電極板 7 と第 2 のはんだ部材を介してはんだ接合されることで電気的に接続され、コレクタ電極プロックとして機能する

このようなパワー半導体モジュール M が複数組み合わせられ、たとえば産業用インバータや、電車・電気自動車などのインバータもしくはコンバータなどの電力制御機器が構成される。

#### 【0023】

つぎに、電力用半導体パッケージ 1A および整流用半導体パッケージ 1B と、第 1 のバスバー 2a および第 2 のバスバー 2b とのはんだ接合について説明する。

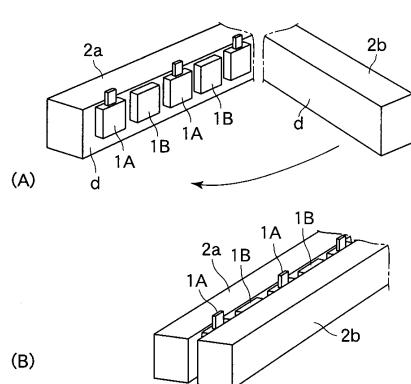

図 2 (A) は電極用半導体パッケージ 1A および整流用半導体パッケージ 1B を第 1 のバスバー 2a にはんだ付けした状態の斜視図、図 2 (B) は両半導体パッケージ 1A, 1B の両面を第 1、第 2 のバスバー 2a, 2b ではんだ付けにより挟持した状態の斜視図である。

#### 【0024】

先に説明したように、電力用半導体パッケージ 1A および整流用半導体パッケージ 1B は、第 1、第 2 のバスバー 2a, 2b の長手方向に沿って交互に同一直線上に並べられ、第 1 のバスバー 2a と第 2 のバスバー 2b の垂直面 d にはんだ接合される。すなわち、片状に形成される各半導体パッケージ 1A, 1B は、主面および裏面と対向する面である裏面を立てた垂直姿勢となし、主面が第 1 のバスバー 2a の垂直面 d に第 1 のはんだ部材を介してはんだ付けされ、裏面が第 2 のバスバー 2b の垂直面 d に第 2 のはんだ部材を介してはんだ付けされる。

#### 【0025】

実際には、電力用半導体パッケージ 1A を構成する第 1 電極板 6 と、整流用半導体パッケージ 1B を構成する第 2 電極板 101 が、第 1 のバスバー 2a の垂直面 d に第 1 のはんだ部材を介してはんだ付けされる。さらに、電力用半導体パッケージ 1A を構成する第 2 電極板 7 と、整流用半導体パッケージ 1B を構成する第 2 電極板 102 が、第 2 のバスバー 2b の垂直面 d にはんだ付けされる。

#### 【0026】

したがって、片状に形成される各半導体パッケージ 1A, 1B は、主面を立てた垂直姿勢となって、第 1 のバスバー 2a と第 2 のバスバー 2b により両面側から挟持され、かつ第 1、第 2 のはんだ部材を介してはんだ接合されて、前記パワー半導体モジュール M が構成される。

#### 【0027】

半導体パッケージ 1A, 1B と第 1、第 2 のバスバー 2a, 2b は、互いの垂直面同士をはんだ接合するので、本発明においては、第 1、第 2 のバスバー 2a, 2b、あるいは半導体パッケージ 1A、あるいは第 1 のはんだ部材 h と第 2 のはんだ部材 h に、はんだ接合厚さを最適にする、はんだ付け制御部（はんだ付け制御手段）を備えることとする。

#### 【0028】

以下、電力用半導体パッケージ 1A を対象として説明するが、整流用半導体パッケージ

10

20

30

40

50

1 Bについても全く同様にしてはんだ付けをなすので、ここでは整流用半導体パッケージ1 Bのはんだ付けについては説明を省略する。また、第1、第2のバスバー2 a, 2 bにおいては同一処理をなすが、図面上は一方のバスバーのみを図示し、かつ単に、「バスバー2」として表記する。

#### 【0029】

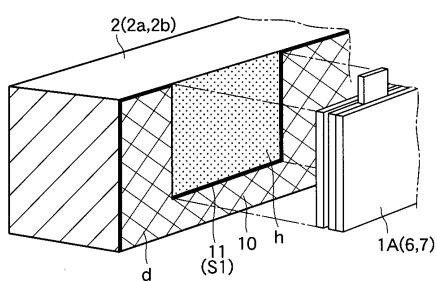

図3は、第1のバスバー2 aと、第2のバスバー2 bのそれぞれに、参考例である第1の実施の形態 [ただし、「参考例」との断り書きの無い実施の形態は、本発明の実施例である：以下、同]におけるはんだ付け制御部（はんだ付け制御手段）S 1を備えた、バスバー2の一部斜視図である。

第1のバスバー2 aの垂直な一面dと、第2のバスバー2 bの垂直な一面dは、図に交差ハッチングで示すはんだ付け制御部S 1であるところの、ソルダーレジスト膜1 0で被覆される。このソルダーレジスト膜1 0は厚さ20～30 μm程度であり、たとえば印刷により形成される。材質や種類については、特に限定されない。（以下、同じ）

前記ソルダーレジスト膜1 0には、所定間隔を存して複数（図では1つのみ示す）の、矩形状の開口部からなる取付け部1 1が設けられている。換言すれば、ソルダーレジスト膜1 0は取付け部1 1を残してバスバー2の垂直な一面dを全面的に覆っている。

#### 【0030】

前記第1のバスバー2 aに設けられる取付け部1 1には、第1のはんだ部材hがコーティングされ、前記第2のバスバー2 bに設けられる取付け部1 1には、第2のはんだ部材hがコーティングされる。

前記第1、第2のはんだ部材hとして、Sn-Pb共晶はんだ、鉛フリーはんだ、Pbリッチ高温はんだ等、どのようなはんだ材料であってもよい。また、取付け部1 1の形状に合せて切断されたはんだシート、印刷法により印刷されたはんだペースト、メッキもしくは蒸着により成膜されたはんだ等を使用することができる。（以下、同じ）

はんだ付け加工にあたって、第1のバスバー2 aの垂直面dを覆う前記ソルダーレジスト膜1 0の取付け部1 1に、半導体パッケージ1 Aの第1電極板6が位置合せされ、仮保持される。さらに、第2のバスバー2 bの垂直面dを覆う前記ソルダーレジスト膜1 0の取付け部1 1に、半導体パッケージ1 Aの第2電極板7が位置合せされ、仮保持される。

#### 【0031】

この状態で半導体パッケージ1 Aと第1、第2のバスバー2 a, 2 bが加熱炉に収容され、加熱される。所定時間経過後、第1のはんだ部材hは溶融し、第1電極板6と第1のバスバー2 aをはんだ接合する。同時に、第2のはんだ部材hは溶融し、第2電極板7と第2のバスバー2 bをはんだ接合する。

#### 【0032】

溶融したはんだ部材hは、特に重力の影響で、半導体パッケージ1 Aと取付け部1 1との下端部に多く溜る傾向にある。しかしながら、溶融したはんだ部材hが取付け部1 1を越えて、それ以上の範囲に濡れ拡がろうとしても、取付け部1 1の周囲はソルダーレジスト膜1 0で囲まれているので、ソルダーレジスト膜1 0によってはんだ部材の濡れ拡がりや、流れ落ちが確実に防止される。

#### 【0033】

このように、はんだ付け制御部S 1として、第1のバスバー2 aの垂直な一面dを覆うソルダーレジスト膜1 0に、第1電極板6の主面と同じ大きさの開口部である取付け部1 1を設け、第2のバスバー2 bの垂直な一面dを覆うソルダーレジスト膜1 0に、第2電極板7の主面と同じ大きさの開口部である取付け部1 1を設けることで、はんだ付けの必要領域にのみはんだ溜りを形成し、半導体パッケージ1 Aと第1、第2のバスバー2 a, 2 bとのはんだ付けに最適なはんだ接合厚さ(50～100 μm)を確保でき、はんだ継手の信頼性向上を得る。

#### 【0034】

なお、前記実施の形態のようにはんだ付け制御部S 1を構成するソルダーレジスト膜1 0の取付け部1 1を半導体パッケージ1 Aの第1、第2の電極板6, 7主面と同一とせず

10

20

30

40

50

、これよりも小に形成すると、必要なはんだ接合面積を確保できなくなり、はんだ付けの信頼性を損なう虞れがある。

#### 【0035】

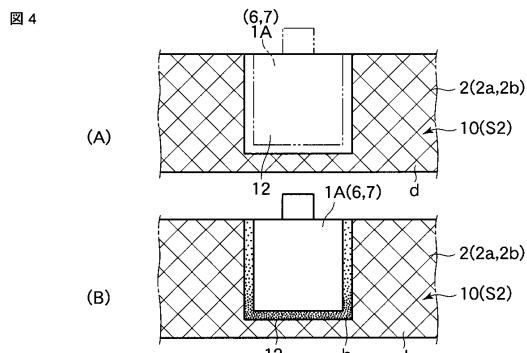

図4(A)は、第1のバスバー2aと第2のバスバー2bのそれぞれに、第2の実施の形態におけるはんだ付け制御部(はんだ付け制御手段)S2を備えた、バスバー2の一部正面図、図4(B)はバスバー2に半導体パッケージ1Aをはんだ付けした一部正面図である。

#### 【0036】

図4(A)に示すように、第1のバスバー2aの垂直な一面dと、第2のバスバー2bの垂直な一面dは、図に交差ハッチングで示す、はんだ付け制御部S2であるところのソルダーレジスト膜10で被覆される。

10

前記ソルダーレジスト膜10には、所定間隔を存して複数の(図では1つのみ示す)矩形状の開口部からなる取付け部12が設けられている。換言すれば、ソルダーレジスト膜10は取付け部12を残してバスバー2の垂直な一面dを全面的に覆っている。

#### 【0037】

第1のバスバー2aに設けられる前記取付け部12は、半導体パッケージ1Aの第1電極板6の主面(図に二点鎖線で示す)よりも大きな面積に形成され、第2のバスバー2bに設けられる前記取付け部12は、半導体パッケージ1Aの第2電極板7の主面(図に二点鎖線で示す)よりも大きな面積に形成される。

#### 【0038】

20

具体的には、はんだ接合時において、第1電極板6の上端縁と第1のバスバー2aの上端縁との位置が揃えられ、第2電極板7の上端縁と第2のバスバー2bの上端縁との位置が揃えられている。ただし、各電極板6,7の左右の幅寸法よりも取付け部12の左右の幅寸法が大に形成されるとともに、各電極板6,7の下端縁よりも取付け部12の下端縁が下方位置にある。

#### 【0039】

図4(B)に示すように、前記第1のバスバー2aのソルダーレジスト膜10に設けられる取付け部12に、第1のはんだ部材hがコーティングされ、前記第2のバスバー2bのソルダーレジスト膜10に設けられる取付け部12に、第2のはんだ部材hがコーティングされる。

30

#### 【0040】

そして、第1のバスバー2aにおけるソルダーレジスト膜10の取付け部12に、半導体パッケージ1Aの第1電極板6が位置合せされ、仮保持される。このとき、第1の電極板6上端縁と第1のバスバー2a上端縁の位置が揃えられるが、第1電極板6の左右の幅寸法よりも取付け部12の左右の幅寸法が大であり、第1電極板6の下端縁よりも取付け部12の下端縁が下方にある。

#### 【0041】

さらに、第2のバスバー2bにおけるソルダーレジスト膜10の取付け部12に、半導体パッケージ1Aの主面と対向する裏面を構成する第2電極板7が位置合せされ、仮保持される。このとき、第2の電極板7上端縁と第2のバスバー2b上端縁の位置が揃えられるが、第2電極板7の左右の幅寸法よりも取付け部12の左右の幅寸法が大であり、第2電極板7の下端縁よりも取付け部12の下端縁が下方にある。

40

#### 【0042】

半導体パッケージ1Aと第1、第2のバスバー2a,2bが加熱炉に収容され、加熱される。所定時間経過後、第1のはんだ部材hが溶融し、第1電極板6と第1のバスバー2aがはんだ接合される。同時に、第2のはんだ部材hも溶融し、第2電極板7と第2のバスバー2bがはんだ接合される。

#### 【0043】

第1の電極板6および第2の電極板7の左右側縁と下端縁は、取付け部12の左右側縁と下端縁とは間隙を存して形成されているので、加熱された第1、第2のはんだ部材hが

50

溶融して、第1電極板6全面と第1のバスバー2aを確実にはんだ接合し、第2電極板7全面と第2のバスバー2bを確実にはんだ接合したうえで、前記した各電極板6, 7と取付け部12との各端縁間に形成される隙間に滲出する。

#### 【0044】

溶融したはんだ部材hは、特に重力の影響で、各電極板6, 7の下端縁と取付け部12との下端縁間に形成される隙間に多く溜り易い。しかしながら、溶融したはんだ部材hが取付け部12を越えようとしても、ソルダーレジスト膜10によって濡れ拡がりや流れ落ちが防止される。

#### 【0045】

このように、はんだ付け制御部S1として、第1のバスバー2aの垂直な一面dを覆うソルダーレジスト膜10に、第1電極板6の主面よりも大きな面積の開口部である取付け部12を設け、第2のバスバー2bの垂直な一面dを覆うソルダーレジスト膜10に、第2電極板7の主面よりも大きな面積の開口部である取付け部12を設けることで、はんだ付けの必要領域にはんだ溜りを形成し、半導体パッケージ1Aと第1、第2のバスバー2a, 2bとのはんだ付けに最適なはんだ接合厚さ(50~100μm)を確保でき、はんだ付けの信頼性向上を得る。10

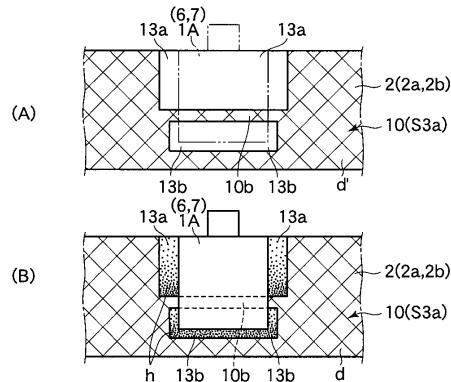

#### 【0046】

図5(A)は、第1のバスバー2aと第2のバスバー2bのそれぞれに、第3の実施の形態におけるはんだ付け制御部(はんだ付け制御手段)S3を備えた、バスバー2の一部正面図、図5(B)はバスバー2に半導体パッケージ1Aをはんだ付けした一部正面図である。20

図5(A)に示すように、第1のバスバー2aの垂直な一面dと、第2のバスバー2bの垂直な一面dは、図に交差ハッチングで示す、はんだ付け制御部S3であるところのソルダーレジスト膜10で被覆される。

#### 【0047】

第1のバスバー2aのソルダーレジスト膜10には、所定間隔を存して(図では1組のみ示す)複数の取付け部13a, 13bが設けられている。換言すれば、ソルダーレジスト膜10は取付け部13a, 13bを残して第1のバスバー2aの垂直な一面dを全面的に覆っている。

#### 【0048】

第2のバスバー2bのソルダーレジスト膜10には、所定間隔を存して(図では1組のみ示す)複数の取付け部13a, 13bが設けられている。換言すれば、ソルダーレジスト膜10は取付け部13a, 13bを残して第2のバスバー2bの垂直な一面dを全面的に覆っている。30

#### 【0049】

いずれのバスバー2a, 2bにおいても、前記取付け部13aは垂直面dの上端縁から上下方向の略半分位置までに亘って設けられるとともに、左右に2つずつ並設される。取付け部13bは、前記取付け部13aの下部側に離間した位置に設けられていて、この下端縁は垂直面dの下端から所定間隔を存している。そして、取付け部13bは左右に2つずつ並設される。40

#### 【0050】

ここでは、上部側取付け部13aを「第1の取付け部」と呼び、下部側取付け部13bを「第2の取付け部」と呼ぶ。第1の取付け部13a相互間の間隙と、第2の取付け部13b相互間の間隔は互いに同一であり、第1の取付け部13aと第2の取付け部13bとの間隙は互いに同一である。

#### 【0051】

すなわち、第1の取付け部13a相互間と、第2の取付け部13b相互間、および第1の取付け部13aと第2の取付け部13bとの相互には、同一幅で略十字状に形成されるソルダーレジスト膜10が介在する。

第1の取付け部13a相互間と第2の取付け部13b相互間に垂直方向に形成されるソ50

ルダーレジスト膜 10 部分を縦仕切り部 10 a と呼び、第 1 の取付け部 13 a の下端縁と第 2 の取付け部 13 b の上端縁との間に水平に形成されるソルダーレジスト膜 10 部分を横仕切り部 10 b と呼ぶ。

#### 【 0 0 5 2 】

特に横仕切り部 10 b は、第 1 の取付け部 13 a と第 2 の取付け部 13 b を上下二段に区画している。すなわち、ソルダーレジスト膜 10 は、第 1 のバスバー 2 a における第 1 電極板 6 がはんだ付けされる主面を覆うとともに、第 1 電極板 6 がはんだ付けされる位置に、第 1 電極板 6 の主面よりも大きな面積の取付け領域（第 1 、第 2 の取付け部 13 a , 13 b ）を区画するとともに、前記取付け領域が複数に区画されるように仕切り領域（横仕切り部 10 b ）を有する。

10

#### 【 0 0 5 3 】

さらに、ソルダーレジスト膜 10 は、第 2 のバスバー 2 b における第 2 電極板 7 がはんだ付けされる主面を覆うとともに、第 2 電極板 7 がはんだ付けされる位置に、第 2 電極板 7 の主面よりも大きな面積の取付け領域（第 1 、第 2 の取付け部 13 a , 13 b ）を区画するとともに、前記取付け領域が複数に区画されるように仕切り領域（横仕切り部 10 b ）を有する。

#### 【 0 0 5 4 】

図 5 ( B ) に示すように、前記第 1 のバスバー 2 a のソルダーレジスト膜 10 に設けられる第 1 の取付け部 13 a と第 2 の取付け部 13 b に、第 1 のはんだ部材 h がコーティングされ、前記第 2 のバスバー 2 b のソルダーレジスト膜 10 に設けられる第 1 の取付け部 13 a と第 2 の取付け部 13 b に、第 2 のはんだ部材 h がコーティングされる。

20

#### 【 0 0 5 5 】

そして、半導体パッケージ 1 A の第 1 電極板 6 の上端縁を第 1 のバスバー 2 a における垂直面 d 上端縁に合せるとともに、第 1 電極板 6 の幅方向の中央部を縦仕切り部 10 b に合せる。さらに、第 2 電極板 7 の上端縁を第 2 のバスバー 2 b における垂直面 d 上端縁に合せるとともに、第 2 電極板 7 の幅方向の中央部を縦仕切り部 10 b に合せる。

#### 【 0 0 5 6 】

この状態で、各第 1 の取付け部 13 a における左側部と右側部は、第 1 、第 2 電極板 6 , 7 の左側縁と右側縁から突出する。また、各第 2 の取付け部 13 b における左側部と下端部および右側部と下端部は、第 1 、第 2 電極板 6 , 7 の左側縁と下端縁および右側縁とした端縁から突出する。

30

#### 【 0 0 5 7 】

第 1 の取付け部 13 a の第 1 、第 2 電極板 6 , 7 から突出する部分が略 I 字状に形成され、第 2 の取付け部 13 b の第 1 、第 2 電極板 6 , 7 から突出する部分が互いに逆向きの略 L 字状に形成されることになる。なお、縦仕切り部 10 a と横仕切り部 10 b の、それほどんど大部分は、第 1 、第 2 電極板 6 , 7 によって覆われる。

#### 【 0 0 5 8 】

このように、第 1 のバスバー 2 a におけるソルダーレジスト膜 10 の第 1 、第 2 の取付け部 13 a , 13 b に、半導体パッケージ 1 A の第 1 電極板 6 を位置合せして仮保持する。さらに、第 2 のバスバー 2 b におけるソルダーレジスト膜 10 の第 1 、第 2 の取付け部 13 a , 13 b に、半導体パッケージ 1 A の第 2 電極板 7 を位置合せして仮保持する。

40

#### 【 0 0 5 9 】

この状態で半導体パッケージ 1 A と第 1 、第 2 のバスバー 2 a , 2 b を加熱炉に収容し、加熱する。所定時間経過後、第 1 、第 2 のはんだ部材 h が溶融し、第 1 電極板 6 の主面と第 1 のバスバー 2 a がはんだ接合され、第 2 の電極板 7 の主面と第 2 のバスバー 2 b がはんだ接合される。

#### 【 0 0 6 0 】

なお、第 1 の電極板 6 および第 2 の電極板 7 の左右側縁は、第 1 の取付け部 13 a の左右側縁とは間隙を存して形成されている。第 1 の電極板 6 および第 2 の電極板 7 の左右側縁と下端縁は、第 2 の取付け部 13 b の左右側縁と下端縁とは間隙を存して形成されてい

50

る。

#### 【0061】

したがって、加熱された第1、第2のはんだ部材hが溶融して、第1電極板6全面と第1のバスバー2aを確実にはんだ接合し、第2電極板7全面と第2のバスバー2bを確実にはんだ接合したうえで、前記した各電極板6, 7と第1、第2の取付け部13a, 13bとの端縁間に形成される隙間に滲出する。

#### 【0062】

溶融したはんだ部材hは、特に重力の影響で、各電極板6, 7から突出する第1の取付け部13aと第2の取付け部13bとの間に形成される隙間に多く溜り易い。しかしながら、この溶融したはんだ部材hが第1、第2の取付け部13a, 13bを越えようとしても、ソルダーレジスト膜10によって濡れ拡がりや流れ落ちが規制される。

10

#### 【0063】

すなわち、第1の取付け部13aで溶融するはんだ部材hが重力の影響を受けて第2の取付け部13b側に流れ落ちようとしても、ソルダーレジスト膜10で形成される横仕切り部10bが全てのはんだ部材hを第1の取付け部13aの範囲内に納まるよう規制する。

#### 【0064】

溶融したはんだ部材hは重力の影響で上部側に薄く、下部側に厚く溜り易い。この実施の形態では、面積の大きい第1の取付け部13aを上部に並べ、面積の小さい第2の取付け部13bを下部に並べ、半導体パッケージ1Aから突出する面積も第1の取付け部13aが第2の取付け部13bよりも大となるよう形成している。したがって、はんだ接合厚さは、第1の取付け部13aと第2の取付け部13bにおいてほとんど同量ずつ確保される。

20

#### 【0065】

このように、はんだ付け制御部S3として、ソルダーレジスト膜10は第1、第2の取付け部13a, 13bを横仕切り部10bで仕切ることで、はんだ付けの必要領域にはんだ溜りを形成して、はんだ接合厚さを最適化でき、はんだ付けの信頼性の向上化を得られる。

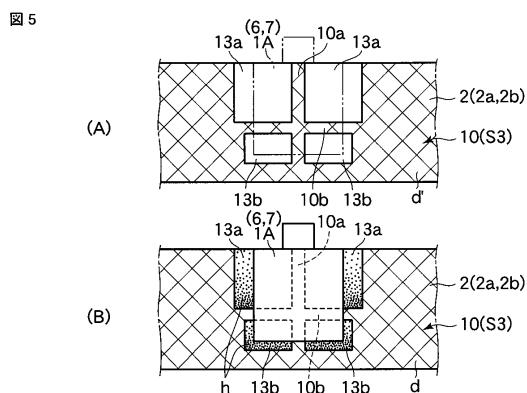

#### 【0066】

図6(A)は、上述した第3の実施の形態における変形例のはんだ付け制御部(はんだ付け制御手段)S3aを備えた、バスバー2の一部正面図、図6(B)はバスバー2に半導体パッケージ1Aをはんだ付けした状態の一部正面図である。

30

第3の実施の形態として上述したはんだ制御部S3と相違する点は、第1のバスバー2aと、第2のバスバー2bの垂直面dを覆うソルダーレジスト膜10に設けられる第1の取付け部13aと、第2の取付け部13bのそれぞれに、縦仕切り部10aが存在せず、横仕切り部10bのみによって仕切られている。

#### 【0067】

すなわち、ソルダーレジスト膜10の横仕切り部10bは、第1の取付け部13aと第2の取付け部13bとを上下2段に仕切っている。第1の取付け部13aの位置は同じであり、縦仕切り部10aが無い分、面積が大となる。第2の取付け部13bも位置は同じであり、縦仕切り部10aが無い分、面積が大となる。いずれも、半導体パッケージ1Aに対する突出面積と形状は変りがない。したがって、第3の実施の形態と同様の作用効果を得られる。

40

#### 【0068】

一方、上述したように半導体パッケージ1Aと、第1、第2のバスバー2a, 2bを第1、第2のはんだ部材hを介してはんだ付け加工する際には、片状の半導体パッケージ1Aを立てて垂直姿勢とする。そして、この半導体パッケージ1Aの正面にはんだ接合する第1のバスバー2aの取付け部は、バスバーの垂直面dに形成される。同様に、半導体パッケージ1Aの正面と対向する裏面にはんだ接合する第2のバスバー2bの取付け部は、バスバー2bの垂直面dに形成される。

50

## 【0069】

しかも、半導体パッケージ1Aを構成する絶縁基板8には引出し部Kが設けられていて、これを第1、第2のバスバー2a, 2bから突出させる必要がある。ここでは、第1、第2のバスバー2a, 2bの上端縁から突出させるべく、半導体パッケージ1Aの上端縁位置と、各バスバー2a, 2bの垂直面d上端縁とを位置合せして、前記引出し部Kを引出す。そのため、半導体パッケージ1Aの下端縁は、各バスバー2a, 2bの垂直面d下端縁と間隙を存した位置になる。

## 【0070】

半導体パッケージ1Aをはんだ付けするにあたって、半導体パッケージ1Aと第1、第2のバスバー2a, 2bのはんだ付け面が全て平坦な垂直面をなし、半導体パッケージ1Aを仮固定する手段がないので、バスバー2a, 2bに対する半導体パッケージ1Aの垂直方向の位置合せが難しい。10

たとえ、1個の半導体パッケージ1Aを正確に位置合せができたとしても、長手方向に長いバスバー2a, 2bに複数の半導体パッケージ1Aをはんだ付けするのであるから、他の半導体パッケージ1Aの位置がずれる虞れが生じる。

## 【0071】

また、半導体パッケージ1Aとバスバー2a, 2bとの間には第1、第2のはんだ部材が介在していて、加熱することで溶融し、当然、重力の影響を受けて流下する。バスバー2a, 2bは作業台上に載置されているので、これらの位置は変化しないが、半導体パッケージ1Aは言わば浮いた状態で各バスバー2a, 2b間に挟持されているだけなので、位置が変動する虞れが大である。20

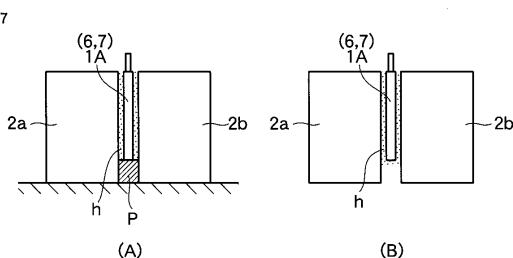

## 【0072】

そこで、特にはんだ加工中に、複数の全ての半導体パッケージ1Aにおいて位置の変動がないよう確実に支持する手段を提供する必要がある。

一つの支持手段として、図7(A)に示すように、半導体パッケージ1Aの浮き分に相当する高さ寸法のスペーサPを用意し、このスペーサP上に各半導体パッケージ1Aを支持する。半導体パッケージ1AとともにスペーサPも、第1のバスバー2aと第2のバスバー2bの間に挟持されることはない。

## 【0073】

前記スペーサPの素材は、たとえばガラエボ、ベークライト、テフロン(登録商標)、ポリイミド等の合成樹脂材、ステンレス、アルミニウムなどの金属材等の耐熱材で、はんだ付けされない素材が選択される。半導体パッケージ1Aとバスバー2a, 2bとのはんだ付け後、図7(B)に示すように、前記スペーサPを抜き出し、次のはんだ付けに用いる。30

## 【0074】

この場合、半導体パッケージ1AをスペーサP上に載置し、バスバー2a, 2b相互間に介在するだけで、はんだ部材hが溶融しても半導体パッケージ1Aの位置ずれがなく、有利である。

しかしながら、スペーサPは別部品であり、これを製作し、管理する手間が必要となる。しかも、スペーサPはバスバー2a, 2bと同一の長さ寸法が必要であり、かつ幅寸法は半導体パッケージ1Aの幅寸法と同一で、高さ寸法は極くわずかであるから、断面積が極端に小さい。そのため、実際のはんだ付け加工時には取扱いが極めて困難となる。40

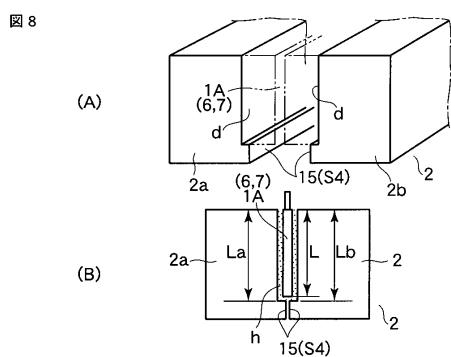

## 【0075】

そこで、第4の実施の形態では、第1のバスバー2aと第2のバスバー2bに、はんだ接合厚さを最適化するとともに、半導体パッケージ1Aのはんだ付け時の位置決めを容易化した、はんだ制御部S4を備えることとする。

## 【0076】

図8(A)は、第1のバスバー2aと第2のバスバー2bのそれぞれに、第4の実施の形態におけるはんだ付け制御部(はんだ付け制御手段)S4を備えた、バスバー2a, 2bの一部斜視図、図8(B)はバスバー2a, 2bに半導体パッケージ1Aをはんだ付け50

した状態の側面図である。

**【0077】**

第1のバスバー2aと第2のバスバー2b端部に、はんだ付け制御部（はんだ付け制御手段）S4が設けられている。このはんだ付け制御部S4は、第1のバスバー2aにおける垂直面dの下端部に設けられる第1の突条部15であり、第2のバスバー2bにおける垂直面dの下端部に設けられる第2の突条部15である。

**【0078】**

第1のバスバー2aの垂直面d上端縁から第1の突条部15の上端縁までの距離L<sub>a</sub>は、第1電極板6における垂直方向の一端縁から他端縁までの長さ寸法Lと略同一である。

第2のバスバー2bの垂直面d上端縁から第2の突条部15の上端縁までの距離は、第2電極板7における垂直方向の一端縁から他端縁までの長さ寸法Lと略同一である。実際には、第1のバスバー2aの垂直面dが第1の突条部15を残して切欠加工され、第2のバスバー2bの垂直面dが第2の突条部15を残して切欠加工される。

10

**【0079】**

それぞれのバスバー2a, 2bの垂直面dにおける、第1、第2の突条部15から上部側は、半導体パッケージ1Aの取付け部相互間のみソルダーレジスト膜10で覆われている。前記取付け部にはんだ部材がコーティングされていて、互いの取付け部に対向して半導体パッケージ1Aが位置合せされる。

**【0080】**

図8(B)に示すように、第1、第2のバスバー2a, 2b間に半導体パッケージ1Aをはんだ付けするにあたって、第1のバスバー2aと第2のバスバー2bの垂直面dを互いに対向させる。このとき、各バスバー2a、2bの下端部に設けられる第1、第2の突条部15相互を接触させず、ある程度離間する。

20

**【0081】**

すなわち、各突条部15の対向面の平坦度精度が低い状態で接触させると、バスバー2a, 2b相互が傾いて平行度を保持できない虞れがある。極めて高精度を保持する必要から工数に影響してしまう。したがって、各突条部15の対向面の平坦度精度を低くして工数への影響を避け、互いの対向面を離間させる。

**【0082】**

つぎに、半導体パッケージ1Aを各バスバー2a, 2bの第1、第2の突条部15上に載せる。具体的には、半導体パッケージ1Aを垂直姿勢にして第1電極板6を第1のバスバー2aに設けられる第1の突条15上に載せ、第2電極板7を第2のバスバー2bに設けられる第2の突条部15上に載せる。

30

**【0083】**

第1のバスバー2aの垂直面d上端縁から第1の突条部15の上端縁までの距離L<sub>a</sub>は、第1電極板6の垂直方向の長さ寸法Lと略同一であるので、バスバー2aの上端縁と第1電極板6上端縁の位置が略一致する。

同時に、第2のバスバー2bの垂直面d上端縁から第2の突条部15の上端縁までの距離L<sub>a</sub>は、第2電極板7の垂直方向の長さ寸法Lと略同一であるので、バスバー2bの上端縁と第2電極板7上端縁の位置が略一致する。

40

**【0084】**

すなわち、半導体パッケージ1Aを各バスバー2a, 2bの垂直面dに位置合せするのに、単に半導体パッケージ1Aを第1、第2の突条部15上に載せるだけで半導体パッケージ1Aの垂直方向の位置決めが容易にできることとなる。

半導体パッケージ1Aとバスバー2を加熱炉に入れて加熱すると、はんだ部材hが溶融する。第1電極板6は第1のバスバー2aに第1のはんだ部材hを介してはんだ付けされ、第2電極板7は第2のバスバー2bに第2のはんだ部材hを介してはんだ付けされる。さらに、取付け部周辺に形成されるソルダーレジスト膜によって、それぞれのはんだ部材hの濡れ拡がりが規制される。

**【0085】**

溶融したはんだ部材 h の一部が半導体パッケージ 1 A の下端部から流れ落ちようとしても、その下死点が第 1、第 2 の突条部 1 5 によって定まっている。換言すれば、第 1、第 2 の突条部 1 5 を設けることにより、この上部にはんだ溜りを形成して、各突条部 1 5 からバスバー 2 a , 2 b の下端面側へのはんだ部材 h の流出を阻止する。

#### 【 0 0 8 6 】

このように、はんだ付け制御部 S 4 として、第 1 のバスバー 2 a の下端部に第 1 の突条部 1 5 を設け、第 2 のバスバー 2 b の下端部に第 2 の突条部 1 5 を設けることにより、半導体パッケージ 1 A を第 1 の突条部 1 5 と第 2 の突条部 1 5 に載せるだけで、半導体パッケージ 1 A の垂直方向の位置決めが容易に可能である。

#### 【 0 0 8 7 】

そして、これら突条部 1 5 を下死点として、この上部であるはんだ付けの必要領域にはんだ溜りを確実に形成でき、よってはんだ接合厚さを最適化し、はんだ付けの信頼性の向上化を得られる。

#### 【 0 0 8 8 】

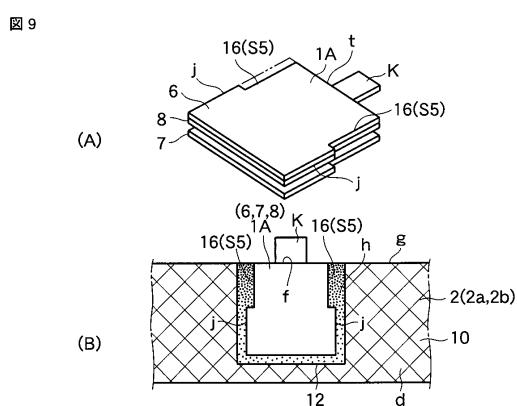

図 9 ( A ) は第 5 の実施の形態を説明する、半導体パッケージ 1 A の斜視図、図 9 ( B ) は半導体パッケージ 1 A をバスバー 2 にはんだ付けした一部正面図である。この実施の形態では、半導体パッケージ 1 A にはんだ付け制御部 ( はんだ付け制御手段 ) S 5 を備えている。

#### 【 0 0 8 9 】

先に説明したように、半導体パッケージ 1 A を構成する絶縁基板 8 は、第 1 電極板 6 および第 2 電極板 7 の外周縁 f より外側に突出する引出し部 K を備えていて、この引出し部 K に前記パワー半導体素子 5 の制御電極と接続する外部接続端子が設けられる。

また、半導体パッケージ 1 A を構成する第 1 電極板 6 と、第 2 電極板 7 および絶縁基板 8 は、平面視で矩形状に形成されていて、第 1 のバスバー 2 a および第 2 のバスバー 2 b の上端縁 g と位置を合せられる前記外周縁 f から、前記引出し部 K の突出方向と逆方向に形成される加工用辺部 j を備えている。

#### 【 0 0 9 0 】

前記はんだ付け制御部 S 5 は、前記加工用辺部 j の外周縁 f から所定距離に亘って設けられる切欠部 1 6 である。具体的には、第 1、第 2 の電極板 6 , 7 と絶縁板 8 は、半導体パッケージ 1 A がバスバー 2 にはんだ付けされた状態での左右両辺部 ( すなわち、加工用辺部 ) j で、しかもそれぞれの辺部 j における上端縁 f から略半分程度の距離に亘って、辺部 j 端縁と平行で幅寸法が略 0 . 5 ~ 1 mm 程度の切欠部 1 6 が設けられる。

#### 【 0 0 9 1 】

図 9 ( B ) に示すように、第 1 のバスバー 2 a と、第 2 のバスバー 2 b のそれぞれ垂直面 d は、半導体パッケージ 1 A 外形面積よりも大きな取付け部 1 2 を形成するソルダーレジスト膜 1 0 で覆われ、前記取付け部 1 2 にははんだ部材 h がコーティングされる。

そして、取付け部 1 2 に対して半導体パッケージ 1 A が位置決めされ、加熱炉に収容されて加熱される。はんだ部材 h は溶融し、第 1 電極板 6 と第 1 のバスバー 2 a が第 1 のはんだ部材 h を介してはんだ接合され、第 2 電極板 7 と第 2 のバスバー 2 b が第 2 のはんだ部材 h を介してはんだ接合される。このとき、取付け部 1 2 周辺のソルダーレジスト膜 1 0 によって、各はんだ部材 h の取付け部 1 2 外への濡れ拡がりと流れ落ちが規制される。

#### 【 0 0 9 2 】

半導体パッケージ 1 A の第 1 電極板 6 と、第 2 電極板 7 および絶縁基板 8 の両加工用辺部 j に複数の切欠部 1 6 が設けられていて、この切欠部 1 6 に溶融したはんだ部材 h が多く溜る。しかも、切欠部 1 6 は半導体パッケージ 1 A の上半分に位置するので、加工用辺部 j において下部側よりも上部側に多くのはんだ部材 h が溜ることになる。

そして、切欠部 1 6 と取付け部 1 2 側縁であるソルダーレジスト膜 1 0 との間の間隔が、切欠部 1 6 を除く加工用辺部 j 側縁とソルダーレジスト膜 1 0 との間隔よりも大に形成されていて、より多くのはんだ部材 h が溜まる。

#### 【 0 0 9 3 】

10

20

30

40

50

先にも説明したように、溶融したはんだ部材 h は重力の影響で上部側に薄く、下部側に厚く溜り易い。そこでこの実施の形態では、半導体パッケージ 1 A の上半分に切欠部 1 6 を設け、ソルダーレジスト膜 1 0 との間隔を下半分の間隔よりも大に形成した。切欠部 1 6 は溶融したはんだ部材 h をより多く溜める、はんだ溜り（フィレット）となり、はんだ部材 h の接合厚さの最適化が得られ、はんだ付けの信頼性の向上化を得られる。

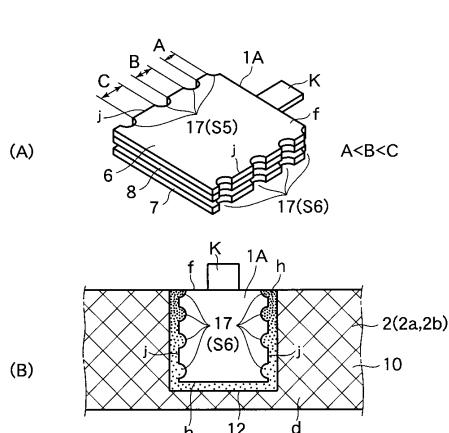

#### 【0094】

図 10 (A) は参考例である第 6 の実施の形態を説明する、半導体パッケージ 1 A の斜視図、図 10 (B) は半導体パッケージ 1 A をバスバー 2 にはんだ付けした一部正面図である。この実施の形態では、半導体パッケージ 1 A にはんだ付け制御部（はんだ付け制御手段）S 6 を備えている。10

#### 【0095】

図 10 (A) に示すように、半導体パッケージ 1 A を構成する絶縁基板 8 は、第 1 電極板 6 および第 2 電極板 7 の外周縁 f より外側に突出する引出し部 K を備えている。第 1 電極板 6 と、第 2 電極板 7 および絶縁基板 8 は平面視で矩形状に形成され、第 1 のバスバー 2 a および第 2 のバスバー 2 b の上端縁 g と位置を合せられる外周縁 f から、引出し部 K の突出方向と逆方向に加工用辺部 j を備えている。

#### 【0096】

さらに、半導体パッケージ 1 A を構成する第 1、第 2 電極板 6, 7 と絶縁板 8 の両加工用辺部 j には、複数の半円状もしくは四分の 1 円状の複数の切欠部 1 7 が設けられていて、これら切欠部 1 7 で、はんだ付け制御部 S 6 が構成される。20

#### 【0097】

ここでは、各加工用辺部 j に設けられる切欠部 1 7 は、4 つずつ設けられる。それぞれの切欠部 1 7 は互いに同一の半径であり、したがって半円状の切欠部 1 7 の切欠面積は全て同一である。

#### 【0098】

ただし、各切欠部 1 7 相互の間隔は、半導体パッケージ 1 A の外周縁 f から下端部に亘って漸次広く形成されている。図において、最上端（1 段目）の切欠部 1 7 と 2 段目の切欠部 1 7 との間隔を A、2 段目の切欠部 1 7 と 3 段目の切欠部 1 7 との間隔を B、3 段目の切欠部 1 7 と最下端（4 段目）の切欠部 1 7 との間隔を C としたとき、 $A < B < C$  に設定される。30

#### 【0099】

図 10 (B) に示すように、バスバー 2 の垂直面 d は半導体パッケージ 1 A よりも大きな面積の取付け部 1 2 を形成するソルダーレジスト膜 1 0 で覆われ、取付け部 1 2 にはんだ部材 h がコーティングされる。

そして、取付け部 1 2 に対して半導体パッケージ 1 A が位置決めされ、加熱炉に収容されて加熱される。はんだ部材 h は溶融し、第 1 電極板 6 と第 1 のバスバー 2 a が第 1 のはんだ部材 h を介してはんだ接合され、第 2 電極板 7 と第 2 のバスバー 2 b が第 2 のはんだ部材 h を介してはんだ接合される。このとき、取付け部 1 2 周辺のソルダーレジスト膜 1 0 によって、はんだ部材 h の濡れ拡がりと流れ落ちが規制される。40

#### 【0100】

半導体パッケージ 1 A の両加工用辺部 j に複数の切欠部 1 7 が設けられていて、切欠部 1 7 は溶融したはんだ部材 h がより多く溜る、はんだ溜りとなる。切欠部 1 7 相互の間隔が、加工用辺部 j の外周縁 f 側から下端部に亘って漸次広く形成されているので、上部側の切欠部 1 7 に溶融したはんだ部材 h が多く溜り、下部側の切欠部 1 7 になるにつれて、はんだ部材 h が溜る量が少くなる。

#### 【0101】

先にも説明したように、溶融したはんだ部材 h は重力の影響で上部側に薄く、下部側に厚く溜り易い。そこでこの実施の形態では、同一の切欠面積に形成される切欠部 1 7 の相互間隔を、加工用辺部 j の上部から下部に亘って漸次広く形成して、上部側に溶融したはんだ部材 h をより多く溜める。よって、はんだ部材 h の接合厚さの最適化が得られ、はん50

だ付けの信頼性の向上化を得られる。

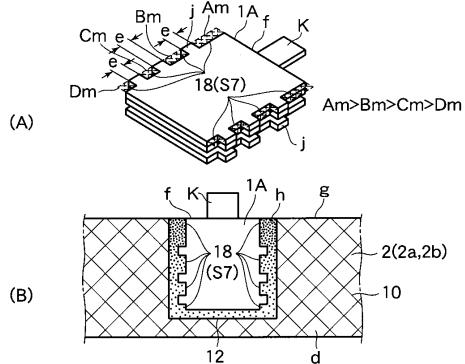

**【0102】**

図11(A)は第7の実施の形態を説明する、半導体パッケージ1Aの斜視図、図11(B)は半導体パッケージ1Aをバスバー2にはんだ付けした一部正面図である。この実施の形態では、半導体パッケージ1Aにはんだ付け制御部(はんだ付け制御手段)S7を備えている。

**【0103】**

図11(A)に示すように、半導体パッケージ1Aを構成する絶縁基板8は、第1電極板6および第2電極板7の外周縁fより外側に突出する引出し部Kを備えている。第1電極板6と、第2電極板7および絶縁基板8は平面視で矩形状に形成され、第1のバスバー2aおよび第2のバスバー2bの上端縁gと位置を合せられる外周縁fから、引出し部Kの突出方向と逆方向に加工用辺部jを備えている。10

**【0104】**

さらに、半導体パッケージ1Aを構成する第1、第2電極板6,7と絶縁板8の両加工用辺部jには、複数の切欠部18が設けられていて、これらの切欠部18で、はんだ付け制御部S7が構成される。

**【0105】**

ここでは、各加工用辺部jに設けられる切欠部18は、4つずつ設けられる。それぞれの切欠部18相互の間隔eは全て同一に形成され、かつ切欠部18自体の幅寸法は全て同一であるが、切欠部18の長さ寸法が互いに相違し、したがって切欠面積が互いに相違している。20

**【0106】**

具体的には、半導体パッケージ1Aの外周縁fから下端部に亘って切欠部18相互の切欠面積が、漸次、小さくなるよう形成されている。すなわち、最上端(1段目)の切欠部18の切欠面積をAm、2段目の切欠部18の切欠面積をBm、3段目の切欠部18の切欠面積をCm、最下端(4段目)の切欠部18の切欠面積をDmとしたとき、 $Am > Bm > Cm > Dm$ に設定される。

**【0107】**

図11(B)に示すように、第1のバスバー2aと、第2のバスバー2bの垂直面dは、半導体パッケージ1Aよりも大きな面積の取付け部12を形成するソルダーレジスト膜10で覆われ、取付け部12にはんだ部材hがコーティングされる。30

そして、取付け部12に対して半導体パッケージ1Aが位置決めされ、加熱炉に収容されて加熱される。はんだ部材hは溶融し、第1電極板6と第1のバスバー2aが第1のはんだ部材hを介してはんだ接合され、第2電極板7と第2のバスバー2bが第2のはんだ部材hを介してはんだ接合される。このとき、取付け部12周辺のソルダーレジスト膜10によって、各はんだ部材hの濡れ拡がりと流れ落ちが規制される。

**【0108】**

半導体パッケージ1Aの第1電極板6と、第2電極板7および絶縁基板8の両加工用辺部jに複数の切欠部18が設けられて、これらの切欠部18は溶融したはんだ部材hがより多く溜る、はんだ溜りとなる。切欠部18の切欠面積が加工用辺部jの外周縁fである上端部から下端部に亘って漸次小さく形成されるので、上部側の切欠部18に溶融したはんだ部材hが多く溜り、下部側の切欠部18になるにしたがって、はんだ部材hが溜る量が少くなる。40

**【0109】**

先にも説明したように、溶融したはんだ部材hは重力の影響で上部側に薄く、下部側に厚く溜り易い。そこでこの実施の形態では、切欠部18の切欠面積を、加工用辺部jの上部から下部に亘って漸次狭く形成して、上部側に溶融したはんだ部材hをより多く溜める。よって、はんだ部材hの接合厚さの最適化が得られ、はんだ付けの信頼性の向上化を得られる。

**【0110】**

50

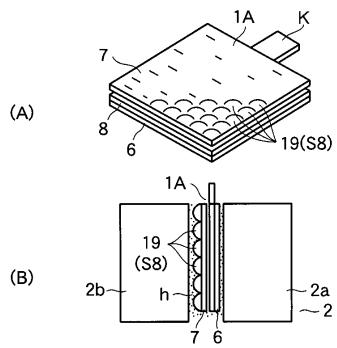

図12(A)は参考例である第8の実施の形態を説明する、半導体パッケージ1Aの斜視図、図12(B)は半導体パッケージ1Aをはんだ付けした側面図である。この実施の形態では、半導体パッケージ1Aにはんだ付け制御部(はんだ付け制御手段)S8を備えている。

図12(A)に示すように、半導体パッケージ1Aを構成する第2電極板7の正面に、この全面に亘って、同一高さの複数の小突起19が設けられていて、これら小突起19ではんだ付け制御部S8を構成する。

#### 【0111】

なお説明すると、第1電極板6と第2電極板7は、たとえば銅材などの金属材が用いられているので、いわゆるローレット加工が可能である。したがって、ここでは第2電極板17の表面をローレット加工して、突出量が0.05~0.1mm程度の多数の球状小突起19を形成する(なお、同図において、小突起19を誇張して示している)。

#### 【0112】

図12(B)に示すように、半導体パッケージ1Aとバスバー2とのはんだ付けにあたって、第1電極板6を第1のバスバー2aに当接し、第2電極板7を第2のバスバー2bに当接する。この状態で、第2電極板7の正面に設けられる球状小突起19の頂部が第2のバスバー2bの垂直面に当接する。したがって、それぞれの球状小突起19相互間に、球状小突起19の突出量と同一の凹部が形成されることになる。

#### 【0113】

各バスバー2a, 2bの垂直面dは、半導体パッケージ1A正面よりも大きな面積の取付け部を形成するソルダーレジスト膜で覆われていて、取付け部にはんだ部材がコーティングされている。取付け部に半導体パッケージ1Aが位置決めされ、加熱炉に入れられて加熱される。

#### 【0114】

はんだ部材hは溶融し、第1電極板6と第1のバスバー2aが第1のはんだ部材hを介してはんだ接合され、第2電極板7と第2のバスバー2bが第2のはんだ部材hを介してはんだ接合される。このとき、取付け部12周辺のソルダーレジスト膜10によって、各はんだ部材hの濡れ拡がりと流れ落ちが規制される。

#### 【0115】

半導体パッケージ1Aの第2電極板7の正面に複数の球状小突起19が設けられていて、球状小突起19相互間に形成される凹部にはんだ部材hが溜る、はんだ溜りとなる。先にも説明したように、溶融したはんだ部材hは重力の影響で上部側に薄く、下部側に厚く溜り易い。

#### 【0116】

そこでこの実施の形態では、半導体パッケージ1Aの第2電極板7正面に多数の球状小突起19を設け、これら球状小突起19相互間の凹部に溶融したはんだ部材hを溜めることができる。よって、はんだ部材hの接合厚さの最適化が得られ、はんだ付けの信頼性の向上化を得られる。

#### 【0117】

なお、前記実施の形態では小突起19として球状をなすように形成したが、この形状に限定されるものではない。そして、小突起19ばかりでなく、たとえばディンプル状であってもよく、複眼レンズ状等の凹部を設けてよい。要は半導体パッケージ1A正面とバスバー2との間に、はんだ溜りを形成できればよい。また、小突起19を第2電極板7に設けたが、第1電極板6に設けてもよく、第1電極板6と第2電極板7の両方に設けてよい。

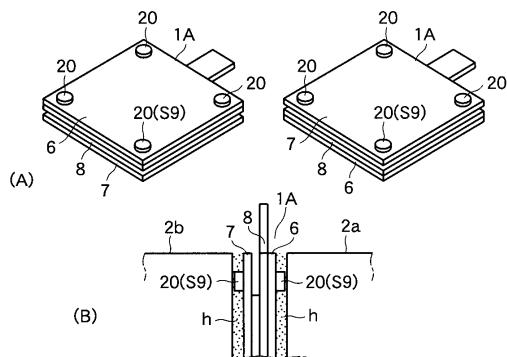

#### 【0118】

図13(A)は参考例である第9の実施の形態を説明する、半導体パッケージ1Aの正面側と裏面側の斜視図、図11(B)はバスバー2に半導体パッケージ1Aをはんだ付けした一部拡大図である。この実施の形態では、半導体パッケージ1Aにはんだ付け制御部(はんだ付け制御手段)S9を備えている。

10

20

30

40

50

## 【0119】

図13(A)に示すように、半導体パッケージ1Aを構成する第1電極板6と第2電極板7のそれぞれ正面の四隅部にスペーサ用突部20が設けられていて、これらスペーサ用突部20ではんだ付け制御部S9を構成する。

なお説明すると、前記スペーサ用突部20は直径が0.5~1mm程度の円形状(限定されない)をなし、その突出量は半導体パッケージ1Aとバスバー2とのはんだ接合に必要なはんだ厚と略同等の、0.03~0.5mm程度である。

## 【0120】

図13(B)に示すように、半導体パッケージ1Aとバスバー2とのはんだ接合にあたって、第1のバスバー2aと第2のバスバー2bとの間に半導体パッケージ1Aが挟持される。すなわち、各バスバー2の垂直面は半導体パッケージ1Aよりも大きな面積の取付け部を形成するソルダーレジスト膜で覆われ、前記取付け部にはんだ部材hがコーティングされている。そして、取付け部に対して半導体パッケージ1Aが位置決めされ、各バスバー2a, 2b間に挟持され、加熱炉に収容される。

10

## 【0121】

はんだ部材hは溶融し、第1電極板6と第1のバスバー2aが第1のはんだ部材hを介してはんだ接合され、第2電極板7と第2のバスバー2bが第2のはんだ部材hを介してはんだ接合される。このとき、取付け部12周辺のソルダーレジスト膜10によって、各はんだ部材hの濡れ拡がりと流れ落ちが規制される。

20

## 【0122】

なお、半導体パッケージ1Aとバスバー2とのはんだ付け加工の際に、バスバー2に対して半導体パッケージ1Aを位置合せして挟持するが、このとき半導体パッケージ1Aに位置ずれが生じないよう、ある程度は強い圧力が必要である。

ところが、この圧力が強過ぎれば、溶融したはんだ部材hがバスバー2と半導体パッケージ1Aとの間に介在し難くなり、必要量のはんだ接合厚を確保できなくなる虞れがある。圧力が弱過ぎれば、はんだ接合厚さが必要以上に厚くなってしまい、全面に亘って均一なはんだ厚を確保できなくなる。

## 【0123】

そこでこの実施の形態では、半導体パッケージ1Aの両面にスペーサ用突部20を設けて第1のバスバー2aと第2のバスバー2bに当接させ、半導体パッケージ1Aに対してバスバー2に強い圧力を付与し、半導体パッケージ1Aを強固に挟持したうえで、はんだ部材hを溶融させる。

30

## 【0124】

半導体パッケージ1Aに対してバスバー2から強い圧力で押付けても、半導体パッケージ1Aとバスバー2との間にはスペーサ用突部20が介在し、この突出量の間隙が確保されているから、溶融したはんだ部材hはスペーサ用突部20によって形成される間隙を円滑に、かつ確実に満たす。したがって、はんだ部材hの接合厚さの最適化が得られ、はんだ付けの信頼性の向上化を得られる。

## 【0125】

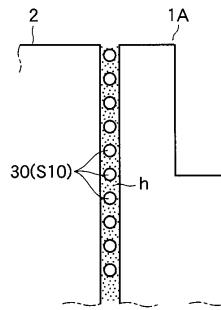

図14は第10の実施の形態を説明する、はんだ付された半導体パッケージ1Aとバスバー2の一部拡大図である。この実施の形態は、半導体パッケージ1Aとバスバー2をはんだ付けするはんだ部材h中に、はんだ付け制御部S10を備えている。

40

すなわち、はんだ付け制御部S10は、はんだ部材h中に混入される多数の粉末状のスペーサ用ボール(金属ボール)30からなる(図では、スペーサ用ボール30を誇張して描いている)。前記スペーサ用ボール30は直径が0.03~0.5mm程度であり、素材としてニッケル、銅、もしくはアルミニウムにニッケルメッキを施している。いずれも、はんだに固溶しない金属材が選択される。

## 【0126】

そして、はんだ部材hをシート状に圧延して前記スペーサ用ボール30を略均一な状態に配置する。このはんだシートを、バスバー2の垂直面を覆う前記ソルダーレジスト膜の

50

取付け部の形状面積に合せて切断し、半導体パッケージ 1 A とバスバー 2との間に挟み込んで保持する。このときの重ね合わせの圧力は半導体パッケージ 1 A に位置ずれが生じないよう、強固であってよい。

#### 【0127】

この状態で加熱炉に入れ加熱するとはんだ部材 h は溶融し、第 1 電極板 6 と第 1 のバスバー 2 a が第 1 のはんだ部材 h を介してはんだ接合され、第 2 電極板 7 と第 2 のバスバー 2 b が第 2 のはんだ部材 h を介してはんだ接合される。このとき、取付け部 1 2 周辺のソルダーレジスト膜 1 0 によって、各はんだ部材 h の濡れ拡がりと流れ落ちが規制される。

#### 【0128】

なお、はんだ部材 h に混在するスペーサ用ボール 3 0 は半導体パッケージ 1 A とバスバー 2との間に挟持され、これらの間隙を確保する。すなわち、スペーサ用ボール 3 0 の存在により、半導体パッケージ 1 A とバスバー 2との間のはんだ接合厚を必要量だけ確保できる。

#### 【0129】

このように、はんだ付け制御部 S 9 として、はんだ部材 h 中に多数の粉末状のスペーサ用ボール（金属ボール）3 0 を混入したので、半導体パッケージ 1 A とバスバー 2とのはんだ付けにともなって、はんだ接合厚さの最適化が得られ、はんだ付けの信頼性の向上化を得られる。

#### 【0130】

なお、本発明は上述した実施の形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。そして、上述した実施の形態に開示されている複数の構成要素の適宜な組み合わせにより種々の発明を形成できる。

#### 【図面の簡単な説明】

#### 【0131】

【図 1】本発明における実施の形態に係る、パワー半導体モジュール一部の平面図と正面図。

【図 2】同実施の形態に係る、半導体パッケージとバスバーとのはんだ付けを説明する斜視図。

【図 3】はんだ付け制御手段に係る第 1 の実施の形態での、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 4】はんだ付け制御手段に係る第 2 の実施の形態での、バスバーの一部正面図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 5】はんだ付け制御手段に係る第 3 の実施の形態での、バスバーの一部正面図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 6】はんだ付け制御手段に係る第 3 の実施の形態での変形例を示す、バスバーの一部正面図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 7】はんだ付け制御手段に係る参考例での、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 8】はんだ付け制御手段に係る第 4 の実施の形態での、バスバーの一部斜視図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 9】はんだ付け制御手段に係る第 5 の実施の形態での、半導体パッケージの斜視図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 10】はんだ付け制御手段に係る第 6 の実施の形態での、半導体パッケージの斜視図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 11】はんだ付け制御手段に係る第 7 の実施の形態での、半導体パッケージの斜視図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 12】はんだ付け制御手段に係る第 8 の実施の形態での、半導体パッケージの斜視図と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図 13】はんだ付け制御手段に係る第 9 の実施の形態での、半導体パッケージの斜視図

10

20

30

40

50

と、バスバーと半導体パッケージのはんだ付けを説明する図。

【図14】はんだ付け制御手段に係る第10の実施の形態での、バスバーと半導体パッケージのはんだ付けを説明する図。

### 【符号の説明】

( 0 1 3 2 )

5 … パワー半導体素子、 6 … 第 1 電極板、 7 … 第 2 電極板、 8 … 絶縁基板、 1 A … 半導体パッケージ（半導体装置）、 h …（第 1 、第 2 の）はんだ部材、 2 a … 第 1 バスバー、 2 b … 第 2 のバスバー、 S 1 ~ S 1 0 … はんだ付け制御部（はんだ付け制御手段）、 1 1 , 1 2 , 1 3 a , 1 3 b … 取付け部、 1 0 … ソルダーレジスト膜、 1 0 b …（横）仕切り部、 1 5 …（第 1 、第 2 の）突条部、 K … 引出し部、 j … 加工辺部、 1 6 , 1 7 , 1 8 … 切欠部、 1 9 … 小突起、 2 0 … スペーサ用突起、 3 0 … 金属ボール。 10

〔 1 〕

【 2 】

【 3 】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図 1 1】

図 11

【図 1 3】

図 13

【図 1 2】

図 12

【図 1 4】

図 14

---

フロントページの続き

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 渡邊 尚威

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 坂本 薫昭

(56)参考文献 特開昭60-001837(JP,A)

特開2002-164485(JP,A)

特開2003-110064(JP,A)

特開2004-087609(JP,A)

特開2004-140068(JP,A)

特開2008-085201(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/48-50

H01L 25/00-18