(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-190045

(P2012-190045A)

(43) 公開日 平成24年10月4日(2012.10.4)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G09F 9/30</b> (2006.01)  | GO9F 9/30  | 338 3K107   |

| <b>H01L 27/32</b> (2006.01) | GO9F 9/30  | 365Z 5C094  |

| <b>H01L 51/50</b> (2006.01) | HO5B 33/14 | A           |

| <b>HO5B 33/26</b> (2006.01) | HO5B 33/26 | Z           |

審査請求 有 請求項の数 9 O L (全 29 頁)

|            |                                     |          |                                               |

|------------|-------------------------------------|----------|-----------------------------------------------|

| (21) 出願番号  | 特願2012-119382 (P2012-119382)        | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日   | 平成24年5月25日 (2012.5.25)              | (74) 代理人 | 100095728<br>弁理士 上柳 雅善                        |

| (62) 分割の表示 | 特願2011-245314 (P2011-245314)<br>の分割 | (74) 代理人 | 100107261<br>弁理士 須澤 修                         |

| 原出願日       | 平成22年4月23日 (2010.4.23)              | (74) 代理人 | 100127661<br>弁理士 宮坂 一彦                        |

|            |                                     | (72) 発明者 | 窪田 岳彦<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

|            |                                     | (72) 発明者 | 神田 栄二<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

|            |                                     |          | 最終頁に続く                                        |

(54) 【発明の名称】発光装置および電子機器

## (57) 【要約】

【課題】電源線の抵抗を抑制しながら各要素を電源線と同層から形成する。

【解決手段】基板10の面上には駆動トランジスタTdrと素子導通部71と初期化トランジスタTintと接続部61とが配置される。駆動トランジスタTdrは、電源線15から発光素子Eに供給される電流量を制御する。素子導通部71は、駆動トランジスタTdrと発光素子Eとを電気的に接続する。初期化トランジスタTintは、オン状態に遷移することで駆動トランジスタTdrをダイオード接続する。接続部61は、駆動トランジスタTdrと初期化トランジスタTintとを電気的に接続する。電源線15はX方向に延在する。素子導通部71および接続部61は、電源線15と同層から形成され、基板10に垂直な方向からみて、駆動トランジスタTdrを挟んで電源線15の幅方向(Y方向)における一方の側に位置する。

【選択図】図7

**【特許請求の範囲】****【請求項 1】**

電源線から発光素子に供給される電流量を制御する駆動トランジスタと、前記駆動トランジスタと前記発光素子とを電気的に接続する素子導通部と、オン状態に変化することで前記駆動トランジスタをダイオード接続する初期化トランジスタと、前記駆動トランジスタと前記初期化トランジスタとを電気的に接続する接続部とが基板上に配置された発光装置であって、

前記電源線は、所定の方向に延在する第1部分を含み、

前記素子導通部および前記接続部は、前記電源線と同層から形成され、前記駆動トランジスタを挟んで前記第1部分の幅方向における一方の側に位置する

10

ことを特徴とする発光装置。

**【請求項 2】**

前記駆動トランジスタのゲート電極に電気的に接続された容量素子を具備し、

前記容量素子は、前記駆動トランジスタを挟んで前記接続部および前記素子導通部の反対側に配置され、

前記電源線の第1部分は、前記容量素子と重なり合う

請求項1に記載の発光装置。

**【請求項 3】**

選択信号に応じてオン状態またはオフ状態となる選択トランジスタを具備し、

前記駆動トランジスタのゲート電極は、オン状態となった前記選択トランジスタを介してデータ線から供給されるデータ信号に応じた電位に設定され、

20

前記選択トランジスタは、前記容量素子を挟んで前記駆動トランジスタとは反対側に配置される

請求項2に記載の発光装置。

**【請求項 4】**

前記駆動トランジスタと前記選択トランジスタと前記初期化トランジスタとを各々が含む複数の単位素子が前記所定の方向とは交差する方向に配列し、

前記選択トランジスタは、前記所定の方向に沿った一方の側に配置され、

前記初期化トランジスタは、前記所定の方向に沿った他方の側に配置される

請求項3に記載の発光装置。

30

**【請求項 5】**

電源線から発光素子に供給される電流量を制御する駆動トランジスタと、前記駆動トランジスタと前記発光素子とを電気的に接続する素子導通部と、オン状態に変化することで前記駆動トランジスタをダイオード接続する初期化トランジスタと、前記駆動トランジスタと前記初期化トランジスタとを電気的に接続する接続部とが基板上に配置された発光装置であって、

前記電源線は、所定の方向に延在する第1部分を含み、

前記素子導通部および前記接続部は、前記電源線と同層から形成され、

前記素子導通部は、前記駆動トランジスタを挟んで前記第1部分の幅方向における一方の側に位置し、前記接続部は、前記駆動トランジスタに対して前記第1部分の幅方向における他方の側に位置する

40

ことを特徴とする発光装置。

**【請求項 6】**

前記駆動トランジスタのゲート電極に電気的に接続された容量素子を具備し、

前記容量素子は、前記駆動トランジスタと前記接続部との間隙に配置され、

前記電源線の第1部分は、前記容量素子と重なり合う

請求項1に記載の発光装置。

**【請求項 7】**

選択信号に応じてオン状態またはオフ状態となる選択トランジスタを具備し、

前記駆動トランジスタのゲート電極は、オン状態となった前記選択トランジスタを介し

50

てデータ線から供給されるデータ信号に応じた電位に設定され、

前記選択トランジスタは、前記容量素子を挟んで前記駆動トランジスタとは反対側に配置される

請求項 6 に記載の発光装置。

【請求項 8】

前記駆動トランジスタと前記素子導通部と前記初期化トランジスタと前記接続部とを各々が含む複数の単位素子が前記所定の方向とは交差する方向に配列し、

前記電源線は、前記各単位素子に対応する複数の前記第1部分と、相互に隣接する各第1部分を連結する第2部分とを含む

請求項 1 または請求項 5 に記載の発光装置。

10

【請求項 9】

請求項 1 から請求項 8 の何れかに記載の発光装置を具備する電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機 E L (ElectroLuminescent) 材料などの発光材料を利用した発光装置の構造に関する。

【背景技術】

【0002】

発光素子に供給される電流量を制御するトランジスタ（以下「駆動トランジスタ」という）が発光素子ごとに配置されたアクティブマトリクス方式の発光装置が従来から提案されている。また、例えば特許文献 1 や特許文献 2 には、駆動トランジスタの閾値電圧の誤差を補償するためのトランジスタ（以下「初期化トランジスタ」という）が駆動トランジスタのゲート電極とドレン電極（またはソース電極）との間に介在する構成も開示されている。この構成においては、初期化トランジスタがオン状態に変化して駆動トランジスタがダイオード接続されると、駆動トランジスタのゲート電極はその閾値電圧に応じた電位に設定される。この状態から駆動トランジスタのゲート電極を所望の階調に応じた電位に変化させることによって、その閾値電圧に依存しない電流量を発光素子に供給することができる。

20

【先行技術文献】

30

【特許文献】

【0003】

【特許文献 1】米国特許第 6 , 229 , 506 号公報 (FIG.2)

【特許文献 2】特開 2004 - 133240 号公報 (図 2 および図 3 )

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、以上の構成においては、発光素子の発光に関わる各要素を電気的に接続するための配線が必要となる。例えば、駆動トランジスタと初期化トランジスタとを電気的に接続するための配線（以下「接続部」という）や駆動トランジスタと発光素子とを電気的に接続するための配線（以下「素子導通部」という）である。しかしながら、これらの配線の各々を別個の工程にて形成するとすれば、製造プロセスの煩雑化や製造コストの増大が問題となる。

40

【0005】

この問題を解決するための方策としては、ひとつの導電膜のパターニングによって接続部や素子導通部を他の要素（例えば電源線）と同工程で形成するという方法も考えられる。しかしながら、この方法のもとでは、接続部や素子導通部を避ける形状に電源線などの他の要素を形成する必要がある。そして、このような制約から例えば電源線に充分な線幅を確保できず、この結果として電源線の抵抗が充分に低減されないといった問題が発生し得る。以上のような事情を背景として、本発明は、電源線の抵抗を抑制しながら接続部や

50

素子導通部を電源線と同層から形成するという課題の解決を目的としている。

【課題を解決するための手段】

【0006】

本発明に係る発光装置の第1の特徴は、電源線から発光素子に供給される電流量を制御する駆動トランジスタと、駆動トランジスタと発光素子とを電気的に接続する素子導通部（例えば図7の素子導通部71）と、オン状態に変化することで駆動トランジスタをダイオード接続する初期化トランジスタと、駆動トランジスタと初期化トランジスタとを電気的に接続する接続部（例えば図7の接続部61）とが基板上に配置され、電源線は、所定の方向に延在する第1部分（例えば図7に図示された電源線15）を含み、素子導通部および接続部は、電源線と同層から形成され、駆動トランジスタを挟んで第1部分の幅方向（例えば図7のY方向）における一方の側に位置することにある。本態様の具体例は第1実施形態として後述される。

10

【0007】

この構成によれば、素子導通部や接続部が電源線と同層から形成されるため、各部が別層から形成された構成と比較して、製造工程の簡素化や製造コストの低減が実現される。さらに、駆動トランジスタを挟んで第1部分の幅方向における一方の側に接続部や素子導通部が配置されるから、駆動トランジスタを挟んで他方の側に電源線のスペースを確保することができる。したがって、電源線を充分な面積（あるいは線幅）に形成してその抵抗を抑制することができる。

20

【0008】

なお、複数の要素が「同層から形成される」とは、共通の膜体（単層であるか複数層であるかは不問である）の選択的な除去によって複数の要素が同工程で形成されることを意味し、各要素が相互に離間しているか連続しているかは不問である。

【0009】

本発明の好適な態様においては、駆動トランジスタのゲート電極に電気的に接続された容量素子（例えば図2の容量素子C1や図20または図21の容量素子C2）がさらに設けられ、容量素子は、駆動トランジスタを挟んで接続部および素子導通部の反対側に配置され、電源線の第1部分は、容量素子と重なり合う。この態様によれば、容量素子と重なり合うように電源線が形成されるから、電源線の面積をさらに充分に確保することができる。

30

【0010】

より具体的な態様においては、選択信号に応じてオン状態またはオフ状態となる選択トランジスタがさらに設けられ、駆動トランジスタのゲート電極は、オン状態となった選択トランジスタを介してデータ線から供給されるデータ信号に応じた電位に設定され、選択トランジスタは、容量素子を挟んで駆動トランジスタとは反対側に配置される。この態様によれば、容量素子を挟んで駆動トランジスタとは反対側の選択トランジスタが配置されるから、例えば駆動トランジスタと容量素子との間隙に選択トランジスタが配置された構成と比較して、電源線の面積（線幅）を充分に確保するとともに電源線の形状を単純化（例えば切欠などを含まない単純な帯状）することが可能である。

【0011】

複数の単位素子が配列する構成も好適に採用される。各単位素子は、駆動トランジスタと選択トランジスタと初期化トランジスタとを含み、所定の方向とは交差する方向（さらには所定の方向）に配列する。この態様において、所定の方向に沿った一方の側（例えば図8におけるX方向の負側）に選択トランジスタを配置し、所定の方向に沿った他方の側（例えば図8におけるX方向の正側）に初期化トランジスタを配置してもよい。この構成によれば、所定の方向に沿った位置が選択トランジスタと初期化トランジスタとで相違するから、選択トランジスタと初期化トランジスタとの電気的な絶縁を維持しながら、各単位素子の間隙（例えば図8の領域B）を狭小化することが可能である。

40

【0012】

本発明に係る発光装置の第2の特徴は、電源線から発光素子に供給される電流量を制御

50

する駆動トランジスタと、駆動トランジスタと発光素子とを電気的に接続する素子導通部（例えば図15の素子導通部72）と、オン状態に変化することで駆動トランジスタをダイオード接続する初期化トランジスタと、駆動トランジスタと初期化トランジスタとを電気的に接続する接続部（例えば図15の接続部62）とが基板上に配置された発光装置であって、電源線は、所定の方向に延在する第1部分（例えば図15の第1部分151）を含み、素子導通部および接続部は、電源線と同層から形成され、素子導通部は、駆動トランジスタを挟んで第1部分の幅方向における一方の側（例えば図15におけるY方向の負側）に位置し、接続部は、駆動トランジスタに対して第1部分の幅方向における他方の側（例えば図15におけるY方向の正側）に位置することにある。この態様の具体例は第2実施形態として後述される。

10

## 【0013】

この構成によれば、素子導通部や接続部が電源線と同層から形成されるため、第1の態様と同様に、各部が別層から形成された構成と比較して、製造工程の簡素化や製造コストの低減が実現される。また、駆動トランジスタを挟んで相互に反対側の各領域に素子導通部および接続部の各々が形成されるから、素子導通部と接続部との間隙に電源線のスペースを確保することができる。したがって、電源線を充分な面積（あるいは線幅）に形成してその抵抗を抑制することができる。

## 【0014】

第2の特徴に係る発光装置の好適な態様においては、駆動トランジスタのゲート電極に電気的に接続された容量素子（例えば図2の容量素子C1や図20または図21の容量素子C2）がさらに設けられ、容量素子は、駆動トランジスタと接続部との間隙に配置され、電源線の第1部分は、容量素子と重なり合う。この態様によれば、容量素子と重なり合うように電源線が形成されるから、電源線の面積をさらに充分に確保することができる。

20

## 【0015】

さらに好適な態様においては、選択信号に応じてオン状態またはオフ状態となる選択トランジスタが設けられ、駆動トランジスタのゲート電極は、オン状態となった選択トランジスタを介してデータ線から供給されるデータ信号に応じた電位に設定され、選択トランジスタは、容量素子を挟んで駆動トランジスタとは反対側に配置される。この態様によれば、容量素子を挟んで駆動トランジスタとは反対側の選択トランジスタが配置されるから、例えば駆動トランジスタと容量素子との間隙に選択トランジスタが配置された構成と比較して、電源線の面積（線幅）を充分に確保するとともに電源線の形状を単純化（例えば切欠などを含まない単純な帯状）することが可能である。

30

## 【0016】

以上に例示したように駆動トランジスタのゲート電極に容量素子が接続された構成においては、電源線は容量素子の一部のみと重なり合ってもよいしその全部と重なり合ってもよい。なお、以上に例示した各態様における容量素子は、典型的には駆動トランジスタのゲート電極の電位を設定または保持するために利用される。例えば、ひとつの態様における容量素子（例えば図2の容量素子C1）は、駆動トランジスタのゲート電極とデータ線との間に介在する。この構成においては、容量素子における容量カップリングによって、駆動トランジスタのゲート電極がデータ線の電位の変動量に応じた電位に設定される。また、その他の態様における容量素子（例えば図20や図21の容量素子C2）は、駆動トランジスタのゲート電極と定電位が供給される配線（例えば電源線）との間に介在する。この構成においては、データ線から駆動トランジスタのゲート電極に供給された電位が容量素子に保持される。

40

## 【0017】

本発明の第1および第2の特徴に係る発光装置の具体的な態様において、駆動トランジスタと素子導通部と初期化トランジスタと接続部とを各々が含む複数の単位素子が所定の方向とは交差する方向に配列し、電源線は、各単位素子に対応する複数の第1部分と、相互に隣接する各第1部分を連結する第2部分（例えば図15における第2部分152）とを含む。この態様によれば、電源線が第1部分のみからなる構成と比較して電源線の抵抗

50

をさらに低減することができる。

**【0018】**

本発明に係る発光装置は各種の電子機器に利用される。この電子機器の典型例は、発光装置を表示装置として利用した機器である。この種の電子機器としては、パーソナルコンピュータや携帯電話機などがある。もっとも、本発明に係る発光装置の用途は画像の表示に限定されない。例えば、光線の照射によって感光体ドラムなどの像担持体に潜像を形成するための露光装置（露光ヘッド）、液晶装置の背面側に配置されてこれを照明する装置（バックライト）、あるいは、スキャナなどの画像読み取り装置に搭載されて原稿を照明する装置など各種の照明装置など、様々な用途に本発明の発光装置を適用することができる。

**【図面の簡単な説明】**

**【0019】**

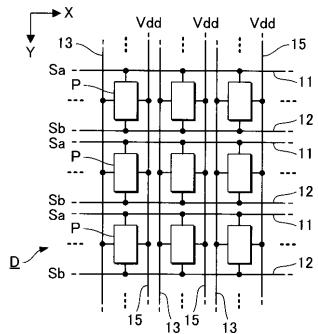

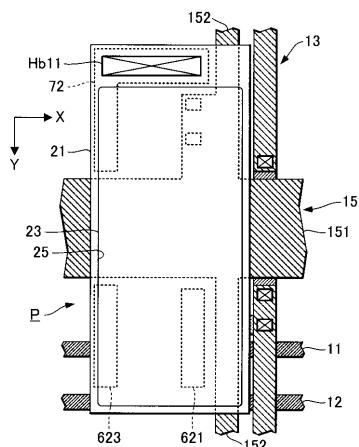

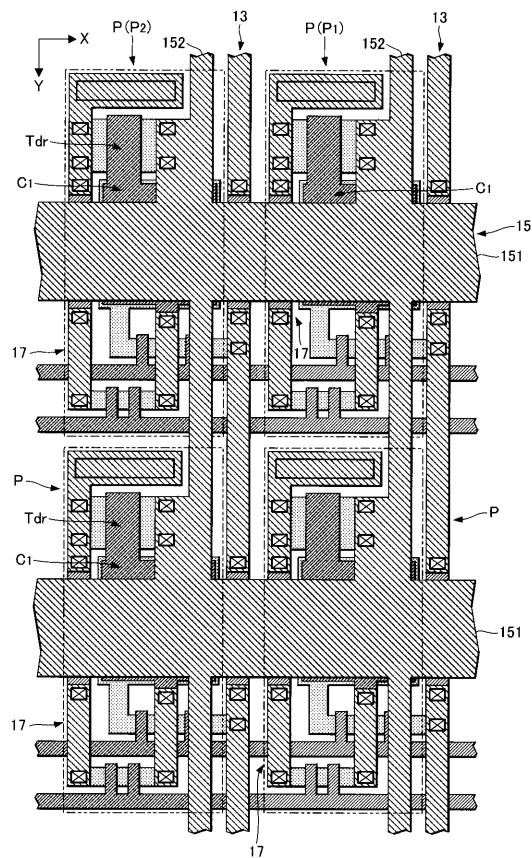

【図1】発光装置において複数の単位素子が配列する様子を示すブロック図である。

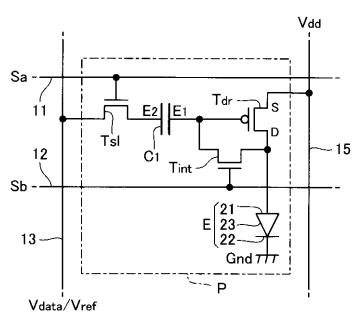

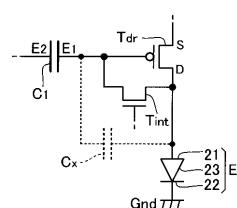

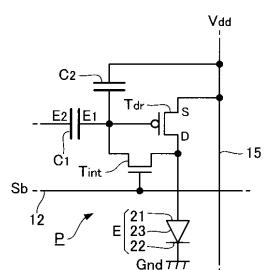

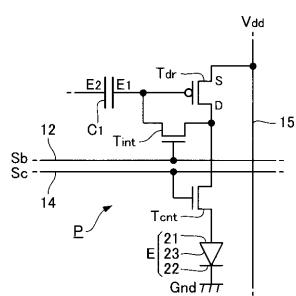

【図2】各単位素子の電気的な構成を示す回路図である。

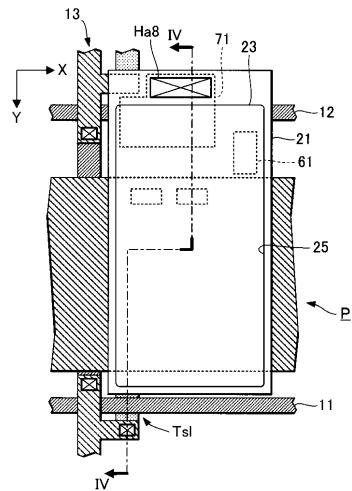

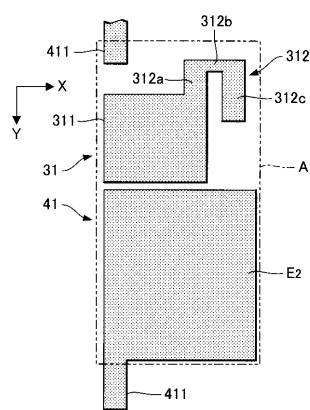

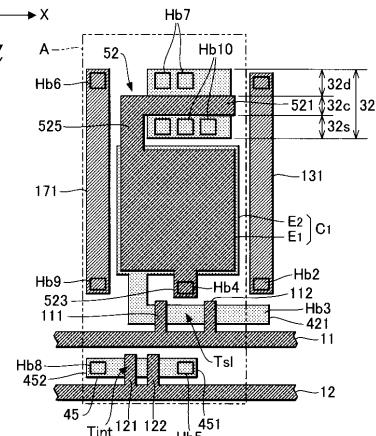

【図3】本発明の第1実施形態における単位素子の構成を示す平面図である。

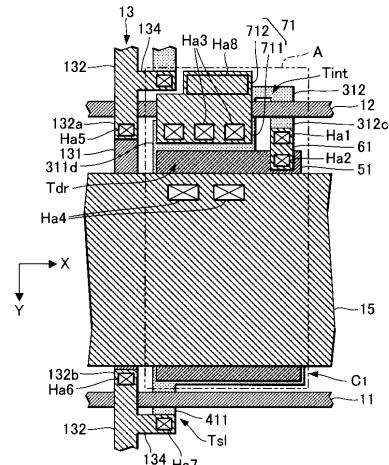

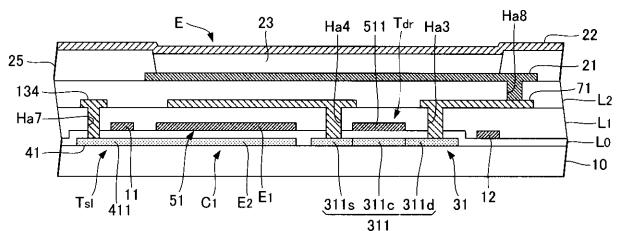

【図4】図3におけるIV-IV線からみた断面図である。

【図5】ゲート絶縁層が形成された段階を示す平面図である。

【図6】第1絶縁層が形成された段階を示す平面図である。

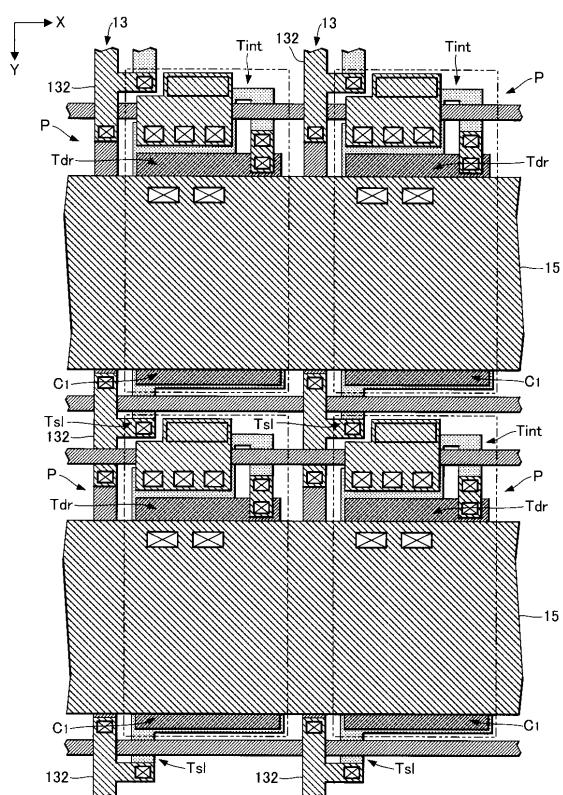

【図7】第2絶縁層が形成された段階を示す平面図である。

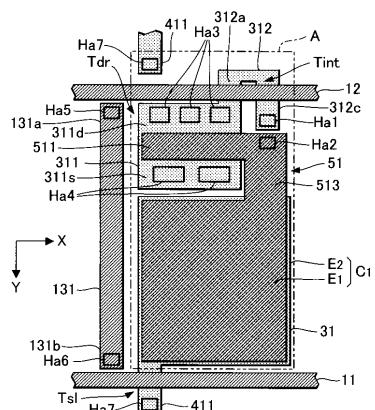

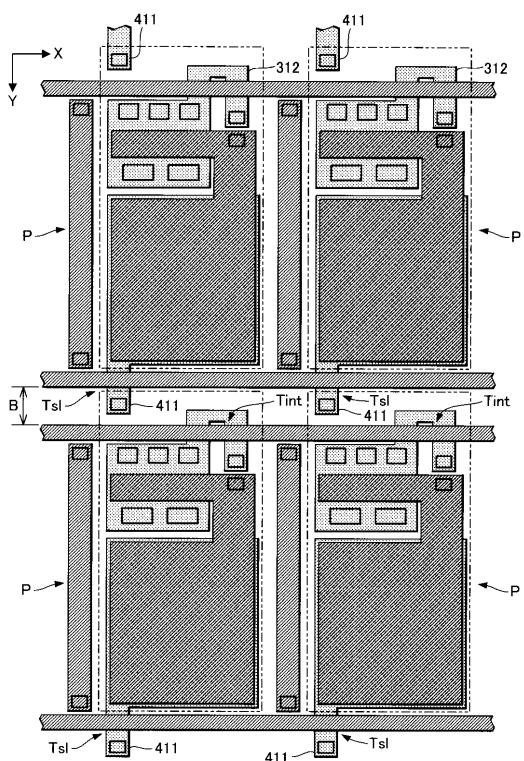

【図8】第1絶縁層が形成された段階にある複数の単位素子を示す平面図である。

【図9】第2絶縁層が形成された段階にある複数の単位素子を示す平面図である。

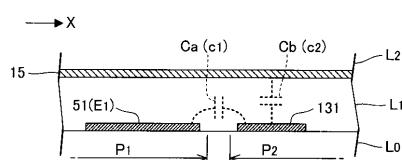

【図10】実施形態の効果を説明するための断面図である。

【図11】実施形態の効果を説明するための回路図である。

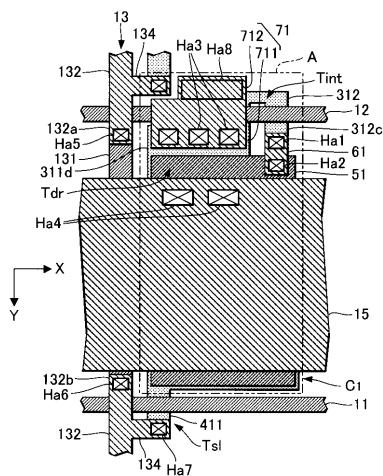

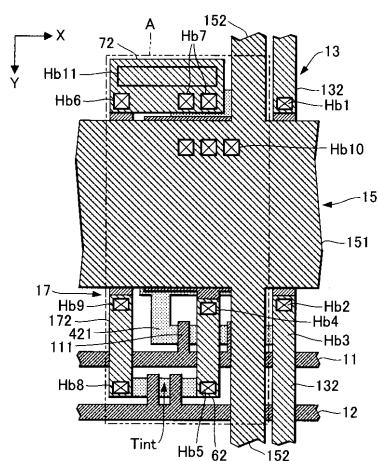

【図12】本発明の第2実施形態における単位素子の構成を示す平面図である。

【図13】ゲート絶縁層が形成された段階を示す平面図である。

【図14】第1絶縁層が形成された段階を示す平面図である。

【図15】第2絶縁層が形成された段階を示す平面図である。

【図16】第2絶縁層が形成された段階にある複数の単位素子を示す平面図である。

【図17】第2実施形態の変形例において第1絶縁層が形成された段階を示す平面図である。

【図18】第2実施形態の変形例において第2絶縁層が形成された段階を示す平面図である。

【図19】変形例に係る単位素子の構成を示す回路図である。

【図20】変形例に係る単位素子の構成を示す回路図である。

【図21】変形例に係る単位素子の構成を示す回路図である。

【図22】本発明に係る電子機器の具体例であるパーソナルコンピュータの斜視図である。

【図23】本発明に係る電子機器の具体例である携帯電話機の斜視図である。

【図24】本発明に係る電子機器の具体例である携帯型情報端末の斜視図である。

**【発明を実施するための形態】**

**【0020】**

< A : 発光装置の電気的な構成 >

図1は、本発明の各実施形態に係る発光装置Dの電気的な構成を示すブロック図である。同図に示すように、発光装置Dは、複数の選択線11と複数の初期化線12と複数のデータ線13とを有する。各選択線11および各初期化線12はX方向に延在する。各データ線13はX方向に直交するY方向に延在する。選択線11および初期化線12の各対とデータ線13との各交差には単位素子（画素）Pが配置される。したがって、これらの単位素子PはX方向およびY方向にわたってマトリクス状に配列する。ひとつの単位素子Pは発光の最小の単位となる要素である。各単位素子Pには電源線15を介して高位側の電源電位Vddが供給される。

**【0021】**

10

20

30

40

50

図2は、各単位素子Pの構成を示す回路図である。同図に示すように、電源線15から接地線（接地電位Gnd）に至る経路上には発光素子Eと駆動トランジスタTdrとが配置される。発光素子Eは、有機EL材料からなる発光層23を第1電極21（陽極）と第2電極22（陰極）との間に介在させた素子である。第1電極21は、単位素子Pごとに相互に離間して形成される。第2電極22は、複数の単位素子Pにわたって連續に形成されて接地（Gnd）される。発光層23は、第1電極21から第2電極22に流れる電流量に応じた光量で発光する。

#### 【0022】

駆動トランジスタTdrは、発光素子Eに供給される電流量をゲート電極の電位（以下「ゲート電位」という）Vgに応じて制御するためのpチャネル型の薄膜トランジスタである。駆動トランジスタTdrのソース電極（S）は電源線15に接続され、そのドレイン電極（D）は発光素子Eの第1電極21に接続される。

10

#### 【0023】

駆動トランジスタTdrのゲート電極とドレイン電極（発光素子Eの第1電極21）との間には、両者の電気的な接続を制御するためのnチャネル型のトランジスタ（以下では「初期化トランジスタ」という）Tintが介在する。初期化トランジスタTintのゲート電極は初期化線12に接続される。初期化線12には駆動回路（図示略）から初期化信号Sbが供給される。初期化信号Sbがアクティブルレベルとなって初期化トランジスタTintがオン状態に変化すると、駆動トランジスタTdrのゲート電極とドレイン電極とが電気的に接続（ダイオード接続）される。

20

#### 【0024】

図2に示すように、単位素子Pは、電極E1と電極E2とから構成される容量素子C1を含む。電極E1は駆動トランジスタTdrのゲート電極に接続される。電極E2とデータ線13との間には、両者の電気的な接続を制御するnチャネル型のトランジスタ（以下「選択トランジスタ」という）Tslが介在する。選択トランジスタTslのゲート電極は選択線11に接続される。選択線11には駆動回路（図示略）から選択信号Saが供給される。なお、駆動トランジスタTdrや選択トランジスタTslや初期化トランジスタTintの導電型は図2の例示から適宜に変更される。

30

#### 【0025】

次に、ひとつの単位素子Pの動作を初期化期間と書き込み期間と駆動期間とに区分して説明する。まず、初期化期間においては、駆動回路（図示略）からデータ線13に所定の電位Vrefが供給されるとともに選択線11の選択信号Saと初期化線12の初期化信号Sbとがアクティブルレベル（ハイレベル）を維持する。したがって、容量素子C1の電極E2にはデータ線13から選択トランジスタTslを介して電位Vrefが供給される。また、初期化トランジスタTintがオン状態に変化することで駆動トランジスタTdrがダイオード接続される。したがって、駆動トランジスタTdrのゲート電位Vgは、電源線15に供給される電源電位Vddと駆動トランジスタTdrの閾値電圧Vthとの差分値（ $Vg = Vdd - Vth$ ）に収束する。

#### 【0026】

次に、初期化期間の経過後の書き込み期間においては、初期化信号Sbが非アクティブル（ローレベル）に遷移する。したがって、初期化トランジスタTintがオフ状態に変化して駆動トランジスタTdrのダイオード接続は解除される。また、選択トランジスタTslがオン状態に維持されたまま、データ線13から電極E2に供給される電位Vrefがデータ電位Vdataに変更される。データ電位Vdataは、単位素子Pに指定された階調に応じた電位である。

40

#### 【0027】

駆動トランジスタTdrのゲート電極のインピーダンスは充分に高いから、電極E2が電位Vrefからデータ電位Vdataまで変化量 $V$ （=  $Vref - Vdata$ ）だけ変動すると、電極E1の電位は、容量素子C1における容量カップリングによって、初期化期間にて設定された電位Vg（=  $Vdd - Vth$ ）から変動する。このときの電極E1の電位の変化量は、容量素

50

子C1とその他の寄生容量（例えば駆動トランジスタTdrのゲート容量やその他の配線に寄生する容量）との容量比に応じて定まる。より具体的には、容量素子C1の容量値を「C」として寄生容量の容量値を「Cs」とすると、電極E1の電位の変化量は「V · C / (C + Cs)」と表現される。したがって、駆動トランジスタTdrのゲート電位Vgは、書込期間の終点において以下の式(1)のレベルに設定される。

$$Vg = Vdd - Vth - k \cdot V \quad \dots \dots (1)$$

$$\text{ただし、 } k = C / (C + Cs)$$

#### 【0028】

次いで、書込期間の経過後の駆動期間においては、選択信号Saが非アクティブレベルに遷移して選択トランジスタTslがオフ状態に変化する。そして、駆動トランジスタTdrのゲート電位Vgに応じた電流が電源線15から駆動トランジスタTdrのソース電極とドレイン電極とを経由して発光素子Eに供給される。この電流の供給によって発光素子Eはデータ電位Vdataに応じた光量で発光する。

10

#### 【0029】

いま、駆動トランジスタTdrが飽和領域で動作する場合を想定すると、駆動期間にて発光素子Eに供給される電流量Iは以下の式(2)によって表現される。ただし、式(2)における「」は駆動トランジスタTdrの利得係数であり、「Vgs」は駆動トランジスタTdrのゲート-ソース間の電圧である。

$$\begin{aligned} I &= (\quad / 2) (Vgs - Vth)^2 \quad \dots \dots (2) \\ &= (\quad / 2) (Vdd - Vg - Vth)^2 \end{aligned}$$

20

式(1)の代入によって式(2)は以下のように変形される。

$$I = (\quad / 2) (k \cdot V)^2$$

すなわち、発光素子Eに供給される電流量Iは駆動トランジスタTdrの閾値電圧Vthに依存しない。したがって、本実施形態によれば、各駆動トランジスタTdrの閾値電圧Vthのバラツキ（設計値からの相違や他の単位素子Pの駆動トランジスタTdrとの相違）に起因した発光素子Eの光量の誤差（輝度のムラ）を抑制することができる。

30

#### 【0030】

<B：単位素子Pの具体的な構造>

次に、図面を参照して、以上に説明した単位素子Pの具体的な構造を説明する。なお、以下で参照する各図面においては、説明の便宜のために、各要素の寸法や比率を実際の装置から適宜に異ならせてある。

30

#### 【0031】

<B-1：第1実施形態>

まず、本発明の第1実施形態に係る発光装置Dの単位素子Pの具体的な構成を説明する。図3は、ひとつの単位素子Pの構成を示す平面図であり、図4は、図3におけるIV-IV線からみた断面図である。なお、図3は平面図であるが、各要素の把握を容易化するために、図3と共に通する要素については適宜に図3と同様のハッチングが施されている。以下で参照する他の平面図についても同様である。

40

#### 【0032】

図4に示すように、駆動トランジスタTdrや発光素子Eといった図2の各要素は基板10の面上に形成される。基板10は、ガラスやプラスチックなど各種の絶縁性材料からなる板状の部材である。なお、基板10を覆う絶縁性の膜体（例えば酸化珪素や窒化珪素の膜体）を下地として基板10の面上に単位素子Pの各要素を形成してもよい。また、本実施形態の発光装置Dはトップエミッション型である。したがって、基板10に光透過性は要求されない。

#### 【0033】

図5ないし図7は、単位素子Pが形成される各段階における基板10の面上の様子を示す平面図である。なお、図5ないし図7においては、図3に図示された第1電極21が形成されるべき領域Aが二点鎖線によって併記されている。

50

#### 【0034】

図4および図5に示すように、基板10の面上には、半導体層31と半導体層41とがシリコンなどの半導体材料によって形成される。半導体層31と半導体層41とは、基板10の全域にわたって連続に形成された膜体のパターニングによって同一の工程で一括的に形成される。なお、半導体層31と半導体層41との関係のように、複数の要素が共通の膜体（単層および複数層の何れであるかは不問である）の選択的な除去によって同一の工程で形成されることを以下では単に「同層から形成される」と表記する。同層から形成された各要素は当然に同一の材料からなり、各々の膜厚は略一致する。複数の要素が同層から形成される構成によれば、その各々が別層から形成される構成と比較して、製造工程の簡素化や製造コストの低減が実現されるという利点がある。

## 【0035】

10

図4および図5に示すように、半導体層31は、第1素子部311と第2素子部312とを含む。第1素子部311は、駆動トランジスタTdrの半導体層として機能する略矩形状の部分である。第2素子部312は、初期化トランジスタTintの半導体層として機能する部分であり、第1素子部311からみてX方向の正側かつY方向の負側の領域（すなわち第1素子部311の右上部）に形成される。さらに詳述すると、第2素子部312は、図5に示すように、第1素子部311からY方向の負側に連続する部分312aと、この部分312aからX方向の正側に延在する部分312bと、部分312bからY方向の正側に延在する部分312cとを含む。

## 【0036】

20

半導体層41は、半導体層31からみてY方向の正側に配置された部分であり、図2の容量素子C1を構成する略矩形状の電極E2と、電極E2からY方向に延在する素子部411とを含む。素子部411は、選択トランジスタTslの半導体層として機能する部分であり、電極E2からみてX方向の負側かつY方向の正側の領域（すなわち電極E2の左下部）に形成される。

## 【0037】

図4に示すように、半導体層31と半導体層41とが形成された基板10の表面はその全域にわたってゲート絶縁層L0に覆われる。図4および図6に示すように、ゲート絶縁層L0の面上には、選択線11と初期化線12と中間導電体51と第1データ線部131とが導電性材料によって同層から形成される。

## 【0038】

30

選択線11は、複数の単位素子PにわたってX方向に延在して半導体層41の素子部411と重なり合う。素子部411のうちゲート絶縁層L0を挟んで選択線11に対向する領域が選択トランジスタTslのチャネル領域である。初期化線12は、複数の単位素子PにわたってX方向に延在して半導体層31の第2素子部312と重なり合う。第2素子部312の部分312aおよび部分312cの各々のうちゲート絶縁層L0を挟んで初期化線12に対向する領域が初期化トランジスタTintのチャネル領域である。すなわち、本実施形態における初期化トランジスタTintはデュアルゲート構造のトランジスタである。

## 【0039】

中間導電体51は、選択線11と初期化線12との間隙の領域に形成された部分であり、電極E1とゲート電極511と連結部513とを含む。電極E1は、基板10に垂直な方向からみて半導体層41の電極E2と重なり合う略矩形状の部分である。図4および図6に示すように、ゲート絶縁層L0（誘電体）を挟んで電極E1と電極E2とが対向することによって図2の容量素子C1が構成される。

## 【0040】

40

連結部513は、電極E1の右上部からY方向の負側に延在する。ゲート電極511は、電極E1と間隔をあけて連結部513からX方向の負側に延在する部分であり、第1素子部311の略全幅（X方向の寸法）にわたって第1素子部311と重なり合う。図4に示すように、第1素子部311のうちゲート絶縁層L0を挟んでゲート電極511に対向する領域が駆動トランジスタTdrのチャネル領域311cである。また、第1素子部311のうちチャネル領域311cよりも電極E2側の領域（すなわち、図6のように基板10

50

に垂直な方向からみてゲート電極 511 と電極 E1 との間隙に位置する領域) はソース領域 311s であり、その反対側の領域はドレイン領域 311d である。

#### 【0041】

第 1 データ線部 131 は、図 2 のデータ線 13 を構成する部分である。この第 1 データ線部 131 は、中間導電体 51 からみて X 方向の負側の領域に配置され、選択線 11 と初期化線 12 との間隙にて Y 方向に延在する。

#### 【0042】

図 8 は、図 6 の段階にある 4 個の単位素子 P が X 方向および Y 方向にわたって配列する様子を示す平面図である。図 6 および図 8 に示すように、各単位素子 P において、Y 方向の負側の周縁に形成された第 2 素子部 312 (初期化トランジスタ Tint) は X 方向の正側に位置し、Y 方向の正側の周縁に形成された素子部 411 (選択トランジスタ Tsl) は X 方向の負側に位置する。

10

#### 【0043】

いま、第 2 素子部 312 と素子部 411 とが各単位素子 P における X 方向の同じ側に配置された構成を想定する。この構成においては、第 2 素子部 312 と素子部 411 とを確実に離間させるために、Y 方向に隣接する各単位素子 P の間隙の領域 (図 8 の領域 B に相当する領域) を充分に確保する必要があるから、単位素子 P の高精細化が阻害されるという問題がある。これに対し、本実施形態においては、第 2 素子部 312 および素子部 411 の X 方向における位置が相違するから、図 8 に示すように、第 2 素子部 312 と素子部 411 とは領域 B 内にて X 方向に沿って交互に配列する。この構成によれば、領域 B を狭小化した場合であっても第 2 素子部 312 と素子部 411 とは確実に離間するから、単位素子 P の高精細化が容易であるという利点がある。

20

#### 【0044】

図 4 に示すように、中間導電体 51 や第 1 データ線部 131 が形成されたゲート絶縁層 L0 の表面はその全域にわたって第 1 絶縁層 L1 に覆われる。図 4 および図 7 に示すように、第 1 絶縁層 L1 の面上には、接続部 61 と素子導通部 71 と電源線 15 と第 2 データ線部 132 とが導電性材料によって同層から形成される。

30

#### 【0045】

図 7 のように基板 10 に垂直な方向からみると、接続部 61 は、第 2 素子部 312 の部分 312c における Y 方向の正側の端部と中間導電体 51 (ゲート電極 511) とに重なり合う。そして、接続部 61 は、第 1 絶縁層 L1 とゲート絶縁層 L0 とを貫通するコンタクトホール Ha1 を介して部分 312c に導通するとともに、第 1 絶縁層 L1 を貫通するコンタクトホール Ha2 を介して中間導電体 51 に導通する。すなわち、駆動トランジスタ Tdr のゲート電極 511 (容量素子 C1 の電極 E1) と初期化トランジスタ Tint とは接続部 61 を介して電気的に接続される。なお、本明細書におけるコンタクトホールとは、絶縁層の一方の側に位置する要素と絶縁層の他方の側に位置する要素とを電気的に接続するための部分であり、より具体的には絶縁層をその厚さ方向に貫通する部分 (孔や穴) である。コンタクトホールの平面的な形状は任意である。

30

#### 【0046】

素子導通部 71 は、駆動トランジスタ Tdr と発光素子 E との間に介在して両者を電気的に接続する部分であり、基板 10 に垂直な方向からみると、駆動トランジスタ Tdr を挟んで容量素子 C1 とは反対側の領域 (すなわち駆動トランジスタ Tdr に対して Y 方向の負側の領域) に配置される。本実施形態の素子導通部 71 は、基板 10 に垂直な方向からみて第 1 素子部 311 のドレイン領域 311d に重なり合う部分 711 と、初期化線 12 を挟んで部分 711 とは反対側に位置する部分 712 とが連続する形状である。

40

#### 【0047】

基板 10 に垂直な方向からみて第 1 絶縁層 L1 のうちドレイン領域 311d と重なり合う領域には、第 1 絶縁層 L1 とゲート絶縁層 L0 とを貫通する複数のコンタクトホール Ha3 が形成される。これらのコンタクトホール Ha3 はゲート電極 511 が延在する X 方向 (すなわち駆動トランジスタ Tdr のチャネル幅の方向) に配列する。素子導通部 71 の部分 71

50

1は、各コンタクトホールHa3を介してドレイン領域311dに導通する。

#### 【0048】

次に、図9は、図8の段階にある4個の単位素子PがX方向およびY方向にわたって配列する様子を示す平面図である。図7および図9に示すように、電源線15は、複数の単位素子Pの配列に沿ってX方向に延在する帯状の配線である。この電源線15は、基板10に垂直な方向からみて、各単位素子Pの容量素子C1と駆動トランジスタTdrのソース領域311sとの双方に重なり合う。図7に示すように、第1絶縁層L1のうちソース領域311sと重なり合う領域には、第1絶縁層L1とゲート絶縁層L0とを貫通する複数のコンタクトホールHa4が形成される。これらのコンタクトホールHa4はゲート電極511が延在するX方向に配列する。電源線15は、各コンタクトホールHa4を介して駆動トランジスタTdrのソース領域311sに導通する。

10

#### 【0049】

本実施形態の電源線15は、基板10に垂直な方向からみて、選択トランジスタTsl(素子部411)や選択線11および初期化トランジスタTint(第2素子部312)や初期化線12と重なり合わないように、その形状や寸法が選定されている。換言すると、電源線15は、図9に示すように、選択線11に沿った各選択トランジスタTslの配列と初期化線12に沿った各初期化トランジスタTintの配列との間隙の領域にてX方向に延在する。

#### 【0050】

第2データ線部132は、第1データ線部131と協働してデータ線13を構成する部分であり、図7および図9に示すように各電源線15の間隙にてY方向に延在する。図7に示すように、第2データ線部132のうちY方向の正側(下側)の端部132aは、第1データ線部131におけるY方向の負側(上側)の端部131a(図6参照)と重なり合う。端部132aと端部131aとは第1絶縁層L1を貫通するコンタクトホールHa5を介して相互に導通する。同様に、第2データ線部132のうちY方向の負側の端部132bと第1データ線部131におけるY方向の正側の端部131b(図6参照)とはコンタクトホールHa6を介して相互に導通する。以上のように、Y方向に沿って交互に配列する第1データ線部131と第2データ線部132とが電気的に接続されることによって、Y方向に直線状に延在するデータ線13が構成される。

20

#### 【0051】

図7に示すように、第2データ線部132には分岐部134が連設される。分岐部134は、選択線11を挟んで容量素子C1とは反対側に位置する部分であり、X方向に延在して半導体層41の素子部411と重なり合う。この分岐部134は、第1絶縁層L1とゲート絶縁層L0とを貫通するコンタクトホールHa7を介して素子部411に導通する。すなわち、選択トランジスタTslとデータ線13とは分岐部134を介して電気的に接続される。

30

#### 【0052】

図7および図9に示すように、各単位素子Pの容量素子C1は、そのX方向の正側に隣接する他の単位素子Pに対応したデータ線13に隣接する。図10は、任意のひとつの単位素子P1とそのX方向の正側に隣接する他の単位素子P2との近傍を拡大して示す断面図である。同図においては、単位素子P1の中間導電体51(ここでは特に容量素子C1の電極E1)と、単位素子P2に対応したデータ線13の第1データ線部131とが図示されている。

40

#### 【0053】

中間導電体51と第1データ線部131とは同層から形成されて相互に近接するから、図10に示すように、中間導電体51の電極E1と第1データ線部131とは容量的に結合して両者間には容量(寄生容量)Caが付随する。したがって、単位素子P1の電極E1(さらには駆動トランジスタTdrのゲート電極511)の電位Vgは、本来ならば単位素子P1に対応したデータ線13の電位の変動量(単位素子P1の階調に応じた電圧)のみによって設定されるべきにも拘わらず、実際には単位素子P2に対応した第1データ線部1

50

3 1 の電位の変動量（単位素子 P 2 の階調に応じた電圧）の影響も受ける。すなわち、各単位素子 P の駆動トランジスタ T dr におけるゲート電位 Vg を正確に設定できず、この結果として発光素子 E の光量に誤差が生じる可能性がある。

#### 【 0 0 5 4 】

図 7 に示すように、第 1 データ線部 1 3 1 と電源線 1 5 とは第 1 絶縁層 L 1 を挟んで対向する。したがって、第 1 データ線部 1 3 1 と電源線 1 5 との間には容量が形成される。本実施形態においては、図 1 0 に示すように、単位素子 P 2 の第 1 データ線部 1 3 1 と電源線 1 5 との間に形成される容量 Cb の容量値 c 2 が、この第 1 データ線部 1 3 1 と単位素子 P 1 の中間導電体 5 1 （電極 E 1 ）との間に付随する容量 Ca の容量値 c 1 よりも大きい。この構成によれば、単位素子 P 2 の第 1 データ線部 1 3 1 の電位の変動によって単位素子 P 1 の中間導電体 5 1 （電極 E 1 ）に与えられる影響が容量 Cb によって低減される。したがって、各単位素子 P における駆動トランジスタ T dr のゲート電位 Vg やこのゲート電位 Vg に応じた発光素子 E の光量を高い精度で所期値に設定することができる。

10

#### 【 0 0 5 5 】

本実施形態においては、以上の条件 ( $c 2 > c 1$ ) が満たされるように、第 1 データ線部 1 3 1 と電源線 1 5 との距離（第 1 絶縁層 L 1 の膜厚）や、単位素子 P 1 の中間導電体 5 1 と単位素子 P 2 の第 1 データ線部 1 3 1 との間隔が選定されている。さらに詳述すると、単位素子 P 2 の第 1 データ線部 1 3 1 と電源線 1 5 との距離（第 1 絶縁層 L 1 の膜厚）は、単位素子 P 1 の中間導電体 5 1 と単位素子 P 2 の第 1 データ線部 1 3 1 との間隔よりも小さい。また、単位素子 P 2 の第 1 データ線部 1 3 1 と電源線 1 5 とが第 1 絶縁層 L 1 を挟んで対向する面積（すなわち基板 1 0 に垂直な方向からみて第 1 データ線部 1 3 1 と電源線 1 5 とが重なり合う部分の面積）は、この第 1 データ線部 1 3 1 と単位素子 P 1 の中間導電体 5 1 とが対向する面積（すなわち中間導電体 5 1 の側端面（基板 1 0 に垂直な側面）のうち第 1 データ線部 1 3 1 の側端面に対向する領域の面積）よりも大きい。以上のように各部の寸法や間隔を選定することによって容量値 c 2 を容量値 c 1 よりも大きくすることができる。

20

#### 【 0 0 5 6 】

ただし、データ線 1 3 のデータ電位 V data に応じて駆動トランジスタ T dr のゲート電位 Vg を正確に設定するためには、任意の単位素子 P 2 における容量 Cb の容量値 c 2 が、その単位素子 P 2 の容量素子 C 1 の容量値 C ( ゲート電極 5 1 1 に容量 Cs が寄生する場合には容量素子 C 1 と寄生容量 Cs の合成容量 ) よりも小さいことが望ましい。この条件を満たすために、例えば、第 1 データ線部 1 3 1 と電源線 1 5 との間隙は、容量素子 C 1 における電極 E 1 と電極 E 2 との間隙よりも大きい寸法に選定される。さらに詳述すると、第 1 データ線部 1 3 1 と電源線 1 5 との間に介在する第 1 絶縁層 L 1 ( すなわち容量 Cb の誘電体 ) の膜厚は、電極 E 1 と電極 E 2 との間に介在するゲート絶縁層 L 0 ( 容量素子 C 1 の誘電体 ) の膜厚よりも大きい寸法に選定される。また、電極 E 1 と電極 E 2 との対向する面積（すなわち容量素子 C 1 の面積）が第 1 データ線部 1 3 1 と電源線 1 5 との対向する面積よりも大面積とされた構成によっても、容量 Cb の容量値 c 2 は容量素子 C 1 の容量値 C よりも小さくなる。

30

#### 【 0 0 5 7 】

さて、図 4 に示すように、第 2 データ線部 1 3 2 や電源線 1 5 が形成された第 1 絶縁層 L 1 の表面はその全域にわたって第 2 絶縁層 L 2 に覆われる。図 3 および図 4 に示すように、第 2 絶縁層 L 2 の表面には第 1 電極 2 1 が形成される。第 1 電極 2 1 は、基板 1 0 に垂直な方向からみて素子導通部 7 1 や駆動トランジスタ T dr や容量素子 C 1 と重なり合う略矩形状の電極である。本実施形態の第 1 電極 2 1 は、アルミニウムや銀などの金属またはこれらの金属を主成分とする合金など光反射性の導電性材料によって形成される。この第 1 電極 2 1 は、第 2 絶縁層 L 2 を貫通するコンタクトホール Ha8 を介して素子導通部 7 1 の部分 7 1 2 に導通する。すなわち、駆動トランジスタ T dr のドレイン領域 3 1 1 d と発光素子 E の第 1 電極 2 1 とは素子導通部 7 1 を介して電気的に接続される。

40

#### 【 0 0 5 8 】

50

第1電極21が形成された第2絶縁層L2の面上には、各単位素子Pの境界を仕切る形状(格子状)の隔壁25が形成される。この隔壁25は、相隣接する第1電極21を電気的に絶縁させる役割(すなわち第1電極21の電位の個別的な制御を可能とする役割)を担う。各発光素子Eの発光層23は、隔壁25の内周面に包囲されて第1電極21を底面とする窪みに形成される。なお、発光層23による発光を促進または効率化するための各種の機能層(正孔注入層、正孔輸送層、電子注入層、電子輸送層、正孔ブロック層、電子ブロック層)が発光層23に積層された構成としてもよい。

#### 【0059】

図4に示すように、第2電極22は、複数の単位素子Pにわたって連続に形成されて発光層23および隔壁25を覆う電極である。したがって、隔壁25は、各発光素子Eの間隙の領域において各第1電極21と第2電極22とを電気的に絶縁する。換言すると、隔壁25は、第1電極21と第2電極22との間に電流が流れる領域(すなわち実際に発光する領域)を画定する。第2電極22は、ITO(Indium Tin Oxide)やIZO(Indium Zinc Oxide)といった光透過性の導電性材料によって形成される。したがって、発光層23から基板10とは反対側に出射した光と発光層23から基板10側に出射して第1電極21の表面で反射した光とは第2電極22を透過して出射する。すなわち、本実施形態の発光装置Dはトップエミッション型である。

10

#### 【0060】

第2電極22はその全域にわたって封止材(図示略)に覆われる。この封止材は、第2電極22を保護する第1層と、第2電極22の表面の段差を平坦化する第2層と、第2電極22や発光層23への不純物(例えば水分)の浸入を防止する第3層(バリア層)とが第2電極22側からこの順番に積層された構造となっている。

20

#### 【0061】

以上に説明したように、本実施形態においては、駆動トランジスタTdrを挟んで容量素子C1とは反対側の領域に素子導通部71が配置される。この構成によれば、容量素子C1に要求される容量値を低減できるという効果が奏される。この効果について詳述すると以下の通りである。

20

#### 【0062】

いま、基板10に垂直な方向からみて駆動トランジスタTdrと容量素子C1との間隙に素子導通部71が配置された構成(以下「構成1」という)を想定する。この構成1においては、容量素子C1の電極E1と素子導通部71とが第1絶縁層L1を挟んで近接する。したがって、図11に破線で図示されるように、電極E1と素子導通部71(第1電極21)との間には容量Cxが付随する。

30

#### 【0063】

書き期間において電極E1の電位は「 $V \cdot C / (C + Cs)$ 」だけ変化する。構成1における容量値Csは、電極E1と素子導通部71とが容量的に結合しない場合と比較して容量Cxの分だけ増大するから、データ線13の電位の変動量Vに対する駆動トランジスタTdrのゲート電位Vgの変動量は制限される。したがって、ゲート電位Vgを変動量Vに応じて広範囲に変動させるためには(すなわち発光素子Eの光量の範囲を充分に確保するためには)、ゲート絶縁層L0の膜厚の低減や電極E1および電極E2の面積の増大といった方策によって、容量素子C1に充分な容量値Cを確保する必要がある。ゲート絶縁層L0の膜厚を低減するには限界があるから、構成1においては結局のところ電極E1や電極E2の面積を増大させる必要がある。しかしながら、容量素子C1の面積を増大した場合には単位素子Pの高精細化が制限されるという問題がある。

40

#### 【0064】

なお、第1絶縁層L1を充分な膜厚に形成することで電極E1と素子導通部71とを離間させれば、構成1においても容量Cxは低減される。しかしながら、第1絶縁層L1を厚く形成すると、クラックなど成膜の不良が発生し易くなるという問題や、コンタクトホールの不良(例えば第1絶縁層L1のうちコンタクトホールの部分が完全に除去されないといった不良)に起因して各要素が完全には導通されないといった問題が生じ得るから、この

50

方法による容量  $C_x$  の低減には限界がある。

【0065】

これに対し、本実施形態においては、駆動トランジスタ  $T_{dr}$  を挟んで容量素子  $C_1$  とは反対側の領域に素子導通部 71 が配置されるから、電極 E1 と素子導通部 71 とに付随する容量  $C_x$  は構成 1 と比較して充分に低減される。したがって、容量素子  $C_1$  の面積を構成 1 ほど増大させなくても、駆動トランジスタ  $T_{dr}$  のゲート電極 511 のゲート電位  $V_g$  (さらには発光素子 E の光量) を広範囲にわたって変化させることができる。

【0066】

また、本実施形態においては、電源線 15 と同層から形成される素子導通部 71 および接続部 61 の双方が、基板 10 に垂直な方向からみて駆動トランジスタ  $T_{dr}$  の Y 方向の負側 (すなわち電源線 15 の幅方向の一方の側) に位置する。この構成によれば、第 1 絶縁層 L1 の表面のうち駆動トランジスタ  $T_{dr}$  に対して Y 方向の正側 (電源線 15 の幅方向の他方の側) に、電源線 15 が形成されるスペースを充分に確保することが可能である。したがって、電源線 15 を幅広に形成してその抵抗を低減できるという効果が奏される。特に、本実施形態においては、容量素子  $C_1$  と重なり合うように電源線 15 が形成されるから、例えば電源線 15 が駆動トランジスタ  $T_{dr}$  のソース領域 31s のみと重なり合う構成と比較して、電源線 15 の抵抗は大幅に低減される。そして、この低抵抗化によって電源線 15 の面内における電圧降下が抑制されるから、各単位素子 P に供給される電源電位  $V_{dd}$  のバラツキやこれに起因した各発光素子 E の光量のバラツキを低減できる。

【0067】

また、例えば素子導通部 71 や接続部 61 が駆動トランジスタ  $T_{dr}$  と容量素子  $C_1$  との間に配置された構成においては、素子導通部 71 や接続部 61 を避ける形状に電源線 15 を形成する必要がある。しかしながら、このように電源線 15 の形状を複雑化すると、製造技術上の理由から電源線 15 の断線や損傷が発生し易いという問題がある。これに対し、本実施形態によれば、駆動トランジスタ  $T_{dr}$  を挟んで素子導通部 71 や接続部 61 とは反対側に電源線 15 のスペースが確保されるから、図 7 に例示したように電源線 15 を単純な帯状の形状とすることが可能である。この結果として電源線 15 の断線や破損が抑制されるから、本実施形態によれば発光装置 D の歩留まりを向上することも可能である。

【0068】

ところで、電源線 15 の低抵抗化という観点のみからすれば、駆動トランジスタ  $T_{dr}$  や容量素子  $C_1$  だけでなく選択トランジスタ  $T_{sl}$  や初期化トランジスタ  $T_{int}$  にも電源線 15 が重なり合う構成 (以下「構成 2」という) としてもよい。しかしながら、この構成 2においては、選択トランジスタ  $T_{sl}$  や選択線 11 が電源線 15 と容量的に結合し (すなわち両者間に容量が寄生し)、この容量に起因して選択信号  $S_a$  に波形の鈍りが発生し易いという問題がある。同様に、初期化トランジスタ  $T_{int}$  や初期化線 12 と電源線 15 との間に付随する容量も、初期化信号  $S_b$  の波形の鈍りの原因となり得る。したがって、構成 2においては、選択トランジスタ  $T_{sl}$  や初期化トランジスタ  $T_{int}$  のスイッチングが遅延するという問題がある。

【0069】

これに対し、本実施形態においては、基板 10 に垂直な方向からみて、選択トランジスタ  $T_{sl}$  や選択線 11 および初期化トランジスタ  $T_{int}$  や初期化線 12 には電源線 15 が重なり合わないから、これらの要素と電源線 15 との間に寄生する容量は構成 2 と比較して低減される。したがって、本実施形態によれば、選択信号  $S_a$  や初期化信号  $S_b$  の波形の鈍りを抑制して選択トランジスタ  $T_{sl}$  や初期化トランジスタ  $T_{int}$  を高速に動作させることができる。

【0070】

< B - 2 : 第 2 実施形態 >

次に、本発明の第 2 実施形態における単位素子 P の具体的な構成を説明する。図 12 は、本実施形態における単位素子 P の構成を示す平面図であり、図 13 ないし図 15 は、単位素子 P が形成される各段階における基板 10 の面上の様子を示す平面図である。なお、

10

20

30

40

50

以下に示す各形態において、第1実施形態と共通する要素には同一の符号を付してその説明を適宜に省略する。

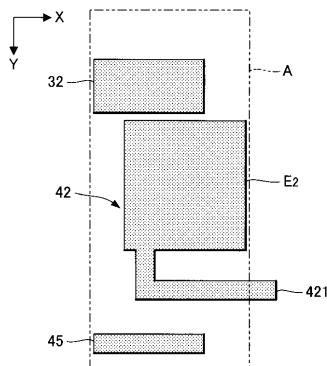

#### 【0071】

図13に示すように、基板10の面上には半導体層32と半導体層42と半導体層45とが半導体材料によって同層から形成される。半導体層32は、駆動トランジスタTdrを構成する略矩形状の部分である。半導体層42は、半導体層32からみてY方向の正側に形成された部分であり、略矩形状の電極E2と、電極E2の左下部からX方向に延在する素子部421とを含む。素子部421は、選択トランジスタTsIの半導体層として機能する部分である。半導体層45は、初期化トランジスタTintを構成する部分であり、半導体層42を挟んで半導体層32とは反対側の領域にてX方向に延在する。

10

#### 【0072】

以上の各部が形成された基板10の表面はゲート絶縁層L0に覆われる。図14に示すように、ゲート絶縁層L0の面上には、第1データ線部131と選択線11および初期化線12と中間導電体52と第1中継配線部171とが同層から形成される。第1データ線部131は、第1実施形態と同様にデータ線13を構成する部分であり、中間導電体52からみてX方向の正側の領域にてY方向に延在する。

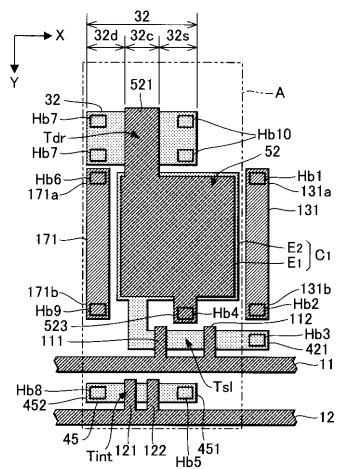

#### 【0073】

初期化線12は、X方向に延在する部分からY方向の負側に分岐して半導体層45に重なり合う第1ゲート電極121と第2ゲート電極122とを有する。半導体層45のうち第1ゲート電極121および第2ゲート電極122の各々と重なり合う部分が初期化トランジスタTintのチャネル領域である。同様に、選択線11は、X方向に延在する部分からY方向の負側に分岐して半導体層42の素子部421に重なり合う第1ゲート電極111と第2ゲート電極112とを有する。第1ゲート電極111と第2ゲート電極112とは間隔をあけてX方向に隣接する。素子部421のうちゲート絶縁層L0を挟んで第1ゲート電極111および第2ゲート電極112の各々と重なり合う部分が選択トランジスタTsIのチャネル領域である。以上のように、本実施形態の選択トランジスタTsIおよび初期化トランジスタTintは、デュアルゲート構造の薄膜トランジスタである。

20

#### 【0074】

中間導電体52は、電極E2に対向して容量素子C1を構成する電極E1と、電極E1からY方向の負側に連続するゲート電極521と、電極E1のうちX方向における略中央からY方向の正側に突出する接続部523とを含む。ゲート電極521は、半導体層32のY方向に沿った全寸法にわたって半導体層32と重なり合うようにY方向に延在する。図14に示すように、半導体層32のうちゲート絶縁層L0を挟んでゲート電極521に対向する領域が駆動トランジスタTdrのチャネル領域32cである。また、チャネル領域32cを挟んでX方向の負側の領域はドレイン領域32dであり、その反対側の領域はソース領域32sである。

30

#### 【0075】

第1中継配線部171は、初期化トランジスタTintと駆動トランジスタTdrのドレイン領域32dとを電気的に接続するための配線（以下「中継配線」という）を構成する部分であり、中間導電体52からみてX方向の負側の領域にてY方向に延在する。すなわち、本実施形態における中間導電体52は第1データ線部131と第1中継配線部171との間隙に配置される。

40

#### 【0076】

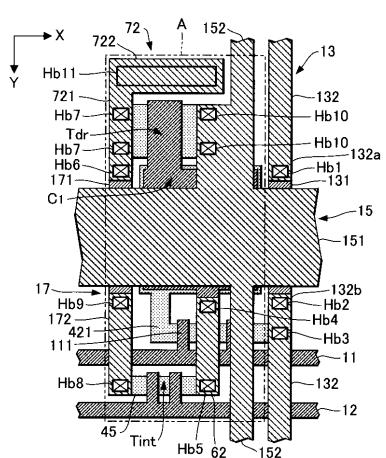

以上の各部が形成されたゲート絶縁層L0の表面はその全域にわたって第1絶縁層L1に覆われる。図12および図15に示すように、第1絶縁層L1の面上には、第2データ線部132と接続部62と第2中継配線部172と素子導通部72と電源線15とが形成される。

#### 【0077】

第2データ線部132は、第1実施形態と同様に、第1データ線部131と協働してデータ線13を構成する配線である。すなわち、第2データ線部132は、コンタクトホー

50

ル Hb1を介して第1データ線部 131 の上端部 131a(図14参照)に導通する端部 132aからY方向に延在して端部 132bに至る。端部 132bは、コンタクトホール Hb2を介して第1データ線部 131 の下端部 131b(図14参照)に導通する。また、本実施形態の第2データ線部 132 は、第1絶縁層 L1とゲート絶縁層 L0とを貫通するコンタクトホール Hb3を介して素子部 421 の端部に導通する。すなわち、データ線 13 と選択トランジスタ Tsl とはコンタクトホール Hb3を介して電気的に接続される。

#### 【0078】

図14および図15に示すように、接続部 62 は、中間導電体 52 の接続部 523 と半導体層 45 のX方向における正側の端部 451 とに重なり合うようにY方向に延在する。

接続部 62 は、第1絶縁層 L1 を貫通するコンタクトホール Hb4を介して接続部 523 (電極 E1 やゲート電極 521 ) ) に導通するとともに、第1絶縁層 L1とゲート絶縁層 L0とを貫通するコンタクトホール Hb5を介して半導体層 45 の端部 451 に導通する。すなわち、容量素子 C1 の電極 E1 (さらには駆動トランジスタ Tdr のゲート電極 521 ) と初期化トランジスタ Tint とは接続部 62 を介して電気的に接続される。

#### 【0079】

図15のように基板 10 に垂直な方向からみると、接続部 62 は、選択トランジスタ Tsl の第1ゲート電極 111 と第2ゲート電極 112との間隙の領域内に位置する。したがって、接続部 62 は第1ゲート電極 111 や第2ゲート電極 112 と重なり合わない。ここで、例えば第1ゲート電極 111 (または第2ゲート電極 112 ) と接続部 62 とが重なり合う構成においては、両者が容量的に結合する。したがって、接続部 62 の電位 (すなわち電極 E1 や駆動トランジスタ Tdr のゲート電極 511 の電位) の変動に伴なって第1ゲート電極 111 の電位も変化し、この結果として初期化信号 Sb の波形が鈍る場合がある。初期化信号 Sb の波形の鈍りは初期化トランジスタ Tint の動作の動作の遅延の原因となる。

#### 【0080】

これに対し、本実施形態においては、第1ゲート電極 111 や第2ゲート電極 112 とは重なり合わないように接続部 62 が形成されるから、接続部 62 と第1ゲート電極 111 や第2ゲート電極 112 との間の容量的な結合は抑制される。したがって、接続部 62 の電位の変動が初期化トランジスタ Tint に与える影響が低減され、この結果として初期化トランジスタ Tint を高速に動作させることが可能となる。

#### 【0081】

また、以上のように初期化トランジスタ Tint と容量素子 C1 の電極 E1 とが接続部 62 を介して導通する構成によれば、選択トランジスタ Tsl や初期化トランジスタ Tint のチャネル長を充分に確保できるから、チャネル長が制限される構成と比較して選択トランジスタ Tsl や初期化トランジスタ Tint における電流のリークを抑制することが可能である。選択トランジスタ Tsl や初期化トランジスタ Tint は駆動トランジスタ Tdr のゲート電極 521 に接続されるから、各々における電流のリークの削減によって、駆動期間におけるゲート電極 521 の電位の変動が抑制される。したがって、本実施形態によれば、発光素子 E の光量を高い精度で所期値に維持することが可能である。

#### 【0082】

図15の素子導通部 72 は、第1実施形態の素子導通部 71 と同様に駆動トランジスタ Tdr のドレイン電極と発光素子 E の第1電極 21 との間に介在して両者を電気的に接続する部分である。この素子導通部 72 は、Y方向に延在する部分 721 と、駆動トランジスタ Tdr を挟んで容量素子 C1 とは反対側に位置する部分 722 とが連続する形状 (略 L 字状) である。部分 721 は、第1中継配線部 171 の端部 171a(図14参照)と半導体層 32 のドレイン領域 32d とに重なり合う。部分 721 は、第1絶縁層 L1 を貫通するコンタクトホール Hb6を介して上端部 171a に導通する。

#### 【0083】

第1絶縁層 L1 のうちドレイン領域 32d と重なり合う領域には、第1絶縁層 L1 とゲート絶縁層 L0 とを貫通する複数 (ここでは 2 個) のコンタクトホール Hb7 が形成される。

10

20

30

40

50

これらのコンタクトホールHb7はゲート電極521が延在するY方向（すなわち駆動トランジスタTdrのチャネル幅の方向）に配列する。素子導通部72の部分721は、各コンタクトホールHb7を介してドレイン領域32dに導通する。

#### 【0084】

第2中継配線部172は、図14および図15に示すように、半導体層45におけるX方向の負側の端部452と第1中継配線部171とに重なり合うようにY方向に延在する配線である。この第2中継配線部172は、第1絶縁層L1とゲート絶縁層L0とを貫通するコンタクトホールHb8を介して端部452に導通するとともに、第1絶縁層L1を貫通するコンタクトホールHb9を介して第1中継配線部171の下端部171bに導通する。以上のように、初期化トランジスタTintと駆動トランジスタTdrのドレイン領域32d（さらには素子導通部72）とは、第1中継配線部171と第2中継配線部172とから構成される中継配線17を介して電気的に接続される。10

#### 【0085】

図16は、図15の段階にある4個の単位素子PがX方向およびY方向にわたって配列する様子を示す平面図である。図15および図16に示すように、本実施形態における電源線15は、複数の単位素子PにわたってX方向に延在する第1部分151と、複数の単位素子PにわたってY方向に延在する第2部分152とが交差する形状（格子状）の配線である。

#### 【0086】

図15に示すように、第1絶縁層L1のうち半導体層32のソース領域32sと重なり合う領域には、第1絶縁層L1とゲート絶縁層L0とを貫通する複数（ここでは2個）のコンタクトホールHb10が形成される。これらのコンタクトホールHb10はゲート電極521が延在するY方向に配列する。電源線15（第2部分152）は、各コンタクトホールHb10を介してソース領域32sに導通する。20

#### 【0087】

第1部分151は、各第2データ線部132の間隙の領域と、第2中継配線部172および素子導通部72（部分721）の間隙の領域とを通過するようにX方向に延在する。したがって、図15や図16のように基板10に垂直な方向からみると、第1部分151は、第1データ線部131と第1中継配線部171と容量素子C1とに重なり合う。また、第2部分152は、素子導通部72（部分722）および第2データ線部132の間隙の領域と、接続部62および第2データ線部132の間隙の領域とを通過するようにY方向に延在する。図15や図16に示すように、電源線15は、選択トランジスタTslや初期化トランジスタTintに重なり合わない。30

#### 【0088】

以上の各要素が形成された第1絶縁層L1の表面はその全域にわたって第2絶縁層L2に覆われる。図12に示すように、発光素子Eやその間隙を仕切る隔壁25は第2絶縁層L2の面上に形成される。素子導通部72の部分722は、第1実施形態と同様に、第2絶縁層L2を貫通するコンタクトホールHb11を介して第1電極21に導通する。図12に示すように、発光素子Eや隔壁25の具体的な構成は第1実施形態と同様である。

#### 【0089】

以上に説明したように、本実施形態においては、駆動トランジスタTdrを挟んで容量素子C1とは反対側に素子導通部72が配置される。したがって、第1実施形態と同様に、電極E1と素子導通部72とに寄生する容量（図11の容量Cx）が削減され、この結果として容量素子C1の容量値を削減することができる。また、選択トランジスタTslや初期化トランジスタTintと重なり合わないように電源線15が形成されるから、第1実施形態と同様に、選択トランジスタTslや初期化トランジスタTintを所期のタイミングにて高速に動作させることができる。40

#### 【0090】

また、本実施形態においては、素子導通部72や接続部62や第2中継配線部172が電源線15と同層から形成され、かつ、駆動トランジスタTdrを挟んでX方向の負側（す

50

なわち電源線 15 の幅方向の一方の側)に素子導通部 72 が配置されるとともにその反対側(電源線 15 の幅方向における他方の側)に接続部 62 や第 2 中継配線部 172 が配置される。したがって、素子導通部 72 と接続部 62 (第 2 中継配線部 172)との間隙に、電源線 15 のうち X 方向に延在する第 1 部分 151 が形成されるべきスペースを充分に確保することが可能である。さらに、基板 10 に垂直な方向からみて容量素子 C1 と重なり合うスペースも電源線 15 の形成に利用できる。したがって、第 1 実施形態と同様に、電源線 15 (第 1 部分 151) を幅広に形成してその抵抗を低減できるという効果が奏される。

#### 【0091】

しかも、本実施形態においては、Y 方向に延在する第 2 部分 152 によって各第 1 部分 151 が連結されるから、電源線 15 が第 1 部分 151 のみから構成される場合と比較して、電源線 15 の抵抗をいっそう低減することができる。また、電源線 15 の第 1 部分 151 の形状が単純な帯状とされるから、電源線 15 と同層から形成される要素(素子導通部 72 や接続部 62)を避けるように電源線 15 が複雑な形状に形成された構成と比較して、電源線 15 の断線や破損を抑制することができる。

10

#### 【0092】

また、本実施形態においては、各単位素子 P における X 方向の正側の周縁に沿ってデータ線 13 が延在するとともに X 方向の負側の周縁に沿って中継配線 17 が延在する。この構成において、例えば図 16 に示すように任意のひとつの単位素子 P1 とその X 方向の負側に隣接する他の単位素子 P2 とに着目すると、単位素子 P1 の容量素子 C1 と単位素子 P2 に対応したデータ線 13 との間には単位素子 P1 の中継配線 17 が介在する。したがって、ひとつの単位素子 P の容量素子 C1 とこれに隣接する単位素子 P のデータ線 13 とが近接する第 1 実施形態の構成と比較して、単位素子 P1 の容量素子 C1 と単位素子 P2 のデータ線 13 との間に形成される容量は低減される。この構成によれば、単位素子 P2 のデータ線 13 の電位の変動が単位素子 P1 の容量素子 C1 に与える影響が低減されるから、各単位素子 P における駆動トランジスタ Tdr のゲート電位 Vg やこのゲート電位 Vg に応じた発光素子 E の光量を高い精度で所期値に設定することができる。

20

#### 【0093】

##### <第 2 実施形態の変形例>

次に、以上に説明した第 2 実施形態の変形例を説明する。図 17 は、本変形例において第 1 絶縁層 L1 が形成された段階(図 14 の段階)を示す平面図である。第 2 実施形態においては、駆動トランジスタ Tdr のゲート電極 521 が Y 方向に延在する構成を例示した。これに対し、本変形例においては、図 17 に示すようにゲート電極 521 が X 方向に延在する。なお、本変形例のうち第 2 実施形態と同様の要素については共通の符号を付してその説明を適宜に省略する。

30

#### 【0094】

図 17 に示すように、本実施形態の中間導電体 52 は、電極 E1 の左上部から Y 方向の負側に延在する連結部 525 と、この連結部 525 から X 方向に延在して半導体層 32 と重なり合うゲート電極 521 とを含む。ゲート電極 521 は、半導体層 32 の X 方向における全寸法にわたって X 方向に延在する。半導体層 32 のうちゲート絶縁層 L0 を挟んでゲート電極 521 に対向する領域が駆動トランジスタ Tdr のチャネル領域 32c である。また、チャネル領域 32c を挟んで電極 E1 側の領域がソース領域 32s であり、その反対側の領域がドレイン領域 32d である。

40

#### 【0095】

図 18 は、図 17 の段階からさらに電源線 15 や素子導通部 72 が形成された段階(図 15 の段階)を示す平面図である。図 18 に示すように、素子導通部 72 は、駆動トランジスタ Tdr を挟んで容量素子 C1 とは反対側の領域に略矩形状に形成される。図 17 および図 18 に示すように、素子導通部 72 は、ゲート電極 511 が延在する X 方向(すなわち駆動トランジスタ Tdr のチャネル長の方向)に配列する複数のコンタクトホール Hb7 を介してドレイン領域 32d に導通する。また、電源線 15 は、ゲート電極 511 に沿って

50

X 方向に配列する複数のコンタクトホール Hb10 を介してソース領域 32s に導通する。

【0096】

以上に説明したように駆動トランジスタ Tdr のゲート電極 521 は X 方向に延在するから、ドレイン領域 32d は、ゲート電極 521 を挟んで容量素子 C1 とは反対側の領域に、X 方向に沿って長尺状に形成される。この構成においては、駆動トランジスタ Tdr に沿って Y 方向に延在する部分（第 1 実施形態の部分 721）を素子導通部 72 に形成する必要がない。したがって、本変形例によれば、図 18 と図 15との対比から理解されるように、電源線 15 のうちゲート電極 521 の方向に延在する第 1 部分 151 を、第 2 実施形態よりも幅広に形成できるという利点がある。

【0097】

また、本変形例においては、各コンタクトホール Hb7 とコンタクトホール Hb6（中継配線 17 と素子導通部 72 とが導通する部分）とコンタクトホール Hb1（第 1 データ線部 131 と第 2 データ線部 132 とが導通する部分）とが X 方向に沿って直線状に配列する。したがって、各コンタクトホール（Hb7・Hb6・Hb1）の Y 方向における位置が相違する構成と比較して、X 方向に沿って直線状（帯状）に延在する第 1 部分 151 の線幅を充分に確保することができる。

【0098】

ところで、第 2 実施形態においては、電源線 15 の第 1 部分 151 と直交する方向にゲート電極 521 が延在する。したがって、ゲート電極 521 の長さ（より厳密には素子導通部 72 の部分 721 の長さ）が増加するほど第 1 部分 151 の線幅は縮小される。これに対し、本変形例においては、第 1 部分 151 と平行な方向にゲート電極 521 が延在するから、第 1 部分 151 の線幅を縮小することなくゲート電極 521 の長さを増加させることができる。ゲート電極 521 の長さは駆動トランジスタ Tdr のチャネル幅に相当するから、本変形例によれば、第 1 部分 151 の線幅を維持しながら駆動トランジスタ Tdr のチャネル幅を増大させることができる。このようにチャネル幅が大きい駆動トランジスタ Tdr によれば、電源線 15 から駆動トランジスタ Tdr を経由して発光素子 E に供給される電流量を充分に確保できるという利点がある。

【0099】

< C : 変形例 >

以上の形態には様々な変形が加えられる。具体的な変形の態様を例示すれば以下の通りである。なお、以下の各態様を適宜に組み合わせてもよい。

【0100】

< C - 1 : 変形例 1 >

以上の各形態における単位素子 P の電気的な構成は適宜に変更される。本発明に適用される単位素子 P の具体的な態様を以下に例示する。

【0101】

(1) 図 19 に示すように、駆動トランジスタ Tdr と発光素子 E との間にトランジスタ（以下「発光制御トランジスタ」という） Tcnt が介在する構成としてもよい。この発光制御トランジスタ Tcnt は、駆動トランジスタ Tdr のドレイン電極と発光素子 E の第 1 電極 21 との電気的な接続を、発光制御線 14 に供給される発光制御信号 Sc に応じて制御するスイッチング素子である。発光制御トランジスタ Tcnt がオン状態に変化すると電源線 15 から発光素子 E への電流の経路が形成されて発光素子 E の発光が許可され、発光制御トランジスタ Tcnt がオフ状態に変化するとこの経路が遮断されて発光素子 E の発光が禁止される。したがって、この構成によれば、初期化期間や書き込み期間を除外した駆動期間のみにおいて発光制御トランジスタ Tcnt をオン状態として発光素子 E を発光させるといった具合に、発光素子 E が実際に発光する期間を正確に規定することができる。

【0102】

第 1 実施形態および第 2 実施形態の各々において、発光制御トランジスタ Tcnt は、例えば駆動トランジスタ Tdr を挟んで容量素子 C1 とは反対側（すなわち Y 方向の負側）に配置される。この態様によれば、例えば発光制御トランジスタ Tcnt が駆動トランジスタ

10

20

30

40

50

$T_{dr}$ と容量素子C1との間隙の領域に配置された構成と比較して、電源線15を駆動トランジスタ $T_{dr}$ および容量素子C1の双方と重なり合うように幅広に形成できるという利点がある。

#### 【0103】

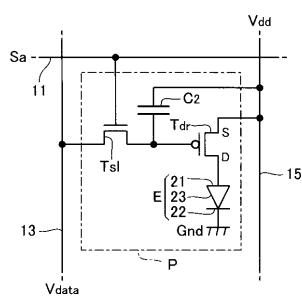

(2) 図20に示すように、駆動トランジスタ $T_{dr}$ のゲート電極とソース電極(電源線15)との間に容量素子C2が介挿された構成としてもよい。この構成によれば、書込期間にて設定された駆動トランジスタ $T_{dr}$ のゲート電位 $V_g$ を駆動期間にて容量素子C2に保持できるという利点がある。もっとも、駆動トランジスタ $T_{dr}$ のゲート電極の面積(チャネル領域の面積)が充分に確保される構成においては、この駆動トランジスタ $T_{dr}$ のゲート容量によってゲート電位 $V_g$ が保持される。したがって、第1実施形態および第2実施形態のように容量素子C2が配置されない構成であっても、駆動期間にてゲート電位 $V_g$ を保持することは可能である。10

#### 【0104】

(3) 図21に示す構成の単位素子Pも採用される。この単位素子Pにおいては、以上の各形態における容量素子C1や初期化トランジスタ $T_{int}$ (初期化線12)が形成されず、駆動トランジスタ $T_{dr}$ のゲート電極とデータ線13との電気的な接続が選択トランジスタ $T_{sl}$ によって制御される。また、駆動トランジスタ $T_{dr}$ のゲート電極とソース電極(電源線15)との間には容量素子C2が介在する。20

#### 【0105】

この構成において選択トランジスタ $T_{sl}$ がオン状態に変化すると、発光素子Eに指定された階調に応じたデータ電位 $V_{data}$ がデータ線13から選択トランジスタ $T_{sl}$ を経由して駆動トランジスタ $T_{dr}$ のゲート電極に供給される。このときに容量素子C2にはデータ電位 $V_{data}$ に応じた電荷が蓄積されるから、選択トランジスタ $T_{sl}$ がオフ状態に変化しても、駆動トランジスタ $T_{dr}$ のゲート電位 $V_g$ はデータ電位 $V_{data}$ に維持される。したがって、発光素子Eには、駆動トランジスタ $T_{dr}$ のゲート電位 $V_g$ に応じた電流(データ電位 $V_{data}$ に応じた電流)が継続的に供給される。この電流の供給によって発光素子Eはデータ電位 $V_{data}$ に応じた輝度で発光する。20

#### 【0106】

図21の容量素子C2は、例えば以上の各形態における容量素子C1と同様の態様で基板10の面上に配置される。この形態によっても第1実施形態から第2実施形態と同様の作用および効果が奏される。以上のように、駆動トランジスタ $T_{dr}$ のゲート電極に接続される容量素子は、容量カップリングによって駆動トランジスタ $T_{dr}$ のゲート電位 $V_g$ を設定するための容量素子C1であってもよいし、データ線13から駆動トランジスタ $T_{dr}$ のゲート電極に供給されるデータ電位 $V_{data}$ を保持するための容量素子C2であってもよい。30

#### 【0107】

< C - 2 : 変形例 2 >

以上の形態においては第1電極21が光反射性の材料によって形成された構成を例示したが、発光層23から基板10側への出射光が第1電極21とは別個の反射層によって基板10とは反対側に反射される構成としてもよい。この構成においては、光反射性の材料によって第1絶縁層L1の面上に反射層が形成され、この反射層を覆うように第1電極21が形成される。第1電極21は、ITOやIZOなどの光透過性の導電性材料によって形成される。また、以上の形態においては第2電極22が光透過性の材料によって形成された構成を例示したが、遮光性または光反射性を有する導電性材料を充分に薄く形成した電極が第2電極22とされた構成によっても発光層23からの放射光を透過させることができる。40

#### 【0108】

もっとも、発光層23からの出射光が基板10を透過して出射するボトムエミッション型の発光装置にも本発明は適用される。この構成においては、例えば、光反射性の導電性材料によって第2電極22が形成されるとともに光透過性の導電性材料によって第1電極21が形成される。そして、発光層23から基板10側への出射光と、発光層23から基

10

20

30

40

50

板10とは反対側に出射して第2電極22の表面にて反射した光とが、第1電極21および基板10を透過して出射する。

【0109】

<C-3：変形例3>

第1実施形態や第2実施形態においては電源線15が選択トランジスタT<sub>s1</sub>および初期化トランジスタT<sub>int</sub>の何れにも重なり合わない構成を例示したが、電源線15が選択トランジスタT<sub>s1</sub>と重なり合う構成や電源線15が初期化トランジスタT<sub>int</sub>と重なり合う構成も採用される。

【0110】

<C-4：変形例4>

第2実施形態においては、接続部62が選択トランジスタT<sub>s1</sub>の第1ゲート電極111と第2ゲート電極112との間隙の領域に形成される構成を例示した。これと同様に、電源線15の第2部分152が初期化トランジスタT<sub>int</sub>の第1ゲート電極121と第2ゲート電極122との間隙の領域に形成されてもよい。

【0111】

<C-5：変形例5>

第1実施形態においては、電源線15がX方向に延在する部分（本発明における「第1部分」）のみを含む構成を例示したが、第2実施形態のように、これらの部分の各々を相互に連結するようにY方向に延在する部分（以下「第2部分」という）を電源線15が含む構成としてもよい。この第2部分は、例えば、図7に図示された接続部61と素子導通部71との間隙の領域や各単位素子Pの間隙の領域にてY方向に延在し、Y方向に隣接する各電源線15（第1部分）を相互に連結する。この構成によれば、第1実施形態と比較して電源線15の抵抗を低減することが可能である。

【0112】

<C-6：変形例6>

以上の各形態においては、隔壁25の内周縁の内側の領域のみに発光層23が形成された構成を例示したが、基板10の全面（より詳細には第2絶縁層L2の全面）にわたって発光層23が連続に形成された構成としてもよい。この構成によれば、例えば、スピント法などの低廉な成膜技術を発光層23の形成に採用できるという利点がある。なお、第1電極21は発光素子Eごとに個別に形成されるから、発光層23が複数の発光素子Eにわたって連続することは言っても、発光層23の光量は発光素子Eごとに個別に制御される。以上のように発光層23が複数の発光素子Eにわたって連続する構成においては隔壁25を省略してもよい。

【0113】

なお、隔壁25で仕切られた各空間に発光材料の液滴を吐出するインクジェット法（液滴吐出法）で発光層23を形成する場合には、以上の各形態のように第2絶縁層L2の面上に隔壁25を配置した構成が好適に採用される。ただし、発光層23を発光素子Eごとに形成するための方法は適宜に変更される。より具体的には、基板10の全域に形成された発光材料の膜体を選択的に除去する方法や、レーザ転写（LITI: Laser-Induced Thermal Imaging）法など各種のパターニング技術によっても発光層23は発光素子Eごとに形成される。この場合には、隔壁25の形成を不要としながら発光素子Eごとに独立に発光層23を形成できる。以上のように、本発明の発光装置において隔壁25は必ずしも必要な要素ではない。

【0114】

<C-7：変形例7>

以上の各形態においては有機EL材料からなる発光層23を含む発光素子Eを例示したが、本発明における発光素子はこれに限定されない。例えば、無機EL材料からなる発光層を含む発光素子やLED（Light Emitting Diode）素子など様々な発光素子を採用することができる。本発明における発光素子は、電気エネルギーの供給（典型的には電流の供給）によって発光する素子であれば足り、その具体的な構造や材料の如何は不問である。

## 【0115】

## &lt; D : 應用例 &gt;

次に、本発明に係る発光装置を利用した電子機器の具体的な形態を説明する。図22は、以上に説明した何れかの形態に係る発光装置Dを表示装置として採用したモバイル型のパソコンコンピュータの構成を示す斜視図である。パソコンコンピュータ2000は、表示装置としての発光装置Dと本体部2010とを備える。本体部2010には、電源スイッチ2001およびキーボード2002が設けられている。この発光装置Dは有機EL材料の発光層23を発光素子Eに使用しているので、視野角が広く見易い画面を表示できる。

## 【0116】

図23に、各形態に係る発光装置Dを適用した携帯電話機の構成を示す。携帯電話機3000は、複数の操作ボタン3001およびスクロールボタン3002、ならびに表示装置としての発光装置Dを備える。スクロールボタン3002を操作することによって、発光装置Dに表示される画面がスクロールされる。

## 【0117】

図24に、各形態に係る発光装置Dを適用した携帯情報端末(PDA:Personal Digital Assistants)の構成を示す。情報携帯端末4000は、複数の操作ボタン4001および電源スイッチ4002、ならびに表示装置としての発光装置Dを備える。電源スイッチ4002を操作すると、住所録やスケジュール帳といった各種の情報が発光装置Dに表示される。

## 【0118】

なお、本発明に係る発光装置が適用される電子機器としては、図22から図24に示したもののはか、デジタルスチルカメラ、テレビ、ビデオカメラ、カーナビゲーション装置、ページヤ、電子手帳、電子ペーパー、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、プリンタ、スキヤナ、複写機、ビデオプレーヤ、タッチパネルを備えた機器等などが挙げられる。また、本発明に係る発光装置の用途は画像の表示に限定されない。例えば、光書き込み型のプリンタや電子複写機といった画像形成装置においては、用紙などの記録材に形成されるべき画像に応じて感光体を露光する書き込みヘッドが使用されるが、この種の書き込みヘッドとしても本発明の発光装置を利用することができる。

## 【符号の説明】

## 【0119】

D……発光装置、P……単位素子、E……発光素子、10……基板、11……選択線、12……初期化線、13……データ線、15……電源線、21……第1電極、22……第2電極、23……発光層、31, 32, 41, 42, 45……半導体層、51, 52……中間導電体、61, 62……接続部、71, 72……素子導通部、511, 521……ゲート電極、Tdr……駆動トランジスタ、Tsl……選択トランジスタ、Tint……初期化トランジスタ、C1……容量素子、E1, E2……電極、L0……ゲート絶縁層、L1……第1絶縁層、L2……第2絶縁層。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【 図 1 3 】

【 図 1 4 】

【 図 1 5 】

【図16】

【図17】

【図18】

【図20】

【図19】

【図21】

【図22】

【図24】

【図23】

## 【手続補正書】

【提出日】平成24年6月22日(2012.6.22)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

発光素子と、

電源線と、

前記電源線と前記発光素子との間に電気的に接続された第1のトランジスタと、

前記第1のトランジスタのソースまたはドレインと前記発光素子とを電気的に接続する素子導通部と、を備え、

前記電源線と前記素子導通部は、同層に設けられており、

前記素子導通部は、第1の方向に沿って設けられた第1の部分と、前記第1の方向と交差する第2の方向に沿って設けられた第2の部分と、を有し、

平面視において、前記第1の部分と前記第2の部分との間には、前記第1のトランジスタのゲート電極が位置していることを特徴とする電気光学装置。

## 【請求項2】

前記電源線は、前記第1の方向に延在する第3の部分と、前記第2の方向に延在する第4の部分と、を有し、

平面視において、前記第1の部分、前記第2の部分および前記第1のトランジスタのゲート電極は、前記電源線の前記第3の部分と前記第4の部分とで区画された複数の領域内のうちの第1の領域に位置していることを特徴とする請求項1に記載の発光装置。

**【請求項 3】**

前記第1のトランジスタのゲート電極と前記第1のトランジスタのドレインとの間に電気的に接続された第2のトランジスタと、

前記第1のトランジスタのゲート電極と前記第2のトランジスタのソースまたはドレンとを電気的に接続する接続部と、を備え、

平面視において、前記第2のトランジスタおよび前記接続部は、前記電源線の前記第3の部分と前記第4の部分とで区画された複数の領域内のうちの前記第1の領域とは異なる第2の領域に位置していることを特徴とする請求項2に記載の発光装置。

**【請求項 4】**

駆動期間において、前記第1のトランジスタは前記発光素子に電流を供給し、

前記駆動期間の前の期間において、前記第2のトランジスタがオン状態にあることで、前記第1のトランジスタがダイオード接続されることを特徴とする請求項1乃至3のいずれか1項に記載の発光装置。

**【請求項 5】**

前記発光素子は、第1の電極と、第2の電極と、前記第1の電極と前記第2の電極との間に設けられた発光層と、を有し、

前記第1の電極と前記素子導通部とは、第1のコンタクトホールを介して電気的に接続されており、

前記第1のコンタクトホールは、前記素子導通部の第1の部分に設けられていることを特徴とする請求項1乃至4のいずれか1項に記載の発光装置。

**【請求項 6】**

前記素子導通部と前記第1のトランジスタのソースまたはドレンとは、第2のコンタクトホールを介して電気的に接続されており、

前記第2のコンタクトホールは、前記素子導通部の第2の部分に設けられていることを特徴とする請求項5に記載の発光装置。

**【請求項 7】**

前記第1の電極は、前記電源線と平面的に重なる部分を有することを特徴とする請求項5または6に記載の発光装置。

**【請求項 8】**

前記第2の方向は、データ線が延在する方向であることを特徴とする請求項1乃至7のいずれか1項に記載の発光装置。

**【請求項 9】**

請求項1から請求項8のいずれかに記載の発光装置を備える電子機器。

---

フロントページの続き

(72)発明者 野澤 陵一

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

Fターム(参考) 3K107 AA01 BB01 BB04 BB08 CC45 DD39 EE03 HH05

5C094 AA04 AA13 AA25 AA43 AA53 BA03 BA27 DA13 DB04 DB10

EA10