(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5962167号

(P5962167)

(45) 発行日 平成28年8月3日(2016.8.3)

(24) 登録日 平成28年7月8日(2016.7.8)

|                |                            |

|----------------|----------------------------|

| (51) Int.Cl.   | F 1                        |

| G 0 1 J  1/42  | (2006.01)   G 0 1 J  1/42  |

| G 0 1 J  1/44  | (2006.01)   G 0 1 J  1/44  |

| G 0 1 V  8/10  | (2006.01)   G 0 1 V  9/04  |

| G 0 1 N  21/35 | (2014.01)   G 0 1 N  21/35 |

| H 0 4 N  5/33  | (2006.01)   H 0 4 N  5/33  |

請求項の数 12 (全 20 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2012-95353 (P2012-95353)    |

| (22) 出願日  | 平成24年4月19日(2012.4.19)         |

| (65) 公開番号 | 特開2013-221907 (P2013-221907A) |

| (43) 公開日  | 平成25年10月28日(2013.10.28)       |

| 審査請求日     | 平成27年3月25日(2015.3.25)         |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (74) 代理人  | 100095728<br>弁理士 上柳 雅善                       |

| (74) 代理人  | 100107261<br>弁理士 須澤 修                        |

| (72) 発明者  | 山村 光宏<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内       |

| 審査官       | 塙本 丈二                                        |

最終頁に続く

(54) 【発明の名称】検出回路、センサーデバイス及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

焦電素子と、

前記焦電素子からの検出信号がゲートに入力されるトランジスターを含むソースフォローワー回路と、

前記トランジスターに流れる電流を遮断する第1スイッチング素子と、

前記焦電素子と前記トランジスターのゲートとの接続を遮断する第2スイッチング素子と、を有し、

前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除する前に、前記第2スイッチング素子が前記焦電素子と前記トランジスターのゲートとの接続を遮断することを特徴とする検出回路。

## 【請求項 2】

請求項1において、

前記第2スイッチング素子と前記トランジスターのゲートとを接続する配線の電荷を放電させる放電スイッチをさらに有することを特徴とする検出回路。

## 【請求項 3】

請求項2において、

前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除する後であつて、かつ、前記第2スイッチング素子が前記焦電素子と前記トランジスターのゲートとの接続の遮断を解除する前に、前記放電スイッチによる放電が終了することを特徴とする

検出回路。

【請求項 4】

請求項3において、

前記第2スイッチング素子により前記ゲートと前記焦電素子との接続が解除される前に、前記放電スイッチが放電動作を開始することを特徴とする検出回路。

【請求項 5】

請求項1乃至4のいずれか1項において、

前記ソースフォロワー回路は、

前記検出回路の出力ノードと低電位電源ノードとの間に設けられ、前記焦電素子からの検出信号がゲートに入力される第1のP型トランジスターと、

高電位電源ノードと前記出力ノードとの間に設けられ、ゲートが基準電圧に設定される第2のP型トランジスターと、

を有することを特徴とする検出回路。

【請求項 6】

請求項5において、

前記第2のP型トランジスターのゲートに前記基準電圧を供給する基準電圧生成回路がさらに設けられ、

前記基準電圧生成回路は、前記高電位電源ノードと前記低電位電源ノードとの間に直列接続された第3のP型トランジスターと第4のP型トランジスターとを有し、

前記低電位電源ノードがドレインに接続された前記第3のP型トランジスターのソースと、前記高電位電源ノードがソースに接続された前記第4のP型トランジスターのドレインとの接続ノードが、前記基準電圧生成回路の出力ノードとされ、

前記第3のP型トランジスターは、前記低電位電源ノードがゲートに接続され、

前記第4のP型トランジスターは、前記基準電圧生成回路の出力ノードがゲートに接続されることを特徴とする検出回路。

【請求項 7】

請求項6において、

前記第1スイッチング素子は、前記第1のP型トランジスター及び前記第2のP型トランジスターに流れる電流を遮断する第5のP型トランジスターであり、

前記基準電圧生成回路は、前記第3のP型トランジスター及び前記第4のP型トランジスターに流れる電流を遮断する第6のP型トランジスターを有し、

前記第5のP型トランジスター及び前記第6のP型トランジスターのゲートに同一信号が供給されることを特徴とする検出回路。

【請求項 8】

請求項1乃至7のいずれか1項に記載の検出回路を含むことを特徴とするセンサーデバイス。

【請求項 9】

複数の行線と、

複数の列線と、

前記複数の行線と前記複数の列線の各1本に接続される複数の画素回路と、を有し、

前記複数の画素回路の各々は、

焦電素子と、

前記焦電素子からの検出信号がゲートに入力されるトランジスターを含むソースフォロワー回路と、

前記トランジスターに流れる電流を遮断する第1スイッチング素子と、

前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除する前に、前記焦電素子と前記トランジスターのゲートとの間を遮断する第2スイッチング素子と、

前記複数の行線の1本が駆動される期間に、前記焦電素子の電荷の変化に基づく信号を、前記複数の列線の1本に供給する画素選択スイッチと、

前記第2スイッチング素子と前記トランジスターのゲートとを接続する配線の電荷を放

10

20

30

40

50

電させる放電スイッチと、を含み、

駆動された前記 1 本の行線に接続された画素回路では、前記第 1 スイッチング素子が前記トランジスターに流れる電流の遮断を解除した後であって、かつ、前記第 2 スイッチング素子が前記焦電素子と前記トランジスターのゲートとの接続の遮断を解除する前に、前記放電スイッチによる放電を終了することを特徴とするセンサーデバイス。

【請求項 10】

請求項 9 において、

前記第 1 スイッチング素子は、前記 1 本の行線に接続された画素回路に共用されることを特徴とするセンサーデバイス。

【請求項 11】

10

請求項 1 乃至 7 のいずれか 1 項に記載の検出回路を含むことを特徴とする電子機器。

【請求項 12】

請求項 8 乃至 10 のいずれか 1 項に記載のセンサーデバイスを含むことを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、焦電素子を備えた検出回路、センサーデバイス及び電子機器等に関する。

【背景技術】

【0002】

20

従来、焦電素子等を用いた赤外線の検出回路が知られている。例えば人体からは、波長が  $10 \mu m$  付近の赤外線が輻射されており、これを検出することで人体の存在や温度の情報を非接触で取得できる。従って、このような赤外線の検出回路を利用して侵入検知や物理量計測を実現できる。

【0003】

赤外線の検出回路の従来技術としては例えば非特許文献 1 に開示される技術が知られている。非特許文献 1 の従来技術では図 1 に示すように、直列接続されたトランジスター (J F E T) と抵抗とから構成されるソースフォロワー回路により、焦電素子の焦電流を検出している。

【先行技術文献】

30

【非特許文献】

【0004】

【非特許文献 1】 Daisuke Akai et al. , "Pyroelectric infrared sensors with fast response time and high sensitivity using epitaxial PbZr, TiO<sub>3</sub> films on epitaxial -Al<sub>2</sub>O<sub>3</sub>/Si substrates" , Sensors and Actuators A: Physical, Volumes 130-131, 14 August 2006, Pages 111-115, Elsevier Science B.V.

【発明の概要】

【発明が解決しようとする課題】

【0005】

非特許文献 1 では、各画素回路内のソースフォロア回路に常時電流が流れている。この電流は画素数の増加に伴って増大し、大きな電源電圧降下を引き起こすという問題があった。

【0006】

本発明の幾つかの態様によれば、画素回路内のソースフォロア回路に常時電流が流れるのを抑制し、あるいは電流遮断時のノイズが焦電流に悪影響することを抑制できる検出回路、センサーデバイス及び電子機器を提供することができる。

【課題を解決するための手段】

【0007】

(1) 本発明の一態様は、

焦電素子と、

40

50

前記焦電素子からの検出信号がゲートに入力されるトランジスターを含むソースフォロワー回路と、

前記トランジスターに流れる電流を遮断する第1スイッチング素子と、

前記焦電素子と前記トランジスターのゲートとの接続を遮断する第2スイッチング素子と、

を有する検出回路に関する。

【0008】

本発明の一態様によれば、第1スイッチング素子がソースフォロワー回路内のトランジスターに流れる電流を遮断するので、画素回路内のソースフォロア回路に常時電流が流れることを抑制できる。ソースフォロワー回路内のトランジスターには比較的大きな電流が流れているので、第1スイッチング素子の遮断解除動作によりソースフォロワー回路を動作させる際に、スイッチングノイズを引き起こす。このスイッチングノイズが、トランジスターのゲート-ソース間寄生容量を介してゲートに伝達され、さらにゲートから焦電素子に伝達される虞がある。焦電素子にノイズが伝達されると、微小な焦電流による電荷はノイズの大きな電荷に埋もれてしまい、焦電流の変動に伴う電圧変化をソースフォロワー回路が検出できなくなる。第2スイッチング素子が焦電素子とトランジスターのゲートとの接続を遮断できるので、スイッチングノイズが焦電素子に伝達されることはない。なお、焦電素子からの焦電流は十分に小さいので、第2スイッチング素子のオン/オフによるスイッチングノイズは無視できる。

【0009】

(2) 本発明の一態様では、前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除する前に、前記第2スイッチング素子が前記焦電素子と前記トランジスターのゲートとの接続を遮断することができる。

【0010】

それにより、ソースフォロワー回路が動作中にスイッチングノイズが焦電素子に伝達されることはない。なお、第1スイッチング素子の遮断動作時のスイッチングノイズが焦電素子に伝達されても問題はない。つまり、第1スイッチング素子がトランジスターに流れる電流を遮断するときに、第2スイッチング素子が焦電素子とトランジスターのゲートとの接続を維持していてもよい。このときソースフォロワー回路は動作停止状態だからである。

【0011】

(3) 本発明の一態様では、前記第2スイッチング素子と前記トランジスターのゲートとを接続する配線の電荷を放電させる放電スイッチをさらに有することができる。

【0012】

放電スイッチは、ゲートから第2スイッチング素子を接続する配線上にスイッチングノイズが重畳しているとき、そのスイッチングノイズを含む電荷を放電させることができる。

【0013】

(4) 本発明の一態様では、前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除した後であって、かつ、前記第2スイッチング素子が前記焦電素子と前記トランジスターのゲートとの接続の遮断を解除する前に、前記放電スイッチによる放電を終了することができる。

【0014】

こうすると、第1スイッチング素子の動作によりスイッチングノイズが発生しても、そのノイズの電荷は放電スイッチにより放電され、放電後に第2スイッチング素子によりゲートと焦電素子とが接続されるので、ノイズの電荷が焦電素子に伝達されない。

【0015】

(5) 本発明の一態様では、前記第2スイッチング素子により前記ゲートと前記焦電素子との接続が解除される前に、前記放電スイッチが放電動作を開始することができる。

【0016】

10

20

30

40

50

放電スイッチのオン／オフによって、光照射後の焦電素子にチャージされた電荷と、焦電素子よりディスチャージされた光照射前の電荷との変化に基づく信号（電圧変化）を検出することができる。こうして、光照射前後の電圧変化を高感度にて検出することができる。

【0017】

（6）本発明の一態様では、

前記ソースフォロア回路は、

前記検出回路の出力ノードと低電位電源ノードとの間に設けられ、前記焦電素子からの検出信号がゲートに入力される第1のP型トランジスターと、

高電位電源ノードと前記出力ノードとの間に設けられ、ゲートが基準電圧に設定される第2のP型トランジスターと、

を有することができる。

【0018】

こうすると、第1、第2のP型トランジスターのしきい値電圧等の特性バラツキの影響が出力電圧に及ぶのを抑制できるため、素子特性のバラツキを原因とする出力電圧のバラツキの低減が可能になる。

【0019】

（7）本発明の一態様では、前記第2のP型トランジスターのゲートに前記基準電圧を供給する基準電圧生成回路がさらに設けられ、

前記基準電圧生成回路は、前記高電位電源ノードと前記低電位電源ノードとの間に直列接続された第3のP型トランジスターと第4のP型トランジスターとを有し、

前記低電位電源ノードがドレインに接続された前記第3のP型トランジスターのソースと、前記高電位電源ノードがソースに接続された前記第4のP型トランジスターのドレインとの接続ノードが、前記基準電圧発生回路の出力ノードとされ、

前記第3のP型トランジスターは、前記低電源ノードがゲートに接続され、

前記第4のP型トランジスターは、前記基準電圧発生回路の出力ノードをゲートに接続することができる。

【0020】

このように、基準電圧  $V_{CC}/2$  を生成する基準電圧発生回路の第3、第4のP型トランジスターは、ソースフォロワー回路の第1、第2のP型トランジスターと同じ構成となり、プロセスばらつきがあっても第1、第2のP型トランジスターと同じ傾向でばらつくので、相対的なばらつきが解消されて、プロセス変動への依存が少ない出力を確保することができる。特に、第1～第4のP型トランジスターのサイズを同一にすれば、プロセスばらつきの影響を最小にすることができます。

【0021】

（8）本発明の一態様では、

前記第1スイッチング素子は、前記第1のP型トランジスター及び前記第2のP型トランジスターに流れる電流を遮断する第5のP型トランジスターであり、

前記基準電圧生成回路は、前記第3のP型トランジスター及び前記第4のP型トランジスターに流れる電流を遮断する第6のP型トランジスターを有し、

前記第5のP型トランジスター及び前記第6のP型トランジスターのゲートに同一信号を供給することができる。

【0022】

これにより、ソースフォロワー回路と、それを駆動する基準電圧生成回路の双方での貫通電流を抑制して消費電力を低減できる。

【0023】

（9）本発明の他の態様は、上述の（1）～（8）の検出回路を含むセンサーデバイスを定義している。

【0024】

（10）本発明のさらに他の態様は、

10

20

30

40

50

複数の行線と、

複数の列線と、

前記複数の行線と前記複数の列線の各1本に接続される複数の画素回路と、

を有し、

前記複数の画素回路の各々は、

焦電素子と、

前記焦電素子からの検出信号がゲートに入力されるトランジスターを含むソースフォローワー回路と、

前記トランジスターに流れる電流を遮断する第1スイッチング素子と、

前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除する前に、

前記焦電素子と前記トランジスターのゲートとの間を遮断する第2スイッチング素子と、

前記複数の行線の1本が駆動される期間に、前記焦電素子の電荷の変化に基づく信号を、

前記複数の列線の1本に供給する画素選択スイッチと、

前記第2スイッチング素子と前記トランジスターのゲートとを接続する配線の電荷を放電させる放電スイッチと、

を含み、

駆動された前記1本の行線に接続された画素回路では、前記第1スイッチング素子が前記トランジスターに流れる電流の遮断を解除した後であって、かつ、前記第2スイッチング素子が前記焦電素子と前記トランジスターのゲートとの接続の遮断を解除する前に、前記放電スイッチによる放電を終了するセンサーデバイスに関する。

【0025】

こうすると、1本の行線を駆動する期間毎に1本の行線に接続された画素回路から同時に読み出す際に、上述したスイッチングノイズが焦電素子に与える悪影響を排除できる。

【0026】

(11) 本発明のさらに他の態様では、前記第1スイッチング素子は、前記1本の行線に接続された画素回路に共用することができる。こうすると、1本の行線に接続された画素回路に対して共用される一つの第1スイッチング素子を設けるだけでよく、1本の行線に接続された画素回路の各々に第1スイッチング素子を設けなくて済む。

【0027】

(12) 本発明のさらに他の態様は、(1)～(8)の検出回路または(9)～(11)のセンサーデバイスを含む電子機器を定義している。

【図面の簡単な説明】

【0028】

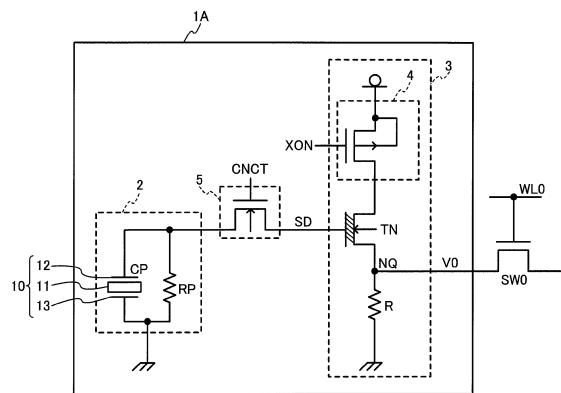

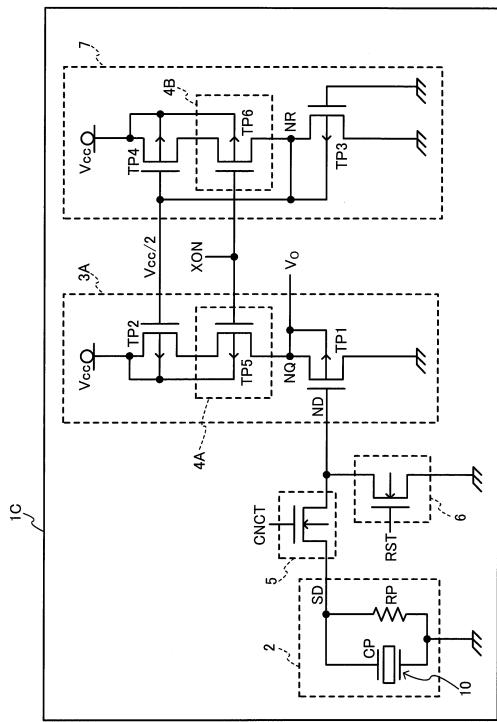

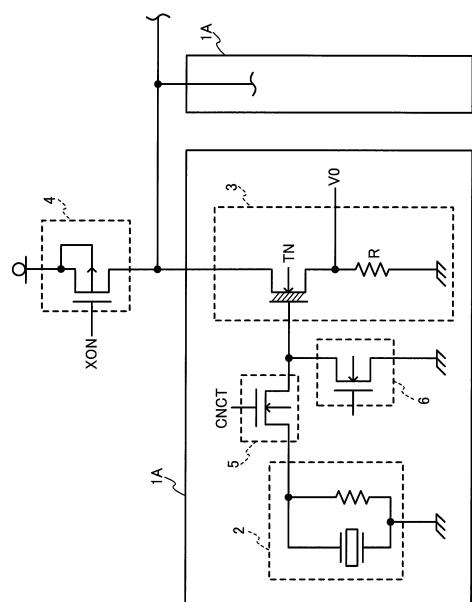

【図1】本発明の一実施形態に係る検出回路の回路図である。

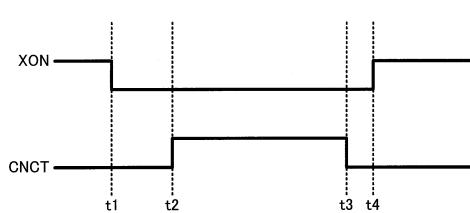

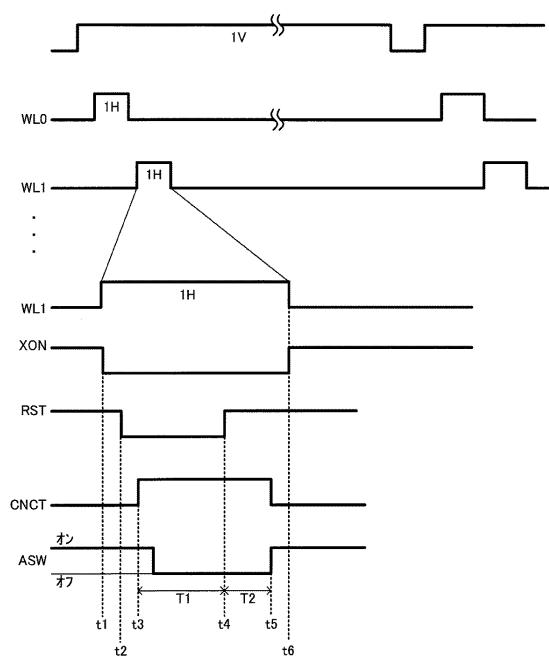

【図2】図1に示す検出回路の動作を示すタイミングチャートである。

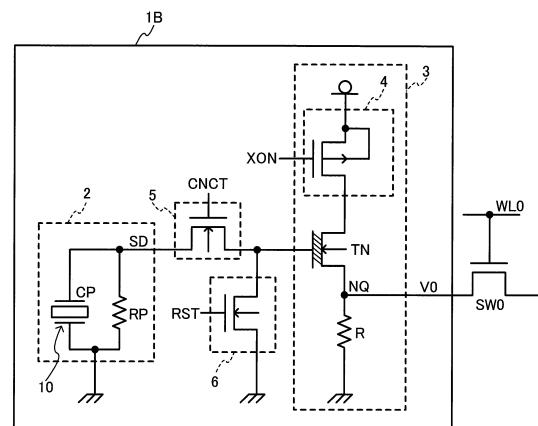

【図3】本発明の他の実施形態に係る検出回路の回路図である。

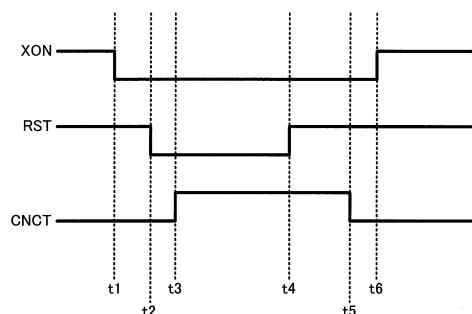

【図4】図3に示す検出回路の動作を示すタイミングチャートである。

【図5】2つのP型トランジスターを備えたソースフォローワー回路と基準電圧生成回路を備えた本発明のさらに他の実施形態に係る検出回路の回路図である。

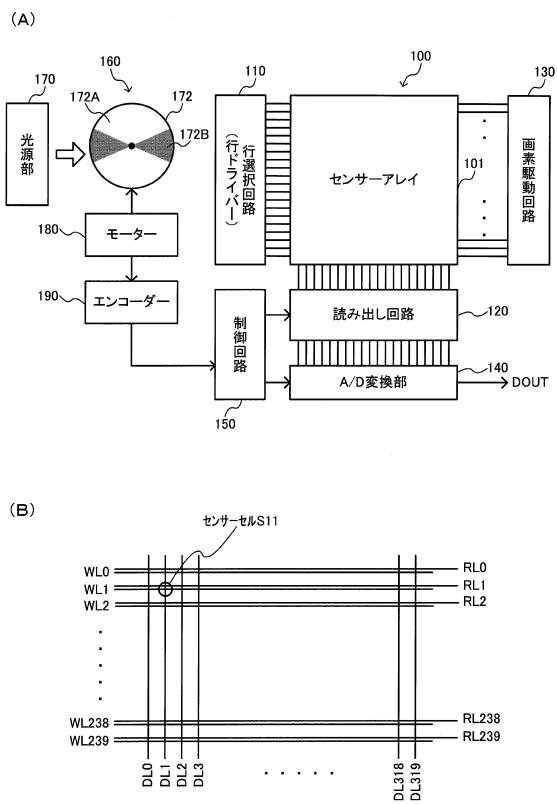

【図6】図6(A)(B)はセンサーデバイスの構成図である。

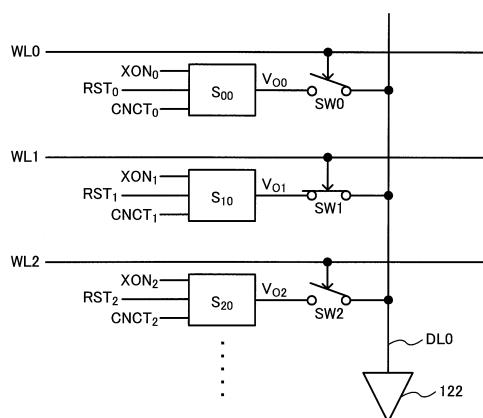

【図7】增幅回路を備えた1本の列線に接続される複数の画素回路を示すブロック図である。

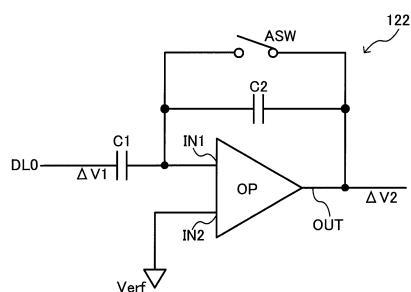

【図8】增幅回路を示す回路図である。

【図9】センサーデバイスのタイミングチャートである。

【図10】複数の画素回路に対して一つの第1スイッチング素子を共用する変形例の回路図である。

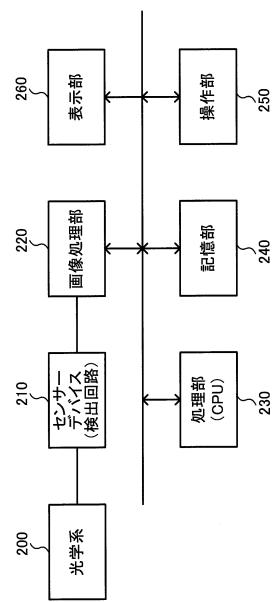

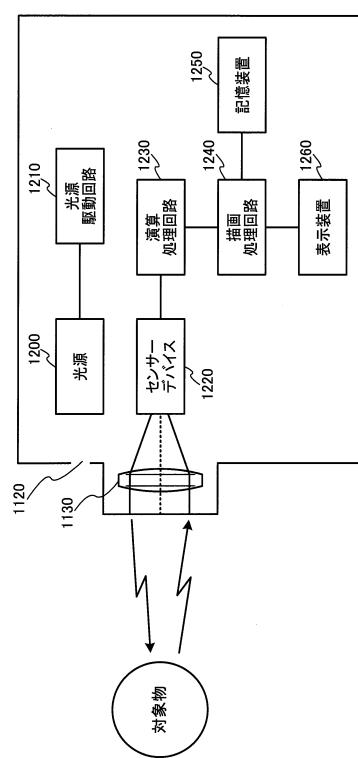

【図11】電子機器のブロック図である。

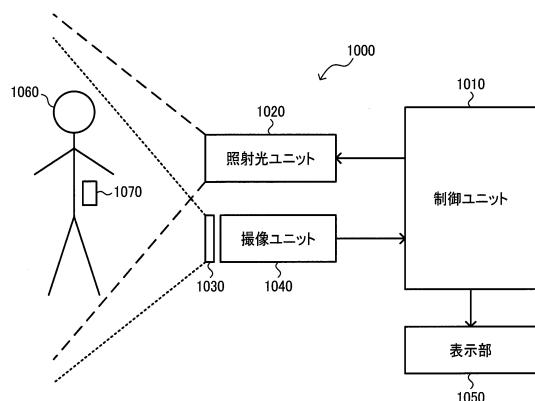

【図12】テラヘルツカメラを含む体温測定装置(電子機器)を示す図である。

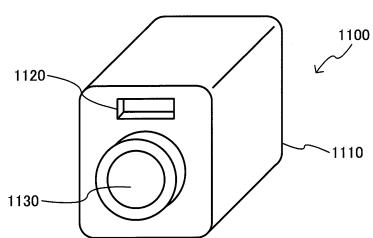

【図13】テラヘルツカメラの斜視図である。

【図14】テラヘルツカメラのブロック図である。

10

20

30

40

50

## 【発明を実施するための形態】

## 【0029】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

## 【0030】

## 1. 第1実施形態

図1に示す検出回路(画素回路ともいう)1Aは、焦電素子2とソースフォロワー回路3とを含む基本回路を有する。図1に示す画素回路1Aは、行線WL0により制御される画素選択スイッチSW0に接続することができる。

10

## 【0031】

焦電素子2は、焦電キャパシター10の容量CPと抵抗RPとにより、等価的に表される。焦電素子2には例えば波長が赤外帯域の光(赤外線線)やテラヘルツの光(電磁波ともいう)等の光が入射され、焦電キャパシター10の焦電体(強誘電体)11には、焦電素子2の温度に応じた自発分極が発生している。そして電極12、13の表面電荷と電気的に中性を保っている。

## 【0032】

ソースフォロワー回路3は、例えばN型のデプレッション・トランジスターTNと、ブルダウン抵抗Rとを含む。

20

## 【0033】

N型のデプレッション・トランジスターTNと抵抗Rは、VCCのノード(広義には高電位電源ノード)とGNDのノード(広義には低電位電源ノード)の間に直列に設けられ、ソースフォロワー回路3を構成している。

## 【0034】

N型トランジスターTNのゲートには、焦電素子2からの検出信号SD(検出電圧)が入力され、N型トランジスターTNのソースは、抵抗Rの一端に接続される。これらのトランジスターTNと抵抗Rによりソースフォロワー回路3が構成され、そのゲインはほぼ1になる。そしてN型トランジスターTNのソースに対応する出力ノードNQから、検出信号SDの電圧変化に伴い変化する出力電圧VOが出力される。

30

## 【0035】

本実施形態の画素回路1Aは、焦電素子2とソースフォロワー回路3とを含む基本回路に、さらに追加の構成を備えている。第1スイッチング素子4は、N型トランジスターTNに流れる電流を遮断し、N型トランジスターTNと直列接続された例えばP型トランジスターにて形成されている。第2スイッチング素子5は、焦電素子2とN型トランジスターTNのゲートとの接続を遮断し、例えばN型トランジスターで形成されている。

## 【0036】

画素回路1Aでは、第1スイッチング素子4のゲートに入力される信号XONが、図2に示すように一定期間だけLOWとなる。なお、信号XONは、図1に示す行線WL0をアクティブとして画素選択スイッチSW0をオンさせる水平走査信号の反転信号とすることができます。信号XONがHIGHである期間は第1スイッチングトランジスター4がオフされるので、ソースフォロワー回路3内のトランジスターTNに流れる電流を遮断して、画素回路1A内のソースフォロア回路3に常時電流が流れることを抑制できる。

40

## 【0037】

信号XONがLOWである期間に第1スイッチング素子4がオンする。このとき、従来のように光入射に起因して焦電素子2にて温度変化があると、その温度変化によって分極量が変化する焦電素子2に焦電流が流れ、検出信号SDが変化する。この検出信号SDがゲートに供給されるトランジスターTNは、そのソースに対応する出力ノードNQから、検出信号SDの電圧変化に伴い変化する出力電圧VOが出力される。

## 【0038】

このとき、第1スイッチング素子4がオン/オフされると、トランジスターTNのソ-

50

ス電圧、チャネル電圧、ドレイン電圧が大きく変動する。これらの電圧変動がノイズとして、比較的大きなトランジスターTNのゲート寄生容量を介してトランジスターTNのゲートに伝達され、さらにゲートから焦電素子2に伝達される虞がある。

【0039】

もし焦電素子2にノイズが伝達されると、微小な焦電流による電荷はノイズの大きな電荷に埋もれてしまい、焦電流の変動に伴う電圧変化をソースフォロワー回路3が検出できなくなる。

【0040】

そこで、焦電素子2とトランジスターTNのゲートとの接続を遮断する第2スイッチング素子5を設けている。こうして、第1スイッチング素子4がオン／オフされる時には、第2スイッチング素子5により焦電素子2とトランジスターTNのゲートとの接続を遮断しておくことができる。それにより、スイッチングノイズがトランジスターTNのゲートに伝達されたとしても、そのスイッチングノイズが焦電素子2に伝達されることを防止できる。なお、第2スイッチング素子5はノイズの発生の少ないトランジスターで構成できるため、オン／オフ動作によるスイッチングノイズは無視できるほど小さくすることができる。

10

【0041】

特に、第1スイッチング素子4が図2の時刻t1にてオンされて遮断解除されたときに発生するノイズが問題となる。ソースフォロワー回路3が動作状態となり、ノイズが重畠された電荷に基づく検出信号SDが、ソースフォロワー回路3のトランジスターTNのゲートに供給された状態で検出動作が実施されてしまうからである。従って、本実施形態では、図2に示すように、時刻t1にて信号XONをLOWにして第1スイッチング素子4により遮断解除する時には、第2スイッチング素子5のゲートに供給される信号CNCCTをLOWとして、第2スイッチング素子5により焦電素子2とトランジスターTNのゲートとの接続を遮断している。

20

【0042】

図2の時刻t1後の時刻t2にて、第2スイッチング素子5のゲートに供給される信号CNCCTがHIGHとなるので、焦電素子2からの、ノイズが重畠されていない電荷に基づく検出信号SDが、ソースフォロワー回路3のトランジスターTNのゲートに供給されて、検出動作を実施できる。

30

【0043】

一方、第1スイッチング素子4が図2の時刻t4にて遮断動作する時のスイッチングノイズは、焦電素子2に伝達されても問題はない。つまり、第1スイッチング素子4がトランジスターTNに流れる電流を遮断するときに、第2スイッチング素子5が焦電素子2とトランジスターTNのゲートとの接続を維持していてもよい。このときソースフォロワー回路3は動作停止状態だからである。よって、第2スイッチング素子5のゲートに供給される信号CNCCTをLOWとして第2スイッチング素子5により遮断動作を開始する時刻t3は、時刻t4の前後の何れであってもよい。

【0044】

2. 第2実施形態

40

図3は、図1の検出回路(画素回路)1Aに放電スイッチ6を追加した検出回路(画素回路)1Bを示している。

【0045】

図3に示す放電スイッチは、第2スイッチング素子5とトランジスターTNのゲートとを接続する配線の電荷を放電させるスイッチであり、例えばN型トランジスターにて形成される。

【0046】

放電スイッチ6は、トランジスターTNのゲートと第2スイッチング素子5とを接続する配線上にスイッチングノイズが重畠しているとき、そのスイッチングノイズを含む電荷を放電させることができる。

50

## 【0047】

図4は、図3に示す画素回路1Bのタイミングチャートであり、信号XONのLOW期間 $t_1 - t_6$ と、信号CNCTのHIGH期間 $t_3 - t_5$ は、図2と同様に設定されている。

## 【0048】

放電スイッチ6による放電動作は、図4に示す時刻 $t_1$ の前から実施され、時刻 $t_1$ と時刻 $t_3$ との間の時刻 $t_2$ に終了させることができる。つまり、放電スイッチ6による放電動作は、第1スイッチング素子4がトランジスターTNに流れる電流の遮断を解除する時(図4の時刻 $t_1$ )の後であって、かつ、第2スイッチング素子5が焦電素子2とトランジスターTNのゲートとの接続の遮断を解除する時(図4の時刻 $t_3$ )よりも前の時刻 $t_2$ に終了させることができる。10

## 【0049】

こうすると、第1スイッチング素子4の動作によりスイッチングノイズが発生しても、そのノイズの電荷は放電スイッチ6により放電され、放電後に第2スイッチング素子5によりトランジスターTNのゲートと焦電素子2とが接続されるので、ノイズの電荷が焦電素子2に伝達されることはない。

## 【0050】

また、放電スイッチ6による放電動作は、図4に示す時刻 $t_1$ と同時またはそれ以前から開始されていると良い。時刻 $t_1$ での第1スイッチング素子4の動作によりスイッチングノイズが発生しても、直ちにそのノイズの電荷を放電スイッチ6により放電できるからである。20

## 【0051】

また、第2スイッチング素子5によりトランジスターTNのゲートと焦電素子2との接続が解除される時刻 $t_5$ の前の時刻 $t_4$ に、放電スイッチ6が放電動作を開始することができる。

## 【0052】

ここで、図3の放電スイッチ6がオフしている図4の期間 $t_2 - t_4$ では、焦電素子2に電荷がチャージされた状態である。その一方で、図3の放電スイッチ6が図4の時刻 $t_4$ でオンすると、光照射時に蓄えられた電荷がディスチャージされる。放電スイッチ6がオンされた後の焦電素子2の電荷は、光照射中にも拘わらず光照射がない時の電荷となる。つまり、ソースフォロア回路3の出力電圧VOは、光照射前後の焦電流を反映した電圧変化となる。なお、放電スイッチ6がオンしてソースフォロワー回路3のトランジスターTNのゲートに0Vが印加されても、トランジスターTNはデエプレッション型であるのでオンされて、光照射前の出力電圧VOを出力することができる。30

## 【0053】

このように、第2スイッチング素子5がオンしている期間 $t_3 - t_5$ の途中で放電スイッチ6をオンさせることで、放電スイッチ6を電子チョッパーとして利用できる。つまり、図示しない機械式チョッパーにより光が継続して照射しているにも拘わらず、放電スイッチ6のオン/オフによって、期間 $t_3 - t_4$ での光照射後の焦電素子2の電荷と、期間 $t_4 - t_5$ での光照射前と等価のディスチャージ後の電荷との変化に基づく信号(電圧変化)を検出することができる。こうして、期間 $t_3 - t_5$ 中に時系列で出力される光照射の前後の電圧変化VOを高感度にて検出することができる。このため、各画素回路1Bに增幅回路を設ける必要が必ずしもなく、画素回路1Bを小型化することができる。40

## 【0054】

## 3. 第3実施形態

## 3.1. ソースフォロワー回路

図5は、本発明のさらに他の実施形態に係る検出回路(画素回路)1Cを示している。この画素回路1Cのソースフォロワー回路3Aは、図3に示すN型デプレッション・トランジスターTNに代えて、第1のP型トランジスターTP1と第2のP型トランジスターTP2とを有する。図5に示す検出回路1Cが、焦電素子2、第2スイッチング素子5及

び放電スイッチ 6 を有する点は、図 3 と同じである。なお、検出回路 1 C に接続される画素選択スイッチ SW 0 は省略されている。

【 0 0 5 5 】

第 1 の P 型トランジスター TP 1 ( P 型 M O S トランジスター ) は、出力ノード N Q と G N D ノード ( 低電位電源ノード ) との間に設けられる。例えば図 5 では TP 1 のソースが出力ノード N Q に接続され、ドレインが G N D ノードに接続され、焦電素子 2 からの検出信号 S D がゲートに入力される。

【 0 0 5 6 】

第 2 の P 型トランジスター TP 2 ( P 型 M O S トランジスター ) は、 V C C ノード ( 高電位電源ノード ) と出力ノード N Q との間に設けられる。例えば図 5 では TP 2 のソースが V C C ノードに接続され、ドレインが出力ノード N Q に接続され、ゲートが出力ノード N Q と接続されて、そのゲートは基準電圧 V c c / 2 に設定される。

10

【 0 0 5 7 】

また、 P 型トランジスター TP 1 の基板電位は TP 1 のソースの電位に設定される。また P 型トランジスター TP 2 の基板電位は TP 2 のソースの電位に設定される。このように P 型トランジスター TP 1 、 TP 2 の基板電位をそのソース電位に設定することで、基板バイアス効果による TP 1 、 TP 2 のしきい値電圧の変動を防止できるため、 TP 1 と TP 2 のしきい値電圧を、より近づけることが可能になる。

【 0 0 5 8 】

P 型トランジスター TP 1 と TP 2 とは、そのゲート長及びゲート幅の両方を同一にして、 P 型トランジスター TP 1 、 TP 2 のしきい値電圧等の素子特性を近づけることが可能になる。こうして、製造プロセス変動等に起因する出力電圧 V o の変動を抑制できる。

20

【 0 0 5 9 】

図 5 に示すようにトランジスター TP 2 のゲートは基準電圧 V c c / 2 に設定されている。従って、トランジスター TP 2 のゲート・ソース間電圧はほとんど V c c / 2 であり、 TP 2 は飽和領域で動作するため、 TP 2 には、ほとんどゲート・ソース間電圧 V c c / 2 としきい値電圧だけが決まる電流が流れる。

【 0 0 6 0 】

一方、トランジスター TP 1 はトランジスター TP 2 に直列接続されているため、 TP 1 には同じ電流が流れる。そしてトランジスター TP 1 の基板電位は、トランジスター TP 2 と同様にソース電位に設定されている。従って、トランジスター TP 1 のしきい値電圧とトランジスター TP 2 のしきい値電圧を等しくできる。更にトランジスター TP 1 は飽和領域で動作し、トランジスター TP 1 と TP 2 が同一のトランジスタサイズ ( ゲート幅、ゲート長が同一 ) であるとすると、 TP 1 のゲート・ソース間電圧は、 TP 2 のゲート・ソース間電圧である V c c / 2 とほぼ同じ電圧になる。また、トランジスター TP 1 のゲートは第 2 スイッチング素子 5 を介して焦電素子 2 に接続され、 TP 1 のゲートのノード N D と G N D の間には焦電素子 1 0 の抵抗 R P が存在するため、ノード N D は定常的にはほぼ 0 V に設定される。より正確には、放電スイッチ 6 がオンしているときにはノード N D は 0 V であり、第 2 スイッチング素子 5 を介して焦電素子 2 がノード N D と接続された場合も、焦電素子 2 に蓄積された電荷は非常に小さいので、それが充電されたノード N D の電位はほぼ 0 V である。従って、トランジスター TP 1 のソースノードである検出回路の出力ノード N Q の電圧 V o は、定常的には V c c / 2 とほぼ同じ電圧に設定される。

30

【 0 0 6 1 】

この状態で焦電素子 2 に光が照射されて焦電素子 2 の温度が変化すると、図 4 の期間 t 3 - t 4 では、発生した焦電流によりトランジスター TP 1 のゲート ( ゲート容量 ) が過渡的に充電され、電圧が V だけ変動する。このとき、トランジスター TP 1 とトランジスター TP 2 には等しい電流が流れるため、トランジスター TP 1 とトランジスター TP 2 のゲート・ソース間電圧が等しくなるようにノード N Q の電圧が変化する。これにより、トランジスター TP 1 とトランジスター TP 2 のゲート・ソース間電圧は共に V c c /

40

50

2 -  $V / 2$  となり、このとき、TP1のソース電圧であるVQは、 $VQ = V_{CC} / 2 + V / 2$  となる。即ち、トランジスターTP1、TP2からなる回路はゲイン = 0.5のソースフォロワー回路3Aとして動作する。なお、ソースフォロワー回路3Aの電流を遮断する第1スイッチング素子4Aを、図1及び図3の第1スイッチング素子4として機能させることで、図4の期間  $t_4 - t_5$  での光照射前のディスチャージ電圧もサンプリングすることができる。

#### 【0062】

本実施形態の検出回路では、P型トランジスターTP1とTP2のしきい値電圧等が相殺されて、これらのしきい値電圧等の特性バラツキが出力電圧のバラツキとして現れることを抑制できる。従って、出力電圧のバラツキを低減でき、赤外線の検出精度等を向上できる。

10

#### 【0063】

##### 3.2. 基準電圧発生回路

図5では、例えば画素回路1C中に、第2のP型トランジスターTP2のゲートに基準電圧  $V_{CC} / 2$  を供給する基準電圧生成回路7を設けることができる。

#### 【0064】

基準電圧生成回路7は、高電位電源ノードと低電位電源ノードとの間に直列接続された第3のP型トランジスターTP3と第4のP型トランジスターTP4とを有する。低電位電源ノードがドレインに接続された第3のP型トランジスターTP3のソースと、高電位電源ノードがソースに接続された第4のP型トランジスターTP4のドレインとの接続ノードNRが、基準電圧発生回路7の出力ノードとされる。

20

#### 【0065】

第3のP型トランジスターTP3は低電位電源ノードがゲートに接続され、第4のP型トランジスターTP4は、基準電圧発生回路7の出力ノードNRがゲートに接続される。

#### 【0066】

つまり、基準電圧生成回路7の第3、第4のP型トランジスターTP3、TP4の構成は、焦電素子2に接続される第1、第2のP型トランジスターTP1、TP2と実質的に同じ構成である。第3のP型トランジスターTP3のゲートは低電位電源ノードの電圧0Vが供給されるが、焦電素子2の定常状態では第1のP型トランジスターTP1のゲート電圧SDは上述の通り0Vだからである。

30

#### 【0067】

ここで、基準電圧発生回路7の出力ノードNRの電圧は、焦電素子2が定常状態の時の第1、第2のP型トランジスターTP1、TP2と同様に第3、第4のトランジスターTP3、TP4が動作することで、 $V_{CC} / 2$  の定電圧となる。よって、第2のP型トランジスターTP2のゲートに、基準電圧  $V_{CC} / 2$  を供給することができる。

#### 【0068】

このように、基準電圧発生回路7の第3、第4のP型トランジスターTP3、TP4は、焦電素子2に接続される第1、第2のP型トランジスターTP1、TP2のソースフォロワー回路3Aと同じ構成となり、プロセスばらつきがあっても第1、第2のP型トランジスターTP1、TP2と同じ傾向となるので、プロセス変動への依存が少ない出力を確保することができる。特に、第1～第4のP型トランジスターTP1～TP4のサイズを同一にすれば、プロセスばらつきの影響を最小にすることができます。

40

#### 【0069】

##### 3.3. 第1のスイッチング素子

図5では、図1に示す第1スイッチング素子4と同様にして、ソースフォロワー回路3Aの電流を遮断する第1スイッチング素子4Aと、基準電圧発生回路7の電流を遮断する第1スイッチング素子4Bとを設けることができる。第1スイッチング素子4Aは第5のP型トランジスターTP5で形成でき、第1スイッチング素子4Bは第6のP型トランジスターTP6で形成できる。この場合、同一の信号XONにより第1スイッチング素子4A、4Bをオン／オフすることができる。

50

## 【0070】

## 4. センサーデバイス

## 4.1. センサーデバイスの概要

図6(A)(B)に本発明の一実施形態に係るセンサーデバイス100を示す。このセンサーデバイス100は、センサーレイ101と、行選択回路(行ドライバー)110と、読み出し回路120と、画素駆動回路130とを含む。またA/D変換部140、制御回路150を含むことができる。このセンサーデバイス100を用いることで、例えば赤外線カメラやテラヘルツカメラなどを実現できる。

## 【0071】

センサーレイ101(焦点面アレイ)には、複数の行線(ワード線、走査線)WLと複数の列線(データ線)DLとが設けられる。なお、図1、図3及び図5に示す信号XON、CNCST及びRSTの信号線は、図6(A)(B)では省略されている。

10

## 【0072】

センサーレイ101の各センサーセルは、各行線WLと各列線DLの交差位置に対応する場所に配置(形成)される。例えば図6(B)のセンサーセルS11は、行線WL1と列線DL1の交差位置に対応する場所に配置されている。他のセンサーセルも同様である。

## 【0073】

行選択回路110は、複数の行線WLに接続される。そして各行線WLの選択動作を行う。例えば図1(B)のようなQVGA(320×240画素)のセンサーレイ101(焦点面アレイ)を例にとれば、行線WL0、WL1、WL2、...WL239を順次選択(走査)する動作を行う。即ちこれらの行線WLを選択する信号(ワード選択信号)をセンサーレイ101に出力する。

20

## 【0074】

読み出し回路120は、複数の列線DLに接続される。そして各列線DLの読み出し動作を行う。QVGAのセンサーレイ101を例にとれば、列線DL0、DL1、DL2、...DL319からの検出信号(検出電流、検出電荷)を読み出す動作を行う。例えば読み出し回路120には、複数の列線の各列線に対応して各增幅回路が設けられる。そして、各增幅回路は、対応する列線の信号の增幅処理を行う。

## 【0075】

30

画素駆動回路130は、図1、図3及び図5に示す信号XON、CNCST及びRSTの信号線を駆動する。

## 【0076】

A/D変換部140は、読み出し回路120において取得された検出電圧(測定電圧、到達電圧)をデジタルデータにA/D変換する処理を行う。そしてA/D変換後のデジタルデータDOOUTを出力する。具体的には、A/D変換部140には、複数の列線DLに対応して各A/D変換器が設けられる。そして、各A/D変換器は、対応する列線DLにおいて読み出し回路120により取得された検出電圧のA/D変換処理を行う。なお、複数の列線DLに対応して1つのA/D変換器を設け、この1つのA/D変換器を用いて、複数の列線DLの検出電圧を時分割にA/D変換してもよい。また読み出し回路120の増幅回路を設けないで、各列線の信号を直接にA/D変換部140の各A/D変換器に入力するようにしてもよい。

40

## 【0077】

制御回路150(タイミング生成回路)は、各種の制御信号を生成して、行選択回路110、読み出し回路120、画素駆動回路130及びA/D変換部140のタイミングを制御する信号などを生成して出力する。

## 【0078】

センサーデバイス100の制御回路150は、このセンサーデバイスが搭載される電子機器側からタイミング信号を入力することができる。例えば図6(A)に示すように、電子機器は、波長が赤外帯域の光(赤外線)やテラヘルツ帯域の光(電磁波ともいう)を断

50

統制御が可能な光源 160 を有することができる。光源 160 は、例えば連続発光する光源部 170 と、チョッパー 172 と、チョッパー 172 を回転駆動するモーター 180 と、モーター 180 の回転量を符号化するエンコーダー 190 とを有することができる。

#### 【0079】

チョッパー 172 は、光源部 170 からの連続光をセンサーレイ 101 に透過させる透過部 172A と、連続光を遮断する遮断部 172B とが形成された円盤であり、モーター 180 の駆動により透過部 172A と遮断部 172B とが交互にセンサーレイ 101 と対向される。チョッパー 172 の透過部 172A がセンサーレイ 101 と対向する期間を少なくとも一水平走査期間 (1H) 以上、例えば一垂直期間 (1V) とすることができる。センサーデバイス 100 の制御回路 150 は、エンコーダー 190 からの出力が基準タイミング信号として入力されることで、一水平走査期間 (1H)、一垂直走査期間 (1V) やその他のタイミング信号を生成することができる。10

#### 【0080】

##### 4.2. 読み出し回路

本実施形態では、各画素回路に增幅回路を設ける必要はないが、図 6 (A) に示す読み出し回路 120 が、複数の列線 DL0 ~ DL319 に接続される複数の増幅回路をさらに有することができ、図 7 には列線 DL0 に接続される増幅回路 122 を示している。

#### 【0081】

図 7 に示す増幅回路 122 は、図 8 に示すように、第 1 入力端 IN1 に入力される列線 DL0 からの電圧と第 2 入力端 IN2 に入力される基準電圧 Vref ( 例えは Vcc/2 ) とを差動増幅して出力端に出力するアンプ OP と、第 1 入力端 IN1 と出力端 OUT をショートさせるアンプスイッチ ASW と、を有する。20

#### 【0082】

1 本の列線 DL に一つの増幅回路 122 が設けられることで、1 本の列線 DL に画素選択スイッチ SW0, SW1, SW2, ... を介して接続される列方向の複数の画素回路 1 ( 図 7 に示すセンサセル S00, S10, S20, ... 内の画素回路 1 ) で一つの増幅回路 122 が共用される。アンプスイッチ ASW をオンするとアンプ OP は第 1 入力端 S1 と出力端 OUT とがショートされて不動作状態となる。一水平走査期間 (1H) 毎にアンプ OP を不動作状態として、1 本の列線 DL に流れる複数の画素回路 1 からの電圧同士が影響するクロストークを防止できる。なお、画素選択スイッチ SW0, SW1, SW2, ... は、対応する画素回路に含めることができる。30

#### 【0083】

##### 4.3. センサーデバイスの動作

図 9 は、センサーデバイス 100 の動作を示すタイミングチャートである。図 6 (A) のチョッパー 172 の透過部 172A がセンサーレイ 101 と対向する期間が、図 9 に示す一垂直走査期間 (1V) である。図 9 に示す一垂直走査期間 (1V) に亘って、図 6 (A) に示すセンサーレイ 101 に光が照射されることになる。

#### 【0084】

図 6 (A) に示す制御回路 150 は、エンコーダー 190 からの基準タイミング信号に基づいて、一垂直走査期間 (1V) を示す一垂直走査信号を生成し、さらに行線 WL の本数に基づいて一水平走査期間 (1H) を示す一水平走査信号を生成する。40

#### 【0085】

図 6 (A) に示す行選択回路 110 は、複数の行線 WL0, WL1, ... に、図 9 に示すように一水平走査期間 (1H) 毎にアクティブとなる電位の走査信号を供給する。例えば行線 WL1 の電位がアクティブとなると、図 7 に示す行線 WL1 に接続された 320 個の画素回路 1 にて、図 7 に示す画素選択スイッチ SW1 が一水平走査期間 (1H) に亘って同時にオンされる。

#### 【0086】

これにより、行線 WL1 に接続された 320 個の画素回路 1 の各々にてセンサーデバイス 100 の焦電素子 2 からの検出信号 SD の電圧変化に伴う出力電圧 VO が画素選択スイ50

ツチ SW1 を介して、複数の列線 D L 0 ~ D L 2 3 9 に出力可能となる。

【 0 0 8 7 】

本実施形態では、画素駆動回路 1 3 0 は、一水平走査期間 ( 1 H ) の途中で、アクティブ電位である例えば行線 W L 1 に接続された一行分の 3 2 0 個の画素回路 1 内の放電スイッチ 6 を、複数のリセット線 R L 0 ~ R L 2 3 9 の 1 本 ( R L 1 ) に供給されるリセット信号 R S T ( 図 9 ) によりオンさせている。

【 0 0 8 8 】

一水平走査期間 ( 1 H ) は一垂直期間 ( 1 V ) に含まれるので図 6 ( A ) のセンサー アレイ 1 0 1 に光が入射されており、しかも一水平走査期間 ( 1 H ) 中では対応する画素回路 1 の画素選択スイッチ SW1 がオンされて、出力電圧 V O を対応する列線 D L 0 に出力することができる。

【 0 0 8 9 】

ここで、信号 X O N は例えば水平走査信号 W L の反転信号とすることができます。また、アンプスイッチ A S W のオフ期間の開始時期は、信号 C N C T が H I G H となる時刻 t 3 の後に設定され、アンプスイッチ A S W のオフ期間の終了時期は、信号 C N C T の H I G H 期間が終了する時刻 t 5 と一致させることができます。

【 0 0 9 0 】

図 9 に示すように、アンプスイッチ A S W は、一水平走査期間 ( 1 H ) 内であって放電スイッチ 6 がオンされる前にオフされる。信号 C N C T が H I G H となって第 2 スイッチング素子 5 がオンしてから放電スイッチ 6 がオンされるまでの第 1 期間 T 1 に、焦電素子 2 に電荷がチャージされた光照射後の焦電流を反映した電圧が出力される。その後放電スイッチ 6 がオンされた後の第 2 期間 T 2 では照射前の焦電流を反映した電圧が出力される。図 8 に示すアンプ O P は、上述した第 1 , 第 2 期間 T 1 + T 2 ではアンプスイッチ A S W がオフとなって動作状態であり、この期間の途中にて放電スイッチ 6 がオンされる。アンプ O P は第 1 期間 T 1 での光照射時の焦電流に伴う電圧と第 2 期間 T 2 での光照射前の焦電流に伴う電圧との差分 ( 電圧変化 ) V 1 を増幅する。

【 0 0 9 1 】

なお、図 9 でも図 4 に示す時刻 t 1 ~ t 6 の関係と等しく設定されているので、図 4 にて説明した作用効果をセンサー デバイス 1 0 0 の各画素でも奏することができます。

【 0 0 9 2 】

図 8 に示すように、アンプ O P は列線 D L 0 に接続される第 1 容量 C 1 と、第 1 入力端 I N 1 と出力端 O U T とに接続される第 2 容量 C 2 とをさらに有する。ここで、列線 D L 0 からの電圧変化を V 1 とし、アンプ O P の出力端 O U T の電圧変化を V 2 とし、第 1 容量 C 1 の容量値を C 1 とし、第 2 容量 C 2 の容量値を C 2 としたとき、 V 2 = V 1 × C 1 / C 2 が成立する。

【 0 0 9 3 】

このように、アンプ O P の出力端 O U T の電圧変化 V 2 には第 1 入力端 I N 1 の電圧変化 V 1 のみが利得 C 1 / C 2 で増幅されるので、焦電流の変化を電圧変化として増幅できる。

【 0 0 9 4 】

なお、図 6 ( A ) に示すセンサー デバイス 1 0 0 のようにセンサー セルをマトリクス状に有する場合には、図 1 、図 3 及び図 5 に示す一つの画素回路 1 A , 1 B , 1 C 内の特定の回路を全画素回路に設けることなく、特定回路を複数の画素回路にて共用することができます。

【 0 0 9 5 】

例えば、図 1 0 は一つの第 1 スイッチング素子 4 を、1 本の行線 W L に接続される一行分の画素回路 1 A にて共用する例を示している。1 本の行線 W L に接続される一行分の画素回路 1 A は、同一の一水平走査期間 ( 1 H ) 内にて同時に動作するので、その一行分の

10

20

30

40

50

画素回路 1 A 内のソースフォロワー回路 3 を一つの第 1 スイッチング素子 4 により同時に不動作とすることができる。

【 0 0 9 6 】

この他、図 3 に示す第 1 スイッチング素子 4 も図 10 と同様に共用することができる。また、図 5 に示す基準電圧発生回路 7 も 1 本の行線 W L に接続される一行分の画素回路 1 A にて共用することができる。もし、図 5 に示す基準電圧発生回路 7 に第 1 スイッチング素子 4 B を設けないのであれば、その基準電圧発生回路 7 は図 6 ( A ) ( B ) に示すセンサー アレイ 101 中の全画素回路に共用することができる。

【 0 0 9 7 】

5 . 電子機器

10

図 11 に本実施形態のセンサー デバイス含む電子機器の構成例を示す。この電子機器は、図 6 ( A ) に示す光源 160 の他に、光学系 200 、センサー デバイス 210 ( 検出回路 ) 、画像処理部 220 、処理部 230 、記憶部 240 、操作部 250 、表示部 260 を含む。なお本実施形態の電子機器は図 11 の構成に限定されず、その構成要素の一部 ( 例えば光学系、操作部、表示部等 ) を省略したり、他の構成要素を追加したりするなどの種々の変形実施が可能である。

【 0 0 9 8 】

光学系 200 は、例えば 1 又は複数のレンズや、これらのレンズを駆動する駆動部などを含む。そしてセンサー デバイス 210 への物体像の結像などを行う。また必要であればフォーカス調整なども行う。

20

【 0 0 9 9 】

センサー デバイス 210 は、図 6 等で説明したものであり、物体像の撮像処理を行う。画像処理部 220 は、センサー デバイス 210 からのデジタルの画像データ ( 画素データ ) に基づいて、画像補正処理などの各種の画像処理を行う。

【 0 1 0 0 】

処理部 230 は、電子機器の全体の制御を行ったり、電子機器内の各ブロックの制御を行ったりする。この処理部 230 は、例えば C P U 等により実現される。記憶部 240 は、各種の情報を記憶するものであり、例えば処理部 230 や画像処理部 220 のワーク領域として機能する。操作部 250 は、ユーザが電子機器を操作するためのインターフェースとなるものであり、例えば各種ボタンや G U I ( Graphical User Interface ) 画面などにより実現される。表示部 260 は、例えばセンサー デバイス 210 により取得された画像や G U I 画面などを表示するものであり、液晶ディスプレイや有機 E L ディスプレイなどの各種のディスプレイや投写型表示装置などにより実現される。

30

【 0 1 0 1 】

なお本実施形態は、 F P A ( Focal Plane Array: 焦点面アレイ ) を用いた赤外線カメラや赤外線カメラを用いた電子機器に適用できる。赤外線カメラを適用した電子機器としては、例えば夜間の物体像を撮像するナイトビジョン機器、物体の温度分布を取得するサーモグラフィー機器、人の侵入を検知する侵入検知機器、物体の物理情報の解析 ( 測定 ) を行う解析機器 ( 測定機器 ) 、火や発熱を検知するセキュリティー機器、工場などに設けられる F A ( Factory Automation ) 機器などが想定できる。ナイトビジョン機器を車載機器に適用すれば、車の走行時に夜間の人等の姿を検知して表示することができる。またサーモグラフィー機器に適用すれば、インフルエンザ検疫等に利用することができる。

40

【 0 1 0 2 】

図 12 に本実施形態の焦電型光検出器または焦電型光検出装置を含む電子機器の例として、前述のセンサー デバイス 110 の焦電型光検出器の光吸収材の吸収波長をテラヘルツ域としたセンサー デバイスをテラヘルツ光センサー デバイスとして用い、テラヘルツ光照射ユニットと組み合わせて特定物質探知装置 1000 を構成した例を示す。

【 0 1 0 3 】

特定物質探知装置 1000 は、制御ユニット 1010 と、照射光ユニット 1020 と、光学フィルター 1030 と、撮像ユニット 1040 と、表示部 1050 とを備えて構成さ

50

れている。撮像ユニット 1040 は、図示しないレンズなどの光学系と前述の焦電型光検出器の光吸収材の吸収波長をテラヘルツ域としたセンサーデバイスを含んで構成されている。

【0104】

制御ユニット 1010 は、本装置全体を制御するシステムコントローラーを含み、該システムコントローラーは制御ユニットに含まれる光源駆動部および画像処理ユニットを制御する。照射光ユニット 1020 は、テラヘルツ光（波長が  $100 \mu\text{m} \sim 1000 \mu\text{m}$  の範囲にある電磁波を指す。）出射するレーザー装置と光学系を含み、テラヘルツ光を検査対象の人物 1060 に照射する。なお、照射光ユニット 1020 は、図 6 (A) の光源 160 と同様に光照射を断続できるが、必ずしもチョッパー 172 を使用せずにレーザー発振自体をオン／オフしてもよい。人物 1060 からの反射テラヘルツ光は、探知対象である特定物質 1070 の分光スペクトルのみを通過させる光学フィルター 1030 を介して撮像ユニット 1040 に受光される。撮像ユニット 1040 で生成された画像信号は、制御ユニット 1010 の画像処理ユニットで所定の画像処理が施され、その画像信号が表示部 1050 へ出力される。そして人物 1060 の衣服内等に特定物質 1070 が存在するか否かにより受光信号の強度が異なるので特定物質 1070 の存在が判別できる。

【0105】

図 13 は、周波数がテラヘルツの光を受信して撮像するテラヘルツカメラ 1100 を示している。テラヘルツカメラ 1100 は、筐体 1110 にスリット 1120 とレンズ 1130 を有する。

10

20

【0106】

図 14 に示すように、筐体 1110 内には、テラヘルツ光源 1200 と、光源駆動回路 1210 とが設けられ、スリット 1120 を介して対象物に向けてテラヘルツ光を出射する。

【0107】

対象物からの反射光はレンズ 1130 にて集光され、上述した実施形態に係るセンサーデバイス（焦電型光検出装置）1220 にて検出される。センサーデバイス 1220 からのデジタル信号は、演算処理装置 1230 にて演算処理され、描画処理回路 1240 で描画処理されて、記憶装置 1250 に記憶され、あるいは表示装置 1260 に表示される。

【0108】

30

テラヘルツカメラの用途は様々であり、上述した以外の分野、例えば薬剤検査の分野では、製薬時には決勝投薬多形の混入、薬効成分の偏り、空洞または異物の有無が検査される。調剤時には、薬の種類や分量のチェックや異物混合が検査される。投薬時には、投薬すべき薬剤の種類や成分が正しいかがチェックされる。この他、テラヘルツカメラを各種工場ラインに組み込めば、製品の全数チェックが可能となる。

【0109】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは、当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語（高電位電源ノード、低電位電源ノード等）と共に記載された用語（VCC ノード、GND ノード）は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また検出回路、センサーデバイス、電子機器の構成、動作も本実施形態で説明したものに限定に限定されず、種々の変形実施が可能である。

40

【符号の説明】

【0110】

1A, 1B, 1C 画素回路、2 焦電素子、3, 3A ソースフォロア回路、4, 4A, 4B 第 1 スイッチング素子、5 第 2 スイッチング素子、6 放電スイッチ、7 基準電圧発生回路、10 焦電キャパシター、100 センサーデバイス、120 読み出し回路、122 増幅回路、130 画素駆動回路、160 光源、170 光源部、

50

172 チョッパー、WL 行線、DL 列線、OP アンプ、IN1 第1入力端、IN2 第2入力端、OUT 出力端、C1 第1容量、C2 第2容量、ASW アンプスイッチ、SW0, SW1, SW2 画素選択スイッチ、TP1, TP2 第1, 第2のP型トランジスター、1H 一水平走査期間

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 4】

【図 1 3】

---

フロントページの続き

(56)参考文献 特開昭61-002025(JP,A)

特開2009-010640(JP,A)

特開2010-050636(JP,A)

特開2009-253559(JP,A)

米国特許第04808822(US,A)

特開2005-303325(JP,A)

特開平05-145853(JP,A)

特開2009-068863(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |                   |

|--------|-------------------|

| G 01 J | 1 / 0 0 - 1 / 6 0 |

| G 01 J | 5 / 0 0 - 5 / 6 2 |

| G 01 N | 2 1 / 3 5         |

| G 01 V | 8 / 1 0           |

| H 04 N | 5 / 3 3           |

| G 08 B | 1 3 / 1 9 1       |