(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7000326号

(P7000326)

(45)発行日 令和4年1月19日(2022.1.19)

(24)登録日 令和3年12月27日(2021.12.27)

|                          |                       |

|--------------------------|-----------------------|

| (51)国際特許分類               | F I                   |

| G 0 6 F 21/53 (2013.01)  | G 0 6 F 21/53         |

| G 0 6 F 9/30 (2018.01)   | G 0 6 F 9/30 3 7 0    |

| G 0 6 F 12/0875(2016.01) | G 0 6 F 12/0875 1 0 0 |

| G 0 6 F 21/55 (2013.01)  | G 0 6 F 21/55         |

| G 0 6 F 21/56 (2013.01)  | G 0 6 F 21/56 3 6 0   |

請求項の数 20 (全205頁) 最終頁に続く

|                   |                                  |          |                                                                                                    |

|-------------------|----------------------------------|----------|----------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2018-531549(P2018-531549)      | (73)特許権者 | 591044474<br>ザ・チャールズ・スターク・ドレイパー<br>・ラボラトリー・インコーポレイテッド<br>アメリカ合衆国 0 2 1 3 9 マサチューセッツ州、ケンブリッジ、テクノロジー |

| (86)(22)出願日       | 平成28年12月12日(2016.12.12)          | (74)代理人  | 100108453<br>弁理士 村山 靖彦                                                                             |

| (65)公表番号          | 特表2019-504403(P2019-504403<br>A) | (74)代理人  | 100110364<br>弁理士 実広 信哉                                                                             |

| (43)公表日           | 平成31年2月14日(2019.2.14)            | (74)代理人  | 100133400<br>弁理士 阿部 達彦                                                                             |

| (86)国際出願番号        | PCT/US2016/066188                | (72)発明者  | アンドレ・デホン<br>アメリカ合衆国・ペンシルベニア・1 9<br>1 3 9 ・ フィラデルフィア・サンサム・<br>最終頁に続く                                |

| (87)国際公開番号        | WO2017/106101                    |          |                                                                                                    |

| (87)国際公開日         | 平成29年6月22日(2017.6.22)            |          |                                                                                                    |

| 審査請求日             | 令和1年12月12日(2019.12.12)           |          |                                                                                                    |

| (31)優先権主張番号       | 15/168,689                       |          |                                                                                                    |

| (32)優先日           | 平成28年5月31日(2016.5.31)            |          |                                                                                                    |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                                    |

| (31)優先権主張番号       | 62/268,639                       |          |                                                                                                    |

| (32)優先日           | 平成27年12月17日(2015.12.17)          |          |                                                                                                    |

|                   | 最終頁に続く                           |          |                                                                                                    |

(54)【発明の名称】 メタデータ処理のための技法

## (57)【特許請求の範囲】

## 【請求項 1】

コード実行領域及びメタデータ処理領域を含むコンピュータシステムのプロセッサによって命令を処理する方法であって、

メタデータ処理のために、関連するメタデータタグとともに現在の命令を受信するステップであって、前記メタデータ処理が前記現在の命令を含む前記コード実行領域から隔離された前記メタデータ処理領域において実行される、ステップと、

前記メタデータ処理領域において、かつ前記メタデータタグおよび前記現在の命令に従つて、ルールキャッシュに前記現在の命令のためのルールが存在するかどうかを判定するステップであって、前記ルールキャッシュが前記メタデータ処理により使用されるメタデータについてのルールを含み、前記ルールは前記現在の命令のために許容される動作を定義する、ステップと、

前記ルールキャッシュに前記現在の命令のためのルールが存在しないと判定したことに応答して、前記メタデータ処理領域においてルールキャッシュミス処理を実行するステップであって、

前記現在の命令の実行が許容されるか禁止されるかを判定するステップと、

前記現在の命令が前記コード実行領域において実行されることが許容されると判定したことに応答して、前記現在の命令のための新しいルールを生成するステップと、

生成された前記新しいルールのためのタグ値をレジスタに書き込むステップと、

前記メタデータ処理領域における前記レジスタへの書き込みに応答して、前記新しいルール

を前記ルールキャッシュに挿入するステップと

を備える、ステップとを備え、

前記現在の命令の実行が許容されることを判定するステップが、

前記現在の命令の特権レベルを判定するステップと、

前記メタデータ処理領域の複数のセキュリティモードのなかから実行されるべき現行セキ

ュリティモードを決定するためにタグモード制御ステータスレジスタにアクセスするステ

ップと、

前記現在の命令の前記特権レベルが、決定された前記現行セキュリティモードで実行され

ることが許容されると判定するステップと、

を備える、方法。

10

【請求項 2】

前記現在の命令のための前記ルールを選択するために使用される第1のメタデータが、前記メタデータ処理により使用される複数の制御ステータスレジスタの少なくとも一つの第1の部分に記憶され、前記複数の制御ステータスレジスタの少なくとも一つの前記第1の部分が、前記現在の命令のための複数のメタデータタグを前記メタデータ処理領域に伝えるために使用され、前記複数のメタデータタグが前記メタデータ処理領域においてメタデータとして使用される、請求項1に記載の方法。

【請求項 3】

前記レジスタが、前記メタデータ処理により使用される前記複数の制御ステータスレジスタの第1の制御ステータスレジスタであり、前記複数の制御ステータスレジスタの前記第1の部分が、前記メタデータ処理領域から前記ルールキャッシュに前記複数のメタデータタグを伝えるために使用される、請求項2に記載の方法。

20

【請求項 4】

前記複数のメタデータタグが前記現在の命令のためのものである、請求項3に記載の方法。

【請求項 5】

別のメタデータタグを前記第1の制御ステータスレジスタに書き込んだことに応答して、前記新しいルールが前記ルールキャッシュへと挿入され、前記別のメタデータタグが前記現在の命令の結果に付けられ、前記結果が宛先レジスタまたはメモリ位置のいずれかである、請求項4に記載の方法。

30

【請求項 6】

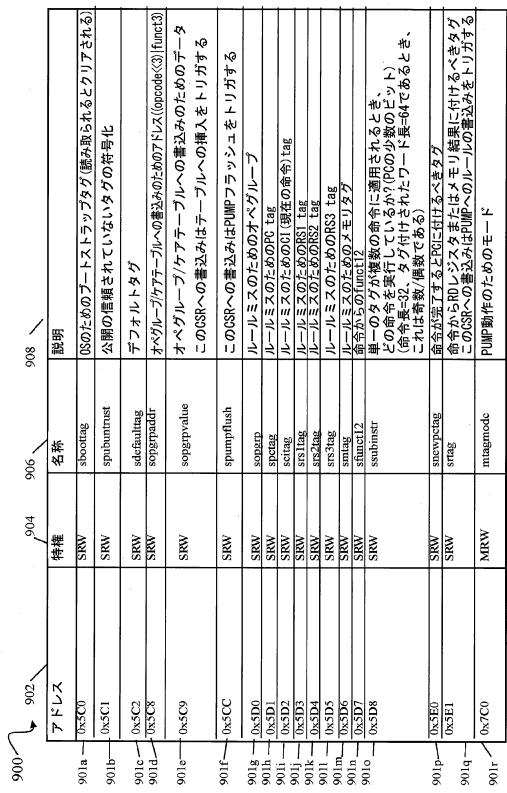

前記複数の制御ステータスレジスタが、すべての他の生成されるメタデータタグがそこから導出される初期メタデータタグを含む、ブートストラップタグ制御ステータスレジスタと、

デフォルトメタデータタグを指定するデフォルトタグ制御ステータスレジスタと、公開であり信頼されないものとして分類される命令およびデータをタグ付けするために使用される公開信頼不可メタデータタグを指定する、公開信頼不可制御ステータスレジスタと、

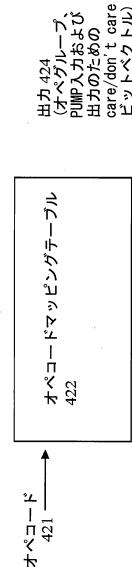

オペグループについての情報と様々なオペコードのためのケア情報とを含むテーブルに書き込まれるデータを含む、オペグループ値制御ステータスレジスタと、

前記オペグループ値制御ステータスレジスタのデータが書き込まれる前記テーブルの中の位置を指定する、オペグループアドレス制御ステータスレジスタと、

pump フラッシュ制御ステータスレジスタであって、前記pump フラッシュ制御ステータスレジスタへの書き込みが前記ルールキャッシュのフラッシュをトリガする、pump フラッシュ制御ステータスレジスタと

のうちの任意の1つまたは複数を含む、請求項2に記載の方法。

【請求項 7】

前記複数の制御ステータスレジスタが、実行されるべき前記現行セキュリティモードを示す前記タグモード制御ステータスレジスタを含む、請求項2に記載の方法。

【請求項 8】

前記タグモード制御ステータスレジスタが、メタデータ処理がいつ不関与であり、それに

40

50

より、1つまたは複数の定義されたポリシーのルールがメタデータ処理によって実施されないかを示す、請求項7に記載の方法。

【請求項 9】

前記タグモード制御ステータスレジスタが、メタデータ処理の前記現在のモードを示すために前記複数のセキュリティモードのうちの1つに設定され、前記複数のセキュリティモードが、メタデータ処理がすべての結果にデフォルトタグを書き込むオフ状態と、命令が1つまたは複数の指定された特権レベルで前記コード実行領域において実行されるときにメタデータ処理が関与しており動作可能であることを示す関与状態とを含む、請求項8に記載の方法。

【請求項 10】

前記ルールキャッシュミス処理が、メタデータ処理が不関与である前記複数のセキュリティモードのうちの第1のモードにおいて実行される、請求項9に記載の方法。

【請求項 11】

前記複数のセキュリティモードが、命令がユーザ特権レベルで前記コード実行領域において実行するときにのみメタデータ処理が関与していることを示す第1の状態と、命令がユーザ特権レベルまたはスーパーバイザー特権レベルで前記コード実行領域において実行するときにのみメタデータ処理が関与していることを示す第2の状態と、命令がユーザ特権レベル、スーパーバイザー特権レベル、またはハイパーバイザー特権レベルで前記コード実行領域において実行するときにのみメタデータ処理が関与していることを示す第3の状態と、命令がユーザ特権レベル、スーパーバイザー特権レベル、ハイパーバイザー特権レベル、またはマシン特権レベルで前記コード実行領域において実行するときにのみメタデータ処理が関与していることを示す第4の状態とを含む、請求項9に記載の方法。

10

【請求項 12】

前記メタデータ処理が関与しているか不関与であるかが、前記現在の命令の前記特権レベルと前記現行セキュリティモードとに従って前記現在の命令の実行が許容されるか禁止されるかどうかに従って判定され、メタデータ処理が不関与であるときに1つまたは複数の定義されるポリシーのルールが実施されず、メタデータ処理が関与しているときに前記ルールが実施される、請求項7に記載の方法。

20

【請求項 13】

テーブルが、命令セットのオペコードを対応するオペグルーブおよびビットベクトル情報にマッピングする情報を含み、前記オペグルーブが、前記メタデータ処理領域によって同様に扱われる関連するオペコードのグループを示し、前記ビットベクトル情報が、前記メタデータ処理領域に関する特定の入力および出力が前記オペコードを処理することに関連して使用されるかどうかを示し、前記テーブルが、許容可能なオペコードビットの最大の数より少ないオペコードビットの第1の部分を使用してインデクシングされ、前記最大の数が前記命令セットのオペコードのビットの数の上限を示す、請求項2に記載の方法。

30

【請求項 14】

前記複数の制御ステータスレジスタの前記第1の部分が、前記現在の命令のための追加のオペコードビットがもしあればそれを含む、拡張オペコード制御ステータスレジスタを含み、前記現在の命令が可変長オペコードを有する前記命令セットに含まれ、前記命令セットの各オペコードが、任意選択で前記追加のオペコードビットを含み、前記拡張オペコード制御ステータスレジスタが、前記現在の命令のための前記追加のオペコードビットがもしあればそれを含む、請求項13に記載の方法。

40

【請求項 15】

前記テーブルを使用してマッピングされる各オペコードに対して、前記各オペコードに対応する結果ビットベクトルがあり、前記結果ビットベクトルが、もしあれば、前記拡張オペコード制御ステータスレジスタの中の前記追加のオペコードビットのどの部分がメタデータ処理のために前記各オペコードとともに使用されるかを示す、請求項14に記載の方法。

【請求項 16】

50

前記現在の命令が、単一のメタデータタグと関連付けられるメモリの単一のワードに記憶される複数の命令のうちの1つであり、前記単一のメタデータタグが、前記単一のワードに含まれる前記複数の命令と関連付けられる、請求項2に記載の方法。

【請求項17】

前記複数の制御ステータスレジスタが、前記単一のワードに記憶されている前記複数の命令のいずれが前記現在の命令であるかを示す、サブ命令制御ステータスレジスタを含む、請求項16に記載の方法。

【請求項18】

前記単一のメタデータタグが、前記単一のワードの中の前記複数の命令の各々に対する異なるメタデータタグを含む第1のメモリ位置への第1のポインタである、請求項17に記載の方法。

10

【請求項19】

前記複数の命令のうちの第1の命令のための前記第1のメモリ位置に記憶されている少なくとも第1のメタデータタグが、前記第1の命令のためのメタデータタグ情報を含む第2のメモリ位置への第2のポインタを含む、請求項18に記載の方法。

【請求項20】

前記第1の命令のための前記メタデータタグ情報が複雑な構造を含み、前記複雑な構造が、少なくとも1つのスカラーデータフィールドと、第3のメモリ位置への少なくとも1つのポインタフィールドとを備える、請求項19に記載の方法。

20

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願は、2015年12月17日に出願された米国仮出願第62/268,639号、SOFTWARE DEFINED METADATA PROCESSING、および2015年12月21日に出願された米国仮出願第62/270,187号、SOFTWARE DEFINED METADATA PROCESSINGの優先権を主張する、2016年5月31日に出願された米国出願第15/168,689号の優先権を主張し、これらのすべての全体が参照によって本明細書に組み込まれる。

【0002】

本出願は全般にデータ処理に関し、より具体的には、メタデータ処理のためのプログラム可能ユニットに関する。

30

【背景技術】

【0003】

今日のコンピュータシステムは、セキュアにするのが難しいことで有名である。従来のプロセッサーアーキテクチャは、たとえば、バッファオーバーフローおよびポインタ偽造などの、高水準の抽象化に違反する様々な挙動を許容する。プログラミング言語とハードウェアとのギャップを埋めることはソフトウェア任せであることがあり、完璧な抽象化を実施することのコストはしばしば高すぎると見なされる。

【0004】

実行の間にメタデータを伝播し、安全性の侵害および悪意のある攻撃をそれらが発生するにつれて捉えるポリシーを実施することの価値を、一部の最近の試みが示している。これらのポリシーは、ソフトウェアにおいて実施され得るが、性能および/またはコストなどにおいて望ましくない大きなオーバーヘッドを通常は招き、このことは、ポリシーの展開を妨げ、または他には、より保護の程度が低い粗悪な類似物を用いる動機を与える。不变のポリシーに対するハードウェアのサポートは、オーバーヘッドを許容可能なレベルに減らし、悪意のあるコードまたはマルウェア攻撃により実行され得るような望ましくないコードの侵入の大部分を防ぐことができる。たとえば、Intelは最近、境界チェックおよび隔離のためのハードウェアを発表した。これらは今日の攻撃の多くを軽減するが、完全にシステムをセキュアにするには、メモリの安全性および隔離以上のものが必要である。攻撃は、あらゆる形態の残存する脆弱性を利用するように高速に進化する。

40

50

【先行技術文献】

【非特許文献】

【0005】

【文献】K. Mai、R. Ho、E. Alon、D. Liu、Y. Kim、D. Patil、およびM. Horowitz、

Architecture and Circuit Techniques for a 1.1GHz 16-kb Reconfigurable Mem-

ory in 0.18um-CMOS、IEEE J. Solid-State Circuits、40(1):261-275、2005年1月

PROGRAMMING THE PUMP, Hardware-Assisted Micro-Policies for Security

The RISC-V Instruction Set Manual Vol. I, User-Level ISA, Version 2.0、2014

年5月6日、Waterman, Andrew他

The RISC-V Instruction Set Manual Volume II: Privileged Architecture, Version

1.7、2015年5月9日

10

【発明の概要】

【発明が解決しようとする課題】

【0006】

したがって、この変化し続ける状況に迅速に適応できる、フレキシブルなセキュリティア-

ーキテクチャが必要である。そのようなアーキテクチャに、最小限のオーバーヘッドで、

ソフトウェアにより定義されるメタデータの処理をサポートさせることが望ましい。その

ようなアーキテクチャは、メタデータに割り振られるビット数に対する目に見える厳しい

制限を課すことなく、あらゆる数およびタイプのポリシーを全般にサポートし実施するよ

うに拡張可能であることが望ましい。ポリシーを実施し、たとえば悪意のあるコードまたは

マルウェア攻撃などの、そのようなポリシーの侵害を捉えるために、実行の間にメタデ

ータが伝播され得る。

20

【課題を解決するための手段】

【0007】

本明細書において説明される技法の一態様に従うのは、メタデータ処理のために、関連す

るメタデータタグとともに現在の命令を受信するステップであって、前記メタデータ処理

が現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行され

る、ステップと、メタデータ処理領域において、かつメタデータタグおよび現在の命令に

従って、現在の命令のためのルールキャッシュにルールが存在するかどうかを判定するス

テップであって、前記ルールキャッシュが、許容される動作を定義するために前記メタデ

ータ処理によって使用されるメタデータについてのルールを含む、ステップと、現在の命令

のためのルールキャッシュにルールが存在しないと判定したことに応答して、メタデ

ータ処理領域においてルールキャッシュミス処理を実行するステップであって、現在の命令

の実行が許容されるかどうかを判定するステップを備える、ステップと、現在の命令がコ

ード実行領域において実行されると判定したことに応答して、現在の命令のための新しいル

ールを生成するステップと、レジスタに書き込むステップと、レジ

スタへの書き込みに応答して、新しいルールをルールキャッシュに挿入するステップとを備

える、命令を処理する方法である。現在の命令のためのルールを選択するために使用される

第1のメタデータは、メタデータ処理により使用される複数の制御ステータスレジスタの

第1の部分に記憶されてよく、複数の制御ステータスレジスタの第1の部分は、現在の命令

のための複数のメタデータタグをメタデータ処理領域に伝えるために使用されてよく、前

記複数のメタデータタグは、メタデータ処理領域においてデータとして使用されてよい。

レジスタは、メタデータ処理によって使用される複数の制御ステータスレジスタの第1の

制御ステータスレジスタであってよく、複数の制御ステータスレジスタの第1の部分は、

メタデータ処理領域からルールキャッシュに複数のメタデータタグを伝えるために使用さ

れてよい。複数のメタデータタグは、現在の命令のためのものであり得る。別のメタデ

ータタグを第1の制御ステータスレジスタに書き込んだことに応答して、新しいルールがル

ールキャッシュに挿入されてよく、別のメタデータタグが現在の命令の結果に対して付け

られてよく、この結果は宛先レジスタまたはメモリ位置のいずれかであってよい。複数の

制御ステータスレジスタは、すべての他の生成されるメタデータタグがそこから導出され

30

40

50

る初期メタデータタグを含む、ポートストラップタグ制御ステータスレジスタ、デフォルトのメタデータタグを指定するデフォルトタグ制御ステータスレジスタ、公開であり信頼されないものとして分類される命令およびデータをタグ付けするために使用される公開信頼不可メタデータタグを指定する、公開信頼不可制御ステータスレジスタ、オペグループについての情報および様々なオペコードのためのケア情報を含むテーブルに書き込まれるデータを含む、オペグループ値制御ステータスレジスタ、オペグループ値制御ステータスレジスタのデータが書き込まれるテーブルの中の位置を指定するオペグループアドレス制御ステータスレジスタ、ならびに、pumpフラッシュ制御ステータスレジスタのうちの、任意の1つまたは複数を含むことがあり、pumpフラッシュ制御ステータスレジスタへの書き込みはルールキャッシュのフラッシュをトリガする。複数の制御ステータスレジスタが、メタデータ処理の現在のモードを示すタグモード制御ステータスレジスタを含み得る。タグモード制御ステータスレジスタは、メタデータ処理がいつ不関与であり、それにより、1つまたは複数の定義されたポリシーのルールがメタデータ処理によって実施されないかを、示し得る。タグモード制御ステータスレジスタは、メタデータ処理の現在のモードを示すために、許容される状態の定義された集合のうちの1つに設定され得る。許容される状態は、メタデータ処理がすべての結果にデフォルトタグを書き込む状態であるオフ状態、および命令が1つまたは複数の指定された特権レベルでコード領域において実行されるときにメタデータ処理が関与しており動作可能であることを示す状態のうちの、いずれかを含み得る。ルールキャッシュミス処理は、メタデータ処理が不関与である許容される状態の定義された集合のうちの第1の状態において実行され得る。許容される状態は、命令がユーザ特権レベルでコード領域において実行するときにのみメタデータ処理が関与していることを示す第1の状態と、命令がユーザ特権レベルまたはスーパーバイザー特権レベルでコード領域において実行するときにのみメタデータ処理が関与していることを示す第2の状態と、命令がユーザ特権レベル、スーパーバイザー特権レベル、またはハイパーバイザー特権レベルでコード領域において実行するときにのみメタデータ処理が関与していることを示す第3の状態と、命令がユーザ特権レベル、スーパーバイザー特権レベル、ハイパーバイザー特権レベル、またはマシン特権レベルでコード領域において実行するときにのみメタデータ処理が関与していることを示す第4の状態とを含み得る。メタデータ処理が関与しているか不関与であるかは、タグモード制御ステータスレジスタの現在のタグモードと、コード領域において実行するコードの現在の特権レベルとの組合せに従って判定されることがある、メタデータ処理が不関与であるときに1つまたは複数の定義されたポリシーのルールは実施されないことがあり、メタデータ処理が関与しているときにルールは実施されることがある。テーブルは、命令セットのオペコードを対応するオペグループおよびビットベクトル情報にマッピングする情報を含み得る。オペグループは、メタデータ処理領域によって同様に扱われる関連するオペコードのグループを示し得る。ビットベクトル情報は、メタデータ処理領域に関する特定の入力および出力がオペコードを処理することに関連して使用されるかどうかを示し得る。テーブルは、許容可能なオペコードビットの最大の数より少ないオペコードビットの第1の部分を使用してインデクシングされることがあり、この最大の数は命令セットのオペコードのビット数に対する上限を示すことがある。複数の制御ステータスレジスタの第1の部分は、現在の命令のための追加のオペコードビットがもしあればそれを含む、拡張オペコード制御ステータスレジスタを含むことがある、現在の命令は可変長オペコードを有する命令セットに含まれることがあり、命令セットの各オペコードは追加のオペコードビットを任意選択で含むことがあり、拡張オペコード制御ステータスレジスタは現在の命令のための追加のオペコードビットがもしあればそれを含む。テーブルを使用してマッピングされる各オペコードに対して、前記各オペコードに対応する結果ビットベクトルがあり、結果ビットベクトルは、もしあれば、拡張オペコード制御ステータスレジスタの中の追加のオペコードビットのどの部分がメタデータ処理のために前記各オペコードとともに使用されるかを示し得る。現在の命令は、単一のメタデータタグと関連付けられるメモリの単一のワードに記憶される複数の命令のうちの1つであることがあり、前記単一のメタデータタグは、単一のワードに含まれる

10

20

30

40

50

複数の命令と関連付けられることがある。複数の制御ステータスレジスタは、单一のワードに記憶されている複数の命令のいずれが現在の命令であるかを示す、サブ命令制御ステータスレジスタを含み得る。单一のメタデータタグは、单一のワードの中の複数の命令の各々に対する異なるメタデータタグを含む第1のメモリ位置への第1のポインタであり得る。少なくとも、複数の命令のうちの第1の命令のための第1のメモリ位置に記憶される第1のメタデータタグは、第1の命令のためのメタデータタグ情報を含む第2のメモリ位置への第2のポインタを含み得る。第1の命令のためのメタデータタグ情報は複雑な構造を含み得る。複雑な構造は、少なくとも1つのスカラーデータフィールドと、第3のメモリ位置への少なくとも1つのポインタフィールドとを含み得る。

#### 【0008】

本明細書の技法の別の態様に従うのは、実行されると、命令を処理する方法を実行するコードを備える非一時的コンピュータ可読媒体であり、この方法は、メタデータ処理のために、関連するメタデータタグとともに現在の命令を受信するステップであって、前記メタデータ処理が現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行される、ステップと、メタデータ処理領域において、かつメタデータタグおよび現在の命令に従って、現在の命令のためのルールキャッシュにルールが存在するかどうかを判定するステップであって、前記ルールキャッシュが許容される動作を定義するために前記メタデータ処理によって使用されるメタデータについてのルールを含む、ステップと、現在の命令のためのルールキャッシュにルールが存在しないと判定したことに応答して、メタデータ処理領域においてルールキャッシュミス処理を実行するステップであって、現在の命令の実行が許容されるかどうかを判定するステップを備える、ステップと、現在の命令がコード実行領域において実行されると判定したことに応答して、現在の命令のための新しいルールを生成するステップと、レジスタに書き込むステップと、レジスタへの書き込みに応答して、新しいルールをルールキャッシュに挿入するステップとを備える。

#### 【0009】

本明細書の技法の別の態様に従うのは、プロセッサと、プロセッサによって実行されると命令を処理する方法を実行するコードを記憶したメモリとを備えるシステムであり、この方法は、メタデータ処理のために、関連するメタデータタグとともに現在の命令を受信するステップであって、前記メタデータ処理が現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行される、ステップと、メタデータ処理領域において、かつメタデータタグおよび現在の命令に従って、現在の命令のためのルールキャッシュにルールが存在するかどうかを判定するステップであって、前記ルールキャッシュが許容される動作を定義するために前記メタデータ処理によって使用されるメタデータについてのルールを含む、ステップと、現在の命令のためのルールキャッシュにルールが存在しないと判定したことに応答して、メタデータ処理領域においてルールキャッシュミス処理を実行するステップであって、現在の命令の実行が許容されるかどうかを判定するステップを備える、ステップと、現在の命令がコード実行領域において実行されると判定したことに応答して、現在の命令のための新しいルールを生成するステップと、レジスタに書き込むステップと、レジスタへの書き込みに応答して、新しいルールをルールキャッシュに挿入するステップとを備える。プロセッサは、縮小命令セットコンピューティングアーキテクチャにおけるパイプラインプロセッサであり得る。

#### 【0010】

本明細書の技法の別の態様に従うのは、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行されるメタデータ処理のための現在の命令を受信するステップと、現在の命令のためのメタデータに関連するメタデータ処理領域によって、1つまたは複数のポリシーの集合に従った現在の命令の実行を許容するかどうかを判定するステップとを備える、命令を処理する方法であって、現在の命令は第1のルーチンのスタックフレームの第1の位置にアクセスし、現在の命令およびスタックフレームの位置は関連するメタデータタグを有し、1つまたは複数のポリシーの集合は、スタック保護を提供し

10

20

30

40

50

第1のルーチンのスタックフレームの記憶位置を含むスタック記憶位置への不適切なアクセスを防ぐ、スタック保護ポリシーを含む。スタック保護ポリシーは、第1のルーチンのスタックフレームの第1の位置にアクセスする現在の命令のメタデータ処理において使用される第1のルールを含み得る。第1のルールは、第1の位置が第1のルーチンのスタック位置であることを示すメタデータを第1の位置が有し、現在の命令が第1のルーチンに含まれる場合、現在の命令の実行を許容し得る。現在の命令は、第1のルーチンの特定の呼出しインスタンスによって使用されることがあり、スタック保護ポリシーは現在の命令のメタデータ処理において使用される第1のルールを含むことがある。第1のルールは、現在の命令が第1のルーチンに含まれ第1のルーチンの特定の呼出しインスタンスによっても使用される場合、現在の命令の実行を許容し得る。第1のルールは、第1のルーチンの特定の呼出しインスタンスによる現在の命令の実行を許容するかどうかを判定するために、プログラムカウンタと関連付けられるとともに権限および能力のいずれかを示すメタデータを、調査することを含み得る。スタック保護ポリシーは、オブジェクトレベルの保護のいずれかを提供することができ、単一のスタックフレームの中の異なるオブジェクトは異なる色メタデータタグを有し、階層的なオブジェクトのための階層的なオブジェクト保護は複数のサブオブジェクトを含み、ここで単一のスタックフレームの複数のサブオブジェクトの各々は異なるメタデータタグを有する。方法は、新しいルーチン呼出しのために新しいスタックフレームを作成するステップと、厳密なオブジェクト初期化または遅延オブジェクト色付けに従って新しいスタックフレームのメモリ位置をタグ付けまたは色付けするステップとを含むことがあり、厳密なオブジェクト初期化は、新しいスタックフレームに情報を記憶する前に新しいスタックフレームの各メモリ位置を最初にタグ付けする1つまたは複数のルールのメタデータ処理をトリガする1つまたは複数の命令を実行する初期化処理を実行することを含み、遅延オブジェクト色付けは、特定のメモリ位置にデータを記憶する命令に応答してトリガされるルールのメタデータ処理に関連して新しいスタックフレームのその特定のメモリ位置をタグ付けする。1つまたは複数のポリシーは、特定のリターン位置へのリターンが特定の呼出しの後に行われるときにのみ有効であることを保証する、動的制御フロー整合性ポリシーの実施のためのルールの集合を含み得る。第1の位置は、リターン命令を含む呼び出されたルーチンに制御を移転する呼出し命令を含むことがあり、第2の位置は第2の命令を含むことがあり、ここで前記第2の位置は、呼び出されたルーチンのリターン命令を実行した結果として制御が移転されるリターンターゲット位置を示し得る。方法は、呼出し命令を含む第1の位置を第1のコードタグでタグ付けするステップと、リターンターゲット位置を示す第2の位置を第2のコードタグでタグ付けするステップと、第1のコードタグでタグ付けされる呼出し命令のために集合の第1のルールのメタデータ処理を実行するステップであって、第1のコードタグでタグ付けされた呼出し命令のための第1のルールのメタデータ処理が、リターンアドレスレジスタが第2の位置のための有効なリターンアドレスを含むことを示す有効リターンアドレスタグでリターンアドレスレジスタをタグ付けするステップを含み、呼出し命令の実行が、第2の位置に戻る能力を示すようにリターンアドレスレジスタのタグを更新する、ステップと、リターンアドレスレジスタが有効なリターンアドレス能力タグでタグ付けされる場合に、リターンアドレスレジスタに記憶されているリターンアドレスへ制御を移転するためにリターン命令の実行を許容する、呼び出されたルーチンのリターン命令のための集合の第2のルールのメタデータ処理を実行するステップであって、第2のルールが、リターン命令のランタイム実行に続く次の命令のために使用されるプログラムカウンタタグにリターンアドレスレジスタの有効なリターンアドレス能力タグを伝播する、ステップと、リターン命令のランタイム実行に続く第2の命令のための集合の第3のルールのメタデータ処理を実行するステップであって、第2の命令が第2のコードタグに等しいコードタグを有し、かつプログラムカウンタタグが有効なリターンアドレス能力タグである場合に、第3のルールのメタデータ処理が第2の命令の実行を許容し、第3のルールが、第2の命令のランタイム実行に続く次の命令のために使用されるプログラムカウンタタグをクリアする、ステップとを含み得る。

本明細書の技法の別の態様に従うのは、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行されるメタデータ処理のために現在の命令を受信するステップと、現在の命令のためのメタデータに関連するメタデータ処理領域によって、1つまたは複数のポリシーの集合に従って現在の命令の実行を許容するかどうかを判定するステップとを備える、命令を処理する方法であって、1つまたは複数のポリシーは、命令の完全なシーケンスの実行を、完全なシーケンスの最初の命令から完全なシーケンスの最後の命令まで指定された順序で実施するルールの集合を含む。方法は、第1の共有される物理ページを第1のプロセスの第1の仮想アドレス空間へとマッピングするステップと、第1の共有される物理ページを第2のプロセスのための第2の仮想アドレス空間へとマッピングするステップとを含むことがあり、前記第1の共有される物理ページが複数のメモリ位置を含み、複数のメモリ位置の各々がメタデータ処理領域におけるルール処理に関連して使用される複数のグローバルメタデータタグのうちの1つと関連付けられる。複数のグローバルメタデータタグは、少なくとも第1のプロセスおよび第2のプロセスを含む複数のプロセスによって共有されるメタデータタグの集合を示すことがあり、第1のプロセスと第2のプロセスの両方のために同じポリシーがメタデータ処理領域によって実施されることがある。メタデータ処理領域による同じポリシーの実施は、そうされなければ第2のプロセスのために同じポリシーによって許容されない動作を第1のプロセスが実行することを許容するためにメタデータを使用することがあり、プログラムカウンタは関連するプログラムカウンタタグを有することがあり、関連するプログラムカウンタタグの異なる値が、そうされなければ第2のプロセスのために同じポリシーによって許容されない動作を第1のプロセスが実行することを許容するために、同じポリシーのルールによって使用されることがある。方法は、アプリケーションの割振りルーチンによって第1の処理を実行して、アプリケーションの現在の色を使用してアプリケーションの次の色を生成するステップを含むことがあり、アプリケーションの現在の色はアプリケーションのためのアプリケーション固有の色シーケンスの現在の状態を示し、次の色はアプリケーションのためのアプリケーション固有の色シーケンスの次の状態を示し、現在の色は第1のアトムの第1のメタデータタグに記憶される。第1の処理は、第1の1つまたは複数の命令を実行することを含むことがあり、第1の1つまたは複数の命令は、メタデータ処理領域による1つまたは複数のルールを使用したメタデータ処理をトリガし、メタデータ処理領域による1つまたは複数のルールを使用したメタデータ処理は、現在の色を使用して次の色を生成し、第1のアトムの第1のメタデータタグに次の色を記憶することによってアプリケーションのためのアプリケーション固有の色シーケンスの現在の状態を更新する。第1の1つまたは複数の命令はアプリケーションの割振りルーチンに含まれてよく、第1のアトムはレジスタおよびメモリ位置のいずれかであってよい。アプリケーション固有の色シーケンスは、アプリケーションによる使用が可能な異なる色の無限のシーケンスであってよく、次の色はアプリケーションにより使用される1つまたは複数のメモリ位置の各々のためのタグ値として記憶されてよく、1つまたは複数のメモリ位置は割振りルーチンによって割り振られてよい。ルールの集合は第1のルールおよび第2のルールを含むことがあり、命令の完全なシーケンスは第1の命令および第2の命令を含むことがあり、第2の命令は第1の命令の直後に実行されることがある。方法は、第1の命令のための第1のルールのメタデータ処理を実行するステップであって、第1のルールのメタデータ処理が、第1の命令のランタイム実行に続く次の命令のために使用されるプログラムカウンタのプログラムカウンタタグを特別なタグ値に設定することを含む、ステップと、第2の命令のための第2のルールのメタデータ処理を実行するステップであって、第2のルールのメタデータ処理が、第2の命令のためのプログラムカウンタのプログラムカウンタタグが特別なタグに等しいときにのみ第2の命令の実行が許容されることを保証することを含む、ステップとを含み得る。

#### 【 0 0 1 2 】

本発明の別の態様に従うのは、実行されると、命令を処理する方法を実行するコードを記憶した非一時的コンピュータ可読媒体であり、この方法は、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行されるメタデータ処理のための現在

10

20

30

40

50

の命令を受信するステップと、現在の命令のためのメタデータに関連するメタデータ処理領域によって、1つまたは複数のポリシーの集合に従った現在の命令の実行を許容するかどうかを判定するステップとを備え、現在の命令は第1のルーチンのスタックフレームの第1の位置にアクセスし、現在の命令およびスタックフレームの位置は関連するメタデータタグを有し、1つまたは複数のポリシーの集合は、スタック保護を提供し第1のルーチンのスタックフレームの記憶位置を含むスタック記憶位置への不適切なアクセスを防ぐ、スタック保護ポリシーを含む。

#### 【 0 0 1 3 】

本明細書の技法の別の態様に従うのは、プロセッサと、プロセッサによって実行されると命令を処理する方法を実行するコードを記憶したメモリとを備える、システムであり、この方法は、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行されるメタデータ処理のための現在の命令を受信するステップと、現在の命令のためのメタデータに関連するメタデータ処理領域によって、1つまたは複数のポリシーの集合に従った現在の命令の実行を許容するかどうかを判定するステップとを備え、現在の命令は第1のルーチンのスタックフレームの第1の位置にアクセスし、現在の命令およびスタックフレームの位置は関連するメタデータタグを有し、1つまたは複数のポリシーの集合は、スタック保護を提供し第1のルーチンのスタックフレームの記憶位置を含むスタック記憶位置への不適切なアクセスを防ぐ、スタック保護ポリシーを含む。

10

#### 【 0 0 1 4 】

本明細書の技法の別の態様に従うのは、実行されると、命令を処理する方法を実行するコードを記憶した非一時的コンピュータ可読媒体であり、この方法は、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行されるメタデータ処理のために現在の命令を受信するステップと、現在の命令のためのメタデータに関連するメタデータ処理領域によって、1つまたは複数のポリシーの集合に従った現在の命令の実行を許容するかどうかを判定するステップとを備え、1つまたは複数のポリシーは、命令の完全なシーケンスの実行を、完全なシーケンスの最初の命令から完全なシーケンスの最後の命令まで指定された順序で実施するルールの集合を含む。

20

#### 【 0 0 1 5 】

本明細書の技法の別の態様に従うのは、プロセッサと、プロセッサによって実行されると命令を処理する方法を実行するコードを記憶したメモリとを備える、システムであり、この方法は、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において実行されるメタデータ処理のために現在の命令を受信するステップと、現在の命令のためのメタデータに関連するメタデータ処理領域によって、1つまたは複数のポリシーの集合に従った現在の命令の実行を許容するかどうかを判定するステップとを備え、1つまたは複数のポリシーは、命令の完全なシーケンスの実行を、完全なシーケンスの最初の命令から完全なシーケンスの最後の命令まで指定された順序で実施するルールの集合を含む。

30

#### 【 0 0 1 6 】

本明細書の技法の別の態様に従うのは、コード実行領域から隔離されたメタデータ処理領域において使用される複数の指定されたレジスタのうちの第1の指定されたレジスタにブートストラップタグを記憶するステップと、ブートストラップタグから1つまたは複数の追加のメタデータタグを導出するため第1の処理を実行するステップとを備える、メタデータタグを生成して使用する方法であって、前記第1の処理は、メタデータ処理領域における1つまたは複数のルールのメタデータ処理をトリガする1つまたは複数の命令をコード実行領域において実行するステップを含む。ブートストラップタグは、メタデータ処理領域により使用されるすべての他のメタデータタグがそこから導出される、初期シードタグとして使用され得る。ブートストラップタグは、ハードウェアリングされ、または読み取り専用メモリの一部分に記憶され得る。この記憶および第1の処理は、メタデータ処理領域およびコード実行領域を含むシステムをブートするときにブートストラッププログラムの第1のコード部分を実行することにより実行される処理に含まれ得る。方法は、第1の指定されたレジスタに記憶されているブートストラップタグからデフォルトタグを導出する

40

50

ステップと、複数の指定されたレジスタのうちの第2の指定されたレジスタにデフォルトタグを記憶するステップと、コード実行領域により使用される複数のメモリ位置の各々のためのメタデータタグとして第2の指定されたレジスタからデフォルトタグを書き込むメタデータ処理領域におけるルールのメタデータ処理をトリガする、命令シーケンスを実行するステップとを含み得る。第1の処理は、ブートストラップタグから導出されたメタデータタグの初期集合を生成するステップを含むことがあり、初期集合のメタデータタグの各々は、メタデータ処理領域におけるルールキャッシュミス処理をトリガするコード実行領域における現在の命令を実行することによって生成されることがあり、これにより、現在の命令のためのルールキャッシュにルールが存在せず、ルールキャッシュは許容される動作を定義するためにメタデータ処理領域によって使用されるメタデータについてのルールを含む。ルールキャッシュミス処理は、メタデータ処理領域において実行するルールキャッシュミスハンドラによって、現在の命令のための新しいルールを計算するステップを含むことがあり、新しいルールはメタデータタグの初期集合の結果メタデータタグを含む。初期集合の各メタデータタグは、他のメタデータタグを導出するためにさらに使用され得るタグ生成源であり得る。1つまたは複数の指定された命令のうちの第1の集合の実行は、1つまたは複数の他のメタデータタグのシーケンスを生成するために使用されるタグ生成源として示される各メタデータタグを生成する、メタデータ処理領域におけるルールおよびルールキャッシュミス処理をトリガすることがあり、1つまたは複数の指定された命令の第2の集合の実行は、追加のメタデータタグをさらに生成するために使用できない非生成タグとして示される各メタデータタグを生成する、メタデータ処理領域におけるルールおよびルールキャッシュミス処理をトリガし得る。ブートストラッププログラムはさらに、拡張された特権、能力、または権限をタグ付けされた1つまたは複数の命令に与えるために、指定されたコード部分の1つまたは複数の命令に1つまたは複数の特別なメタデータコードタグを書き込む、メタデータ処理領域において処理されるルールをトリガする命令を含み得る。指定されたコード部分は、カーネルコードおよびローダコードのうちの1つまたは複数を含み得る。1つまたは複数の特別なメタデータコードタグは、メタデータタグの初期集合の第1のメタデータタグから導出され、第1のメタデータタグは特別な命令タグ生成源である。メタデータタグの初期集合は、命令をタグ付けするために使用される1つまたは複数のコードタグのシーケンスを生成するために使用されるタグ生成源である初期命令メタデータタグと、1つまたは複数の他のmallocタグ生成源のシーケンスを生成するために使用されるタグ生成源である初期mallocメタデータタグであって、1つまたは複数の他のmallocタグ生成源の各々が、割り振られたメモリセルおよび異なるアプリケーションにより使用される割り振られたメモリセルへのポインタのいずれかを色付けすることに関連して異なるアプリケーションのための1つまたは複数の他のメタデータタグのシーケンスを生成するために使用される、初期mallocメタデータタグと、1つまたは複数の他の制御フロー整合性タグ生成源のシーケンスを生成するために使用されるタグ生成源である初期制御フロー整合性タグであって、1つまたは複数の他の制御フロー整合性タグ生成源の各々が、異なるアプリケーションの制御移転ターゲットをタグ付けすることに関連して異なるアプリケーションのための1つまたは複数の他のメタデータタグのシーケンスを生成するために使用される、初期制御フロー整合性タグと、1つまたは複数の他のティントタグ生成源のシーケンスを生成するために使用されるタグ生成源である初期ティントタグであって、1つまたは複数の他のティントタグ生成源の各々が、データアイテムを產生または修正したコードに基づいて、異なるアプリケーションにより使用されるデータアイテムをメタデータティントタグでタグ付けすることに関連して異なるアプリケーションのための1つまたは複数の他のメタデータティントタグのシーケンスを生成するために使用される、初期ティントタグのうちの任意の1つまたは複数を含み得る。メタデータタグのシーケンスは、メタデータ処理領域におけるルールの他の処理をトリガする命令を実行することによって生成され得る。他の処理は、シーケンスの中の現在のメタデータタグを使用してシーケンスの中の次のメタデータタグを生成するステップであって、現在のメタデータタグが、シーケンスの現在の状態を示し、アトムと関連付けられるメタデータタグ

10

20

30

40

50

として記憶され、アトムがレジスタまたはメモリ位置のいずれかである、ステップと、アトムと関連付けられるメタデータタグとして次のメタデータタグを保存することによってシーケンスの現在の状態を更新するステップとを含み得る。

【0017】

本明細書の技法の別の態様に従うのは、プロセッサによる実行のためにアプリケーションをロードするローダを実行するステップであって、ローダを実行する前記ステップが、メタデータ処理領域における1つまたは複数のルールの第1の集合のメタデータ処理をトリガする1つまたは複数の命令を含む第1のコード部分を実行するステップを含み、1つまたは複数のルールの第1の集合の前記メタデータ処理が、メタデータ処理領域にアクセス可能でありコード実行領域にアクセス可能ではないアプリケーションメタデータとしてアプリケーションのための制御フロー情報を収集して記憶するステップを含む、ステップと、コード実行領域においてアプリケーションの命令を実行するステップであって、アプリケーションの前記命令を実行する前記ステップが、アプリケーションにおける制御の第1のソース位置から第1のターゲット位置への移転を許容するかどうかを判定するために制御フロー情報の少なくとも一部分を使用する、制御フローポリシーのルールの第2の集合のメタデータ処理をトリガする、ステップとを備える、アプリケーションのための制御フロー情報を取得する方法である。第1のターゲット位置は、制御を第1のターゲット位置に移転することが許容される1つまたは複数の許容可能なソース位置の集合を有し得る。アプリケーションメタデータとしてアプリケーションのための制御フロー情報を収集して記憶するステップはさらに、メタデータ処理領域が他の処理を実行するステップを備え得る。他の処理は、1つまたは複数の許容可能なソース位置の集合を特定する第1のメタデータで第1のターゲット位置をタグ付けするステップを含むことがあり、第1のメタデータはアプリケーションメタデータの制御フロー情報の一部分として記憶される。アプリケーションの第1の命令は、制御を第1のソース位置から第1のターゲット位置に移転することができ、第1の命令は、制御を第1のターゲット位置に移転することができる1つまたは複数の許容可能なソース位置の集合に第1のソース位置が含まれるかどうかを判定することによって第1の命令の実行を許容するかどうかを判定するために第1のメタデータを使用する、制御フローポリシーの1つまたは複数のルールのメタデータ処理をトリガすることができる。他の処理も、固有のソースメタデータタグで集合の各々の許容可能なソース位置をタグ付けするステップを含み得る。各々の許容可能なソース位置の各々の固有のソースメタデータタグは、アプリケーションのためのソースメタデータタグの第1のシーケンスに含まれることがあり、第1のシーケンスは、制御フロー生成源タグから生成されるソースメタデータタグの固有のシーケンスであり得る。制御フロー生成源タグは、初期ブートストラップタグから導出された初期制御フロー生成源タグから生成され得る。初期制御フロー生成源タグは、複数の追加の制御フロー生成源タグを生成するために使用されがあり、追加の制御フロー生成源タグの各々は、異なるアプリケーションのための固有のソースメタデータタグのシーケンスを生成するために使用されることがある。

【0018】

本明細書の技法の別の態様に従うのは、実行されると、メタデータタグを生成して使用する方法を実行するコードを記憶した非一時的コンピュータ可読媒体であって、この方法は、コード実行領域から隔離されたメタデータ処理領域において使用される複数の指定されたレジスタのうちの第1の指定されたレジスタにブートストラップタグを記憶するステップと、ブートストラップタグから1つまたは複数の追加のメタデータタグを導出するために第1の処理を実行するステップとを備え、前記第1の処理は、メタデータ処理領域における1つまたは複数のルールのメタデータ処理をトリガする1つまたは複数の命令をコード実行領域において実行するステップを含む。

【0019】

本明細書の技法の別の態様に従うのは、プロセッサと、実行されるとメタデータタグを生成して使用する方法を実行するコードを記憶したメモリとを備える、システムであって、この方法は、コード実行領域から隔離されたメタデータ処理領域において使用される複数

10

20

30

40

50

の指定されたレジスタのうちの第1の指定されたレジスタにブートストラップタグを記憶するステップと、ブートストラップタグから1つまたは複数の追加のメタデータタグを導出するために第1の処理を実行するステップとを備え、前記第1の処理は、メタデータ処理領域における1つまたは複数のルールのメタデータ処理をトリガする1つまたは複数の命令をコード実行領域において実行するステップを含む。

#### 【0020】

本明細書の技法の別の態様に従うのは、実行されると、アプリケーションのための制御フロー情報を取得する方法を実行するコードを記憶した非一時的コンピュータ可読媒体であり、この方法は、プロセッサによる実行のためにアプリケーションをロードするローダを実行するステップであって、ローダを実行する前記ステップが、メタデータ処理領域における1つまたは複数のルールの第1の集合のメタデータ処理をトリガする1つまたは複数の命令を含む第1のコード部分を実行するステップを含み、1つまたは複数のルールの第1の集合の前記メタデータ処理が、メタデータ処理領域にアクセス可能でありコード実行領域にアクセス可能ではないアプリケーションメタデータとしてアプリケーションのための制御フロー情報を収集して記憶するステップを含む、ステップと、コード実行領域においてアプリケーションの命令を実行するステップであって、アプリケーションの前記命令を実行する前記ステップが、アプリケーションにおける制御の第1のソース位置から第1のターゲット位置への移転を許容するかどうかを判定するために制御フロー情報の少なくとも一部分を使用する、制御フローポリシーのルールの第2の集合のメタデータ処理をトリガする、ステップとを備える。

10

#### 【0021】

本明細書の技法の別の態様に従うのは、プロセッサと、実行されるとアプリケーションのための制御フロー情報を取得する方法を実行するコードを記憶したメモリとを備える、システムであり、この方法は、プロセッサによる実行のためにアプリケーションをロードするローダを実行するステップであって、ローダを実行する前記ステップが、メタデータ処理領域における1つまたは複数のルールの第1の集合のメタデータ処理をトリガする1つまたは複数の命令を含む第1のコード部分を実行するステップを含み、1つまたは複数のルールの第1の集合の前記メタデータ処理が、メタデータ処理領域にアクセス可能でありコード実行領域にアクセス可能ではないアプリケーションメタデータとしてアプリケーションのための制御フロー情報を収集して記憶するステップを含む、ステップと、コード実行領域においてアプリケーションの命令を実行するステップであって、アプリケーションの前記命令を実行する前記ステップが、アプリケーションにおける制御の第1のソース位置から第1のターゲット位置への移転を許容するかどうかを判定するために制御フロー情報の少なくとも一部分を使用する、制御フローポリシーのルールの第2の集合のメタデータ処理をトリガする、ステップとを備える。

20

30

#### 【0022】

本明細書の技法の別の態様に従うのは、プロセッサ上で、タグ付けされていないデータソースから第1のデータをロードする第1の命令を実行するステップであって、前記タグ付けされていないデータソースが関連するメタデータタグを有しないメモリ位置を含む、ステップと、第1のハードウェアによって、第1のデータが信頼されず公開のデータソースからのものであることを示す第1のメタデータタグで第1のデータをタグ付けするステップであって、第1のメタデータタグを有する第1のデータが第1のバッファに記憶される、ステップと、プロセッサ上で、第1の1つまたは複数のルールを使用するメタデータ処理をトリガする第1のコードを実行するステップであって、第1の1つまたは複数のルールを使用するメタデータ処理が、第1のデータが信頼されることを示す第2のメタデータタグを有するように第1のデータを再タグ付けする再タグ付けを実行する、ステップとを備える、タグ付けされたデータソースとタグ付けされていないデータソースとの間でプロセッサにより仲介されるデータ転送を実行するための方法である。第2のメタデータタグは追加で、第1のデータが公開のソースからのものであることを示し得る。第2のメタデータタグを有する第1のデータは、関連するメタデータタグを各々有するメモリ位置を含むタグ付けされた

40

50

データソースであるメモリに記憶され得る。メモリは、1つまたは複数の信頼されるデータソースからのデータを含む信頼されるメモリであり得る。メタデータ処理は、第1のコードを含むコード実行領域から隔離されたメタデータ処理領域において実行され得る。第1の1つまたは複数のルールは、許容された動作を定義するためにメタデータ処理によって使用されるメタデータについてのルールであり得る。第1のコードは1つまたは複数の命令を含むことがあり、1つまたは複数の命令の各々は、第2のメタデータタグを有するように第1のデータを再タグ付けする1つまたは複数のルールを呼び出す権限を前記各々の命令が有することを示す、特別な命令タグを有し得る。第1のメタデータタグを有する第1のデータは暗号化されることがあり、方法は、プロセッサ上で1つまたは複数の命令を実行することによって、第1のメタデータタグを有する第1のデータを復号し、第1のメタデータタグを有する第1のデータの復号された形式を生成するステップと、プロセッサ上で1つまたは複数の追加の命令を実行することによって検証処理を実行するステップとを含むことがあり、前記検証処理は第1のデータの復号された形式が有効であることを確実にするためにデジタル署名を使用し、前記再タグ付けは第1のデータの検証処理の成功の後で実行される。第2のメタデータタグを有する第1のデータは、タグ付けされたメモリの第1のメモリ位置に復号された形式で記憶されがあり、方法は、暗号化された形式の第1のデータを產生するために第1のデータを暗号化し、第1のデータに従ってデジタル署名を生成するステップであって、暗号化する前記ステップおよび生成する前記ステップがプロセッサ上で追加のコードを実行することによって実行される、ステップと、プロセッサ上で、タグ付けされたメモリの第1のメモリ位置からの第1のデータの暗号化された形式をタグ付けされていないメモリの宛先位置に記憶する第2の命令を実行するステップであって、第1のデータの暗号化された形式が関連するメタデータタグなしで宛先位置に記憶され、第2のメタデータタグが宛先位置に第1のデータの暗号化された形式を記憶する前に第2のハードウェアによって除去される、ステップとを含み得る。第1の時点において、第1のデータが、タグ付けされていないメモリ部分の第1の位置に記憶されがあり、第2の時点において、第1のメタデータタグを有し、第1のデータが信頼されず公開のデータソースからのものであることを示す第1のデータが、タグ付けされたメモリ部分の第2の位置に記憶されることがある。タグ付けされていないメモリ部分および前記タグ付けされたメモリ部分は、同じメモリコントローラによってサービスされる同じメモリに含まれることがあり、第2のメタデータ処理ルールは、データが公開されることを示す関連するメタデータタグを有するデータをタグ付けされていないメモリ部分に書き込む動作を実行することのみをプロセッサに許容することがあり、タグ付けされていないデータに対して動作する外部のタグ付けされていないソースからの直接のメモリ動作は、同じメモリのタグ付けされていないメモリ部分にアクセスすることのみを許容されることがある。第2のメタデータ処理ルールの少なくとも一部分はさらに、データが公開であり、加えて信頼されないことを示す関連するメタデータタグを有するデータをタグ付けされていないメモリ部分に書き込む動作を実行することのみをプロセッサに許容することがある。タグ付けされていないデータソースは、タグ付けされていないデータソースのみを含む第1のインターフェクトファブリックに接続されることがある、第2のメタデータタグを伴う第1のデータは、タグ付けされたデータソースのみを含む第2のインターフェクトファブリックに接続されるメモリの位置に記憶され得る。第2のプロセッサは、第1のインターフェクトファブリックに接続されることがあり、タグ付けされていないデータソースからのタグ付けされていないデータを使用して他の命令を実行することがある。他の命令は、メタデータ処理を実行することなく、かつ許容可能な動作を実施するためにメタデータについてのルールを使用することなく、実行されることがある、前記第2のプロセッサによる前記他の命令の実行は、第1のインターフェクトファブリックのタグ付けされていないデータソースからデータを読み取ること、および第1のインターフェクトファブリックのタグ付けされていないデータソースにデータを書き込むことのうちのいずれかを含む1つまたは複数の動作を実行することを含み得る。

本明細書の技法の別の態様に従うのは、プロセッサと、1つまたは複数のタグ付けされたメモリであって、1つまたは複数のタグ付けされたメモリの各メモリ位置が関連するメタデータタグを有する、メモリと、第1のタグ付けされていないメモリを含む1つまたは複数のタグ付けされていないメモリであって、1つまたは複数のタグ付けされていないメモリのメモリ位置が関連するメタデータタグを有しない、メモリと、命令に関連して許容される動作を定義するためにメタデータ処理を実行する際に使用されるメタデータについてのルールを含むルールキャッシュであって、プロセッサによって現在の命令を実行する前に、現在の命令の実行が許容されるかどうかを判定するためにルールキャッシュの1つまたは複数のルールを使用したメタデータ処理が実行される、ルールキャッシュと、プロセッサによって実行されると、第1のタグ付けされていないメモリからプロセッサにより使用されるデータキャッシュへと第1のデータをロードする第1の命令であって、データキャッシュに記憶されている第1のデータが関連する第1のメタデータタグを有する、第1の命令と、プロセッサによって実行されると、データキャッシュからの第2のデータを第1のタグ付けされていないメモリに記憶する第2の命令であって、データキャッシュに記憶されている第2のデータが関連する第2のメタデータタグを有する、第2の命令と、プロセッサによってシステムにおいて使用されるタグ付けされたデータにタグ付けされていないデータを変換する第1のハードウェア構成要素であって、第1の命令の実行に応答して、第1のハードウェア構成要素が、第1のタグ付けされていないメモリから、どのような関連するメタデータタグも伴わずに第1のデータを受信し、関連する第1のメタデータタグを有する第1のデータを出力する、第1のハードウェア構成要素と、タグ付けされたデータをタグ付けされていないデータに変換する第2のハードウェア構成要素であって、第2の命令の実行に応答して、第2のハードウェア構成要素が、関連する第2のメタデータタグを有する第2のデータを受信し、どのような関連するメタデータタグも伴わずに第2のデータを出力する、第2のハードウェア構成要素とを備える、システムである。どのような関連するメタデータタグも伴わない第1のデータは暗号化されることがあり、第1のハードウェア構成要素は、第1のデータを復号された形式に変換することができ、デジタル署名を使用して第1のデータの検証処理を実行することができ、検証処理が成功すると、第1のデータが信頼されることを示す関連する第1のメタデータタグを有するように第1のデータをタグ付けすることができる。第2の関連するメタデータタグを有する第2のデータは、復号された形式であることがあり、第2のハードウェア構成要素は、第2のデータを暗号化された形式に変換することができ、第2のデータに従ってデジタル署名を生成する。第1のハードウェア構成要素は、第1のデータが信頼されることを示すとともに、第1のデータが公開のソースからのものであることを特定する、関連する第1のメタデータタグを有するように第1のデータをタグ付けすることができる。1つまたは複数の暗号鍵集合は、ハードウェアにおいて符号化されるか、メモリに記憶されるかのいずれかであり得る。1つまたは複数の暗号鍵集合は、復号および検証処理を実行することに関連して第1のハードウェア構成要素によって使用されることがあり、暗号化を実行することおよびデジタル署名を作成することに関連して第2のハードウェア構成要素によって使用されることがある。第1のデータは、第1のデータを復号するために第1のハードウェア構成要素によって使用される暗号鍵集合のうちの特定の1つを特定することができ、第2のデータの関連する第2のメタデータタグは、第2のデータを暗号化してそれに署名するために第2のハードウェア構成要素によって使用される暗号鍵集合のうちの特定の1つを特定することができる。

#### 【 0 0 2 4 】

本明細書の技法の別の態様に従うのは、メタデータ処理のために現在の命令を受信するステップと、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において現在の命令のためのメタデータ処理を実行するステップであって、前記現在の命令がメタデータ処理において使用される第1のメタデータタグを有する第1のメモリ位置を参照し、現在の命令のための前記メタデータ処理が、メモリから第1のメタデータタグを取り出すための処理を実行するステップを含む、ステップと、メモリから第1のメモリ位置のための第1のメタデータタグを受信する前に、第1のメモリ位置の第1のメタデータタグの予測

10

20

30

40

50

される値を判定するステップと、第1のメモリ位置の第1のメタデータタグの予測される値を使用して、現在の命令の結果オペランドのための第1の結果メタデータタグを判定するステップと、メモリから第1のメタデータタグを受信するステップと、第1のメタデータタグが第1のメタデータタグの予測される値と一致するかどうかを判定するステップと、第1のメタデータタグが第1のメタデータタグの予測される値と一致すると判定したことに応答して、結果オペランドのための最終的な結果メタデータタグとして第1の結果メタデータタグを使用するステップとを備える、現在の命令を処理する方法である。現在の命令のためのメタデータ処理は、現在の命令および現在の命令のための入力メタデータタグの集合に従って、現在の命令のための第1のルールを判定するステップであって、前記第1のルールが、第1のメモリ位置の第1のメタデータタグの予測される値を含み、第1の結果メタデータタグを含み、前記第1のルールがメタデータ処理領域におけるメタデータ処理のために使用されるルールキャッシュに含まれる、ステップと、第1のメタデータタグが第1のメタデータタグの予測される値と一致しないと判定したことに応答して、現在の命令のためのメタデータ処理領域においてルールキャッシュミス処理を実行するステップとを含み得る。現在の命令のためのメタデータ処理領域におけるルールキャッシュミス処理は、コード実行領域における現在の命令の実行が許容されるかどうかを判定するステップと、コード実行領域における現在の命令の実行が許容されると判定したことに応答して、現在の命令のための新しいルールを生成するステップであって、前記新しいルールが現在の命令、入力メタデータタグの集合、および第1のメタデータタグに従って生成される、ステップと、メタデータ処理領域におけるメタデータ処理のために使用されるルールキャッシュへと新しいルールを挿入するステップとを含み得る。他の入力メタデータタグの集合は、現在の命令のための複数の他のメタデータタグを含むことがあり、他のメタデータ入力タグの前記集合は、プログラムカウンタ、現在の命令、および現在の命令の入力オペランドのうちのいずれかのためのメタデータタグを含むことがある。結果オペランドは、現在の命令を実行したことの結果を記憶する宛先メモリ位置または宛先レジスタであり得る。命令は、第1の段階および第2の段階を含む複数の段階に従って処理されることがあり、第1の段階は第2の段階の前に発生することがある。第1のメモリ位置の第1のメタデータタグの予測される値は第1の段階において判定されることがあり、第2の段階は、第1のメタデータタグが第1のメタデータタグの予測される値と一致するかどうかを判定する前記ステップを実行することを含むことがあり、第2の段階はまた、第1のメタデータタグが第1のメタデータタグの予測される値と一致しないと判定したことに応答して、現在の命令のためのメタデータ処理領域における前記ルールキャッシュミス処理を実行することを含むことがある。ルールキャッシュは、予測セレクタモードに従って、予測モードまたは通常処理モードのいずれかで動作するように構成可能であり得る。ルールキャッシュは、現在の命令のための前記メタデータ処理を実行するとき、予測モードで動作するように構成され得る。ルールキャッシュが前記予測モードで動作するように構成されるとき、ルールキャッシュは第1のルールに従って第1の出力を生成し得る。第1の出力は、次の命令のプログラムカウンタのためのメタデータタグ、現在の命令の結果オペランドのための第1の結果メタデータタグ、および第1のメタデータタグの予測される値を、第1の段階の出力として含むことがある。ルールキャッシュが前記通常処理モード動作するように構成されるとき、ルールキャッシュは、第1のルールとは異なる第2のルールに従って第2の出力を生成することができ、第2の出力は第1のメタデータタグの予測される値を含まないことがある。ルールキャッシュは、予測モードにおいて動作するときに第1のポリシーのルールの第1のバージョンを使用することができ、そうではなく通常の処理モードで動作するときに第1のポリシーのルールの第2のバージョンを使用することができ、第1のルールはルールの第1のバージョンに含まれることがあり、第2のルールはルールの第2のバージョンに含まれることがある。

【 0 0 2 5 】

本明細書の技法の別の態様に従うのは、複数のパイプライン段階を含むパイプラインプロ

10

20

30

40

50

セッサであって、前記複数の段階がメモリ段階およびライトバック段階を含む、パイプラインプロセッサと、メモリ段階の完了の前に動作する統合されたメタデータ処理のためのプログラム可能ユニット(PUMP:programmable unit for metadata processing)であって、PUMPがメタデータ処理において使用される第1のメタデータタグを有する第1のメモリ位置を参照する現在の命令のためのメタデータ処理を実行し、PUMPが現在の命令のための第1のメタデータタグを含む第1の入力を受信し、PUMPがライトバック段階への入力として与えられる第1の出力を生成し、第1の出力が第1のメモリ位置の第1のメタデータタグの予測される値および現在の命令の結果オペランドのための第1の結果メタデータタグを含み、第1の結果メタデータタグが第1のメモリ位置のための第1のメタデータタグの予測される値に従ってPUMPによって判定される、PUMPと、第1のメモリ位置のための第1のメタデータタグが第1のメタデータタグの予測される値と一致するかどうかを判定し、第1のメタデータタグが第1のメタデータタグの予測される値と一致するときに結果オペランドのための最終的な結果メタデータタグとして第1の結果メタデータタグを使用する、前記ライドバック段階のハードウェア構成要素とを備える、システムである。PUMPは、メモリ段階と同時に動作し、さらに予測モードで動作する第1のPUMPであることがあり、第1のメモリ位置の第1のメタデータタグの予測される値を判定することができ、システムは、通常の非予測モードで動作する第2のPUMPを含むことがあり、第1のメモリ位置の第1のメタデータタグのためのいずれの予測される値も判定しないことがある。第2のPUMPは、メモリ段階とライトバック段階との間の別の段階として統合されることがある。第1のPUMPは、予測モードで動作するときに使用するための第1のポリシーのルールの第1のバージョンを使用することができ、第2のPUMPは、通常の非予測モードで動作するときに使用するための第1のポリシーのルールの第2のバージョンを使用することができる。第1のPUMPは、第1のバージョンからの第1のルールに従って第1の出力を判定することができ、第2のPUMPは、第2のバージョンからの第2のルールに従って第2の出力を判定することができる。第2の出力は、第1のメモリ位置のための第2の結果メタデータタグを含むことができ、前記第2の出力は、ライトバック段階への入力として与えられることがある。ライトバック段階のハードウェア構成要素は追加で、第1のメタデータが予測される値と一致しないとき、結果オペランドのための最終的な結果メタデータタグとして第2の結果メタデータタグを使用することができる。

#### 【0026】

本明細書の技法の別の態様に従うのは、実行されると、タグ付けされたデータソースとタグ付けされていないデータソースとの間でプロセッサにより仲介されるデータ転送の方法を実行するコードを記憶した、非一時的コンピュータ可読媒体であり、この方法は、プロセッサ上で、タグ付けされていないデータソースから第1のデータをロードする第1の命令を実行するステップであって、前記タグ付けされていないデータソースが、関連するメタデータタグを有しないメモリ位置を含む、ステップと、第1のハードウェアによって、第1のデータが信頼されず公開されているデータソースからのものであることを示す第1のメタデータタグで第1のデータをタグ付けするステップであって、第1のメタデータタグを有する第1のデータが第1のバッファに記憶される、ステップと、プロセッサ上で、第1の1つまたは複数のルールを使用したメタデータ処理をトリガする第1のコードを実行するステップであって、第1の1つまたは複数のルールを使用したメタデータ処理が、第1のデータが信頼されることを示す第2のメタデータタグを有するように第1のデータを再タグ付けする再タグ付けを実行する、ステップとを備える。

#### 【0027】

本明細書の別の態様に従うのは、実行されると、現在の命令を処理する方法を実行するコードを記憶した、非一時的コンピュータ可読媒体であり、この方法は、メタデータ処理のために現在の命令を受信するステップと、現在の命令を含むコード実行領域から隔離されたメタデータ処理領域において現在の命令のためのメタデータ処理を実行するステップであって、前記現在の命令がメタデータ処理において使用される第1のメタデータタグを有する第1のメモリ位置を参照し、現在の命令のための前記メタデータ処理が、メモリから

10

20

30

40

50

第1のメタデータタグを取り出すための処理を実行するステップを含む、ステップと、メモリから第1のメモリ位置のための第1のメタデータタグを受信する前に、第1のメモリ位置の第1のメタデータタグの予測される値を判定するステップと、第1のメモリ位置の第1のメタデータタグの予測される値を使用して、現在の命令の結果オペランドのための第1の結果メタデータタグを判定するステップと、メモリから第1のメタデータタグを受信するステップと、第1のメタデータタグが第1のメタデータタグの予測される値と一致するかどうかを判定するステップと、第1のメタデータタグが第1のメタデータタグの予測される値と一致すると判定したことに応答して、結果オペランドのための最終的な結果メタデータタグとして第1の結果メタデータタグを使用するステップとを備える。

【0028】

10

本明細書の技法の特徴および利点は、添付の図面とともに引用される技法の例示的な実施形態の以下の詳細な説明からより明らかになるであろう。

【図面の簡単な説明】

【0029】

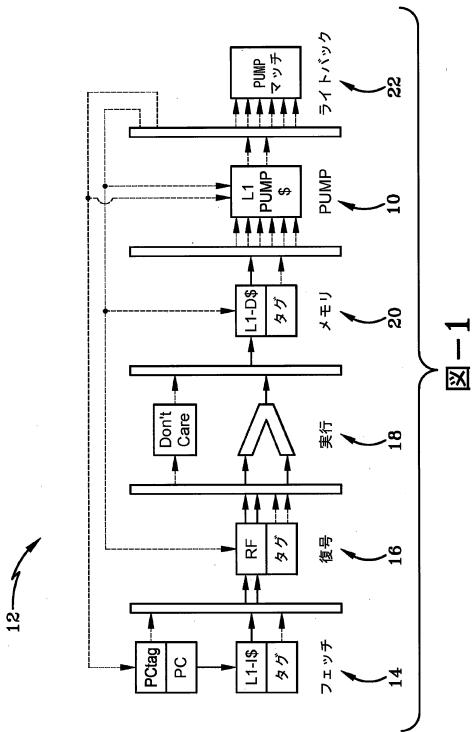

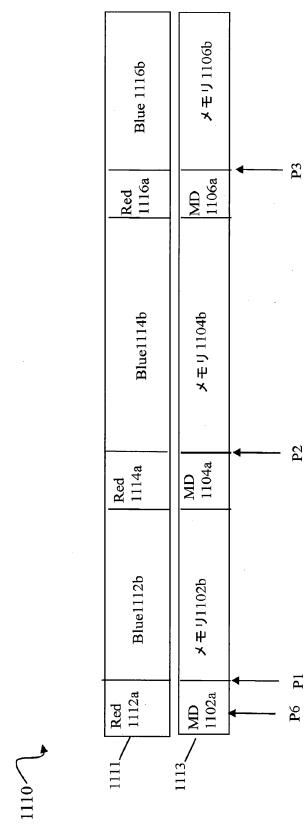

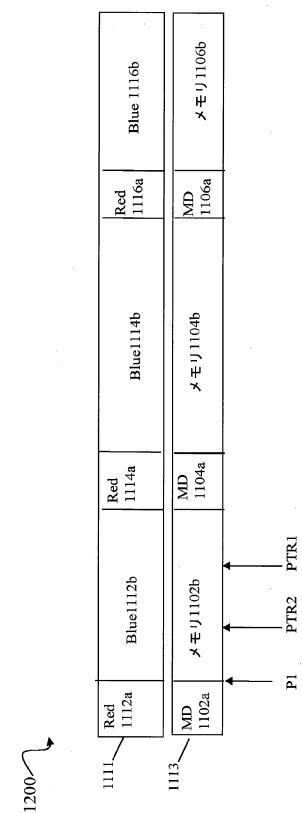

【図1】プロセッサパイプラインの中のパイプライン段階として統合されるPUMPキャッシュの例を示す概略図である。

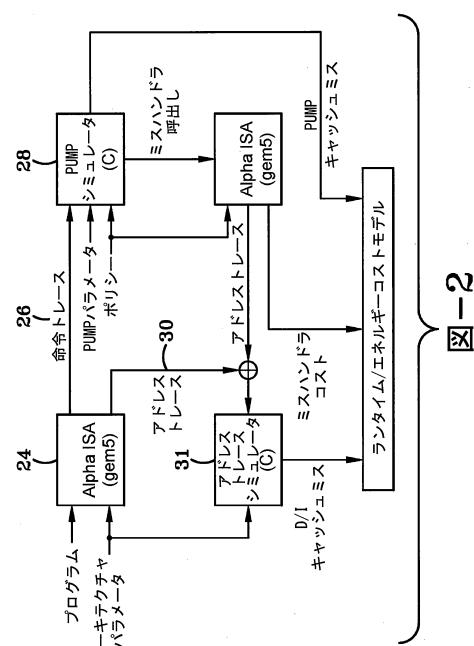

【図2】PUMP評価フレームワークを示す概略図である。

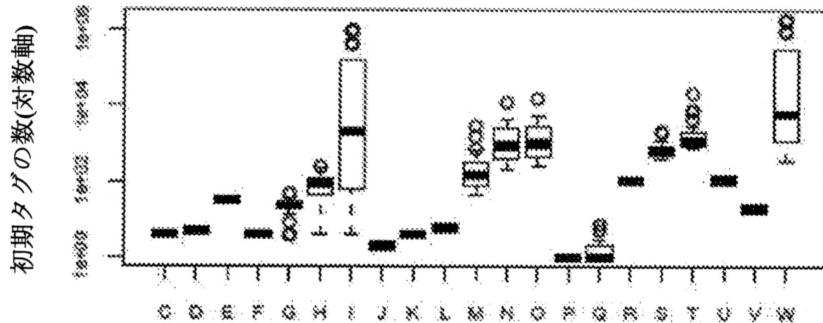

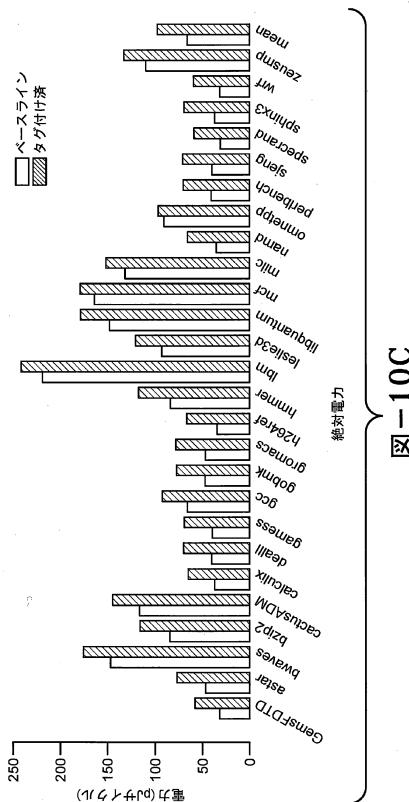

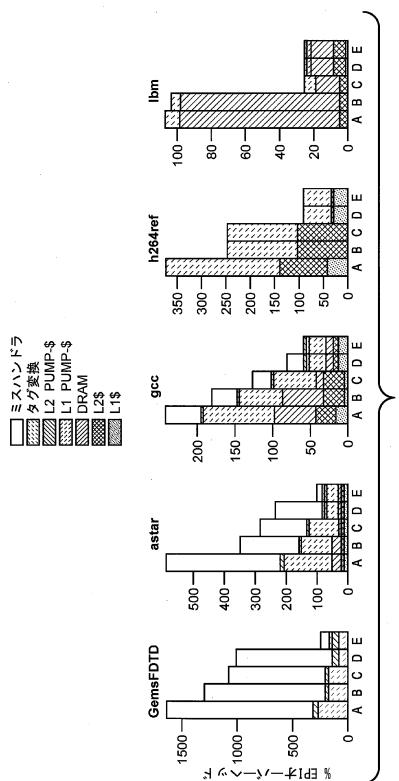

【図3 A】図2に示される評価フレームワークを使用した簡単な実装形態を用いて単一ランタイムポリシーの実行結果を示すグラフである。

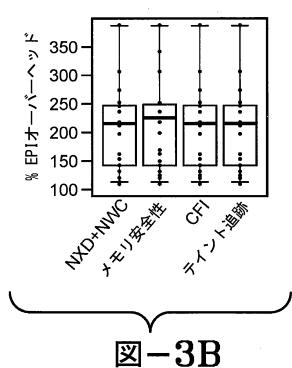

【図3 B】簡単な実装形態を用いて単一エネルギーポリシーの実行結果を示すグラフである。

20

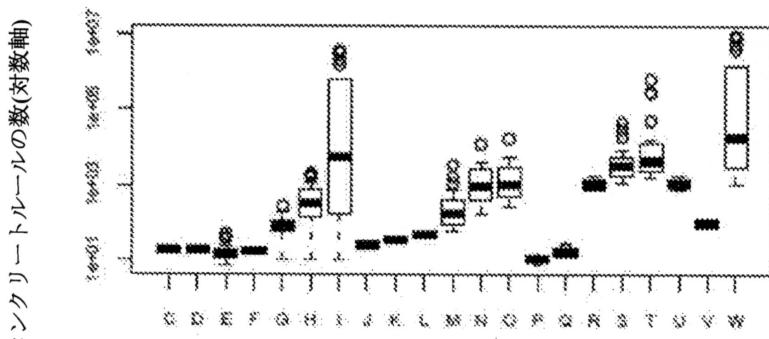

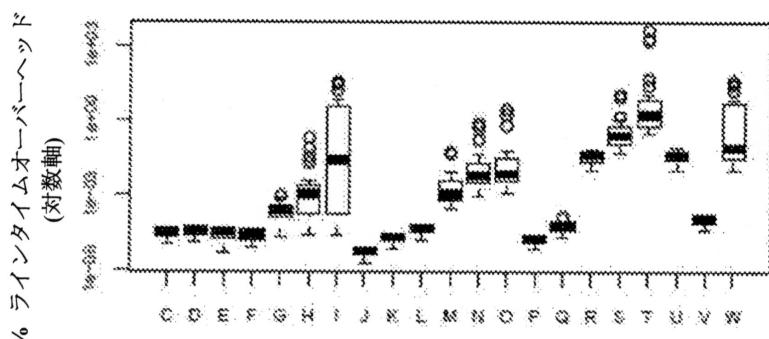

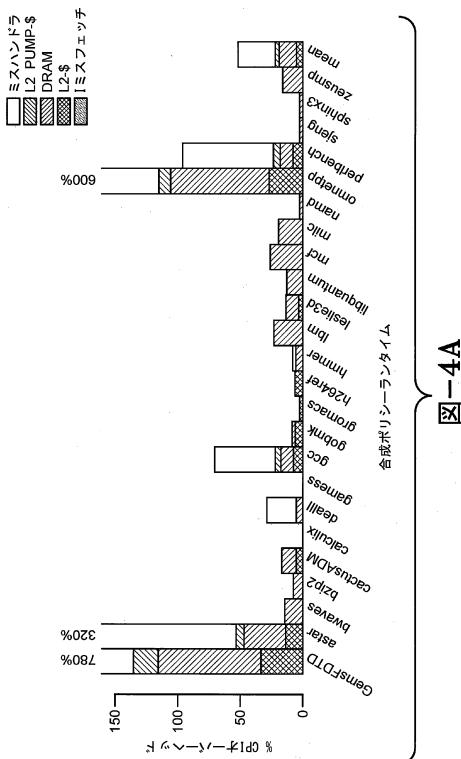

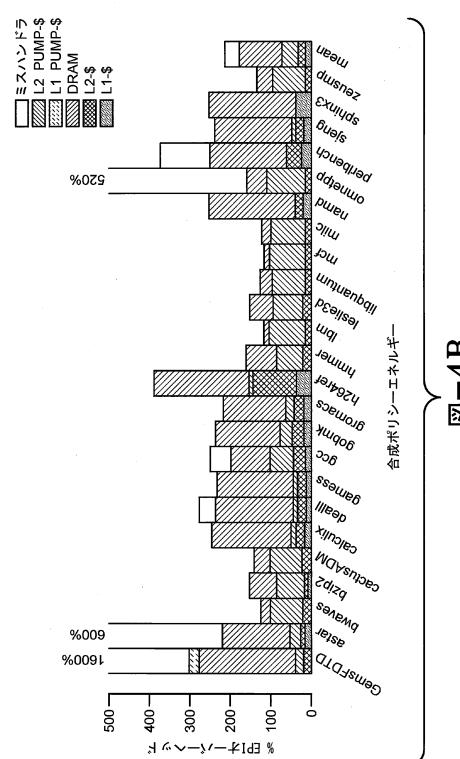

【図4 A】64bのタグを伴う簡単な実装形態の合成ポリシーのランタイムオーバーヘッドを示す一連の棒グラフであり、合成ポリシーは、(i)空間的および時間的なメモリ安全性、(ii)テイント追跡、(iii)制御フロー整合性、および(iv)コードとデータの分離というポリシーを同時に実施する。

【図4 B】64bのタグを伴う簡単な実装形態の合成ポリシーのエネルギーオーバーヘッドを示す一連の棒グラフである。

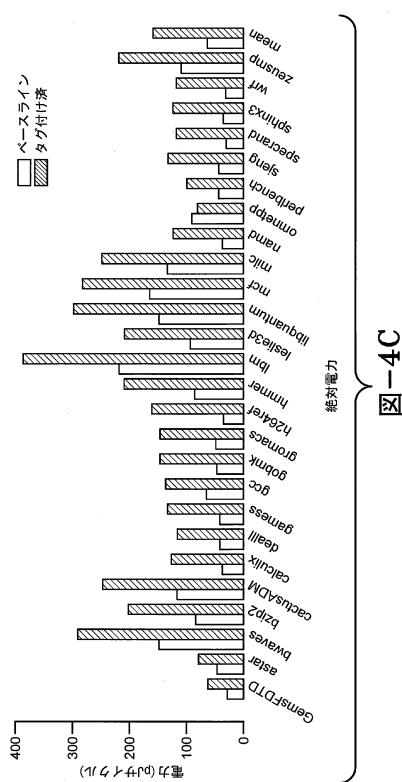

【図4 C】簡単な実装形態の電力の上限をベースラインと比較して示す一連の棒グラフである。

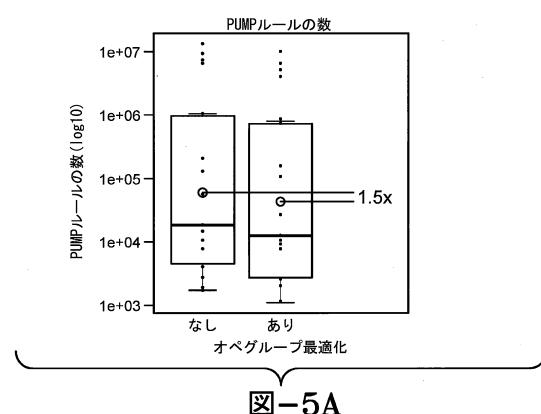

【図5 A】オペグループ最適化ありの場合となしの場合のPUMPルールの数を比較する棒グラフである。

30

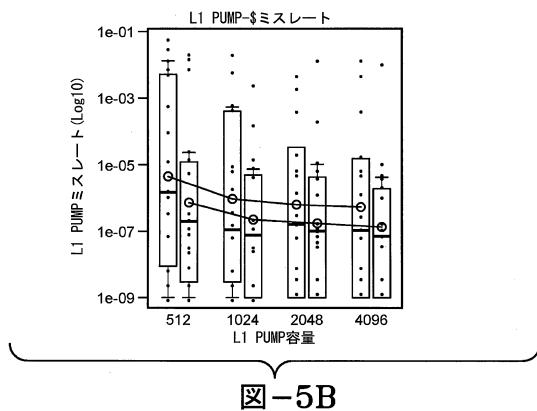

【図5 B】PUMP容量に基づいて異なるオペグループ最適化のミスレートの影響を示す一連のグラフである。

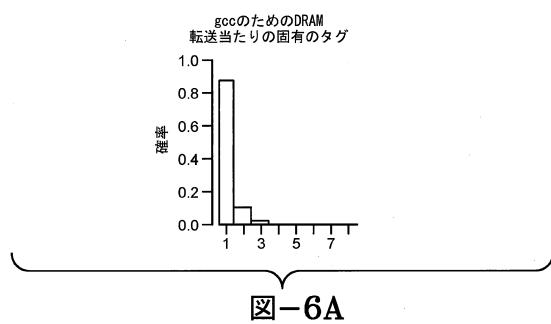

【図6 A】大半のワードが同じタグを有することを示す、合成ポリシーを用いたgccベンチマークについての各DRAM転送のための固有のタグの分布のグラフである。

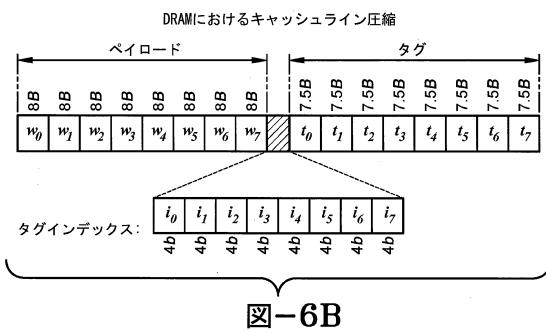

【図6 B】メインメモリのタグ圧縮を示す図である。

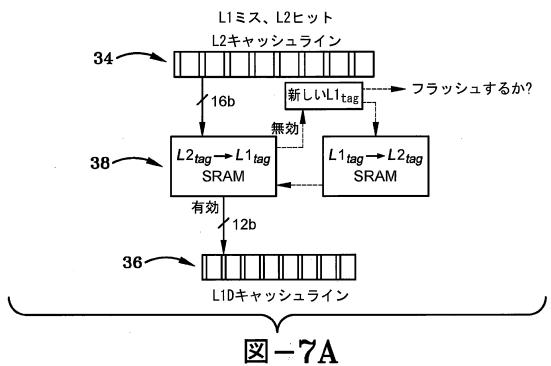

【図7 A】16b L2タグと12b L1タグとの間の変換を示す概略図である。

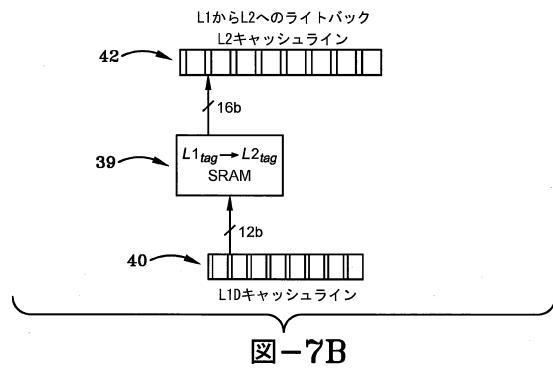

【図7 B】12b L1タグと16b L2タグとの間の変換を示す概略図である。

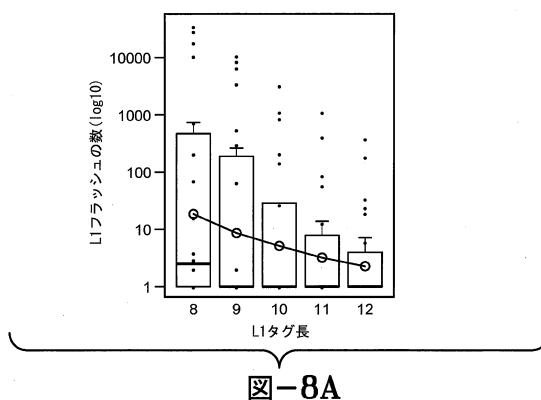

【図8 A】L1 PUMPフラッシュに対するL1タグ長の影響(log10)を示す概略グラフである。

40

【図8 B】L1 PUMPミスレートに対するL1タグ長の影響を示す概略グラフである。

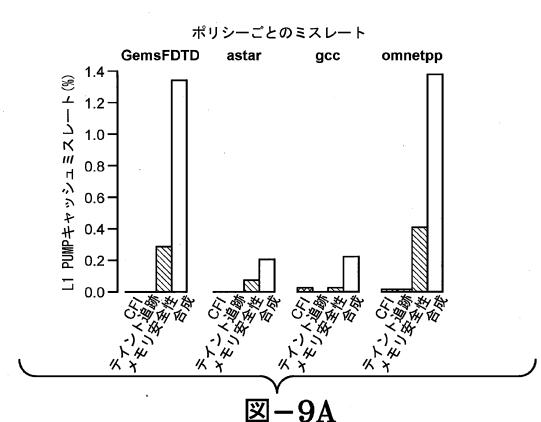

【図9 A】異なるポリシーのミスレートを示す一連の棒グラフである。

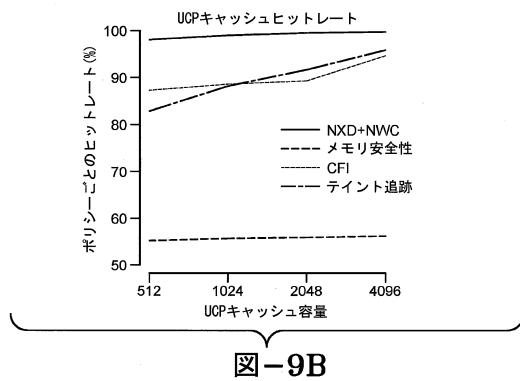

【図9 B】4つの例示的なマイクロアーキテクチャ最適化のためのキャッシュヒットレートを示す折れ線グラフである。

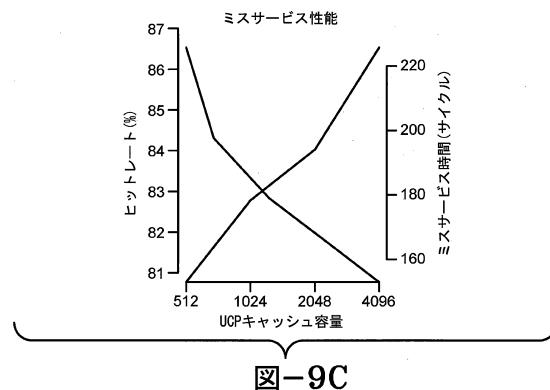

【図9 C】ミスサービス性能を示す折れ線グラフである。

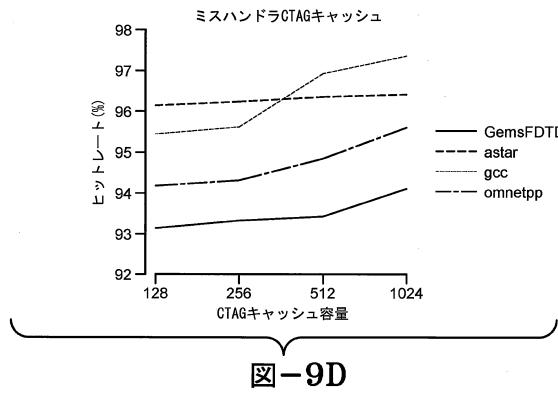

【図9 D】容量に基づいてミスハンドラヒットレートを示す折れ線グラフである。

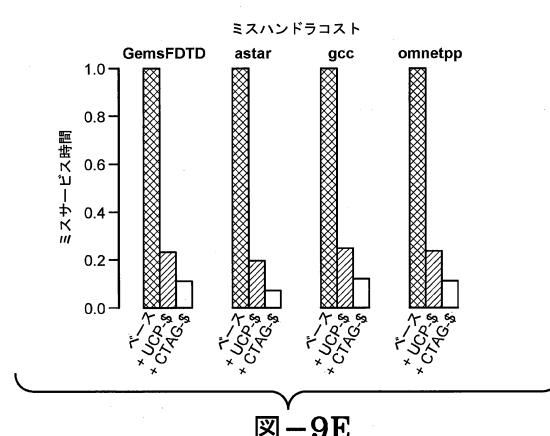

【図9 E】合成ポリシーに対する最適化の影響を示す一連の棒グラフである。

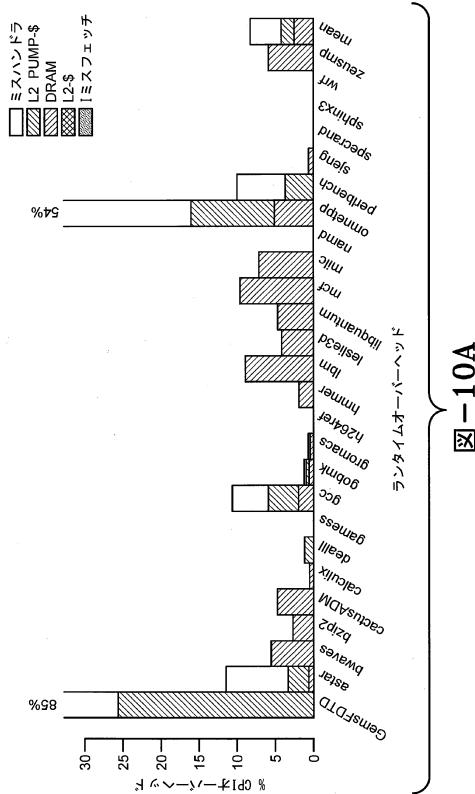

【図10 A】最適化された実装形態のランタイムオーバーヘッドを示す一連のグラフである。

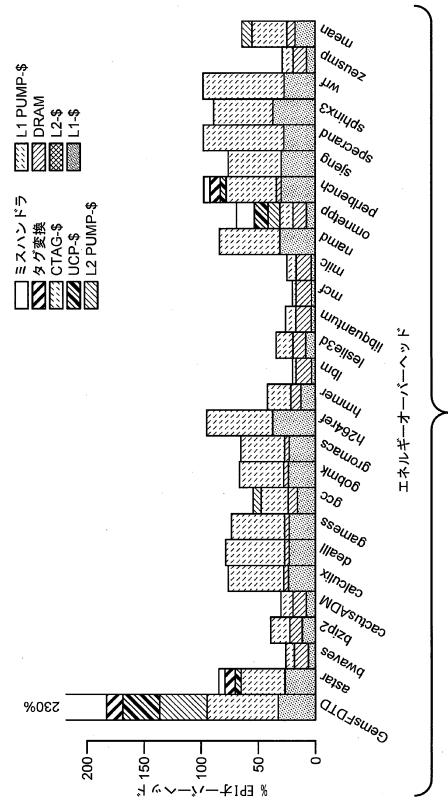

【図10 B】最適化された実装形態のエネルギーオーバーヘッドを示す一連の棒グラフで

50

ある。

【図 1 0 C】最適化された実装形態の絶対的な電力をベースラインと比較して示す一連の棒グラフである。

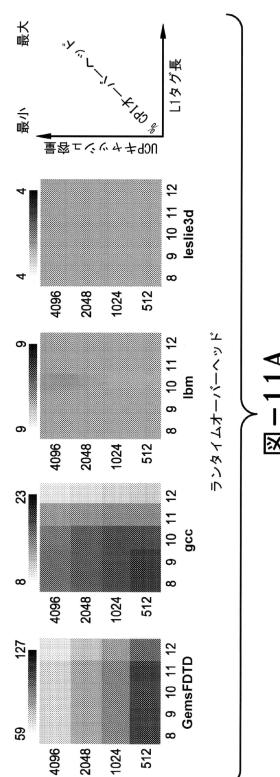

【図 1 1 A】様々な代表的なベンチマークについてタグビット長およびUCP-キャッシュ(\$)容量のランタイムオーバーヘッドへの影響を図示する一連の影付きグラフである。

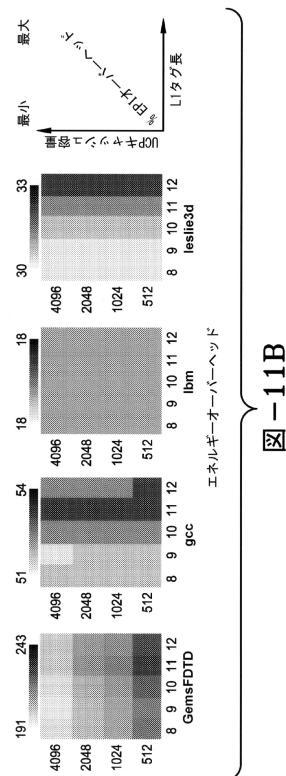

【図 1 1 B】様々な代表的なベンチマークについてタグビット長およびUCP-\$容量のエネルギーオーバーヘッドへの影響を図示する一連の影付きグラフである。

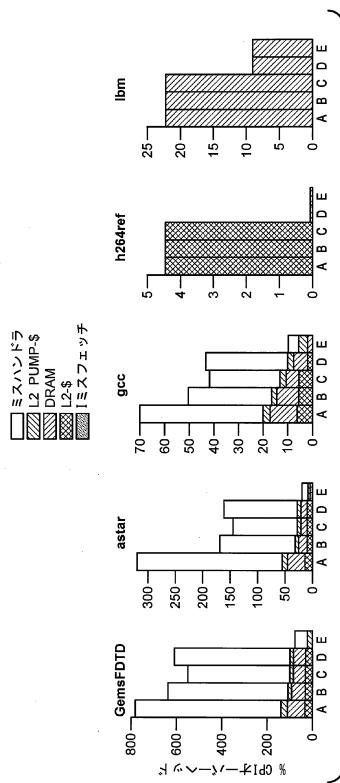

【図 1 2 A】代表的なベンチマークでの最適化のランタイムへの影響を示す一連のグラフであり、A:単純、B:A+オペグループ化、C:B+DRAM圧縮、D:C+(10b L1,14b L2)ショートタグ、E:D+(2048-UCP;512-CTAG)である。

【図 1 2 B】代表的なベンチマークでの最適化のエネルギーへの影響を示す一連のグラフであり、A:単純、B:A+オペグループ化、C:B+DRAM圧縮、D:C+(10b L1,14b L2)ショートタグ、E:D+(2048-UCP;512-CTAG)である。

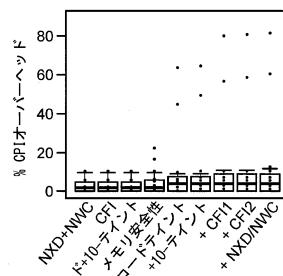

【図 1 3 A】代表的なベンチマークに対する合成におけるランタイムポリシーへの影響を示す一連のグラフである。

【図 1 3 B】合成におけるエネルギーポリシーへの影響を示す一連のグラフである。

【図 1 4】調査されるポリシーの概要を与える「表1」と名付けられる第1の表である。

【図 1 5】タグ付け方式の分類の概要を与える「表2」と名付けられる第2の表である。

【図 1 6】ベースラインおよび簡単なPUMP拡張されたプロセッサに対するメモリリソースの推定の概要を与える「表3」と名付けられる第3の表である。

【図 1 7】実験において使用されたPUMPパラメータ範囲の概要を与える「表4」と名付けられる第4の表である。

【図 1 8】PUMP最適化されたプロセッサに対するメモリリソースの推定の概要を与える「表5」と名付けられる第5の表である。

【図 1 9】ティント追跡ミスハンドラの概要を与える「アルゴリズム1」と名付けられる第1のアルゴリズムである。

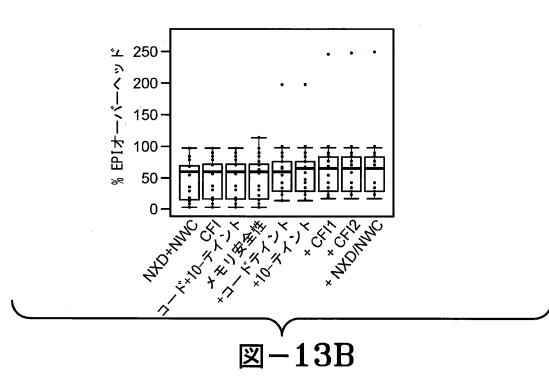

【図 2 0】Nポリシーミスハンドラの概要を与える「アルゴリズム2」と名付けられる第2のアルゴリズムである。

【図 2 1】HWサポートを伴うNポリシーミスハンドラの概要を与える「アルゴリズム3」と名付けられる第3のアルゴリズムである。

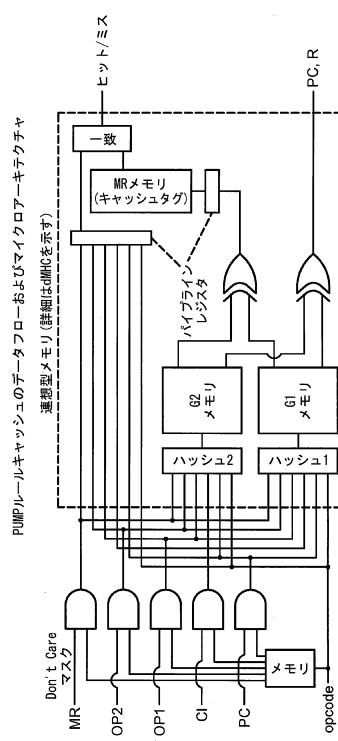

【図 2 2】PUMPルールキャッシュデータフローおよびマイクロアーキテクチャの概略図である。

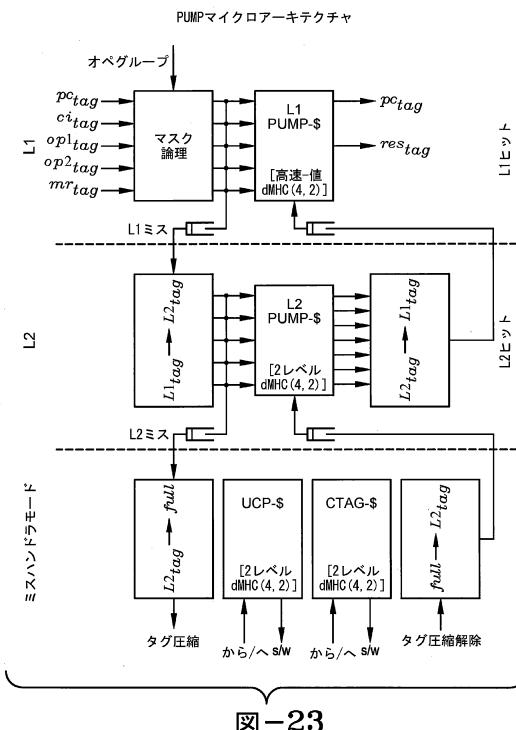

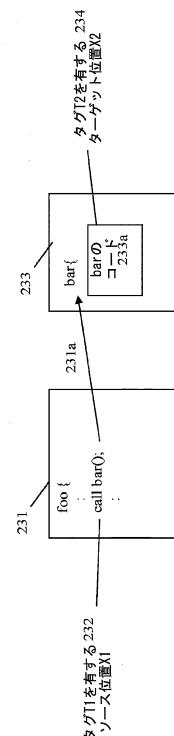

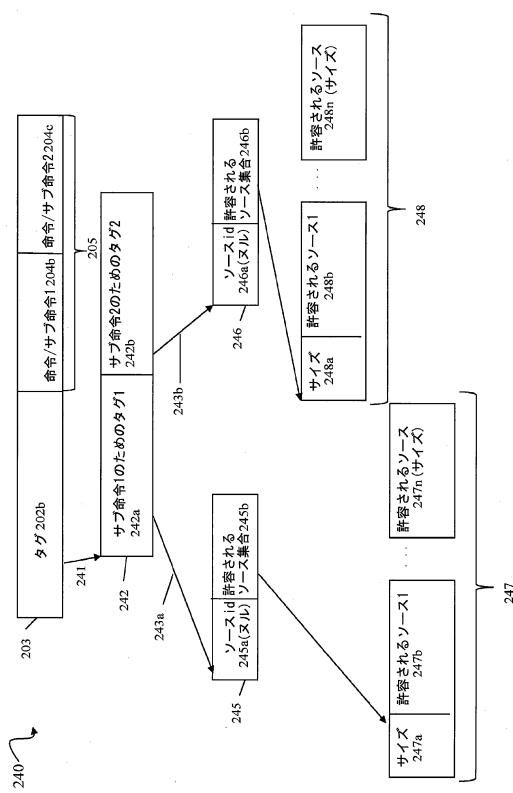

【図 2 3】PUMPマイクロアーキテクチャの概略図である。

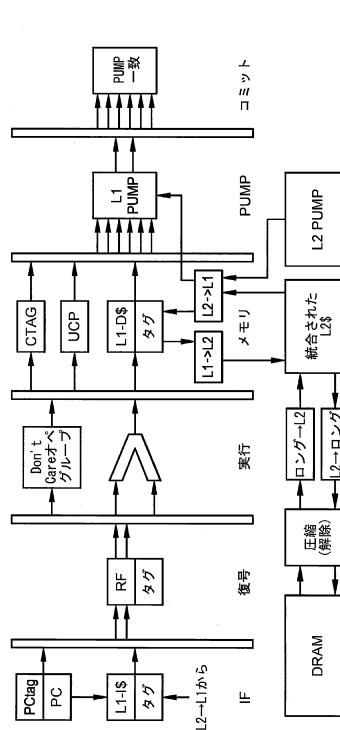

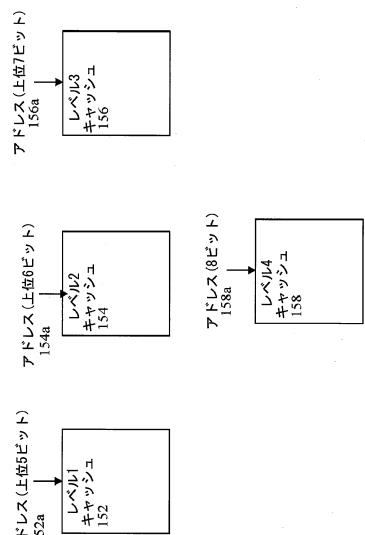

【図 2 4】プロセッサパイプラインおよびそのオペグループ変換においてパイプライン段階として統合される例示的なPUMPキャッシュ、UCPキャッシュ、およびCTAGキャッシュを示す、図1と同様の概略図である。

【図 2 5】本明細書の技法によるある実施形態における制御ステータスレジスタ(CSR)の例の図である。

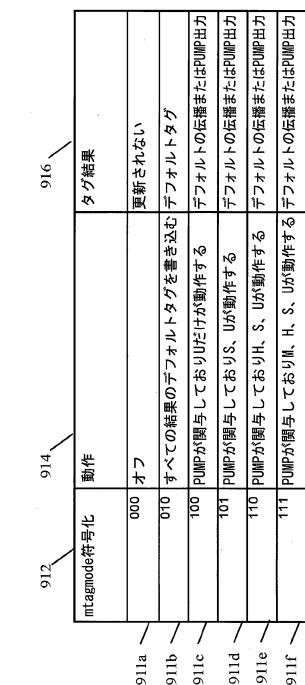

【図 2 6】本明細書の技法によるある実施形態におけるtagmodeの例の図である。

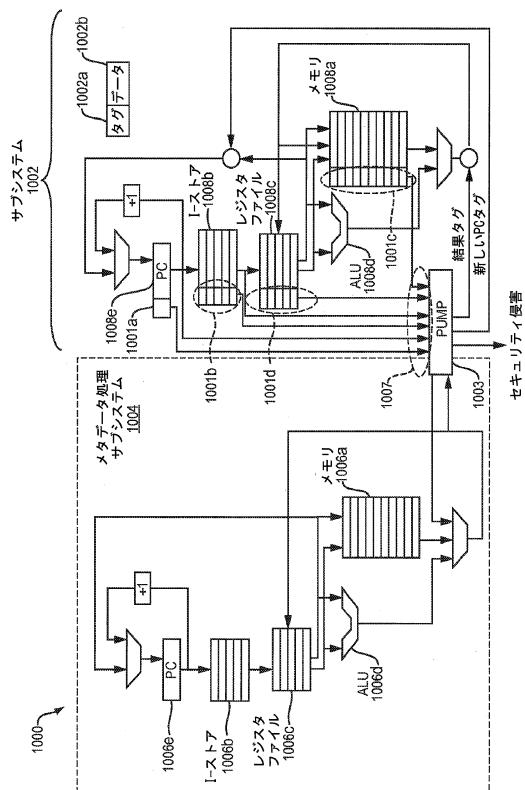

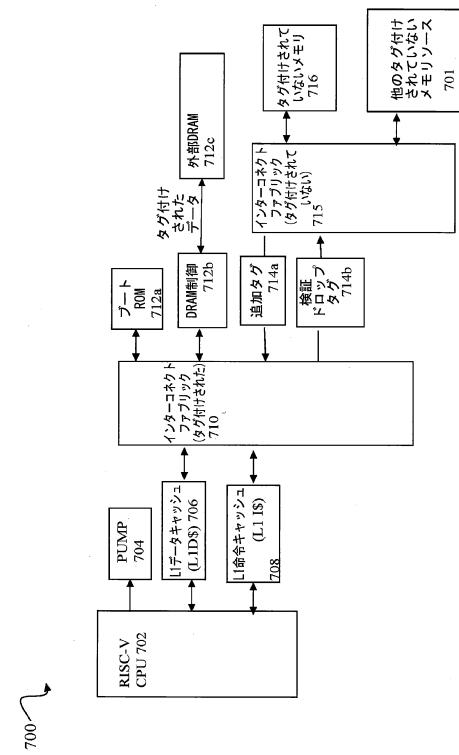

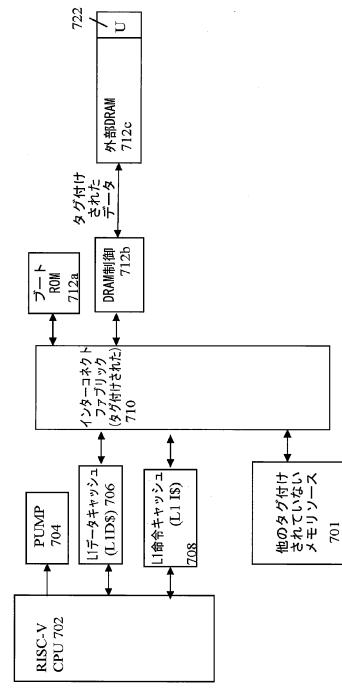

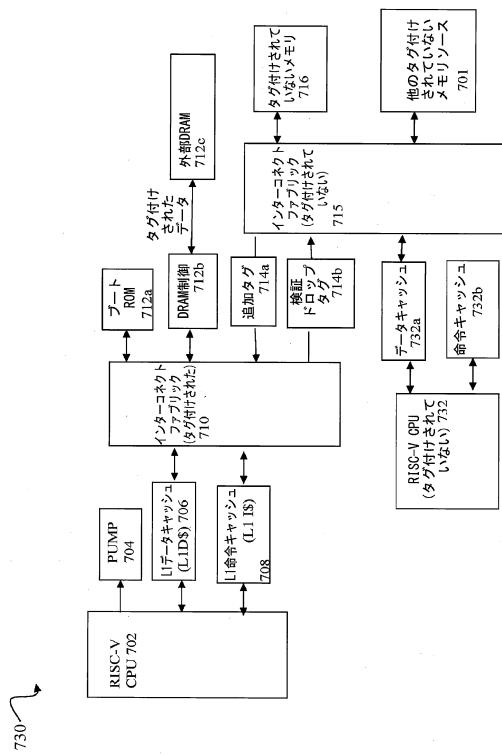

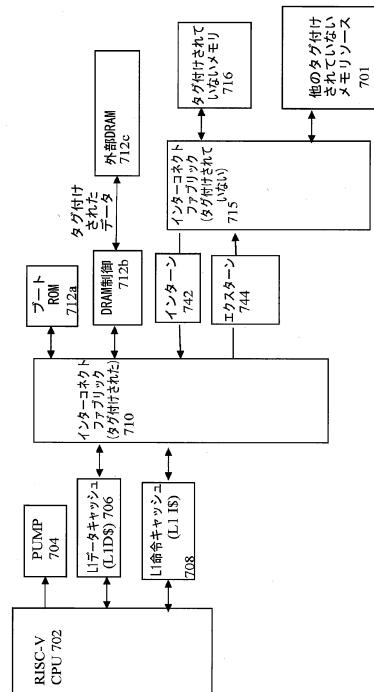

【図 2 7】本明細書の技法によるある実施形態における別個のプロセッサを伴う別個のメタデータ処理サブシステム/領域を示す例の図である。

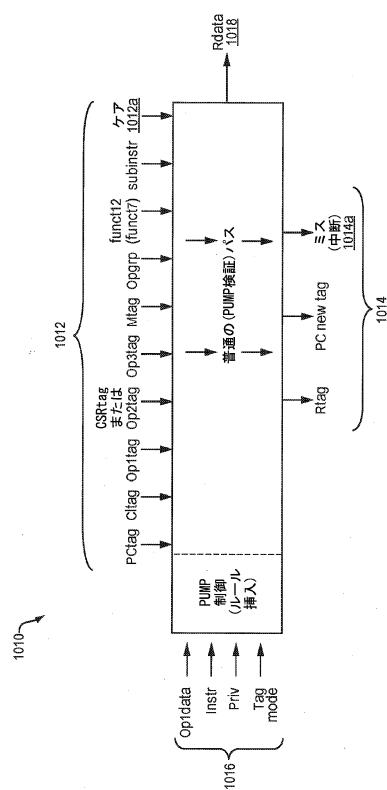

【図 2 8】本明細書の技法によるある実施形態におけるPUMP入力および出力を示す図である。

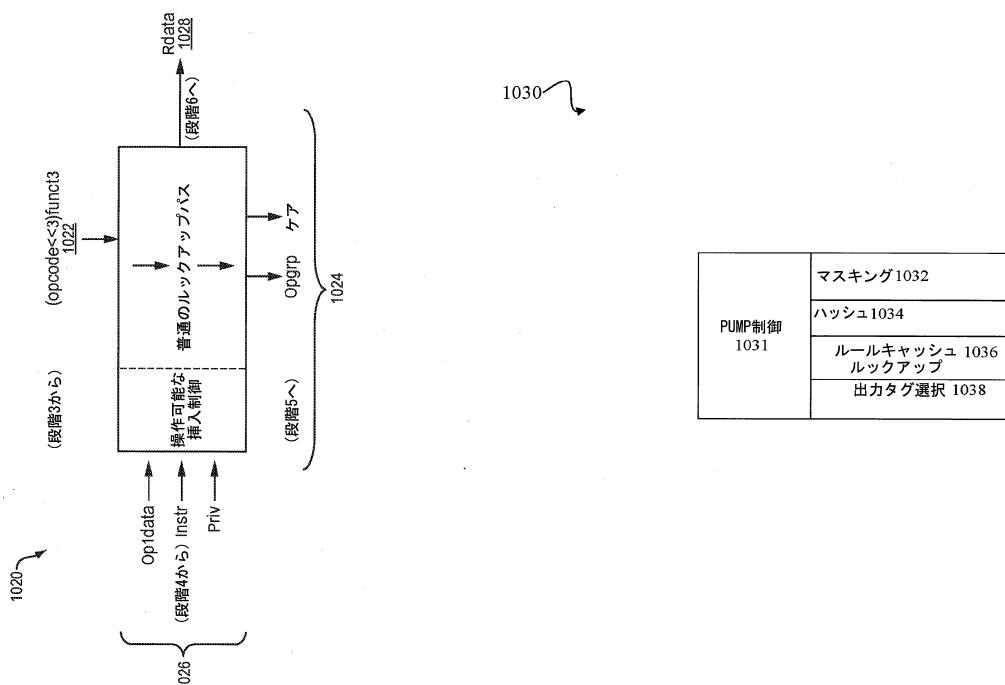

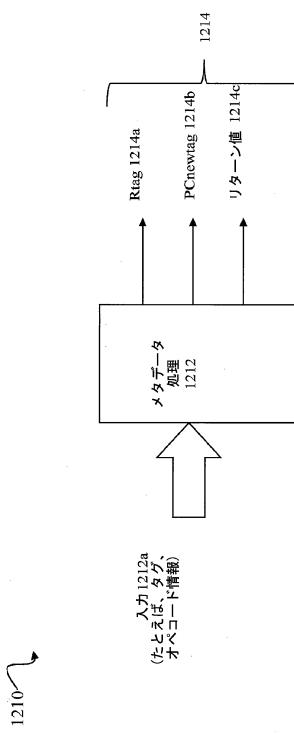

【図 2 9】本明細書の技法によるある実施形態におけるオペグループ表に関連して入力および出力を示す図である。

【図 3 0】本明細書の技法によるある実施形態におけるPUMPにより実行される処理を示す図である。

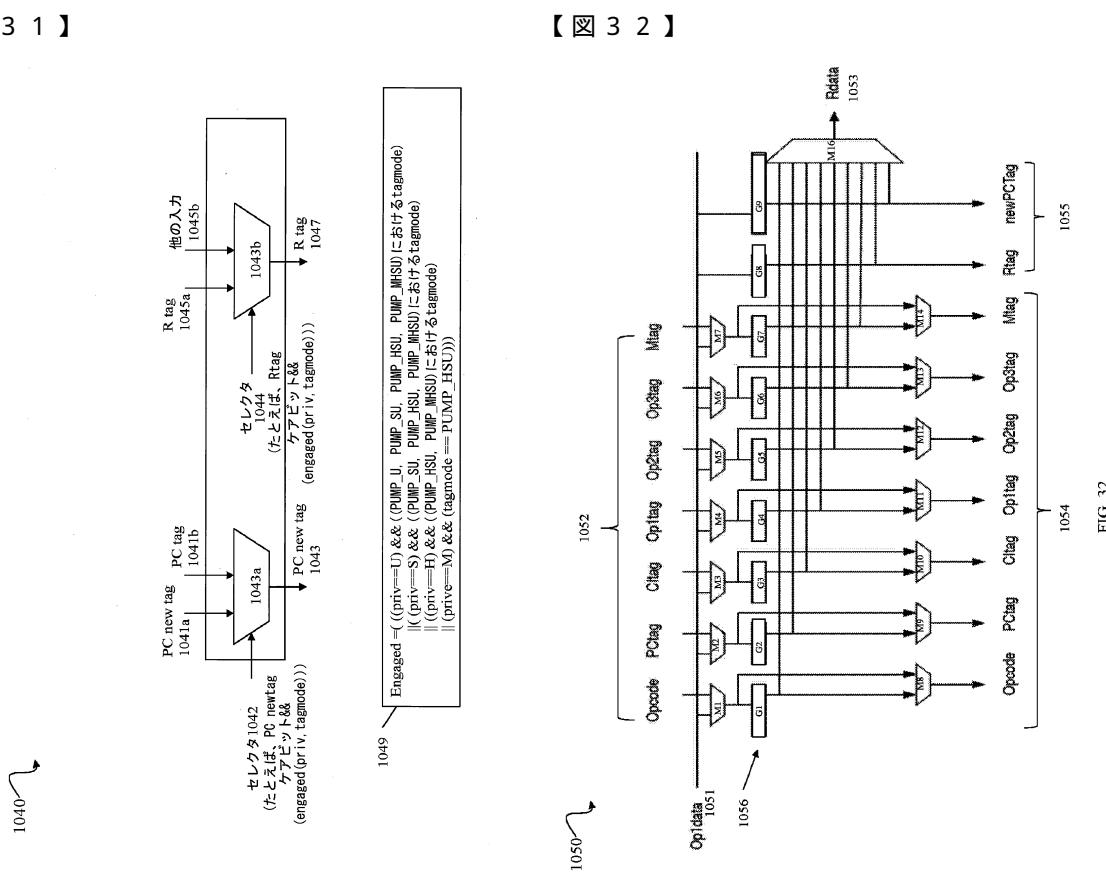

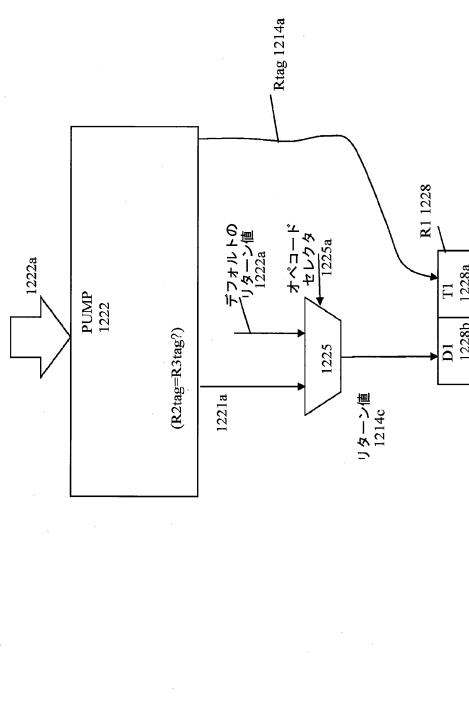

【図 3 1】本明細書の技法によるある実施形態におけるPUMP入力および出力の制御と選択に関する追加の詳細を与える図である。

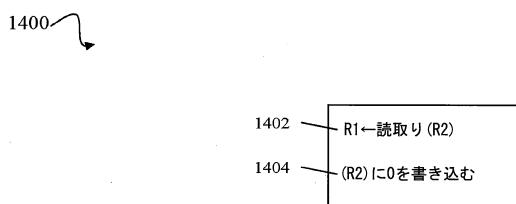

【図 3 2】本明細書の技法によるある実施形態におけるPUMP入力および出力の制御と選

10

20

30

40

50

択に関する追加の詳細を与える図である。

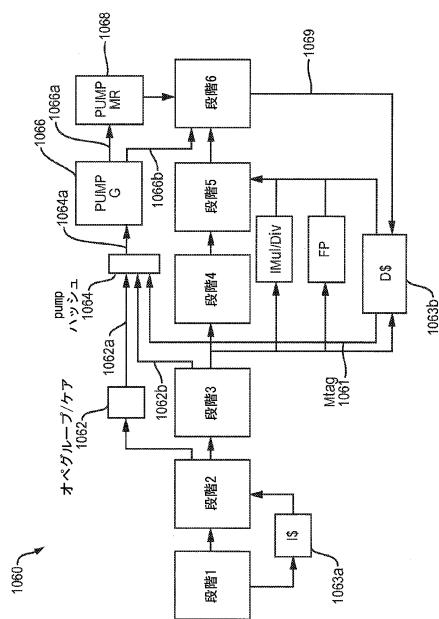

【図 3 3】本明細書の技法によるある実施形態における6段階の処理パイプラインを示す例の図である。

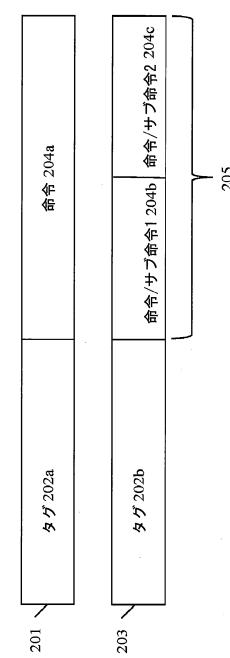

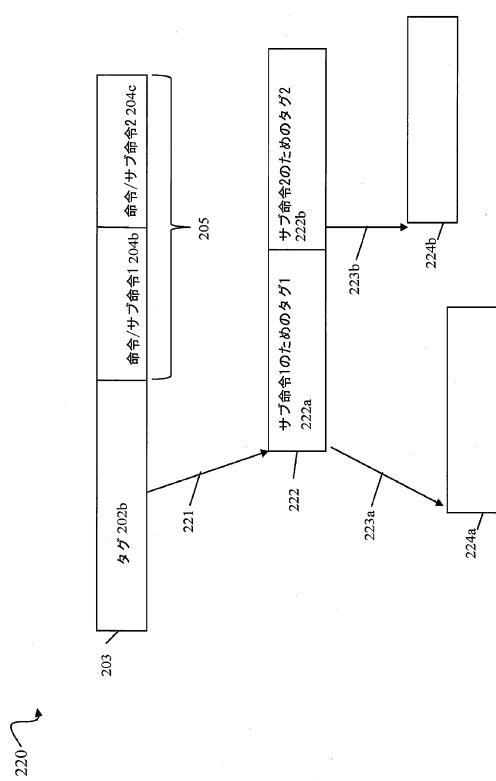

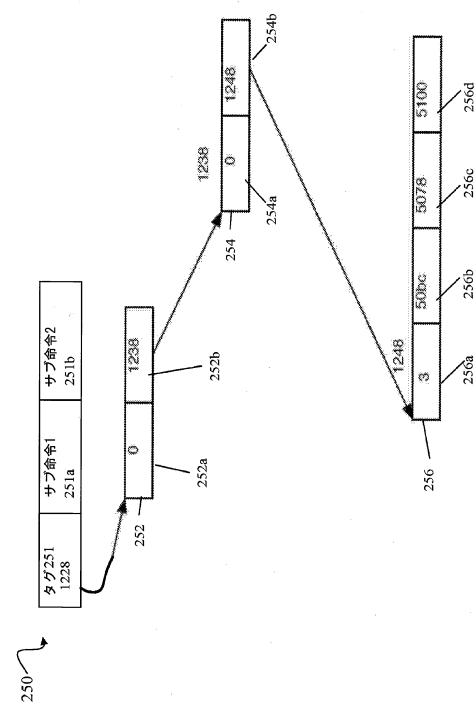

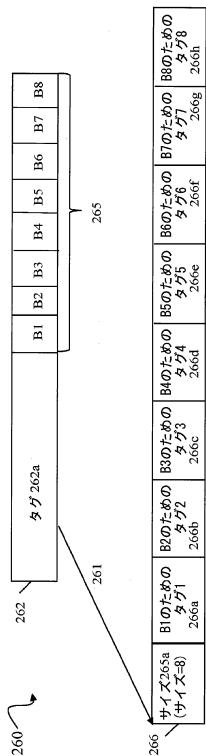

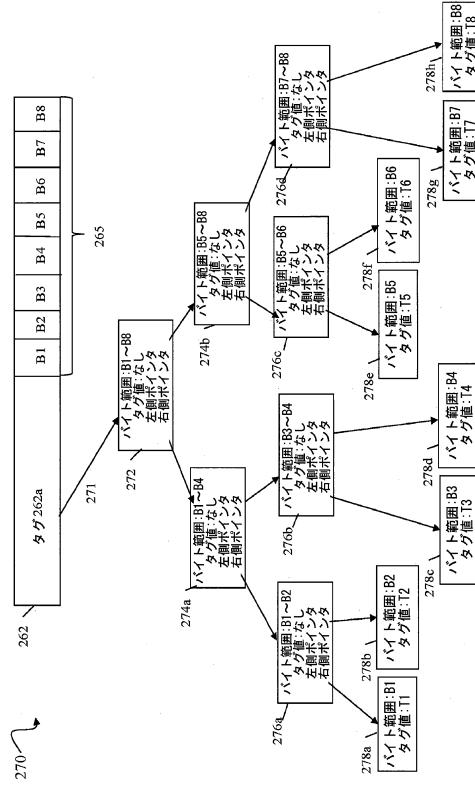

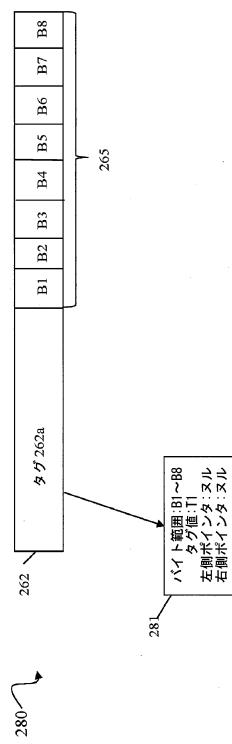

【図 3 4】ある実施形態におけるサブ命令および関連する技法を示す例の図である。

【図 3 5】ある実施形態におけるサブ命令および関連する技法を示す例の図である。

【図 3 6】ある実施形態におけるサブ命令および関連する技法を示す例の図である。

【図 3 7】ある実施形態におけるサブ命令および関連する技法を示す例の図である。

【図 3 8】ある実施形態におけるサブ命令および関連する技法を示す例の図である。

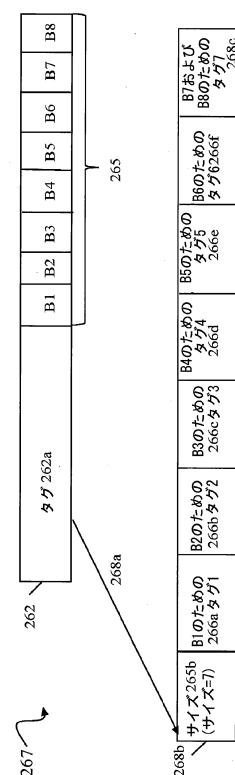

【図 3 9】ある実施形態におけるバイトレベルのタグ付けおよび関連する技法を示す例の図である。 10

【図 4 0】ある実施形態におけるバイトレベルのタグ付けおよび関連する技法を示す例の図である。

【図 4 1】ある実施形態におけるバイトレベルのタグ付けおよび関連する技法を示す例の図である。

【図 4 2】ある実施形態におけるバイトレベルのタグ付けおよび関連する技法を示す例の図である。

【図 4 3】本明細書の技法によるある実施形態における可変長オペコードを示す例の図である。

【図 4 4】本明細書の技法によるある実施形態におけるオペコードマッピングテーブルを示す例の図である。 20

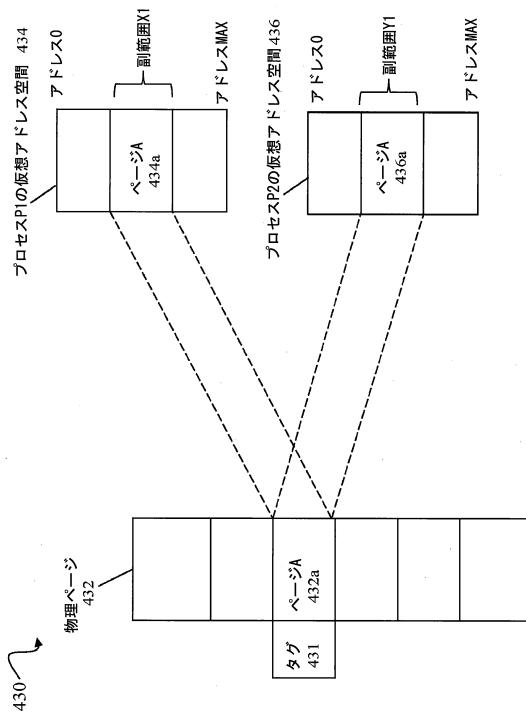

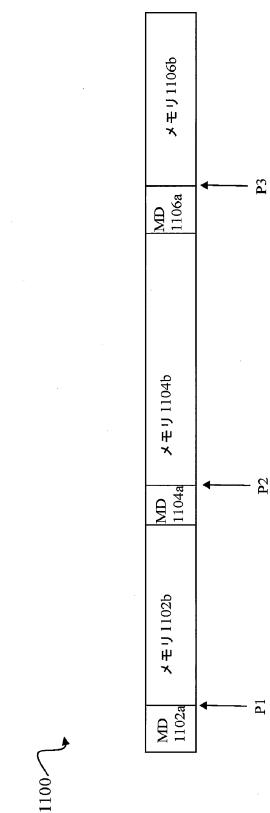

【図 4 5】本明細書の技法によるある実施形態における共有ページを示す例の図である。

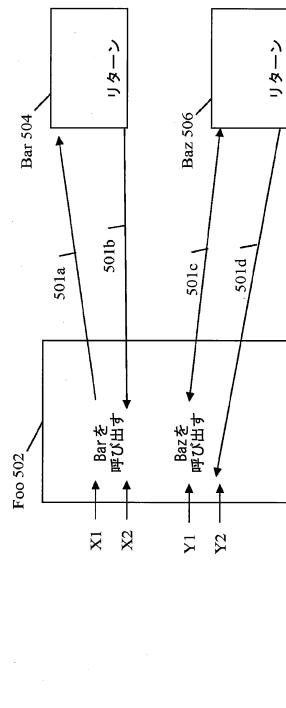

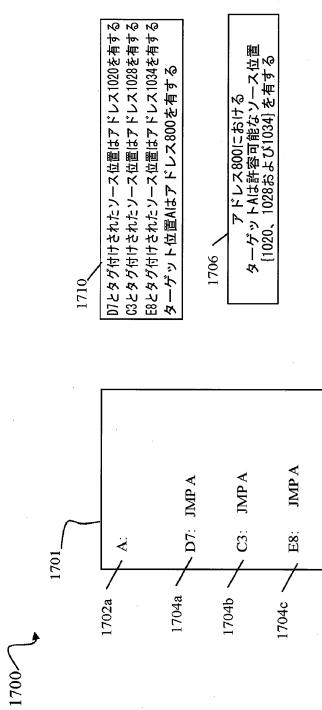

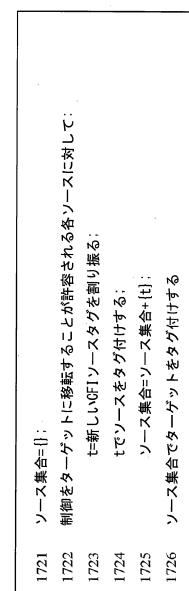

【図 4 6】本明細書の技法によるある実施形態における制御点の移転を示す例の図である。

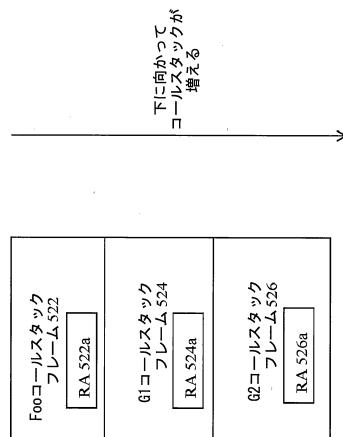

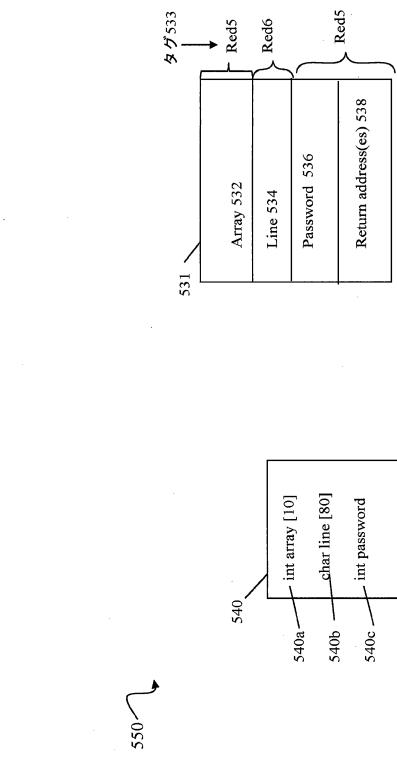

【図 4 7】本明細書の技法によるある実施形態における呼出しスタックを示す例の図である。

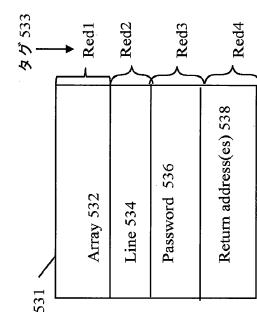

【図 4 8】本明細書の技法によるある実施形態におけるメモリ位置のタグ付けまたは色付けを示す例の図である。

【図 4 9】本明細書の技法によるある実施形態におけるメモリ位置のタグ付けまたは色付けを示す例の図である。

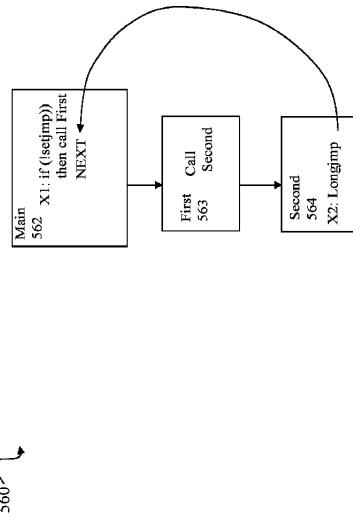

【図 5 0】本明細書の技法によるある実施形態における`setjmp`および`longjmp`を示す例の図である。 30

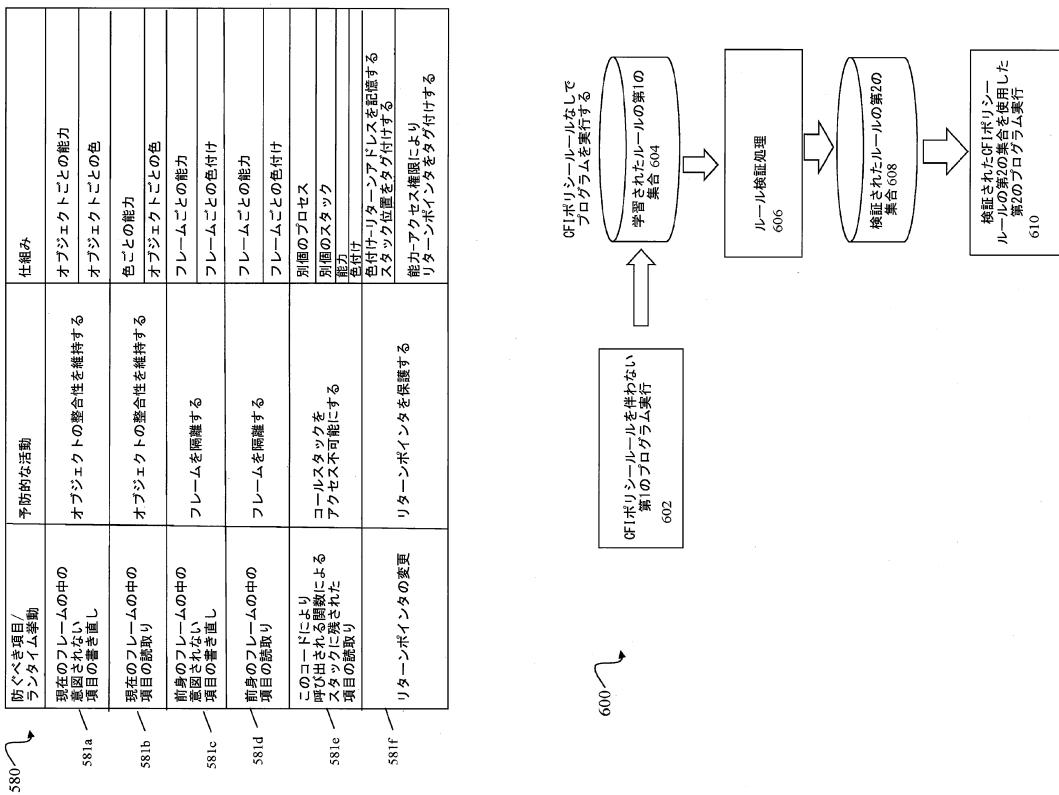

【図 5 1】本明細書の技法によるある実施形態における、あるランタイム挙動および関連する予防的な活動および予防的な活動を実施するために使用される機構の表である。

【図 5 2】本明細書の技法によるある実施形態における、異なるランタイム挙動および関連する予防的な活動および予防的な活動を実施するために使用される機構の表である。

【図 5 3】本明細書の技法によるある実施形態における、異なるランタイム挙動および関連する予防的な活動および予防的な活動を実施するために使用される機構の表である。

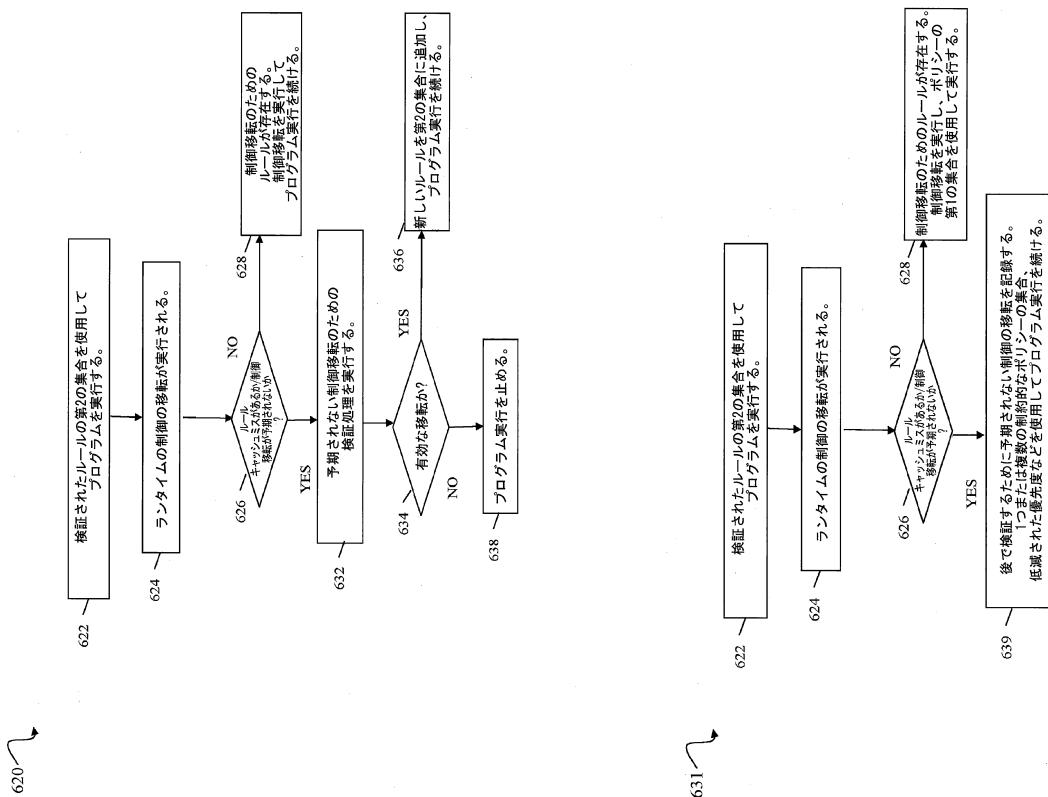

【図 5 4】本明細書の技法によるある実施形態におけるポリシールールを学習または判定するために実行され得る処理を示す例の図である。

【図 5 5】本明細書の技法によるある実施形態におけるポリシールールを学習または判定するために実行され得る処理を示す例の図である。 40

【図 5 6】本明細書の技法によるある実施形態におけるポリシールールを学習または判定するために実行され得る処理を示す例の図である。

【図 5 7】データの外部バージョンと内部のタグ付けされたバージョンとの間の変換に関する実施形態における構成要素を示す例の図である。

【図 5 8】データの外部バージョンと内部のタグ付けされたバージョンとの間の変換に関する実施形態における構成要素を示す例の図である。

【図 5 9】データの外部バージョンと内部のタグ付けされたバージョンとの間の変換に関する実施形態における構成要素を示す例の図である。

【図 6 0】データの外部バージョンと内部のタグ付けされたバージョンとの間の変換に関する実施形態における構成要素を示す例の図である。 50

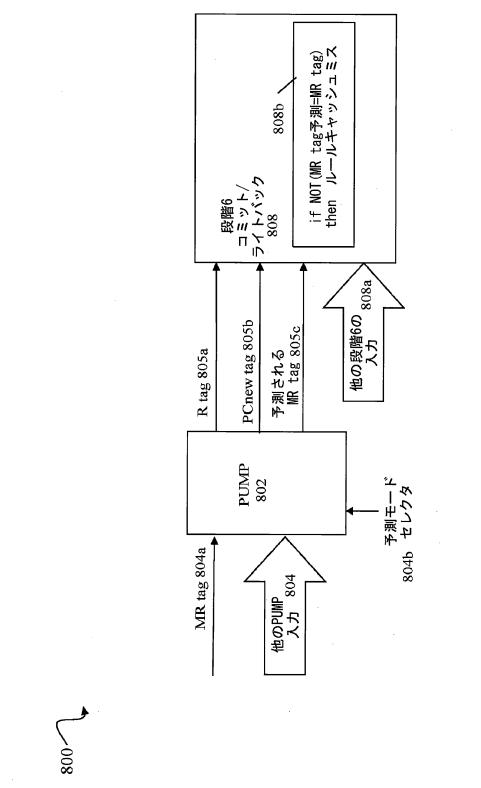

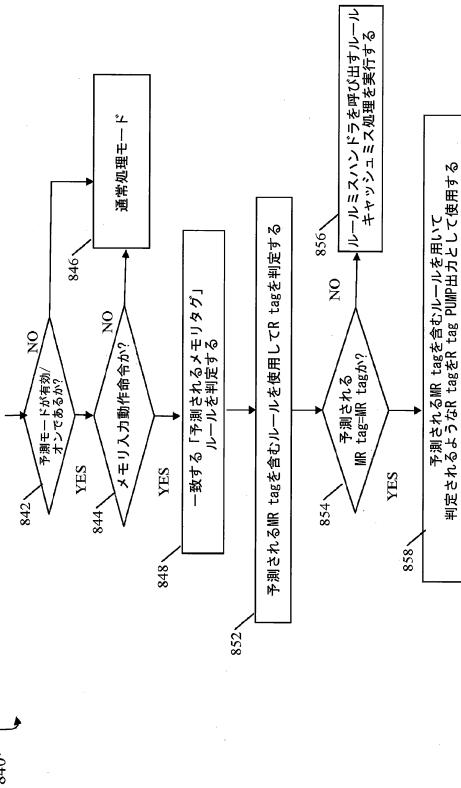

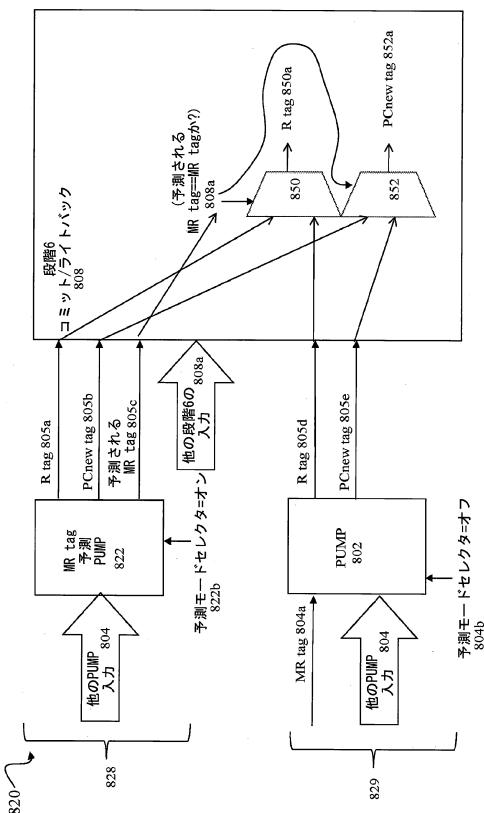

【図 6 1】本明細書の技法によるある実施形態におけるタグ予測を実行することの態様を示す例の図である。

【図 6 2】本明細書の技法によるある実施形態におけるタグ予測を実行することの態様を示す例の図である。

【図 6 3】本明細書の技法によるある実施形態におけるタグ予測を実行することの態様を示す例の図である。

【図 6 4】ある実施形態における、割り振られたメモリについて本明細書のメモリ位置色付け技法の使用を示す図である。

【図 6 5】ある実施形態における、割り振られたメモリについて本明細書のメモリ位置色付け技法の使用を示す図である。

【図 6 6】本明細書の技法によるある実施形態における、ハードウェアルールのサポートを提供する様々な構成要素を示す図である。

【図 6 7】本明細書の技法によるある実施形態における、ハードウェアルールのサポートを提供する様々な構成要素を示す図である。

【図 6 8】PUMPが値を返す実施形態における本明細書の技法の使用を示す例の図である。

【図 6 9】PUMPが値を返す実施形態における本明細書の技法の使用を示す例の図である。

【図 7 0】PUMPが値を返す実施形態における本明細書の技法の使用を示す例の図である。

【図 7 1】命令のシーケンスとともにある実施形態における本明細書の技法の使用を示す例の図である。

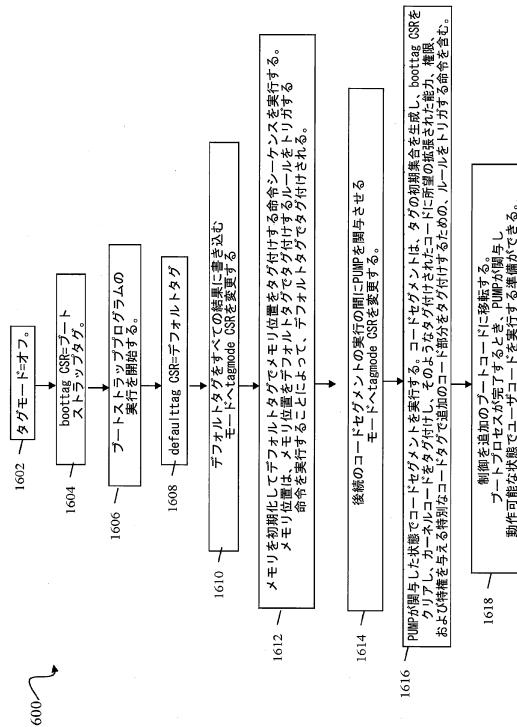

【図 7 2】本明細書の技法によるある実施形態における、システムをブートすることに関連して実行され得る処理ステップのフローチャートである。

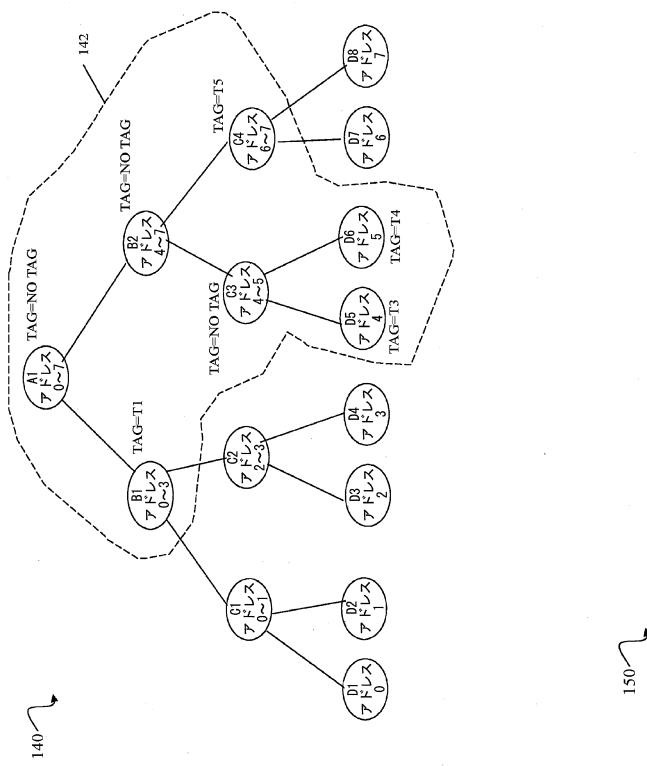

【図 7 3】本明細書の技法によるある実施形態における、タグ生成に関連するツリータグ階層の例の図である。

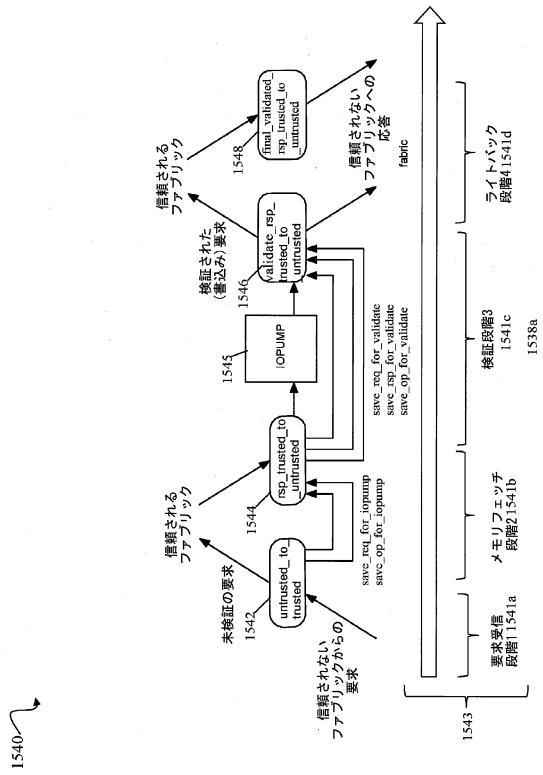

【図 7 4】本明細書の技法によるある実施形態における、I/O PUMPに関連する態様および特徴を示す例の図である。

【図 7 5】本明細書の技法によるある実施形態における、I/O PUMPに関連する態様および特徴を示す例の図である。

【図 7 6】本明細書の技法によるある実施形態における、I/O PUMPに関連する態様および特徴を示す例の図である。

【図 7 7】本明細書の技法によるある実施形態における、I/O PUMPに関連する態様および特徴を示す例の図である。

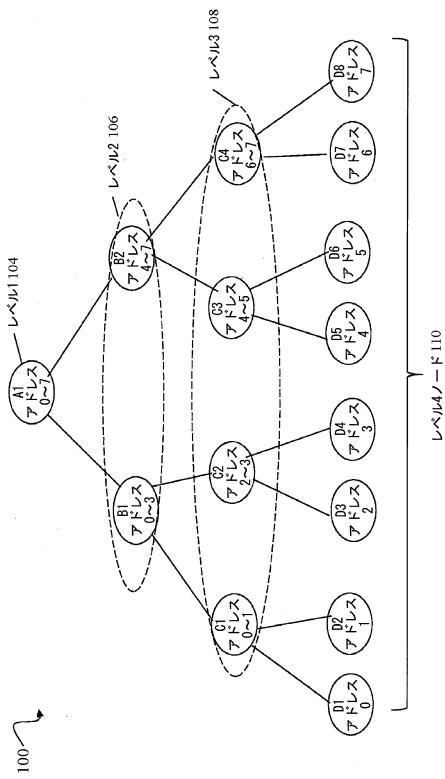

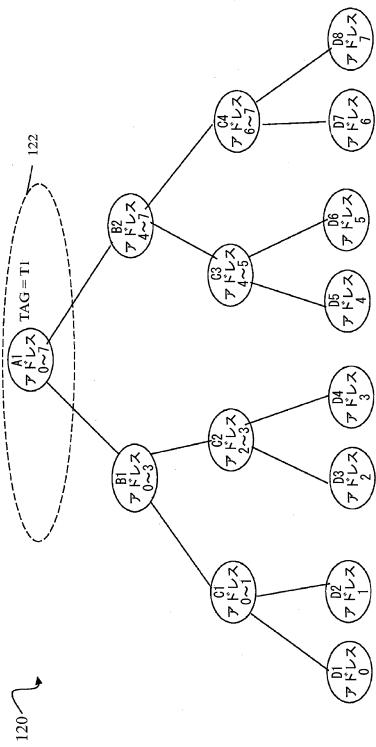

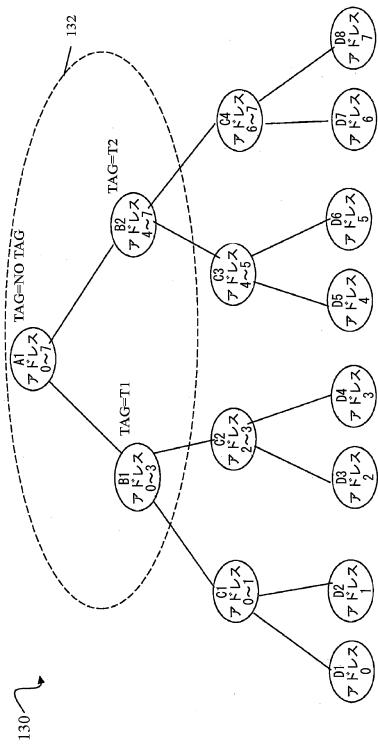

【図 7 8】本明細書の技法によるある実施形態における、タグ値を記憶して判定することに関連して使用される階層を示す例の図である。

【図 7 9】本明細書の技法によるある実施形態における、タグ値を記憶して判定することに関連して使用される階層を示す例の図である。

【図 8 0】本明細書の技法によるある実施形態における、タグ値を記憶して判定することに関連して使用される階層を示す例の図である。

【図 8 1】本明細書の技法によるある実施形態における、タグ値を記憶して判定することに関連して使用される階層を示す例の図である。

【図 8 2】本明細書の技法によるある実施形態における、タグ値を記憶して判定することに関連して使用される階層を示す例の図である。

【図 8 3】本明細書の技法によるある実施形態における、制御フロー整合性および関連する処理を示す例の図である。

【図 8 4】本明細書の技法によるある実施形態における、制御フロー整合性および関連する処理を示す例の図である。

【発明を実施するための形態】

【0030】

以下の段落で説明されるのは、メタデータタグを、システムのメインメモリ、キャッシュ、およびレジスタの中の1つ1つのワードと不可分に関連付ける、メタデータ処理のためのプログラム可能ユニット(PUMP)の様々な実施形態および態様である。無限のメタデータ

10

20

30

40

50

をサポートするために、タグはメモリの中のデータ構造を間接参照するのに十分大きい。1つ1つの命令上で、動作が許容されるかどうかを判定するために、および許容される場合には結果のためのタグを計算するために、入力のタグが使用される。いくつかの実施形態では、タグの確認および伝播のルールはソフトウェアにおいて定義されるが、性能への影響を最小限にするために、これらのルールは、プロセッサの算術論理装置(ALU)部分と並列に動作するハードウェア構造であるPUMPルールキャッシュにキャッシュされる。いくつかの実施形態では、ソフトウェアおよび/またはハードウェアを使用して実装され得るものなどの、ミスハンドラが、現在実施されているポリシーに基づいてキャッシュミスをサービスするために使用され得る。

#### 【0031】

4つの異なるポリシーの合成を使用する少なくとも1つの実施形態では、PUMPに様々な方法でストレスを与え、たとえば、(1)メモリの中のデータからコードを区別するためにタグを使用し、簡単なコードインジェクション攻撃に対する保護を提供する、非実行可能データおよび非書き込み可能コード(NXD+NWC)ポリシー、(2)ヒープに割り振られたメモリにおけるすべての空間的および時間的な侵害を検出し、実質的に無限の(260個の)数の色('ティントマーク')まで拡張する、メモリ安全性ポリシー、(3)間接的な制御の移転をプログラムの制御フローラフの中の許容されるエッジのみに制約し、return-oriented-programmingスタイルの攻撃を防ぐ、制御フロー整合性(CFI)ポリシー(攻撃に対する脆弱性がある可能性がある粗粒度の近似ではなく、細粒度のCFIが実施される)、(4)各ワードが複数のソース(ライブラリおよびIOストリーム)により同時にティントされる可能性があり得る、細粒度のティント追跡ポリシー(一般化)などの、一連のセキュリティ属性を例示する、PUMPの性能への影響が測定され得る(図14参照)。

#### 【0032】

上記は、本明細書の技法に従った実施形態において使用され得るよく知られているポリシーの例である。その保護能力が文献において確立されているそのようなよく知られているポリシーに対して、そのようなポリシーを実施しながら、PUMPを使用してポリシーを実施することの性能への影響も減らすために、本明細書の技法が使用され得る。NXD+NWCを除き、これらのポリシーの各々は、基本的に無限の数の固有のアイテムを区別する必要があり、対照的に、メタデータビットの数が限られている解決法は、せいぜい、ひどく簡略化された近似しかサポートすることができない。

#### 【0033】

本明細書の他の箇所で示され説明されるように、本明細書の技法に従った1つの実施形態は、ポインタサイズ(64bまたはバイト)のタグを64bのワードに対して使用し、それによりシステムの中のすべてのメモリのサイズおよびエネルギーの使用量を少なくとも2倍にする、PUMPの簡単で直接的な実装形態を利用することができる。これに加えて、ルールキャッシュが面積とエネルギーを追加する。この特定の実施形態では、190%の面積オーバーヘッド(図16参照)が測定され、幾何平均のエネルギーオーバーヘッドは220%前後であった。その上、いくつかのアプリケーションではランタイムオーバーヘッドが300%を超えることがある。そのような大きなオーバーヘッドは、それが行うことのできる最良のことであっても、採用を妨げることがある。

#### 【0034】

しかしながら、以下でより詳細に説明されるように、大半のポリシーは、タグと、タグに対して定義されるルールとの両方について、空間的および時間的な局所性を示す。したがって、本明細書の技法に従ったある実施形態は、類似する(または同一ですらある)命令のグループにわたってルールを定義することにより、固有のルールの数を大きく減らすことができ、強制的なミスを減らし、ルールキャッシュの実質的な容量を増やすことができる。オフチップのメモリトラフィックは、タグにおける空間的な局所性を利用することにより減らすことができる。オンチップの面積およびエネルギーオーバーヘッドは、使用されているポインタサイズのタグの部分集合を一度に表すために少数のビットを使用することにより最小限にすることができる。合成ポリシーミスハンドラのランタイムコストは、構

10

20

30

40

50

成要素のポリシーをキャッシュすることのサポートをハードウェアに与えることによって減らすことができる。したがって、本明細書の技法に従ったある実施形態は、そのような最適化を含むことで、PUMPがそのリッチなポリシーモデルを犠牲にすることなくより小さいオーバーヘッドを達成することを可能にし得る。

#### 【 0 0 3 5 】

本明細書の技法に従ったある実施形態は、独立してまたは同時に実施され得る任意の数のセキュリティポリシーを符号化するために使用され得るメタデータを用いて、メモリワードおよび内部プロセッサ状態を強化することができる。本明細書の技法に従ったある実施形態は、「従来の」プロセッサ(たとえば、RISC-CPU、GPU、ベクトルプロセッサなど)に、ポリシーの任意の集合を実施するためにデータフローと並列に動作するメタデータ処理ユニット(PUMP)を追加することによって、上記のことを達成することができ、本開示の技法は特に、メタデータを無制限にし、ソフトウェアをプログラム可能にするので、本明細書の技法は、広範囲のメタデータ処理ポリシーに対して適応され適用され得る。たとえば、PUMPは、従来の(RISC)プロセッサの新しい/別個のパイプライン段階として統合されることがある、または、「ホスト」プロセッサと並列に動作するハードウェアのスタンダロンの断片として統合されることがある。前者の場合、設計を特徴付けるために、命令レベルシミュレータ、精緻化されたポリシー、実装の最適化およびリソースの推定、ならびに広範囲のシミュレーションがあり得る。

10

#### 【 0 0 3 6 】

粒度レベルが細かいポリシー(すなわち、命令)を実施しようとする既存の解決法は、ポリシーの任意の集合を実施できない。一般に、命令レベルでは少数の固定されたポリシーしか実施できない。より細かい粒度レベル(すなわち、スレッド)でポリシーを実施すると、あるクラスのリターン指向プログラミング攻撃を防ぐことができず、したがってそのタイプの実施は有用性の点で限られたものになる。対照的に、本明細書の技法に従った実施形態は、命令レベルにおいて単一でまたは同時に実施され得る、無限の数のポリシーの表現を許容する(唯一の制限はサイズアドレス空間であり、それはメタデータがあらゆる任意のデータ構造を指すことができるアドレスポインタに関して表現されるからである)。

20

#### 【 0 0 3 7 】

以下の段落において説明される様々な図は、本明細書で説明される技法の様々な態様の様々な例、方法、および他の例示的な実施形態を示すことに留意されたい。そのような図面において、示される要素の境界(たとえば、ボックス、ボックスのグループ、または他の形状)は、一般に境界の一例を表すことを理解されたい。いくつかの例では、1つの要素が複数の要素として設計され得ること、または複数の要素が1つの要素として設計され得ることを、当業者は理解するであろう。いくつかの例では、別の要素の内部構成要素として示される要素が外部構成要素として実装されることがあり、その逆であることもある。さらに、要素は縮尺通りに描かれていないことがある。

30

#### 【 0 0 3 8 】

図1を参照すると、メタデータ処理のためのプログラム可能ユニット(PUMP)10は、エネルギー消費を意識するアプリケーションに対して適切なin-orderの実装形態および5段階のパイプラインを伴う、従来の縮小命令セットコンピューティングまたはコンピュータ(RISC)プロセッサ12へと統合され、これは実質的に、PUMP10が追加された6段階のパイプラインに変換される。第1の段階はフェッチ段階14であり、第2の段階は復号段階16であり、第3の段階は実行段階18であり、第4の段階はメモリ段階20であり、第5の段階はライトバック段階22である。PUMP10は、メモリ段階20とライトバック段階22の間に挟まれる。

40

#### 【 0 0 3 9 】

様々な実施形態は、ポリシー実施およびメタデータ伝播を行う機構である電子論理回路を使用して、PUMP10を実装し得る。PUMP10の実施形態は、(i)4つの異なるポリシーおよびそれらの組合せのもとでのベンチマークの標準的な集合に対する、PUMP10の簡単な実装形態のランタイム、エネルギー、電力上限、および面積への影響の経験的な評価、(ii)マ

50

イクロアーキテクチャ最適化の集合、および(iii)これらの最適化による利益の測定結果により特徴付けることができ、この測定結果は、オンチップメモリ構造のために110%の追加の面積を使用することによる、10%を下回る典型的なランタイムオーバーヘッド、10%の電力上限への影響、および60%を下回る典型的なエネルギーオーバーヘッドを示している。

#### 【0040】

コンピューティングにおいて、ベンチマークリングは、普通は数回の標準的なテストおよびそれに対する試行を実行することにより、対象の相対的な性能を評価するために、コンピュータプログラム、プログラムの集合、または他の動作を実行する活動として特徴付けられ得る。本明細書で使用される「ベンチマーク」という用語は、ベンチマークプログラム自身を指す。本出願および図面全体で使用されるベンチマークプログラムのタイプは、GemsFDTD、astar、bwaves、bzip2、cactusADM、calculix、deall、gamess、gcc、gobmk、gromacs、h264ref、hmmer、lbm、leslie3d、libquantum、mcf、milc、namd、omnetpp、perlbench、sjeng、specrand、sphinx3、wrf、zeusmp、およびmeanである。たとえば、図10A、図10B、および図10Cを参照されたい。

10

#### 【0041】

本明細書で使用される「論理」は、限定はされないが、機能もしくは活動を実行するための、かつ/または、別の論理、方法、および/もしくはシステムからの機能もしくは活動を引き起こすための、ハードウェア、ファームウェア、ソフトウェア、および/または各々の組合せを含む。たとえば、所望のアプリケーションまたは必要性に基づいて、論理は、ソフトウェアで制御されるマイクロプロセッサ、プロセッサ(たとえば、マイクロプロセッサ)のようなディスクリート論理、特定用途向け集積回路(ASIC)、プログラムされた論理デバイス、命令を含むメモリデバイス、メモリを有する電子デバイスなどを含み得る。論理は、1つまたは複数のゲート、ゲートの組合せ、または他の回路構成要素を含み得る。論理はまた、ソフトウェアとして完全に具現化され得る。複数の論理が説明される場合、1つの物理的な論理へと複数の論理を組み込むことが可能であり得る。同様に、単一の論理が説明される場合、その単一の論理を複数の物理的な論理の間で分散させることが可能であり得る。

20

#### 【0042】

本明細書の技法に従った少なくとも1つの実施形態では、PUMP10は、従来のRISCプロセッサ12への拡張として特徴付けられ得る。以下の段落は、PUMP10のハードウェアインターフェース層を構成するISA(命令セットアーキテクチャ)レベルの拡張、基本的なマイクロアーキテクチャの変更、および本明細書の技法に従った実施形態において使用され得る付随する低水準ソフトウェアの、さらなる詳細を与える。

30

#### 【0043】

本明細書の技法に従ったある実施形態において、PUMPで強化されたシステムにおける各ワードは、ポインタサイズのタグと関連付けられ得る。これらのタグはハードウェアレベルでは解釈されない。ソフトウェアレベルにおいて、タグは、ポリシーにより定義されるように、無制限のサイズおよび複雑さのメタデータを表し得る。数ビットのメタデータしか必要としないより簡単なポリシーは、メタデータをタグに直接記憶し得る。より多くのビットが必要とされる場合、メタデータをデータ構造として、タグとして使用されるこの構造のアドレスとともにメモリに記憶するために、間接参照が使用される。特に、これらのポインタサイズのタグは、本開示の1つの例示的な態様であり、限定するものと見なされるべきではない。基本的なアドレス指定可能なメモリワードはタグを用いて不可分に拡張され、メモリ、キャッシュ、およびレジスタを含むすべての値スロットを、適度により広くする。プログラムカウンタ(PC)もタグ付けされる。ソフトウェアで定義されるメタデータ、およびポインタサイズのタグとしてのそのメタデータを表現するというこの観念は、タグのために数ビットしか使用されない、および/または固定された解釈にタグがハードワイヤリングされる、従来のタグ付け手法を拡張する。タグ付け方式のいくつかの例示的な分類が表2に表されており、これは図15において再現されている。

40

50

## 【0044】

メタデータタグはユーザプログラムによってアドレス指定可能ではない。むしろ、メタデータタグは、以下で説明されるようなルールキャッシュミスに際して呼び出されるポリシー-ハンドラによってアドレス指定される。タグへのすべての更新はPUMP10のルールを通じて実現される。

## 【0045】

無制限のメタデータ以外では、本明細書の技法に従ったPUMP10の実施形態の別の特徴は、メタデータに対する単一サイクルのコモンケース計算を、ハードウェアがサポートすることである。これらの計算は、形式オペコードのルールに関して定義される:(PC,CI,OP1,OP2,MR) (PC<sub>new</sub>,R)。これは、「現在のオペコードがopcodeであり、プログラムカウンタの現在のタグがPCであり、現在の命令のタグがCIであり、その入力オペランド(もしあれば)のタグがOP1およびOP2であり、メモリ位置のタグ(ロード/記憶の場合)がMRである場合、次のマシン状態におけるプログラムカウンタのタグはPC<sub>new</sub>であるべきであり、命令の結果のタグ(もしあれば、宛先レジスタまたはメモリ位置)はRであるべきである」と読まれるべきである。2つの出力タグが最大で5つの入力タグから計算されることを可能にするこのルールフォーマットは、通常は1つの出力を最大で2つの入力から計算する(図15の表2参照)従来の成果において検討されたものよりも明らかにフレキシブルである。データタグ(OP1,OP2,MR,R)のみを追跡する従来の解決法を超えて、本開示は、コードブロックの起源、整合性、および使用法を追跡して実施するために使用され得る現在の命令タグ(CI)、ならびに、実行履歴、ambient authority、および暗黙的な情報フローを含む「制御状態」を記録するために使用され得るPCタグを提供する。CFIは、間接参照のジャンプのソースを記録するためのPCタグと、ジャンプのターゲットを特定するためのCIタグとを利用し、NXD+NWCは、データが実行可能ではないことを強制するためにCIを利用し、ティント追跡は、データを產生したコードに基づいてデータをティントするためにCIを使用する。

10

20

30

## 【0046】

一般的な場合の単一のサイクルにおけるルールを解決するために、本明細書の技法に従ったある実施形態は、直近に使用されたルールのハードウェアキャッシュを使用し得る。命令およびポリシーに応じて、所与のルールにおける入力スロットのうちの1つまたは複数は使用されないことがある。使用されないスロットのすべてのあり得る値についてのルールでキャッシュを汚染するのを避けるために、ルールキャッシュルックアップ論理は、各々の入力されるスロット-オペコードのペアに対して「don't-care」(図1参照)ビットを格納するビットベクトルを参照し、このビットベクトルは、対応するタグがルールキャッシュのルックアップにおいて実際に使用されるかどうかを判定する。これらの「don't care」入力を効率的に扱うために、それらは、入力をPUMP10に提示する前にマスクされる。don't-careビットベクトルは、ミスハンドラのインストールの一部として特権命令により設定される。

## 【0047】

図1は全般に、PUMP10ハードウェアを組み込む修正された5段階のプロセッサ12のパイプラインを伴う、本明細書の技法に従った1つの実施形態を示す。ルールキャッシュのルックアップは、PUMP10の段階がプロセッサパイプラインにおける追加のストールを生み出さないように、追加の段階およびバイパスタグおよびデータとして独立に追加される。

40

## 【0048】

PUMP10を別個の段階として(メモリ段階20とライトバック段階22の間に)置くことの動機は、PUMP10への入力として、メモリから読み取られる(ロード)、またはメモリに上書きされる(記憶)ことになるワードにタグを提供することの必要性である。書き込まれているメモリ位置の既存のタグに依存してルールが許容されるので、書き込み動作は、読み取り-修正-書き込み動作になる。既存のタグは、読み取りルールのようにメモリ段階20の間に読み取られ、読み取りルールはPUMP10段階において確認され、書き込みはライトバック段階22とも呼ばれ得るコミット段階の間に実行される。あらゆるキャッシュ方式のように、キャッシュ

50

シユの複数のレベルがPUMP10のために使用され得る。以下でより詳細に説明されるよう に、本明細書の技法に従ったある実施形態は、2レベルのキャッシュを利用し得る。複数 のレベルのキャッシュへの拡張は、当業者には容易に明らかである。

#### 【 0 0 4 9 】

1つの非限定的な例では、最終レベルのミスがライトバック段階22においてルールキャッシュ の中に発生し、これは次のように扱われる。(i)この目的のためだけに使用されるプロセッサレジスタの(新しい)集合に現在のオペコードおよびタグが保存され、(ii)制御がポリシーミスハンドラ(以下でより詳細に説明される)に移転され、(iii)ポリシーミスハンドラが、動作が許容されるかどうかを判断し、許容される場合には適切なルールを生成する。 ミスハンドラがリターンするとき、ハードウェアが(iv)このルールをPUMP10のルールキャッシュにインストールし、(v)フォルトした命令を再び発行する。特権のあるミスハンドラと、システムソフトウェアおよびユーザコードの残りとの間を隔離するために、ミスハンドラの動作モードがプロセッサに追加され、これは、ルールキャッシュミスに際して設定されミスハンドラがリターンするときにリセットされる、プロセッサ状態のビットにより制御される。1つ1つのルールキャッシュミスにおいてレジスタを保存して復元する必要をなくすために、整数レジスタファイルが、ミスハンドラにのみ利用可能である16個の追加のレジスタを用いて拡張され得る。加えて、ルールの入力および出力は、ミスハンドラモード(たとえば、レジスタウィンドウ)にある間はレジスタとして出現し、ミスハンドラが(ただしそれだけが)タグを普通の値として操作することが可能になる。やはり、これらはすべて、ライトバック段階22の非限定的な例である。

10

20

#### 【 0 0 5 0 】

ルールをPUMP10のルールキャッシュにインストールすることを終えてユーザコードに戻るため に、新しいミスハンドラリターン命令が追加される。この特定の非限定的な例では、この命令は、ミスハンドラモードにあるときにのみ発行され得る。ミスハンドラモードにある間、ルールキャッシュは無視され、PUMP10が代わりに、単一のハードウェイドルールを適用する。ミスハンドラによって扱われたすべての命令およびデータは、事前に定義されたMISSHANDLERタグを用いてタグ付けされなければならず、すべての命令の結果は同じタグを与えられる。このようにして、PUMP10のアーキテクチャは、ポリシーにより提供される保護をユーザコードが損ねるのを防ぐ。代わりに、PUMPは、ミスハンドラのアクセスについてフレキシブルなルールを実施するために使用され得る。タグは、ユーザコードによって分割可能ではなく、アドレス指定可能ではなく、または置換可能ではない。メタデータデータ構造およびミスハンドラコードを、ユーザコードが扱うことはできず、ユーザコードはルールをルールキャッシュに直接挿入することができない。

30

#### 【 0 0 5 1 】

図19を参照すると、アルゴリズム1は、テイント追跡ポリシーのためのミスハンドラの動作を示す。別個のタグ(および、したがってルール)の数を最小にするために、ミスハンドラは、構築するあらゆる新しいデータ構造を「正規化する」ことによって、論理的に等価なメタデータに対して単一のタグを使用する。

#### 【 0 0 5 2 】

ユーザに単一ポリシーを選ぶことを強いるのではなく、複数のポリシーが同時に実施され、新しいポリシーが後で追加される。これらの「無制限の」タグの例示的な利点は、任意の数のポリシーを同時に実施できるということである。これは、タグを、いくつかの構成要素ポリシーからのタグのタプルへのポインタにすることによって、実現され得る。たとえば、NXD+NWCポリシーをテイント追跡ポリシーと組み合わせるために、各タグはタブル(s,t)へのポインタであってよく、sはNXD+NWCタグ(DATAまたはCODEのいずれか)であり、tはテイントタグ(テイントの集合へのポインタ)である。ルールキャッシュのルックアップは同様であるが、ミスが発生するとき、両方の構成要素ポリシーが別々に評価される。動作は、両方のポリシーがそれを許容する場合にのみ許容され、得られるタグは2つの構成要素ポリシーからの結果のペアである。しかしながら、他の実施形態では、ポリシーがどのように組み合わされるか(すべての構成要素の間のANDのように単純ではない)を

40

50

表現することが可能であり得る。

【 0 0 5 3 】

図20を参照すると、アルゴリズム2は、任意のN個のポリシーのための合成ミスハンドラの一般的な挙動を示す。タブルの中のタグがどのように相関しているかに応じて、これは、タグの、およびしたがってルールの数の大幅な増大をもたらし得る。複数のポリシーを同時にサポートする能力を実証して、ワーキングセットのサイズに対するそのことの影響を測定するために、合成ポリシー(「合成」)が実験を通じて実装され、合成ポリシーは上で説明されたすべての4つのポリシーを備える。合成ポリシーは、以下でさらに詳細に説明される、サポートされるポリシー作業負荷の種類を表す。図4Aおよび図20において見られるように、合成ポリシーは、(i)空間的および時間的なメモリ安全性、(ii)テイント追跡、(iii)制御フロー整合性、および(iv)コードとデータの分離というポリシーを同時に実施する。

10

【 0 0 5 4 】

大半のポリシーは、適切な論理を選択するためにオペコード上にディスパッチする。NXD+NWCのような一部のポリシーは、動作が許容されるかどうかを確認するだけである。他のポリシーはデータ構造を調べることがある(たとえば、CFIポリシーは許容される間接的な呼出しありおよびリターンidのグラフを調べる)。メモリ安全性は、アドレスの色(すなわち、ポインタの色)とメモリ領域の色との間で等しさを確認する。テイント追跡は、入力タグを組み合わせることによって未使用の結果タグを計算する(アルゴリズム1)。大きなデータ構造にアクセスしなければならないポリシー(CFI)、または大きな集団にわたって正規化しなければならないポリシー(テイント追跡、合成)は、オンチップキャッシュにおいてミスするであろう多数のメモリアクセスを行い、DRAMに向かうことがある。ベンチマークのすべてにわたって平均すると、NXD+NWCではミスをサービスするのに30サイクルを必要とし、メモリ安全性では60サイクルを必要とし、CFIでは85サイクルを必要とし、テイント追跡では500サイクルを必要とし、合成では800サイクルを必要とした。

20

【 0 0 5 5 】

動作が許容されないとポリシーミスハンドラが判定する場合、ポリシーミスハンドラは、適切なセキュリティフォルトハンドラを呼び出す。このフォルトハンドラが何をするかは、ランタイムシステムおよびポリシー次第である。通常は、フォルトハンドラは攻撃プロセスをシャットダウンするが、いくつかの場合には、代わりに適切な「安全値」を返すことがある。UNIX(登録商標)型のオペレーティングシステムを用いた増分的な展開のために、想定されるポリシーはプロセスごとに適用され、各プロセスがポリシーの異なる集合を得ることを可能にする。プロセスごとに適用されるものとして記述されることは限定的ではなく、むしろ例示的であり、当業者はこのことを認識する。このことはまた、プロセスのアドレス空間への、タグ、ルール、およびミスハンドリングのサポートを可能にし、OSレベルのコンテキスト切替えの必要をなくす。長期的には、OSを保護するためにPUMPポリシーが使用できるかも知れない。

30

【 0 0 5 6 】

以下は、ランタイム、エネルギー、面積、および電力のオーバーヘッドを測定するための評価方法を詳述し、図1に示される128bのワード(64bのペイロードおよび64bのタグ)と修正されたパイプラインプロセッサ12とを使用して、PUMPハードウェアおよびソフトウェアの単純な実装形態に対してその評価方法を適用する。最適化された実装形態が、(ベースラインのプロセッサに対する相対的な)オーバーヘッドが最終的に所望されるバージョンであるとしても、簡単なPUMPの実装形態をまず説明して測定することが有用である。簡単な実装形態は、より洗練されたバージョンを得る前に重要な機構の基本的なバージョンを詳述するので、簡単な実装形態と最適化された実装形態の両方が説明される。

40

【 0 0 5 7 】

PUMPの物理的なリソースに対する影響を推定するために、メモリコストに主に注目し、それは、簡単なRISCプロセッサおよびPUMPハードウェア拡張においてはメモリが支配的な面積とエネルギーの消費者であるからである。32nmの低動作電力(LOP)プロセスがL1

50

メモリ(図1参照)のために考慮され、低スタンバイ電力(LSTP)がL2メモリのために考慮され、メインメモリおよびプロセッサのオンチップメモリの面積、アクセス時間、アクセス当たりのエネルギー、および静的(漏れ)電力をモデル化するためにCACTI 6.5を使用する。

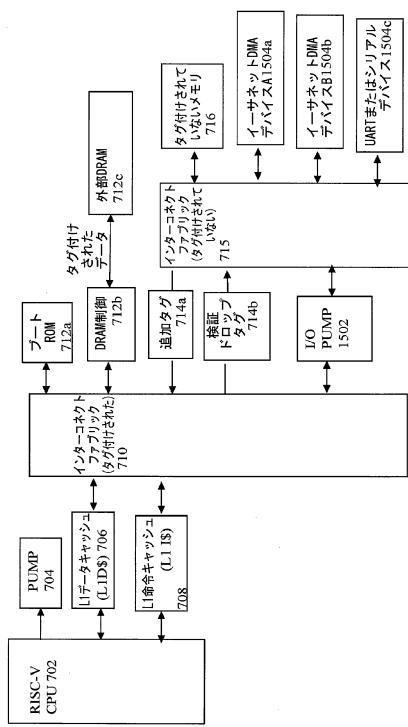

#### 【0058】

ベースラインのプロセッサ(PUMPなし)はデータおよび命令のための別個の64KBのL1キャッシュと、統合された512KBのL2キャッシュとを有する。遅延が最適化されたL1キャッシュおよびエネルギーが最適化されたL2キャッシュが使用された。すべてのキャッシュがライトバックの規律を使用する。ベースラインのL1キャッシュは880ps前後のレイテンシを有し、1サイクルで結果を返すことができクロックを1nsに設定できると想定され、現代の埋め込みプロセッサおよび携帯電話プロセッサに匹敵する1GHzのサイクルの目標を与える。このプロセッサに対するパラメータが、図16の表3に提示される。

10

#### 【0059】

PUMPルールキャッシュ10のハードウェア実装形態の一実施形態は、段階14、16、20の中のすべてのアーキテクチャ状態をタグを用いて延ばすこと、およびPUMPルールキャッシュをプロセッサ12に追加することという、2つの部分を含み得る。オンチップメモリの中の各々の64bのワードを64bのタグを用いて延ばすことは、アクセス当たりのワードの面積およびエネルギーを増やし、アクセスのレイテンシを悪化させる。これはL2キャッシュでは許容可能である可能性があり、L2キャッシュはすでに多サイクルのアクセスレイテンシを有し、すべてのサイクルで使用されるとは限らない。しかし、L1キャッシュ(図1参照)にアクセスするためにレイテンシの余計なサイクルを追加することは、パイプラインにおけるストールにつながり得る。これを避けるために、この簡単な実装形態では、L1キャッシュの実質的な容量はベースラインの設計における容量の半分まで減らされ、次いでタグを追加する。このことは、同じ単一サイクルのアクセス権をL1キャッシュに与えるが、ミスの増大により性能を低下させ得る。

20

#### 【0060】

本明細書の技法に従ったある実施形態では、PUMPルールキャッシュ10は、従来のキャッシュアドレス鍵(アドレス幅より短い)と比較して長い一致キー(5個のポインタサイズのタグ+命令オペコード、すなわち328b)を利用し、128bの結果を返す。一実施形態では、完全に連想型のL1ルールキャッシュが使用され得るが、大きなエネルギーおよび遅延につながる(図16の表3参照)。代替として、本明細書の技法に従ったある実施形態は、図22に示されるように、4つのハッシュ関数から着想を得たマルチハッシュキャッシュ方式を利用することができる。L1ルールキャッシュは、単一のサイクルで結果を產生し、2番目のサイクルにおいて誤ヒットを確認するように設計されるが、L2ルールキャッシュは低エネルギーのために設計され、多サイクルのアクセスレイテンシを与える。やはり、図16の表3は、簡単な実装形態において使用される1024エントリーのL1ルールキャッシュおよび4096エントリーのL2ルールキャッシュのためのパラメータを示す。これらのキャッシュが容量に達するとき、簡単なfirst-in-first-out(FIFO)置換ポリシーが使用され、これは現在の作業負荷に対しては実践的によく機能するように見える(ここではFIFOはLRUの6%以内である)。

30

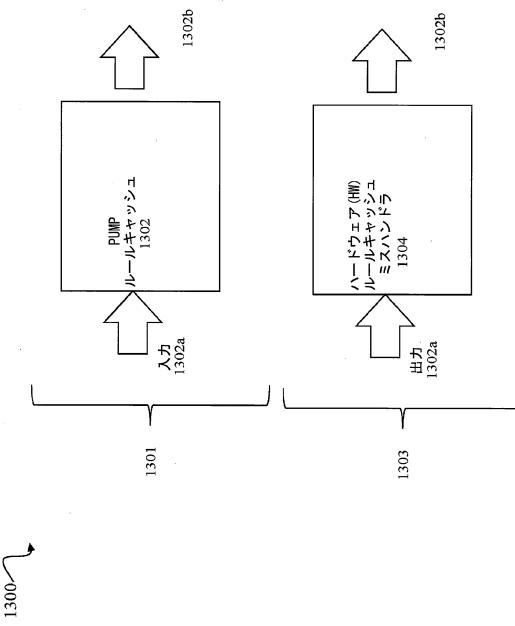

#### 【0061】

図2を参照すると、PUMPの性能への影響の推定は、ISA、PUMP、およびアドレストレースシミュレータの組合せを特定する。gem5シミュレータ24は、64ビットのAlphaベースラインISAでのSPEC CPU2006プログラム(gem5が失敗するxalancbmkおよびtontoを除く)のための命令トレースを生成する。各プログラムは、上で列挙された4つのポリシーおよび1Bの命令のウォームアップ期間のための合成ポリシーの各々についてシミュレートし、次いで、次の500Mの命令を評価する。gem5シミュレータ24では、各ベンチマークは、タグまたはポリシーなしでベースラインプロセッサ上で実行される。得られる命令トレース26が次いで、各命令のためのメタデータ計算を実行するPUMPシミュレータ28を通じて実行される。この「段階的な」シミュレーション戦略は、PUMPの結果によりプログラムの制御フローがそのベースライン実行から逸脱してはならない、フェイルストップ

40

50

ポリシーに対しては正確である。アドレストレースシミュレーションは、高度にパイプライン化されout-of-orderのプロセッサに対しては不正確であり得るが、簡単なin-orderの5段階および6段階のパイプラインに対しては極めて正確である。ベースライン構成では、gem5命令のシミュレーションおよびアドレストレースの生成30と、それに続く、アドレスシミュレータ32におけるカスタムのアドレストレースシミュレーションおよびアカウンティングは、gem5のサイクルアキュレートシミュレーションの1.2%の範囲内にあった。

#### 【 0 0 6 2 】

PUMPシミュレータ28は、各ポリシーを実施するためのミスハンドラコード(Cで書かれている)を含み、メタデータタグは、ポリシーに応じて初期メモリ上に割り当てられる。PUMPシミュレータ28は、PUMP10ルールキャッシュにおけるアクセスパターンを捉え、関連するランタイムおよびエネルギーコストを推定して、L2ルールキャッシュにアクセスするのに必要なより長い待機サイクルを考慮することを可能にする。ミスハンドラコードを有するPUMPシミュレータ28もプロセッサ上で実行するので、gem5でのミスハンドラのための別個のシミュレーションがその動的な挙動を捉える。ミスハンドラコードはデータおよび命令キャッシュに影響する可能性があるので、ユーザコードとミスハンドラコードの両方からの適切にインターリーブされたメモリアクセスを含むマージされたアドレストレースが作成され、これは、メモリシステムの性能への影響を推定するための最終的なアドレストレースシミュレーションのために使用される。

#### 【 0 0 6 3 】

以下の段落では、簡単なPUMPの実装形態の評価が、PUMPなしのベースラインと比較して与えられる。

#### 【 0 0 6 4 】

評価の1つの点として、ベースラインプロセッサに加わるPUMP10の全体的な面積オーバーヘッドは190%であることに留意されたい(図16の表3参照)。この面積オーバーヘッドの主要な部分(110%)は、PUMP10のルールキャッシュに由来する。統合されたL2キャッシュが、残りの面積オーバーヘッドの大半に寄与する。L1 D/Iキャッシュは概ね同じまであり、それはそれらの実質的な容量が半分になるからである。この大きなメモリ面積オーバーヘッドは静的電力を概ね3倍にし、これはエネルギーオーバーヘッドの24%に相当する。

#### 【 0 0 6 5 】

評価の別の点はランタイムオーバーヘッドに関する。大半のベンチマーク上でのすべての単一ポリシーに対して、この簡単な実装形態でも平均ランタイムオーバーヘッドは10%に過ぎず(図3Aおよび図3B参照;ボックスプロットを読むために、棒は中央値であり、ボックスは上位4分の1から下位4分の1(中央の50%のケース)をカバーし、点は各々の個々のデータ点を表し、ひげは外れ値( $1.5 \times$ それぞれの4分位数を超える)を除く全範囲を示す)、追加のDRAMトラフィックに由来する支配的なオーバーヘッドが、プロセッサとの間でタグビットを転送するために必要とされる。メモリ安全性ポリシー(図3Aおよび図3B)について、大きなミスハンドラオーバーヘッドを示す少数のベンチマークがあり、新しく割り振られるメモリブロック上での強制的なミスが原因で全体のオーバーヘッドを40~50%に押し上げている。合成ポリシーランタイム(図では「CPI」または「CPIオーバーヘッド」と名付けられている)について、ベンチマークのうちの5つでミスハンドラにおけるオーバーヘッドが非常に大きく(図4A参照)、最悪の場合にはGemsFTDTにおいて780%に迫り、幾何平均が50%に達する。図4Bに示される合成ポリシーエネルギー(図では「EPI」または「EPIオーバーヘッド」と名付けられている)について、ベンチマークのうちの3つ(すなわち、GemsFTDT、astar、omnetpp)でミスハンドラにおけるオーバーヘッドが非常に大きく、最悪の場合には、GemsFTDTにおいて1600%、astarにおいて600%、omnetppにおいて520%に迫る。

#### 【 0 0 6 6 】

(1)最終レベルのルールキャッシュミスを解決するために必要とされる大量のサイクル(1つの1つの構成要素のミスハンドラが調べられなければならないので)、および(2)ルールの数

の爆発という2つの要因がこのオーバーヘッドに寄与しており、ルールの数の爆発は、ワーキングセットのサイズを大きくし、ルールキャッシュミスレートを高める。最悪の場合、固有の合成タグの数は、各構成要素ポリシーにおける固有のタグの積であり得る。しかしながら、全体のルールは、最大の単一ポリシーであるメモリ安全性よりも、3倍から5倍の係数で増大する。

#### 【 0 0 6 7 】

評価の別の点はエネルギーオーバーヘッドである。より幅広のワードが原因でより多数のビットを動かすことと、ミスハンドラコードが原因でより多数の命令を実行することの両方が、エネルギーオーバーヘッドに寄与し、単一ポリシーと合成ポリシーの両方に影響する(図3Bおよび図4B)。CFIおよびメモリ安全性ポリシーは、またしたがって合成ポリシーも大きなデータ構造にアクセスし、これはしばしばエネルギー的に高価なDRAMアクセスを必要とする。最悪の場合のエネルギーオーバーヘッドは単一ポリシーに対しては400%に迫り、合成ポリシーに対しては約1600%であり、幾何平均オーバーヘッドは220%前後である。

10

#### 【 0 0 6 8 】

多くのプラットフォーム設計では、最悪の場合の電力、または等価的にはサイクル当たりのエネルギーが、制約になる。この電力上限は、プラットフォームが電池から引き出すことができる最大の電流、または、周囲の冷却とともにモバイルデバイスと有線デバイスのいずれかにおける最大の持続する動作温度により決まり得る。図4Cは、簡単な実装形態が最大電力上限を76%上げ、ベースライン実装形態と簡単なPUMP実装形態の両方においてbmが最大の電力を駆動することを示す。この電力上限の上昇は最悪の場合のエネルギーオーバーヘッドより小さく、それは、一部のベンチマークがそれらの消費する余剰のエネルギーよりも大きく速度を下げるこれが一部には原因であり、また、エネルギーオーバーヘッドの大きいベンチマークがベースライン設計においてサイクル当たり最小の絶対的なエネルギーを消費するベンチマークであるこれが一部には原因であることに留意されたい。通常、これらのエネルギー効率の高いプログラムのデータワーキングセットはオンチップキャッシュに収まるので、これらのプログラムがDRAMアクセスのより高いコストを払うことはほとんどない。

20

#### 【 0 0 6 9 】

上で説明された前述の実装形態を組み込む実施形態は、大半のベンチマークで適当な性能を達成し、一部のベンチマークでの合成ポリシーに対するランタイムオーバーヘッドおよびすべてのポリシーおよびベンチマークでのエネルギーと電力のオーバーヘッドは、許容不可能なほど高いよう見える。これらのオーバーヘッドに対処するために、本明細書の技法に従ったある実施形態に、一連の目標を定めたマイクロアーキテクチャ最適化が導入され、また組み込まれ得る。図17の表4では、これらの最適化が、PUMP構成要素と関連付けられるアーキテクチャパラメータの、全体的なコストに対する影響のために調べられる。PUMPルールキャッシュの実質的な容量を増やすために同一のルールを伴うオペコードのグループ化が使用され、DRAM転送の遅延およびエネルギーを減らすためにタグ圧縮が使用され、オンチップメモリにおける面積およびエネルギーを減らすために短いタグが使用され、ミスハンドラにおけるオーバーヘッドを減らすために統合構成要素ポリシー(UCP)および合成タグ(CTAG)キャッシュが使用される。

30

#### 【 0 0 7 0 】

ここで説明されるのは、本明細書の技法に従ったある実施形態において使用され得るような「オペグループ」である。実践的なポリシーでは、いくつかのオペコードに対して類似するルールを定義するのは一般的である。たとえば、テント追跡ポリシーでは、加算および減算の命令のためのルールは同一である(図19のアルゴリズム1参照)。しかしながら、簡単な実装形態では、これらのルールは、ルールキャッシュの中の別個のエントリーを占有する。この観察に基づいて、同じルールを伴う命令動作コード(「オペコード」)が「オペグループ」としてグループ化され、必要なルールの数を減らす。どのオペコードと一緒にグループ化できるかはポリシーに依存するので、ルールキャッシュのルックアップの

40

50

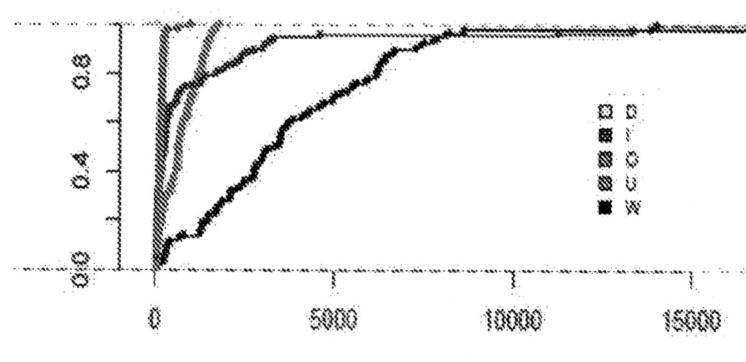

前にもオペコードをオペグループに変換するために、「don't-care」SRAMが実行段階18(図1)において拡張される。合成ポリシーに対して、300個を超えるAlphaオペコードが14個のオペグループに減らされ、ルールの総数は、1/1.1～1/6、平均で1/1.5に減る(図5AはすべてのSPECベンチマークにわたってこの効果を測定する)。このことは、シリコン面積における所与の投資に対するルールキャッシュの容量を実質的に増やす。オペグループはまた、強制的なミスの数を減らし、それは、グループの中の単一の命令でのミスが、グループの中の1つ1つの命令オペコードに適用されるルールをインストールするからである。図5Bは、オペグループ化がある場合とない場合の、合成ポリシーに対する様々なL1ルールキャッシュサイズのためのすべてのSPECベンチマークにわたるミスレートを要約している。図5Bは、ミスレートの範囲と平均の両方がオペグループ化により低減することを示している。具体的には、オペグループ最適化の後の1024エントリーのルールキャッシュは、オペグループ最適化なしの4096エントリーのルールキャッシュよりミスレートが低い。より低いミスレートは当然、ミスハンドラにおいて消費される時間およびエネルギーを減らし(図12Aおよび図12B参照)、より小さいルールキャッシュは面積およびエネルギーを直接減らす。

#### 【0071】

本明細書の技法に従ったある実施形態は、ここで説明されるメインメモリタグ圧縮を利用し得る。64bのワードに64bのタグを使用すると、オフチップメモリトラフィックが2倍になるので、関連するエネルギーがほぼ2倍になる。しかし、通常、タグは空間的な局所性を示し、多くの近くのワードは同じタグを有する。たとえば、図6Aは、合成ポリシーについての、gccベンチマークに対する各DRAM転送のための固有のタグの分布をプロットしたものであり、大半のワードが同じタグを有し、8ワードのキャッシュラインのDRAM転送当たり平均で約1.14個の固有のタグしかないことを示している。この空間的なタグの局所性は、オフチップメモリとの間で転送されなければならないタグビットを圧縮するために利用される。データはキャッシュラインにおいて転送されるので、キャッシュラインがこの圧縮のために基礎として使用される。アドレス指定を簡単なままにするために、キャッシュライン当たり128Bがメインメモリにおいて割り振られる。

#### 【0072】

しかしながら、図6Bに示されるように、128bのタグ付けされたワードを直接記憶するのではなく、8個の64bのワード(ペイロード)が記憶され、次いで8個の4bのインデックスが記憶され、次いで最大で8個の60bのタグが記憶される。インデックスは、60bのタグのいずれが関連するワードに付随するかを特定する。インデックスを収容するためにタグは60bに調整されるが、これはポインタとしてのタグの使用を損なうものではなく、バイトアドレス指定および16B(2つの64bのワード)の揃えられたメタデータ構造を仮定すると、64bのポインタの下側の4bは0として埋められ得る。結果として、インデックスのうちの4Bを転送した後で、残っていることは、キャッシュラインにおいて固有の7.5Bのタグを転送する必要だけである。たとえば、同じタグがキャッシュラインの中のすべてのワードにより使用される場合、1回目の読み取りにおいて64B+4B=68Bの転送があり、そして2回目の読み取りにおいて8Bの転送があり、全体で128Bではなく76Bである。4bのインデックスは、直接インデックスまたは特別値のいずれかであり得る。特別インデックス値はデフォルトタグを表すように定義されるので、この場合にはタグを何ら転送する必要がない。この方式でタグを圧縮することによって、DRAM転送当たりの平均エネルギーオーバーヘッドは110%から15%に減る。

#### 【0073】

上で提示された圧縮方式は、たとえば、簡潔性と、オフチップメモリエネルギーを減らすことに対する有効性との組合せにより、本明細書の技法に従った実施形態において利用され得る。マルチレベルタグページテーブル、可変粒度のTLB構造、およびレンジキャッシュを含む、細粒度のメモリのタグ付けのための追加の代替的な賢い方式が存在し、これらも、本明細書の技法に従ったある実施形態においてDRAMのフットプリントを減らすために使用され得ることを、当業者は明確に認識する。

## 【0074】

ここで説明されるのは、本明細書の技法に従ったある実施形態において、タグ変換がどのように実行され得るかである。図1を再び参照すると、各々のキャッシュされたルールは456bの幅であるので、簡単なPUMPルールキャッシュは大きい(110%の面積を加える)。PUMP10をサポートすることはまた、64bのタグを用いてベースラインオンチップメモリ(RFおよびL1/L2キャッシュ)を拡張することを必要とした。ここで各々の64bのワードに対して完全な64b(または60b)のタグを使用することは、面積およびエネルギーの重いオーバーヘッドを招く。しかしながら、64KBのL1-D\$は8192ワードしか保持しないので、最大でも8192個の固有のタグしか保持しない。64KBのL1-I\$とともに、L1メモリサブシステムにおいて、最大で16384個の固有のタグがあることがあり、これらはわずか14bのタグで表すことができ、システムにおける遅延、面積、エネルギー、および電力を減らす。キャッシュ(L1,L2)は時間的な局所性を利用するために存在し、この観察は、面積およびエネルギーを減らすために局所性を利用できることを示唆している。タグビットが14bに減らされる場合、PUMPルールキャッシュ一致キーは328bから78bに減らされる。

10

## 【0075】

完全なポインタサイズのタグのフレキシビリティを失うことなく前述の節約の利点を得るために、幅の異なるタグが、異なるオンチップメモリサブシステムのために使用され、必要に応じてそれらのオンチップメモリサブシステムの間で変換し得る。たとえば、L1メモリにおいて12bのタグを使用し、L2メモリにおいて16bのタグを使用することができる。図7Aは、L1メモリサブシステムとL2メモリサブシステムとの間で実行され得るようなタグ変換を詳述する。L2キャッシュ34からL1キャッシュ36にワードを動かすことは、ワードの16bのタグを対応する12bタグに変換することを必要とし、必要であれば新しい関連付けを作成する。L2タグのためのL1マッピングがあるかどうかを示す余剰なビットを伴う、L2タグからL1タグへの変換のための簡単なSRAM38。図7Bは、L1タグをアドレスとして使用するSRAM39のルックアップとともに実行される、(ライトバックまたはL2ルックアップに際する)L1タグ40からL2タグ42への変換を詳述する。同様の変換は、60bのメインメモリタグと16bのL2タグとの間で発生する。

20

## 【0076】

長いタグが長から短への変換テーブルの中にはないとき、新しい短いタグが割り振られ、場合によっては、もはや使用されていない以前に割り振られた短いタグを回収する。ガベージコレクションおよびタグ使用カウントを含む、短いタグをいつ回収できるかを判定するための、探究すべきリッチな設計空間がある。簡潔にするために、短いタグが順番に割り振られ、短いタグ空間が使い果たされたときに所与のレベルを超えるすべてのキャッシュ(命令、データ、およびPUMP)をフラッシュし、特定の短いタグがいつ回収可能かを追跡する必要をなくす。キャッシュは、キャッシュのフラッシュを安価にする適切な技法を用いて設計され得る。たとえば、本明細書の技法に従ったある実施形態では、たとえば、参照によって本明細書に組み込まれる、K. Mai、R. Ho、E. Alon、D. Liu、Y. Kim、D. Patti、およびM. Horowitz、Architecture and Circuit Techniques for a 1.1GHz 16-kb Reconfigurable Memory in 0.18um-CMOS、IEEE J. Solid-State Circuits、40(1):261-275、2005年1月において説明され、当技術分野で知られているものなどの、軽量なgang clearを用いてすべてのキャッシュが設計され得る。

30

## 【0077】

表3(図16に再現される)と比較すると、各L1ルールキャッシュのアクセスには51pJかかり、本明細書の技法は8bのL1タグでは10pJへの、または16bのL1タグでは18pJへの低減をもたらし、エネルギーのスケーリングはこれらの点の間のタグの長さに対して線形である。L1命令およびデータキャッシュに対するエネルギーの影響は小さい。同様に、16bのL2タグでは、L2 PUMPアクセスには、64bのタグの場合の173pJから減少して120pJかかる。L1タグを小さくすることは、L1キャッシュの容量を復元することも可能にする。12bのタグでは、全容量(76KB、実質的には64KB)のキャッシュが单一サイクルのタイミング要件を満たし、低減されたL1キャッシュの容量が招く簡単な実装形態の性能悪化を減

40

50

らす。結果として、L1タグ長の探究は12ビット以下に限定される。さらに短いタグはエネルギーを減らすが、フラッシュの頻度も増やす。

【0078】

図8Aおよび図8Bは、L1タグ長の増大とともにフラッシュがどのように減少するか、ならびにL1ルールキャッシュミスレートに対する影響を示す。

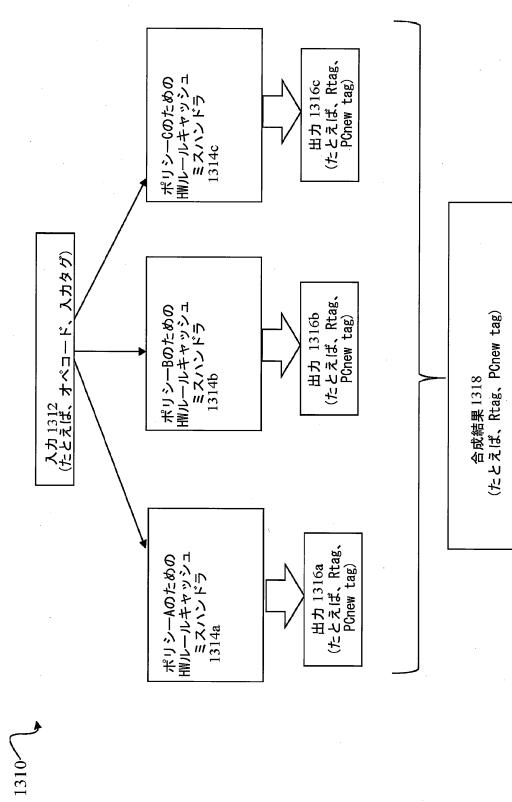

【0079】

ここで説明されるのは、ミスハンドラアクセラレーションに関連して使用され得る様々な技法である。本明細書の技法に従ったある実施形態は、4つのポリシーを单一の合成ポリシーへと合成し得る。図20を参照すると、アルゴリズム2において、Nポリシーのミスハンドラの各呼出しはタグのタプルを分解しなければならず、合成ポリシーに必要なルールはルールキャッシュミスレートを上げ、これらは図9Aにおいて特定される。テイント追跡およびCFIポリシーが個々に低いミスレートを有するとしても、メモリ安全性ポリシーからのより高いミスレートは、合成ポリシーのミスレートも高くする。個々のポリシーのより低いミスレートは、合成ルールがキャッシュ可能ではなくても、個々のポリシーの結果がキャッシュ可能であり得ることを示唆する。

10

【0080】

図23に示されるものなどのPUMPマイクロアーキテクチャの様々な態様に関連して、合成ポリシーミスハンドリングを最適化するためにハードウェア構造が利用され得る。本明細書の技法に従ったある実施形態は、最新の構成要素ポリシーの結果がキャッシュされる、統合構成要素ポリシー(UCP;図21のアルゴリズム3参照)キャッシュ(UCP\$)を利用し得る。そのような実施形態では、合成ポリシーのための一般的なミスハンドラは、構成要素ポリシーを解決しながらこのキャッシュにおいてルックアップを実行するように修正される(たとえば、図21のアルゴリズム3、行3などを参照)。構成要素ポリシーに対するこのキャッシュミスのとき、そのポリシー計算がソフトウェアにおいて実行される(かつ結果をこのキャッシュに挿入する)。

20

【0081】

図24にも示されるように、UCPキャッシュは、追加のポリシー識別子フィールドとともに、普通のPUMPルールキャッシュと同じハードウェア組織を用いて実装され得る。FIFO置換ポリシーは、このキャッシュのために使用され得るが、構成要素ポリシーの再計算コストなどの尺度を使用して空間を優先順位付けることによってより良い結果を達成することが可能であり得る。適度な容量で、このキャッシュは大半のポリシー再計算を除去する(図9B;メモリ安全性に対する低ヒットレートは新しいメモリ割振りと関連付けられる強制的なミスが原因である)。結果として、ミスハンドラサイクルの平均の数は、大半の難しいベンチマークに対して1/5に減る(図9E)。必要な合成ルールは少数の構成要素ポリシールールの積であり得るので、L2 PUMPにおいてミスがあるとき、UCPキャッシュにおいて1つ1つのポリシーがヒットすることが可能である。GemsFDTDでは、3つ以上の構成要素ポリシーが、約96%の時間においてヒットした。

30

【0082】

図23および図24にも含まれるように、キャッシュは、結果タグのタプルをその標準的な合成結果タグに変換するために追加され得る。前述のキャッシュは合成タグ(CTAG)キャッシュ(CTAG\$)と呼ばれることがあり、いくつかの構成要素ポリシールールが結果タグの同じタプルを返すことは一般的であるので、CTAG\$は効果的である(図9D)。たとえば、多くの場合、結果タグが異なっていても、Pctagは同じである。さらに、多くの異なるルール入力は同じ出力をもたらし得る。たとえば、テイント追跡では集合の和集合が実行され、多くの異なる和集合が同じ結果を有する。たとえば、(Blue,{A,B,C})が、{A} {B,C}と{A,B} {B,C}の両方の結果(テイント追跡)をBlueスロット(メモリ安全性)に書き込むための、合成の答えである。FIFO置換ポリシーがこのキャッシュに使用される。CTAGキャッシュは、平均のミスハンドラサイクルを1/2という別の割合に減らす(図9E参照)。

40

【0083】

まとめると、2048エントリーのUCPキャッシュおよび512エントリーのCTAGキャッシュ

50

は、各L2ルールキャッシュミスで費やされる平均時間を800サイクルから80サイクルに減らす。

#### 【 0 0 8 4 】

本明細書の技法に従ったある実施形態はまた、ルールを含むキャッシュのうちの1つまたは複数に記憶される1つまたは複数のルールをプリフェッチすることによって、性能を改善し得る。したがって、近い将来必要であり得る事前計算ルールを用いて強制ミスレートを下げることが追加で可能である。ある事例は、メモリ安全性ルールに対して高い値を有する。たとえば、新しいメモリタグが割り振られると、新しいルールがそのタグのために必要とされる(初期化(1)、オフセットをポインタに追加し移動する(3)、スカラーロード(1)、スカラー記憶(2))。その結果、これらのルールのすべてが、UCPキャッシュに一度に追加され得る。単一ポリシーのメモリ安全性の場合、ルールはルールキャッシュに直接追加され得る。これは、メモリ安全性ミスハンドラの呼出しの回数を1/2に減らす。

10

#### 【 0 0 8 5 】

全体的な評価に関して、かつ図11Aを参照すると、アーキテクチャパラメータはある特定のコストに単調に影響し、エネルギー、遅延、および面積の間のトレードオフをもたらすが、単一のコスト基準の中での最小値を定義しない。タグビットが十分小さくなると、L1 D/Iキャッシュをベースラインの容量に復元できるので、ベースラインがL1タグ長を探究するための上限として採用されるが、その点を超えると、性能への影響が小さい状態でタグ長の減少がエネルギーを減らすという、閾値の効果がある。

20

#### 【 0 0 8 6 】

図11Bは、タグ長を減らすことが大半のベンチマークプログラム(たとえば、leslie3d、mcf)に対する支配的なエネルギー効果であることを示しており、少数のプログラム(たとえば、GemsFDTD、gcc)がUCPキャッシュ容量を増やすことによる等しいまたはより大きい利益を示している。他のコストの問題を無視すると、エネルギーを減らすために、大きなミスハンドラキャッシュおよび少ないタグビットが選択される。ランタイムオーバーヘッド(図11A参照)も、より大きなミスハンドラキャッシュにより最小限にされるが、より少ないタグビットではなくより多くのタグビットから利益を得る(たとえば、GemsFDTD、gcc)。この利益の大きさは、ベンチマークおよびポリシーにより変化する。すべてのベンチマークにわたって、10bのL1タグを超える利益はSPEC CPU2006ベンチマークに対して小さいので、10bがエネルギーと遅延との間の妥協点として使用され、探究されるアーキテクチャパラメータの空間内の最小エネルギーレベルに近づけながら面積オーバーヘッドを減らすために、2048エントリーのUCPキャッシュおよび512エントリーのCTAGキャッシュを使用する。

30

#### 【 0 0 8 7 】

図12Aおよび図12Bは、最適化を適用することのランタイムオーバーヘッドおよびエネルギーオーバーヘッドに対する全体的な影響を示す。一部のベンチマークに対しては1つ1つの最適化が支配的であり(たとえば、astarに対するオペグループ、lsmに対するDRAMタグ圧縮、h264refに対する短いタグ、GemsFDTDに対するミスハンドラアクセラレーション)、一部のベンチマークはすべての最適化からの利益を受け(たとえば、gcc)、各最適化は連続して、あるボトルネックを取り除くと次のボトルネックに曝される。ベンチマークからの異なる挙動は、以下で詳述されるベースライン特性に従う。

40

#### 【 0 0 8 8 】

局所性の低いアプリケーションは、メインメモリのトラフィックが大きいことにより、DRAMにより決まるベースラインのエネルギーおよび性能を有する。そのようなベンチマーク(たとえば、lsm)におけるオーバーヘッドは、DRAMオーバーヘッドの傾向があるので、DRAMオーバーヘッドの低減がランタイムオーバーヘッドおよびエネルギーオーバーヘッドに直接影響する。より局所性の大きいアプリケーションは、ベースライン構成においてより高速であり、より少ないエネルギーを消費し、DRAMオーバーヘッドの影響をより受けず、結果として、これらのベンチマークは、低減されたL1容量ならびにL1 D/Iキャッシュおよびルールキャッシュにおけるタグエネルギーの影響をより大きく受ける。DRAM最

50

適化は、これらのアプリケーションに対する影響がより小さいが、短いタグを使用することが、エネルギーに対する大きな影響を有し、L1 D/Iキャッシュ容量の悪化をなくす(たとえば、h264ref)。

【0089】

重い動的なメモリ割振りを伴うベンチマークは、新しく作成されるタグがキャッシュにインストールされなければならないので強制的なミスがあることにより、より高いL2ルールキャッシュミスレートを有する。これは、簡単な実装形態におけるいくつかのベンチマーク(GemsFDTD、omnetpp)に対するオーバーヘッドを高くする。本明細書で説明されるようなミスハンドラ最適化は、そのようなミスの一般的な場合のコストを減らし、オペグループ最適化は、容量ミスレートを下げる。簡単な実装形態では、GemsFDTDでは、200個の命令ごとにL2ルールキャッシュミスがあり、その780%のランタイムオーバーヘッドの大部分の原因である各ミスをサービスするために800サイクルを要する(図4A参照)。最適化により、GemsFDTDベンチマークは、400個の命令ごとにL2ルールキャッシュミスをサービスし、ミス当たり平均で140サイクルしかかからず、ランタイムオーバーヘッドを約85%に減らす(図10A参照)。

10

【0090】

全体的に、これらの最適化は、メモリ割振りの大きいGemsFDTDおよびomnetppを除くすべてのベンチマークに対して、ランタイムオーバーヘッドを10%未満にする(図10A参照)。平均のエネルギーオーバーヘッドは60%に近く、4つのベンチマークだけが80%を超える(図10B参照)。

20

【0091】

例示すると、PUMPの性能への影響は、4つの異なるポリシーの合成を使用して測定されることがある(図14の表1参照)、これらのポリシーは、PUMPに様々な方法でストレスを与え、(1)メモリの中のデータとコードを区別するためにタグを使用し、簡単なコードインジェクション攻撃に対する保護を提供する、非実行可能データおよび非書き込み可能コード(NXD+NWC)ポリシー、(2)ヒープに割り振られたメモリにおけるすべての空間的および時間的な侵害を検出し、実質的に無限の(260個の)数の色(「ティントマーク」)まで拡張する、メモリ安全性ポリシー、(3)間接的な制御の移転をプログラムの制御フローグラフの中の許容されるエッジのみに制約し、リターン指向プログラミング型の攻撃を防ぐ、制御フロー整合性(CFI)ポリシー(攻撃に対する脆弱性がある可能性がある粗粒度の近似ではなく、細粒度のCFIを実施する)、(4)各ワードが複数のソース(ライブラリおよびI/Oストリーム)により同時にティントされる可能性があり得る、細粒度のティント追跡ポリシー(一般化)という、一連のセキュリティ属性を示す。本明細書の他の箇所で述べられるように、これらは、その保護能力が文献において確立されているよく知られているポリシーであり、本明細書の説明は、PUMPを使用してポリシーを実施することの性能への影響を測定して減らすことに注目し得る。NXD+NWCを除き、これらのポリシーの各々は、基本的に無限の数の固有のアイテムを区別し、対照的に、メタデータビットの数が限られている解決法は、せいぜい、ひどく簡略化された近似しかサポートすることができない。上で述べられたように、PUMPの簡単な直接の実装形態は高価であり得る。たとえば、ポイントサイズ(64b)のタグを64bのワードに追加すると、システムにおけるすべてのメモリのサイズおよびエネルギー使用量が少なくとも2倍になり、これに加えて、ルールキャッシュが面積およびエネルギーを追加する。この簡単な実装形態では、測定される面積オーバーヘッドは約190%であり、幾何平均のエネルギーオーバーヘッドは約220%であり、その上、ランタイムオーバーヘッドは一部のアプリケーションでは期待外れである(300%を超える)。そのような大きなオーバーヘッドは、それが行うことのできる最良のことであっても、採用を妨げるであろう。

30

【0092】

本明細書で説明されるものなどのマイクロアーキテクチャ最適化が、電力上限に対する影響を10%に減らすために、本明細書の技法に従ったある実施形態に含まれることがあり(図10C参照)、これは、最適化されたPUMPがプラットフォームの動作エンベロープにほとん

40

50

ど影響しないことを示唆する。DRAM圧縮は1bmに対するエネルギーオーバーヘッドを20%に減らす。速度も9%下げるのに、電力要件は10%しか増えない。

#### 【0093】

最適化された設計の面積オーバーヘッドは、簡単な設計の190%(たとえば、図16の表3参照)と比較して、110%前後である(たとえば、図18の表5参照)。短いタグはL1キャッシュおよびL2キャッシュの面積を大きく減らし(今やベースラインに5%追加するだけである)、ルールキャッシュの面積を大きく減らす(26%しか追加しない)。反対に、最適化された設計は、ランタイムオーバーヘッドおよびエネルギーオーバーヘッドを減らすためにいくつかの面積を費やす。UCPキャッシュおよびCTAGキャッシュは33%の面積オーバーヘッドを追加するが、短いタグのための変換メモリ(L1とL2の両方)は別の46%を追加する。これらの追加のハードウェア構造は面積を追加するが、ネットでのエネルギー低減をもたらし、それは、それらが頻繁にはアクセスされず、UCPキャッシュおよびCTAGキャッシュもミスハンドラサイクルをかなり減らすからである。

10

#### 【0094】

本明細書で説明されるようなモデルおよび最適化の1つの目標は、同時に実施される追加のポリシーをある実施形態が追加することを、比較的簡単にすることである。簡単なPUM P設計での合成ポリシーは、ミスハンドラランタイムの大きな増大により、いくつかのベンチマークでは付加的なものよりも大きなコストを招いたが、これらはミスハンドラ最適化により減らされる。

20

#### 【0095】

図13A(CPIオーバーヘッドのための)および図13B(EPIオーバーヘッドのための)は、最初に各単一ポリシーのオーバーヘッドを示し、次いで、最も複雑な単一ポリシーであるメモリ安全性にポリシーを追加する合成を示すことによって、ポリシーの付加的な追加がランタイムオーバーヘッドにどのように影響するかを示す。この進行は、どのオーバーヘッドが、より大きなオーバーヘッドのポリシーを追加することではなく単に任意のポリシーを追加することにより生じるかを、より明らかにする。ここで4つのポリシーを超えるスケーリングの感覚を得るために、CFIポリシー(リターンおよび計算されたジャンプ/呼出しを行う)とテイント追跡ポリシー(テインティングおよびI/Oテインティングをコーディングする)が2つの部分に各々分解される。追加のポリシー追跡のランタイムオーバーヘッドは徐々に第1の複雑なポリシー(メモリ安全性)を上回り、非外れ値に対する顕著なランタイムの影響はなく(最悪の場合の非外れ値は9%から10%オーバーヘッドを増やす)、大部分がミスハンドラ解決の複雑さの増大により、各々の新しい種類のポリシーが追加されるにつれて2つの外れ値においてより大きな増大(20~40%)が見られる。エネルギーは同様の傾向に従って、非外れ値のポリシーに対して穏やかな影響(幾何平均が60%から70%増大する)を伴い、これはGemsFDTDを除くすべてのものに当てはまる。

30

#### 【0096】

関連する成果の簡単な概要が図15で再現される表2において特定される。

#### 【0097】

本明細書の技法に従ったポリシープログラミングモデルによれば、PUMPポリシーは、タグ値の集合を、何らかの所望のタグ伝播および実施機構を実装するためにこれらのタグを操作するルールの集合とともに含む。ルールには、システムのソフトウェア層(シンボリックルール)またはハードウェア層(コンクリートルール)という2つの形式がある。

40

#### 【0098】

たとえば、PUMPの動作を例示するために、プログラム実行の間にリターンポイントを制約するための簡単な例示的なポリシーを考える。このポリシーの動機は、リターン指向プログラミング(ROP)として知られているあるクラスの攻撃に由来し、ROPでは、攻撃者は、攻撃されているプログラムのバイナリ実行可能ファイルにおいて「ガジェット」の集合を特定し、これらを使用して、各々が何らかのガジェットを指すリターンアドレスを格納するスタックフレームの適切なシーケンスを構築することにより、複雑な悪意のある挙動を組み立てる。次いで、バッファオーバーフローまたは他の脆弱性が、所望のシーケンス

50

を用いてスタックの上部を上書きするために悪用され、断片が順番に実行されるようする。ROP攻撃を制限する1つの簡単な方法は、リターン命令のターゲットをよく定義されたりターンポイントに制約することである。これは、メタデータタグターゲットを用いて、有効なリターンポイントである命令をタグ付けすることによって、PUMPを使用することにより達成される。リターン命令が実行されるたびに、リターンが発生したばかりであることを示すために、PCのメタデータタグがcheckに設定される。次の命令では、PCタグはcheckであり、現在の命令のタグがtargetであることを検証し、そうでない場合にはセキュリティ侵害をシグナリングする。メタデータをよりリッチにすることによって、どのリターン命令がどのリターンポイントに戻れるかを正確に制御することが可能である。メタデータをさらにリッチにすることによって、完全なCFI確認を実施することができる。

10

#### 【 0 0 9 9 】

ポリシー設計者およびPUMP10のソフトウェア部分の観点からは、ポリシーは、小さな領域固有の言語で書かれたシンボリックルールを使用してコンパクトに記述され得る。例示的なシンボリックルールおよびそのプログラム言語は、たとえば、「PROGRAMMING THE PUMP, Hardware-Assisted Micro-Policies for Security」という表題のセクションにおいて説明される。

#### 【 0 1 0 0 】

シンボリックルールは、多種多様なメタデータ追跡機構をコンパクトに符号化し得る。しかしながら、ハードウェアレベルでは、主要な計算を遅くするのを避けるために、効率的な解釈のために調整された表現に対してルールが必要である。この目的で、コンクリートルールと呼ばれる、より低水準のルールのフォーマットが導入され得る。直観的には、所与のポリシーに対する各シンボリックルールは、コンクリートルールの等価な集合へと拡張され得る。しかしながら、単一のシンボリックルールは一般に、無限の数のコンクリートルールを生成し得るので、この精緻化は遅延して実行され、システムが実行される間に必要に応じてコンクリートルールを生成する。

20

#### 【 0 1 0 1 】

メタデータタグを伴う(たとえば、ROPよりリッチな)ポリシーに対して、シンボリックルールからコンクリートルールへの変換は同じ全般的な道筋に従うが、詳細は少しだけより複雑である。たとえば、テイント追跡ポリシーは、各々が任意のサイズのテイントの集合を記述する(所与のデータに寄与した可能性のあるデータソースまたはシステム構成要素を表す)、メモリデータ構造へのポインタとしてタグを解釈する。loadオペグループのためのシンボリックルールは、ロードされた値のテイントが、命令自体、ロードのためのターゲットアドレス、およびそのアドレスにおけるメモリでのテイントの和集合であるはずであることを述べている。シンボリックルールおよびそのプログラム言語は、前に特定された「PROGRAMMING THE PUMP, Hardware-Assisted Micro-Policies for Security」という表題の論文の総覧から、参照によって組み込まれ、入手可能である。

30

#### 【 0 1 0 2 】

別個のタグの数(および、したがってルールキャッシュに対する圧力)を減らすために、メタデータ構造は内部的に標準的な形式で記憶されることがあり、タグは不变であるので、共有が完全に利用される(たとえば、集合要素は、集合が共通のプレフィックス部分集合を共有してコンパクトに表現され得るように、標準的な順序で与えられる)。これらの構造は、もはや必要とされないとき、(たとえば、ガベージコレクションによって)回収され得る。

40

#### 【 0 1 0 3 】

ある実施形態は合成ポリシーを利用し得る。複数の直交するポリシーが、タグをいくつかの構成要素ポリシーからのタグのタプルへのポインタにすることにより、同時に実施され得る(一般に、複数のポリシーは直交していないことがある)。たとえば、テイント追跡ポリシーを用いて第1のリターンオペグループ(ROP)ポリシーを作るために、各タグをタプル(r,t)の表現へのポインタとし、rはROPタグ(コード位置識別子)であり、tはテイントタグ(テイントの集合へのポインタ)である。キャッシュルックアッププロセスは厳密に同じであるが、ミスが発生すると、ミスハンドラがタプルの構成要素を抽出し、シンボリックル

50

ルの両方の集合を評価するルーチンにディスパッチする。適用されるルールを両方のポリシーが有する場合にのみ、動作は許容される。この場合、得られるタグは、2つのサブポリシーからの結果を格納するペアへのポインタである。

#### 【0104】

ポリシーシステムおよび保護に関連して、ポリシーシステムは、各ユーザプロセス内のメモリの別個の領域として存在する。ポリシーシステムは、たとえば、ミスハンドラのためのコード、ポリシールール、およびポリシーのメタデータタグを表すデータ構造を含み得る。プロセスの中にポリシーシステムを置くことは、既存のUnix（登録商標）プロセスモデルに関して最小限に侵害的であり、ポリシーシステムとユーザコードとの間の軽量な切替えを容易にする。ポリシーシステムは、次に説明される機構を使用してユーザコードから隔離される。

10

#### 【0105】

明らかに、攻撃者がメタデータタグを書き直せる場合、またはそれらの解釈を変更できる場合、PUMPにより提供される保護は無意味である。本明細書で説明される技法は、そのような攻撃を防ぐように設計される。カーネル、ローダ、および(いくつかのポリシーのための)コンパイラが信頼される。具体的には、コンパイラに頼って、初期タグをワードに割り当て、必要な場合に、ルールをポリシーシステムに伝える。ローダは、コンパイラにより提供されるタグを保存し、コンパイラからロードへの経路は、たとえば暗号学的な署名を使用して、改竄から保護される。

20

#### 【0106】

本明細書の技法に従ったある実施形態は、各プロセスのための初期メモリイメージをセットアップする、標準的なUnix（登録商標）型のカーネルを使用し得る(マイクロポリシーを使用してこれらの仮定の一部をなくし、さらにTCBのサイズを減らすことが可能であり得る)。そのような実施形態では、ルールキャッシュミスハンドリングソフトウェアが正しく実装されることがさらに仮定される。ルールキャッシュミスハンドリングソフトウェアは小さいので、正式な検証の良好なターゲットである。1つの重要なことは、プロセスにおいて実行されるユーザコードが、プロセスのポリシーにより提供される保護を損ねるのを防ぐことである。ユーザコードは、(i)タグを直接操作することが可能であるべきではなく、すなわちすべてのタグの変更が現在有効なポリシールール/複数のポリシールールに従って実行されるべきであり、(ii)ミスハンドラによって使用されるデータ構造およびコードを操作することが可能であるべきではなく、(iii)ハードウェアルールキャッシュにルールを直接挿入することが可能であるべきではない。

30

#### 【0107】

アドレス指定に関連して、ユーザコードによるタグの直接の操作を防ぐために、1つ1つの64bのワードに添付されるタグは、それら自体が別々にアドレス指定可能ではない。具体的には、タグを読み取り、または書き込むために、タグまたはタグの一部分にのみ相当するアドレスを指定することが可能ではない。すべてのユーザアクセス可能命令は、アトミックな単位としての(データ,タグ)のペアに対して動作し、標準的なALUが値部分に対して動作しPUMPがタグ部分に対して動作する。

40

#### 【0108】

本明細書の技法に従ったある実施形態におけるミスハンドラーアーキテクチャに関連して、ポリシーシステムは、PUMPキャッシュに対するミスに際してのみアクティビ化され得る。ポリシーシステムとユーザコードを隔離するために、ミスハンドラ動作モードがプロセッサに追加される。整数レジスタファイルは、レジスタを保存して復元することを避けるために、ミスハンドラのみが利用可能な16個の追加のレジスタを用いて拡張される。16個の追加のレジスタの使用は例示的であり、実際には、整数レジスタファイルをより少数/多数のレジスタに拡張する必要があり得ることに留意されたい。フォルトした命令のPC、ルール入力(オペグループおよびタグ)、およびルール出力は、ミスハンドラモードにある間はレジスタとして出現する。ミスハンドラリターン命令が追加され、これで、コンクリートルールをキャッシュにインストールすることが終了し、ユーザコードに戻る。

50

## 【0109】

本明細書の技法に従つたある実施形態では、プロセッサ12がミスハンドラモードにある間、PUMP10の普通の挙動は不関与である。代わりに、単一のハードワイヤードルールが適用される。ミスハンドラにより扱われるすべての命令およびデータが、いずれのポリシーによって使用されるタグとも異なる事前に定義されたミスハンドラタグでタグ付けされなければならない。このことは、同じアドレス空間におけるミスハンドラコードとデータとユーザコードとの隔離を確実にする。ユーザコードはポリシーシステムデータまたはコードを扱うことができず、またはそれらを実行することができず、ミスハンドラは偶発的にユーザデータおよびコードを扱うことができない。ミスハンドラリターン命令は、ミスハンドラモードのみにおいて発行することができ、ユーザコードがルールをPUMPに挿入するのを防ぐ。

10

## 【0110】

これまでの研究は、安全性およびセキュリティポリシーをコンパクトに表現または近似するために賢い方式を使用しているが、これはしばしば意図されるポリシーに対する妥協であり、コンパクトさと引き換えに複雑さを犠牲にすることがある。本明細書で説明されるように、ランタイムオーバーヘッドをほとんどまたはまったく追加することなく、より完全かつより自然に、セキュリティポリシーの必要性を捉えるよりリッチなメタデータを含めることができある。メタデータ表現およびポリシーの複雑さに対して不变の制限を課すのではなく、PUMP10は性能のグレイスフルデグラデーションをもたらす。このことは、一般的な場合の性能およびサイズに影響を与えることなく、必要な場合にポリシーがより多くのデータを使用することを可能にする。このことはさらに、さらに複雑なポリシーを簡単に表現して実行できるので、ポリシーの付加的な改良および性能調整を可能にする。

20

## 【0111】

メタデータベースのポリシー実施の価値を証明するものが続々と現れる中で、本開示は、ソフトウェアで定義されたメタデータ処理のためのアーキテクチャを定義し、ランタイムオーバーヘッドの大半をなくすためのアクセラレータを特定する。専用のハードウェアメタデータ伝播方法に匹敵する性能を達成する4つのマイクロアーキテクチャ最適化(オペグループ、タグ圧縮、タグ変換、およびミスハンドラアクセラレーション)とともに同時にサポートされる、メタデータビットの数またはポリシーの数に対する制約のない(すなわち、あらゆる制約から自由である)、アーキテクチャが本明細書において紹介され説明される。ソフトウェアで定義されるメタデータポリシーモデルおよびそのアクセラレーションは、信頼できる情報フローの制御、細粒度のアクセス制御、整合性、同期、レース検出、デバッグ、アプリケーション固有のポリシー、ならびに動的コードの制御された生成および実行を含む、ここで示されるもの以外の広範囲のポリシーに適用可能である。

30

## 【0112】

本明細書で説明される様々な態様および実施形態のいくつかの非限定的な利点は、(i)このアーキテクチャによりサポートされるポリシーをコンパクトにかつ正確に記述するためのプログラミングモデルおよびサポートインターフェースモデル、(ii)よく研究されているポリシーの4つの異なるクラスを使用したポリシーの符号化および合成の詳細な例、ならびに(iii)これらのポリシーに対する要件、複雑さ、および性能の定量化を提供する。

40

## 【0113】

本明細書で説明されるような実施形態のプログラミングモデルは、他のポリシーのホストを符号化し得る。情報フロー制御は、ここでは簡単なテント追跡モデルよりリッチであるが、暗黙的なフローを追跡することは、RIFLE型のバイナリ変換により、または、コンパイラからのある程度のサポートとともにPC tagを使用することにより、サポートされ得る。マイクロポリシーは、軽量なアクセス制御およびコンパートメント化をサポートすることができる。偽造不可能なリソースを区別するためにタグが使用され得る。固有の生成されたトークンが、データを検印して保証するための鍵として機能することができ、これを次いで強力な抽象化のために使用することができ、データが認証されたコード構成要素のみによって作成され破壊されることを保証する。マイクロポリシールールは、不变性お

50

より線形性などのデータ不变条件を強制することができる。マイクロポリシーは、データまたは特徴のためのフル/エンプティビットなどの同期プリミティブに対するアウトオブバンドメタデータとして、または、ロック状態でレース条件を検出するための状態として、並列処理をサポートすることができる。システムアーキテクトは、1つ1つの行を検査することなく、または書き直すことなく、既存のコードに固有のマイクロポリシーを適用することができる。

#### 【 0 1 1 4 】

本明細書で説明されるPUMP10の設計は、フレキシビリティと性能の魅力的な組合せを提供し、低水準で細粒度のセキュリティポリシーの多様な集合を、多くの場合に専用の機構に匹敵する単一ポリシー性能とともにサポートしながら、ルールの複雑さが増すにつれて大抵の場合に性能のグレイスフルデグラデーションを伴うよりリッチな合成ポリシーをサポートする。さらに、PUMPによって提供される機構は、固有のソフトウェア構造を保護するために使用され得る。本明細書の技法に従ったある実施形態は、PUMP10を使用して「コンパートメント化」マイクロポリシーを実施することによって、かつ、これを使用してミスハンドラコードを保護することによって、特別なミスハンドラ動作モードを置き換えることができる。最後に、本明細書で説明されるように、ポリシーの直交する集合が組み合わされることがあり、ここで、各々の集合により提供される保護は、他方の集合とは完全に独立である。しかし、ポリシーはしばしば相互作用する。たとえば、情報フローポリシーは、メモリ安全性ポリシーにより割り振られている未使用の領域にタグを置くことが必要であり得る。ポリシー合成は、表現と、効率的なハードウェアサポートの両方に関連して、分析を必要とする。

10

#### 【 0 1 1 5 】

ここで説明されるのは、ヒープに割り振られたメモリにおけるすべての時間的および空間的な侵害を特定する、本明細書の技法に従ったある実施形態における、メモリ安全性ポリシーの実装形態を示すさらなる例である。少なくとも1つの実施形態において、各々の新しい割振りに対して、未使用の色idであるcを作り、新しく作られたメモリブロックの中の各メモリ位置のタグとしてcを書き込む(たとえば、memsetなどを介して)ために、処理が実行され得る。新しいブロックへのポインタもcとタグ付けされる。その後、処理がポインタをデリファレンスするために実行されるとき、処理は、ポインタのタグが、ポインタが参照するまたは指すメモリセルのタグと同じであることを確認することを含み得る。ブロックが解放されるとき、ブロックのすべてのセルのタグは、自由なメモリを表す定数Fに変更され得る。ヒープは最初はFとタグ付けされ得る。特別なタグ F が非ポインタのために使用され得る。したがって、一般に、ある実施形態は、色cまたは F のいずれかであるメモリ位置に対してタグtを書き込むことができる。

20

30

#### 【 0 1 1 6 】

メモリセルはポインタを格納し得るので、一般に、メモリの中の各ワードは2つのタグと関連付けられ得る。そのような実施形態では、各メモリセルのタグはペア(c,t)へのポインタであり、ここでcは、このセルが割り振られたメモリブロックのidであり、tは、セルに記憶されているワードのタグである。ある実施形態は、シンボリックルールに関するポリシーを指定するための、本明細書の他の箇所で説明されるルール関数に基づいて領域固有の言語を使用することができる。loadおよびstoreのためのルールは、これらのペアをパックおよびアンパックすることとともに、各メモリアクセスが有効であることを確認することを担当する(すなわち、アクセスされるセルはこのポインタによって指されるブロック内にある)。

40

```

load:(-, -, c1, -, (c2, t2))

(-, t2) if c1=c2

store:(-, -, t1, c2, (c3, t3))

(-, (c3, t1)) if c2=c3

```

#### 【 0 1 1 7 】

前述のルールおよび他のルールにおいて実行される確認は、シンボリックルールが有効で

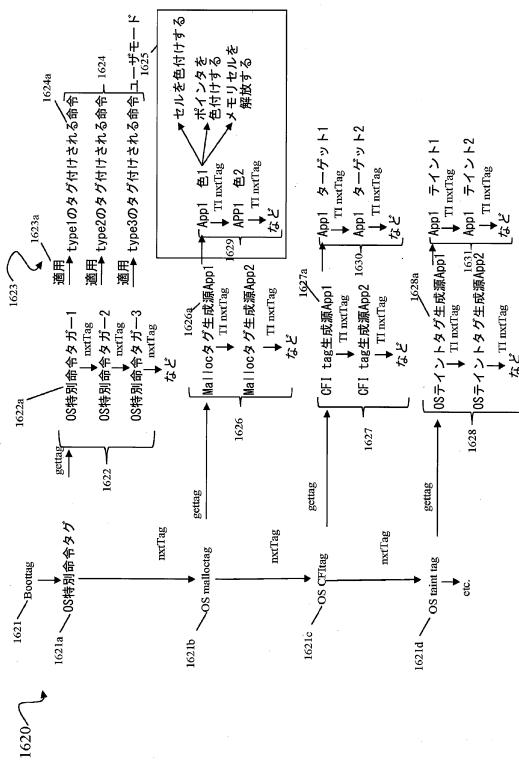

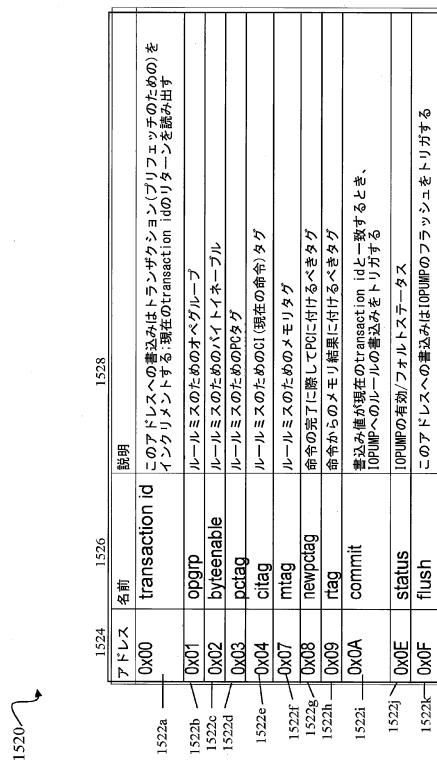

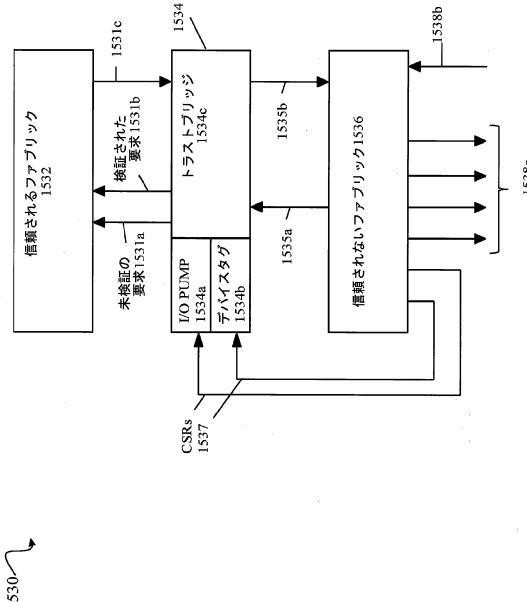

50