(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5584219号

(P5584219)

(45) 発行日 平成26年9月3日(2014.9.3)

(24) 登録日 平成26年7月25日(2014.7.25)

|                      |             |

|----------------------|-------------|

| (51) Int.Cl.         | F 1         |

| HO3M 13/27 (2006.01) | HO3M 13/27  |

| HO3M 13/19 (2006.01) | HO3M 13/19  |

| HO4L 1/00 (2006.01)  | HO4L 1/00 F |

請求項の数 32 (全 31 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-530058 (P2011-530058)  |

| (86) (22) 出願日 | 平成21年10月2日 (2009.10.2)        |

| (65) 公表番号     | 特表2012-504903 (P2012-504903A) |

| (43) 公表日      | 平成24年2月23日 (2012.2.23)        |

| (86) 国際出願番号   | PCT/US2009/005437             |

| (87) 国際公開番号   | W02010/039257                 |

| (87) 国際公開日    | 平成22年4月8日 (2010.4.8)          |

| 審査請求日         | 平成24年10月2日 (2012.10.2)        |

| (31) 優先権主張番号  | 61/102,517                    |

| (32) 優先日      | 平成20年10月3日 (2008.10.3)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 61/196,889                    |

| (32) 優先日      | 平成20年10月21日 (2008.10.21)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 501263810<br>トムソン ライセンシング<br>Thomson Licensing<br>フランス国, 92130 イッサー レ<br>ムーリノー, ル ジヤンヌ ダルク,<br>1-5<br>1-5, rue Jeanne d' Arc, 92130 ISSY LES<br>MOULINEAUX, France |

| (74) 代理人  | 110001243<br>特許業務法人 谷・阿部特許事務所                                                                                                                                      |

最終頁に続く

(54) 【発明の名称】 2元消失サロゲート・チャネルを用いたAWGNチャネル条件下でビット・インターバルをLDPC符号および変調に適合させる方法および装置

## (57) 【特許請求の範囲】

## 【請求項1】

ビット・インターバルをLDPC符号および変調に適合させる方法であって、

非一様並列AWGNチャネルのビット単位容量を計算するステップと、

前記AWGNチャネルを、消失確率を有する1組のQ個のサロゲート2元消失チャネル

(BEC)で近似するステップと、

消失確率密度分布を用いて、復号しきい値信号対雑音比(SNR)が、ビット・インターバル構成に対して最低の復号しきい値信号対雑音比をもたらすかどうかを判定するステップと、

判定した最低の復号しきい値信号対雑音比に対応するビット・インターバル構成に基づいて、前記ビット・インターバルを構成するステップと、

を含む、前記方法。

## 【請求項2】

前記判定するステップが、

前記消失確率がゼロに収束する場合に、前記SNRを所定の刻み幅だけ低減するステップと、

前記低減したSNRに対する消失確率を決定するステップと、

前記低減したSNRの消失確率がゼロに収束するかどうかを判定するステップと、

前記消失確率がゼロに収束しない場合に、前記低減前のSNRをビット・インターバル構成の復号しきい値SNRとして特定するステップと、

10

20

をさらに含む、請求項 1 に記載の方法。

**【請求項 3】**

前記判定するステップが、

前記消失確率がゼロに収束しない場合に、前記 S N R を所定の刻み幅だけ増加するステップと、

前記増加した S N R に対する消失確率を決定するステップと、

前記増加した S N R の消失確率がゼロに収束するかどうかを判定するステップと、

前記消失確率がゼロに収束する場合に、前記増加した S N R をビット・インターバ構成の復号しきい値 S N R として特定するステップと、

をさらに含む、請求項 2 に記載の方法。

10

**【請求項 4】**

各ビット・インターバ構成および対応する決定した最低の復号しきい値 S N R を記憶するステップと、

ビット・インターバ構成を変更するステップと、

前記判定するステップを実行して、前記変更したビット・インターバ構成の復号しきい値 S N R を決定するステップと、

前記最低の復号しきい値 S N R を有するビット・インターバ構成を選択するステップと、

前記選択した構成を有するビット・インターバを構成するステップと、

をさらに含む、請求項 3 に記載の方法。

20

**【請求項 5】**

前記計算したビット単位容量が、前記並列 A W G N チャネルの 2 値入力と有効出力の間の相互情報量に基づいてビット単位容量を計算するステップを含み、前記近似が、前記計算したビット単位容量の同等性に基づいて行われる、請求項 1 に記載の方法。

**【請求項 6】**

前記構成したビット・インターバを用いて前記符号をビット・インターブするステップをさらに含む、請求項 1 に記載の方法。

**【請求項 7】**

前記判定するステップが、前記復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布を決定するステップをさらに含む、請求項 2 に記載の方法。

30

**【請求項 8】**

前記平均消失確率を決定する前記ステップが、

前記 L D P C 符号のノード / エッジ・バースペクティブ次数分布を識別するステップと、

各サブチャネルの消失確率の凸結合を行うステップと、

をさらに含む、請求項 7 に記載の方法。

**【請求項 9】**

前記密度分布のモデル化が、

**【数 1】**

$$\varepsilon_q^l = \varepsilon_q^0 \lambda_q(\alpha^l),$$

$$= 1 - (1 - )^{l-1}$$

**【数 2】**

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1},$$

40

から導出され、上付き文字 l は反復指標を表し、下付き文字 q は B E C サブチャネル番号を表し、 は単一の B E C チャネルの出力における消失確率を表し、 はチェック・ノード ( C N D ) の出力における平均消失確率を表し、 は変数ノード ( V N D ) の出力にお

50

ける平均消失確率を表し、 $w_q$ はサブチャネル q のエッジ割合を表す、請求項 7 に記載の方法。

**【請求項 10】**

ビット・インターバの次数プロファイルの最適化を制約することにより、前記復号しきい値 S N R を最小にするステップをさらに含む、請求項 3 に記載の方法。

**【請求項 11】**

ビット・インターバを L D P C 符号および変調に適合させる装置であって、

非一様並列 A W G N チャネルのビット単位容量を計算し、前記 A W G N チャネルを 1 組のサロゲート 2 元消失チャネルで近似し、消失確率密度分布を用いて 1 つまたは複数のビット・インターバ構成のそれぞれに対して復号しきい値 S N R を決定するように構成されたプロセッサであり、決定した各 S N R に対して消失確率を決定するプロセッサと、

前記 1 つまたは複数の決定した復号しきい値 S N R および対応するビット・インターバ構成を記憶するメモリと、

記憶された 1 つまたは複数の決定された復号しきい値 S N R から選択された最低の復号しきい値 S N R に対応するビット・インターバ構成に基づいて前記プロセッサによって構成されたビット・インターバと、

を備える、前記装置。

**【請求項 12】**

前記プロセッサが、前記決定された 1 つまたは複数の復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布をさらに決定する、請求項 11 に記載の装置。

**【請求項 13】**

前記プロセッサが、前記並列 A W G N チャネルの 2 値入力と有効出力の間の相互情報量に基づいて前記ビット単位容量を計算する、請求項 1 1 に記載の装置。

**【請求項 14】**

前記ビット・インターバが、各しきい値 S N R に対応する決定された消失確率のそれぞれから導出された復号反復の復号収束条件に基づいて前記符号のビット・インターバを行なうように構成される、請求項 1 1 に記載の装置。

**【請求項 15】**

前記プロセッサが、前記 L D P C 符号のノード / エッジ・パースペクティブ次数分布を識別し、各サブチャネルの消失確率の凸結合を行うことによって、前記平均消失確率を決定する、請求項 1 2 に記載の装置。

**【請求項 16】**

前記密度分布のモデル化が、

**【数 3】**

$$\varepsilon'_q = \varepsilon_q^0 \lambda_q(\alpha'),$$

$$l = 1 - (1 - l^{-1})$$

**【数 4】**

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1}.$$

から導出され、上付き文字 l は反復指標を表し、下付き文字 q は B E C サブチャネル番号を表し、 $\varepsilon$  は单一の B E C チャネルの出力における消失確率を表し、 $\lambda$  はチェック・ノード ( C N D ) の出力における平均消失確率を表し、 $\alpha$  は変数ノード ( V N D ) の出力における平均消失確率を表し、 $w_q$  はサブチャネル q のエッジ割合を表す、請求項 1 2 に記載の装置。

10

20

30

40

50

**【請求項 17】**

受信側ビット・インターバを L D P C 符号および変調に適合させる方法であって、

非一様並列 A W G N チャネルのビット単位容量を計算するステップと、

前記 A W G N チャネルを、消失確率を有する 1 組の Q 個のサロゲート 2 元消失チャネル

( B E C ) で近似するステップと、

消失確率密度分布を用いて、復号しきい値信号対雑音比 ( S N R ) が、ビット・インターバ構成に対して最低の復号しきい値信号対雑音比をもたらすかどうかを判定するステップと、

判定した最低の復号しきい値信号対雑音比に対応するビット・インターバ構成に基づいて、前記受信側ビット・インターバを構成するステップと、

を含む、前記方法。

**【請求項 18】**

前記判定するステップが、

前記消失確率がゼロに収束する場合に、前記 S N R を所定の刻み幅だけ低減するステップと、

前記低減した S N R に対する消失確率を決定するステップと、

前記低減した S N R の消失確率がゼロに収束するかどうかを判定するステップと、

前記消失確率がゼロに収束しない場合に、前記低減前の S N R をビット・インターバ構成の復号しきい値 S N R として特定するステップと、

をさらに含む、請求項 17 に記載の方法。

**【請求項 19】**

前記判定するステップが、

前記消失確率がゼロに収束しない場合に、前記 S N R を所定の刻み幅だけ増加するステップと、

前記増加した S N R に対する消失確率を決定するステップと、

前記増加した S N R の消失確率がゼロに収束するかどうかを判定するステップと、

前記消失確率がゼロに収束する場合に、前記増加した S N R をビット・インターバ構成の復号しきい値 S N R として特定するステップと、

をさらに含む、請求項 18 に記載の方法。

**【請求項 20】**

各ビット・インターバ構成および対応する決定した最低の復号しきい値 S N R を記憶するステップと、

ビット・インターバ構成を変更するステップと、

前記判定するステップを実行して、前記変更したビット・インターバ構成の復号しきい値 S N R を決定するステップと、

前記最低の復号しきい値 S N R を有するビット・インターバ構成を選択するステップと、

前記選択した構成を有するビット・インターバを構成するステップと、

をさらに含む、請求項 19 に記載の方法。

**【請求項 21】**

前記計算したビット単位容量が、前記並列 A W G N チャネルの 2 値入力と有効出力の間の相互情報量に基づいてビット単位容量を計算するステップを含み、前記近似が、前記計算したビット単位容量の同等性に基づいて行われる、請求項 17 に記載の方法。

**【請求項 22】**

前記構成したビット・インターバを用いて前記符号をビット・インターブするステップをさらに含む、請求項 17 に記載の方法。

**【請求項 23】**

前記判定するステップが、前記復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布を決定するステップをさらに含む、請求項 18 に記載の方法。

10

20

30

40

50

**【請求項 2 4】**

前記平均消失確率を決定する前記ステップが、

前記 L D P C 符号のノード / エッジ・パースペクティブ次数分布を識別するステップと

、

各サブチャネルの消失確率の凸結合を行うステップと、

をさらに含む、請求項 2 3 に記載の方法。

**【請求項 2 5】**

前記密度分布のモデル化が、

**【数 5】**

$$\varepsilon_q' = \varepsilon_q^0 \lambda_q(\alpha'),$$

$$\beta^{l-1} = 1 - (1 - \varepsilon_q'^{l-1})$$

**【数 6】**

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q'^{l-1},$$

から導出され、上付き文字 l は反復指標を表し、下付き文字 q は B E C サブチャネル番号を表し、 は単一の B E C チャネルの出力における消失確率を表し、 はチェック・ノード ( C N D ) の出力における平均消失確率を表し、 は変数ノード ( V N D ) の出力における平均消失確率を表し、  $w_q$  はサブチャネル q のエッジ割合を表す、請求項 2 3 に記載の方法。

**【請求項 2 6】**

ビット・インターバの次数プロファイルの最適化を制約することにより、前記復号しきい値 S N R を最小にするステップをさらに含む、請求項 1 9 に記載の方法。

**【請求項 2 7】**

受信側ビット・インターバを L D P C 符号および変調に適合させる装置であって、

非一様並列 A W G N チャネルのビット単位容量を計算し、前記 A W G N チャネルを 1 組のサロゲート 2 元消失チャネルで近似し、消失確率密度分布を用いて 1 つまたは複数のビット・インターバ構成のそれぞれに対して復号しきい値 S N R を決定するように構成されたプロセッサであり、決定した各 S N R に対して消失確率を決定するプロセッサと、

前記 1 つまたは複数の決定した復号しきい値 S N R および対応するビット・インターバ構成を記憶するメモリと、

記憶された 1 つまたは複数の決定された復号しきい値 S N R から選択された最低の復号しきい値 S N R に対応するビット・インターバ構成に基づいて前記プロセッサによって構成された受信側ビット・インターバと、

を備える、前記装置。

**【請求項 2 8】**

前記プロセッサが、前記決定された 1 つまたは複数の復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布をさらに決定する、請求項 2 7 に記載の装置。

**【請求項 2 9】**

前記プロセッサが、前記並列 A W G N チャネルの 2 値入力と有効出力の間の相互情報量に基づいて前記ビット単位容量を計算する、請求項 2 7 に記載の装置。

**【請求項 3 0】**

前記ビット・インターバが、各しきい値 S N R に対応する決定された消失確率のそれぞれから導出された復号反復の復号収束条件に基づいて前記符号のビット・インターバを行なうように構成される、請求項 2 7 に記載の装置。

**【請求項 3 1】**

前記プロセッサが、前記 L D P C 符号のノード / エッジ・パースペクティブ次数分布を識別し、各サブチャネルの消失確率の凸結合を行うことによって、前記平均消失確率を決定する、請求項 2 8 に記載の装置。

**【請求項 3 2】**

前記密度分布のモデル化が、

【数 7】

$$\varepsilon_q^l = \varepsilon_q^0 \lambda_q(\alpha^l),$$

10

$$= 1 - (1 - )^{l-1}$$

**【数 8】**

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1},$$

から導出され、上付き文字 l は反復指標を表し、下付き文字 q は B E C サブチャネル番号を表し、 は単一の B E C チャネルの出力における消失確率を表し、 はチェック・ノード ( C N D ) の出力における平均消失確率を表し、 は変数ノード ( V N D ) の出力における平均消失確率を表し、  $w_q$  はサブチャネル q のエッジ割合を表す、 請求項 2 8 に記載の装置。

20

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

( 関連出願の相互参照 )

本願は、2008年10月3日出願の米国仮特許出願第 6 1 / 1 0 2 5 1 7 号および2008年10月21日出願の米国仮特許出願第 6 1 / 1 9 6 8 8 9 号の利益を請求するものである。

**【0 0 0 2】**

30

本発明は、並列非一様チャネルの符号依存ビット・インターバに関する。より詳細には、本発明は、1組のサロゲート2元消失チャネル(通信路)(B E C)を利用した符号整合インタリープに関する。

**【背景技術】****【0 0 0 3】**

ケーブル・ネットワーク、衛星ネットワークおよび地上波ネットワークは、ディジタル放送サービスを最終顧客に届ける3大媒体である。衛星伝送および地上波伝送と異なり、ケーブル・チャネルは、時間および周波数の選択性がそれほど大きくない。そのため、ケーブル・ネットワークでは、スペクトル効率の良い変調(すなわち 2 5 6 Q A M および 1 0 2 4 Q A M)を利用して、H D T V や V o D など帯域幅消費の大きいサービスの容量需要に応え、ディジタル・ビデオ放送の浸透を促進している。近年、設計自由度が高く、復号が簡潔であり、様々なタイプのチャネルで普遍的に誤り訂正性能が優れているという理由から、D V B - S 2 標準およびD V B - T 2 標準で低密度パリティ検査(L D P C)符号が導入されている。

40

**【0 0 0 4】**

実装の容易さおよび構成要素の相互運用性を考えると、D V B - S 2 標準に指定されるL D P C 符号を次世代のD V B - C システムで再使用することが強く推奨される。しかしながら、2値変調用に最適化されているL D P C 符号のアンサンブルは、それより高次の変調では、変調によって誤り保護に不均衡が生じるために、必ずしもうまく機能しないことは周知の通りである。無限コード長のマルチレベル符号化(M L C)の漸近性能は既に

50

研究されており、マルチステージ復号（M S D）を利用するときにはキャパシティ・アプローチング（capacity approaching）手法として最適であることが分かっている。しかし、M S Dアルゴリズムでは、下方の復号ステージの判定結果を上方のステージに送る必要があり、これにより復号の待ち時間が大きくなり、高速のアプリケーションでは容認できないこともある。

#### 【0005】

通信システムの当業者なら分かるように、インタリープは、様々な目的に適うようにシーケンスの順序を並べ替える手続きである。経時的な、また周波数領域による選択的フェージングを受けるチャネルでは、ビットおよび／またはシンボルのインタリープをチャネル符号化と併用して、バースト誤りを分散させている。さらに、連接符号、特にターボ符号では、ビット・インタリープを使用して、長いランダム符号を生成することができるよう第2成分エンコーダへの情報ビットをスクランブルする。10

#### 【0006】

L D P C 符号の結果として、密度発展、差分発展、外因性情報伝達（E X I T）チャートなどのフレームワークを呼び出して、符号アンサンブルの次数プロファイルを設計および解析している。復号収束のためのしきい値S N R に関しては、ブロック長が無限で、符号構造がランダムで、復号反復回数が無制限であると仮定すると、これらのフレームワークに従って構築された符号は、シャノン限界に非常に接近することができる。しかし、実際に実施する観点から見ると、ランダム構造は、符号化／復号の複雑さおよびメモリ要件が非常に厳しくなることが多い。この理由から、パワー効率と実施の簡潔性のより良い兼ね合いを達成することができる構造化L D P C 符号が、システム設計者によってより魅力ある選択肢となっている。例えば、E T S I衛星チャネル用第2世代デジタル・ビデオ放送標準（D V B - S 2）、I E E E 8 0 2 . 1 1 n 標準、およびI E E E 8 0 2 . 1

1 e 標準で採用されている誤り制御符号は全て、構造化L D P C 符号のカテゴリに属する。

#### 【0007】

一方、元々は衛星通信の順方向誤り制御用に設計されたD V B - S 2 L D P C 符号族は、D V B - T 2（地上波チャネル用第2世代D V B 標準）で再利用され、D V B - C 2（ケーブル・チャネル用第2世代D V B 標準）でも強く推奨されている。D V B - S 2 符号が再利用された主な理由は、システムの互換性が考慮されたことに加え、様々なチャネル条件下で普遍的に優れた性能を発揮することに帰することができる。しかし、より高いスペクトル効率および柔軟なスループットを求めるケーブル・オペレータの要求に応えるためには、D V B - S 2 符号をD V B - C 2 で再利用するための技術的難題は、2 5 6 Q A M から4 0 9 6 Q A M の範囲である非常に高次数のコンステレーションに所与の符号をマッピングすることにある。30

#### 【0008】

本発明は、サロゲート・チャネル手法を用いて符号依存ビット・インタリーバの設計を簡略化することを提案するものである。

#### 【0009】

C O D E C の簡潔な構造を維持しながらパワーとスペクトル効率の良好な兼ね合いを実現するために、本発明は、チャネル・エンコーダと変調器の間にビット・インタリーバを挿入し、チャネル・デコーダと復調器の間にビット・デインタリーバを挿入することを提案する。40

#### 【0010】

さらに、不規則なL D P C 符号および高次の変調（例えば2 5 6 Q A M）のコンステレーション・マッパー（変調器）を前提とすると、ビット・インタリーバを利用して、符号の不均衡な誤り訂正を、2 値ラベリング方式に固有の非対称なビット単位ユークリッド距離分離に整合させることができる。

#### 【0011】

一実施態様によれば、A W G N チャネル条件下でビット・インタリーバをL D P C 符号50

および変調に適合させる方法は、非一様並列 A W G N チャネルのビット単位容量を計算するステップと、A W G N チャネルを、消失確率を有する1組のQ個のサロゲート2元消失チャネル（B E C）で近似するステップと、復号しきい値S N Rが、ビット・インタリーバ構成に対して最低の復号しきい値S N Rをもたらすかどうかを判定するステップと、判定した最低の復号しきい値S N Rに対応するビット・インタリーバ構成に基づいてビット・インタリーバを構成するステップとを含む。

#### 【0012】

別の実施態様によれば、A W G N チャネル条件下でビット・インタリーバをL D P C 符号および変調に適合させる装置は、(i) 非一様並列 A W G N チャネルのビット単位容量を計算し、(ii) A W G N チャネルを1組のサロゲート2元消失チャネルで近似し、(iii) 1つまたは複数のビット・インタリーバ構成のそれぞれに対して復号しきい値S N Rを決定するように構成されたプロセッサを含む。また、このプロセッサは、決定した各S N Rに対して消失確率を決定する。メモリが、1つまたは複数の決定した復号しきい値S N R、および対応するビット・インタリーバ構成を記憶する。ビット・インタリーバは、記憶された1つまたは複数の決定された復号しきい値S N Rから選択された最低の復号しきい値S N Rに対応するビット・インタリーバ構成に基づいて、プロセッサによって構成される。

#### 【0013】

本発明の原理の上記その他の特徴、特性および利点は、以下の例示的な実施例の詳細な説明を添付の図面と関連付けて読めば、明らかになるであろう。

#### 【0014】

本発明の原理は、以下の例示的な図面によってより良く理解することができる。

#### 【図面の簡単な説明】

#### 【0015】

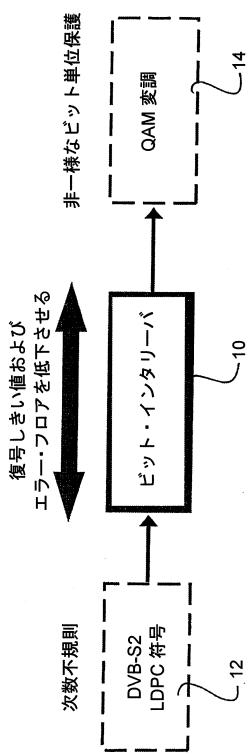

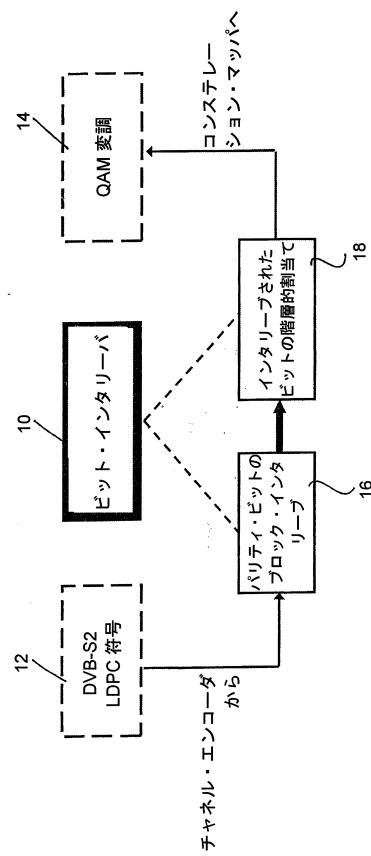

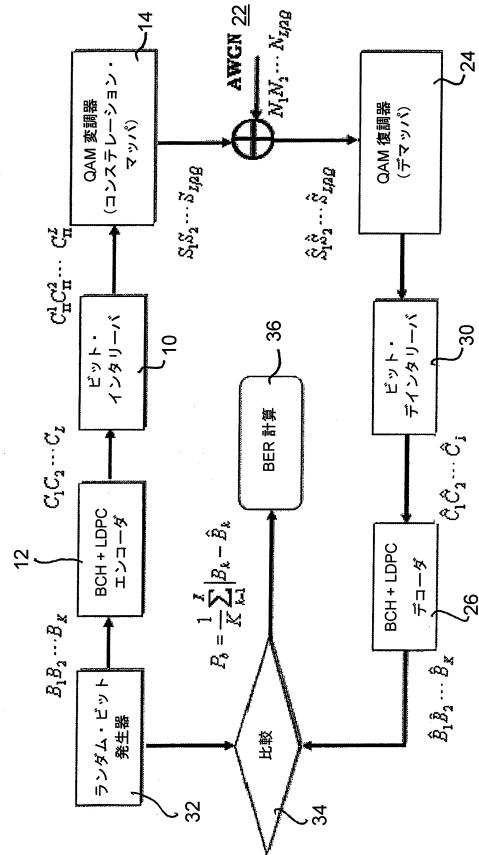

【図1a】本発明の一実施態様による符号整合インタリープを行う装置を示すブロック図である。

【図1b】本発明の一実施態様による符号整合インタリープを行う装置を示すブロック図である。

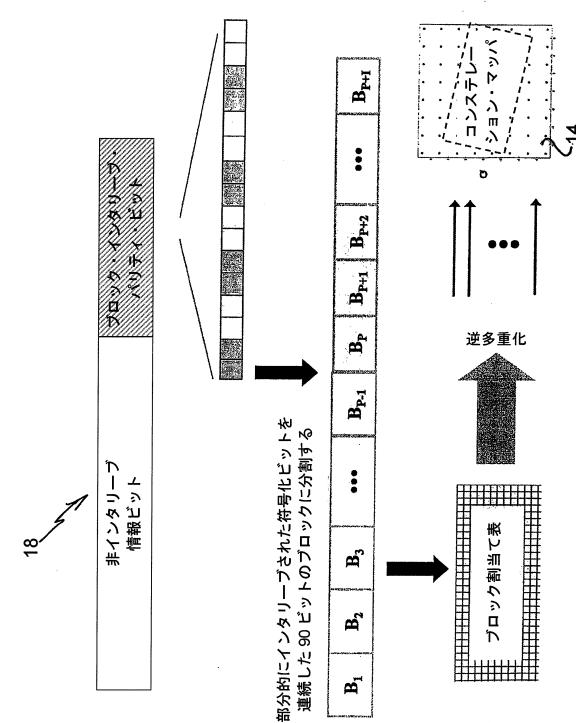

【図1c】本発明の一実施態様によるパリティ・ビットのブロック・インタリープを示すグラフである。

【図1d】本発明の一実施態様によるインタリープされたビットの階層的割当てを示すグラフである。

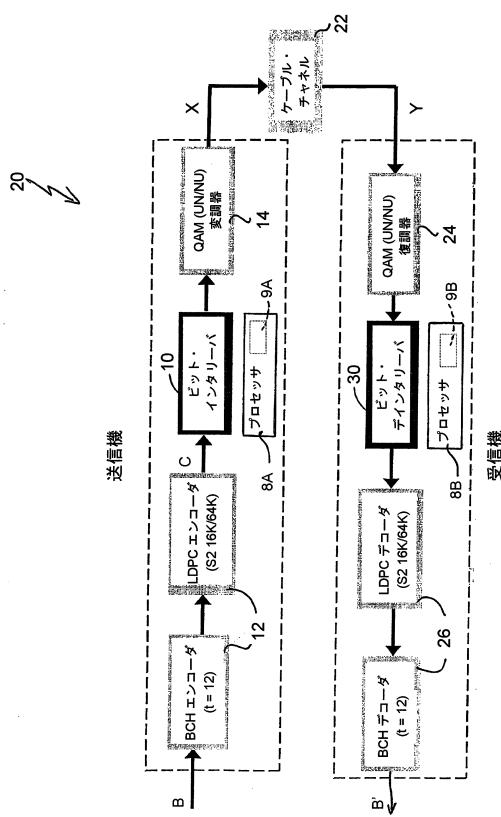

【図1e】本発明の符号整合インタリープの一実施例の通信システムの実施態様を示すブロック図である。

【図1f】図1eに示すシステムのより詳細なシステム図である。

【図1g】本発明の一実施態様による符号整合インタリープを行う装置のシミュレーション設定を示す図である。

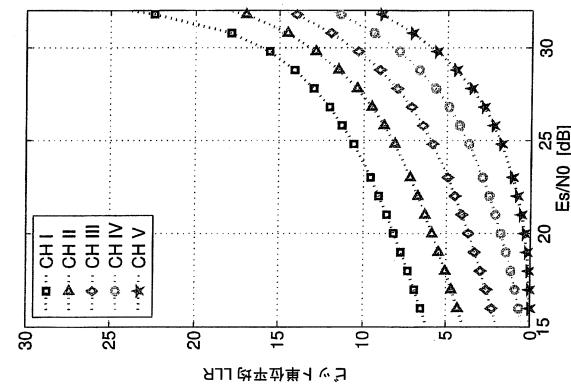

【図2a】本発明の一実施態様による例示的なコンステレーション・マップのチャネル条件を示すグラフである。

【図2b】本発明の一実施態様による例示的なコンステレーション・マップのチャネル条件を示すグラフである。

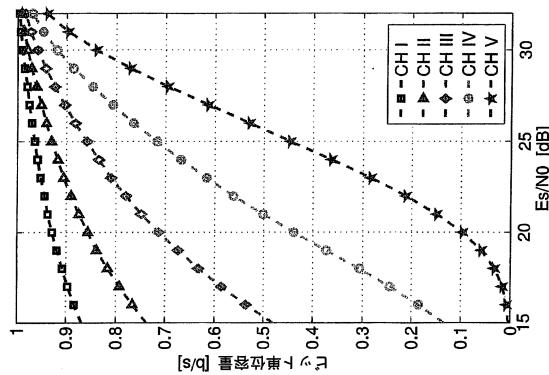

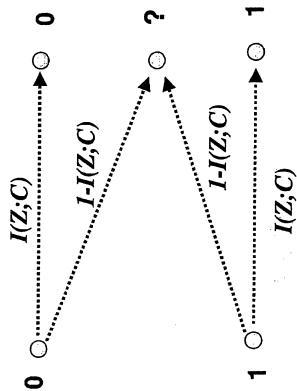

【図3a】所定の容量を有するA W G N チャネルを示すブロック図である。

【図3b】本発明の一実施態様による消失確率を有する2元消失チャネル（B E C）を示す図である。

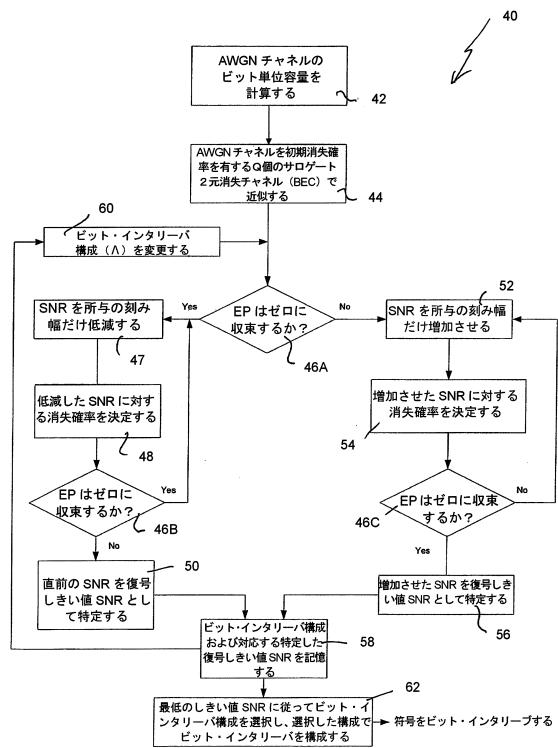

【図4】本発明の一実施態様による複数のサロゲート・チャネルの符号整合インタリープを行う方法を示す流れ図である。

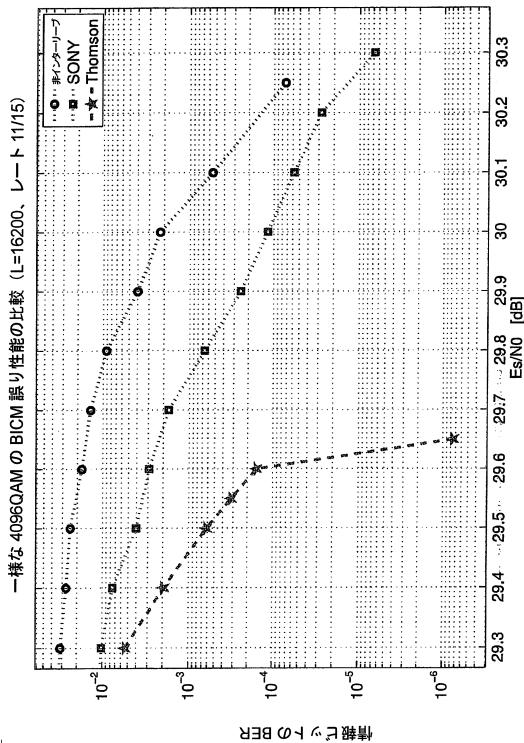

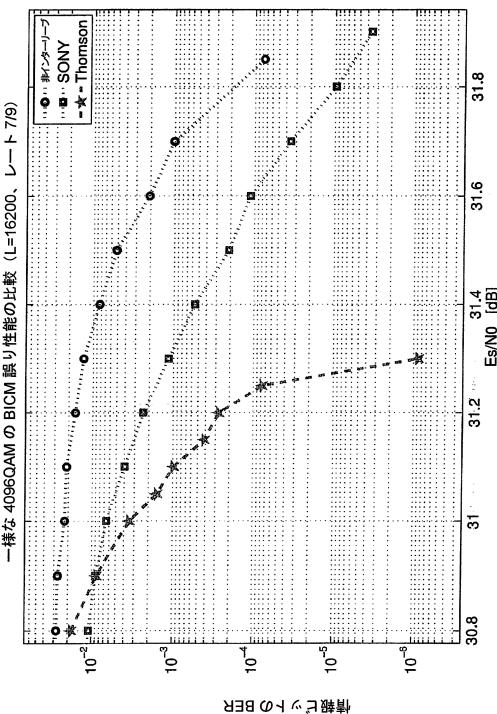

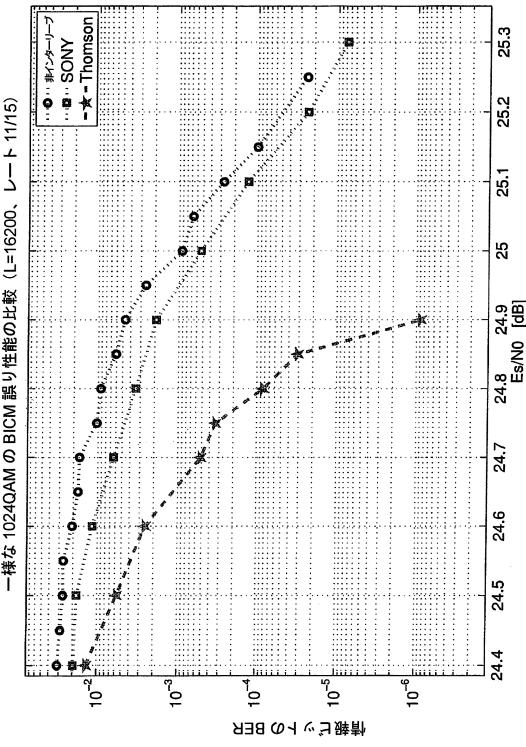

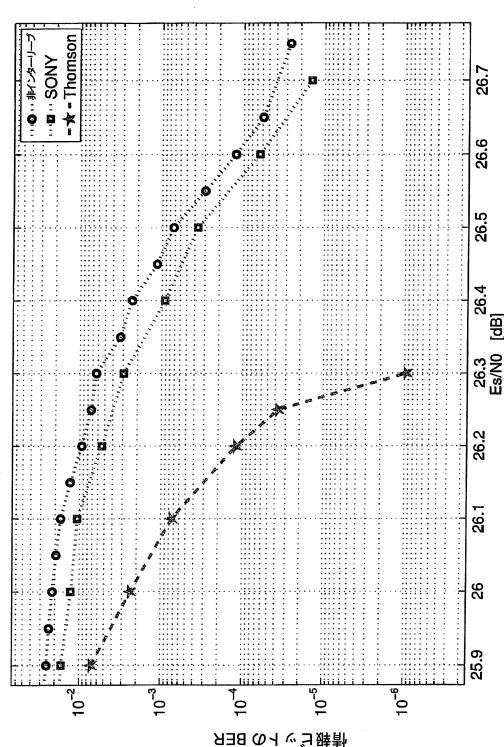

【図5】本発明の装置および方法によって提供される2種類のレートの復号B E Rとその結果得られるパワーの節約の比較を表すグラフである。

【図6】本発明の装置および方法によって提供される2種類のレートの復号B E Rとその結果得られるパワーの節約の比較を表すグラフである。

10

20

30

40

50

【図7】本発明の装置および方法によって提供される2種類のレートの復号BERとその結果得られるパワーの節約の比較を表すグラフである。

【図8】本発明の装置および方法によって提供される2種類のレートの復号BERとその結果得られるパワーの節約の比較を表すグラフである。

**【発明を実施するための形態】**

**【0016】**

本発明の原理は、複数のサロゲート・チャネルの符号整合インタリープを行う方法および装置を対象とする。

**【0017】**

本明細書は、本発明の原理を例示するものである。従って、本明細書に明示的には記述または図示していないなくても、本発明の趣旨および範囲に含まれる本発明の原理を実現する様々な構成を、当業者なら考案することができることを理解されたい。10

**【0018】**

本明細書に記載する全ての例および条件に関する表現は、本発明の原理と、当技術分野をさらに進歩させるために発明者等が与える概念とを、読者が理解するのを助けるという教育的な目的を有するものであって、これらの具体的に列挙した例および条件に限定されるわけではないものと解釈されたい。

**【0019】**

さらに、本発明の原理、特徴および実施例ならびに本発明の具体的な例について本明細書で述べる全ての記述は、その構造的均等物および機能的均等物の両方を含むものとする。さらに、これらの均等物には、現在既知の均等物だけでなく、将来開発されるであろう均等物も含まれる、すなわち、その構造に関わらず、同じ機能を実行する将来開発される任意の要素も含まれるものとする。20

**【0020】**

従って、例えば、当業者なら、本明細書に示すブロック図が本発明の原理を実施する例示的な回路の概念図を表していることを理解するであろう。同様に、任意のフロー・チャート、流れ図、状態遷移図、擬似コードなどが、コンピュータ可読媒体中に実質的に表現され、明示してある場合もしていない場合もあるコンピュータまたはプロセッサによって実質的に実行される様々なプロセスを表すことも理解されたい。

**【0021】**

図面に示す様々な要素の機能は、専用のハードウェアを使用して、またソフトウェアを実行することができるハードウェアを適当なソフトウェアと関連付けて使用して、実現することができる。プロセッサによってそれらの機能を実現するときには、単一の専用プロセッサで実現することも、単一の共用プロセッサで実現することも、あるいはその一部を共用することもできる複数の個別プロセッサで実現することもできる。さらに、「プロセッサ(processor)」または「制御装置(controller)」という用語を明示的に用いていても、ソフトウェアを実行することができるハードウェアのみを指していると解釈すべきではなく、ディジタル信号プロセッサ(DSP)ハードウェア、ソフトウェアを記憶するための読み取り専用メモリ(ROM)、ランダム・アクセス・メモリ(RAM)および不揮発性記憶装置(ただしこれらに限定されない)を暗に含むことがある。30

。

**【0022】**

従来の、且つ/または特注のその他ハードウェアも含まれることがある。同様に、図面に示す任意のスイッチも、概念的なものに過ぎない。それらの機能は、プログラム論理の動作によっても、専用論理によっても、プログラム制御と専用論理の相互作用によっても、あるいは手作業でも実施することができ、開発者が、前後関係から適宜判断して特定の技術を選択することができる。

**【0023】**

本明細書の特許請求の範囲において、特定の機能を実行する手段として表現されている任意の要素は、当該機能を実行する任意の方法を含むものとし、例えば、(a)当該機能40

を実行する回路素子の組合せや、(b) フームウェアやマイクロコードなども含めた任意の形態のソフトウェアを、当該ソフトウェアを実行して当該機能を実行する適当な回路と組み合わせたものなども含むものとする。特許請求の範囲によって定義される本発明の原理は、記載した様々な手段が実施する機能を、特許請求の範囲が要求するかたちで組み合わせ、まとめることがある。従って、これらの機能を実施することができる任意の手段を、本明細書に示す手段の均等物とみなすものとする。

#### 【0024】

本明細書において、本発明の原理の「1実施例」または「実施例」あるいはその変形例と述べている場合、それは、当該実施例に関連して述べられる特定の特性、構造、特徴などが、本発明の原理の少なくとも1つの実施例に含まれるという意味である。従って、本明細書の様々な箇所に見られる「1実施例において」または「実施例において」という表現、あるいはそうした表現の変形表現は、その全てが必ずしも同じ実施例のことを指しているわけではない。10

#### 【0025】

本発明は、サロゲート・チャネル手法を用いて符号依存ビット・インターバの設計を簡略化することを提案する。

#### 【0026】

基本的に、メッセージ・パッシング・デコーダの挙動の解析では、重要な選択を2度行う。1つは、有効チャネルのモデリングであり、もう1つは、反復復号プロセスを追跡する解析ツールの選択である。これまでに、2値入力を有する様々なタイプのチャネルで、LDPC符号アンサンブルの性能が調査されている。理論解析およびシミュレーションの両方の結果によって、復号しきい値がチャネルのタイプに有意なほどは依存していないが、有効チャネルの入力と出力の間の相互情報量には依存していることが実証されている。20

#### 【0027】

一方、密度発展の複雑さを低減するだけでなく復号アルゴリズムを理解する上でも有用な情報を与える反復復号の解析を簡略にするために、様々な1次元ガウス近似(GA)が導入されている。しかしながら、ガウス・モデルはチェック・ノード(CND)から変数ノード(VND)に伝達されるメッセージの確率分布を忠実に捕捉しないので、GAは、特に低い符号レートおよび中程度から高い次数のCNDでは、実用的ではあるが厳密な手法とは言えない。30

#### 【0028】

この問題を克服するために、より正確な復号プロセスのダイナミクスの近似を表す2次元ガウス・モデルに基づく確率的フレームワークが提案されている。しかし、この手法は複雑のために、高次変調により生じる並列チャネルなどの非一様チャネル、OFDMおよび不均衡誤り保護要件を有するディスク・チャネルに拡張することが難しい。

#### 【0029】

GAの制限を回避するために、本発明では、1組のサロゲート2元消失チャネル(BEC)によって非一様並列チャネルをモデル化し、チャネルの近似は、並列AWGNチャネルの2値入力と有効出力の間の相互情報量を表すビット単位容量の同等性に基づいて行う。その結果として、平均消失確率の展開を、1組の再帰方程式で完全に特徴づけることができる。さらに、高SNRレジーム(復号しきい値に近い)の下では、同次線形差分方程式によってデコーダのダイナミクスをさらに簡略化することができ、この同次線形差分方程式から、復号の収束に必要な条件を導出し、これをを利用してビット・インターバを構成することができる。40

#### 【0030】

無線通信と異なり、ケーブル・チャネルは、通常は高い信号対雑音比(SNR)レジームで動作し、信号伝送中に選択的なフェージングが、ほとんど、あるいは全く生じない。従って、ケーブル・チャネルは、256QAMや4096QAMなどのスペクトル効率の良い変調を展開することができる、加法性ホワイト・ガウス・ノイズ(AWGN)チャネルとして定式化することができる。平均伝送パワーの制約がある通信の信頼性を保証する50

ためには、L D P Cなどのキャパシティ・アプローチング誤り訂正符号を、これらの高次変調と組み合わせて利用する必要がある。ここでは、変調形式は次数 $2^Q$ の2乗Q A Mであるものと仮定するが、これにより普遍性が失われることはない。

## 【0031】

2値反射型グレイ符号化(B R G C)が最適であることが分かっているので、これを利用して、コンステレーション・マッパー(例えはQ A M変調器)のラベリングを行う。この実施態様では、Q個の符号化ビット

## 【0032】

## 【数1】

10

$$\{C_{l,q}\}_{q=1}^Q$$

を1グループにまとめ、Q A Mシンボル $\times_b$ にマッピングするものと仮定する。ここで、 $l$ はシンボル指標である。具体的には、ビット $C_{l,q}$ ( $q = 1, 2, \dots, Q/2$ )を使用して、Q A Mコンステレーションの同相(I)ブランチのラベリングを行い、 $C_{l,q+Q/2}$ を使用して、直交(Q)ブランチのラベリングを行う。その結果として、並列復号を利用したときに、これらは同じビット単位容量を有することになる。A W G Nチャネルの出力において、1番目の受信シンボルは、

## 【0033】

## 【数2】

20

$$y_l = x_l + w_l, \quad (1)$$

与えられる。ここで、

## 【0034】

## 【数3】

$w$

は、両側性のスペクトル密度 $N_0/2$ を有する円対称複素ガウス・ノイズのサンプルを表し、 $x_l$ の平均シンボル・エネルギーは $E_s$ であると仮定する。

## 【0035】

30

高次変調によって誘導される非一様ビット単位サブチャネルに集中定理の適用を拡張するために、増補チャネル・アダプタを導入してチャネル対称性を強化している。その結果として、オールゼロ・コードワードの密度発展(D E)を追跡してコードブック全体の性能を予測すれば十分となる。当業者なら、密度発展(D E)が反復システムの設計および解析の基本的な役割を果たしていることが分かるであろう。具体的には、D Eは、符号アンサンブルの漸近的性質を正確に予測することができるので、キャパシティ・アプローチングL D P C符号を設計する実用ツールとして作用している。基本的には、D Eは、異なる2回の畳み込みを必要とする。一方はV N D側用であり、もう一方はC N D側用である。

## 【0036】

40

図1aおよび図1bは、本発明の原理の実施態様によるL D P C符号式ビット・インターバ変調システムのシステム・モデルを示すハイレベル・ブロック図である。図示のように、ビット・インターバ10は、入力L D P C符号(すなわちエンコーダ)12と変調器14の間に挿入される。この設計により、復号しきい値およびエラー・フロアは、より容易に識別され、判定される。図1bに示すように、ビット・インターバは、パリティ・ビットのブロック・インターブ16およびインターブされたビットの階層的割当て18を含むことができる。図1cは、パリティ・ビットのブロック・インターブ16の一例を示す図であり、図1dは、部分的にインターブされた符号化ビットの階層的割当ての一例を示す図である。

## 【0037】

50

図 1 e は、本発明の実施態様による L D P C 符号式ビット・インタリーバ変調システム 20 の通信システム・モデルを示す図である。送信機側は、B C H および L D P C エンコーダ 12 と、ビット・インタリーバ 10 と、変調器（コンステレーション・マッパ）14 とで構成される。さらに、本明細書に開示のプロセスおよび方法を管理するためにプロセッサ 8 a およびメモリ 9 a を使用することもできることは、当業者なら理解するであろう。受信機側は、復調器 24 と、ビット・デインタリーバ 30 と、L D P C および B C H デコーダ 26 と、プロセッサ 8 b およびメモリ 9 b とを含む。この 2 値 L D P C 符号式システムでは、全ての符号化ビットが、集合 {0, 1} 上で一様な分布を有する。C はチャネル・エンコーダの出力を表し、Y は A W G N チャネルの出力を表す。

## 【0038】

10

図 1 f に示す実施例では、独立同分布 (I. I. D.) ビット発生器 32 が、一般的な B I C M (ビット・インタリーブ符号化変調) システム・モデルに組み付けられている。その結果として、入力 C (符号化ビット) と出力 Z (復調器出力のビット単位 L L R ) の間の増補チャネルは、以下の対称条件を満たす。

$$P(Z = z | C = 0) = P(Z = -z | C = 1) \quad (2)$$

特定のラベリング手法によって生じる非一様ユークリッド距離スペクトルにより、ビット単位誤り保護は、ラベリング・ストリングのビット指標によって決まる。

## 【0039】

これに照らして、2<sup>Q</sup> の Q A M コンステレーション・マッパ (変調器) 14、A W G N チャネル 22 および復調器 24 を含む合成チャネルは、Q 個の 2 値入力 A W G N (B I A W G N) サブチャネルに分解することができる。サブチャネル q の入力が離散集合 {0, 1} について一様な分布を有すると仮定すると、その容量は、復調器 24 の出力における入力 C<sub>1, q</sub> と対数尤度比 (L L R) Z<sub>1, q</sub> の間の相互情報量に等しい。ここでは、例示のために、B R G C でラベリングした一様な 1024 Q A M コンステレーションを考える。実際には、平均 L L R の大きさの降順で I および V で示される I ブランチおよび Q ブランチのラベリング方式が同じであるとすると、ビット・レベルで (log<sub>2</sub> 1024) / 2 = 5 個の異なるサブチャネルが存在する。図 2 (a) は、ビット単位平均 L L R をシンボル S N R の関数として表すグラフであり、図 2 (b) は、ビット単位容量をシンボル S N R の関数として表すグラフである。ここで、ビット単位チャネルは、対称 B I A W G N のカテゴリに属し、条件付き確率 P(Z<sub>1, q</sub> | C<sub>1, q</sub>) (q = 1, 2, ..., 5) の関数である。これらのグラフから、特定のビット単位チャネルの信頼性は、そのビット単位平均 L L R およびビット単位容量に比例することが分かる。さらに、これら 2 つのメトリクスが反映する信頼性の順序は一致している。

20

## 【0040】

30

図 1 g は、本発明のシミュレーションの各ステップを示すブロック流れ図である。34 で入力と出力を比較し、ビット誤り率 (B E R) を計算する。

## 【0041】

40

サロゲート・チャネルを用いたビット・インタリーバの設計

サロゲート B E C チャネル

上述のように、所与の L D P C 符号アンサンブルの復号しきい値は、チャネルのタイプ自体によって決まるのではなく、主として有効チャネルの入力と出力の間の相互情報量によって決まることは、当業者なら分かるであろう。このことから、上記で定式化した Q 個の非一様チャネルを、消失確率

## 【0042】

## 【数 4】

$$\left\{ \epsilon_q^0 \right\}_{q=1}^Q$$

の Q 個の 2 元消失チャネル (B E C) で置換することができる。この置換は、

## 【0043】

50

【数5】

$$I(Z_{l,q}; C_{l,q}) = 1 - \varepsilon_q^0, q = 1, 2, \dots, Q, \quad (3)$$

の同等性に基づいている。ここで、この方程式の左辺の項は、一様な入力を有する（B I A W G N）サブチャネルqのビット単位容量を表し、右辺は、まさにB E Cサブチャネルqの容量である。

【0044】

図3(a)は、2値入力Cおよび連続出力Zを有するA W G Nチャネルを示す図である。

図3(b)は、消失確率が $1 - I(Z; C)$ である図3(a)に示すA W G NチャネルのB E Cサロゲート・チャネルを示す図である。数式(3)から、2値A W G Nチャネルおよび2値B E Cサロゲート・チャネルは、2つのチャネルの入力と出力の間の相互情報量が同じである。サロゲートB E Cを用いることにより、復号軌跡を追跡する作業は、各サブチャネルにおける消失確率の展開を観察する作業になるので、復号動作の調査は大幅に簡略化される。その結果、汎用密度発展アルゴリズムの「無限次元代数」によって生じる極めて高い複雑さが回避される。さらに、数式(3)におけるB E C置換により、真の復号軌跡からの逸脱の主原因の1つであるガウス近似を、後続の解析において呼び出す必要もなくなる。

【0045】

実際には、コンステレーション・マッパー（例えば変調器）、A W G Nチャネルおよび復調器を含む合成チャネルは、誤り訂正能力が一様でない任意の組のメモリレス並列チャネルに一般化することができる。数式(3)における置換がこの合成チャネルに限定されることは、当業者なら分かるであろう。例としては、O F D Mシステムの周波数選択サブチャネルや、誤り耐性の要件が一様でない体積ホログラム・メモリ（V H M）システムなどが挙げられる。

【0046】

#### L D P C符号化変調のビット・インタリーブ

表1は、符号化レートが1/4から9/10の範囲であるD V B - S 2で標準化された11個のL D P C符号のV N DおよびC N D次数分布の一例を示している。次数プロファイルの記述を簡略化するために、次数1のV N Dが1つしかないことから、V N Dの次数タイプを3つに減らす。さらに、その相手側と次数が異なるC N Dは1つしかないので、C N Dは一定と仮定することができる。このような小さな摂動は、対応する符号アンサンブルの性能に無視できるほどの影響しか及ぼさないことは既知である。しかし、この簡略化により、本発明のビット・インタリーバの設計の複雑さは大幅に低減される。

【0047】

10

20

30

【表1】

【表1】

| レート  | VND次数<br>カテゴリ | 各カテゴリ中のVNDの番号         | CND次数<br>カテゴリ | 各カテゴリ中の<br>CNDの番号 |    |

|------|---------------|-----------------------|---------------|-------------------|----|

| 1/4  | (12,3,2,1)    | (5400,10800,48599,1)  | (3,4)         | (1,48599)         |    |

| 1/3  | (12,3,2,1)    | (7200,14400,43199,1)  | (4,5)         | (1,43199)         |    |

| 2/5  | (12,3,2,1)    | (8640,17280,38879,1)  | (5,6)         | (1,38879)         |    |

| 1/2  | (8,3,2,1)     | (12960,19440,32399,1) | (6,7)         | (1,32399)         |    |

| 3/5  | (12,3,2,1)    | (12960,25920,25919,1) | (10,11)       | (1,25919)         | 10 |

| 2/3  | (13,3,2,1)    | (4320,38880,21599,1)  | (9,10)        | (1,21599)         |    |

| 3/4  | (12,3,2,1)    | (54000,43200,16199,1) | (13,14)       | (1,16199)         |    |

| 4/5  | (11,3,2,1)    | (6480,45360,12959,1)  | (17,18)       | (1,12959)         |    |

| 5/6  | (13,3,2,1)    | (5400,48600,10799,1)  | (21,22)       | (1,10799)         |    |

| 8/9  | (4,3,2,1)     | (7200,50400,7199,1)   | (26,27)       | (1,7199)          |    |

| 9/10 | (4,3,2,1)     | (6480,51840,6479,1)   | (29,30)       | (1,6479)          |    |

【0048】

本発明の原理の一実施態様では、発明者等は、2値L D P C符号のエッジ・パースペクティブ (edge - perspective) な変数ノード (VND) およびチェック・ノード (CND) の次数分布が、それぞれ

【0049】

【数6】

$$\lambda(x) = \sum_{i=1}^{d_v} \lambda_i x^{i-1}, \quad (4)$$

および

【0050】

【数7】

$$\rho(x) = \sum_{j=1}^{d_c} \rho_j x^{j-1}, \quad (5)$$

で与えられるものと仮定する。ここで、 $\{\lambda_i\}$  は、次数  $i$  の VND に接続されるエッジの割合を示し、 $\{\rho_j\}$  は、次数  $j$  の CND に接続されるエッジの割合を示す。

【0051】

本発明のビット・インタリーバの基本関数は、 $L$  個の符号化ビットをサイズ  $L/Q$  の  $Q$  個のサブセットのみに分割し、次いでそれらを  $q$  番目 ( $q = 1, 2, \dots, Q$ ) の B E C チャネルに割り当てるものである。便宜上、本明細書では、長さ  $L$  の符号を「母符号」と呼び、その  $Q$  個のサブセットのそれを「サブコード」と呼ぶ。サブコード  $q$  の符号化ビットは全て、 $q$  で示されるサロゲート B E C に割り当てられることになる。 $Q$  個のサブコードは、同じ CND パリティ制約を共有するので、ビット・インタリーバの結合により互いに相互作用することになる。従って、これらのサブコードは、非一様並列チャネル用に開発されたマルチレベル符号とは異なる。

【0052】

この L D P C 符号のノード / エッジ・パースペクティブ次数分布から、平均消失確率は、各サブチャネルの消失確率の凸結合となり、重みはビット・インタリーバのプロファイルによって決定される。従って、ビット・インタリーバ設計の目標は、復号しきい値 S N R (メッセージ・パッシング・アルゴリズムを使用するものと仮定する) が最小となるよ

うに、その次数プロファイルの制約付き最適化（母符号の VND および CND の次数分布に制約がある）となる。

【0053】

Q 個のサブセットの基数は同じであるが、それらの VND 次数分布は異なる形態をとることがある。q 番目の BEC サブチャネルに付帯するエッジの数が  $E_q$  で与えられ、母符号のエッジの総数が最大で E になるものと仮定すると、q 番目のサブコードに割り当たるエッジの割合は、

【0054】

【数 8】

$$w_q = \frac{E_q}{E}. \quad (6)$$

10

となる。数式(4)の表記に従うと、q 番目のサブコードのエッジ・パースペクティブ VND 次数分布は、

【0055】

【数 9】

$$\lambda_q(x) = \sum_{i=1}^{d_v} \lambda_{q,i} x^{i-1}, \quad (7)$$

となる。ここで、 $\lambda_{q,i}$  は、次数  $i$  の VND に付帯し、且つ BEC チャネル  $q$  に割り当たられるエッジの割合を表し、 $q = 1, 2, \dots, Q$  に対して、

20

【0056】

【数 10】

$$\lambda_i = \sum_{q=1}^Q w_{q,i}$$

および

【0057】

【数 11】

30

$$\sum_{i=1}^{d_v} \lambda_{q,i} = 1,$$

である。従って、

【0058】

【数 12】

$$\lambda(x) = \sum_{q=1}^Q w_q \lambda_q(x) \quad (8)$$

40

である。

【0059】

LDP C 符号アンサンブルの次数プロファイルの定義に従い、ピット・インタリーバ・アンサンブルの構成( )は、Q 個のエッジ・パースペクティブ次数シーケンスによって、

【0060】

【数 13】

$$\Lambda \doteq \left\{ \lambda_{q,i}; 1 \leq q \leq Q, 1 \leq i \leq d_v \right\}$$

50

として一意的に決定することができる。並列 B E C チャネルの復号プロセスがエルゴード的であると仮定すると、密度発展 ( D E ) は、平均消失確率に関する一次元再帰になる。すなわち、

【 0 0 6 1 】

【 数 1 4 】

$$\varepsilon_q^l = \varepsilon_q^0 \lambda_q (\alpha^l), \quad (9a)$$

$$^1 = 1 - (1 - ^1 - ^1) \quad (9b)$$

【 0 0 6 2 】

【 数 1 5 】

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1}, \quad (9c)$$

である。ここで、上付き文字 l は反復指標を表し、下付き文字 q は B E C サブチャネル番号を表し、 $\varepsilon$  は単一の B E C チャネルの出力における消失確率を表し、 $\beta$  は C N D の出力における平均消失確率を表し、 $w$  は V N D の出力における平均消失確率を表す。最後に、数式 ( 6 ) によって定義されるサブチャネル q のエッジ割合は、 $\lambda$  の関数として以下のように書き換えることができる。

【 0 0 6 3 】

【 数 1 6 】

$$w_q = \frac{\frac{1}{\sum_i (\lambda_{q,i}/i)}}{\sum_{q=1}^Q \frac{1}{\sum_i (\lambda_{q,i}/i)}}, q = 1, 2, \dots, Q. \quad (10)$$

【 0 0 6 4 】

数式 ( 9 a ) ~ ( 9 c ) と数式 ( 10 ) を組み合わせることにより、復号軌跡がビット・インターバル・アンサンブルの次数プロファイル によって決定されることが分かる。

【 0 0 6 5 】

【 数 1 7 】

$$\varepsilon_k^{l-1}$$

に関する

【 0 0 6 6 】

【 数 1 8 】

$$\varepsilon_q^l$$

の偏導関数を取ると、

【 0 0 6 7 】

【 数 1 9 】

$$\frac{\partial \varepsilon_q^l}{\partial \varepsilon_k^{l-1}} = \varepsilon_q^0 w_k \frac{\partial \lambda_q(u)}{\partial u} \frac{\partial \rho(r)}{\partial r}, \quad (11)$$

となる。ここで、 $u = 1 - (r)$  、および

【 0 0 6 8 】

10

20

30

40

【数20】

$$r = 1 - \sum_{k=1}^Q w_k \varepsilon_k^{l-1}.$$

である。S N R が復号しきい値に近い場合には、以下のようになる。

【0069】

【数21】

$$\lim_{\varepsilon_k^{l-1} \rightarrow 0} u = 0, \quad (12b)$$

10

【0070】

【数22】

$$\lim_{\varepsilon_k^{l-1} \rightarrow 0} u = 0, \quad (12b)$$

【0071】

【数23】

$$\lim_{u \rightarrow 0} \lambda_q(u) = \lambda_{q,2}, \quad (12c)$$

20

【0072】

【数24】

$$\lim_{r \rightarrow 1} \rho'(r) = \sum_{j=2}^{d_q} (j-1) \rho_j. \quad (12d)$$

30

ティラー級数を利用すると、数式(11)を、

【0073】

【数25】

$$\varepsilon_k^{l-1} \approx 0.$$

の近傍に拡張することができる。一次の項は維持し、数式(12c)および(12d)における限界値を考慮すると、以下のようになる。

【0074】

【数26】

$$\varepsilon'_q = \varepsilon_q^0 \rho'(1) \lambda_{q,2} \sum_{k=1}^Q w_k \varepsilon_k^{l-1}, \quad l > 0, 1 \leq q \leq Q. \quad (13)$$

40

【0075】

【数27】

$$\{\varepsilon'_q, 1 \leq q \leq Q\}$$

50

をまとめて列ベクトル

【0 0 7 6】

【数28】

$$\Theta' = [\varepsilon_1' \varepsilon_2' \cdots \varepsilon_Q']^T$$

とし(上付き文字Tは転置を表す)、(q, k)エントリが

【0 0 7 7】

【数29】

10

$$\eta_{q,k} = \varepsilon_q^0 \rho'(1) \lambda_{q,2} w_k, \quad 1 \leq q, k \leq Q. \quad (14)$$

で定義される定数行列  $\Theta'$  を導入することにより、復号しきい値 S N R 周辺のメッセージ・パッシング・デコーダの動的挙動は、以下の1次の線形差分方程式で近似することができる。

$$1 = 1 - 1 \quad (15)$$

ここでは、 $\lambda$ は対角化することができ、その固有値の大きさは  $|\lambda_1| > |\lambda_2| > \dots > |\lambda_Q|$  のように降順に配列されると仮定するが、これにより普遍性が失われることはない。その結果、反復復号が収束するための必要条件は、以下のようにになる。

$$|\lambda_1| < 1 \quad (16)$$

【0 0 7 8】

20

要約すると、所与のL D P C 符号がQ個の非一様チャネルを介して伝送され、メッセージ・パッシング・アルゴリズムで復号される場合、その性能は、エンコーダとチャネルの間に挿入されるビット・インタリーバの次数プロファイル  $\lambda$  によって決まるうことになる。特に、復号しきい値 S N R  $\rho$  は  $\lambda$  の関数であり、この依存性は、 $\rho(\lambda)$  として明示的に表現することができる。数式(4)、(7)、(10)および(16)の制約を結合することにより、符号依存ビット・インタリーバの構成を、以下の制約付き(10)最適化問題の解として定式化することができる。

$$\min \rho(\lambda) \quad (17a)$$

30

$$\text{ただし } |\lambda_1| < 1 \quad (17b)$$

【0 0 7 9】

【数30】

$$\sum_{q=1}^Q w_q \lambda_{q,i} = \lambda_i, \quad 1 \leq i \leq d_v; \quad (17c)$$

【0 0 8 0】

【数31】

$$\sum_{i=1}^{d_v} \lambda_{q,i} = 1, \quad 1 \leq q \leq Q; \quad (17d)$$

40

【0 0 8 1】

【数32】

$$w_q = \frac{\sum_i (\lambda_{q,i}/i)}{\sum_{q'=1}^Q (\sum_i \lambda_{q',i}/i)}, \quad 1 \leq q \leq Q; \quad (17e)$$

$w_q, \quad 1 \leq q \leq Q, \quad 1 \leq i \leq d_v \quad (17f)$

ここで、

50

【0082】

【数33】

$$\{\lambda_i\}_{i=1}^{d_p}$$

は、アприオリに母符号のエッジ・パースペクティブVND次数分布として知られる。

【0083】

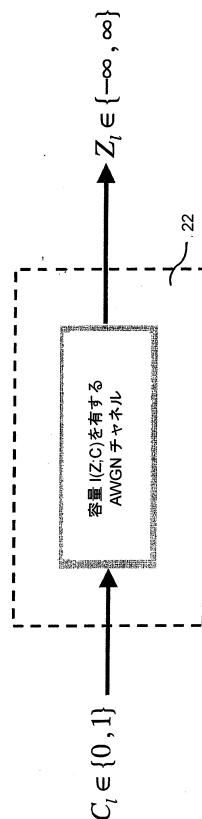

図4は、本発明の一実施態様による、AWGNチャネル条件下でビット・インターバルをLDP符号および変調に適合させる方法40を示すハイレベル流れ図である。上述のように、変調器、復調器および初期SNRを有するAWGNチャネルを含む合成チャネルについて、またで決定される所与のビット・インターバル構成について、最初に、等価なQ個の並列BIAWGNチャネルの容量を計算する(42)。この計算が終わったら、44で、計算した容量の同等性に基づいてQ個のサロゲート2元消失チャネル(BEC)によってQ個のBIAWGNチャネルをモデル化(近似)し、初期消失確率を得る(上記の数式3を参照)。次いで、消去確率がゼロ(0)に収束するかどうかについて、反復密度発展判定を行う(46a)(上記の数式9a~9cを参照)。(I)収束すると判定された場合には、SNRを所与の刻み幅だけ低減する(47)。この所与の刻み幅は、例えば所望の解像度に基づいて決めることができ、例えば0.1dBとすることができるることは、当業者なら分かるであろう。

【0084】

次いで、初期消失確率を決定し(48)、密度発展を使用して、消失確率がゼロに収束するかどうかを判定する(46b)。46bで収束すると判定された場合には、SNRを再度低減し(47)、このプロセスを繰り返す。46bで収束しないと判定された場合には、直前のSNRを、当該所与のビット・インターバル構成のしきい値SNRであるものとして特定し(50)、記憶する(58)。(II)ステップ46aで消失確率がゼロに収束しない場合には、SNRを所与の刻み幅だけ増加させ(52)、上記と同じプロセスを繰り返し、増加したSNRに対する消失確率を決定し(54)、密度発展を使用して、消失確率がゼロに収束するかどうかを判定する(46c)。46cで消失確率がゼロに収束する場合には、そのSNRを、当該所与のビット・インターバル構成の復号しきい値SNRであるものとして特定し(56)、次いでやはり記憶する(58)。ステップ46cで消失確率がゼロに収束しない場合には、SNRを再度増加させ(52)、このプロセスを上述のように引き続き行う。本発明の趣旨によって所与のビット・インターバル構成のしきい値SNRを決定する方法が複数存在することは、当業者なら分かるであろう。所与の、または最初のビット・インターバル構成について内ループを実行したら、ビット・インターバル構成を変更し(60)、このプロセスを再び実行する。このプロセス中のある時点で、例えば時間制約および/または確度要件に応じて、ビット・インターバル構成を選択し、この選択に従ってビット・インターバルを構成する(62)。

【0085】

また、最小のしきい値SNRを得るためにには、ビット・インターバル構成を変更しなければならないことは、当業者なら分かるであろう。これを行う際には、最低の復号しきい値SNRをもたらす正しいを見つけることは困難である場合もあり、多くのサンプルをテストすることになることがあることが分かる。従って、停止点(62)を主観的なものにしてユーザ/設計者が設定するという、代替の実施態様も考えられる。これは、テストを停止し、その時点で得られている最良の、すなわち最低の復号しきい値SNRをとるブルート・フォース手法と呼ばれることがある。例えば、1つのブルート・フォース手法は、単に復号しきい値SNRのテストに関するタイミング制約である場合もある。

【0086】

最小または最低のしきい値SNRが決定または選択されたら(62)、対応するビット・インターバル構成に従ってビット・インターバルを構成する。そのように構成したら、符号をビット・インターバルにすることができる。

## 【0087】

提案するビット・インタリーバの設計方法の有効性を検証するために、発明者等は、DVB-S2/T2標準に指定される短いブロック長( $L = 16200$ )のLDPC符号をビット・インタリーバの母符号として使用して、次世代のケーブル・チャネルでの採用が提案されている、BRGCでラベリングした2乗1024QAMおよび4096QAMコンステレーションを考える。

## 【0088】

本発明が提供する解析的研究とは対称的に、「CND衝突」を回避することを基本とするアドホックなビット・インタリープ方法がDVB-T2では使用されており、これはDVB-C2に対しても提案されている。ここで、「CND衝突」という用語は、3つ以上のビットが同じシンボルにマッピングされ、同じパリティ方程式でチェックされる現象を指すものである。一般に、CND衝突を完全に回避することは困難であり、実現可能性をブルート・フォースに探索すれば、計算負荷の高い組合せプログラミング問題を必然的に伴う。それでも、DVB-S2符号の疑似周期的構造の規則性を利用することにより、研究者は、一部の符号レートについてはCND衝突の発生を回避することができるビット・インタリープ手法を考案している。10

## 【0089】

しかし、発明者等は、特に高次数のVNDを共通のCNDを介して低次数のVNDに接続する場合には、CND衝突の発生は必ずしも悪いとは言えないと考えている。それは、高次数のVNDが、通常はより信頼性の高いLLRメッセージを担持しており、このことが、低次数のVNDが速い復号収束を達成する助けになる可能性があるからである。従って、発明者等の設計およびシミュレーションでは、CND衝突の発生を無視し、符号化ビットを、それらの自然な順序で、によって指定される最適な次数プロファイルに従って、単純にコンステレーション・マップに割り当てる。20

## 【0090】

本項を通じて、発明者等は、モンテカルロ・シミュレーションの結果を考慮し、共通の基準として「非インタリープ」(連続的なビットのグループ化およびコンステレーション・マップへのマッピング)を使用している。インタリープ・タイプ/非インタリープ・タイプのそれぞれで、フレーム誤りが50検出された時点で、シミュレーションの試行を終了している。2種類の符号レート(11/15および7/9)および2種類の変調形式(4096QAMおよび1024QAM)について、情報ビットの復号BERの比較を、図5から図8に与える。これらの曲線から、サロゲートBECチャネルを用いて設計されたビット・インタリーバは、CND衝突を回避しようとするインタリーバに優る、有意なパワーの節約(0.4~0.7dBの利得)を達成することができる事が分かる。これに加えて、どちらの場合でも、ビット・インタリープを行わない場合よりも性能が優れており、このことは、不規則なLDPC符号を非一様なチャネルを介して伝送するときには、スペクトル効率とパワー効率の兼ね合いを図るために、専用ビット・インタリーバが必要であることを実証している。30

## 【0091】

当業者なら、本明細書の教示に基づき、本発明の原理の上記その他の特性および利点を容易に理解することができる。本発明の原理の教示は、様々な形態のハードウェア、ソフトウェア、ファームウェア、特殊目的プロセッサ、またはそれらの組合せによって実施することができることを理解されたい。40

## 【0092】

本発明の原理の教示は、ハードウェアとソフトウェアの組合せとして実施されることが最も好ましい。さらに、ソフトウェアは、プログラム記憶装置に実装されたアプリケーション・プログラムとして実施することができる。アプリケーション・プログラムは、任意の適当なアーキテクチャを備える機械にアップロードして実行することができる。この機械は、1つまたは複数の中央処理装置(CPU)などのハードウェア、ランダム・アクセス・メモリ(RAM)、および入出力(I/O)インターフェースを有するコンピュータ・50

プラットフォームで実施されることが好ましい。コンピュータ・プラットフォームは、オペレーティング・システムおよびマイクロ命令コードも備えることができる。本明細書に記載する様々なプロセスおよび機能は、CPUによって実行することができる、マイクロ命令コードの一部またはアプリケーション・プログラムの一部あるいはそれらの組合せの何れかにすることができる。さらに、追加のデータ記憶装置や印刷装置など、その他の様々な周辺装置をコンピュータ・プラットフォームに接続することもできる。

#### 【0093】

さらに、添付の図面に示すシステム構成要素および方法の一部はソフトウェアで実施することが好ましいので、システム構成要素間またはプロセス機能ブロック間の実際の接続は、本発明の原理をプログラミングする方法によって異なっていてもよいことも理解されたい。本明細書の教示があれば、当業者なら、本発明の原理の上記の実施態様または構成およびそれと同様の実施態様または構成を思いつくことができるであろう。

10

#### 【0094】

本明細書では、添付の図面を参照して例示的な実施例について述べたが、本発明の原理は、これらの具体的な実施例に限定されるわけではなく、当業者なら、本発明の原理の範囲または趣旨を逸脱することなく様々な変更および修正をそれらの実施例に加えることができることを理解されたい。そうした変更および修正は全て、添付の特許請求の範囲に記載する本発明の原理の範囲に含まれるものとする。

#### [付記1]

ビット・インターバルを LDPC 符号および変調に適合させる方法であって、

非一様並列 AWGN チャネルのビット単位容量を計算するステップ(42)と、

前記 AWGN チャネルを、消失確率を有する 1 組の Q 個のサロゲート 2 元消失チャネル

(BEC) で近似するステップ(44)と、

消失確率密度分布を用いて、復号しきい値信号対雑音比(SNR)が、ビット・インターバル構成に対して最低の復号しきい値信号対雑音比をもたらすかどうかを判定するステップ(46、58、60)と、

20

判定した最低の復号しきい値信号対雑音比に対応するビット・インターバル構成に基づいて、前記ビット・インターバルを構成するステップ(58)と、

を含む、前記方法。

#### [付記2]

30

前記判定するステップ(46)が、

前記消失確率がゼロに収束する場合に、前記 SNR を所定の刻み幅だけ低減するステップ(47)と、

前記低減した SNR に対する消失確率を決定するステップ(48)と、

前記低減した SNR の消失確率がゼロに収束するかどうかを判定するステップ(46b)

と、

前記消失確率がゼロに収束しない場合に、前記低減前の SNR をビット・インターバル構成の復号しきい値 SNR として特定するステップ(50)と、

をさらに含む、付記1に記載の方法。

#### [付記3]

40

前記判定するステップ(46)が、

前記消失確率がゼロに収束しない場合に、前記 SNR を所定の刻み幅だけ増加するステップ(52)と、

前記増加した SNR に対する消失確率を決定するステップ(54)と、

前記増加した SNR の消失確率がゼロに収束するかどうかを判定するステップ(46c)

と、

前記消失確率がゼロに収束する場合に、前記増加した SNR をビット・インターバル構成の復号しきい値 SNR として特定するステップ(56)と、

をさらに含む、付記2に記載の方法。

#### [付記4]

50

各ビット・インターバ構成および対応する決定した最低の復号しきい値 S N R を記憶するステップ(58)と、

ビット・インターバ構成( )を変更するステップ(60)と、

前記判定するステップを実行して、前記変更したビット・インターバ構成の復号しきい値 S N R を決定するステップと、

前記最低の復号しきい値 S N R を有するビット・インターバ構成を選択するステップ(62)と、

前記選択した構成を有するビット・インターバを構成するステップ(62)と、

をさらに含む、付記3に記載の方法。

[付記5]

10

前記計算したビット単位容量が、前記並列 A W G N チャネルの2値入力と有効出力の間の相互情報量に基づいてビット単位容量を計算するステップを含み、前記近似が、前記計算したビット単位容量の同等性に基づいて行われる、付記1に記載の方法。

[付記6]

前記構成したビット・インターバを用いて前記符号をビット・インターブするステップ(58)をさらに含む、付記1に記載の方法。

[付記7]

前記判定するステップ(46)が、前記復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布を決定するステップをさらに含む、付記2に記載の方法。

20

[付記8]

前記平均消失確率を決定する前記ステップが、

前記 L D P C 符号のノード / エッジ・パースペクティブ次数分布を識別するステップと

、各サブチャネルの消失確率の凸結合を行うステップと、

をさらに含む、付記7に記載の方法。

[付記9]

前記密度分布のモデル化が、

【数1】

$$\varepsilon_q^l = \varepsilon_q^0 \lambda_q(\alpha^l),$$

30

$$= 1 - (1 - )^{l-1}$$

【数2】

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1},$$

から導出される、付記7に記載の方法。

[付記10]

ビット・インターバの次数プロファイルの最適化を制約することにより、前記復号しきい値 S N R を最小にするステップをさらに含む、付記3に記載の方法。

40

[付記11]

ビット・インターバを L D P C 符号および変調に適合させる装置であって、

非一様並列 A W G N チャネルのビット単位容量を計算し、前記 A W G N チャネルを1組のサロゲート2元消失チャネルで近似し、消失確率密度分布を用いて1つまたは複数のビット・インターバ構成のそれぞれに対して復号しきい値 S N R を決定するように構成されたプロセッサ(8)であり、決定した各 S N R に対して消失確率を決定するプロセッサ(8)と、

前記1つまたは複数の決定した復号しきい値 S N R および対応するビット・インターバ構成を記憶するメモリ(9)と、

記憶された1つまたは複数の決定された復号しきい値 S N R から選択された最低の復号

50

しきい値 S N R に対応するビット・インターバ構成に基づいて前記プロセッサによって構成されたビット・インターバ(10)と、

を備える、前記装置。

## [付記12]

前記プロセッサが、前記決定された1つまたは複数の復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布をさらに決定する、付記11に記載の装置。

## [付記13]

前記並列 A W G N チャネルの2値入力と有効出力の間の相互情報量に基づいて前記ビット単位容量を計算する、付記11に記載の装置。

10

## [付記14]

前記ビット・インターバが、各しきい値 S N R に対応する決定された消失確率のそれから導出された復号反復の復号収束条件に基づいて前記符号のビット・インターブを行いうるように構成される、付記11に記載の装置。

## [付記15]

前記プロセッサが、前記 L D P C 符号のノード／エッジ・パースペクティブ次数分布を識別し、各サブチャネルの消失確率の凸結合を行うことによって、前記平均消失確率を決定する、付記12に記載の装置。

## [付記16]

前記密度分布のモデル化が、

20

## 【数3】

$$\varepsilon'_q = \varepsilon_q^0 \lambda_q(\alpha'),$$

$$\beta^{l-1} = 1 - (1 - \beta^{l-1})$$

## 【数4】

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1},$$

30

から導出される、付記12に記載の装置。

## [付記17]

受信側ビット・インターバを L D P C 符号および変調に適合させる方法であって、

非一様並列 A W G N チャネルのビット単位容量を計算するステップ(42)と、

前記 A W G N チャネルを、消失確率を有する1組の Q 個のサロゲート2元消失チャネル

(B E C)で近似するステップ(44)と、

消失確率密度分布を用いて、復号しきい値信号対雑音比(S N R)が、ビット・インターバ構成に対して最低の復号しきい値信号対雑音比をもたらすかどうかを判定するステップ(46、58、60)と、

40

判定した最低の復号しきい値信号対雑音比に対応するビット・インターバ構成に基づいて、前記受信側ビット・インターバを構成するステップ(58)と、

を含む、前記方法。

## [付記18]

前記判定するステップ(46)が、

前記消失確率がゼロに収束する場合に、前記 S N R を所定の刻み幅だけ低減するステップ(47)と、

前記低減した S N R に対する消失確率を決定するステップ(48)と、

前記低減した S N R の消失確率がゼロに収束するかどうかを判定するステップ(46b)

)と、

50

前記消失確率がゼロに収束しない場合に、前記低減前の S N R をビット・インターバ構成の復号しきい値 S N R として特定するステップ(50)と、

をさらに含む、付記17に記載の方法。

## [付記19]

前記判定するステップ(46)が、

前記消失確率がゼロに収束しない場合に、前記 S N R を所定の刻み幅だけ増加するステップ(52)と、

前記増加した S N R に対する消失確率を決定するステップ(54)と、

前記増加した S N R の消失確率がゼロに収束するかどうかを判定するステップ(46c)と、

前記消失確率がゼロに収束する場合に、前記増加した S N R をビット・インターバ構成の復号しきい値 S N R として特定するステップ(56)と、

をさらに含む、付記18に記載の方法。

## [付記20]

各ビット・インターバ構成および対応する決定した最低の復号しきい値 S N R を記憶するステップ(58)と、

ビット・インターバ構成( )を変更するステップ(60)と、

前記判定ステップを実行して、前記変更したビット・インターバ構成の復号しきい値 S N R を決定するステップと、

前記最低の復号しきい値 S N R を有するビット・インターバ構成を選択するステップ(62)と、

前記選択した構成を有するビット・インターバを構成するステップ(62)と、

をさらに含む、付記19に記載の方法。

## [付記21]

前記計算したビット単位容量が、前記並列 A W G N チャネルの 2 値入力と有効出力の間の相互情報量に基づいてビット単位容量を計算するステップを含み、前記近似が、前記計算したビット単位容量の同等性に基づいて行われる、付記17に記載の方法。

## [付記22]

前記構成したビット・インターバを用いて前記符号をビット・インターブするステップ(58)をさらに含む、付記17に記載の方法。

## [付記23]

前記判定するステップ(46)が、前記復号しきい値 S N R から、所定の線形差分方程式からモデル化された平均消失確率密度分布を決定するステップをさらに含む、付記18に記載の方法。

## [付記24]

前記平均消失確率を決定する前記ステップが、

前記 L D P C 符号のノード / エッジ・パースペクティブ次数分布を識別するステップと、

各サブチャネルの消失確率の凸結合を行うステップと、

をさらに含む、付記23に記載の方法。

## [付記25]

前記密度分布のモデル化が、

## 【数5】

$$\varepsilon'_q = \varepsilon_q^0 \lambda_q(\alpha'),$$

$$= 1 - (1 - )^{-1}$$

## 【数6】

$$\beta^{l-1} = \sum_{q=1}^Q w_q \varepsilon_q^{l-1},$$

から導出される、付記23に記載の方法。

## [付記26]

ビット・インターバルの次数プロファイルの最適化を制約することにより、前記復号しきい値SNRを最小にするステップをさらに含む、付記19に記載の方法。

## [付記27]

10

受信側ビット・インターバルをLDPC符号および変調に適合させる装置であって、

非一様並列AWGNチャネルのビット単位容量を計算し、前記AWGNチャネルを1組のサロゲート2元消失チャネルで近似し、消失確率密度分布を用いて1つまたは複数のビット・インターバル構成のそれぞれに対して復号しきい値SNRを決定するように構成されたプロセッサ(8)であり、決定した各SNRに対して消失確率を決定するプロセッサ(8)と、

前記1つまたは複数の決定した復号しきい値SNRおよび対応するビット・インターバル構成を記憶するメモリ(9)と、

記憶された1つまたは複数の決定された復号しきい値SNRから選択された最低の復号しきい値SNRに対応するビット・インターバル構成に基づいて前記プロセッサによって構成された受信側ビット・インターバル(10)と、

を備える、前記装置。

## [付記28]

20

前記プロセッサが、前記決定された1つまたは複数の復号しきい値SNRから、所定の線形差分方程式からモデル化された平均消失確率密度分布をさらに決定する、付記27に記載の装置。

## [付記29]

前記並列AWGNチャネルの2値入力と有効出力の間の相互情報量に基づいて前記ビット単位容量を計算する、付記27に記載の装置。

## [付記30]

30

前記ビット・インターバルが、各しきい値SNRに対応する決定された消失確率のそれぞれから導出された復号反復の復号収束条件に基づいて前記符号のビット・インターバルを行うように構成される、付記27に記載の装置。

## [付記31]

前記プロセッサが、前記LDPC符号のノード/エッジ・パースペクティブ次数分布を識別し、各サブチャネルの消失確率の凸結合を行うことによって、前記平均消失確率を決定する、付記28に記載の装置。

## [付記32]

前記密度分布のモデル化が、

## 【数7】

40

$$\varepsilon'_q = \varepsilon_q^0 \lambda_q(\alpha'),$$

$${}^l = 1 - (1 - {}^{l-1})$$

## 【数8】

$$\beta'^{-1} = \sum_{q=1}^Q w_q \varepsilon_q'^{-1},$$

50

から導出される、付記28に記載の装置。

【図 1 a】

【図1b】

【図 1 c】

【図 1 d】

【図 1 e】

【図 1 g】

【図 2 a】

【図 2 b】

【図 3 a】

【図3 b】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 レイ , チン

アメリカ合衆国 ニュージャージー州 ニュー・ブランズウイック ラトガース・ユニバーシティ

シーピーオー・ウエイ 18705

(72)発明者 ガオ , ウエン

アメリカ合衆国 ニュージャージー州 ウエスト・ワインザー ワーウィック・ロード 73

審査官 岡 裕之

(56)参考文献 特開2009-296586 (JP, A)

Jing Lei et al., Code-Matched Interleaver Design over Surrogate Channels, Wireless Communications and Networking Conference, 2009. WCNC 2009. IEEE, 2009年 4月 8日

Jing Lei et al., Matching graph connectivity of LDPC codes to high-order modulation by bit interleaving, Communication, Control, and Computing, 2008 46th Annual Allerton Conference on, 2008年 9月26日, pp.1059-1064

Hyun-Koo Yang et al., Optimization of degree-profile matching interleavers for LDPC-coded modulation, Communications Letters, IEEE, 2006年12月, Vol.10, No.12, pp.843-845

Fei Peng et al., Surrogate-channel design of universal LDPC codes, Communications Letters, IEEE, 2006年 6月, Vol.10, No.6, pp.480-482

(58)調査した分野(Int.Cl. , DB名)

H 03M 13 / 27

H 03M 13 / 19

H 04L 1 / 00

I E E E X p l o r e

C i N i i