(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5028811号

(P5028811)

(45) 発行日 平成24年9月19日(2012.9.19)

(24) 登録日 平成24年7月6日(2012.7.6)

(51) Int.Cl.

H01L 21/3065 (2006.01)

H01S 5/02 (2006.01)

F 1

H01L 21/302 105A

H01S 5/02

請求項の数 4 (全 11 頁)

(21) 出願番号 特願2006-27398 (P2006-27398)

(22) 出願日 平成18年2月3日 (2006.2.3)

(65) 公開番号 特開2007-208134 (P2007-208134A)

(43) 公開日 平成19年8月16日 (2007.8.16)

審査請求日 平成20年12月24日 (2008.12.24)

(73) 特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100092657

弁理士 寺崎 史朗

(74) 代理人 100110582

弁理士 柴田 昌聰

(74) 代理人 100108257

弁理士 近藤 伊知良

(72) 発明者 藤本 和徳

神奈川県横浜市栄区田谷町1番地 住友電

気工業株式会社横浜製作所内

最終頁に続く

(54) 【発明の名称】 化合物半導体光デバイスを作製する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

化合物半導体光デバイスを作製する方法であって、

基板上に、III-V 化合物半導体から成る活性領域を含む化合物半導体領域を形成する工程と、

有機シラン系原料および酸素原料を含む成膜ガスを供給して、シリコン化合物からなる

誘電体マスク膜を前記化合物半導体領域上に誘導結合プラズマ-化学的気相成長法で堆積

する工程と、

前記誘電体マスク膜にパターンを形成して誘電体マスクを形成する工程と、

前記誘電体マスクを用いて、前記化合物半導体領域のドライエッチングを行って、メサ

高さ  $h$  が  $3.5 \mu m$  以上のメサ形状の化合物半導体領域を形成する工程とを備え、

前記ドライエッチングは、バイアス電力を供給し炭化水素と水素の混合ガスを用いた R

IE エッチングであり、

前記誘電体マスク膜は、前記メサ形状の化合物半導体領域を形成する工程後の該化合物

半導体のメサ高さ  $h$  との間に前記誘電体マスクの厚み  $H$  が  $H = h / 3$  の関係を満しており、

前記エッチングにおいて、前記誘電体マスクの側面と上面によるマスクエッジの変形が

前記エッチングのスパッタ成分により引き起こされ、該マスクエッジに傾斜面が形成され、

前記誘電体マスクが単層のシリコン化合物からなる、ことを特徴とする方法。

10

20

**【請求項 2】**

前記バイアス電力は 50 ~ 300 W であり、

前記 RIE エッチングは ECR - RIE エッチングである、ことを特徴とする請求項 1 に記載された方法。

**【請求項 3】**

前記有機シラン系原料は TEOS を含み、

前記酸素原料は酸素分子を含み、

前記誘電体マスクの材料はシリコン酸化物からなる、請求項 1 または請求項 2 に記載された方法。

**【請求項 4】**

前記炭化水素は CH<sub>4</sub> を含む、請求項 1 ~ 請求項 3 のいずれか一項に記載された方法。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、化合物半導体光デバイスを作製する方法に関する。

**【背景技術】****【0002】**

特許文献 1 には、化合物半導体のエッチング方法および半導体レーザ素子の製造方法が記載されている。このエッチング方法によれば、化合物半導体のドライエッチングにおいて、垂直で平滑なエッチング面が提供される。具体的には、III - V 族化合物半導体または II - VI 族化合物半導体は、約 10<sup>10</sup> cm<sup>-3</sup> 以上の密度のプラズマを発生するプラズマ源を備えたドライエッチング装置に、ハロゲン元素を含むガスと窒素ガスとの混合ガスを供給して、ドライエッチングされる。(ハロゲン元素を含むガスの流量) / (窒素ガスの流量) は 1 以上であり、エッチング反応中の圧力は、約 1 mTorr または 1 mTorr 以上である。

20

**【0003】**

非特許文献 1 には、化合物半導体デバイス製造においてドライエッチングによりメサ形状を得る方法が記載されている。メサ形状を得る方法として 2 つの方法が説明されている。一方の方法では、ドライエッチングのために SiN、SiO<sub>2</sub> 等の絶縁膜を厚さ 0.3 μm からなる薄膜マスクを用いる。他の方法では、ドライエッチングのために多層マスクを用いる。多層マスクは、例えば、200 ~ 300 で熱処理されて硬化した 1.5 μm 厚のレジスト(下層)、Ti 等からなる 0.1 μm 厚のメタルマスク(中間層)からなる。

30

【特許文献 1】特開平 9 - 283505 号公報

【非特許文献 1】半導体ドライエッチング技術、産業図書、155 頁 ~ 158 頁

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

非特許文献 1 に記載された薄膜マスクを用いるエッチング方法では、エッチング中に、半導体領域がエッチングにより加工されるだけでなく、マスクの形状もエッチングの進行と共に変化する。このため、エッチングされた半導体領域の形状が、裾を引くリッジ形状になる。このエッチングでは、エッチングマスクとして厚さ 0.3 μm 程度の SiN、SiO<sub>2</sub> 等の絶縁膜を用いて反応性イオンエッチング(RIE) を行う。RIE 法では、エッチングが進行するにつれて、マスク側面とマスク上面とからなるエッジから進行する(マスクエッジの変形)。この変形はスパッタ成分により引き起こされマスク上部のエッジから 45 度の角度方向に進み、これによりマスク上部および側面と約 135 度の角度を成す傾斜面が形成される。マスクの変形は、垂直方向のエッチング速度の 8 ~ 10 倍の消失速度で進む。マスクの変形により側面が消失した後は、エッチングの進行に伴いマスク幅が小さくなる(マスク幅の後退)。ドライエッチング中にマスク幅が縮小すると、メサ側

40

50

面が裾を引くようになり、結果的にメサ幅は基板に近づくにつれて広くなる。メサのエッティング角度をほぼ垂直に維持しながらドライエッティングを行うことができない。つまり、ドライエッティングにより直角に近い段差を形成することができない。

【0005】

エッティングマスクとして厚さ1.5μm程度の硬化レジスト、厚さ0.1μm程度のTi等メタルマスクの複合マスクを用いてエッティングを行う。この方法では、マスクとして使用した下層レジストがエッティングによりポリマー化してメサ側面に付着する。この付着したポリマーは、埋め込みエピ成長工程において、有機物コンタミネーションの原因となる。付着有機物は、高温ベーク工程および反応性イオンエッティング工程を経ているので、容易に除去できない。また、発明者の知見によれば、付着有機物は、埋め込みモフォロジーの悪化を引き起こす。これ故に、この方法は、汚染の少ない清浄表面が必要とされる工程、例えば、半導体レーザの活性層を含むメサをドライエッティングで形成する工程、では使用できない。

【0006】

本発明は、このような事情を鑑みてなされたものであり、エッティング中にマスク幅の大きな変化を生じることがない、化合物半導体光デバイスを作製する方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一側面は、化合物半導体光デバイスを作製する方法に係る。この方法は、(a)有機シラン系原料および酸素原料を含む成膜ガスを供給して、シリコン化合物からなる誘電体マスク膜を化合物半導体領域上に誘導結合プラズマ-化学的気相成長法で堆積する工程と、(b)前記誘電体マスク膜にパターンを形成して誘電体マスクを形成する工程と、(c)前記誘電体マスクを用いて、前記化合物半導体領域のドライエッティングを行ってメサ高さhが3.5μm以上のメサ形状の化合物半導体領域を形成する工程とを備え、前記誘電体マスクが単層のシリコン化合物からなる。

【0008】

この発明によれば、誘電体マスクのためのシリコン化合物が誘導結合プラズマ-化学的気相成長法で形成されるので、例えば1マイクロメートル以上の厚みを有する厚膜で単層の誘電体マスクを得ることができる。厚膜の誘電体マスクを用いて化合物半導体領域のドライエッティングを行うので、メサ高さが3.5μm以上の深いメサを加工する場合でも、エッティング中にマスクエッジの消失が生じてもマスク幅が小さくなることはない。これ故に、所望のメサ形状の化合物半導体領域を形成できる。

【0009】

本発明に係る方法では、前記誘電体マスクの厚みHが、メサ形状加工した化合物半導体のメサ高さhとの間に、

$$H = h / 3$$

の関係を満たす誘電体マスク膜が形成される。

【0010】

この発明によれば、メサ形状の化合物半導体領域を形成する前記工程においてドライエッティングが進行するにつれて、前記誘電体マスクが該マスクの上面のエッジから後退すると共に、この後退に伴い該マスクの側面の高さH<sub>M</sub>が小さくなる場合でも、エッティング量が大きく高いメサ形状を作製することができる。

【0011】

本発明に係る方法では、前記有機シラン系原料はTEOS(テトラエトキシシラン)を含み、前記酸素原料は酸素分子を含み、前記誘電体マスクの材料はシリコン酸化物からなることが好ましい。

【0012】

この方法によれば、膜厚を厚くしても膜中の応力が小さいシリコン酸化物を誘電体マスクのために形成できる。

10

20

30

40

50

## 【0013】

本発明に係る方法では、前記ドライエッチングのためのガスは炭化水素を含むことが好ましい。この方法によれば、化合物半導体のドライエッチングが可能であり、所望のメサ形状の化合物半導体領域を形成できる。

## 【0014】

本発明の上記の目的および他の目的、特徴、並びに利点は、添付図面を参照して進められる本発明の好適な実施の形態の以下の詳細な記述から、より容易に明らかになる。

## 【発明の効果】

## 【0015】

以上説明したように、本発明によれば、エッチング中にマスク幅の大きな変化を生じることがない、化合物半導体光デバイスを作製する方法が提供される。 10

## 【発明を実施するための最良の形態】

## 【0016】

本発明の知見は、例示として示された添付図面を参照して以下の詳細な記述を考慮することによって容易に理解できる。引き続いて、添付図面を参照しながら、本発明の化合物半導体光デバイスを作製する方法に係る実施の形態を説明する。可能な場合には、同一の部分には同一の符号を付する。

## 【0017】

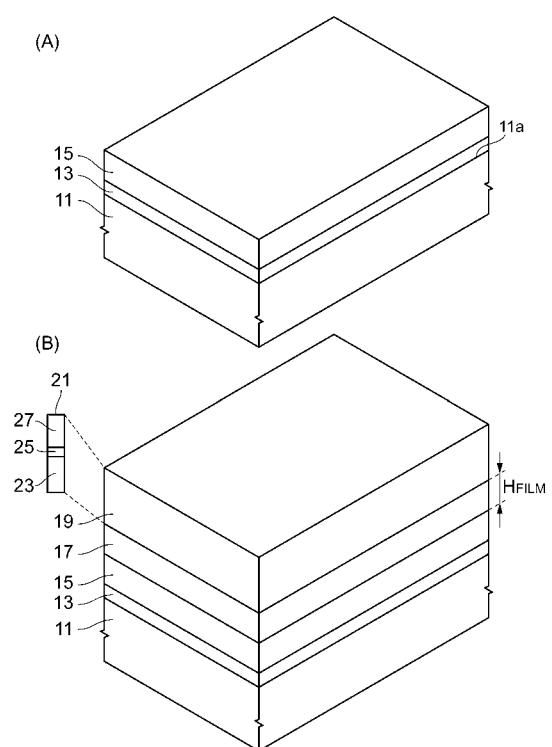

図1(A)は、化合物半導体光デバイスを作製する方法における結晶成長工程を示す模式図である。InP半導体からなる表面11aを有する基板11を準備する。基板11は導電性を示しており、例えば、n型InP半導体からなることができる。基板11上に、III-V化合物半導体から成る活性領域13を成長する。活性領域13は、例えばバルク構造、単一量子井戸構造、多重量子井戸構造といった構造を有することができる。次いで、活性領域13上に、III-V化合物半導体膜15を成長する。III-V化合物半導体膜15は、例えばp型InP半導体からなることができる。活性領域13およびIII-V化合物半導体膜15の成長は、例えば有機金属気相成長炉を用いて行われる。 20

## 【0018】

図1(B)は、誘電体マスクのための多層構造および誘電体マスク膜を形成するマスク作製工程を示す図面である。誘電体マスク膜17をIII-V化合物半導体膜15上に形成する。誘電体マスク膜17は、有機シラン系原料および酸素原料を含む成膜ガスを供給して誘導結合プラズマ気相成長(ICP-CVD)装置を用いて形成される。好ましく、誘電体マスク膜17はシリコン化合物からなり、シリコン化合物は例えばシリコン酸化物等を含むことができる。誘電体マスク膜17の厚みH<sub>FILM</sub>は1マイクロメートル以上である。次いで、誘電体マスク膜17にパターンを形成して誘電体マスクを形成する。有機シラン系原料としては、例えばTEOS等を用いることができ、また酸素原料としては例えばO<sub>2</sub>等を用いることができる。 30

## 【0019】

SiH<sub>4</sub>といったシラン系ガスを使用したプラズマエンハース気相成長法(PE-CVD)によるSiN膜、および熱気相成長法(熱CVD)によるSiO<sub>2</sub>膜は応力制御が不可能であるので、その膜の厚み大きくすることが不可能である。厚いSiN膜およびSiO<sub>2</sub>膜には、割れが発生する。しかしながら、ICP-CVD装置を用いて誘電体マスク膜17を形成するので、膜の応力の制御が可能になる。これ故に、たとえば1マイクロメートル以上の厚みを有する厚膜のマスク膜が利用可能になる。応力の制御が可能なマスク膜は、TEOSといった有機シラン系原料を用いICP-CVD法で形成できるシリコン酸化膜である。これ故に、半導体デバイスの作製において汚染が生じることはない。 40

## 【0020】

この誘電体マスクの形成のための一例を説明する。まず、誘電体マスク膜17上に第1のエッチングマスク材19を形成する。好適な例では、第1のエッチング材19は多層構造21を有することができる。多層構造21は第1～第3の層からなる。第1の層は例えば硬化されたレジスト膜23であり、具体的には、硬化レジスト膜23は、レジストを塗 50

布して1マイクロメートル以上のレジスト膜を形成した後に、摂氏100度以上の温度で熱処理して形成される。第2の膜は例えばシリコン化合物膜25、Ti、Crなどの金属膜、具体的にはスパッタなどの低温で成膜できる金属薄膜等であり、具体的には、スピニコート法で0.1マイクロメートル程度のシリコン酸化物薄膜を形成される。第3の膜27は、例えば感光性レジスト膜であり、具体的には、感光性レジストをシリコン化合物膜25上に塗布して形成される。

【0021】

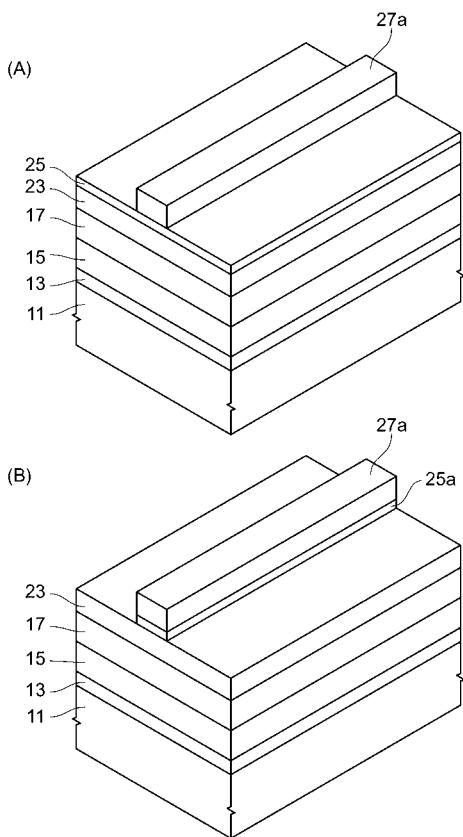

図2(A)は、フォトリソグラフィ法を用いてレジストマスクを形成する工程を示す図面である。化合物半導体光デバイスのための光学マスクを用いて感光性レジスト膜27を露光した後に、露光されたレジスト膜を現像する。図2(A)を参照すると、フォトリソグラフィ法でレジストマスク27aが形成される。本実施例では、半導体レーザのメサストライプを作製するためのパターンを有するマスクが形成される。

【0022】

図2(B)に示されるように、レジストマスク27aを用いてシリコン酸化物薄膜をエッチングして、シリコン酸化物マスク25aを作製する。本実施例では、このエッチングは、例えばRIEエッチング装置を用いて行われる。エッチングガスは、例えばCF<sub>4</sub>ガスを用いることができる。これにより、エッチング中に十分な選択比を維持できる。この結果、メサストライプを作製するためのパターンが転写されたシリコン酸化物マスク25aが得られる。この後に、レジストマスク27aを除去する。この除去は、例えばO<sub>2</sub>ガスによるプラズマアッティングにより行われる。

【0023】

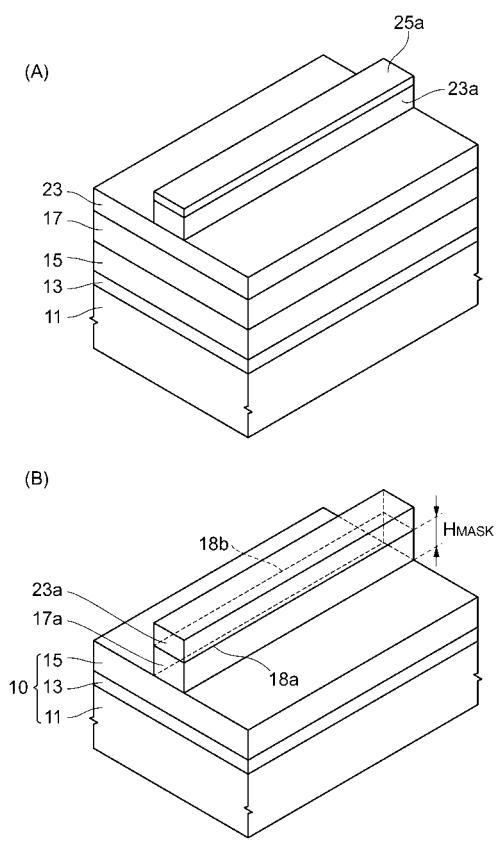

図3(A)は、シリコン酸化物マスクを用いて硬化レジストマスクを形成する工程を示す図面である。シリコン酸化物マスク25aを用いて硬化レジスト膜23をエッチングして硬化レジストマスク23aを形成する。本実施例では、このエッチングは、例えばRIEエッチング装置を用いて行われる。エッチングガスは、例えばO<sub>2</sub>ガスを用いることができる。これにより、十分な選択比を維持できる。この結果、メサストライプを作製するためのパターンが転写された硬化レジストマスク23aが得られる。この後に、シリコン酸化物マスク25aを除去する。この除去は、例えばCHF<sub>3</sub>ガスを用いたRIEエッチングにより行われる。

【0024】

図3(B)は、誘電体マスク膜にパターンを形成して誘電体マスクを形成する工程を示す図面である。硬化レジストマスク23aを用いて誘電体マスク膜17をエッチングする。本実施例では、このエッチングは、例えばRIEエッチング装置を用いて行われる。エッチングガスは、例えばCHF<sub>3</sub>ガスを用いることができる。これにより、十分な選択比を維持できる。この結果、メサストライプを作製するためのパターンが転写された誘電体マスク17aが得られる。誘電体マスク17aの厚みH<sub>MASK</sub>は、1マイクロメートル以上である。この後に、硬化レジストマスク23aを除去する。この除去は、例えばO<sub>2</sub>ガスによるRIEエッチング装置により行われる。また、上記のレジストマスク27a、およびシリコン酸化物マスク25aの除去は、この硬化レジストマスク23aを除去する際、一度に除去することもできるので、このレジストマスク27aの除去工程、およびシリコン酸化物マスク25aの除去工程を省略することもできる。

【0025】

誘電体マスク膜上に直接に感光レジストマスクを形成すると、感光レジストマスクのストライプパターンの断面形状が台形になる。この転写されたストライプパターンの幅の精度の誤差が大きくなる。3層マスクを用いると、感光レジストマスクのストライプパターンの断面形状が矩形になり、反応性イオンエッチングを用いた場合、パターンの転写精度を向上させることができる。

【0026】

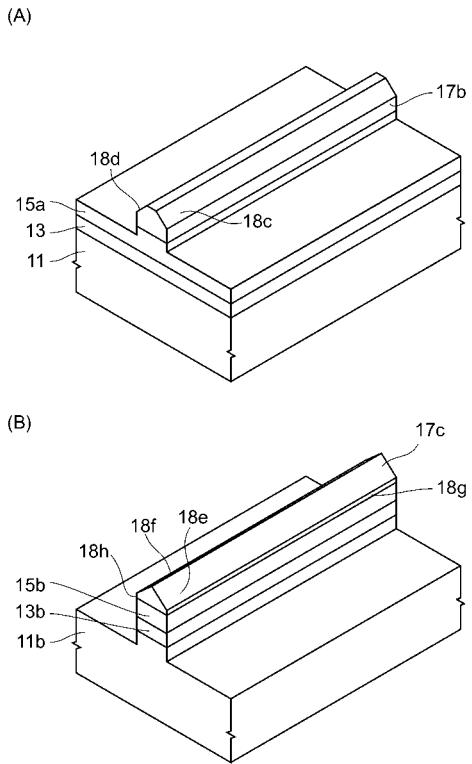

図4(A)および図4(B)は、誘電体マスクを用いて、化合物半導体領域のドライエッチングを行ってメサ形状の化合物半導体領域を形成する工程を示す図面である。誘電体

10

20

30

40

50

マスク 17a を用いて、化合物半導体領域 15、13、11 のドライエッティングを行う。本実施例では、このエッティングは、例えば ECR - RIE エッティング装置を用いて行われる。エッティングガスは、例えば CH<sub>4</sub> ガスといった炭化水素を用いることができ、必要な場合には水素を加えることができる。このときの ECR - RIE エッティングの条件の一例は、

ECR の高周波電力 : 50 ~ 300 (W)

バイアス電力 : 50 ~ 300 (W)

エッティング圧力 : 0.5 ~ 5 (Pa)

CH<sub>4</sub> ガス流量 : 20 ~ 50 (sccm)

H<sub>2</sub> ガス流量 : 0 ~ 50 (sccm)

である。

### 【0027】

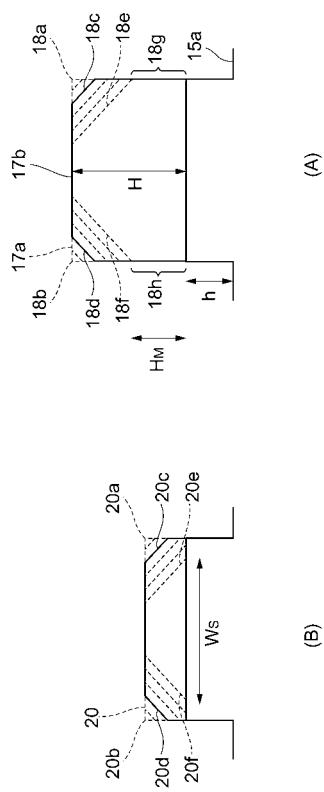

図 4 (A) を参照すると、化合物半導体領域 10 の III-V 化合物半導体膜 15 のエッティングが進み、エッティングされた III-V 化合物半導体膜 15a が形成されている。このエッティングの進行中に、図 3 (B) に示された誘電体マスク 17 のエッジ 18a、18b が消失している。つまり、エッティング中に、半導体領域 11、13、15 がエッティングにより加工されるだけでなく、誘電体マスク 17 の形状もエッティングの進行と共に変化する。この ECR - RIE 法では、図 5 (A) に示されるように、エッティングが進行するにつれて、マスクエッジ 18a、18b から変形が進行する。この変形はスパッタ成分により引き起こされ、誘電体マスクの変形は、垂直方向のエッティング速度の 8 ~ 10 倍の速度で進む。マスクの変形は、マスク上部のエッジからほぼ 45 度の角度方向に進み、これによりマスク上部および側面と約 135 度の角度を成す傾斜面 18c、18d が形成される。

### 【0028】

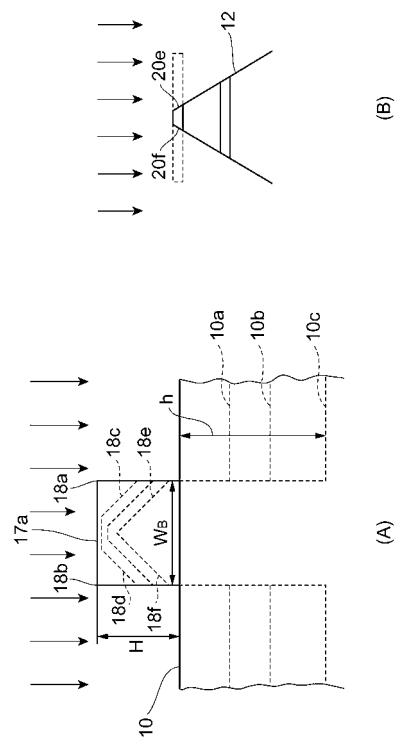

一方、PECVD 法による SiN 膜、および熱 CVD 法による SiO<sub>2</sub> 膜を厚くすると、割れが生じるので、厚膜のマスク膜が得られない。これらの膜から形成された誘電体マスク 20 を用いるエッティング方法でも、エッティング中に、半導体領域がエッティングにより加工されるだけでなく、マスクの形状もエッティングの進行と共に変化する。このエッティングでは、エッティングマスクとして厚さ 0.3 μm 程度の SiN、SiO<sub>2</sub> 等の絶縁膜を用いて RIE 法を用いる。RIE 法では、エッティングが進行するにつれて、マスク側面とマスク上面とからなるエッジ 20a、20b から進行する (マスクエッジの変形)。図 5 (B) に示されるように、この変形はスパッタ成分により引き起こされマスク上部のエッジから 45 度の角度方向に進み、これによりマスク上部および側面と約 135 度の角度を成す傾斜面 20c、20d が形成される。マスクの変形は、垂直方向のエッティング速度の 8 ~ 10 倍の消失速度で進む。マスクの変形により側面が消失して傾斜面 20e、20f が形成されると、エッティングの進行に伴いマスク幅 W<sub>s</sub> が小さくなる (マスク幅の後退)。ドライエッティング中にマスク幅が縮小すると、メサ側面が裾を引くようになり、結果的にメサ幅はメサ上部に近づくにつれて狭くなる。このため、図 6 (B) に示されるように、エッティングされた半導体領域 12 の形状が、裾を引くリッジ形状になる。したがって、メサのエッティング角度を垂直に維持しながらドライエッティングを行うことができない。つまり、ドライエッティングにより直角に近い段差を形成することができない。

### 【0029】

図 4 (B) を参照すると、化合物半導体領域 10 の III-V 化合物半導体膜 15a、13、11 のエッティングが完了し、エッティングされた III-V 化合物半導体領域 15b、13b、11b が形成されている。一方、誘電体マスク 17b はエッティングにより変形されて誘電体マスク 17c になる。しかしながら、誘電体マスク 17a は厚いので、エッティングの進行に伴いマスク幅が小さくなること (マスク幅の後退) はない。このため、半導体領域 11b、13b、15b の形状が、ほぼ垂直にエッティングされたリッジ形状になる。これ故に、メサのエッティング角度を垂直に維持しながらドライエッティングを行うことができる。つまり、図 6 (A) に示されるように、エッティングの進行 10a、10b、10c に伴い誘電体マスクの消失により傾斜面 18c、18d から傾斜面 18e、18f に変形

10

20

30

40

50

していく。しかしながら、誘電体マスクのボトムの幅 $W_B$ が実質的に変化しないので、ドライエッチングにより直角に近い段差を形成できる。既に説明したように、誘電体マスク17aは厚いので、エッチングの進行に伴いマスク幅が小さくなること(マスク幅の後退)はない。これ故に、メサのエッチング角度を垂直に維持しながらドライエッチングを行うことができる。つまり、ドライエッチングにより直角に近い段差を形成できる。

#### 【0030】

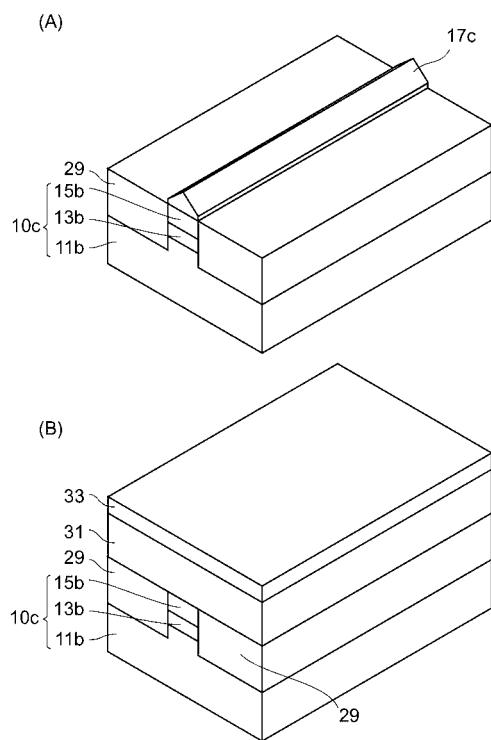

引き続いて、化合物半導体光デバイスを作製する方法を説明する。図7(A)は、化合物半導体光デバイスを作製する方法における埋め込み再成長工程を示す図面である。この工程においても、誘電体マスク17cは除去されずに残されている。誘電体マスク17cを用いてエッチングされた半導体領域10c上に電流プロック領域29を成長する。誘電体マスク17cが設けられているメサ上には、化合物半導体が堆積されない。電流プロック領域29は、例えば、鉄ドープInP、またはp型InP層およびn型InP層から成ることができる。電流プロック領域29の成長は、例えば例えば有機金属気相成長炉を用いて行われる。電流プロック領域29が形成された後に、誘電体マスク17cを除去する。

10

#### 【0031】

図7(B)は、化合物半導体光デバイスを作製する方法における結晶成長工程を示す図面である。半導体領域10cのメサ上および電流プロック領域29上にp型III-V化合物半導体膜31およびp型III-V化合物半導体コンタクト膜33を成長する。これらの工程の後に、アノード電極およびカソード電極を形成する。これにより、化合物半導体光デバイスを作製する方法の主要な工程が説明された。

20

#### 【0032】

埋め込み半導体レーザといった化合物半導体光デバイスの一例は

基板11:n型InP基板

n型III-V化合物半導体膜13:SiドープInP(n型クラッド)

活性領域15:InGaAsPからなる量子井戸構造

埋め込み領域29:FeドープInP(電流プロック)

p型III-V化合物半導体膜31:ZnドープInP(p型クラッド)

p型III-V化合物半導体コンタクト膜33:ZnドープInGaAs

である。

30

#### 【0033】

本実施の形態に係る方法では、メサ形状の化合物半導体領域を形成するためのエッチング中に、誘電体マスク17は、該マスク17の上面のエッジ18a、18bから徐々に後退すると共に、この後退に伴い、図5(A)および図6(A)に示されるように、該マスクの側面の高さ $H_M$ は徐々に小さくなる。ドライエッチングの終了のときに側面の高さ $H_M$ が0以下にならないために、誘電体マスク17の厚み $H$ は、

$$H = h / 3$$

の関係を満たすことが好ましい。この方法によれば、エッチング量が大きく高いメサ形状を作製することができる。例えば、SiO<sub>2</sub>からなる誘電体マスクの高さが約1μmであるとき、メサ側面の垂直性を保ちながらInP半導体を3.5μm程度の深さまでエッチングできる。誘電体マスクの厚み $H$ は、エッチングにより作製されるべきメサの深さ $h$ の3倍程度にすることが好ましい。これにより、ドライエッチング時の横方向へのマスク減退が無くなるので、垂直なエッチング側面を有するメサを作製可能となる。また、横方向のマスク減退を防ぐことができるので、マスク幅に従ったエッチング形状の実現が可能となりエッチング幅の制御性が向上する。

40

#### 【0034】

以上説明したように、本実施の形態に係るエッチング方法によれば、誘電体マスク17aのためのシリコン化合物が誘導結合プラズマ-化学的気相成長法で形成されるので、低応力のため1マイクロメートル以上の厚みを有する誘電体マスク17aを得ることができ。厚膜の誘電体マスク17aを用いて化合物半導体領域のドライエッチングを行うので

50

、エッティング中にマスクエッジの消失が生じてもマスク幅が小さくなることはない。これ故に、所望のメサ形状の化合物半導体領域を形成できる。低応力で厚膜の誘電体マスク膜は、例えば、ICP放電を利用したプラズマCVD装置にTEOS原料を供給すると共に、加熱された基板上にバイアスを印加しながらシリコン酸化物を堆積することにより得られる。

【0035】

好適な実施の形態において本発明の原理を図示し説明してきたが、本発明は、そのような原理から逸脱することなく配置および詳細において変更され得ることは、当業者によって認識される。本実施の形態では、例えば、埋め込み型半導体レーザといった化合物半導体光デバイスを作製する方法を説明したけれども、本発明は、本実施の形態に開示された特定の構成に限定されるものではない。また、本実施の形態では、InP半導体を基板とするInP系埋め込み半導体レーザについて例示的に説明しているけれども、GaAs半導体を基板とするGaAs系埋め込み半導体レーザでもできる。したがって、特許請求の範囲およびその精神の範囲から来る全ての修正および変更に権利を請求する。

10

【図面の簡単な説明】

【0036】

【図1】図1(A)は、化合物半導体光デバイスを作製する方法における結晶成長工程を示す模式図である。図1(B)は、誘電体マスクのための多層構造および誘電体マスク膜を形成するマスク作製工程を示す図面である。

【図2】図2(A)は、フォトリソグラフィ法を用いてレジストマスクを形成する工程を示す図面である。図2(B)は、レジストマスクを用いてシリコン酸化物マスクを形成する工程を示す図面である。

20

【図3】図3(A)は、シリコン酸化物マスクを用いて硬化レジストマスクを形成する工程を示す図面である。図3(B)は、誘電体マスク膜にパターンを形成して誘電体マスクを形成する工程を示す図面である。

【図4】図4(A)および図4(B)は、誘電体マスクを用いて、化合物半導体領域のドライエッティングを行ってメサ形状の化合物半導体領域を形成する工程を示す図面である。

【図5】図5(A)は、本実施の形態における誘電体マスクの変形を示す模式図である。図5(B)は、PE-CVD或いは熱CVD法で形成された誘電体膜を用いる誘電体マスクの変形を示す模式図である。

30

【図6】図6(A)は、本実施の形態における誘電体マスクを用いたエッティングを示す模式図である。図6(B)は、PE-CVD或いは熱CVD法で形成された誘電体膜を用いる誘電体マスクを用いたエッティングを示す模式図である。

【図7】図7(A)は、化合物半導体光デバイスを作製する方法における埋め込み再成長工程を示す図面である。図7(B)は、化合物半導体光デバイスを作製する方法における結晶成長工程を示す図面である。

【符号の説明】

【0037】

11...基板、10...化合物半導体領域、10a、10b、10c...エッティングされた化合物半導体領域、11a...InP半導体表面、11b...III-V化合物半導体領域、13...活性領域、13b...III-V化合物半導体領域、15...III-V化合物半導体膜、15a...III-V化合物半導体膜、15b...III-V化合物半導体領域、17...誘電体マスク膜、17a...誘電体マスク、17b、17c...変形された誘電体マスク、H<sub>FILM</sub>...誘電体マスク膜厚み、H<sub>MASK</sub>...誘電体マスク厚み、19...第1のエッティングマスク材、21...多層構造、23...硬化されたレジスト膜、23a...硬化レジストマスク、25...シリコン化合物膜、25a...シリコン酸化物マスク、27...感光性レジスト膜、27a...レジストマスク、18a、18b...誘電体マスクエッジ、18c、18d...マスク傾斜面、18e、18f...マスク傾斜面、10...化合物半導体領域、29...電流ブロック領域、31...p型III-V化合物半導体膜、33...p型III-V化合物半導体コンタクト膜

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 服部 哲也

神奈川県横浜市栄区田谷町1番地 住友電気工業株式会社横浜製作所内

(72)発明者 村田 道夫

神奈川県横浜市栄区田谷町1番地 住友電気工業株式会社横浜製作所内

審査官 川崎 良平

(56)参考文献 特開平11-097799 (JP, A)

特表2000-501568 (JP, A)

特開平09-232308 (JP, A)

特開平08-288272 (JP, A)

特開平07-153595 (JP, A)

特開平11-168201 (JP, A)

特開平11-135478 (JP, A)

特開2000-091303 (JP, A)

特開平07-169964 (JP, A)

特開2004-281815 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/205, 21/302, 21/3065, 21/316

H01S 5/02

H05H 1/46