(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7319501号

(P7319501)

(45)発行日 令和5年8月2日(2023.8.2)

(24)登録日 令和5年7月25日(2023.7.25)

(51)国際特許分類

|         |                  |     |         |        |         |

|---------|------------------|-----|---------|--------|---------|

| C 3 0 B | 29/36 (2006.01)  | F I | C 3 0 B | 29/36  | A       |

| C 3 0 B | 25/20 (2006.01)  |     | C 3 0 B | 25/20  |         |

| H 0 1 L | 21/205 (2006.01) |     | H 0 1 L | 21/205 |         |

| H 0 1 L | 29/872 (2006.01) |     | H 0 1 L | 29/86  | 3 0 1 D |

| H 0 1 L | 21/329 (2006.01) |     | H 0 1 L | 29/86  | 3 0 1 E |

請求項の数 15 (全20頁) 最終頁に続く

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2019-186235(P2019-186235) |

| (22)出願日  | 令和1年10月9日(2019.10.9)        |

| (65)公開番号 | 特開2021-59480(P2021-59480A)  |

| (43)公開日  | 令和3年4月15日(2021.4.15)        |

| 審査請求日    | 令和4年2月10日(2022.2.10)        |

|          |                                                                    |

|----------|--------------------------------------------------------------------|

| (73)特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号                              |

| (74)代理人  | 110004026<br>弁理士法人iX                                               |

| (72)発明者  | 西尾 譲司<br>東京都港区芝浦一丁目1番1号 株式会社東芝内<br>清水 達雄<br>東京都港区芝浦一丁目1番1号 株式会社東芝内 |

|          | 審査官 今井 淳一                                                          |

最終頁に続く

(54)【発明の名称】 基板の製造方法、半導体装置の製造方法、基板及び半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

第1元素を含む炭化珪素を含む第1半導体部材と、第2元素を含む炭化珪素を含む第2半導体部材と、を含む構造体であって、前記第1元素は、N、P及びAsよりなる第1群から選択された少なくとも1つを含み、前記第2元素は、B、Al及びGaよりなる第2群から選択された少なくとも1つを含む、前記第1半導体部材から前記第2半導体部材への方向は、第1方向に沿う、前記構造体を準備し、

前記第1方向に沿って前記第2半導体部材を貫通し前記第1半導体部材に届く孔を形成し、

前記第1群から選択された少なくとも1つを含む第3元素を含む炭化珪素を含む第3半導体部材を前記孔中に形成し、

前記孔の前記形成は、前記第1半導体部材の一部を除去することを含む、基板の製造方法。

## 【請求項2】

前記第3半導体部材の前記形成は、前記第3元素及び炭素を含む化合物を含むガスを用いて前記第3半導体部材を成長させる、請求項1記載の基板の製造方法。

## 【請求項3】

前記第3半導体部材の前記形成は、前記第3半導体部材をエピタキシャル成長させることを含む、請求項2記載の基板の製造方法。

## 【請求項4】

前記構造体の前記準備は、

前記第1半導体部材の上に、前記第2元素を含むガスを用いて前記第2半導体部材をエピタキシャル成長させることを含む、請求項2または3に記載の基板の製造方法。

【請求項5】

前記第3半導体部材における前記第3元素の濃度は、前記第1半導体部材における前記第1元素の濃度よりも高い、請求項1～4のいずれか1つに記載の基板の製造方法。

【請求項6】

前記構造体は、炭化珪素を含む基体をさらに含み、

前記第1半導体部材は、前記基体の上に設けられ、

前記基体と前記第3半導体部材との間の前記第1方向に沿う距離は、前記基体と前記第2半導体部材との間の前記第1方向に沿う距離よりも短い、請求項1～5のいずれか1つに記載の基板の製造方法。

10

【請求項7】

前記孔の前記形成は、複数の前記孔を形成することを含み、

前記複数の孔は、前記第1方向と交差する第2方向に並ぶ、請求項1～6のいずれか1つに記載の基板の製造方法。

【請求項8】

前記複数の孔は、前記第1方向及び前記第2方向を含む平面と交差する第3方向にさらに並ぶ、請求項7記載の基板の製造方法。

【請求項9】

前記構造体の前記準備は、

前記第1半導体部材を準備し、

前記第1半導体部材に紫外線を照射して基底面転位から積層欠陥を前記第1半導体部材中に拡張させ、

20

前記積層欠陥の位置を検出し、

前記位置の検出の後に前記第2半導体部材を形成すること、

を含み、

前記第2半導体部材は、

前記第1方向において前記積層欠陥の前記位置と重なる重畠領域と、

前記第1方向において前記積層欠陥の前記位置と重ならない非重畠領域と、

30

を含み、

前記孔の前記形成は、複数の前記孔を形成することを含み、

前記孔の前記形成は、前記積層欠陥の前記位置の検出結果に基づいて、

前記複数の孔の少なくとも1つを前記非重畠領域に形成し、

前記複数の孔の少なくとも1つを前記重畠領域に形成しないこと、

を含む、請求項1～6のいずれか1つに記載の基板の製造方法。

【請求項10】

第1元素を含む炭化珪素を含む第1半導体部材と、第2元素を含む炭化珪素を含む第2半導体部材と、を含む構造体であって、前記第1元素は、N、P及びA<sub>s</sub>よりなる第1群から選択された少なくとも1つを含み、前記第2元素は、B、A<sub>1</sub>及びG<sub>a</sub>よりなる第2群から選択された少なくとも1つを含む、前記第1半導体部材から前記第2半導体部材への方向は、第1方向に沿う、前記構造体を準備し、

40

前記第1方向に沿って前記第2半導体部材を貫通し前記第1半導体部材に届く孔を形成し、

前記第1群から選択された少なくとも1つを含む第3元素を含む炭化珪素を含む第3半導体部材を前記孔中に形成し、

前記構造体の前記準備は、

前記第1半導体部材を準備し、

前記第1半導体部材に紫外線を照射して基底面転位から積層欠陥を前記第1半導体部材中に拡張させ、

50

前記積層欠陥の位置を検出し、

前記位置の検出の後に前記第2半導体部材を形成すること、

を含み、

前記第2半導体部材は、

前記第1方向において前記積層欠陥の前記位置と重なる重畳領域と、

前記第1方向において前記積層欠陥の前記位置と重ならない非重畳領域と、

を含み、

前記孔の前記形成は、複数の前記孔を形成することを含み、

前記孔の前記形成は、前記積層欠陥の前記位置の検出結果に基づいて、

前記複数の孔の少なくとも1つを前記非重畳領域に形成し、

前記複数の孔の少なくとも1つを前記重畳領域に形成しないこと、

を含む、基板の製造方法。

【請求項11】

前記構造体の前記準備は、

前記第1半導体部材を準備し、

前記第1半導体部材に紫外線を照射して基底面転位から積層欠陥を前記第1半導体部材中に拡張させ、

前記積層欠陥の位置を検出し、前記第1半導体部材は、前記積層欠陥の前記位置を含む第1領域と、前記積層欠陥の前記位置を含まない第2領域と、を含み、

前記積層欠陥の前記位置の検出結果に基づいて、前記第1領域の少なくとも一部に第4元素を導入し、前記第2領域に前記第4元素を導入せず、

前記第1領域及び前記第2領域の上に前記第2半導体部材を形成すること、

を含み、

前記第4元素は、前記第1群から選択された少なくとも1つ、または、前記第2群から選択された少なくとも1つを含む、請求項1~6のいずれか1つに記載の基板の製造方法。

【請求項12】

第1元素を含む炭化珪素を含む第1半導体部材と、第2元素を含む炭化珪素を含む第2半導体部材と、を含む構造体であって、前記第1元素は、N、P及びAsよりなる第1群から選択された少なくとも1つを含み、前記第2元素は、B、Al及びGaよりなる第2群から選択された少なくとも1つを含む、前記第1半導体部材から前記第2半導体部材への方向は、第1方向に沿う、前記構造体を準備し、

前記第1方向に沿って前記第2半導体部材を貫通し前記第1半導体部材に届く孔を形成し、

前記第1群から選択された少なくとも1つを含む第3元素を含む炭化珪素を含む第3半導体部材を前記孔中に形成し、

前記構造体の前記準備は、

前記第1半導体部材を準備し、

前記第1半導体部材に紫外線を照射して基底面転位から積層欠陥を前記第1半導体部材中に拡張させ、

前記積層欠陥の位置を検出し、前記第1半導体部材は、前記積層欠陥の前記位置を含む第1領域と、前記積層欠陥の前記位置を含まない第2領域と、を含み、

前記積層欠陥の前記位置の検出結果に基づいて、前記第1領域の少なくとも一部に第4元素を導入し、前記第2領域に前記第4元素を導入せず、

前記第1領域及び前記第2領域の上に前記第2半導体部材を形成すること、

を含み、

前記第4元素は、前記第1群から選択された少なくとも1つ、または、前記第2群から選択された少なくとも1つを含む、基板の製造方法。

【請求項13】

前記第4元素は、前記第1群から選択された少なくとも1つを含み、

前記第4元素が導入された領域における前記第4元素の濃度と、前記第4元素が導入さ

10

20

30

40

50

れた前記領域における前記第1元素の濃度の和は、前記第3半導体部材における前記第3元素の濃度以上である、請求項11または12に記載の基板の製造方法。

【請求項14】

前記第4元素は、前記第2群から選択された少なくとも1つを含み、

前記第4元素が導入された領域における前記第4元素の濃度は、前記第4元素が導入された領域における前記第1元素の濃度よりも高い、請求項11または12に記載の基板の製造方法。

【請求項15】

前記孔の少なくとも一部は、前記第1方向において、前記第1領域と重なる、請求項11～14のいずれか1つに記載の基板の製造方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、基板の製造方法、半導体装置の製造方法、基板及び半導体装置に関する。

【背景技術】

【0002】

例えば、炭化珪素(SiC)を含む基板を用いた半導体装置がある。基板及び半導体装置において、安定した特性が望まれる。

20

【先行技術文献】

【特許文献】

【0003】

【文献】特開2017-168666号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、安定した特性が得られる基板の製造方法、半導体装置の製造方法、基板及び半導体装置を提供する。

【課題を解決するための手段】

【0005】

30

本発明の実施形態によれば、基板の製造方法は、構造体を準備することを含む。前記構造体は、第1元素を含む炭化珪素を含む第1半導体部材と、第2元素を含む炭化珪素を含む第2半導体部材と、を含む。前記第1元素は、N、P及びAsよりなる第1群から選択された少なくとも1つを含む。前記第2元素は、B、Al及びGaよりなる第2群から選択された少なくとも1つを含む。前記第1半導体部材から前記第2半導体部材への方向は、第1方向に沿う。前記製造方法は、前記第1方向に沿って前記第2半導体部材を貫通し前記第1半導体部材に届く孔を形成することを含む。前記製造方法は、前記第1群から選択された少なくとも1つを含む第3元素を含む炭化珪素を含む第3半導体部材を前記孔中に形成することを含む。

【図面の簡単な説明】

40

【0006】

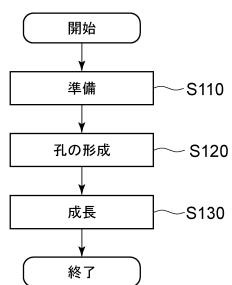

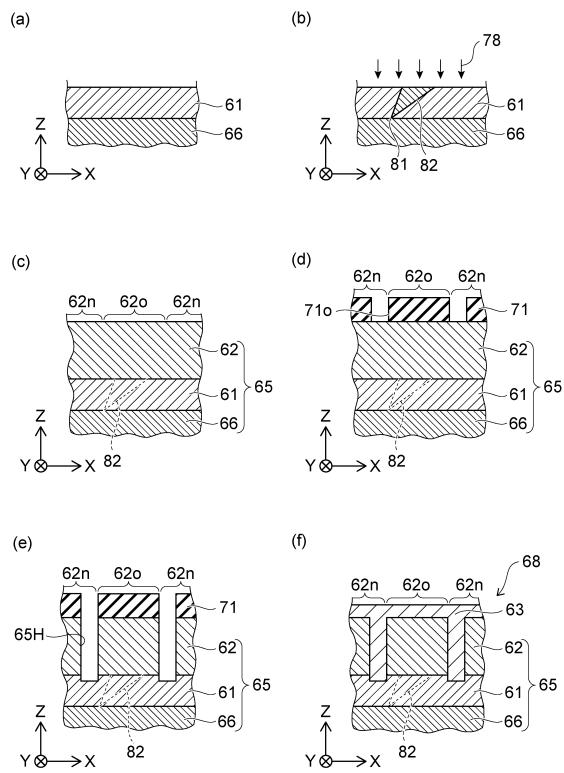

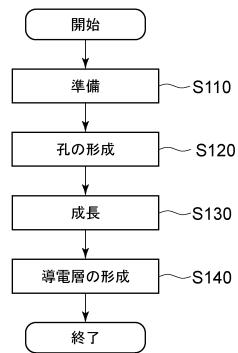

【図1】図1は、第1実施形態に係る基板の製造方法を例示するフローチャート図である。

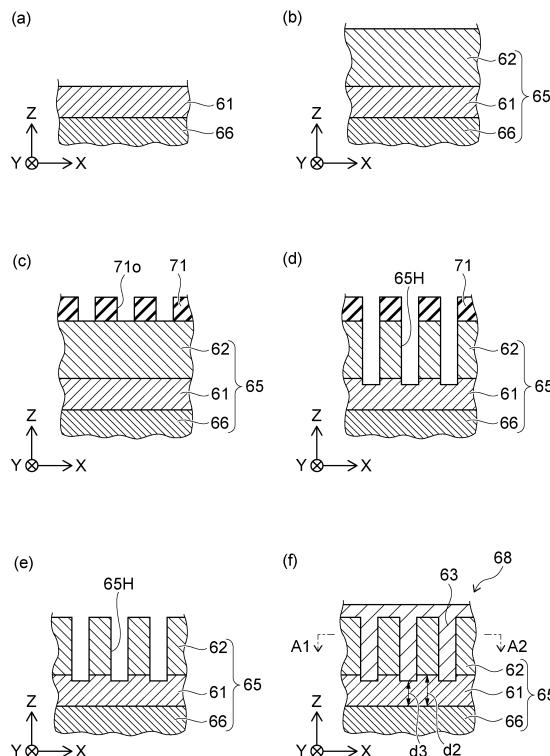

【図2】図2(a)～図2(f)は、第1実施形態に係る基板の製造方法を例示する模式的断面図である。

【図3】図3(a)～図3(f)は、第1実施形態に係る基板を例示する模式的断面図である。

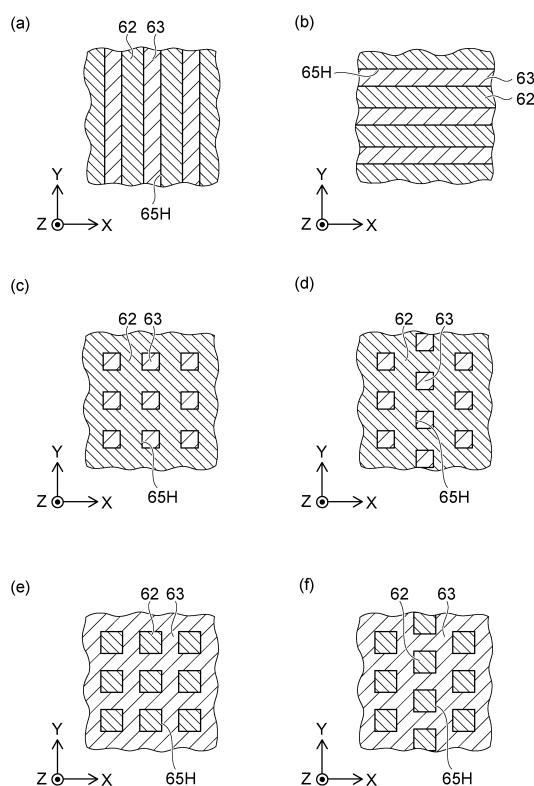

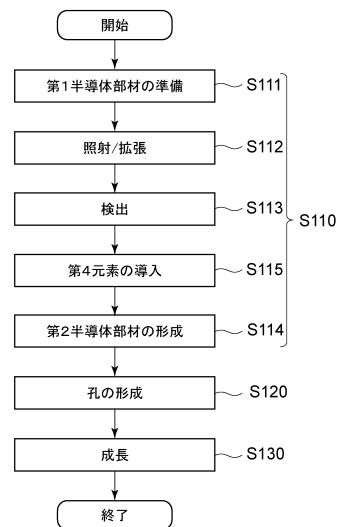

【図4】図4は、第2実施形態に係る基板の製造方法を例示するフローチャート図である。

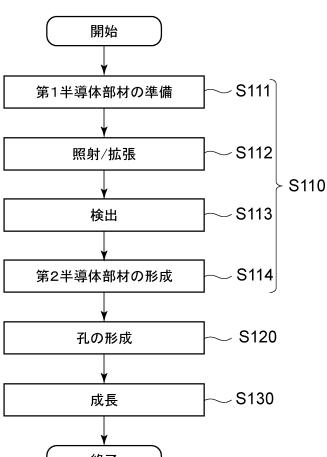

【図5】図5(a)～図5(f)は、第2実施形態に係る基板の製造方法を例示する模式的断面図である。

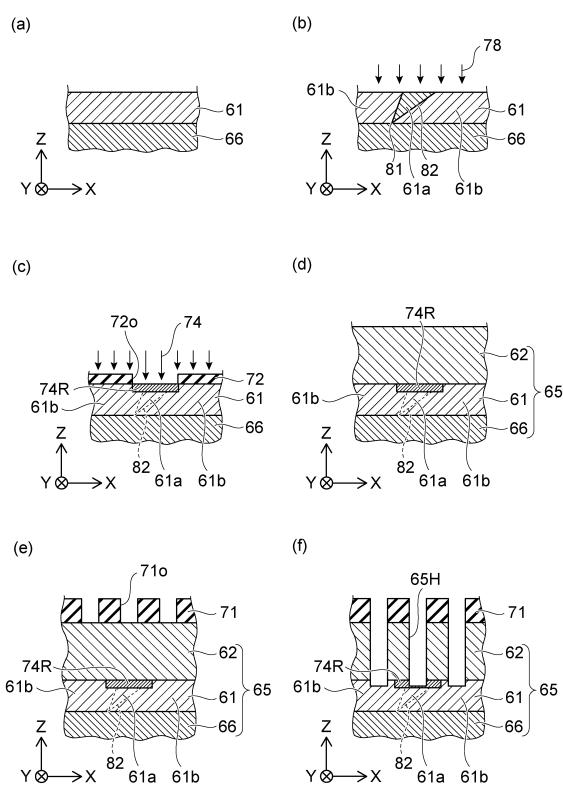

【図6】図6は、第3実施形態に係る基板の製造方法を例示するフローチャート図である。

50

【図7】図7(a)～図7(f)は、第3実施形態に係る基板の製造方法を例示する模式的断面図である。

【図8】図8(a)及び図8(b)は、第3実施形態に係る基板の製造方法を例示する模式的断面図である。

【図9】図9は、第4実施形態に係る半導体装置の製造方法を例示するフローチャート図である。

【図10】図10は、第4実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

【図11】図11は、第6実施形態に係る半導体装置を例示する模式的断面図である。

【図12】図12は、第6実施形態に係る半導体装置を例示する模式的断面図である。

【図13】図13は、第6実施形態に係る半導体装置を例示する模式的断面図である。

【発明を実施するための形態】

【0007】

以下に、本発明の各実施の形態について図面を参照しつつ説明する。

図面は模式的または概念的なものであり、各部分の厚さと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1実施形態)

図1は、第1実施形態に係る基板の製造方法を例示するフローチャート図である。

図2(a)～図2(f)は、第1実施形態に係る基板の製造方法を例示する模式的断面図である。

図1に示すように、実施形態に係る基板の製造方法は、構造体を準備し(ステップS10)、孔を形成し(ステップS120)、第3半導体部材を成長する(ステップS130)ことを含む。

【0009】

例えば、図2(a)に示すように、例えば、基体66の上に、第1半導体部材61が設けられる。基体66と第1半導体部材61との間に別の層が設けられても良い。基体66は、炭化珪素(SiC)を含む。第1半導体部材61は、炭化珪素を含む。図2(b)に示すように、第1半導体部材61の上に第2半導体部材62が設けられる。第2半導体部材62は、炭化珪素を含む。例えば、第2半導体部材62は、第1半導体部材61と接する。

【0010】

図2(b)に示すように、構造体65は、第1半導体部材61及び第2半導体部材62を含む。構造体65は、基体66を含んでも良い。ステップS110では、このような構造体が準備される。

【0011】

第1半導体部材61は、第1元素を含む炭化珪素を含む。第2半導体部材62は、第2元素を含む炭化珪素を含む。第1元素は、N、P及びAsよりなる第1群から選択された少なくとも1つを含む。第2元素は、B、Al及びGaよりなる第2群から選択された少なくとも1つを含む。例えば、第1半導体部材61は、n形の炭化珪素を含む。例えば、第2半導体部材62は、p形の炭化珪素を含む。

【0012】

第1半導体部材61から第2半導体部材62への方向は、第1方向に沿う。第1方向をZ軸方向とする。Z軸方向に対して垂直な方向をX軸方向とする。Z軸方向及びX軸方向に対して垂直な方向をY軸方向とする。

【0013】

基体66、第1半導体部材61及び第2半導体部材62は、X-Y平面に沿って広がる。

10

20

30

40

50

## 【0014】

図2(c)に示すように、例えば、第2半導体部材62の上に、開口部710を有する第1マスク71を形成する。第1マスク71の材料は、例えば、酸化シリコンなどである。

## 【0015】

図2(d)に示すように、第1マスク71をマスクとして用いて、第2半導体部材62の一部を除去する。これにより、孔65Hが形成される。除去には、例えば、CF<sub>4</sub>などをエッティングガスとして用いたドライエッティングなどが行われる。孔65Hの形成がステップS120に対応する。

## 【0016】

孔65Hは、第1方向(Z軸方向)に沿って第2半導体部材62を貫通する。孔65Hは、第1半導体部材61に届く。例えば、第2半導体部材62の一部の除去のエッティングにより、第1半導体部材61の一部が除去されても良い。例えば、孔65Hの底部は、第1半導体部材61中にある。

10

## 【0017】

図2(e)に示すように、第1マスク71を除去する。

## 【0018】

図2(f)に示すように、第3半導体部材63を孔65H中に形成する。第3半導体部材63は、上記の第1群から選択された少なくとも1つを含む第3元素を含む炭化珪素を含む。例えば、第3半導体部材63は、n形の炭化珪素を含む。第3半導体部材63の形成が、ステップS130に対応する。このような第3半導体部材63の形成により基板68が得られる。図2(f)に示すように、ステップS130において、第3半導体部材63は、第2半導体部材62の上にも形成されても良い。

20

## 【0019】

例えば、第2半導体部材62と第3半導体部材63とが、X-Y平面内で交互に並ぶ。これにより、例えば、スーパージャンクション(SJ)構造が得られる。SJ構造においては、例えば、p形ピラー及びn形ピラーがZ軸方向に沿って延びる。このような構造により、例えば、低いオン抵抗を得ることができる。

## 【0020】

実施形態に係る基板の製造方法によれば、均一な特性を有する第3半導体部材63を形成できる。実施形態によれば、安定した特性が得られる基板の製造方法が提供できる。

30

## 【0021】

SJ構造を形成する第1参考例として、n形層に孔を形成し、その孔にp形半導体を埋め込む方法が考えられる。しかしながら、炭化珪素を含むp形半導体を孔に埋め込むと、均一な特性を得ることが困難であることが分かった。これは、例えば、p形半導体を形成する際に用いられるp形不純物の原料が炭化水素を含むことに起因していると考えられる。

## 【0022】

n形不純物を含む炭化珪素半導体を孔中に形成する際には、第1元素(N、P及びAs)よりなる第1群から選択された少なくとも1つ)を含むガスを用いてエピタキシャル成長を行う方法が採用可能である。この場合、n形不純物の原料ガスは、例えば、窒素ガスなどであり、気相反応により、n形不純物を含む炭化珪素半導体が形成される。気相反応の場合は、例えば、孔の側壁と、孔の底面と、で、実質的に同じドーピング特性が得られる。このため、n形不純物を含む炭化珪素半導体を孔中に形成する場合は、均一な特性が容易に得られる。

40

## 【0023】

一方、p形不純物を含む炭化珪素半導体を孔中に形成する際には、第2元素(B、Al及びGa)よりなる第2群から選択された少なくとも1つ)を含むガスを用いてエピタキシャル成長を行う方法が考えられる。p形不純物の原料ガスは、例えば、トリメチルアルミニウム(TMA)、トリメチルガリウム(TMG)、または、トリエチルボラン(TEB)などである。p形不純物の原料ガスは、炭化水素を含む。この場合、p形半導体は、表面反応により成長する。このため、p形不純物を含む炭化珪素半導体を孔中に形成する場

50

合は、孔の側壁と、孔の底面と、で、ドーピング特性が異なると考えられる。第1参考例においては、均一な特性を有するp形炭化珪素半導体を得ることが困難であると考えられる。

【0024】

特に、高い濃度のp形炭化珪素半導体を、細い孔中に形成する際には、p形不純物濃度が不均一になり易い。

【0025】

p形不純物を含む炭化珪素半導体を細い孔中ではなく、広い露出した面に形成する際には、比較的容易に、均一なp形不純物濃度が得られる。細い孔中にp形不純物を含む炭化珪素半導体を形成するすると、特別な困難が生じることが分かった。

10

【0026】

実施形態においては、p形炭化珪素半導体（第2半導体部材62）を、広く露出した第1半導体部材61の上に形成する。これにより、均一なp形不純物濃度が安定して得られる。この後、p形炭化珪素半導体に孔65Hを形成し、n形炭化珪素半導体（第3半導体部材63）を孔65Hに埋め込む。上記のように、n形炭化珪素半導体は、気相反応で成長する。これにより、均一性の高いn形不純物濃度が得られる。

【0027】

実施形態によれば、安定した特性が得られる基板の製造方法が提供できる。

【0028】

SJ構造の窒化物半導体を形成するための第2参考例として、薄いn形炭化珪素層に、A1などをイオンドーピングすることを繰り返す方法が考えられる。しかしながら、第2参考例においては、高い生産性を得ることが困難である。

20

【0029】

実施形態によれば、安定した特性が得られる基板を高い生産性で製造することができる。

【0030】

上記のように、第3半導体部材63の形成は、第3元素及び炭素を含む化合物を含むガスを用いて第3半導体部材63を成長させることを含む。この化合物は、例えば、炭化水素を含む。第3半導体部材63の形成は、第3半導体部材63をエピタキシャル成長させることを含む。

30

【0031】

実施形態において、例えば、第3半導体部材63における第3元素（n形不純物）の濃度は、第1半導体部材61における第1元素（n形不純物）の濃度よりも高い。高い不純物濃度の第3半導体部材63を安定して形成できる。例えば、第3半導体部材63におけるキャリア濃度は、第1半導体部材61におけるキャリア濃度よりも高い。高いキャリア濃度の第3半導体部材63を安定して形成できる。

【0032】

例えば、構造体65の準備（ステップS110）は、第1半導体部材61の上に、第2元素を含むガスを用いて第2半導体部材62をエピタキシャル成長させることを含んでも良い（図2（b）参照）。

40

【0033】

既に説明したように、孔65Hの形成は、第1半導体部材61の一部を除去することを含んでも良い。これにより、図2（e）に示すように、孔65Hの底面は、第1半導体部材61中にある。孔65Hの底面に第2半導体部材62が残らない。これにより、孔65H中に第3半導体部材63を形成することで、第3半導体部材63は、第1半導体部材61と接する。良好な導電特性が得られる。

【0034】

図2（f）に示すように、第1半導体部材61は、基体66の上に設けられる。基体66と第3半導体部材63との間の第1方向（Z軸方向）に沿う距離を距離d3とする。基体66と第2半導体部材62との間の第1方向に沿う距離を距離d2とする。距離d3は、距離d2よりも短い。第3半導体部材63の底部は、第1方向（Z軸方向）と交差する

50

方向（例えば X 軸方向）において、第 1 半導体部材 6 1 と対向する。良好な導電特性が得られる。

【 0 0 3 5 】

図 2 ( f ) に例示した構造において、例えば、表面研磨加工などを行うことで、第 2 半導体部材 6 2 の上の第 3 半導体部材 6 3 を除去しても良い。第 2 半導体部材 6 2 が露出されても良い。図 2 ( f ) に例示した断面とは異なる部分で第 2 半導体部材 6 2 が表面側（上側）の p 形層に接続されても良い。この場合、表面研磨加工などが省略できる。

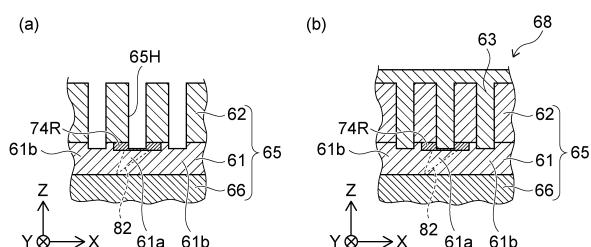

【 0 0 3 6 】

図 3 ( a ) ~ 図 3 ( f ) は、第 1 実施形態に係る基板を例示する模式的断面図である。これらの図は、図 2 ( f ) の A 1 - A 2 線の位置における断面図に対応する。

これらの図は、第 2 半導体部材 6 2 及び第 3 半導体部材 6 3 の形状を例示している。第 3 半導体部材 6 3 の形状は、孔 6 5 H の形状に対応する。

【 0 0 3 7 】

図 3 ( a ) 及び図 3 ( b ) に示すように、孔 6 5 H の形成（ステップ S 1 2 0 ）は、複数の孔 6 5 H（第 3 半導体部材 6 3 ）を形成することを含む。複数の孔 6 5 H（第 3 半導体部材 6 3 ）は、第 1 方向（Z 軸方向）と交差する第 2 方向に並ぶ。図 3 ( a ) の例では、第 2 方向は、X 軸方向である。図 3 ( b ) の例では、第 2 方向は Y 軸方向である。

【 0 0 3 8 】

図 3 ( c ) に示すように、複数の孔 6 5 H は、第 1 方向及び第 2 方向を含む平面と交差する第 3 方向（この例では Y 軸方向）にさらに並ぶ。図 3 ( d ) に示すように、複数の孔 6 5 H（第 3 半導体部材 6 3 ）のピッチが、X 軸方向と Y 軸方向とで異なっても良い。

【 0 0 3 9 】

図 3 ( e ) 及び図 3 ( f ) に示すように、複数の第 2 半導体部材 6 2 が形成されても良い。この場合は、1 つの孔 6 5 H により分断された複数の第 2 半導体部材 6 2 が形成される。

【 0 0 4 0 】

（第 2 実施形態）

図 4 は、第 2 実施形態に係る基板の製造方法を例示するフローチャート図である。

図 4 に示すように、構造体 6 5 の準備（ステップ S 1 1 0 ）は、第 1 半導体部材 6 1 を準備すること（ステップ S 1 1 1 ）を含む。ステップ S 1 1 0 は、紫外線を照射し、積層欠陥を拡張させること（ステップ S 1 1 2 ）を含む。ステップ S 1 1 0 は、積層欠陥の位置を検出すること（ステップ S 1 1 3 ）を含む。ステップ S 1 1 0 は、第 2 半導体部材 6 2 を形成すること（ステップ S 1 1 4 ）を含む。

【 0 0 4 1 】

図 5 ( a ) ~ 図 5 ( f ) は、第 2 実施形態に係る基板の製造方法を例示する模式的断面図である。

図 5 ( a ) に示すように、第 1 半導体部材 6 1 を準備する（ステップ S 1 1 1 ）。

【 0 0 4 2 】

図 5 ( b ) に示すように、第 1 半導体部材 6 1 に紫外線 7 8 を照射して基底面転位 8 1 から積層欠陥 8 2 を第 1 半導体部材 6 1 中に拡張させる（ステップ S 1 1 2 ）。紫外線 7 8 の波長は、例えば、310 nm 以上 370 nm 以下である。紫外線 7 8 のパワー密度は、1 W / cm<sup>2</sup> 以上である。紫外線 7 8 の照射の時間は、例えば、5 分以上 30 分以下である。

【 0 0 4 3 】

この後、積層欠陥 8 2 の位置を検出する（ステップ S 1 1 3 ）。例えば、フォトルミネッセント光の観察により、積層欠陥 8 2 の位置が検出できる。例えば、ウェーハ（例えば、基板 6 6 ）中での、積層欠陥 8 2 の位置が記憶される。紫外線 7 8 により生じた積層欠陥 8 2 は、時間の経過とともに消失する。しかし、基板 6 8 を用いて製造した半導体装置において、動作中に積層欠陥 8 2 が発生する。動作中に発生する積層欠陥 8 2 の位置は、紫外線 7 8 の照射により生じる積層欠陥 8 2 の位置と同じである。

10

20

30

40

50

**【 0 0 4 4 】**

図 5 ( c ) に示すように、位置の検出 (ステップ S 1 1 3 ) の後に、第 2 半導体部材 6 2 を形成する (ステップ S 1 1 4 )。

**【 0 0 4 5 】**

図 5 ( c ) に示すように、第 2 半導体部材 6 2 は、重畠領域 6 2 o 及び非重畠領域 6 2 n を含む。重畠領域 6 2 o は、第 1 方向 ( Z 軸方向 ) において、積層欠陥 8 2 の位置と重なる。非重畠領域 6 2 n は、第 1 方向において積層欠陥 8 2 の位置と重ならない。

**【 0 0 4 6 】**

この後、図 4 に例示したステップ S 1 2 0 (孔 6 5 H の形成)、及び、ステップ S 1 3 0 (第 3 半導体部材 6 3 の成長) が実施される。

10

**【 0 0 4 7 】**

図 5 ( d ) に示すように、開口部 7 1 o を有する第 1 マスク 7 1 が形成される。開口部 7 1 o は、積層欠陥 8 2 の位置と重なる重畠領域 6 2 o には形成されない。開口部 7 1 o は、積層欠陥 8 2 の位置と重ならない非重畠領域 6 2 n に形成される。

**【 0 0 4 8 】**

図 5 ( e ) に示すように、第 1 マスク 7 1 をマスクとして用いて、第 2 半導体部材 6 2 の一部を除去して、孔 6 5 H を形成する (ステップ S 1 2 0 )。例えば、孔 6 5 H の形成 (ステップ S 1 2 0 ) は、複数の孔 6 5 H を形成することを含む。孔 6 5 H の形成は、積層欠陥 8 2 の位置の検出結果に基づいて、複数の孔 6 5 H の少なくとも 1 つを非重畠領域 6 2 n に形成する。複数の孔 6 5 H の少なくとも 1 つは、重畠領域 6 2 o に形成しない。この後、第 1 マスク 7 1 を除去する。

20

**【 0 0 4 9 】**

図 5 ( f ) に示すように、孔 6 5 H の中に、第 3 半導体部材 6 3 を形成する。

**【 0 0 5 0 】**

第 2 実施形態においては、図 5 ( f ) に示すように、積層欠陥 8 2 の位置の上には、第 2 半導体部材 6 2 がある。積層欠陥 8 2 が無い位置に、第 3 半導体部材 6 3 が選択的に設けられる。これにより、例えば、動作中に積層欠陥 8 2 が生じた場合にも、積層欠陥 8 2 は、第 2 半導体部材 6 2 で止まる。

**【 0 0 5 1 】**

積層欠陥 8 2 の位置の上に第 3 半導体部材 6 3 が設けられる場合は、積層欠陥 8 2 が第 1 半導体部材 6 1 から第 3 半導体部材 6 3 に拡張し、半導体装置の上部に届く場合がある。これにより、順方向劣化 (V f 劣化) が生じる場合がある。

30

**【 0 0 5 2 】**

第 2 実施形態においては、積層欠陥 8 2 の位置の上には、第 2 半導体部材 6 2 がある。これにより、動作中に積層欠陥 8 2 が生じた場合も、積層欠陥 8 2 が、第 2 半導体部材 6 2 中に拡張して、上部に届くことがすることが抑制できる。

**【 0 0 5 3 】****( 第 3 実施形態 )**

図 6 は、第 3 実施形態に係る基板の製造方法を例示するフローチャート図である。

図 6 に示すように、構造体 6 5 の準備 (ステップ S 1 1 0 ) は、図 4 に關して説明したステップ S 1 1 1 ~ S 1 1 4 に加えて、第 4 元素を導入すること (ステップ S 1 1 5 ) を含む。

40

**【 0 0 5 4 】**

図 7 ( a ) ~ 図 7 ( f ) 、図 8 ( a ) 及び図 8 ( b ) は、第 3 実施形態に係る基板の製造方法を例示する模式的断面図である。

図 7 ( a ) に示すように、第 1 半導体部材 6 1 を準備する (ステップ S 1 1 1 )。

**【 0 0 5 5 】**

図 7 ( b ) に示すように、第 1 半導体部材 6 1 に紫外線 7 8 を照射して、基底面転位 8 1 から積層欠陥 8 2 を第 1 半導体部材 6 1 中に拡張させる (ステップ S 1 1 2 )。

**【 0 0 5 6 】**

50

この後、積層欠陥 8 2 の位置を検出する。積層欠陥 8 2 の位置が記憶される。図 7 ( b ) に示すように、第 1 半導体部材 6 1 は、積層欠陥 8 2 の位置含む第 1 領域 6 1 a と、積層欠陥 8 2 の位置を含まない第 2 領域 6 1 b と、を含む。

【 0 0 5 7 】

図 7 ( c ) に示すように、第 2 マスク 7 2 を形成する。第 2 マスク 7 2 の開口部 7 2 o は、積層欠陥 8 2 の位置を含む第 1 領域 6 1 a の上にある。第 2 マスク 7 2 は、積層欠陥 8 2 の位置を含まない第 2 領域 6 1 b を覆う。第 2 マスク 7 2 をマスクとして用いて、第 4 元素 7 4 を第 1 半導体部材 6 1 中に導入する。例えば、第 4 元素のイオン注入が行われる。

【 0 0 5 8 】

第 4 元素は、上記の第 1 群から選択された少なくとも 1 つ、または、上記の第 2 群から選択された少なくとも 1 つを含む。第 4 元素は、例えば、n 形不純物または p 形不純物である。第 4 元素が、積層欠陥 8 2 の位置を含む第 1 領域 6 1 a に選択的に導入される。

【 0 0 5 9 】

このように、積層欠陥 8 2 の位置の検出結果に基づいて、第 1 領域 6 1 a の少なくとも一部に第 4 元素を導入し、第 2 領域 6 1 b に第 4 元素を導入しない。これにより、第 4 元素が導入された第 4 元素導入領域 7 4 R が形成される（図 7 ( c ) 参照）。

【 0 0 6 0 】

この後、図 7 ( d ) に示すように、第 1 領域 6 1 a 及び第 2 領域 6 1 b の上に、第 2 半導体部材 6 2 を形成する（ステップ S 1 1 4 ）。第 2 半導体部材 6 2 は、第 4 元素導入領域 7 4 R の上にある。

【 0 0 6 1 】

この後、図 1 に関して説明したステップ S 1 2 0 及びステップ S 1 3 0 が実施される。図 7 ( e ) に示すように、第 1 マスク 7 1 を形成する。図 7 ( f ) に示すように、第 1 マスク 7 1 をマスクとして用いて、孔 6 5 H を形成する。孔 6 5 H は、第 1 半導体部材 6 1 の第 1 領域 6 1 a 及び第 2 領域 6 1 b に届く。

【 0 0 6 2 】

図 8 ( a ) に示すように、第 1 マスク 7 1 を除去する。図 8 ( b ) に示すように、孔 6 5 H 中に第 3 半導体部材 6 3 を形成する。

【 0 0 6 3 】

このような製造方法によれば、図 8 ( b ) に示すように、積層欠陥 8 2 の位置に第 4 元素導入領域 7 4 R が設けられる。積層欠陥 8 2 の位置においては、第 3 半導体部材 6 3 は、第 4 元素導入領域 7 4 R と接する。このような基板 6 8 を用いて製造された半導体装置においては、動作中に積層欠陥 8 2 が生じた場合にも、積層欠陥 8 2 に起因する悪影響を抑制することができる。

【 0 0 6 4 】

例えば、第 4 元素が、N、P 及び A s よりなる第 1 群から選択された少なくとも 1 つを含む場合、第 4 元素導入領域 7 4 R において、ドナー濃度を局所的に上昇させることができる。これにより、積層欠陥 8 2 の存在による抵抗の上昇を抑制することができる。

【 0 0 6 5 】

例えば、第 4 元素が、B、A 1 及び G a よりなる第 2 群から選択された少なくとも 1 つを含む場合、p 形の第 4 元素導入領域 7 4 R により積層欠陥 8 2 の位置への電流経路を実質的に遮断できる。第 4 元素導入領域 7 4 R は、積層欠陥 8 2 の位置の上の蓋となる。第 4 元素導入領域 7 4 R により、積層欠陥 8 2 を無害化できる。

【 0 0 6 6 】

例えば、第 4 元素が第 1 群から選択された少なくとも 1 つを含む場合、第 4 元素が導入された領域（第 4 元素導入領域 7 4 R ）における第 4 元素の濃度と、第 4 元素が導入された領域（第 4 元素導入領域 7 4 R ）における第 1 元素の濃度の和は、第 3 半導体部材 6 3 における第 3 元素の濃度以上であることが好ましい。和は、第 3 半導体部材 6 3 における第 3 元素の濃度よりも高いことがさらに好ましい。これにより、積層欠陥 8 2 の存在によ

10

20

30

40

50

る抵抗の上昇を、より効果的に抑制できる。

【0067】

例えば、第4元素が第2群から選択された少なくとも1つを含む場合、第4元素が導入された領域（第4元素導入領域74R）における第4元素の濃度は、第4元素が導入された領域（第4元素導入領域74R）における第1元素の濃度よりも高いことが好ましい。このような濃度により、第4元素導入領域74Rはp形となる。積層欠陥82の位置への電流経路をより効果的に遮断できる。

【0068】

図8(a)に示すように、孔65Hの少なくとも一部は、第1方向（Z軸方向）において、第1領域61aと重なる。安定した形状の第4元素導入領域74Rを形成し易くなる。

10

【0069】

（第4実施形態）

図9は、第4実施形態に係る半導体装置の製造方法を例示するフローチャート図である。

図10は、第4実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

図9に示すように、実施形態に係る半導体装置の製造方法は、構造体65を準備し（ステップS110）、孔65Hを形成し（ステップS120）、第3半導体部材63を形成（成長）し（ステップS130）、導電層を形成する（ステップS140）ことを含む。

【0070】

構造体65は、第1元素を含む炭化珪素を含む第1半導体部材61と、第2元素を含む炭化珪素を含む第2半導体部材62と、を含む（図2(b)参照）。第1元素は、N、P及びAsよりなる第1群から選択された少なくとも1つを含む。第2元素は、B、Al及びGaよりなる第2群から選択された少なくとも1つを含む。第1半導体部材61から第2半導体部材62への方向は、第1方向（例えばZ軸方向）に沿う。

20

【0071】

孔65Hは、第1方向に沿って第2半導体部材62を貫通し第1半導体部材61に届く（図2(d)参照）。第3半導体部材63は、第1群から選択された少なくとも1つを含む第3元素を含む炭化珪素を含む。第3半導体部材63を孔65H中に形成される（図2(f)参照）。

【0072】

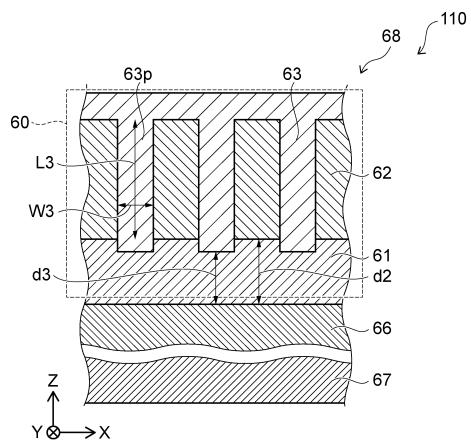

図10に示すように、半導体層60は、第1半導体部材61、第2半導体部材62及び第3半導体部材63を含む。導電層67は、半導体層60に電気的に接続される。この例では、導電層67は、第1半導体部材61に電気的に接続される。これにより、半導体装置110が得られる。

30

【0073】

半導体装置110においては、例えば、第3半導体部材63における不純物濃度が均一であり安定している。例えば、第2半導体部材62に含まれる不純物濃度と、第3半導体部材63に含まれる不純物濃度と、が中和されやすい。第2半導体部材62及び第3半導体部材63を含むSJ構造において、安定した特性が得られる。安定した特性が得られる半導体装置の製造方法が提供できる。

【0074】

40

（第5実施形態）

第5実施形態は、基板68に係る。実施形態に係る基板68の例が図10に示されている。

【0075】

図10に示すように、基板68は、炭化珪素を含む基材66と、半導体層60と、を含む。半導体層60は、第1元素を含む炭化珪素を含む第1半導体部材61と、第2元素を含む炭化珪素を含む第2半導体部材62と、第1群から選択された少なくとも1つを含む第3元素を含む第3半導体部材63とを含む。第1元素は、N、P及びAsよりなる第1群から選択された少なくとも1つを含む。第2元素は、B、Al及びGaよりなる第2群から選択された少なくとも1つを含む。第1半導体部材61は、第1方向（例えばZ軸方

50

向)において、基体66と第2半導体部材62との間にある。第3半導体部材63の少なくとも一部は、第2半導体部材62中において第1方向に沿って延びる。第3半導体部材63の少なくとも一部は、第1半導体部材61に接する。

【0076】

図10に示すように、基体66と第3半導体部材63の上記の少なくとも一部との間の第1方向( Z軸方向)に沿う距離を距離d3とする。基体66と第2半導体部材62との間の第1方向に沿う距離を距離d2とする。距離d3は、距離d2よりも短い。第3半導体部材63と第1半導体部材61との間においてより確実な電気的な接続が得やすい。第3半導体部材63において、均一で安定した不純物濃度が得られる。例えば、第3半導体部材63におけるキャリア濃度は、第1半導体部材61におけるキャリア濃度よりも高い。

10

【0077】

(第6実施形態)

第6実施形態は、半導体装置(例えば半導体装置110)に係る。実施形態に係る半導体装置の例が、図10に示されている。

【0078】

半導体装置110は、炭化珪素を含む基体66と、半導体層60と、半導体層60と電気的に接続された導電層67と、を含む。半導体層60は、上記の、第1半導体部材61、第2半導体部材62及び第3半導体部材63を含む。半導体装置110において、距離d3は、距離d2よりも短い。第3半導体部材63と第1半導体部材61との間においてより確実な電気的な接続が得られる。第3半導体部材63において、均一で安定した不純物濃度が得られる。例えば、第3半導体部材63におけるキャリア濃度は、第1半導体部材61におけるキャリア濃度よりも高い。

20

【0079】

図10に示すように、基板68及び半導体装置110において、第3半導体部材63は、第1方向と交差する第2方向で第2半導体部材62と対向する部分63pを含む。第2方向は、例えば、X軸方向である。第2方向は、Y軸方向でも良い。対向する部分63pの第1方向( Z軸方向)に沿う長さL3は、対向する部分63pの第2方向(例えばX軸方向)に沿う長さW3よりも長い。このような細長い形状を有する第3半導体部材63において、均一な不純物濃度(キャリア濃度)が得られる。

【0080】

30

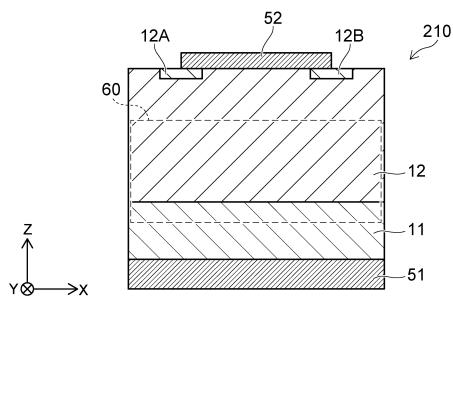

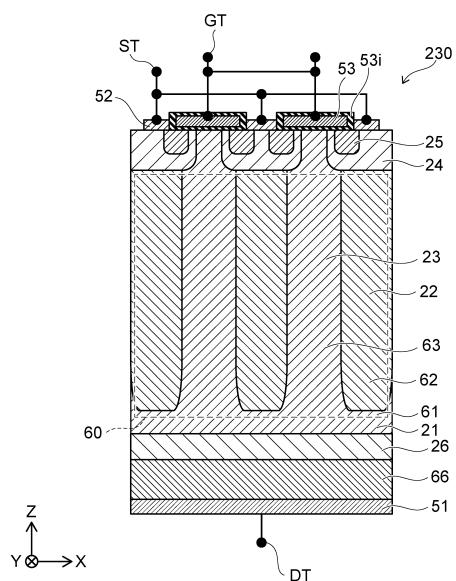

図11は、第6実施形態に係る半導体装置を例示する模式的断面図である。

図11に示すように、実施形態に係る半導体装置210は、第1半導体領域11、第2半導体領域12、第1電極51及び第2電極52を含む。第1半導体領域11及び第2半導体領域12の少なくともいずれかが、半導体層60に対応する。第1電極51及び第2電極52の少なくともいずれかが、導電層67に対応する。

【0081】

第1電極51と第2電極52との間に第1半導体領域11がある。第1半導体領域11と第2電極52との間に第2半導体領域12がある。例えば、第1半導体領域11は、第1導電形(例えば、n形)であり、第2半導体領域12は、第1導電形である。例えば、第1半導体領域11における第1導電形の不純物濃度は、第2半導体領域12における第1導電形の不純物濃度よりも高い。例えば、第2電極52は、第2半導体領域12とショットキー接合する。

40

【0082】

この例では、第2電極52の1つの端部と第2半導体領域12との間に、接合終端領域12Aが設けられている。第2電極52の別の端部と第2半導体領域12との間に、接合終端領域12Bが設けられている。

【0083】

第1電極51は、例えば、カソード電極である。第2電極52は、例えば、アノード電極である。第1半導体領域11は、例えば、n<sup>+</sup>領域に対応する。第2半導体領域12は、例えば、n<sup>-</sup>領域に対応する。第2半導体領域12は、例えば、ドリフト層に対応する。

50

## 【0084】

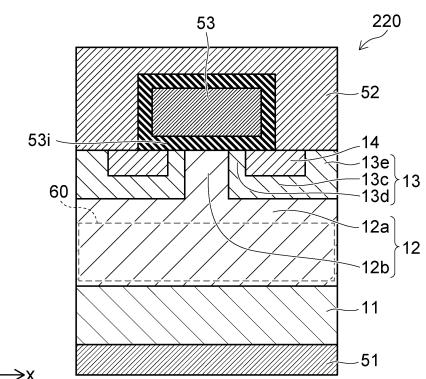

図12は、第6実施形態に係る半導体装置を例示する模式的断面図である。

図12に示すように、実施形態に係る半導体装置220は、第1半導体領域11、第2半導体領域12、第3半導体領域13、第4半導体領域14、第1～第3電極51～53、及び、絶縁部53iを含む。例えば、第1半導体領域11は、基体66に対応する。例えば、第2半導体領域12の少なくとも一部が半導体層60に対応する。第1電極51が、導電層67に対応する。

## 【0085】

第2半導体領域12は、第1導電形である。第3半導体領域13は、第2導電形である。第4半導体領域14は、第1導電形である。例えば、第1導電形はn形であり、第2導電形はp形である。

10

## 【0086】

第1半導体領域11は、第1方向(Z軸方向)において、第1電極51と第2電極52の少なくとも一部との間、及び、第1電極51と第3電極53との間にある。第3電極53から第2電極52の上記の少なくとも一部への方向は、第2方向(例えばX軸方向)に沿う。

## 【0087】

第2半導体領域12は、第1部分12a及び第2部分12bを含む。第1部分12aは、第1方向(Z軸方向)において、第1半導体領域11と第2電極52の上記の少なくとも一部との間にある。第2部分12bは、第1方向(Z軸方向)において、第1半導体領域11と第3電極53との間にある。

20

## 【0088】

第3半導体領域13は、第3部分13c及び第4部分13dを含む。第3部分13cは、第1方向(Z軸方向)において、第1部分12aと第2電極52の上記の少なくとも一部との間にある。この例では、第3半導体領域13は、第5部分13eをさらに含む。

## 【0089】

第4半導体領域14は、第1方向(Z軸方向)において、第3部分13cと第2電極52の上記の少なくとも一部との間にある。第4半導体領域14は、第2電極52と電気的に接続される。

30

## 【0090】

第3半導体領域13の第4部分13dは、第2方向(例えばX軸方向)において、第2半導体領域12の第2部分12bの少なくとも一部と、第4半導体領域14との間にある。

## 【0091】

この例では、X軸方向において、第3部分13cと第5部分13eとの間に、第4半導体領域14がある。第5部分13eは、第2電極52と電気的に接続される。

## 【0092】

絶縁部53iは、第1方向(Z軸方向)において、第2部分12bと第3電極53との間にある。この例では、絶縁部53iの一部は、Z軸方向において、第3電極53と第4部分13dとの間、及び、第3電極53と第4半導体領域14の一部との間に設けられている。

40

## 【0093】

第1電極51は、例えば、ドレイン電極に対応する。第2電極52は、例えば、ソース電極に対応する。第3電極53は、例えば、ゲート電極に対応する。第1半導体領域11は、例えば、SiC基板である。第1半導体領域11は、例えば、n<sup>+</sup>領域である。第2半導体領域12は、例えば、ドリフト層に対応する。第2半導体領域12は、例えば、n<sup>-</sup>領域である。第3半導体領域13は、例えば、pウエルに対応する。第4半導体領域14は、例えば、n<sup>+</sup>ソースに対応する。半導体装置220は、例えば、MOSFETである。半導体装置220は、例えば、縦型パワーMOSFETである。第1半導体領域11は、例えば、p領域でも良い。この場合、半導体装置220は、例えば、IGBT(Insulated Gate Bipolar Transistor)である。

50

## 【0094】

図13は、第6実施形態に係る半導体装置を例示する模式的断面図である。

図13に示すように、実施形態に係る半導体装置230において、第1電極51の上に基体66がある。基体66の上に、n<sup>+</sup>層26がある。n<sup>+</sup>層26の上に、n層21がある。基体66からn<sup>+</sup>層26への方向は、Z軸方向に沿う。n層21の上に、複数のn層23及び複数のp層22が設けられる。n層23及びp層22は、例えば、X軸方向に沿って交互に並ぶ。p層22の上に、p<sup>+</sup>層24が設けられる。p<sup>+</sup>層24の一部の上に複数のn<sup>+</sup>層25が設けられる。複数のn<sup>+</sup>層25の1つと、複数のn<sup>+</sup>層25の別の1つと、の間にp<sup>+</sup>層24の一部がある。

## 【0095】

10

複数のn<sup>+</sup>層25の1つの上に絶縁部53iが設けられる。その絶縁部53iの上に、1つの第3電極53が設けられる。複数のn<sup>+</sup>層25の別の1つの上に別の絶縁部53iが設けられる。その別の絶縁部53iの上に、別の1つの第3電極53が設けられる。

## 【0096】

複数のn<sup>+</sup>層25の1つと、複数のn<sup>+</sup>層25の別の1つと、の間に設けられたp<sup>+</sup>層24の一部の上に、第2電極52が設けられる。第2電極52は、p<sup>+</sup>層24と電気的に接続される。

## 【0097】

第1電極51にドレイン端子DTが電気的に接続される。第2電極52にソース端子STが電気的に接続される。第3電極53にゲート端子GTが電気的に接続される。

20

## 【0098】

半導体装置230は、複数のn層23及び複数のp層22を含むSJ構造を有する。n層21、複数のn層23及び複数のp層22が半導体層60に対応する。第1電極51が導電層67に対応する。例えば、図2(f)に例示した構造において、例えば、表面研磨加工などにより第2半導体部材62(複数のp層22)を露出させる。複数のn層23の上にp<sup>+</sup>層24及び複数のn<sup>+</sup>層25を形成する。これにより、半導体装置230が得られる。半導体装置230においては、例えば、複数のn層23及び複数のp層22を含むSJ構造において、均一で安定した不純物濃度が得られる。

## 【0099】

実施形態によれば、安定した特性が得られる基板の製造方法、半導体装置の製造方法、基板及び半導体装置を提供することができる。

30

## 【0100】

実施形態において、不純物濃度に関する情報は、例えば、SIMS(Secondary Ion Mass Spectrometry)などにより得られる。上記において、不純物濃度は、例えば、キャリア濃度でも良い。キャリア濃度は、例えば、C-V(キャパシタンス-電圧)特性装置などにより測定できる。

## 【0101】

本願明細書において、「電気的に接続される状態」は、複数の導電体が物理的に接してこれら複数の導電体の間に電流が流れる状態を含む。「電気的に接続される状態」は、複数の導電体の間に、別の導電体が挿入されて、これらの複数の導電体の間に電流が流れる状態を含む。

40

## 【0102】

本願明細書において、「垂直」及び「平行」は、厳密な垂直及び厳密な平行だけではなく、例えば製造工程におけるばらつきなどを含むものであり、実質的に垂直及び実質的に平行であれば良い。

## 【0103】

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。例えば、半導体装置に含まれる半導体部材、電極及び絶縁部などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明

50

の範囲に包含される。

【0104】

また、各具体例のいずれか2つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

【0105】

その他、本発明の実施の形態として上述した半導体装置、基板、半導体装置の製造方法、及び、基板の製造方法を基にして、当業者が適宜設計変更して実施し得る全ての半導体装置、基板、半導体装置の製造方法、及び、基板の製造方法も、本発明の要旨を包含する限り、本発明の範囲に属する。

【0106】

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【0107】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0108】

1 1 ~ 1 4 ... 第 1 ~ 第 4 半導体領域、 1 2 A、 1 2 B ... 接合終端領域、 1 2 a、 1 2 b ... 第 1、 第 2 部分、 1 3 c ~ 1 3 e ... 第 3 ~ 第 5 部分、 2 1 ... n 層、 2 2 ... p 層、 2 3 ... n 層、 2 4 ... p + 層、 2 5 ... n + 層、 2 6 ... n + 層、 5 1 ~ 5 3 ... 第 1 ~ 第 3 電極、 5 3 i ... 絶縁部、 6 0 ... 半導体層、 6 1 ~ 6 3 ... 第 1 ~ 第 3 半導体部材、 6 1 a、 6 1 b ... 第 1、 第 2 領域、 6 2 n ... 非重畳領域、 6 2 o ... 重畳領域、 6 3 p ... 対向する部分、 6 5 ... 構造体、 6 5 H ... 孔、 6 6 ... 基体、 6 7 ... 導電層、 6 8 ... 基板、 7 1、 7 2 ... 第 1、 第 2 マスク、 7 1 o、 7 2 o ... 開口部、 7 4 ... 第 4 元素、 7 4 R ... 第 4 元素導入領域、 7 8 ... 紫外線、 8 1 ... 基底面転位、 8 2 ... 積層欠陥、 1 1 0、 2 1 0、 2 2 0、 2 3 0 ... 半導体装置、 D T ... ドレイン端子、 G T ... ゲート端子、 L 3 ... 長さ、 S T ... ソース端子、 W 3 ... 長さ、 d 2、 d 3 ... 距離

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図 3】

【図 4】

終了

【図5】

【図6】

10

20

30

40

【図7】

【図8】

50

【図9】

【図10】

【図11】

【図12】

30

40

50

【図 1 3】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

|                        | F I           |         |

|------------------------|---------------|---------|

| H 01 L 29/12 (2006.01) | H 01 L 29/86  | 3 0 1 P |

| H 01 L 29/78 (2006.01) | H 01 L 29/78  | 6 5 2 T |

| H 01 L 29/739(2006.01) | H 01 L 29/78  | 6 5 2 H |

| H 01 L 21/336(2006.01) | H 01 L 29/78  | 6 5 5 A |

| H 01 L 21/20 (2006.01) | H 01 L 29/78  | 6 5 8 E |

| H 01 L 21/265(2006.01) | H 01 L 21/20  |         |

|                        | H 01 L 21/265 | Z       |

## (56)参考文献

特開2016-015378 (JP, A)

特開2007-013058 (JP, A)

特開2018-049928 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

C 30 B 29 / 36

C 30 B 25 / 20

H 01 L 21 / 205

H 01 L 29 / 872

H 01 L 21 / 329

H 01 L 29 / 12

H 01 L 29 / 78

H 01 L 29 / 739

H 01 L 21 / 336

H 01 L 21 / 20

H 01 L 21 / 265