(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5350655号

(P5350655)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年8月30日(2013.8.30)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 626C |

| HO1L 29/786 | (2006.01) | HO1L 27/12 | B    |

| HO1L 21/02  | (2006.01) |            |      |

| HO1L 27/12  | (2006.01) |            |      |

請求項の数 1 (全 40 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-73142 (P2008-73142)    |

| (22) 出願日     | 平成20年3月21日 (2008.3.21)        |

| (65) 公開番号    | 特開2008-294408 (P2008-294408A) |

| (43) 公開日     | 平成20年12月4日 (2008.12.4)        |

| 審査請求日        | 平成23年2月15日 (2011.2.15)        |

| (31) 優先権主張番号 | 特願2007-118086 (P2007-118086)  |

| (32) 優先日     | 平成19年4月27日 (2007.4.27)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 官入 秀和<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 鈴木 聰一郎                                         |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ベース基板と、前記ベース基板上の複数の開口部が形成された絶縁膜と、前記複数の開口部以外の領域において前記絶縁膜に接する半導体膜と、前記半導体膜上のゲート絶縁膜と、前記ゲート絶縁膜上の電極と、を有し、

前記半導体膜は、前記ゲート絶縁膜を間に挟んで前記電極と重なるチャネル形成領域と、前記チャネル形成領域を挟む一对の不純物領域と、を有し、

前記チャネル形成領域は、前記複数の開口部と重なっており、

前記複数の開口部は、第1の開口部と、第2の開口部と、を有し、

前記第1の開口部は、前記一对の不純物領域の一方から他方に向かって設けられ、且つ、前記一对の不純物領域の一方及び他方の外部まで広がっており、

前記第2の開口部は、前記一对の不純物領域の一方から他方に向かって設けられ、且つ、前記一对の不純物領域の一方及び他方の外部まで広がっていることを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、SOI (Silicon on Insulator) 基板を用いた半導体装置及びその作製方法に関する。特に貼り合わせSOI技術に関するものであって、絶縁膜を間に挟んで単結晶若しくは多結晶の半導体膜を基板に貼り合わせることで得られるSO

I 基板を用いた、半導体装置及びその作製方法に関する。

【背景技術】

【0002】

半導体集積回路に対する高集積化、高速化、高機能化、低消費電力化への要求が厳しさを増しており、その実現に向け、バルクのトランジスタに替わる有力な手段としてS O I 基板を用いたトランジスタが注目されている。S O I 基板を用いたトランジスタはバルクのトランジスタと比較すると、半導体膜が絶縁膜上に形成されているので、寄生容量を低減し、基板に流れる漏れ電流の発生を抑えることができ、高速化、低消費電力化がより期待できる。そして活性層として用いる半導体膜を薄くできるので、短チャネル効果を抑制し、よって素子の微細化、延いては半導体集積回路の高集積化を実現することができる。またS O I 基板を用いたトランジスタは完全にラッチアップフリーであるため、ラッチアップによる発熱で素子が破壊される懼れがない。さらにバルクのトランジスタのようにウェルによる素子分離を行う必要がないため、素子間の距離を短くすることができ、高集積化を実現できるといったメリットをも有している。10

【0003】

S O I 基板の作製方法の一つに、スマートカットに代表されるU N I B O N D、E L T R A N ( E p i t a x i a l L a y e r T r a n s f e r ) 、誘電体分離法、P A C E ( P l a s m a A s s i s t e d C h e m i c a l E t c h i n g ) 法などの、絶縁膜を介して半導体膜を基板に貼り合わせる貼り合わせ法がある。上記貼り合わせ法を用いることで、単結晶の半導体膜を用いた高機能な集積回路をあらゆる基板上に形成することができる。20

【0004】

ところで、S O I 基板を用いたトランジスタは、半導体膜の不純物領域と基板との間に接合容量が形成される。半導体集積回路のさらなる低消費電力化を実現するにあたり、この接合容量の低減は非常に重要な課題である。接合容量を低減し、なおかつ集積回路の安定した動作を確保するためには、不純物領域と基板の間に存在する絶縁膜に、絶縁性を維持しつつ誘電率の低い材料を用いることが望まれる。

【0005】

下記の特許文献 1 には、半導体膜と基板との間に中空のスペースが設けられた、S O N ( S i l i c o n o n N o t h i n g ) 構造のトランジスタについて記載されている。30 また特許文献 2 には、半導体膜と基板との間に空洞を有するS O I 基板の構成について記載されている。比誘電率が 1 である空気を用いて基板と半導体膜との間を絶縁することで、接合容量を低減することができる。

【特許文献 1】特開 2001 - 144276 号公報

【特許文献 2】特開 2004 - 146461 号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかし特許文献 1 に記載されているS O N 構造のトランジスタは、作製工程において取り扱いに注意を要する水素ガスを多用する上に、半導体膜の膜厚や空洞の位置の制御が難しく、複雑なプロセスで形成しなくてはならない。そして半導体膜中において、結晶成長が進んでぶつかるところの結晶性が他と比べて劣ってしまうため、素子の特性がばらつき、高い歩留まりを得るのが難しいという問題がある。一方、特許文献 2 に記載されているS O I 基板では、形成されるS O N 構造のトランジスタに接合容量を低減させる余地がさらに残されている。40

【0007】

本発明は上述した問題に鑑み、より単純なプロセスで、従来よりも接合容量を低減し、低消費電力化を実現することが出来る半導体装置及びその作製方法の提案を課題とする。

【課題を解決するための手段】

【0008】

本発明では、ベース基板（支持基板）に開口部を有する絶縁膜を形成し、該絶縁膜を間に挟んでボンド基板（半導体基板）の一部をベース基板に転置することで、ベース基板との間に空洞を有する半導体膜をベース基板上に形成する。そして該半導体膜を用い、トランジスタなどの半導体素子を有する半導体装置を形成する。具体的に、本発明の半導体装置が有するトランジスタは、活性層として用いる半導体膜とベース基板との間に、絶縁膜の開口部によって形成される空洞を有する。上記空洞は単数であっても良いし、複数であっても良い。また上記空洞は、半導体膜のチャネル形成領域と重なるように形成されても良いし、ソースまたはドレインのいずれか一方と重なるように形成されていても良いし、或いは、ソース、ドレイン及びチャネル形成領域と重なるように形成されていても良い。

10

#### 【0009】

また本発明の半導体装置の作製方法は、後に空洞として用いられる開口部を有する絶縁膜を、ベース基板上に形成する。次に、該開口部がボンド基板側に向くようにボンド基板とベース基板を貼り合わせることで、ボンド基板とベース基板の間に空洞を形成する。そして、その一部がベース基板に残存するようにボンド基板を劈開し、該空洞をベース基板との間に有するように、半導体膜をベース基板上に形成する。次に、該空洞をベース基板との間に維持したまま該半導体膜を所望の形状に加工し、トランジスタなどの半導体素子を形成する。

#### 【発明の効果】

#### 【0010】

本発明の半導体装置が有するトランジスタは、半導体膜と空洞が接している。よって、例えば酸化珪素などの無機絶縁膜に比べて比誘電率の低い空気、窒素、不活性ガスなどの材料で空洞を満たしておくことで、トランジスタの寄生容量または接合容量を低減することが出来る。よって、半導体装置の低消費電力化を実現することが出来る。

20

#### 【0011】

本発明の作製方法では、エッティングなどの既に確立された手法を用いて開口部を形成することが出来るので、所望の深さ及び形状を有する空洞を、より安全かつ簡単な作製方法で制御良く形成することが出来るので、半導体装置の作製にかかるコストを抑えることができ、歩留まりも高くすることができる。

#### 【発明を実施するための最良の形態】

30

#### 【0012】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

#### 【0013】

##### （実施の形態1）

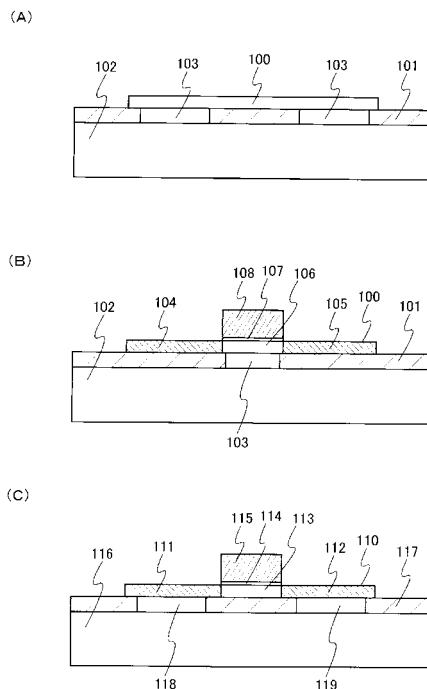

本発明の半導体装置において、半導体素子が有する半導体膜の構成について、図1(A)を用いて説明する。

#### 【0014】

40

図1(A)に示す半導体膜100は、絶縁膜101を間に挟むようにベース基板102上に形成されている。絶縁膜101と半導体膜100とが接合することで、半導体膜100をベース基板102に貼り合わせることが出来る。また絶縁膜101は開口部を少なくとも1つ有しており、該開口部によって、半導体膜100とベース基板102の間に空洞103が形成されている。空洞103の一部または全ては半導体膜100の一部と重なっており、よって、絶縁膜101は開口部以外の領域において、少なくともその一部が半導体膜100と接している。空洞103の数は、図1(A)に示す構成に限定されない。半導体膜100とベース基板102の間に空洞103が単数設けられていても良いし、複数設けられていても良い。

#### 【0015】

50

絶縁膜 101 は単数の絶縁膜で形成されていても良いし、複数の絶縁膜が積層されるように形成されていても良い。

#### 【0016】

絶縁膜 101 は、開口部を除くベース基板 102 の全面に形成されていても良いし、少なくとも半導体膜 100 とその一部が接する程度に、部分的に形成されていても良い。また図 1 (A) では、絶縁膜 101 が有する開口部においてベース基板 102 が露出しているが、本発明はこの構成に限定されない。絶縁膜 101 が、開口部においてもベース基板 102 上に形成されていても良い。

#### 【0017】

次に、図 1 (A) に示す半導体膜 100 を用いた半導体素子の一つである、トランジスタの構成について説明する。図 1 (B) は、半導体膜 100 を用いて形成されたトランジスタの断面図の一例である。図 1 (B) に示すトランジスタは、半導体膜 100 に、ソースまたはドレインとして機能する一対の不純物領域 104、105 と、チャネル形成領域 106 とを有する。そして図 1 (B) に示すトランジスタは、ゲート絶縁膜 107 を間に挟んでチャネル形成領域 106 と重なるように、ゲートとして機能する電極 108 を有する。

#### 【0018】

図 1 (B) に示すトランジスタでは、空洞 103 が、チャネル形成領域 106、電極 108 と重なる位置に設けられている。なお本発明において、空洞の位置は、図 1 (B) に示した構成に限定されない。空洞は、一対の不純物領域 104、105 のいずれか一方と重なるように形成されていても良いし、一対の不純物領域 104、105 及びチャネル形成領域 106 と重なるように形成されていても良い。少なくともチャネル形成領域 106 と重なるように空洞を形成する場合、不純物領域 104、105 とのみ重なるように空洞を形成する場合に比べて、よりセルフヒーティングを抑えることが出来る。

#### 【0019】

次に、2つの空洞と重なるように形成される半導体膜 110 を用いたトランジスタの構成について説明する。図 1 (C) は、2つの空洞と重なる半導体膜 110 を用いて形成されたトランジスタの断面図の一例である。図 1 (C) に示すトランジスタは、半導体膜 110 に、ソースまたはドレインとして機能する一対の不純物領域 111、112 と、チャネル形成領域 113 とを有する。そして図 1 (C) に示すトランジスタは、ゲート絶縁膜 114 を間に挟んでチャネル形成領域 113 と重なるように、ゲートとして機能する電極 115 を有する。

#### 【0020】

図 1 (C) に示すトランジスタでは、半導体膜 110 とベース基板 116との間に、絶縁膜 117 が有する開口部によって形成される空洞 118、119 を有する。そして空洞 118、119 が、一対の不純物領域 111、112 と、それぞれ重なる位置に設けられている。空洞 118、119 が少なくとも不純物領域 111、112 と重なっている場合、チャネル形成領域 113 とのみ重なっている空洞を形成する場合と比べて、トランジスタの接合容量をより低減させることが出来る。

#### 【0021】

本発明の半導体装置が有するトランジスタは、半導体膜 100、110 とベース基板 102、116 の間に空洞 103、118、119 を有しており、さらに半導体膜 100、110 と空洞 103、118、119 とがそれぞれ接している。よって、例えば酸化珪素などの無機絶縁膜に比べて比誘電率の低い空気、窒素、不活性ガスなどで空洞 103、118、119 を満たしておることで、トランジスタの寄生容量または接合容量を低減することが出来る。上記気体は、温度変化に伴う体積膨張を抑えるために、水分の含有率を低減させておくのが望ましい。なお、実際のところ半導体膜 100、110 の、空洞 103、118、119 とそれぞれ接する部分には、自然酸化膜が形成される場合がある。しかし特許文献 2 に記載されている絶縁膜は数  $\mu\text{m}$  から数百  $\mu\text{m}$  の膜厚を有していることが前提となっており、自然酸化膜は、上記の絶縁膜に比べてその膜厚は数  $\text{nm}$  程度と飛躍的に薄

10

20

30

40

50

い。よって本発明は、半導体膜100、110の空洞103、118、119に接する部分に上記膜厚を有する絶縁膜を形成した場合に比べて、トランジスタの寄生容量または接合容量を低減することが出来ると言える。

#### 【0022】

なお本実施の形態では、空洞103、118、119を気体で満たす場合について示したが、本発明はこの構成に限定されない。例えば空洞103、118、119を、酸化珪素などの無機絶縁膜よりも比誘電率の低い材料、例えば内部に多数の気孔を有する多孔質絶縁膜（ポーラス材料）などで満たすようにしても良い。

#### 【0023】

なお本発明の範疇に含まれる半導体装置には、マイクロプロセッサ、画像処理回路などの集積回路や、半導体表示装置等、ありとあらゆる半導体装置が含まれる。半導体表示装置には、液晶表示装置、有機発光素子（OLED）に代表される発光素子を各画素に備えた発光装置、DMD（Digital Micromirror Device）、PDP（Plasma Display Panel）、FED（Field Emission Display）等や、半導体膜を用いた回路素子を駆動回路に有しているその他の表示装置がその範疇に含まれる。

#### 【0024】

##### （実施の形態2）

本実施の形態では、本発明の半導体装置が有するトランジスタの、より具体的な構成について説明する。

#### 【0025】

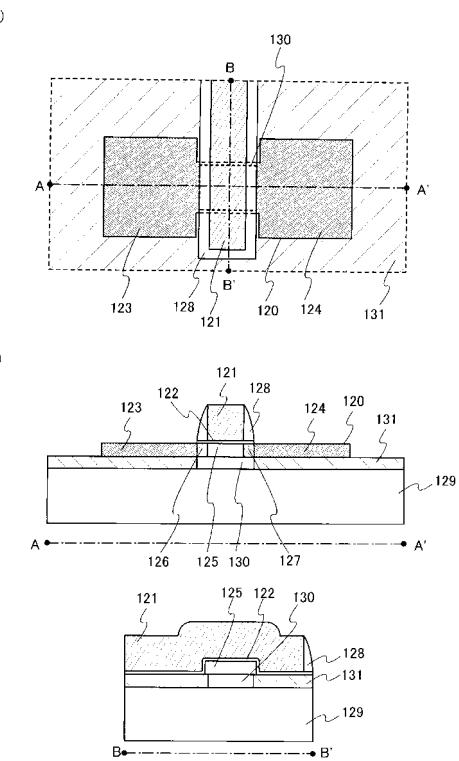

図2に、本発明の半導体装置が有するトランジスタの、断面図及び上面図の一例を示す。図2（A）はトランジスタの上面図であり、図2（A）のA-A'における断面図を図2（B）に、図2（A）のB-B'における断面図を図2（C）に示す。

#### 【0026】

図2に示すトランジスタは、活性層として機能する半導体膜120と、半導体膜120と重なる部分がゲートとして機能する電極121と、半導体膜120と電極121の間に設けられたゲート絶縁膜122とを有する。また半導体膜120は、ソースまたはドレインとして機能する不純物領域123、124、チャネル形成領域125、不純物領域123、124とチャネル形成領域125の間に設けられたLDD（Lightly Doped Drain）領域126、127を有している。

#### 【0027】

半導体膜120とベース基板129の間には、絶縁膜131が形成されている。そして、絶縁膜131が有する開口部によって、半導体膜120とベース基板129の間に空洞130が1つ形成されている。図2では、空洞130が、半導体膜120と重なる領域の内部に完全に納まっている。また空洞130は、半導体膜120のうち、チャネル形成領域125と重なっている。少なくともチャネル形成領域125と重なるように空洞を形成する場合、不純物領域123、124とのみ重なるように空洞を形成する場合に比べて、よりセルフヒーティングを抑えることが出来る。

#### 【0028】

なお図2では、空洞130が半導体膜120と重なる領域の内部に完全に納まっているが、本発明はこの構成に限定されない。空洞130が半導体膜120と重なる領域の外部にまで広がっていても良い。この場合、空洞130が半導体膜120と重なる領域の外部において開口していることになる。空洞130が開口していることで、空洞130の内部と外部の気圧の差がなくなる。よって、加熱処理における温度変化が急激であっても半導体膜120の形状が変化するのを防ぐことが出来る。

#### 【0029】

なお図2に示すトランジスタは、半導体膜120がLDD領域126、127を有しているが、本発明はこの構成に限定されない。LDD領域126、127は必ずしも設けなくとも良いし、或いはいずれか一方のみが設けられていても良い。また図2に示すトランジ

10

20

30

40

50

スタは、半導体膜 120 のうち、電極 121 と重なっている領域とは異なる領域に LDD 領域 126、127 が設けられているが、本発明はこの構成に限定されない。LDD 領域 126、127 は、電極 121 と重なっている領域に設けられていても良い。或いは、電極 121 と重なっている領域と、それ以外の領域とに跨るように設けられていても良い。

#### 【0030】

また図 2 に示すトランジスタは、LDD 領域 126、127 を形成する際にマスクとして用いるサイドウォール 128 が電極 121 の側部に設けられているが、本発明はこの構成に限定されない。

#### 【0031】

図 3 に、本発明の半導体装置が有するトランジスタの、断面図及び上面図の一例を示す。

図 3 (A) はトランジスタの上面図であり、図 3 (A) の A - A' における断面図を図 3 (B) に、図 3 (A) の B - B' における断面図を図 3 (C) に示す。

#### 【0032】

図 3 に示すトランジスタは、活性層として機能する半導体膜 140 と、半導体膜 140 と重なる部分がゲートとして機能する電極 141 と、半導体膜 140 と電極 141 の間に設けられたゲート絶縁膜 142 を有する。また半導体膜 140 は、ソースまたはドレンとして機能する不純物領域 143、144、チャネル形成領域 145、不純物領域 143、144 とチャネル形成領域 145 の間に設けられた LDD (Lightly Doped Drain) 領域 146、147 を有している。

#### 【0033】

半導体膜 140 とベース基板 149 の間には、絶縁膜 152 が形成されている。そして、絶縁膜 152 が有する開口部によって、半導体膜 140 とベース基板 149 の間に 2 つの空洞 150 と空洞 151 が形成されている。空洞 150 は不純物領域 143 と、空洞 151 は不純物領域 144 と重なっている。空洞 150、151 が少なくとも不純物領域 143、144 と重なっている場合、チャネル形成領域 145 とのみ重なっている空洞を形成する場合と比べて、トランジスタの接合容量をより低減させることが出来る。なお、空洞 150 と空洞 151 は、半導体膜 140 と重なる領域の内部に完全に納まっていても良いし、図 3 のように、空洞 150、空洞 151 が半導体膜 140 と重なる領域の外部にまで広がっていても良い。後者の場合、空洞 150、空洞 151 が半導体膜 140 と重なる領域の外部において開口していることになる。空洞 150、151 が開口している場合、空洞 150、151 の内部と外部の気圧の差がなくなる。よって、加熱処理における温度変化が急激であっても、半導体膜 140 の形状が変化するのを防ぐことが出来る。

#### 【0034】

なお図 3 に示すトランジスタは、半導体膜 140 が LDD 領域 146、147 を有しているが、本発明はこの構成に限定されない。LDD 領域 146、147 は必ずしも設けなくとも良いし、或いはいずれか一方のみが設けられていても良い。また図 3 に示すトランジスタは、半導体膜 140 のうち、電極 141 と重なっている領域とは異なる領域に LDD 領域 146、147 が設けられているが、本発明はこの構成に限定されない。LDD 領域 146、147 は、電極 141 と重なっている領域と、それ以外の領域とに跨るように設けられていても良い。

#### 【0035】

また図 3 に示すトランジスタは、LDD 領域 146、147 を形成する際にマスクとして用いるサイドウォール 148 が電極 141 の側部に設けられているが、本発明はこの構成に限定されない。

#### 【0036】

図 4 に、本発明の半導体装置が有するトランジスタの、断面図及び上面図の一例を示す。図 4 (A) はトランジスタの上面図であり、図 4 (A) の A - A' における断面図を図 4 (B) に、図 4 (A) の B - B' における断面図を図 4 (C) に示す。

#### 【0037】

図 4 に示すトランジスタは、活性層として機能する半導体膜 160 と、半導体膜 160 と

10

20

30

40

50

重なる部分がゲートとして機能する電極 161 と、半導体膜 160 と電極 161 の間に設けられたゲート絶縁膜 162 とを有する。また半導体膜 160 は、ソースまたはドレインとして機能する不純物領域 163、164、チャネル形成領域 165、不純物領域 163、164 とチャネル形成領域 165 の間に設けられた LDD (Lightly Doped Drain) 領域 166、167 を有している。

#### 【0038】

半導体膜 160 とベース基板 169 の間には、絶縁膜 171 が形成されている。そして、絶縁膜 171 が有する開口部によって、半導体膜 160 とベース基板 169 の間に 1 つの空洞 172 が形成されている。そして空洞 172 は不純物領域 163、164 及びチャネル形成領域 165 と重なっている。空洞 172 が不純物領域 163、164 及びチャネル形成領域 165 と重なっている場合、セルフヒーティングを抑えるのみならず、トランジスタの接合容量をより低減させることができることになる。なお空洞 172 は、図 4 のように、半導体膜 160 と重なる領域の内部に完全に納まっていても良いし、空洞 172 が半導体膜 160 と重なる領域の外部にまで広がっていても良い。後者の場合、空洞 172 が半導体膜 160 と重なる領域の外部において開口していることになる。空洞 172 が開口している場合、空洞 172 の内部と外部の気圧の差がなくなる。よって、加熱処理における温度変化が急激であっても、半導体膜 160 の形状が変化するのを防ぐことが出来る。

#### 【0039】

なお図 4 に示すトランジスタは、半導体膜 160 が LDD 領域 166、167 を有しているが、本発明はこの構成に限定されない。LDD 領域 166、167 は必ずしも設けなくとも良いし、或いはいずれか一方のみが設けられていても良い。また図 4 に示すトランジスタは、半導体膜 160 のうち、電極 161 と重なっている領域とは異なる領域に LDD 領域 166、167 が設けられているが、本発明はこの構成に限定されない。LDD 領域 166、167 は、電極 161 と重なっている領域に設けられていても良い。或いは、電極 161 と重なっている領域と、それ以外の領域とに跨るように設けられていても良い。

#### 【0040】

また図 4 に示すトランジスタは、LDD 領域 166、167 を形成する際にマスクとして用いるサイドウォール 168 が電極 161 の側部に設けられているが、本発明はこの構成に限定されない。

#### 【0041】

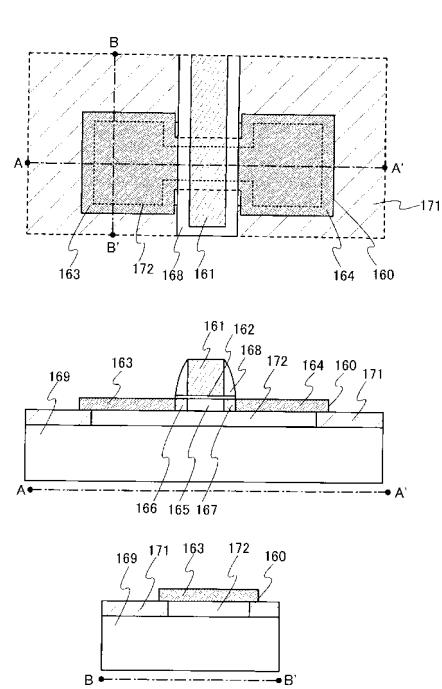

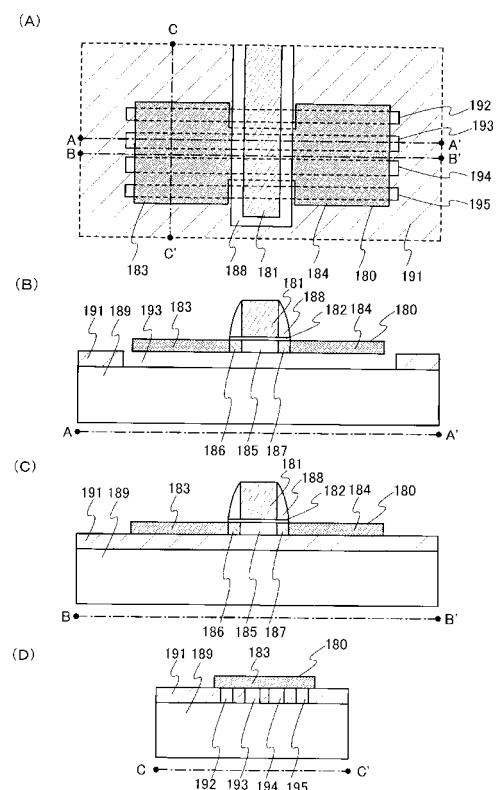

図 5 に、本発明の半導体装置が有するトランジスタの、断面図及び上面図の一例を示す。図 5 (A) はトランジスタの上面図であり、図 5 (A) の A - A' における断面図を図 5 (B) に、図 5 (A) の B - B' における断面図を図 5 (C)、図 5 (A) の C - C' における断面図を図 5 (D) に示す。

#### 【0042】

図 5 に示すトランジスタは、活性層として機能する半導体膜 180 と、半導体膜 180 と重なる部分がゲートとして機能する電極 181 と、半導体膜 180 と電極 181 の間に設けられたゲート絶縁膜 182 とを有する。また半導体膜 180 は、ソースまたはドレインとして機能する不純物領域 183、184、チャネル形成領域 185、不純物領域 183、184 とチャネル形成領域 185 の間に設けられた LDD (Lightly Doped Drain) 領域 186、187 を有している。

#### 【0043】

半導体膜 180 とベース基板 189 の間には、絶縁膜 191 が形成されている。そして、絶縁膜 191 が有する開口部によって、半導体膜 180 とベース基板 189 の間に、複数の空洞 192 ~ 195 が設けられている。空洞 192 ~ 195 は、不純物領域 183、184 及びチャネル形成領域 185 と重なっている。空洞 192 ~ 195 が不純物領域 183、184 及びチャネル形成領域 185 と重なることで、セルフヒーティングを抑えるのみならず、トランジスタの接合容量をより低減させることができる。

#### 【0044】

なお、空洞 192 ~ 195 は、半導体膜 180 と重なる領域の内部に完全に納まっていて

10

20

30

40

50

も良いし、図5のように、半導体膜180と重なる領域の外部にまで広がっていても良い。後者の場合、空洞192～195が半導体膜180と重なる領域の外部において開口していることになる。空洞192～195が開口している場合、空洞192～195の内部と外部の気圧の差がなくなる。よって、加熱処理における温度変化が急激であっても、半導体膜180の形状が変化するのを防ぐことが出来る。

#### 【0045】

なお図5に示すトランジスタは、半導体膜180がLDD領域186、187を有しているが、本発明はこの構成に限定されない。LDD領域186、187は必ずしも設けなくとも良いし、或いはいずれか一方のみが設けられていても良い。また図5に示すトランジスタは、半導体膜180のうち、電極181と重なっている領域とは異なる領域にLDD領域186、187が設けられているが、本発明はこの構成に限定されない。LDD領域186、187は、電極181と重なっている領域に設けられていても良い。或いは、電極181と重なっている領域と、それ以外の領域とに跨るように設けられていても良い。

10

#### 【0046】

また図5に示すトランジスタは、LDD領域186、187を形成する際にマスクとして用いるサイドウォール188が電極181の側部に設けられているが、本発明はこの構成に限定されない。

#### 【0047】

なお、半導体膜の下部に設けられる空洞が図4に示すように単数である場合、半導体膜の下部により広い面積で空洞をレイアウトすることが可能になるので、空洞が複数の場合よりも接合容量及び寄生容量をより低減させることができ、セルフヒーティングもより抑えることができる。また、半導体膜の下部に設けられる空洞が図5に示すように複数である場合、単数の場合よりも物理的強度のより強いトランジスタを形成することが出来る。

20

#### 【0048】

また図2に示すトランジスタの場合、チャネル形成領域と重なるように空洞が1つだけ設けられているが、本発明はこの構成に限定されない。チャネル形成領域と重なるように空洞が複数設けられても良い。空洞が単数である場合、チャネル形成領域の下部により広い面積で空洞をレイアウトすることが可能になるので、空洞が複数の場合よりもセルフヒーティングをより抑えることができる。また、チャネル形成領域の下部に設けられる空洞が複数である場合、単数の場合よりも物理的強度のより強いトランジスタを形成することが出来る。

30

#### 【0049】

また図3に示すトランジスタの場合、各不純物領域と重なるような空洞が1つずつ設けられているが、本発明はこの構成に限定されない。一つの不純物領域と重なる空洞が複数設けられても良い。一つの不純物領域と重なる空洞が単数である場合、不純物領域の下部により広い面積で空洞をレイアウトすることが可能になるので、空洞が複数の場合よりもセルフヒーティングをより抑えることができる。また、1つの不純物領域の下部に設けられる空洞が複数である場合、単数の場合よりも物理的強度のより強いトランジスタを形成することが出来る。

#### 【0050】

40

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0051】

##### (実施の形態3)

本実施の形態では、半導体基板(ボンド基板)から、開口部を有する絶縁膜が形成された支持基板(ベース基板)に半導体膜を転置する、本発明の半導体装置の作製方法について説明する。

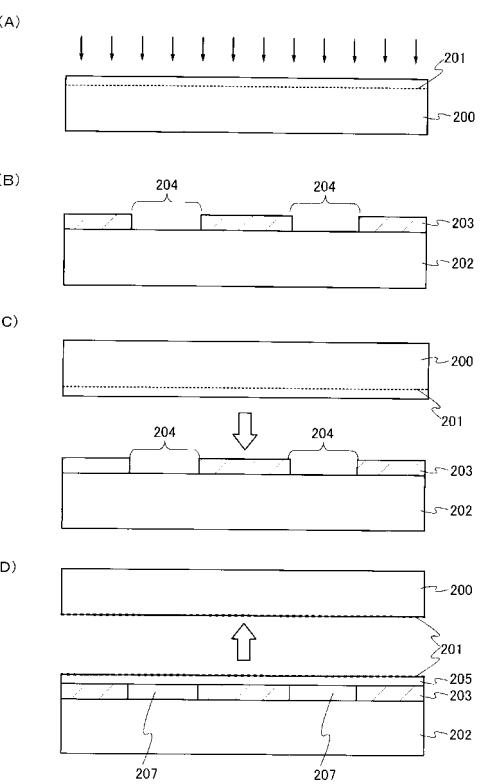

#### 【0052】

まず図6(A)に示すように、ボンド基板200に、矢印で示すように水素又は希ガス、或いは水素イオン又は希ガスイオンを照射し、ボンド基板200の表面から一定の深さの領域に、微小ボイドを有する欠陥層201を形成する。欠陥層201が形成される位置は

50

、上記注入の加速電圧によって決まる。そして欠陥層 201 の位置により、ボンド基板 200 からベース基板に転置する半導体膜 205 の厚さが決まるので、注入の加速電圧は半導体膜の厚さを考慮して行う。当該半導体膜 205 の厚さは 10 nm 乃至 200 nm、好みしくは 10 nm 乃至 50 nm の厚さとする。例えば水素をボンド基板 200 に注入する場合、ドーズ量は  $1 \times 10^{16}$  乃至  $1 \times 10^{17} / \text{cm}^2$  とするのが望ましい。

#### 【0053】

次に図 6 (B) に示すように、ベース基板 202 上に形成された絶縁膜 203 を所望の形状に加工 (パターニング) することで、絶縁膜 203 を部分的に除去して開口部 204 を形成する。ベース基板 202 は開口部 204 において露出していても良いし、開口部 204 において絶縁膜 203 に覆われていても良い。具体的には、レジストで形成されたマスクを用い、絶縁膜 203 をエッチングすることで、パターニングを行うことが出来る。開口部 204 は、後にトランジスタの半導体膜とベース基板 202 の間に形成される空洞に相当する。よって開口部 204 の形成は、トランジスタの半導体膜のレイアウトを考慮して行われる。

#### 【0054】

絶縁膜 203 は、酸化珪素、窒化酸化珪素、窒化珪素等の絶縁性を有する材料を用いて形成する。例えば酸化珪素を絶縁膜 203 として用いる場合、絶縁膜 203 はシランと酸素、TEOS (テトラエトキシシラン) と酸素等の混合ガスを用い、熱 CVD、プラズマ CVD、常圧 CVD、バイアス ECR CVD 等の気相成長法によって形成することができる。この場合、絶縁膜 203 の表面を酸素プラズマ処理で緻密化しても良い。

#### 【0055】

また絶縁膜 203 として、有機シランガスを用いて化学気相成長法により作製される酸化珪素を用いていても良い。有機シランガスとしては、珪酸エチル (TEOS : 化学式 Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン (TMS : 化学式 Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン (SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン (SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>) 等のシリコン含有化合物を用いることができる。

#### 【0056】

絶縁膜 203 は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。例えば本実施の形態では、ベース基板 202 に近い側から、窒素よりも酸素の含有量が高い窒化酸化珪素、酸素よりも窒素の含有量が高い窒化酸化珪素、有機シランガスを用いて化学気相成長法により作製される酸化珪素の順に積層された絶縁膜 203 を用いる。

#### 【0057】

また、窒化珪素を絶縁膜 203 として用いる場合、シランとアンモニアの混合ガスを用い、プラズマ CVD 等の気相成長法によって形成することができる。また、窒化酸化珪素を絶縁膜 203 として用いる場合、シランとアンモニアの混合ガス、またはシランと酸化窒素の混合ガスを用い、プラズマ CVD 等の気相成長法によって形成することができる。

#### 【0058】

なお、ボンド基板 200 と、ベース基板 202 とを貼り合わせる前に、ボンド基板 200 に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中において 350℃、2 時間程度行う。

#### 【0059】

マスクを除去した後、図 6 (C) に示すように、ボンド基板 200 と、ベース基板 202 とを、絶縁膜 203 を間に挟むように貼り合わせる。ボンド基板 200 とベース基板 202 の貼り合わせは、開口部 204 がボンド基板 200 側を向くように行う。絶縁膜 203 とボンド基板 200 とが、開口部 204 以外の領域において接合することで、ボンド基板 200 とベース基板 202 とを貼り合わせることができる。

#### 【0060】

10

20

30

40

50

接合の形成はファン・デル・ワールス力を用いて行われており、室温で強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、ベース基板202は様々なものを用いることが可能である。例えばベース基板202としては、アルミニノシリケートガラス、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラスなどのガラス基板の他、石英基板、サファイア基板などの基板を用いることが出来る。さらにベース基板202として、シリコン、ガリウムヒ素、インジウムリンなどの半導体基板などを用いることができる。

#### 【0061】

なお、半導体基板をベース基板202として用いる場合、ベース基板202を熱酸化させることで、絶縁膜203を形成することができる。

10

#### 【0062】

ボンド基板200として、シリコン、ゲルマニウムなどの単結晶半導体基板または多結晶半導体基板を用いることができる。その他に、ガリウムヒ素、インジウムリンなどの化合物半導体で形成された単結晶半導体基板または多結晶半導体基板を、ボンド基板200として用いることができる。またボンド基板200として、結晶格子に歪みを有するシリコン、シリコンに対しゲルマニウムが添加されたシリコングルマニウムなどの半導体基板を用いていても良い。歪みを有するシリコンは、シリコンよりも格子定数の大きいシリコングルマニウムまたは窒化珪素上における成膜により、形成することができる。

#### 【0063】

なおベース基板202とボンド基板200とを貼り合わせた後に、加熱処理又は加圧処理を行っても良い。加熱処理又は加圧処理を行うことで接合強度を向上させることができる。

20

#### 【0064】

ボンド基板200とベース基板202の間で接合を行った後、熱処理を行うことにより、欠陥層201において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、図6(D)に示すように、欠陥層201においてボンド基板200が劈開し、ボンド基板200の一部であった半導体膜205が乖離する。熱処理の温度はボンド基板200の耐熱温度以下で行なうことが好ましく、例えば400乃至600の範囲内で熱処理を行えば良い。この剥離により、半導体膜205が、ベース基板202に転置される。その後、絶縁膜203と半導体膜205の接合をさらに強固にするため、400乃至600の熱処理を行うのが好ましい。

30

#### 【0065】

半導体膜205の結晶面方位はボンド基板200の面方位によって制御することができる。形成する半導体素子に適した結晶面方位を有するボンド基板200を、適宜選択して用いればよい。またトランジスタの移動度は半導体膜205の結晶面方位によって異なる。より移動度の高いトランジスタを得たい場合、チャネルの向きと結晶面方位とを考慮し、ボンド基板200の貼り合わせの方向を定めるようにする。

#### 【0066】

半導体膜205とベース基板202の間には、開口部204によって形成される一対の空洞207が設けられている。

40

#### 【0067】

次に、図7(A)に示すように、転置された半導体膜205の表面を平坦化する。平坦化は必ずしも必須ではないが、平坦化を行うことで、後に形成されるトランジスタにおいて半導体膜205とゲート絶縁膜の界面の特性を向上させることが出来る。具体的に平坦化は、化学的機械的研磨(CMP: Chemical Mechanical Polishing)または液体ジェット研磨などにより、行なうことができる。半導体膜205の厚さは、上記平坦化により薄膜化される。平坦化後の半導体膜205は、5nm乃至25nmの厚さであることが望ましい。

#### 【0068】

なお本実施の形態では、欠陥層201の形成により半導体膜205をボンド基板200か

50

ら剥離するスマートカット法を用いる場合について示すが、ELTRAN (Epitaxial Layer Transfer)、誘電体分離法、PACE (Plasma Assisted Chemical Etching) 法などの、他の貼り合わせ法を用いて半導体膜 205 をベース基板 202 に貼り合わせるようにしても良い。

#### 【0069】

次に、図 7 (B) に示すように、半導体膜 205 をパターニングすることで、島状の半導体膜 206 を形成する。半導体膜 205 をパターニング後においても、島状の半導体膜 206 とベース基板 202 の間には、開口部 204 によって形成される一対の空洞 207 が維持されている。

#### 【0070】

上記工程を経て形成された半導体膜 206 を用い、本発明はトランジスタ等の各種半導体素子を形成することが出来る。図 7 (C) には、半導体膜 206 を用いて形成されたトランジスタ 210 を例示している。

#### 【0071】

本発明の作製方法では、開口部 204 をエッティングで形成しているので、所望の深さ及び形状を有する空洞 207 を、簡単な手順で制御良く形成することが出来る。

#### 【0072】

また作製されたトランジスタ 210 は、半導体膜 206 とベース基板 202 の間に空洞 207 を有しており、さらに半導体膜 206 と空洞 207 とが接している。よって、例えば酸化珪素などの無機絶縁膜に比べて比誘電率の低い空気、窒素、不活性ガスなどで空洞 207 を満たしておくことで、トランジスタ 210 の寄生容量または接合容量を低減することが出来る。上記気体は、温度変化に伴う体積膨張を抑えるために、水分の含有率を低減させておくのが望ましい。なお実際のところ半導体膜 206 の、空洞 207 と接する部分には、自然酸化膜が形成される場合がある。しかし特許文献 2 に記載されている絶縁膜は数  $\mu\text{m}$  から数百  $\mu\text{m}$  の膜厚を有していることが前提となっており、自然酸化膜は、上記の絶縁膜に比べてその膜厚は数  $\text{nm}$  程度と飛躍的に薄い。よって本発明は、半導体膜 206 の空洞に接する部分に上記膜厚を有する絶縁膜を形成した場合に比べて、トランジスタ 210 の寄生容量または接合容量を低減することが出来ると言える。

#### 【0073】

なお本実施の形態では、空洞 207 を気体で満たす場合について示したが、本発明はこの構成に限定されない。例えば空洞 207 を、酸化珪素などの無機絶縁膜よりも比誘電率の低い材料、例えば内部に多数の気孔を有する多孔質絶縁膜（ポーラス材料）などで満たすようにしても良い。

#### 【0074】

また本実施の形態では、島状の半導体膜 206 とベース基板 202 の間に空洞 207 が 2 つ設けられている構成を示しているが、本発明はこの構成に限定されない。設けられる空洞 207 は単数であっても良いし、3 以上の複数であっても良い。また本実施の形態では、ソースまたはドレインとして機能する不純物領域 211 と重なるように空洞 207 が形成されているが、本発明はこの構成に限定されない。半導体膜 206 のチャネル形成領域 212 と重なるように空洞 207 が形成されていても良いし、一対の不純物領域 211 及びチャネル形成領域 212 と重なるように空洞 207 が形成されていても良い。

#### 【0075】

なお空洞 207 が少なくとも不純物領域 211 と重なっている場合、チャネル形成領域 212 とのみ重なっている空洞 207 を形成する場合と比べて、トランジスタ 210 の接合容量をより低減させることが出来る。また、少なくともチャネル形成領域 212 と重なっている空洞 207 を形成する場合、不純物領域 211 とのみ重なっている空洞 207 を形成する場合に比べて、よりセルフヒーティングを抑えることが出来る。

#### 【0076】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0077】

10

20

30

40

50

## (実施の形態 4 )

本実施の形態では、開口部を有する絶縁膜が形成された半導体基板（ボンド基板）と、支持基板（ベース基板）とを貼り合わせることで、半導体膜をベース基板に転置する、本発明の半導体装置の作製方法について説明する。

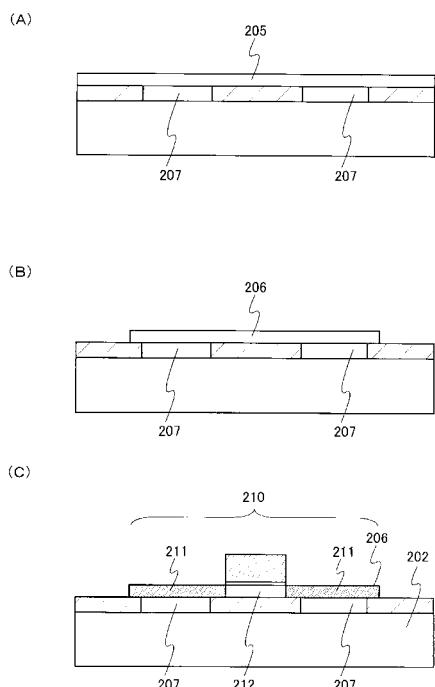

## 【0078】

まず図8(A)に示すように、表面に絶縁膜301が形成されたボンド基板300を用意する。絶縁膜301は、酸化珪素、窒化酸化珪素、窒化珪素等の絶縁性を有する材料を用いて形成する。絶縁膜301の膜厚は後に形成される欠陥層302の深さに関与するため、その膜厚は均一であることが望ましい。例えば酸化珪素を絶縁膜301として用いる場合、絶縁膜301はボンド基板300を熱酸化することで形成するのが望ましく、例えば、水蒸気雰囲気下で900～1100の熱処理により形成すると良い。或いは酸素プラズマ処理によりボンド基板300を酸化することで、絶縁膜301を形成しても良い。また酸化珪素を絶縁膜301として用いる場合、絶縁膜301はシランと酸素、TEOS(テトラエトキシシラン)と酸素等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の気相成長法によって形成することもできる。この場合、絶縁膜301の表面を酸素プラズマ処理で緻密化しても良い。

10

## 【0079】

また絶縁膜301として、有機シランガスを用いて化学気相成長法により作製される酸化珪素を用いていても良い。有機シランガスとしては、珪酸エチル(TEOS:化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン(TMS:化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

20

## 【0080】

絶縁膜301は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。例えば本実施の形態では、ボンド基板300に近い側から、窒素よりも酸素の含有量が高い窒化酸化珪素、酸素よりも窒素の含有量が高い窒化酸化珪素、有機シランガスを用いて化学気相成長法により作製される酸化珪素の順に積層された絶縁膜301を用いる。

30

## 【0081】

また、窒化珪素を絶縁膜301として用いる場合、シランとアンモニアの混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。また、窒化酸化珪素を絶縁膜301として用いる場合、シランとアンモニアの混合ガス、またはシランと酸化窒素の混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。

## 【0082】

なお、ボンド基板300から半導体膜305を取り出す工程において、ボンド基板300に高い濃度の水素又は希ガス、或いは水素イオン又は希ガスイオンを注入するので、ボンド基板300の表面が粗くなってしまい、ベース基板との接合で十分な結合強度が得られない場合がある。絶縁膜301を設けることで、水素又は希ガス、或いは水素と希ガスのイオンを注入する際にボンド基板300の表面が保護され、ベース基板とボンド基板300の接合を良好に行うことが出来る。

40

## 【0083】

次に、ボンド基板300に、矢印で示すように水素又は希ガス、或いは水素イオン又は希ガスイオンを注入し、ボンド基板300の表面から一定の深さの領域に、微小ボイドを有する欠陥層302を形成する。欠陥層302が形成される位置は、上記注入の加速電圧によって決まる。そして欠陥層302の位置により、ボンド基板300からベース基板に転置する半導体膜305の厚さが決まるので、注入の加速電圧は半導体膜の厚さを考慮して行う。当該半導体膜305の厚さは10nm乃至200nm、好ましくは10nm乃至50nmの厚さとする。例えば水素をボンド基板300に注入する場合、ドーズ量は1×1

50

$0^{1.6}$  乃至  $1 \times 10^{1.7} / \text{cm}^2$  とするのが望ましい。

#### 【0084】

なお本実施の形態では、絶縁膜301をボンド基板300上に形成してからボンド基板300に欠陥層302を形成しているが、本発明はこの構成に限定されない。絶縁膜301を形成する前にボンド基板300に欠陥層302を形成しても良い。或いは、複数の絶縁膜を絶縁膜301として用いる場合、該複数の絶縁膜のうちの幾つかをボンド基板300上に形成した後に、ボンド基板300に欠陥層302を形成し、次に、該複数の絶縁膜のうちの残りの絶縁膜を形成するようにしても良い。この場合、例えば窒化酸化珪素膜と酸化珪素膜を積層したものを、絶縁膜301として用いると良い。そして、窒化酸化珪素膜をボンド基板300上に形成してからボンド基板300に欠陥層302を形成し、次に有機シランガスを用いて化学気相成長法により作製される酸化珪素膜を形成すると良い。10

#### 【0085】

次に図8(B)に示すように、ボンド基板300上に形成された絶縁膜301を所望の形状に加工(パターニング)することで、絶縁膜301を部分的に除去して開口部303を形成する。ボンド基板300は開口部303において露出していても良いし、開口部303において絶縁膜301に覆われていても良い。具体的には、レジストで形成されたマスクを用い、絶縁膜301をエッチングすることで、パターニングを行うことが出来る。開口部303は、後にトランジスタの半導体膜とベース基板304の間に形成される空洞に相当する。よって開口部303の形成は、トランジスタの半導体膜のレイアウトを考慮して行われる。20

#### 【0086】

なお、ボンド基板300と、ベース基板304とを貼り合わせる前に、ボンド基板300に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中において350、2時間程度行う。

#### 【0087】

マスクを除去した後、図8(C)に示すように、ボンド基板300と、ベース基板304とを、絶縁膜301を間に挟むように貼り合わせる。ボンド基板300とベース基板304の貼り合わせは、開口部303がベース基板304側を向くように行う。絶縁膜301とベース基板304とが、開口部303以外の領域において接合することで、ボンド基板300とベース基板304とを貼り合わせることができる。30

#### 【0088】

接合の形成はファン・デル・ワールス力を用いて行われており、室温で強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、ベース基板304は様々なものを用いることが可能である。例えばベース基板304としては、アルミニシリケートガラス、バリウムホウケイ酸ガラス、アルミニホウケイ酸ガラスなどのガラス基板の他、石英基板、サファイア基板などの基板を用いることが出来る。さらにベース基板304として、シリコン、ガリウムヒ素、インジウムリンなどの半導体基板などを用いることができる。

#### 【0089】

ボンド基板300として、シリコン、ゲルマニウムなどの単結晶半導体基板または多結晶半導体基板を用いることができる。その他に、ガリウムヒ素、インジウムリンなどの化合物半導体で形成された単結晶半導体基板または多結晶半導体基板を、ボンド基板300として用いることができる。またボンド基板300として、結晶格子に歪みを有するシリコン、シリコンに対しゲルマニウムが添加されたシリコンゲルマニウムなどの半導体基板を用いていても良い。歪みを有するシリコンは、シリコンよりも格子定数の大きいシリコンゲルマニウムまたは窒化珪素上における成膜により、形成することができる。40

#### 【0090】

なおベース基板304とボンド基板300とを貼り合わせた後に、加熱処理又は加圧処理を行っても良い。加熱処理又は加圧処理を行うことで接合強度を向上させることができる。50

## 【0091】

ボンド基板300とベース基板304の間で接合を行った後、熱処理を行うことにより、欠陥層302において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、図8(D)に示すように、欠陥層302においてボンド基板300が劈開し、ボンド基板300の一部であった半導体膜305と、絶縁膜301とが乖離する。熱処理の温度はボンド基板300の耐熱温度以下で行なうことが好ましく、例えば400乃至600の範囲内で熱処理を行なえば良い。この剥離により、半導体膜305と、絶縁膜301とが、ベース基板304に転置される。その後、絶縁膜301とベース基板304の接合をさらに強固にするため、400乃至600の熱処理を行うのが好ましい。

## 【0092】

10

半導体膜305の結晶面方位はボンド基板300の面方位によって制御することができる。形成する半導体素子に適した結晶面方位を有するボンド基板300を、適宜選択して用いればよい。またトランジスタの移動度は半導体膜305の結晶面方位によって異なる。より移動度の高いトランジスタを得たい場合、チャネルの向きと結晶面方位とを考慮し、ボンド基板300の貼り合わせの方向を定めるようにする。

## 【0093】

半導体膜305とベース基板304の間には、開口部303によって形成される空洞306が設けられている。

## 【0094】

20

図8(D)の工程まで終了したら、後は実施の形態3と同様に、転置された半導体膜305の表面を平坦化し、パターニングすることで、島状の半導体膜を形成する。半導体膜305のパターニング後においても、島状の半導体膜とベース基板304の間には、開口部303によって形成される空洞306が維持される。

## 【0095】

上記工程を経て形成された島状の半導体膜を用い、本発明はトランジスタ等の各種半導体素子を形成することが出来る。

## 【0096】

本発明の作製方法では、開口部303をエッチングで形成しているので、所望の深さ及び形状を有する空洞306を、簡単な手順で制御良く形成することが出来る。

## 【0097】

30

なお本実施の形態では、欠陥層302の形成により半導体膜305をボンド基板300から剥離するスマートカット法を用いる場合について示すが、ELTRAN(Epitaxial Layer Transfer)、誘電体分離法、PACE(Plasma Assisted Chemical Etching)法などの、他の貼り合わせ法を用いて半導体膜305をベース基板304に貼り合わせるようにしても良い。

## 【0098】

また島状の半導体膜を用いて作製されるトランジスタは、島状の半導体膜とベース基板304の間に空洞306を有しており、さらに半導体膜305と空洞306とが接している。よって、例えば酸化珪素などの無機絶縁膜に比べて比誘電率の低い空気、窒素、不活性ガスなどで空洞306を満たしておくことで、トランジスタの寄生容量または接合容量を低減することが出来る。上記気体は、温度変化に伴う体積膨張を抑えるために、水分の含有率を低減させておくのが望ましい。

40

## 【0099】

なお、実際のところ島状の半導体膜の、空洞306と接する部分には、自然酸化膜が形成される場合がある。しかし特許文献2に記載されている絶縁膜は数μmから数百μmの膜厚を有していることが前提となっており、自然酸化膜は、上記の絶縁膜に比べてその膜厚は数nm程度と飛躍的に薄い。よって本発明は、島状の半導体膜の空洞に接する部分に上記膜厚を有する絶縁膜を形成した場合に比べて、トランジスタの寄生容量または接合容量を低減する、或いはセルフヒーティングを抑えることが出来ると言える。

## 【0100】

50

なお本実施の形態では、空洞306を気体で満たす場合について示したが、本発明はこの構成に限定されない。例えば空洞306を、酸化珪素などの無機絶縁膜よりも比誘電率の低い材料、例えば内部に多数の気孔を有する多孔質絶縁膜（ポーラス材料）などで満たすようにしても良い。

#### 【0101】

また本実施の形態では、半導体膜305と接するように絶縁膜301を先に形成してから、絶縁膜301とベース基板304とを接合させている。よって、半導体膜305と絶縁膜301の界面における界面準位密度を、半導体膜305と絶縁膜301とを接合させた場合に比べて、均一にすることができる。従って、半導体膜305をパターニングすることで形成される島状の半導体膜を用いたトランジスタは、閾値電圧などの特性のばらつきをより抑えることができる。10

#### 【0102】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0103】

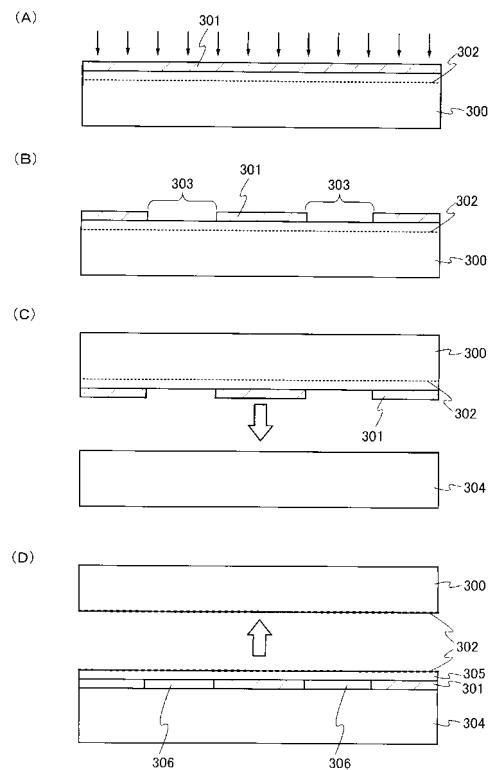

##### (実施の形態5)

本実施の形態では、開口部を有する絶縁膜が形成された半導体基板（ボンド基板）と、開口部を有する絶縁膜が形成された支持基板（ベース基板）とを貼り合わせることで、半導体膜をベース基板に転置する、本発明の半導体装置の作製方法について説明する。

#### 【0104】

まず図9(A)に示すように、表面に絶縁膜311が形成されたボンド基板310を用意する。絶縁膜311は、酸化珪素、窒化酸化珪素、窒化珪素等の絶縁性を有する材料を用いて形成する。絶縁膜311の膜厚は後に形成される欠陥層312の深さに関与するため、その膜厚は均一であることが望ましい。例えば酸化珪素を絶縁膜311として用いる場合、絶縁膜311はボンド基板310を熱酸化することで形成するのが望ましく、例えば、水蒸気雰囲気下で900～1100の熱処理により形成すると良い。或いは酸素プラズマ処理によりボンド基板310を酸化することで、絶縁膜311を形成しても良い。また酸化珪素を絶縁膜311として用いる場合、絶縁膜311はシランと酸素、TEOS（テトラエトキシシラン）と酸素等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の気相成長法によって形成することもできる。この場合、絶縁膜311の表面を酸素プラズマ処理で緻密化しても良い。2030

#### 【0105】

また絶縁膜311として、有機シランガスを用いて化学気相成長法により作製される酸化珪素を用いていても良い。有機シランガスとしては、珪酸エチル（TEOS：化学式Si(OCH<sub>3</sub>)<sub>4</sub>）、テトラメチルシラン（TMS：化学式Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(OCH<sub>3</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物を用いることができる。

#### 【0106】

絶縁膜311は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。例えば本実施の形態では、ボンド基板310に近い側から、窒素よりも酸素の含有量が高い窒化酸化珪素、酸素よりも窒素の含有量が高い窒化酸化珪素、有機シランガスを用いて化学気相成長法により作製される酸化珪素の順に積層された絶縁膜311を用いる。40

#### 【0107】

また、窒化珪素を絶縁膜311として用いる場合、シランとアンモニアの混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。また、窒化酸化珪素を絶縁膜311として用いる場合、シランとアンモニアの混合ガス、またはシランと酸化窒素の混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。

#### 【0108】

10

20

30

40

50

なお、ボンド基板310から半導体膜317を取り出す工程において、ボンド基板310に高い濃度の水素又は希ガス、或いは水素イオン又は希ガスイオンを注入するので、ボンド基板310の表面が粗くなってしまい、ベース基板との接合で十分な結合強度が得られない場合がある。絶縁膜311を設けることで、水素又は希ガス、或いは水素と希ガスのイオンを注入する際にボンド基板310の表面が保護され、ベース基板とボンド基板310の接合を良好に行うことが出来る。

#### 【0109】

次に、ボンド基板310に、矢印で示すように水素又は希ガス、或いは水素イオン又は希ガスイオンを注入し、ボンド基板310の表面から一定の深さの領域に、微小ボイドを有する欠陥層312を形成する。欠陥層312が形成される位置は、上記注入の加速電圧によって決まる。そして欠陥層312の位置により、ボンド基板310からベース基板に転置する半導体膜317の厚さが決まるので、注入の加速電圧は半導体膜の厚さを考慮して行う。当該半導体膜317の厚さは10nm乃至200nm、好ましくは10nm乃至50nmの厚さとする。例えば水素をボンド基板310に注入する場合、ドーザ量は $1 \times 10^{16}$ 乃至 $1 \times 10^{17} / \text{cm}^2$ とするのが望ましい。

10

#### 【0110】

なお本実施の形態では、絶縁膜311をボンド基板310上に形成してからボンド基板310に欠陥層312を形成しているが、本発明はこの構成に限定されない。絶縁膜311を形成する前にボンド基板310に欠陥層312を形成しても良い。或いは、複数の絶縁膜を絶縁膜311として用いる場合、該複数の絶縁膜のうちの幾つかをボンド基板310上に形成した後に、ボンド基板310に欠陥層312を形成し、次に、該複数の絶縁膜のうちの残りの絶縁膜を形成するようにしても良い。この場合、例えば窒化酸化珪素膜と酸化珪素膜を積層したものを、絶縁膜311として用いると良い。そして、窒化酸化珪素膜をボンド基板310上に形成してからボンド基板310に欠陥層312を形成し、次に有機シランガスを用いて化学気相成長法により作製される酸化珪素膜を形成すると良い。

20

#### 【0111】

次に図9(B)に示すように、ボンド基板310上に形成された絶縁膜311を所望の形状に加工(パターニング)することで、絶縁膜311を部分的に除去して開口部313を形成する。ボンド基板310は開口部313において露出していても良いし、開口部313において絶縁膜311に覆われていても良い。具体的には、レジストで形成されたマスクを用い、絶縁膜311をエッチングすることで、パターニングを行うことが出来る。開口部313は、後にトランジスタの半導体膜とベース基板314の間に形成される空洞に相当する。よって開口部313の形成は、トランジスタの半導体膜のレイアウトを考慮して行われる。

30

#### 【0112】

なお、ボンド基板310と、ベース基板314とを貼り合わせる前に、ボンド基板310に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中において350、2時間程度行う。

#### 【0113】

マスクを除去した後、図9(C)に示すように、ボンド基板310と、ベース基板314とを貼り合わせる。本実施の形態では、開口部315を有する絶縁膜316が形成されたベース基板314を用意する。絶縁膜316は、絶縁膜311として用いることができる上述の材料で、形成することができる。また開口部315はエッチングなどにより形成することができる。ボンド基板310とベース基板314の貼り合わせは、絶縁膜311及び絶縁膜316を間に挟むように、なおかつ開口部313と開口部315とが少なくとも一部重なるように貼り合わせる。絶縁膜311と絶縁膜316とが、開口部313及び開口部315以外の領域において接合することで、ボンド基板310とベース基板314とを貼り合わせることができる。

40

#### 【0114】

接合の形成はファン・デル・ワールス力を用いて行われており、室温で強固な接合が形成

50

される。なお、上記接合は低温で行うことが可能であるため、ベース基板314は様々なものを用いることが可能である。例えばベース基板314としては、アルミニノシリケートガラス、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラスなどのガラス基板の他、石英基板、サファイア基板などの基板を用いることが出来る。さらにベース基板314として、シリコン、ガリウムヒ素、インジウムリンなどの半導体基板などを用いることができる。

#### 【0115】

なお、半導体基板をベース基板314として用いる場合、ベース基板314を熱酸化させることで、絶縁膜316を形成することができる。

#### 【0116】

ボンド基板310として、シリコン、ゲルマニウムなどの単結晶半導体基板または多結晶半導体基板を用いることができる。その他に、ガリウムヒ素、インジウムリンなどの化合物半導体で形成された単結晶半導体基板または多結晶半導体基板を、ボンド基板310として用いることができる。またボンド基板310として、結晶格子に歪みを有するシリコン、シリコンに対しゲルマニウムが添加されたシリコングルマニウムなどの半導体基板を用いていても良い。歪みを有するシリコンは、シリコンよりも格子定数の大きいシリコングルマニウムまたは窒化珪素上における成膜により、形成することができる。

#### 【0117】

なおベース基板314とボンド基板310とを貼り合わせた後に、加熱処理又は加圧処理を行っても良い。加熱処理又は加圧処理を行うことで接合強度を向上させることができる。

#### 【0118】

ボンド基板310とベース基板314の間で接合を行った後、熱処理を行うことにより、欠陥層312において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、図9(D)に示すように、欠陥層312においてボンド基板310が劈開し、ボンド基板310の一部であった半導体膜317と、絶縁膜311とが乖離する。熱処理の温度はボンド基板310の耐熱温度以下で行なうことが好ましく、例えば400乃至600の範囲内で熱処理を行えば良い。この剥離により、半導体膜317と、絶縁膜311とが、ベース基板314に転置される。その後、絶縁膜311と絶縁膜316の接合をさらに強固にするため、400乃至600の熱処理を行うのが好ましい。

#### 【0119】

半導体膜317の結晶面方位はボンド基板310の面方位によって制御することができる。形成する半導体素子に適した結晶面方位を有するボンド基板310を、適宜選択して用いればよい。またトランジスタの移動度は半導体膜317の結晶面方位によって異なる。より移動度の高いトランジスタを得たい場合、チャネルの向きと結晶面方位とを考慮し、ボンド基板310の貼り合わせの方向を定めるようにする。

#### 【0120】

半導体膜317とベース基板314の間には、開口部313及び開口部315によって形成される空洞318が設けられている。

#### 【0121】

図9(D)の工程まで終了したら、後は実施の形態3と同様に、転置された半導体膜317の表面を平坦化し、パターニングすることで、島状の半導体膜を形成する。半導体膜317のパターニング後においても、島状の半導体膜とベース基板314の間には、開口部313、315によって形成される空洞318が維持される。

#### 【0122】

上記工程を経て形成された島状の半導体膜を用い、本発明はトランジスタ等の各種半導体素子を形成することが出来る。

#### 【0123】

本発明の作製方法では、開口部313または開口部315をエッティングで形成しているので、所望の深さ及び形状を有する空洞318を、簡単な手順で制御良く形成することが出

10

20

30

40

50

来る。

【0124】

なお本実施の形態では、欠陥層312の形成により半導体膜317をボンド基板310から剥離するスマートカット法を用いる場合について示すが、ELTRAN(Epitaxial Layer Transfer)、誘電体分離法、PACE(Plasma Assisted Chemical Etching)法などの、他の貼り合わせ法を用いて半導体膜317をベース基板314に貼り合わせるようにも良い。

【0125】

また島状の半導体膜を用いて作製されるトランジスタは、島状の半導体膜とベース基板314の間に空洞318を有しており、さらに半導体膜317と空洞318とが接している。よって、例えば酸化珪素などの無機絶縁膜に比べて比誘電率の低い空気、窒素、不活性ガスなどで空洞318を満たしておくことで、トランジスタの寄生容量または接合容量を低減することが出来る。上記気体は、温度変化に伴う体積膨張を抑えるために、水分の含有率を低減させておくのが望ましい。

10

【0126】

なお、実際のところ島状の半導体膜の、空洞318と接する部分には、自然酸化膜が形成される場合がある。しかし特許文献2に記載されている絶縁膜は数 $\mu\text{m}$ から数百 $\mu\text{m}$ の膜厚を有していることが前提となっており、自然酸化膜は、上記の絶縁膜に比べてその膜厚は数nm程度と飛躍的に薄い。よって本発明は、島状の半導体膜の空洞に接する部分に上記膜厚を有する絶縁膜を形成した場合に比べて、トランジスタの寄生容量または接合容量を低減する、或いはセルフヒーティングを抑えることが出来ると言える。

20

【0127】

なお本実施の形態では、空洞318を気体で満たす場合について示したが、本発明はこの構成に限定されない。例えば空洞318を、酸化珪素などの無機絶縁膜よりも比誘電率の低い材料、例えば内部に多数の気孔を有する多孔質絶縁膜(ポーラス材料)などで満たすようにしても良い。

【0128】

また本実施の形態では、半導体膜317と接するように絶縁膜311を先に形成してから、絶縁膜311と、ベース基板314上に形成された絶縁膜316とを接合させている。よって、半導体膜317と絶縁膜311の界面における界面準位密度を、半導体膜317と絶縁膜311とを接合させた場合に比べて、均一にすることができる。従って、半導体膜317をパターニングすることで形成される島状の半導体膜を用いたトランジスタは、閾値電圧などの特性のばらつきをより抑えることができる。

30

【0129】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【0130】

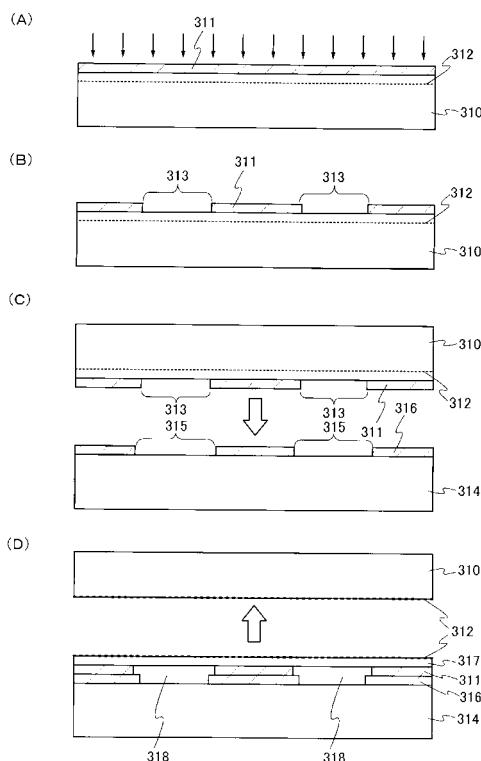

(実施の形態6)

本実施の形態では、実施の形態3に示す作製方法を用いて形成された半導体膜で、トランジスタを作製する方法の一例について説明する。なお、実施の形態4または実施の形態5に示す作製方法を用いて形成された半導体膜でも、本実施の形態に示す作製方法でトランジスタを作製することは可能である。

40

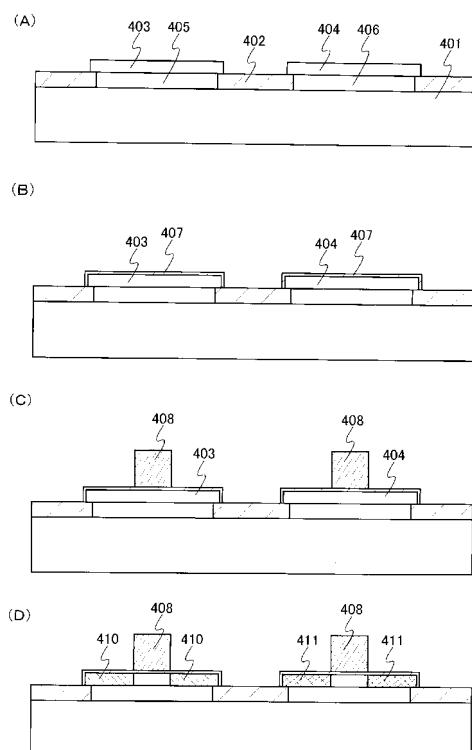

【0131】

まず図10(A)に示すように、開口部を有する絶縁膜402を、ベース基板401との間に有する島状の半導体膜403、島状の半導体膜404を形成する。実施の形態3に示す作製方法を用いる場合、絶縁膜402と島状の半導体膜403及び島状の半導体膜404とが接合することで、ベース基板401に島状の半導体膜403及び島状の半導体膜404が貼り合わされている。そして絶縁膜402が有する開口部により、ベース基板401と島状の半導体膜403の間に空洞405が、ベース基板401と島状の半導体膜404の間に空洞406がそれぞれ形成されている。

【0132】

50

島状の半導体膜403、404には、閾値電圧を制御するために不純物が添加されていても良い。例えば、p型不純物としてボロンを添加する場合、 $5 \times 10^{17} \text{ cm}^{-3}$ 以上 $1 \times 10^{18} \text{ cm}^{-3}$ 以下の濃度で添加すれば良い。閾値電圧を制御するための不純物の添加は、ベース基板401に半導体膜を転置する前に行っても良いし、転置後に行っても良い。

#### 【0133】

また島状の半導体膜403、404を形成した後、ゲート絶縁膜407を形成する前に水素化処理を行っても良い。水素化処理は、例えば、水素雰囲気中において350、2時間程度行う。

#### 【0134】

次に図10(B)に示すように、島状の半導体膜403、404を覆うように、ゲート絶縁膜407を形成する。ゲート絶縁膜407は、高密度プラズマ処理を行うことにより島状の半導体膜403、404の表面を酸化または窒化することで形成することができる。高密度プラズマ処理は、例えばHe、Ar、Kr、Xeなどの希ガスと酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスとを用いて行う。この場合プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、半導体膜の表面を酸化または窒化することにより、1~20nm、望ましくは5~10nmの絶縁膜が半導体膜に接するように形成される。この5~10nmの絶縁膜をゲート絶縁膜407として用いる。

10

#### 【0135】

上述した高密度プラズマ処理による半導体膜の酸化または窒化は固相反応で進むため、ゲート絶縁膜407と島状の半導体膜403、404の界面準位密度をきわめて低くすることができます。また高密度プラズマ処理により半導体膜を直接酸化または窒化することで、形成される絶縁膜の厚さのばらつきを抑えることが出来る。また半導体膜が結晶性を有する場合、高密度プラズマ処理を用いて半導体膜の表面を固相反応で酸化させることにより、結晶粒界においてのみ酸化が速く進んでしまうのを抑え、均一性が良く、界面準位密度の低いゲート絶縁膜を形成することができる。高密度プラズマ処理により形成された絶縁膜を、ゲート絶縁膜の一部または全部に含んで形成されるトランジスタは、特性のばらつきを抑えることができる。

20

#### 【0136】

あるいは、プラズマCVD法またはスパッタリング法などを用い、酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウムまたは酸化タンタルを含む膜を、単層で、または積層させることで、ゲート絶縁膜407を形成しても良い。

30

#### 【0137】

次に図10(C)に示すように、ゲート絶縁膜407上に導電膜を形成した後、該導電膜を所定の形状に加工(パターニング)することで、島状の半導体膜403、404の上方に電極408を形成する。導電膜の形成にはCVD法、スパッタリング法等を用いることができる。導電膜は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等を用いることが出来る。また上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。または、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶珪素などの半導体を用いて形成しても良い。

40

#### 【0138】

2つの導電膜の組み合わせとして、1層目に窒化タンタルまたはタンタル(Ta)を、2層目にタングステン(W)を用いることが出来る。上記例の他に、窒化タングステンとタングステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また

50

、2層目の導電膜の組み合わせとして、例えば、n型を付与する不純物がドーピングされた珪素とNiSi（ニッケルシリサイド）、n型を付与する不純物がドーピングされたSiとWSix等も用いることが出来る。

#### 【0139】

また、本実施の形態では電極408を単層の導電膜で形成しているが、本実施の形態はこの構成に限定されない。電極408は積層された複数の導電膜で形成されていても良い。3つ以上の導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

#### 【0140】

なお電極408を形成する際に用いるマスクとして、レジストの代わりに酸化珪素、酸化窒化珪素等をマスクとして用いてもよい。この場合、パターニングして酸化珪素、酸化窒化珪素等のマスクを形成する工程が加わるが、エッチング時におけるマスクの膜減りがレジストよりも少ないため、所望の幅を有する電極408を形成することができる。またマスクを用いずに、液滴吐出法を用いて選択的に電極408を形成しても良い。

10

#### 【0141】

なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出または噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

#### 【0142】

また電極408は、導電膜を形成後、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用い、エッチング条件（コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等）を適宜調節することにより、所望のテーパー形状を有するようにエッチングすることができる。また、テーパー形状は、マスクの形状によっても角度等を制御することができる。なお、エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などの塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などのフッ素系ガス又は酸素を適宜用いることができる。

20

#### 【0143】

ゲート絶縁膜407に高誘電率物質（high-k材料）を用いる場合には、電極408を多結晶シリコン、シリサイド、金属若しくは金属窒化物で形成する。特に高誘電率物質を用いる場合、金属若しくは金属窒化物で電極408を形成することが最も望ましい。例えば、ゲート絶縁膜407と接する導電膜を金属窒化物材料で形成し、その上の導電膜を金属材料で形成する。この組み合わせを用いることによって、ゲート絶縁膜407が薄膜化した場合でも電極408に空乏層が広がってしまうことを防止でき、微細化した場合にもトランジスタの駆動能力を損なうことを防止できる。

30

#### 【0144】

次に図10(D)に示すように、電極408をマスクとして一導電型を付与する不純物元素を半導体膜403、404に添加する。本実施の形態では、半導体膜404にp型を付与する不純物元素（例えばボロン）を、半導体膜403にn型を付与する不純物元素（例えばリンまたはヒ素）を添加する。なお、p型を付与する不純物元素を半導体膜404に添加する際、n型の不純物が添加される半導体膜403はマスク等で覆い、p型を付与する不純物元素の添加が選択的に行われるようになる。また、n型を付与する不純物元素を半導体膜403に添加する際、p型の不純物が添加される半導体膜404はマスク等で覆い、n型を付与する不純物元素の添加が選択的に行われるようになる。或いは、先に半導体膜403及び半導体膜404にp型もしくはn型を付与する不純物元素を添加した後、一方の半導体膜のみに選択的により高い濃度でp型もしくはn型を付与する不純物元素のいずれか一方を添加するようにしても良い。上記不純物の添加により、半導体膜403に不純物領域410、半導体膜404に不純物領域411が形成される。

40

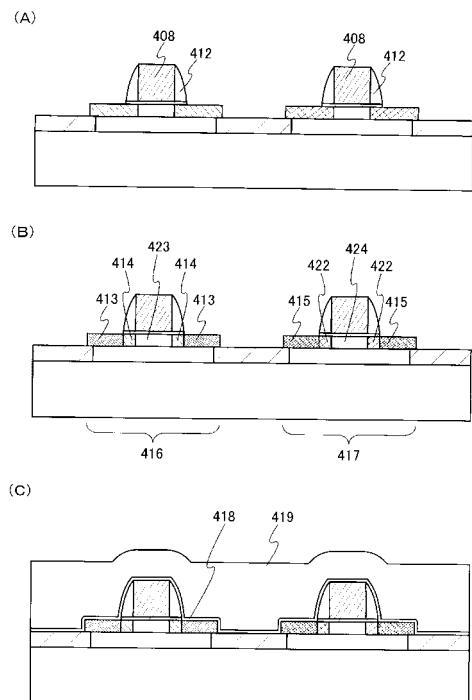

#### 【0145】

次に、図11(A)に示すように、電極408の側面にサイドウォール412を形成する。サイドウォール412は、例えば、ゲート絶縁膜407及び電極408を覆うように新

50

たに絶縁膜を形成し、垂直方向を主体とした異方性エッティングにより、新たに形成された該絶縁膜を部分的にエッティングすることで、形成することが出来る。上記異方性エッティングにより、新たに形成された絶縁膜が部分的にエッティングされて、電極 408 の側面にサイドウォール 412 が形成される。なお上記異方性エッティングにより、ゲート絶縁膜 407 も部分的にエッティングしても良い。サイドウォール 412 を形成するための絶縁膜は、プラズマ CVD 法やスパッタリング法等により、珪素膜、酸化珪素膜、酸化窒化珪素膜または窒化酸化珪素膜や、有機樹脂などの有機材料を含む膜を、単層または積層して形成することができる。本実施の形態では、膜厚 100 nm の酸化珪素膜をプラズマ CVD 法によって形成する。またエッティングガスとしては、CHF<sub>3</sub> と He の混合ガスを用いることができる。なお、サイドウォール 412 を形成する工程は、これらに限定されるものではない。

10

#### 【0146】

次に図 11 (B) に示すように、電極 408 及びサイドウォール 412 をマスクとして、半導体膜 403、404 に一導電型を付与する不純物元素を添加する。なお、半導体膜 403、404 には、それぞれ先の工程で添加した不純物元素と同じ導電型の不純物元素をより高い濃度で添加する。なお、p 型を付与する不純物元素を半導体膜 404 に添加する際、n 型の不純物が添加される半導体膜 403 はマスク等で覆い、p 型を付与する不純物元素の添加が選択的に行われるようとする。また、n 型を付与する不純物元素を半導体膜 403 に添加する際、p 型の不純物が添加される半導体膜 404 はマスク等で覆い、n 型を付与する不純物元素の添加が選択的に行われるようとする。

20

#### 【0147】

上記不純物元素の添加により、半導体膜 403 に、一対の高濃度不純物領域 413 と、一対の低濃度不純物領域 414 と、チャネル形成領域 423 とが形成される。高濃度不純物領域 413 はソース又はドレインとして機能し、低濃度不純物領域 414 は LDD (Lightly Doped Drain) 領域として機能する。また上記不純物元素の添加により、半導体膜 404 に、一対の高濃度不純物領域 415 と、一対の低濃度不純物領域 422 と、チャネル形成領域 424 とが形成される。

#### 【0148】

なお、半導体膜 404 上に形成されたサイドウォール 412 と、半導体膜 403 上に形成されたサイドウォール 412 は、チャネルが移動する方向における幅が同じになるよう形成しても良いが、該幅が異なるように形成しても良い。p 型トランジスタとなる半導体膜 404 上のサイドウォール 412 の幅は、n 型トランジスタとなる半導体膜 403 上のサイドウォール 412 の幅よりも長くすると良い。なぜならば、p 型トランジスタにおいてソース及びドレインを形成するために注入されるボロンは拡散しやすく、短チャネル効果を誘起しやすいためである。p 型トランジスタにおいて、サイドウォール 412 の幅をより長くすることで、ソース及びドレインに高濃度のボロンを添加することが可能となり、ソース及びドレインを低抵抗化することができる。

30

#### 【0149】

次に、ソース及びドレインをさらに低抵抗化するために、半導体膜 403、404 をシリサイド化することで、シリサイド層を形成しても良い。シリサイド化は、半導体膜に金属を接触させ、加熱処理、GRTA 法、LRTA 法等により、半導体膜中の珪素と金属とを反応させて行う。シリサイド層としては、コバルトシリサイド若しくはニッケルシリサイドを用いれば良い。半導体膜 403、404 の厚さが薄い場合には、この領域の半導体膜 403、404 の底部までシリサイド反応を進めてフルシリサイド化しても良い。シリサイド化に用いる金属の材料として、チタン (Ti)、ニッケル (Ni)、タンゲステン (W)、モリブデン (Mo)、コバルト (Co)、ジルコニウム (Zr)、ハフニウム (Hf)、タンタル (Ta)、バナジウム (V)、ネオジム (Nb)、クロム (Cr)、白金 (Pt)、パラジウム (Pd) 等を用いることができる。また、レーザ照射やランプなどの光照射によってシリサイドを形成しても良い。

40

#### 【0150】

50

上述した一連の工程により、nチャネル型トランジスタ416と、pチャネル型トランジスタ417とが形成される。

#### 【0151】

次に図11(C)に示すように、トランジスタ416、417を保護するための絶縁膜418を形成する。絶縁膜418は必ずしも設ける必要はないが、絶縁膜418を形成することで、アルカリ金属やアルカリ土類金属などの不純物がトランジスタ416、417へ侵入するのを防ぐことが出来る。具体的に絶縁膜418として、窒化珪素、窒化酸化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素などを用いるのが望ましい。本実施の形態では、膜厚600nm程度の酸化窒化珪素膜を、絶縁膜418として用いる。この場合、上記水素化の工程は、該酸化窒化珪素膜形成後に行っても良い。

10

#### 【0152】

次に、トランジスタ416、417を覆うように、絶縁膜418上に絶縁膜419を形成する。絶縁膜419は、ポリイミド、アクリル、ポリイミドアミド、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low-k材料)、シロキサン系樹脂、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、PSG(リンシリケートガラス)、BPSG(リンボロンシリケートガラス)、アルミナ等を用いることができる。シロキサン系樹脂は、置換基に水素の他、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有していても良い。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁膜419を形成しても良い。絶縁膜419は、その表面をCMP法または液体ジェット研磨などにより平坦化させてても良い。

20

#### 【0153】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は、置換基に水素の他、フッ素、アルキル基、または芳香族炭化水素のうち、少なくとも1種を有していても良い。

#### 【0154】

絶縁膜419の形成には、その材料に応じて、CVD法、スパッタ法、SOG法、スピニコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

30

#### 【0155】

次に図12に示すように、島状の半導体膜403、404がそれぞれ一部露出するように絶縁膜418及び絶縁膜419にコンタクトホールを形成する。そして、該コンタクトホールを介して島状の半導体膜403、404に接する導電膜420、421を形成する。コンタクトホール開口時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。

#### 【0156】

導電膜420、421は、CVD法やスパッタリング法等により形成することができる。具体的に導電膜420、421として、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、珪素(Si)等を用いることができる。また上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。導電膜420、421は、上記金属が用いられた膜を単層または複数積層させて形成することができる。

40

#### 【0157】

アルミニウムを主成分とする合金の例として、アルミニウムを主成分としニッケルを含むものが挙げられる。また、アルミニウムを主成分とし、ニッケルと、炭素または珪素の一方または両方とを含むものも例として挙げることが出来る。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜420、421を形成する材料として最適である。特にアルミニウムシリコン(Al-Si)膜は、導電膜420、421をパ

50

ターニングで形成するとき、レジストバークにおけるヒロックの発生をアルミニウム膜に比べて防止することができる。また、珪素(Si)の代わりに、アルミニウム膜に0.5重量%程度のCuを混入させても良い。

#### 【0158】

導電膜420、421は、例えば、バリア膜とアルミニウムシリコン膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデンまたはモリブデンの窒化物を用いて形成された膜である。アルミニウムシリコン膜を間に挟むようにバリア膜を形成すると、アルミニウムやアルミニウムシリコンのヒロックの発生をより防止することができる。また、還元性の高い元素であるチタンを用いてバリア膜を形成すると、島状の半導体膜403、404上に薄い酸化膜ができていたとしても、バリア膜に含まれるチタンがこの酸化膜を還元し、導電膜420、421と島状の半導体膜403、404が良好なコンタクトをとることができる。またバリア膜を複数積層するようにして用いても良い。その場合、例えば、導電膜420、421を下層からチタン、窒化チタン、アルミニウムシリコン、チタン、窒化チタンの5層構造とすることが出来る。10

#### 【0159】

なお、導電膜420はnチャネル型トランジスタ416の高濃度不純物領域413に接続されている。導電膜421はpチャネル型トランジスタ417の高濃度不純物領域415に接続されている。20

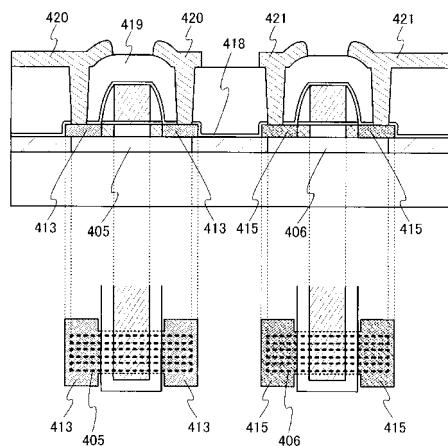

#### 【0160】

図12には、nチャネル型トランジスタ416及びpチャネル型トランジスタ417の上面図が示されている。本実施の形態では、複数の各空洞405が、一対の不純物領域413及びチャネル形成領域423と重なっている。また複数の各空洞406が、一対の不純物領域415及びチャネル形成領域424と重なっている。しかし本発明はこの構成に限定されない。空洞405及び空洞406の数及びそのレイアウトは、本実施の形態で示した構成に限定されない。20

#### 【0161】

また本実施の形態では、nチャネル型トランジスタ416とpチャネル型トランジスタ417が、それぞれゲートとして機能する電極408を1つずつ有する場合を例示しているが、本発明はこの構成に限定されない。本発明の半導体装置が有するトランジスタは、ゲートとして機能する電極を複数有し、なおかつ該複数の電極が電気的に接続されているマルチゲート構造を有していても良い。30

#### 【0162】

また本発明の半導体装置が有するトランジスタは、ゲートプレナー構造を有していても良い。

#### 【0163】

本発明の作製方法を用いた半導体装置では、ベース基板に島状の半導体膜を形成するため、素子分離を行う必要がないので、工程を簡略化できる。また本発明の作製方法では、絶縁膜402をエッチングすることで空洞405、空洞406を形成しているので、所望の深さ及び形状を有する空洞405、空洞406を、簡単な手順で制御良く形成することが出来る。40

#### 【0164】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【実施例1】

#### 【0165】

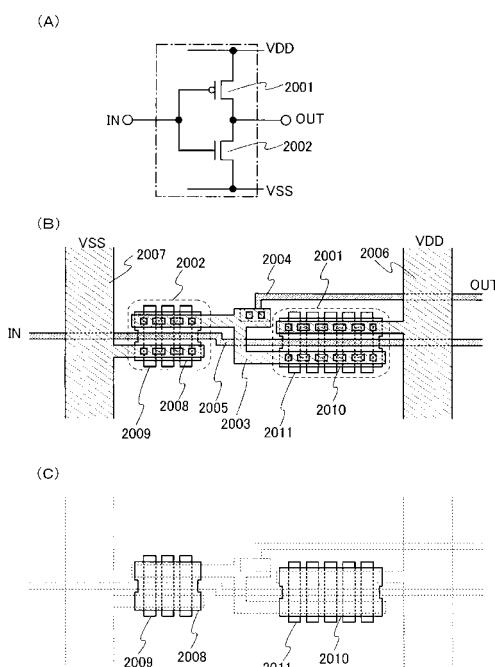

本実施例では、本発明のSON構造を有するトランジスタを用いた各種回路の具体的な構成について、インバータを例に挙げて説明する。インバータの回路図を図13(A)に、また図13(A)に示すインバータの上面図を図13(B)に、一例として示す。

#### 【0166】

図13(A)に示すインバータは、pチャネル型のトランジスタ2001と、nチャネル

50

型のトランジスタ2002とを有する。トランジスタ2001とトランジスタ2002とは直列に接続されている。具体的には、トランジスタ2001のドレインと、トランジスタ2002のドレインが接続されている。そして、トランジスタ2001のドレイン及びトランジスタ2002のドレインの電位は、出力端子OUTに与えられる。

#### 【0167】

またトランジスタ2001のゲートとトランジスタ2002のゲートは接続されている。そして、入力端子INに入力された信号の電位は、トランジスタ2001のゲート及びトランジスタ2002のゲートに与えられる。トランジスタ2001のソースにはハイレベルの電圧VDDが与えられ、トランジスタ2002のソースにはローレベルの電圧VSSが与えられる。

10

#### 【0168】

図13(B)に示すインバータでは、トランジスタ2001のドレインと、トランジスタ2002のドレインは、配線2003を介して電気的に接続されている。そして配線2003は配線2004に接続されている。よって、トランジスタ2001のドレイン及びトランジスタ2002のドレインの電位は、配線2003及び配線2004を介して、出力端子OUTの電位として後段の回路に与えられる。

#### 【0169】

また図13(B)に示すインバータでは、配線2005の一部がトランジスタ2001のゲート及びトランジスタ2002のゲートとして機能している。そして配線2005に与えられた電位が、入力端子INの電位としてトランジスタ2001のゲート及びトランジスタ2002のゲートに与えられる。そしてトランジスタ2001のソースには、配線2006を介して電圧VDDが与えられ、トランジスタ2002のソースには、配線2007を介して電圧VSSが与えられている。

20

#### 【0170】

トランジスタ2002が有する半導体膜2008は、基板との間に空洞2009が設けられている。またトランジスタ2001が有する半導体膜2010は、基板との間に空洞2011が設けられている。半導体膜2008と空洞2009との位置関係、半導体膜2010と空洞2011との位置関係を明確にするため、図13(B)に示すインバータのうち、半導体膜2008、空洞2009、半導体膜2010、空洞2011のみを図13(C)に示す。

30

#### 【0171】

図13(C)に示すように、空洞2009は、半導体膜2008と基板との間に複数形成されている。そして複数の空洞2009は、トランジスタ2001のソース、チャネル形成領域、ドレインと重なる領域にそれぞれ形成されている。また空洞2011も、半導体膜2010と基板との間に複数形成されている。そして複数の空洞2011は、トランジスタ2002のソース、チャネル形成領域、ドレインと重なる領域にそれぞれ形成されている。

#### 【0172】

なお図13(B)及び図13(C)では、半導体膜2008、半導体膜2010とそれ重なるような空洞2009、空洞2011が複数設けられている例を示しているが、本発明はこの構成に限定されない。半導体膜の下部に設けられる空洞は単数であっても良い。空洞の形成される面積が同じであるならば、空洞が複数の方が単数の場合よりもより物理的強度の強いトランジスタを形成することが出来る。また空洞が単数の場合、半導体膜の下部により広い面積で空洞をレイアウトすることが可能になるので、空洞が複数の場合よりもより接合容量を低減させることが出来る。

40

#### 【0173】

また図13(B)及び図13(C)では、空洞2009、空洞2011がトランジスタ2001、トランジスタ2002のソース、チャネル形成領域、ドレインと重なる領域に形成されている例を示しているが、本発明はこの構成に限定されない。ソースとドレインのうち、いずれか一方とのみ空洞が重なるように形成されていても良い。この場合、空洞は

50

チャネル形成領域と重なっていても良いし、重なっていないとも良い。空洞が少なくともソースまたはドレインと重なっている場合、チャネル形成領域とのみ重なっている空洞を形成する場合と比べて、より接合容量を低減させることが出来る。また、少なくともチャネル形成領域と重なっている空洞を形成する場合、ソースまたはドレインとのみ重なっている空洞を形成する場合に比べて、よりセルフヒーティングを抑えることが出来る。

#### 【0174】

本実施例は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【実施例2】

#### 【0175】

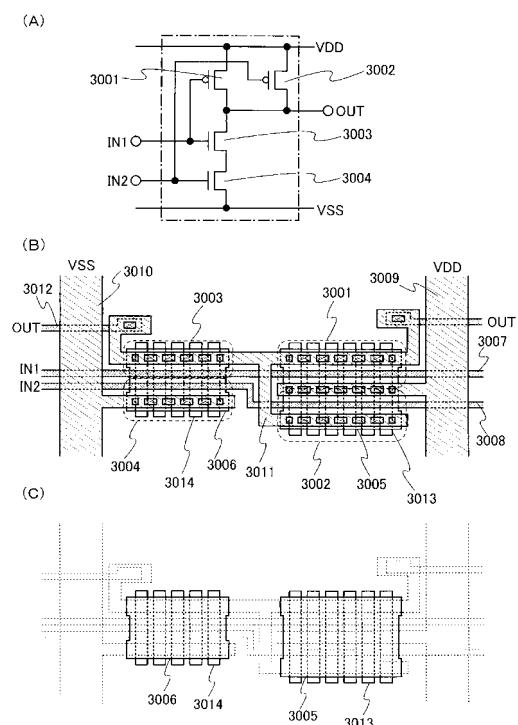

本実施例では、本発明のSON構造を有するトランジスタを用いた各種回路の具体的な構成について、NANDを例に挙げて説明する。NANDの回路図を図14(A)に、また図14(A)に示すNANDの上面図を図14(B)に、一例として示す。

10

#### 【0176】

図14(A)に示すNANDは、pチャネル型のトランジスタ3001と、pチャネル型のトランジスタ3002と、nチャネル型のトランジスタ3003と、nチャネル型のトランジスタ3004とを有する。トランジスタ3001と、トランジスタ3003と、トランジスタ3004とは、順に直列に接続されている。またトランジスタ3001と、トランジスタ3002とは並列に接続されている。

#### 【0177】

具体的にトランジスタ3001のソースとドレインは、一方にはハイレベルの電圧VDDが与えられ、他方は出力端子OUTに接続されている。トランジスタ3002のソースとドレインは、一方にはハイレベルの電圧VDDが与えられ、他方は出力端子OUTに接続されている。トランジスタ3004のソースとドレインは、一方にはローレベルの電圧VSSが与えられている。トランジスタ3003のソースとドレインは、一方は出力端子OUTに接続されている。そして、トランジスタ3003のソースとドレインの他方と、トランジスタ3004のソースとドレインの他方とが接続されている。トランジスタ3001のゲートと、トランジスタ3003のゲートには、入力端子IN1の電位が与えられる。またトランジスタ3002のゲートと、トランジスタ3004のゲートには、入力端子IN2の電位が与えられる。

20

#### 【0178】

図14(B)に示すNANDでは、直列に接続されているトランジスタ3001とトランジスタ3002とが、半導体膜3005を共有している。また直列に接続されているトランジスタ3003とトランジスタ3004とが、半導体膜3006を共有している。また配線3007の一部はトランジスタ3001のゲート及びトランジスタ3003のゲートとして機能している。そして配線3007に与えられた電位が、入力端子IN1の電位としてトランジスタ3001のゲート及びトランジスタ3003のゲートに与えられる。配線3008の一部はトランジスタ3002のゲート及びトランジスタ3004のゲートとして機能している。そして配線3008に与えられた電位が、入力端子IN2の電位としてトランジスタ3002のゲート及びトランジスタ3004のゲートに与えられる。

30

#### 【0179】

ハイレベルの電圧VDDは、配線3009を介してトランジスタ3001のソースとドレインの一方、及びトランジスタ3002のソースとドレインの一方に与えられる。またローレベルの電圧VSSは、配線3010を介してトランジスタ3004のソースとドレインの一方に与えられる。トランジスタ3001のソースとドレインの他方、トランジスタ3002のソースとドレインの他方、及びトランジスタ3003のソースとドレインの一方は、その電位が配線3011及び配線3012を介して出力端子OUTの電位として後段の回路に与えられる。

40

#### 【0180】

半導体膜3005は、基板との間に空洞3013が設けられている。また半導体膜3006は、基板との間に空洞3014が設けられている。半導体膜3005と空洞3013と

50

の位置関係、半導体膜 3006 と空洞 3014との位置関係を明確にするため、図 14 (B) に示すNAND のうち、半導体膜 3005、空洞 3013、半導体膜 3006、空洞 3014のみを図 14 (C) に示す。

#### 【0181】

図 14 (C) に示すように、空洞 3013 は、半導体膜 3005 と基板との間に複数形成されている。そして複数の空洞 3013 は、トランジスタ 3001 のソース、チャネル形成領域、ドレイン及びトランジスタ 3002 のソース、チャネル形成領域、ドレインと重なる領域に、それぞれ形成されている。また空洞 3014 も、半導体膜 3006 と基板との間に複数形成されている。そして複数の空洞 3014 は、トランジスタ 3003 のソース、チャネル形成領域、ドレイン及びトランジスタ 3004 のソース、チャネル形成領域、ドレインと重なる領域に、それぞれ形成されている。10

#### 【0182】

なお図 14 (B) 及び図 14 (C) では、半導体膜 3005、半導体膜 3006 とそれぞれ重なるような空洞 3013、空洞 3014 が複数設けられている例を示しているが、本発明はこの構成に限定されない。半導体膜の下部に設けられる空洞は単数であっても良い。空洞の形成される面積が同じであるならば、空洞が複数の方が単数の場合よりもより物理的強度の強いトランジスタを形成することが出来る。また空洞が単数の場合、半導体膜の下部により広い面積で空洞をレイアウトすることが可能になるので、空洞が複数の場合よりもより接合容量を低減させることが出来る。20

#### 【0183】

また図 14 (B) 及び図 14 (C) では、空洞 3013、空洞 3014 がトランジスタ 3001、トランジスタ 3002、トランジスタ 3003、トランジスタ 3004 のソース、チャネル形成領域、ドレインと重なる領域に形成されている例を示しているが、本発明はこの構成に限定されない。ソースとドレインのうち、いずれか一方とのみ空洞が重なるように形成されていても良い。この場合、空洞はチャネル形成領域と重なっていても良いし、重なっていないとも良い。空洞が少なくともソースまたはドレインと重なっている場合、チャネル形成領域とのみ重なっている空洞を形成する場合と比べて、より接合容量を低減させることが出来る。また、少なくともチャネル形成領域と重なっている空洞を形成する場合、ソースまたはドレインとのみ重なっている空洞に比べて、よりセルフヒーティングを抑えることが出来る。30

#### 【0184】

さらに図 14 (B) 及び図 14 (C) では、トランジスタ 3001 とトランジスタ 3002 とが、半導体膜 3005 及び空洞 3013 を共有している例について示しているが、本発明はこの構成に限定されない。複数のトランジスタで半導体膜及び空洞を共有する場合、基板における複数のトランジスタの専有面積をより小さく抑えつつも、接合容量のより小さいトランジスタを形成することが可能になる。

#### 【0185】

本実施例は、上記実施の形態または実施例と適宜組み合わせて実施することが可能である。40

#### 【実施例 3】

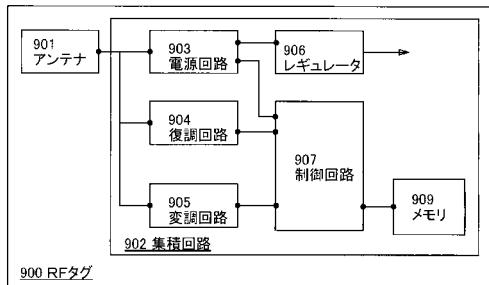

#### 【0186】

本実施例では、本発明の半導体装置の一つであるRFタグの構成について説明する。図 15 は本発明のRFタグの一形態を示すブロック図である。図 15においてRFタグ 900 は、アンテナ 901 と、集積回路 902 とを有している。集積回路 902 は、電源回路 903、復調回路 904、変調回路 905、レギュレータ 906、制御回路 907、メモリ 909 を有している。本発明の整流回路は、電源回路 903、復調回路 904 において用いることができる。

#### 【0187】

質問器から電波が送られてくると、アンテナ 901 において該電波が交流電圧に変換される。電源回路 903 では、アンテナ 901 からの交流電圧を整流し、電源用の電圧を生成50

する。電源回路 903において生成された電源用の電圧は、制御回路 907とレギュレータ 906に与えられる。レギュレータ 906は、電源回路 903からの電源用の電圧を安定化させるか、またはその高さを調整した後、集積回路 902内の復調回路 904、変調回路 905、制御回路 907またはメモリ 909などの各種回路に供給する。

#### 【0188】

復調回路 904は、アンテナ 901が受信した交流信号を復調して、後段の制御回路 907に出力する。制御回路 907は復調回路 904から入力された信号に従って演算処理を行い、別途信号を生成する。上記演算処理を行う際に、メモリ 909は一次キャッシュメモリまたは二次キャッシュメモリとして用いることが出来る。また制御回路 907は、復調回路 904から入力された信号を解析し、質問器から送られてきた命令の内容に従って、メモリ 909内の情報の出力、またはメモリ 909内における命令の内容の保存を行う。制御回路 907から出力される信号は符号化され、変調回路 905に送られる。変調回路 905は該信号に従ってアンテナ 901が受信している電波を変調する。アンテナ 901において変調された電波は質問器で受け取られる。そしてRFタグ 900から出力された情報を知ることができる。10

#### 【0189】

このようにRFタグ 900と質問器との通信は、キャリア（搬送波）として用いる電波を変調することで行われる。キャリアは、125kHz、13.56MHz、950MHzなど規格により様々である。また変調の方式も規格により振幅変調、周波数変調、位相変調など様々な方式があるが、規格に即した変調方式であればどの変調方式を用いても良い。20

#### 【0190】

信号の伝送方式は、キャリアの波長によって電磁結合方式、電磁誘導方式、マイクロ波方式など様々な種類に分類することが出来る。

#### 【0191】

メモリ 909は不揮発性メモリであっても揮発性メモリであってもどちらでも良い。メモリ 909として、例えばSRAM、DRAM、フラッシュメモリ、EEPROM、FeRAMなどを用いることが出来る。

#### 【0192】

本実施例では、アンテナ 901を有するRFタグ 900の構成について説明しているが、本発明のRFタグは必ずしもアンテナを有していないとも良い。また図15に示したRFタグに、発振回路または二次電池を設けても良い。30

#### 【0193】

また図15では、アンテナを1つだけ有するRFタグの構成について説明したが、本発明はこの構成に限定されない。電力を受信するためのアンテナと、信号を受信するためのアンテナとの、2つのアンテナを有していても良い。アンテナが1つだと、例えば950MHzの電波で電力の供給と信号の伝送を両方行う場合、遠方まで大電力が伝送され、他の無線機器の受信妨害を起こす可能性がある。そのため、電力の供給は電波の周波数を下げて近距離にて行う方が望ましいが、この場合通信距離は必然的に短くなってしまう。しかしアンテナが2つあると、電力を供給する電波の周波数と、信号を送るための電波の周波数とを使い分けることができる。例えば電力を送る際は電波の周波数を13.56MHzとして電磁誘導方式を用い、信号を送る際は電波の周波数を950MHzとして電波方式を用いることができる。このように機能合わせてアンテナを使い分けることによって、電力の供給は近距離のみの通信とし、信号の伝送は遠距離も可能なものとすることができます。40

#### 【0194】

本発明の半導体装置の一つであるRFタグは、絶縁表面を有する基板もしくは絶縁基板上に接合された単結晶半導体層（SOI層）によって集積回路 902が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。また接合容量を抑えたトランジスタを用いることで、RFタグの高速駆動が可能になる。さらに半導体膜に接す50

る空洞を有することで、トランジスタの駆動時に発生する熱を効率的に放散することができ、セルフヒーティングによる誤動作、素子の破壊などを防ぐことができる。

#### 【0195】

本実施例は、上記実施の形態または実施例と適宜組み合わせて実施することが可能である。

#### 【実施例4】

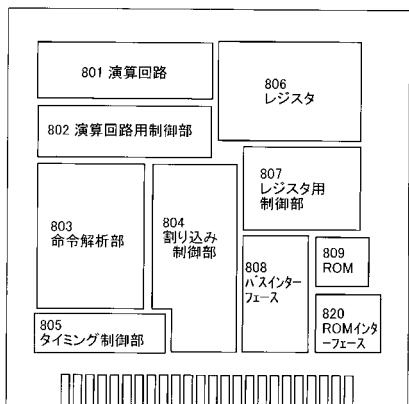

#### 【0196】

本実施例では、本発明の半導体装置の一つであるCPU (central processing unit) の構成について説明する。

#### 【0197】

図16に、本実施例のCPUの構成をブロック図で示す。図16に示すCPUは、基板800上に、演算回路(ALU: Arithmetic logic unit)801、演算回路用制御部(ALU Controller)802、命令解析部(Instruction Decoder)803、割り込み制御部(Interrupt Controller)804、タイミング制御部(Timing Controller)805、レジスタ(Register)806、レジスタ制御部(Register Controller)807、バスインターフェース(Bus I/F)808、メモリ809、メモリ用インターフェース820を主に有している。メモリ809及びメモリ用インターフェース820は、別チップに設けても良い。勿論、図16に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

10

#### 【0198】

バスインターフェース808を介してCPUに入力された命令は、命令解析部803においてデコードされた後、演算回路用制御部802、割り込み制御部804、レジスタ制御部807、タイミング制御部805に入力される。演算回路用制御部802、割り込み制御部804、レジスタ制御部807、タイミング制御部805は、デコードされた命令にもとづき、各種制御を行なう。具体的に演算回路用制御部802は、演算回路801の動作を制御するための信号を生成する。また、割り込み制御部804は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタ制御部807は、レジスタ806のアドレスを生成し、CPUの状態に応じてレジスタ806の読み出しや書き込みを行なう。

20

#### 【0199】

またタイミング制御部805は、演算回路801、演算回路用制御部802、命令解析部803、割り込み制御部804、レジスタ制御部807の動作のタイミングを制御する信号を生成する。例えばタイミング制御部805は、基準クロック信号をもとに、内部クロック信号を生成する内部クロック生成部を備えており、内部クロック信号を上記各種回路に供給する。

30

#### 【0200】

本発明の半導体装置の一つであるCPUは、絶縁表面を有する基板もしくは絶縁基板上に接合された単結晶半導体層(SOI層)によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。また接合容量を抑えたトランジスタを用いることで、CPUの高速駆動が可能になる。さらに半導体膜に接する空洞を有することで、トランジスタの駆動時に発生する熱を効率的に放散することができ、セルフヒーティングによる誤動作、素子の破壊などを防ぐことができる。

40

#### 【0201】

また、半導体基板はガラス基板よりも熱処理によるシュリンクが小さく、基板の表面におけるうねりが小さい。よって、半導体基板をベース基板として用いる場合、マスクの合わせ精度を高くすることができるため、100nm以下の極微細パターンを形成することができる。また、半導体基板をベース基板として用いる場合、解像度の高いマスクを用いることができるため、トランジスタのチャネル長Lを短くすることができる。よって、

50

高性能、低消費電力、高集積度を実現できるため、CPUを含む各種の大規模集積回路（LSI）を作製することが可能である。

【0202】

本実施例は、上記実施の形態または実施例と適宜組み合わせて実施することが可能である。

【実施例5】

【0203】

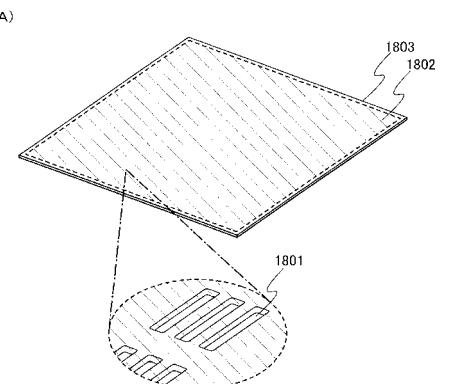

本実施例では、1枚のベース基板を用いて複数の半導体装置を形成する場合の手順について説明する。

【0204】

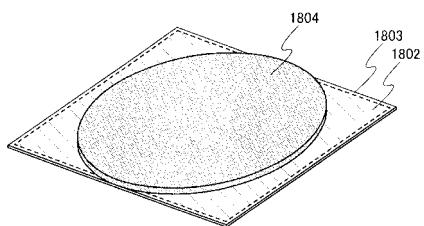

図17(A)に、開口部1801を有する絶縁膜1802が形成された、ベース基板1803の外観を示す。図17(A)では、ベース基板1803の表面を部分的に拡大した図も併せて示している。

10

【0205】

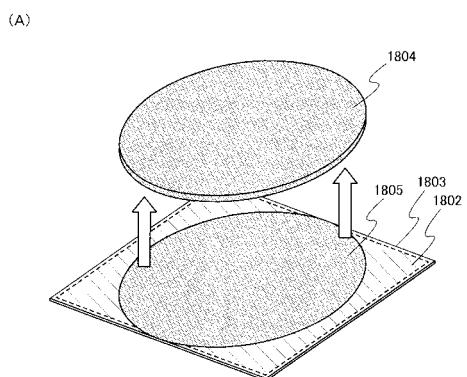

次に図17(B)に示すように、ボンド基板1804をベース基板1803に、接合により貼り合わせる。ボンド基板1804は、開口部1801を有する絶縁膜1802を間に挟むように、ベース基板1803に貼り合わせる。

【0206】

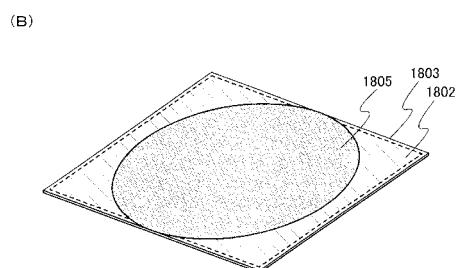

そして、図18(A)に示すようにボンド基板1804を劈開させることで、図18(B)に示すようにボンド基板1804の一部である半導体膜1805を、ベース基板1803に転置する。半導体膜1805とベース基板1803の間には、絶縁膜1802が有する開口部1801によって形成される空洞が設けられている。

20

【0207】

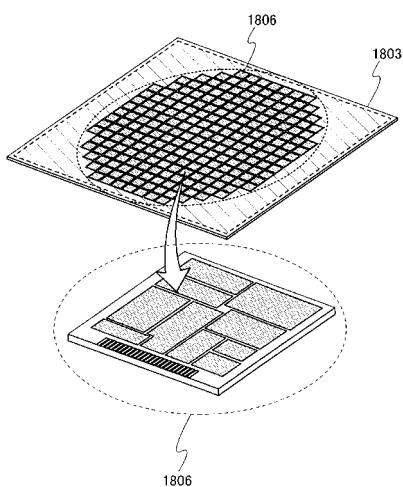

そして図19に示すように、ベース基板1803上に形成された半導体膜1805を用いて、半導体装置1806を複数形成し、ダイシングなどでベース基板1803ごと半導体装置1806どうしを切り離す。上記構成により、複数の半導体装置1806を形成することが出来る。

【0208】

なお、本実施例ではベース基板1803とボンド基板1804とを一対一で貼り合わせる場合について説明したが、本発明はこの構成に限定されない。1つのベース基板1803にボンド基板1804を複数貼り合わせるようにしても良い。ただしこの場合、各ボンド基板1804の面方位が揃うようにすることで、ベース基板1803上に形成される複数の半導体膜の結晶面方位を揃えることができ、よって半導体装置1806の特性を揃えることができる。

30

【0209】

本実施例は、上記実施の形態または実施例と適宜組み合わせて実施することが可能である。

【実施例6】

【0210】

本発明の半導体装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機または電子書籍、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）などが挙げられる。これら電子機器の具体例を図20に示す。

40

【0211】

図20(A)は携帯電話であり、本体2101、表示部2102、音声入力部2103、音声出力部2104、操作キー2105を有する。表示部2102に本発明の表示装置を用いることで、消費電力を抑えることができ、高性能で信頼性の高い携帯電話が得られる

50

。

**【0212】**

図20(B)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を有する。表示部2602に本発明の表示装置を用いることで、消費電力を抑えることができ、高性能で信頼性の高いビデオカメラが得られる。

**【0213】**

図20(C)は映像表示装置であり、筐体2401、表示部2402、スピーカー部2403等を有する。表示部2402に本発明の表示装置を用いることで、消費電力を抑えることができ、高性能で信頼性の高い映像表示装置が得られる。なお、映像表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの、映像を表示するための全ての映像表示装置が含まれる。

10

**【0214】**

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。

**【0215】**

本実施例は、上記実施の形態または上記実施例と適宜組み合わせて実施することができる。

**【図面の簡単な説明】**

20

**【0216】**

【図1】本発明の半導体装置が有するトランジスタの構成を示す断面図。

【図2】本発明の半導体装置が有するトランジスタの構成を示す上面図及び断面図。

【図3】本発明の半導体装置が有するトランジスタの構成を示す上面図及び断面図。

【図4】本発明の半導体装置が有するトランジスタの構成を示す上面図及び断面図。

【図5】本発明の半導体装置が有するトランジスタの構成を示す上面図及び断面図。

【図6】本発明の半導体装置の作製方法を示す図。

【図7】本発明の半導体装置の作製方法を示す図。

【図8】本発明の半導体装置の作製方法を示す図。

【図9】本発明の半導体装置の作製方法を示す図。

30

【図10】本発明の半導体装置の作製方法を示す図。

【図11】本発明の半導体装置の作製方法を示す図。

【図12】本発明の半導体装置の作製方法を示す図。

【図13】本発明の半導体装置が有するインバータの構成を示す図。

【図14】本発明の半導体装置が有するNANDの構成を示す図。

【図15】本発明の半導体装置の一つであるRFタグの構成を示す図。

【図16】本発明の半導体装置の一つであるCPUの構成を示す図。

【図17】本発明の半導体装置の作製方法を示す図。

【図18】本発明の半導体装置の作製方法を示す図。

【図19】本発明の半導体装置の作製方法を示す図。

40

【図20】本発明の半導体装置を用いた電子機器の図。

**【符号の説明】**

**【0217】**

100 半導体膜

101 絶縁膜

102 ベース基板

103 空洞

104 不純物領域

106 チャネル形成領域

107 ゲート絶縁膜

50

|       |          |    |

|-------|----------|----|

| 1 0 8 | 電極       |    |

| 1 1 0 | 半導体膜     |    |

| 1 1 1 | 不純物領域    |    |

| 1 1 3 | チャネル形成領域 |    |

| 1 1 4 | ゲート絶縁膜   |    |

| 1 1 5 | 電極       |    |

| 1 1 6 | ベース基板    |    |

| 1 1 7 | 絶縁膜      |    |

| 1 1 8 | 空洞       |    |

| 1 2 0 | 半導体膜     | 10 |

| 1 2 1 | 電極       |    |

| 1 2 2 | ゲート絶縁膜   |    |

| 1 2 3 | 不純物領域    |    |

| 1 2 5 | チャネル形成領域 |    |

| 1 2 6 | LDD領域    |    |

| 1 2 8 | サイドウォール  |    |

| 1 2 9 | ベース基板    |    |

| 1 3 0 | 空洞       |    |

| 1 3 1 | 絶縁膜      |    |

| 1 4 0 | 半導体膜     | 20 |

| 1 4 1 | 電極       |    |

| 1 4 2 | ゲート絶縁膜   |    |

| 1 4 3 | 不純物領域    |    |

| 1 4 4 | 不純物領域    |    |

| 1 4 5 | チャネル形成領域 |    |

| 1 4 6 | LDD領域    |    |

| 1 4 8 | サイドウォール  |    |

| 1 4 9 | ベース基板    |    |

| 1 5 0 | 空洞       |    |

| 1 5 1 | 空洞       | 30 |

| 1 5 2 | 絶縁膜      |    |

| 1 6 0 | 半導体膜     |    |

| 1 6 1 | 電極       |    |

| 1 6 2 | ゲート絶縁膜   |    |

| 1 6 3 | 不純物領域    |    |

| 1 6 5 | チャネル形成領域 |    |

| 1 6 6 | LDD領域    |    |

| 1 6 8 | サイドウォール  |    |

| 1 6 9 | ベース基板    |    |

| 1 7 1 | 絶縁膜      | 40 |

| 1 7 2 | 空洞       |    |

| 1 8 0 | 半導体膜     |    |

| 1 8 1 | 電極       |    |

| 1 8 2 | ゲート絶縁膜   |    |

| 1 8 3 | 不純物領域    |    |

| 1 8 5 | チャネル形成領域 |    |

| 1 8 6 | LDD領域    |    |

| 1 8 8 | サイドウォール  |    |

| 1 8 9 | ベース基板    |    |

| 1 9 1 | 絶縁膜      | 50 |

|       |          |    |

|-------|----------|----|

| 1 9 2 | 空洞       |    |

| 2 0 0 | ボンド基板    |    |

| 2 0 1 | 欠陥層      |    |

| 2 0 2 | ベース基板    |    |

| 2 0 3 | 絶縁膜      |    |

| 2 0 4 | 開口部      |    |

| 2 0 5 | 半導体膜     |    |

| 2 0 6 | 半導体膜     |    |

| 2 0 7 | 空洞       |    |

| 2 1 0 | トランジスタ   | 10 |

| 2 1 1 | 不純物領域    |    |

| 2 1 2 | チャネル形成領域 |    |

| 3 0 0 | ボンド基板    |    |

| 3 0 1 | 絶縁膜      |    |

| 3 0 2 | 欠陥層      |    |

| 3 0 3 | 開口部      |    |

| 3 0 4 | ベース基板    |    |

| 3 0 5 | 半導体膜     |    |

| 3 0 6 | 空洞       |    |

| 3 1 0 | ボンド基板    | 20 |

| 3 1 1 | 絶縁膜      |    |

| 3 1 2 | 欠陥層      |    |

| 3 1 3 | 開口部      |    |

| 3 1 4 | ベース基板    |    |

| 3 1 5 | 開口部      |    |

| 3 1 6 | 絶縁膜      |    |

| 3 1 7 | 半導体膜     |    |

| 3 1 8 | 空洞       |    |

| 4 0 1 | ベース基板    |    |

| 4 0 2 | 絶縁膜      | 30 |

| 4 0 3 | 半導体膜     |    |

| 4 0 4 | 半導体膜     |    |

| 4 0 5 | 空洞       |    |

| 4 0 6 | 空洞       |    |

| 4 0 7 | ゲート絶縁膜   |    |

| 4 0 8 | 電極       |    |

| 4 1 0 | 不純物領域    |    |

| 4 1 1 | 不純物領域    |    |

| 4 1 2 | サイドウォール  |    |

| 4 1 3 | 不純物領域    | 40 |

| 4 1 4 | 不純物領域    |    |

| 4 1 5 | 不純物領域    |    |

| 4 1 6 | トランジスタ   |    |

| 4 1 7 | トランジスタ   |    |

| 4 1 8 | 絶縁膜      |    |

| 4 1 9 | 絶縁膜      |    |

| 4 2 0 | 導電膜      |    |

| 4 2 1 | 導電膜      |    |

| 4 2 2 | 低濃度不純物領域 |    |

| 4 2 3 | チャネル形成領域 | 50 |

|         |              |    |

|---------|--------------|----|

| 4 2 4   | チャネル形成領域     |    |

| 8 0 0   | 基板           |    |

| 8 0 1   | 演算回路         |    |

| 8 0 2   | 演算回路用制御部     |    |

| 8 0 3   | 命令解析部        |    |

| 8 0 4   | 制御部          |    |

| 8 0 5   | タイミング制御部     |    |

| 8 0 6   | レジスタ         |    |

| 8 0 7   | レジスタ制御部      |    |

| 8 0 8   | バスインターフェース   | 10 |

| 8 0 9   | メモリ          |    |

| 8 2 0   | メモリ用インターフェース |    |

| 9 0 0   | R F タグ       |    |

| 9 0 1   | アンテナ         |    |

| 9 0 2   | 集積回路         |    |

| 9 0 3   | 電源回路         |    |

| 9 0 4   | 復調回路         |    |

| 9 0 5   | 変調回路         |    |

| 9 0 6   | レギュレータ       |    |

| 9 0 7   | 制御回路         | 20 |

| 9 0 9   | メモリ          |    |

| 1 8 0 1 | 開口部          |    |

| 1 8 0 2 | 絶縁膜          |    |

| 1 8 0 3 | ベース基板        |    |

| 1 8 0 4 | ボンド基板        |    |

| 1 8 0 5 | 半導体膜         |    |

| 1 8 0 6 | 半導体装置        |    |

| 2 0 0 1 | トランジスタ       |    |

| 2 0 0 2 | トランジスタ       |    |

| 2 0 0 3 | 配線           | 30 |

| 2 0 0 4 | 配線           |    |

| 2 0 0 5 | 配線           |    |

| 2 0 0 6 | 配線           |    |

| 2 0 0 7 | 配線           |    |

| 2 0 0 8 | 半導体膜         |    |

| 2 0 0 9 | 空洞           |    |

| 2 0 1 0 | 半導体膜         |    |

| 2 0 1 1 | 空洞           |    |

| 2 1 0 1 | 本体           |    |

| 2 1 0 2 | 表示部          | 40 |

| 2 1 0 3 | 音声入力部        |    |

| 2 1 0 4 | 音声出力部        |    |

| 2 1 0 5 | 操作キー         |    |

| 2 4 0 1 | 筐体           |    |

| 2 4 0 2 | 表示部          |    |

| 2 4 0 3 | スピーカー部       |    |

| 2 6 0 1 | 本体           |    |

| 2 6 0 2 | 表示部          |    |

| 2 6 0 3 | 筐体           |    |

| 2 6 0 4 | 外部接続ポート      | 50 |

|         |         |    |

|---------|---------|----|

| 2 6 0 5 | リモコン受信部 |    |

| 2 6 0 6 | 受像部     |    |

| 2 6 0 7 | バッテリー   |    |

| 2 6 0 8 | 音声入力部   |    |

| 2 6 0 9 | 操作キー    |    |

| 2 6 1 0 | 接眼部     |    |

| 3 0 0 1 | トランジスタ  | 10 |

| 3 0 0 2 | トランジスタ  |    |

| 3 0 0 3 | トランジスタ  |    |

| 3 0 0 4 | トランジスタ  |    |

| 3 0 0 5 | 半導体膜    |    |

| 3 0 0 6 | 半導体膜    |    |

| 3 0 0 7 | 配線      |    |

| 3 0 0 8 | 配線      |    |

| 3 0 0 9 | 配線      |    |

| 3 0 1 0 | 配線      |    |

| 3 0 1 1 | 配線      |    |

| 3 0 1 2 | 配線      |    |

| 3 0 1 3 | 空洞      |    |

| 3 0 1 4 | 空洞      | 20 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

(B)

【図18】

【図19】

## 【図 20】

---

フロントページの続き

(56)参考文献 特開平11-274500(JP,A)

特開2004-221530(JP,A)

特開2002-343977(JP,A)

特開2004-336052(JP,A)

特開2007-027232(JP,A)

特開2005-101234(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 21/336

H01L 27/12

H01L 29/786