(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4580550号

(P4580550)

(45) 発行日 平成22年11月17日(2010.11.17)

(24) 登録日 平成22年9月3日(2010.9.3)

(51) Int.Cl.

F 1

H01L 23/12 (2006.01)

H01L 23/12 501P

H01L 21/3205 (2006.01)

H01L 21/88 T

H01L 23/52 (2006.01)

請求項の数 26 (全 14 頁)

(21) 出願番号 特願2000-517447 (P2000-517447)

(86) (22) 出願日 平成10年10月19日 (1998.10.19)

(65) 公表番号 特表2001-521288 (P2001-521288A)

(43) 公表日 平成13年11月6日 (2001.11.6)

(86) 國際出願番号 PCT/US1998/022071

(87) 國際公開番号 WO1999/021226

(87) 國際公開日 平成11年4月29日 (1999.4.29)

審査請求日 平成17年9月27日 (2005.9.27)

(31) 優先権主張番号 08/954,426

(32) 優先日 平成9年10月20日 (1997.10.20)

(33) 優先権主張国 米国(US)

(73) 特許権者 505469643

フリップチップ インターナショナル エ

ルエルシー

アメリカ合衆国 アリゾナ州 85034

フェニックス イースト ユニバーシテ

イ ドライブ 3701

(74) 代理人 100147485

弁理士 杉村 薫司

(74) 代理人 100134005

弁理士 澤田 達也

(74) 代理人 100151677

弁理士 播磨 里江子

(74) 代理人 230101339

弁護士 高松 薫

最終頁に続く

(54) 【発明の名称】チップスケールパッケージ、はんだバンプ半導体ウェハ構造及び集積回路用のフリップチップパッケージの形成方法

## (57) 【特許請求の範囲】

## 【請求項1】

チップスケール(8)パッケージにして、

a. 前面(12)及び反対側の後面(16)とを有する半導体チップ(ダイ)上に形成された集積回路(10)であって、該半導体チップは、該集積回路と電気的な相互配線を形成するために、その前面に複数の導電結合パッド(18, 20)を含む、集積回路と、

b. 前記半導体チップの前面(12)上に形成されたパターン化された金属層(30)であって、該パターン化された金属層は、前記半導体チップ上に複数のはんだバンプパッド(26)及び複数の再分配トレースを提供し、前記導電結合パッドを前記複数のはんだバンプパッドに電気的に結合する金属層と、

c. 前記半導体チップの前記前面及び前記パターン化された金属層(30)を被覆して延在するポリマー層(32)であって、前記ポリマー層は、前記はんだバンプパッド上に位置する開口部を有し、

d. リフロー温度を有する複数の延性はんだボール(28)であって、該延性はんだボールの各々は、対応するはんだバンプパッドの一つに固定され、前記リフロー温度まで前記半導体チップを加熱してそれぞれのはんだバンプパッドに固定した後に略球形の形状を有し、少なくとも0.2286mmの直径を有する、延性はんだボールとの組み合わせからなる、延性はんだボールとを具備する、チップスケールパッケージ。

## 【請求項2】

10

20

請求項 1 に記載のチップスケールパッケージにおいて、前記複数のはんだボール ( 28 ) の各々は、少なくとも重量比 80 % の鉛 ( Pb ) からなる、チップスケールパッケージ。

**【請求項 3】**

請求項 1 に記載のチップスケールパッケージにおいて、前記複数のはんだボール ( 28 ) の各々は、インジウム ( In ) 合金からなる、チップスケールパッケージ。

**【請求項 4】**

請求項 1 に記載のチップスケールパッケージにおいて、前記複数のはんだボール ( 28 ) の各々は、共晶スズ/鉛 ( 63Sn/Pb ) からなる、チップスケールパッケージ。

**【請求項 5】**

請求項 1 に記載のチップスケールパッケージにおいて、前記集積回路は、中心部と外縁 ( 21 ) とを有し、また前記集積回路は、その外縁 ( 21 ) に隣接して少なくとも 1 つの周辺導電結合パッド ( 18 ) を有し、前記集積回路の少なくとも 1 つのはんだバンプパッド ( 26 ) は、それが電気的に結合される、対応する周辺導電結合パッドよりも前記集積回路の中心部に接近して前記半導体チップ上に配置される、チップスケールパッケージ。

**【請求項 6】**

請求項 1 に記載のチップスケールパッケージにおいて、前記ポリマー層は、ベンゾシクロブテンからなる、チップスケールパッケージ。

**【請求項 7】**

請求項 1 に記載のチップスケールパッケージにおいて、前記パターン化された金属層は、該複数の再分配トレースと共に前記複数のはんだバンプパッドの双方を提供する、単一金属層からなる、チップスケールパッケージ。

**【請求項 8】**

請求項 1 に記載のチップスケールパッケージにおいて、前記半導体チップの後面上に形成された保護被覆 ( 34 ) を備える、チップスケールパッケージ。

**【請求項 9】**

はんだバンプ半導体ウェハ構造にして、

a . 複数の集積回路 ( 10 ) 等を含む、前面 ( 12 ) 及び後面 ( 16 ) を有する半導体ウェハであって、該集積回路の各々は、集積回路を電気的に相互接続するために、前記半導体チップの前面に形成された、複数の導電結合パッド ( 18 , 20 ) を含み、また該集積回路の各々は、各集積回路の外縁 ( 21 ) に接近して形成された、集積回路自身の複数の導電結合パッドを有する、半導体ウェハを具備し、

b . 前記集積回路の各々は、前記半導体チップの前面に形成された、パターン化された金属層 ( 30 ) を含み、各パターン化された金属層は、前記各集積回路の前面に複数のはんだバンプパッド ( 26 ) 及び複数の再分配トレースを提供し、前記集積回路の導電結合パッドを前記各集積回路の複数のはんだバンプパッドに電気的に結合し、前記はんだバンプ半導体ウェハ構造は、さらに

c . 前記半導体ウェハの前面及び前記パターン化された各金属層上を被覆するように伸びるポリマー層 ( 32 ) であって、前記ポリマー層は、前記はんだバンプパッド上に位置する開口部を有するものであり、

d . 複数の延性はんだボール ( 28 ) であって、各延性はんだボールは、前記複数の集積回路の各々の上の対応するはんだバンプパッドに固定され、前記半導体ウェハをリフロー温度まで加熱し、それぞれのはんだバンプパッドに固定した後に略球形の形状を有し、少なくとも 0.2286 mm の直径を有する、延性はんだボールとを具備する、はんだバンプ半導体ウェハ構造。

**【請求項 10】**

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記複数のはんだボール ( 28 ) の各々は、少なくとも重量比 80 % の鉛 ( Pb ) からなる、はんだバンプ半導体ウェハ構造。

**【請求項 11】**

10

20

30

40

50

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記複数のはんだボール(28)の各々は、インジウム(In)合金からなる、はんだバンプ半導体ウェハ構造。

【請求項 12】

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記複数のはんだボール(28)の各々は、共晶スズ/鉛(63Sn/Pb)からなる、はんだバンプ半導体ウェハ構造。

【請求項 13】

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記各集積回路は中心部を有し、前記各集積回路の複数のはんだバンプパッド(26)は、前記はんだバンプパッドに電気的に結合される、対応する導電結合パッド(18, 20)よりも前記集積回路の中心に接近した、前記半導体ウェハの前面上に配置される、はんだバンプ半導体ウェハ構造。

【請求項 14】

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記ポリマー層は、ベンゾシクロブテンからなる、はんだバンプ半導体ウェハ構造。

【請求項 15】

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記パターン化された金属層の各々は、該複数の再分配トレースと共に前記複数のはんだバンプパッドの双方を提供する、单一金属層から形成される、はんだバンプ半導体ウェハ構造。

【請求項 16】

請求項 9 に記載のはんだバンプ半導体ウェハ構造において、前記半導体ウェハの後面上に形成された保護被覆(34)を含む、はんだ半導体ウェハ構造。

【請求項 17】

集積回路(10)用のフリップチップパッケージ(8)を形成する方法であって、

a. 複数の集積回路(10)を含む半導体ウェハ(14)であって、上記半導体ウェハ(14)は前面(12)及び反対側の裏面(16)を有し、各上記集積回路(10)は上記半導体ウェハ(14)の前面(12)上に形成され且つ各集積回路を電気的に相互連結する複数の導電性ボンドパッド(18, 20)を含む、かのような半導体ウェハ(14)を準備するステップと、

b. 上記半導体ウェハの前面全体に金属層を塗布するステップと、

c. 各上記集積回路の全体に塗布された金属層の部分を選択的に除去して、それぞれ集積回路の前面上に複数のはんだバンプパッド(26)を付与し且つ各集積回路の導電性ボンドパッド(18, 20)を各集積回路のはんだバンプパッド(26)に電気的に結合させるパターン化された金属層(30)を各上記集積回路上に付与するステップと、

d. 上記半導体ウェハの前面全体及び各上記パターン化された金属層の上に、ポリマー層(32)を塗布するステップと、

e. 各上記はんだバンプパッドの上に塗布された前記ポリマー層に開口を形成するステップと、

f. 各上記はんだバンプパッドに、予め形成された延性はんだボール(28)を機械的に配置するステップであって、前記予め形成された延性はんだボール(28)の各々は、略球形で少なくとも0.2286mmの直径を有し、前記予め形成された延性はんだボール(28)は全て、リフロー温度を有するステップと、

g. ステップf.に続いて、このような延性はんだボールが、それぞれのはんだバンプパッドに永久的に固定するように前記延性はんだボールのリフロー温度まで前記半導体ウェハを加熱するステップであって、前記はんだボールは、それぞれのはんだバンプパッドに固定された後に略球形の形状となるステップと、

h. ステップg.に続いて、上記半導体ウェハをダイシングして、チップスケールパッケージ形態での複数の集積回路を与えるステップと、

を備えることを特徴とする方法。

【請求項 18】

10

20

30

40

50

請求項 17 の方法であって、前記ステップ f .において塗布された延性はんだボール ( 28 ) は、少なくとも 80 重量 % の鉛 ( Pb ) を含有する、ことを特徴とする方法。

**【請求項 19】**

請求項 17 の方法であって、前記ステップ f .において塗布された延性はんだボール ( 28 ) は、インジウム ( In ) 合金を含有する、ことを特徴とする方法。

**【請求項 20】**

請求項 17 の方法であって、前記ステップ f .において塗布された延性はんだボール ( 28 ) は、共晶スズ / 鉛 ( 63Sn / Pb ) を含有する、ことを特徴とする方法。

**【請求項 21】**

請求項 17 の方法であって、各前記集積回路 ( 10 ) は中央部及び外周部 ( 21 ) を有して、上記外周部に近接して形成された少なくとも 1 個の外周導電性ボンドパッド ( 18 ) を有し、前記ステップ c . は、各前記集積回路の少なくとも 1 個のはんだバンプパッド ( 26 ) を、上記はんだバンプパッドが電気的に結合する対応する上記外周導電性ボンドパッド ( 18 ) よりも各上記集積回路の中央部に近い位置にて、前記半導体ウェハ ( 14 ) の前面に配設するステップを含む、ことを特徴とする方法。 10

**【請求項 22】**

請求項 17 の方法であって、前記ステップ d .において塗布された前記ポリマー層 ( 32 ) は、ベンゾシクロブテンであることを特徴とする方法。

**【請求項 23】**

請求項 17 の方法であって、前記各集積回路の全体に塗布された金属層の部分を選択的に除去するステップは、各集積回路の複数のはんだバンプパッド ( 26 ) を各集積回路の対応する複数の導電性ボンドパッド ( 18 、 20 ) に電気的に結合させる複数の再分配トレース ( 30 ) を付与するステップを含み、前記ステップ b . 及び c . は、前記はんだバンプパッド及び上記再分配トレースの両者を单一のパターン化された金属層として形成する、ことを特徴とする方法。 20

**【請求項 24】**

請求項 17 の方法であって、前記延性はんだボール ( 28 ) は、延性はんだボールが溶融するようになるリフロー温度を有し、さらに、上記延性はんだボールを塗布する前に、はんだバンプパッドにはんだ融剤を塗布し、その後、上記延性はんだボールを塗布して半導体ウェハを上記延性はんだボールのリフロー温度まで加熱して、上記延性はんだボールをはんだバンプパッド ( 26 ) に永久的に固着させる、ことを特徴とする方法。 30

**【請求項 25】**

請求項 17 の方法であって、前記延性はんだボール ( 28 ) を各はんだバンプパッド ( 26 ) に塗布するステップは、各上記はんだバンプパッドに予め形成されたはんだボールを機械的に配置するステップを含む、ことを特徴とする方法。

**【請求項 26】**

請求項 17 の方法であって、さらに、前記半導体ウェハの裏面全体に、保護コーティング ( 34 ) を塗布するステップを含む、ことを特徴とする方法。

**【発明の詳細な説明】**

**【0001】**

40

**【技術分野】**

本発明は、集積回路のフリップチップを回路基板等にはんだバンプを介して実装する技術、具体的には、チップスケールパッケージ及び、集積回路をその下側の回路基板等に直接接続する、チップスケールパッケージ関連方法に関する。

**【0002】**

**【背景技術】**

フリップチップとは、パターン処理された基板に取り付けるための接点山支持はんだバンプを備えるパッケージ化されていない集積回路チップを指す、と当業者には通常解されている。斯かるフリップチップは半導体ウェハに印刻された集積回路チップで形成される。処理に際しては、半導体ウェハの上面側である活性面に不純物が化学的拡散及び / 又は注

50

入によって導入され、トランジスタ等の電子部品が個々に形成される。又、印刻形成された集積回路チップの上面側である活性面に金属層がパターン配置され、半導体ウェハ上に形成された種々のデバイスの電極が電子的に接続される。フリップチップは、印刻形成された集積回路チップの上面側である活性面を反転、即ち、裏返すと、下側に位置するパターン処理された基板に溶接される。はんだバンプを「リフロー」温度まで加熱するとはんだが溶融し、溶接部の「リフロー」によってフリップチップがパターン処理された支持基盤に電気的且つ機械的に接合される。フリップチップを支持基盤に接合するはんだバンプの使用例は、ケイソン等に付与された米国特許第5,261,593号、プラントンに付与された米国特許第5,220,200号、ヒグドン等に付与された米国特許第5,547,740号及びデガーニ等に付与された米国特許第5,564,617号に開示されている。10

#### 【0003】

パッケージ化されていない集積回路は、本質的に裸状態の半導体チップであるため、組立時に取り扱いを誤ると損傷しやすい。このため、電子機器製造業者の多くは、パッケージ化されていないフリップチップを回路基板に直接取り付けることを嫌い、パッケージ化された装置を好む。そこで、集積回路部品製造業者の多くは「チップスケールパッケージ」と称される「パッケージ化」された集積回路を採用して、裸チップでは取り扱いが難しいという顧客の懸念を払拭している。「チップスケールパッケージ」は、通常、集積回路チップ自体より大きさが1.2倍以下のパッケージを指す。斯かるチップスケールパッケージは集積回路を機械的に必要最低限度に保護して、その取り扱いを容易にする。これにより、顧客は、裸チップを取り扱っていないという点で安心感を享受できる。チップスケールパッケージは主に集積回路の活性面を幾分大きな基板に接合する。一方、基板上に設けられた電気接点はチップスケールパッケージを回路基板に接続するために用いられる。20

#### 【0004】

フリップチップアセンブリの支持基盤とその集積回路とは、互いの熱膨張率がしばしば異なる。異なる熱膨張率に起因して熱応力が発生すると、フリップチップ集積回路を支持基盤に接合するはんだバンプが破損する可能性がある。破損すれば回路は使い物にならなくなる。チップスケールパッケージの業界では、チップと基板との間で熱膨張率が異なるのを抑止するために、はんだバンプの周囲並びに集積回路と支持基盤との間に余盛不足物質を用いることが知られている。斯かる余盛不足物質を使用すると溶接部の寿命を引き延ばすことができるが、処理費用が高くなることが多い。これは、標準的な表面実装技術を用いた製造方法に反することになる。30

#### 【0005】

標準的なフリップチップ溶接部は一般的に非常に小さい（例えば、直径が100ミクロンで高さが70~85ミクロン）。そこで、標準的な表面実装処理に適合させるには、溶接部を、主に、63Sn/Pbはんだ合金とする。例えば、はんだバンプをスズ63パーセント、鉛37パーセントとする。公知技術の一例として、63Sn/Pbはんだ合金を、基板のはんだ接点山に盛り付け、鉛の含有率が高いはんだバンプを蒸発させる、即ち、集積回路のフリップチップ溶接山に鍍金する。但し、はんだ山の寸法は一般に7ミリ（0.007インチ）である。小型の溶接部やフリップチップ溶接部の寿命を考慮すると、はんだバンプの応力を極力抑えるには、余盛不足物質の使用が欠かせないことになる。40

#### 【0006】

多くの公知のチップ・スケール・パッケージ法は、集積回路の接着パッドを支持基板に結合するようにはんだバンプを使用する。これらの接着パッドは、代表的には集積回路チップの外周に配置される。複雑な集積回路は、集積回路と外側の世界との間の必要な電力、入力、出力をつくるために、百を超える別個の接着パッドを必要とする。その結果、このような接着パッドは、代表的には互いに密接して配置され、このような接着パッドに横たわるはんだバンプのサイズおよび高さに物理的制約を与える。Higdon等に特許された米国特許第5,547,740号は、はんだバンプ接触パッドのうちのいくつかが、集積回路の外周から離れて一体に再配分され、はんだバンプのサイズが変えられないことを50

開示している。

【0007】

さらに、集積回路のチップ・スケール・パッケイギングを形成する公知の技術の大部分は、個々のチップ・レベルで実施されなければならない。すなわち、集積回路がとられる半導体ウェハは、まず刻み目を付けられ、チップ・スケール・パッケイギング方法が実行される前に、個々のチップに切断されなければならない。これらのチップ・レベル・パッケージング技術八、ウェハ・スケール処理技術の経費上の利点を得られない。さらに、メモリ・チップのような特定の集積回路市場は、形態因子（すなわち、圧縮された集積回路の物理的サイズ）およびパッケージングの費用によって大きく動かされる。しかも、多くの公知のチップ・スケール・パッケージ技術は、著しい追加の費用を要し、圧縮された集積回路の寸法を増加させる。10

【0008】

チップ・スケール・パッケージを形成するために用いられた公知のウェハ・レベル処理技術のうちの1つは、三菱PMEB ( Plastic Molded, Extended Bump ) 技術である。三菱からのPMEBパッケージは、集積回路の接着パッドから離れてはんだバンプ・パッドを動かすように再配分技術を利用し、また、ウェハ・レベルで最初にはんだ隆起を行う。しかし、これらの工程に続いて、三菱PMEB技術は、半導体ウェハからの成分を型に入れ、それらを包囲し、共晶「延長バンプ」をパッケージの表面に置く。得られたチップ・スケール・パッケージ構造は、湿気の侵入に敏感であり、低リード・カウントにおいて比較的に高い。さらに、三菱PMEBパッケージは、63Sn/Pb延長はんだバンプ（プラスチック・カプセルが高いはんだ再流温度を阻止する）を用いる。これは、延長はんだバンプの疲労寿命を制限する。20

【0009】

チップ・スケール・パッケージを形成するために用いられる別の公知のウェハ・レベル技術は、Sandia Ball Grid Array技術である。この技術は、集積回路上のはんだバンプ位置の配置を再配分するが、多金属層を必要とする。その理由は、メッキ方法がはんだ堆積に用いられているからである。再分配線は、パターン化されかつ不動態化された堆積金属の第1層によって与えられる。金属の第2層は、はんだバンプ・パッドを形成するようにウェハ上にスパッタされ、そして、標準の電子メッキ方法が標準サイズはんだバンプを形成するために用いられる。30

【0010】

したがって、本発明の目的は、改良されたチップ・スケール・パッケージおよびそれを形成する方法、ならびに標準表面装着技術製造技術からなり、熱係数微分によって誘導された疲労からのはんだバンプを保護するために集積回路と支持基板との間に材料を追加する必要を避けるフリップ・チップ集積回路のための改良されたチップ・スケール・パッケージおよびそれを形成する方法を提供することにある。

【0011】

本発明の別の目的は、改良されたチップ・スケール・パッケージおよび個々の集積回路チップ・レベルに反して、ウェハ処理レベルで実施されるチップ・スケール・パッケージを形成する方法を提供することにある。40

【0012】

本発明のさらに別の目的は、集積回路用の改良されたチップ・スケール・パッケージおよび装備に比較的に安価で、小さい形態因子を生じ、すなわち、得られたチップ・スケール・パッケージが最初の集積回路のサイズよりも大きくなきチップ・スケール・パッケージを形成する方法を提供することにある。

【0013】

本発明のさらに別の目的は、直接に表面に装着され、しかも裸のフリップ・チップ集積回路チップよりも良好に保護されかつ取り扱いが容易であるウェハ・スケール・チップ・スケール・パッケージを提供することにある。

【0014】

10

20

30

40

50

本発明のさらに別の目的は、はんだバンプをかいして支持基板に直接に表面装着され、疲労に対するはんだバンプの感受性が低減されるウェハ・スケール・チップ・スケール・パッケージを提供することにある。

#### 【 0 0 1 5 】

本発明のさらに別の目的は、はんだバンプを容易にするように集積回路に付着された金属層の数を最小にし、かつ、メッキ以外の方法によってはんだバンプの形成を許すウェハ・スケール・チップ・スケール・パッケージを提供することにある。

#### 【 0 0 1 6 】

本発明のこれらの及びその他の目的は、本発明の説明が進むにつれて当業者にとってより明らかとなるであろう。

10

#### 【 0 0 1 7 】

##### 発明の開示

簡単に説明すると、好ましい実施形態によれば、本発明は、前面とこれと正反対の後面とを有する半導体チップ上に形成された集積回路を含んでいるチップスケールパッケージに関する。この集積回路チップの前面上の外周の近くには、この集積回路内に形成されたデバイスへの電気的連絡をさせるための一群の導電性接合パッドが形成されている。半導体チップの前面には、集積回路チップの導電性接合パッドに電気的に結合されているが集積回路チップの外周から横方向に外れて配置されている多数のはんだバンプパッドを形成している導電性パターンが形成された層が形成される。不動態化保護層が半導体チップの前面に亘って前記パターンが形成された金属層の上に広がっており、この不動態化保護層内に形成された穴がはんだバンプパッドを露出させる。保護コーティングが、機械的な保護のために半導体チップの後面を覆って広がることができる。各々ほぼ球形であり且つ直径が少なくとも 9 ミル (.009 インチ) の大きさの延性はんだボールがこのようなはんだパッドの各々の上に形成されて、得られた構造が回路基板又はその他の構造に直接面装着できようになされている。

20

#### 【 0 0 1 8 】

本発明の好ましい実施形態においては、上記の延性はんだボールは、少なくとも重量比 80 % の鉛 (Pb) によって形成される。はんだボールはより高いリフロー温度を有するけれども、機械的疲労は受け難い。インジウム (In) 合金を含むその他のはんだボールの塑性を使用してもよい。

30

#### 【 0 0 1 9 】

はんだボールの各々は、半導体チップの前面において、各はんだバンプパッドが電気的に接合される対応する導電性接合パッドよりも中心により近い位置に配置されるのが好ましい。このような配置によって、はんだボールが半導体チップの周縁を越えて広がる虞れがなく且つはんだボールが相互に当接する虞れがなく、はんだボールの直径をより大きいものとすることができます。パターンが形成された金属層は、はんだバンプパッドをこれらの対応する導電性接合パッドに電気的に接合するための複数の再分布軌道を提供する。このパターンが形成された金属層は、理想的には、はんだバンプパッドだけでなく再分布軌道の両方ともを同時に提供する単一の金属層によって形成される。上記の不動態化保護層は、ポリマーであるのが好ましく、合成ベンゾシクロブテンであるのが好ましい。

40

#### 【 0 0 2 0 】

本発明のもう一つ別の特徴は、各々が各集積回路に電気的に連絡させるために半導体ウェハの前面の外周の近くに形成された一連の導電性接合パッドを含んでいる複数の同様の集積回路を含む半導体ウェハを含むはんだバンプ化された半導体ウェハに関する。このような集積回路の各々の上には、一連のはんだバンプパッドを提供し且つこのような集積回路の各々の導電性接合パッドを対応する一連のはんだバンプパッドに電気的に接合させるために、半導体ウェハの前面に亘ってパターンが形成された金属層が形成される。半導体ウェハの前面は、半導体ウェハの前面に亘って広がる不動態化保護層によって保護され、同不動態化保護層内のはんだバンプパッドの各々の上に穴が形成される。半導体ウェハの後面は、その上に形成された保護コーティングによって保護することができる。各々ほぼ球

50

形であり且つ直径が少なくとも 9 ミル ( . 0 0 9 インチ ) の大きさの延性はんだボールが、集積回路の各々の上の各はんだバンプパッドに固定される。このようにして得られた半導体ウェハは、次いで、線を刻み付けられるか賽の目に切られて、チップスケールの集積回路パッケージの形態の複数の集積回路が提供される。

#### 【 0 0 2 1 】

本発明はまた、フリップチップが一体化された回路用のチップスケールパッケージ ( c h i p s c a l e p a c k a g e ) を形成する方法に関する。そのような方法によると、半導体ウェハーは多数の同じ一体化された回路を収容しており、かかる一体化された回路の各々は半導体ウェハーの前面に形成された一連の電導性接着パッドを備え、この電導性接着パッドは相互に電気的結合をなすべく各一体化された回路の周縁に配置されている。

10 防護コーティングを半導体ウェハーの後面に塗布する事ができる。金属層が半導体ウェハーの前面に設けられており、かかる金属層の幾つかの部分は各一体化された回路上にパターン化された金属層を残すために選択的に除去される。各パターン化された金属層には、そのような各一体化された回路の前面に一連のはんだバンプパッドが備わっており、各はんだバンプパッドはパターン化された金属層により、はんだバンプパッドの対応する一つに電気的結合されている。不動態化層が次に半導体ウェハーの前面を覆いかつ各パターン化された金属層の上に付与されて、各はんだバンプパッドの上に付与された不動態化層の開口部を残したまま、各一体化された回路の前面を封止する。延性はんだボールが次に各はんだバンプパッドに付与され、延性はんだボールは略球状の形状を有し少なくとも 9

20 ミル ( 0 . 0 0 9 インチ ) の直径を有する。その結果得られた半導体ウェハーは次にチップスケールパッケージ状に多数の一体回路を与えるべく賽の目状に切断される。

#### 【 0 0 2 2 】

本方法に使用される不動態化層はポリマー層が望ましく、ベンゾシクロブタン ( b e n z o c y c l o b u t e n e ) 製品がそのような不動態化層として特に有益であることが見出された。

#### 【 0 0 2 3 】

本発明の方法を実施する場合、はんだボールが高度に延性であるようにされ、少なくとも 80 パーセント重量比の鉛 ( P b ) からなる、はんだボール化合物を選定する事が望ましい。その換りとして、インジウム合金からなるはんだボール化合物もまた使用可能である。本方法の好ましい実施形態では、延性はんだボールは、各はんだバンプパッド上に予め形成されたはんだボールを機械的に配置することにより、各はんだバンプパッド上に設けられる。延性はんだボールを付与する前に、はんだフラックスがはんだバンプパッドに塗布されることが望ましい。半導体ウェハーは次にはんだボールの溶融温度まで加熱され、その後延性はんだボールが付与されて、はんだボールを下層のはんだバンプパッドに永久的に固定する。

30

#### 【 0 0 2 4 】

はんだボールの比較的大きい寸法を鑑みて、本方法は、一体化された回路の対応する電導性接着パッドの最初の配置と比較すると、一体化された回路の周縁から離れて各一体化された回路の中心に接近して配置された点まではんだパッドを再配分することを意図している。このようなはんだバンプパッドの再配分は、各はんだバンプパッドを対応する電導性接着パッドに電気的結合するように、付与された金属層の部分を選択的に除去する工程で一連の再配分トレースをすることにより達成される。この方法を実施する場合、はんだバンプパッドと上述の再配分トレースの双方を形成するように、付与された同一の金属層がパターン化されることが望ましい。

40

#### 本願発明を実施するための最良の態様

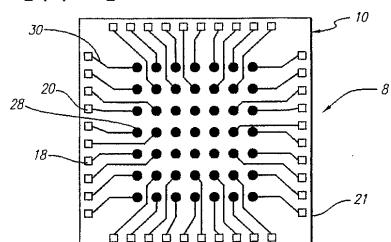

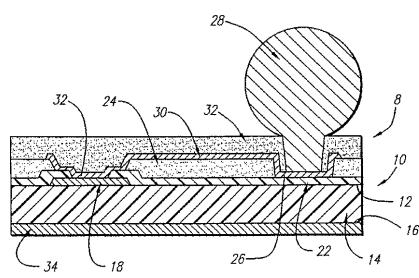

図 1 及び図 2 は、全体が参照符号 8 によって示され、本願発明にしたがって構成されたフリップチップ集積回路用のチップ・スケール・パッケージを図示している。図 1 において、集積回路 10 が、通常の態様で、半導体チップ上に形成されており、トランジスター及び他の電気素子 ( 図示せず ) されたネットワークを含んでいる。図 2 を参照すると、集積回路 10 は、半導体ウェハ 14 の表面 12 に形成されている。半導体ウェハ 14 は、また

50

、その反対側に裏面 16 を有している。化学的な不純物が、集積回路 10 の処理の間に、その表面 12 を介して半導体ウェハ 14 内に、拡散され、移植され、又は導入されており、これによって、集積回路 10 内に種々のトランジスターや他の電気素子を形成している。そのような電気素子は、半導体ウェハ 14 の表面 12 に形成された、1つ又はそれ以上の金属被覆層（図示せず）によって、互いに相互に接続されている。

#### 【 0 0 2 5 】

集積回路 10 は、一連の入力端子、出力端子、電力端子とを有している。入力端子、出力端子、電力端子は、集積回路 10 を実際に使用するために、外の世界に電気的に接続されなければならない。このため、ほとんどの集積回路には、図 1 及び図 2 の参考符号 18 及び 20 によって示されているような一連の導電性の接着用パッドが設けられている。一連の導電性の接着用パッドは、集積回路 10 と電気的に相互接続できるように、半導体ウェハ 14 の表面に形成されている。図 1 に示されているように、これらの導電性の接着用パッド 18 及び 20 は、典型的に、集積回路 10 を含む半導体チップの外側周辺部 21 近くに形成され且つ配置されている。集積回路 10 は、また、図 2 に示されているように、典型的に、集積回路 10 の相互接続用の上側メタル層を保護するために、半導体ウェハ 14 の表面に塗布されたウェハパシベーション層 22 を有している。

図 2 に示されているように、開口部が、典型的に、導電性の接着用パッド 18 / 20 にアクセスすることができるよう、導電性の接着用パッド 18 / 20 上でウェハパシベーション層 22 に設けられている。上述した構造及び工程は、通常の集積回路の典型であり、そのような集積回路は、最後に、パッケージにワイヤーボンディングされるか、あるいは、はんだバンプされる。

#### 【 0 0 2 6 】

上述したように、本願発明は、延性のはんだボールを用いて、チップ・スケール・パッケージ 8 と外部電気回路とを相互接続する。はんだバンプを用意するために、オプションとして、第 1 のパシベーション層 24 を、ウェハパシベーション層 22 の真上で半導体ウェハ 14 の表面に亘って塗布してもよい。第 1 のパシベーション層 24 は、絶縁体であり、ウェハ表面に保護膜を被せ、また、ウェハ表面を平坦にする。第 1 のパシベーション層 24 は、既存のウェハパシベーション層 22 の特性に応じて、ある場合には削除してもよい。本願発明の好適な実施例において、第 1 のパシベーション層 24 は、商品名「Cyclootene」の下で、ミシガン州のミッドランドに所在する Dow Chemical 社から市場で入手可能なベンゾイルシクロブテン（Benzocyclobutene）で形成される。しかしながら、他の組成物を用いて、ポリイミド、ポリオレフィン、及び他の有機パシベーションや無機パシベーションを含む第 1 のパシベーション層 24 を形成してもよい。第 1 のパシベーション層 24 は、ほぼ 4 - 5 μm の厚さの層を形成できるように、スピンドルコートィング（spin coating）によって、半導体ウェハ 14 上に塗布することが好ましい。通常の写真印刷技術を用いて、導電性の接着用パッド 18 / 20 の各々上で、また、はんだバンプパッドが最後に形成される位置で、第 1 のパシベーション層 24 内にパターン化された開口部を形成することができる。あるいは、そのような開口部は、導電性の接着用パッド 18 / 20 上の各々の領域に限定することもできる。この場合、はんだバンプパッドは、最後に、第 1 のパシベーション層 24 上に位置する。

#### 【 0 0 2 7 】

上述したように、チップ・スケール・パッケージ 8 は、過去に用いられたものよりもいくらか大きな寸法の延性のはんだボールを利用している。そのようなはんだボールを収容するために、対応する導電性の接着用パッドに対して、はんだバンプパッドを再配置したり、あるいは、再分配したりすることが要求される。図 1 及び図 2 に示されているように、延性のはんだボール 28 が取り付けられるはんだバンプパッド 26 は、導電性の接着用パッド 18 から横方向に変位させられている。さらに図 1 及び図 2 に示されているように、はんだバンプパッド 26 と導電性の接着用パッド 18 は、再分配トレース 30 によって、電気的に相互接続されている。

#### 【 0 0 2 8 】

10

20

30

40

50

リディストリビューショントレース 30 とはんだバンプパッド 26 が、ウェハパッシベーション層 22 上と第1パッシベーション層 24 上に形成されるパターン化金属層として、半導体ウェハ 14 の表面上方に設けられる。このパターン化金属層は、最初に、半導体ウェハ 14 の表面を、いわゆるアンダーバンプ冶金 (Under Bump Metal urging) (またはUBM) 層でプランケッティングすることにより行われることが好ましい。このUBM層は、アルミニウム (Al)、ニッケルバナジウム (NiV) 及び銅 (Cu) からなる 3 金属層構造物であることが好ましいが、または、チタニウム (Ti)、ニッケルバナジウム (NiV) 及び銅 (Cu) からなる 3 金属層構造物若しくは他の適当な金属構造物であってもよい。UBM層は、公知の金属スパッタリング技術によって、半導体ウェハ 14 上に設けることができる。そのように設けられたUBM層の厚みは、約 2 ミクロンであることが好ましい。UBM層は、いくつかの目的を達成する。第一に、UBM層はその下にある面に密着する。第2に、UBM層は、溶融状態のはんだが、半導体ウェハ 14 表面中に侵入することを防止する、はんだ拡散防止壁として作用する。UBM層は、また、はんだ付け性の観点から、「濡れやすい (wettable)」層として作用する。最後に、UBM層は、延性はんだボール 28 と伝導性ボンドパッド 18 との間の電気接触抵抗を最小限に抑えるように作用する。そのようなUBM層を設けた後、該UBM層は、公知のフォトリソグラフィ技術によってエッチングされて、所望のパターン化金属層を構成し、それによって、伝導性ボンドパッド 18 に、はんだバンプパッド 26 と、リディストリビューショントレース 30 と、電気接触子 32 とを設ける。

## 【0029】

10

当業者であれば、上記のUBM層によって、典型的な伝導性ボンドパッドの、図1に示すアレイリディストリビューションパターンのような新しいパターンへのリディストリビューションが可能になることを理解するであろう。はんだバンプパッドを再配置するための上記のリディストリビューションプロセスにおいては、リディストリビューショントレース 30 と、はんだボール 28 へのUBMインターフェース 26 との両方に対して同じ冶金学が用いられている。リディストリビューションされたはんだバンプパッド 26 は、装置表面の、実質的にどこにでも配置することができる。例えば、はんだバンプパッド 26 は、各はんだバンプパッド 26 が電気的に結合される対応の伝導性ボンドパッド 18 よりも、集積回路 10 の中心に、より近いポイントに配置される。

## 【0030】

20

UBM層が上記の方法で設けられ、パターン化された後、図2に示すように、そのパターン化された金属層上に第2パッシベーション層 32 が設けられる。この第2パッシベーション層もまた、上記のベンゾシクロブテンにより形成されることが好ましいが、ポリイミド、ポリオレフィンや、他の有機または無機パッシベーションを用いてもよい。第2パッシベーション層 32 は、好ましくは、スピノコーティングによって、半導体ウェハ 14 上に設けられることにより、約 4 ミクロンの厚みを有する層を形成する。従来のフォトリソグラフィ技術を用いて、第2パッシベーション層 32 中の、各はんだバンプパッド 26 の箇所に、パターン化された開口を形成する。

## 【0031】

30

一度、第2パッシベーションレイヤ 32 が作られると、図2に示すはんだボール 28 のような柔軟なはんだボールが、露出したはんだパッド 22 の各々に形成される。柔軟なはんだボールの各々はほぼ球形であり、少なくとも 9 ミル (0.02286 cm) (0.009 インチ)、即ち少なくとも 229 ミクロンの直径を有する。従来のはんだバンピングは 63 Sn / Pb はんだまたは 95 Pb / Sn からはんだバンプを形成するが、0.01778 cm (0.007 インチ) 直径より小さいサイズのものは工程制限を受ける。対照的にはんだボール 28 はより柔軟な組成物を形成する。はんだボール 28 の好ましい組成物は少なくとも鉛 (Pb) を 80 重量 % 含み、残りが亜鉛で構成されている。またははんだボール 28 はインジウム (In) 合金または柔軟性を増すために少なくとも 80 重量 % の鉛を含む鉛合金で形成することもできる。より大きな直径で柔軟性が大きいはんだボールはチップスケールパッケージ 8 と最終的に取り付けられる基板との間の熱膨張率の違いによる

40

50

疲労負荷に対する強い抵抗を有するはんだボールを作ることができ、これによりどんな余盛不足を追加する必要もなくなる。本発明の好ましい実施例では、はんだボール28を予め形成し、機械的にこれをはんだパッド26に置く。そのような機械的配置前に、はんだフラックスをはんだバンプパッドに付与し、はんだボール28とはんだバンプパッド26間に最終的に形成される接合を向上させる。はんだボールを各はんだバンプパッドに機械的に配置することは、はんだボールが置かれる機械的なマスクによってなされる。しかし柔軟なはんだボールはメッキ、はんだペースト、蒸着、ボールバンピング及びはんだジェッティングを含む他のあらゆる方法によって形成することができる。はんだボールをはんだバンプパッドに形成したら、半導体ウェハチップスケールパッケージ8をはんだボール28の環流温度(reflow temperature)まで加熱し、これによりはんだボール28のはんだバンプパッド26への固定を形成する。

#### 【0032】

図2に関し、半導体ウェハ14の後ろ側即ち後面は参考符号16で示す。本発明の好ましい実施の形態では、有機保護コーティング34が半導体ウェハ14の後面16にコートされている。この保護コーティング34は、周知のスピンドルウェハプロセス装置を使用して半導体ウェハ14の後面14にコートし、この後硬化させることができる。有機保護コーティング34はエポキシや、取扱中にチップの後面に機械的保護を提供するその他の適切な有機保護コーティングが好ましい。保護コーティング34はウェハダイシングプロセスの一部として通常はダイシングされるが、切り口(kerf)を提供するために保護コーティング34を写真画像とすることもできる。いずれの場合にも、保護コーティング34の最終寸法はチップの最終寸法と同じであり、これにより最小形態要素のチップスケールパッケージ装置を提供する。保護コーティング34をチップスケールパッケージの形態で異なるステージに適用しながら、第1のパシベーション層24を半導体ウェハ14の前面に付与する前に、保護コーティング34を付与することが好ましい。

#### 【0033】

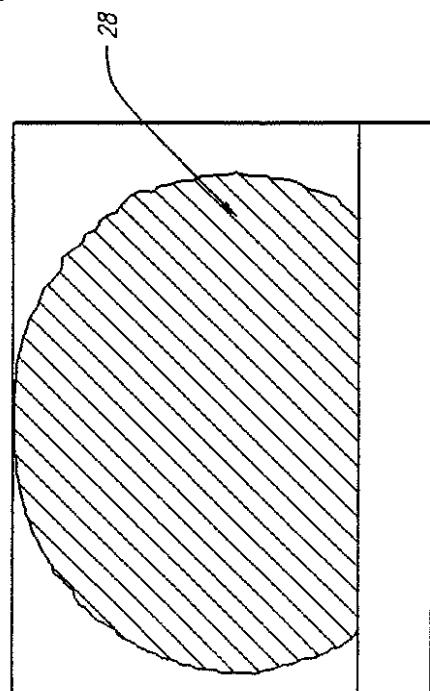

図3は、電子検査顕微鏡によって得られる延性はんだボール28を、該はんだボールのリフロー温度まで加熱したはんだバンプ構造の断面図を示している。リフロー中、はんだボール28は幾分平らになるが、延性はんだボール28の高さはなお、9.5ミル(0.0095インチ(0.02413cm))か、それ以上である。標準のはんだバンププロセスと比較すると、この増加した高さ及び延性によって、アンダーフィル(余盛不足)作業の必要がなくなり、さらに、チップスケールパッケージとこれを取り付ける基板との間の熱膨張率の違いによって生じるストレスに起因するクラックを抑えることができる。

#### 【0034】

上述した如く、本発明はまた上記集積回路のフリップチップパッケージを形成する方法に関する。そのような方法を実施する際に、半導体ウェハ14は複数の疑似集積回路10を含んで提供される。各集積回路10は、前面12上に形成された一連の導電性ボンドパッド18、20を含み、該ボンドパッドの少なくとも幾つかは半導体ウェハの外側周辺の直前に位置して、該半導体ウェハに対して電気的に相互接続される。保護コーティング34が半導体ウェハの後面16上に付加される。金属層26、30、32が半導体ウェハの前面12上に付加され、そのような金属層の所定部分がその後選択的に除去されて、パターン化された金属層を提供し、これにより各集積回路10の前面12上に一連のはんだバンプパッド26を提供する。パターン化された金属層30は、各集積回路10の導電性ボンドパッド18、20をそれらの関連するはんだバンプパッド22に電気的に連結する。典型的には、導電性ボンドパッド18、20の大部分は、集積回路10の外側周辺部に近接して配置され、金属層をパターン化するステップは好ましくは、複数のはんだバンプパッド26を、該各はんだバンプパッドが電気的に連結された対応する導電性ボンドパッド18よりも、集積回路10の中心の方へより近く配置するステップを含む。かくして、付加された金属層の所定部分を選択的に除去するステップは好ましくは一連の再分配トレース30を形成するステップを含み、該再分配トレース30は各はんだバンプパッド26を対応する導電性ボンドパッド18へ電気的に連結するものである。理想的には、各はんだバ

10

20

30

40

50

ンプパッド 26 及び再分配トレース 30 は単一のパターン化された金属層として形成される。

**【 0 0 3 5 】**

不動態化層 ( passivation layer ) 24 がそのとき半導体ウェハ 14 の前面 12、22 上及び各パターン化された金属層 26, 30, 32 上に付加される。この不動態化層 24 はポリマー層であり、好ましくはポリマー・ベンゾシクロブテン ( polymer Benzenocyclobutene ) からなる。そのとき各はんだバンプパッド 26 の各々上の付加された不動態化層 24 内に開口部が形成される。

**【 0 0 3 6 】**

延性のはんだボール 28 が各はんだバンプパッド 26 上に形成され、各延性のはんだボールは略球形状をしておりかつその直径が約 0.009 インチ ( 0.23 mm ) 又はそれ以上である。この工程の好ましい具体例では、延性のはんだボールは重量で少なくとも 80 パーセントの鉛 ( Pb ) を含み、所望の程度の延性 ( ductility ) を提供する。代替例としては、そのような延性のはんだボールはインジウム ( In ) 合金からなってもよい。好ましくは、そのような延性のはんだボールは、各はんだバンプパッド上に予備的形成されたはんだボールを機械的に置くことにより、各はんだバンプパッド上に形成される。延性はんだボール 28 は特徴あるリフロー ( reflow ) 温度を有し、その温度で溶融状態になる。好ましい工程は、延性はんだボール 28 を付加する以前にはんだバンプパッド 26 にはんだフラックスを付加し、その後、延性はんだボールを付加してそのような延性はんだボールをそれらの各はんだバンプパッドへ恒久的に固着させた後に、半導体ウェハ 14 をはんだボールのリフロー温度まで加熱することを含む。10

**【 0 0 3 7 】**

本発明を実施するに使用される全ての処理ステップは、ウェハのレベル、即ち半導体ウェハが区画状に切り分けられて ( diced ) 個々の集積回路 / チップのスケールのパッケージを形成する前に、行われる。この段階において、半導体ウェハ 14 はそのとき従来の刻引 / 破断 ( scribing / breaking ) 方法により区画状に切り分けられて、回路ボード又は他のパターン化基板に取付けられる得る多くのチップスケールがパッケージされた集積回路を提供する。20

当業者は、記述したフリップチップ集積回路の改良されたチップ・スケール・パッケージ及びそのようなチップ・スケール・パッケージを提供する方法を理解するであろう。ここに記載のフリップチップ・スケールのパッケージ方法は、個々の集積回路がけがきされ半導体ウェハから切断される前に遂行可能であり、それ故、低コストのウェハレベルの処理である。露出チップの操作は、処理のどの段階においても必要でなく、それは、三菱の上述の P M B E パッケージに対する重要な利点である。大きな延性はんだボールは、フリップチップ集積回路とそれがはんだ付けされる基板との間の熱膨張の異なる係数により引き起こされる疲労の可能性を著しく減少し、それにより不完全充填の作業を含めることの必要性、及びそのための費用を無くする。ウェハの背面の被覆処理は、集積回路を取り扱いし易くそして追加の機械的保護を提供する。対照的にサンディア ( Sandia ) のミニ BGA 処理は、集積回路に追加のパッケージを提供しない。30

**【 0 0 3 8 】**

加えて、はんだバンプ・パッド及びそのようなはんだバンプを再配置する再配分トレースの両者を形成するための同一パターンの金属層を使用する能力は、処理工程の数を最少にし、製造コストを減少する。対照的に、前記サンディアによるミニ BGA はんだバンプ技術は、板金工程がはんだバンプを適用するために使用されることを必要とし、それ故、はんだバンプ・パッド位置の再配置を遂行するために、2つの金属化された層を使用することが必要とされる。更に、ミニ BGA はんだバンプ技術を使用して用意されるはんだバンプの寸法形状は、それらの個々のはんだパッドの上のはんだボールを機械的に配置することにより得ることができるほどの大きさではない。

**【 0 0 3 9 】**

本発明は、発明の好ましい実施例について記述されたが、それらの記述は、ただ事例の目40

50

的であり、発明の範囲を限定するものとして解釈されるべきではない。例えば、本発明の好ましい実施例は、高鉛含有量を有する高延性はんだボールを使用するが、慣用の共晶すず・鉛（63Sn/Pb）のはんだボールを使用することも可能である。本発明に従って作られるはんだボールのより大きな直径は、そのようなはんだボールの疲労に対する抵抗を増加し、たとえそのようなはんだボールが慣用の共晶すず・鉛で作られるとしても、不完全充填の必要を避けるために充分であろう。種々の修正及び変更が記述された実施例に対して、添付の請求の範囲に定義される本発明の真の精神及び範囲から離れることなく、当業者によりなすことができる。

【図面の簡単な説明】

【図1】 本発明の好ましい実施形態により構成された、チップスケールパッケージ化された一体型回路の上面図である。 10

【図2】 図1に図示されたチップスケールパッケージ化された一体型回路を形成するために使用される半導体ウェハー部分の断面図である。

【図3】 半導体ウェハーの加熱に続いて延性はんだボールを下層のはんだ接着パッドに永久的に固定した状態の延性はんだボールの断面図である。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

---

フロントページの続き

(72)発明者 エレニアス , ピーター

アメリカ合衆国アリゾナ州85258 , スコットデール , イースト・コーチース 9885

(72)発明者 ホラック , ハリー

アメリカ合衆国アリゾナ州85251 , スコットデール , イースト・モンテサイト 6235

審査官 宮本 靖史

(56)参考文献 特開平08-097217(JP,A)

特開平09-232464(JP,A)

特開平06-045740(JP,A)

特開平08-330313(JP,A)

特開平09-172036(JP,A)

特開平08-064725(JP,A)

特開平08-340002(JP,A)

特開平08-250498(JP,A)

特開昭61-295639(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 21/3205

H01L 23/52