(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5296803号

(P5296803)

(45) 発行日 平成25年9月25日(2013.9.25)

(24) 登録日 平成25年6月21日(2013.6.21)

(51) Int.CI.

H04L 12/70 (2013.01)

F 1

H04L 12/70 100A

請求項の数 21 (全 19 頁)

(21) 出願番号 特願2010-537549 (P2010-537549)

(86) (22) 出願日 平成20年11月4日 (2008.11.4)

(65) 公表番号 特表2011-507378 (P2011-507378A)

(43) 公表日 平成23年3月3日 (2011.3.3)

(86) 國際出願番号 PCT/IB2008/054587

(87) 國際公開番号 WO2009/074902

(87) 國際公開日 平成21年6月18日 (2009.6.18)

審査請求日 平成23年9月15日 (2011.9.15)

(31) 優先権主張番号 11/955,933

(32) 優先日 平成19年12月13日 (2007.12.13)

(33) 優先権主張国 米国(US)

(73) 特許権者 598036300

テレフォンアクチーボラゲット エル エ

ム エリクソン (パブル)

スウェーデン国 ストックホルム エスー

164 83

(74) 代理人 100095957

弁理士 龜谷 美明

(74) 代理人 100096389

弁理士 金本 哲男

(74) 代理人 100101557

弁理士 萩原 康司

(74) 代理人 100128587

弁理士 松本 一騎

最終頁に続く

(54) 【発明の名称】処理メトリック情報のノード間における交換

## (57) 【特許請求の範囲】

## 【請求項 1】

ノードの処理キャパシティに関する情報を取得する方法であつて、

前記ノードから第1のレートで第1の信号を受信するステップと、

前記ノードから第2のレートで第2の信号を受信するステップと、

前記第2のレートと前記第1のレートとの間の比率を算出するステップと、

前記比率のプリセット値との比較に基づいて前記ノードの前記処理キャパシティを決定するステップと、

を含み、

前記第1の信号の連続するインスタンスの各々は、前記第1の信号の前回のインスタンスのシーケンス番号に基づいて算出されるシーケンス番号を含み、

前記第1の信号の最新のインスタンスの直後に受信される前記第2の信号のインスタンスは、前記第1の信号の前記最新のインスタンスのシーケンス番号に基づくシーケンス番号を含み、

前記第1の信号の次回のインスタンスの前に受信される前記第2の信号の連続するインスタンスの各々は、前記第2の信号の前回のインスタンスのシーケンス番号に基づくシーケンス番号を含む、

方法。

## 【請求項 2】

前記第1のレートは一定であり、及び

10

20

前記第2のレートは可変である、

請求項1に記載の方法。

**【請求項3】**

前記プリセット値は、前記ノードが通常の処理キャパシティを有する場合の前記第2及び第1のレートの間に等しい、

請求項1に記載の方法。

**【請求項4】**

前記ノードの前記処理キャパシティを決定する前記ステップに基づいてルーティングテーブルを更新するステップと、

前記ノードの前記処理キャパシティが低い場合に、前記ノードに向けてメッセージを送信することを控えるステップと、

10

をさらに含む、請求項1に記載の方法。

**【請求項5】**

前記比率における変化を監視するステップと、

前記比率が変化する場合に、前記ノードの処理キャパシティの変化を検出するステップと、

15

をさらに含む、請求項1に記載の方法。

**【請求項6】**

前記第2のレートの減少は、前記処理キャパシティの低下を示す、

請求項5に記載の方法。

20

**【請求項7】**

前記第1の信号の連続するインスタンスの各々における前記シーケンス番号は、前記第1の信号の前記前回のインスタンスの前記シーケンス番号に前記プリセット値を加えたものに等しく、

前記第1の信号の前記最新のインスタンスの直後に受信される前記第2の信号の前記インスタンスにおける前記シーケンス番号は、前記第1の信号の前記最新のインスタンスの前記シーケンス番号に1を加えたものに等しく、

前記第1の信号の前記次回のインスタンスの前に受信される前記第2の信号の連続するインスタンスの各々における前記シーケンス番号は、前記第2の信号の前記前回のインスタンスの前記シーケンス番号に1を加えたものに等しい、

30

請求項1に記載の方法。

**【請求項8】**

前記第1の信号の前記最新のインスタンスの前記シーケンス番号に基づいて、又は前記第2の信号の前記前回のインスタンスの前記シーケンス番号に基づいて、前記第2の信号の次回のインスタンスの期待されるシーケンス番号を算出するステップと、

前記期待されるシーケンス番号に等しくないシーケンス番号を含む前記第2の信号の前記次回のインスタンスを受信することにより、キャパシティの問題を検出するステップと、

35

をさらに含む、請求項1に記載の方法。

**【請求項9】**

前記第1の信号の前記最新のインスタンスの前記シーケンス番号に基づいて、又は前記第2の信号の前記前回のインスタンスの前記シーケンス番号に基づいて、前記第2の信号の次回のインスタンスの期待されるシーケンス番号を算出するステップ、をさらに含み、

前記第2のレートと前記第1のレートとの間の前記比率を算出することは、前記期待されるシーケンス番号に合致しないシーケンス番号を含む前記第2の信号の所与のインスタンスを無視することを含む、

40

請求項1に記載の方法。

**【請求項10】**

ノードの処理キャパシティに関する情報を発信する方法であって、

前記ノードの通常の処理キャパシティを示すプリセット値以下である提供キャパシティ

50

値を決定するステップと、

前記ノードから基本レートで周期的に第1の信号を送信するステップと、

前記ノードから前記提供キャパシティ値を示す第2のレートで周期的に第2の信号を送信するステップと、

を含み、

前記第2のレートは、前記基本レートに前記提供キャパシティ値を乗じたものに等しく

前記第1の信号及び前記第2の信号は、前記基本レートと前記第2のレートとの間の比率に基づいて前記ノードの処理キャパシティを決定するピアノードへ送信される、

方法。

10

#### 【請求項11】

前記ノードは複数のインターフェースを含み、

周期的な第1の信号の各々は全てのインターフェース上で送信され、及び

周期的な第2の信号の各々は全てのインターフェース上で送信される、

請求項10に記載の方法。

#### 【請求項12】

前記提供キャパシティ値は、周期的に決定される、

請求項10に記載の方法。

#### 【請求項13】

前記提供キャパシティ値は、前記ノードの実際の処理キャパシティに従って設定される

20

請求項10に記載の方法。

#### 【請求項14】

前記提供キャパシティ値は、前記ノードの前記通常の処理キャパシティの所定の割合に従って設定される、

請求項10に記載の方法。

#### 【請求項15】

自身の処理キャパシティに関する情報を発信するためのノードであって、

プロセッサと、

前記プロセッサの負荷レベルを示すよう構成される負荷インジケータと、

30

ピアノードに向けて信号を送信するよう構成される1つ以上のインターフェースと、

第1のレートで第1の信号を送信するよう前記1つ以上のインターフェースに要求し、

前記負荷レベルと前記ノードの処理キャパシティの最大量との比較に基づいて第2のレートを算出し、並びに

前記第2のレートで第2の信号を送信するよう前記1つ以上のインターフェースに要求する、

よう構成される、制御ロジックと、

を含み、

前記負荷レベルと処理キャパシティの前記最大量との比較に基づいて第2のレートを算出することは、前記負荷レベルが低い場合に前記第2のレートを最大値に設定することを含み、

40

前記第1の信号及び前記第2の信号は、前記第1のレートと前記第2のレートとの間の比率に基づいて前記ノードの処理キャパシティを決定する前記ピアノードへ送信される、ノード。

#### 【請求項16】

前記第1のレートで前記制御ロジックのシーケンスを開始するよう構成されるクロックをさらに含む、請求項15に記載のノード。

#### 【請求項17】

自身の処理キャパシティに関する情報を発信するためのノードであって、

プロセッサと、

50

前記プロセッサの負荷レベルを示すよう構成される負荷インジケータと、

ピアノードに向けて信号を送信するよう構成される1つ以上のインターフェースと、

第1のレートで第1の信号を送信するよう前記1つ以上のインターフェースに要求し、

前記負荷レベルと前記ノードの処理キャパシティの最大量との比較に基づいて第2のレ

ートを算出し、並びに

前記第2のレートで第2の信号を送信するよう前記1つ以上のインターフェースに要求す

る、

よう構成される、制御ロジックと、

を含み、

前記負荷レベルと処理キャパシティの前記最大量との比較に基づいて第2のレートを算

出することは、前記負荷レベルが低い場合に前記第2のレートを最大値に設定することを

含み、

前記第1の信号の連続するインスタンスの各々は、前記第1の信号の前回のインスタンスのシーケンス番号に基づいて算出されるシーケンス番号を含み、

前記第1の信号の最新のインスタンスの直後に送信される前記第2の信号のインスタンスは、前記第1の信号の前記最新のインスタンスのシーケンス番号に基づくシーケンス番号を含み、及び

前記第1の信号の次のインスタンスの前に送信される前記第2の信号の連続するインスタンスの各々は、前記第2の信号の前回のインスタンスのシーケンス番号に基づくシーケンス番号を含む、

ノード。

#### 【請求項18】

ピアノードの処理キャパシティに関する情報を取得するためのノードであって、

前記ピアノードから信号を受信するよう構成される1つ以上のインターフェースと、

前記1つ以上のインターフェースから第1の信号を複数回受信し、

前記第1の信号の第1のレートを決定し、

前記1つ以上のインターフェースから第2の信号を複数回受信し、

前記第2の信号の第2のレートを決定し、

前記第2及び第1のレートの間の比率を算出し、並びに

前記比率に基づく前記ピアノードの処理キャパシティをピアテーブルに記憶する、

よう構成される、制御ロジックと、

クロックと、

を含み、

前記制御ロジックは、前記クロックからのタイミング情報を使用して前記第1及び第2のレートを決定し、並びに前記第1及び第2のレートを前記ピアテーブルに記憶する、ノード。

#### 【請求項19】

前記第1及び第2の信号は、シーケンス番号を含み、

前記制御ロジックは、最新の第1の信号のシーケンス番号に基づいて、又は前回の第2の信号のシーケンス番号に基づいて、次回の第2の信号の期待されるシーケンス番号を計算するようさらに構成され、並びに

前記制御ロジックは、前記期待されるシーケンス番号を前記ピアテーブルに記憶するようさらに構成される、

請求項18に記載のノード。

#### 【請求項20】

前記制御ロジックは、前記期待されるシーケンス番号に等しくないシーケンス番号を含む次回の第2の信号を受信することにより、キャパシティの問題を検出するようさらに構成される、

請求項19に記載のノード。

#### 【請求項21】

10

20

30

40

50

前記第2及び第1のレートの間の比率を算出することは、前記期待されるシーケンス番号に合致しないシーケンス番号を含む所与の第2の信号を無視することを含む、請求項19に記載のノード。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、計算キャパシティに関するメトリック (metric) 情報をノード間で交換するための方法及びノードに関する。

##### 【背景技術】

10

##### 【0002】

計算ノード (computing nodes) のネットワークにおいて、ノード間の通信は、予め定義されたルールに従って行われてもよく、又はネットワークの現在の状態に基づくメトリックに従って行われてもよい。ネットワーク、特にアドホックなネットワークにおけるノードの調整は、問題を孕み得る。例えば、複数のノードが全て同じ処理パワーを有しているわけではない場合、ノード間のリンクの既知の又は期待されるキャパシティのみに従ってルーティングすることは、効率的でない可能性がある。ネットワークには、可変レベルの柔軟性をもって設計されるものもあり、そのノードのうちのいくつかはメッセージ又は要求を送信する際にピアノード間における宛先を選択することができる。これらネットワークを効率的な手法で運用できるようにするために、ノードがそのような選択をすることを可能とする改良されたメトリックを提供することが必要となる。

20

##### 【0003】

2つのコプロセッサ上に負荷をバランシングする単純な手法は、単純に一方のプロセッサ上に一定のタスクを、もう一方のプロセッサ上に他のタスクを割り当てる事である。例えば、パーソナルコンピュータ上の1つの中央処理装置 (CPU) は、もう一方のCPUが入力データの計算を処理する傍ら、画像表示を処理し得る。このような所定の構成 (pre-arranged) は、例えば出力を画像で表示できるようにする前に大量の入力データを処理する必要がある場合、非常に非効率的である。

##### 【0004】

30

処理負荷をバランシングする他の方法は、様々なプロセッサをスキャンすることにより、各プロセッサにおいて処理を待つタスクキューの長さを取得することである。この方法は、様々なプロセッサが同一の場所に配置されている場合のみ効果があり、例えばコプロセッサの場合、少なくともある部分スキャン処理の実行に供される1つの個別のプロセッサに依存し得る。

##### 【0005】

並行スケジューリングは、負荷をバランシングするための別のアプローチである。並行スケジューリングの方法において、全てのプロセッサは協同して仕事をスケジューリングする。並行スケジューリングは、コンパイル時間又は実行時間において全体的な負荷情報を使用することにより負荷をバランシングする。これらの方法は一般に、プロセッサの相対的な処理キャパシティを考慮した、様々なプロセッサへの予め決定されたタスクの割り当てに依存する。並行スケジューリングの方法は、ノードにかかる負荷の観点についての時間的に変化する要件のような、変化する条件にほとんど適応できない。

40

##### 【0006】

2つのノード間における最適な計算パスを見つけるためにルーティングプロトコルと共に通常使用されるメトリックは、最小ホップカウントと呼ばれる。2つのノード間における様々なパスが比較され、離散リンク、リピータ、ルータ、及び / 又はゲートウェイの数がカウントされ、パス毎のホップの数を生じさせる。ホップの数が最小となる所与のパスが、2つのノードを接続するための最適なパスとして選択される。第1のノードが2つ以上のピアノードとの間で通信する選択肢を有する場合、ピアノードのうち最小数のホップを使用して到達され得る1つを選択してもよい。故に、最小ホップカウントを使用して 2

50

つのノード間における複数のパスのうちの1つを選択してもよく、又は複数のピアノードのうちの1つを選択してもよい。

#### 【0007】

ノードが異なる能力を有する環境において、ホップカウントのルーティングは適切ではないことが示されている。例えば“*A High-Throughput Path Metric for Multi-Hop Wireless Routing*”(D.S.J. De Couto et al., M.I.T. Computer Science and Artificial Intelligence Laboratory, International Conference on Mobile Computing and Networking, San Diego CA, September 2003)において、最小ホップカウントのルーティング技術は、ある環境において貧弱な性能を有することを著者は実証している。彼らは、2つのノード間に配置されるリンクの前方及び後方への配信比率(forward and reverse delivery ratio)を使用して算出される期待される送信カウントに基づいて、別のメトリックを提案している。その一方、“*Comparison of Routing Metrics for Static Multi-Hop Wireless Networks*”(R.Draves et al., Microsoft Research, Proceedings of the 2004 conference on Applications, technologies, architectures, and protocols for computer communications, Portland OR, August-September 2004)の他の著者は、メッセージの送信者が移動体である場合、ホップカウントのメトリックは他のリンク品質(link-quality)のメトリックよりも優れた性能を有することを主張している。

#### 【0008】

それにも関らず、ホップカウント又はより高度なメトリックにより最善のルーティングパスを決定する先行技術の方法は、ノードにはトラフィック処理能力が非常に高いものもあれば、非常に低いものもあり得るという事実を考慮に入れていない。ノードがネットワークのキャパシティを最適に使用できるように、その個々の処理キャパシティに関するメトリック情報をノード間において交換することに関する問題は、キャパシティの限界又はノード自身の現在の負荷を考慮に入れていないノード間の通信手段のみに基づくノードの調整によっては解決されない。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

通信するノードが、そのピアノードの現在の処理能力に関する正確で最新の情報を取得できるようにするための手段を有することは明らかに利点があるであろう。そのため、本発明の広範な目的は、1つのノードの処理キャパシティに関するメトリック情報をノード間において交換するための方法及びノードを提供することである。

#### 【課題を解決するための手段】

#### 【0010】

本発明の第1の観点は、ノードの処理キャパシティに関する情報を取得する方法を対象とする。上記方法は、上記ノードから第1のレートで受信される第1の信号を含む。上記ノードから第2のレートで第2の信号も受信される。上記第2のレートと上記第1のレートとの間の比率が算出される。上記比率のプリセット値との比較に基づいて上記ノードの上記処理キャパシティが決定される。

#### 【0011】

本発明の第2の観点は、ノードの処理キャパシティに関する情報を取得する上記方法の変形を対象とする。連続する第1の信号の各々は、前回の第1の信号のシーケンス番号に基づいて算出されるシーケンス番号を含む。最新の第1の信号の直後に第2の信号が受信される場合、それは上記最新の第1の信号のシーケンス番号に基づくシーケンス番号を含む。その後、次回の第1の信号の前に受信される連続する第2の信号の各々は、前回の第2の信号のシーケンス番号に基づくシーケンス番号を含む。上記最新の第1の信号の、又は上記前回の第2の信号の上記シーケンス番号に基づいて、次回の第2の信号の期待されるシーケンス番号が算出される。上記期待されるシーケンス番号に等しくないシーケンス番号を含む上記次回の第2の信号を受信することにより、生じ得るキャパシティの問題が

10

20

30

40

50

検出される。

【0012】

本発明の第3の観点は、ノードの処理キャパシティに関する情報を発信する方法を対象とする。上記方法は、提供キャパシティ値を決定するステップをもって開始される。上記提供キャパシティ値は、上記ノードの通常の処理キャパシティを示すプリセット値以下である。上記ノードは、基本レートで周期的に第1の信号を送信する。上記ノードは、上記提供キャパシティ値を示す第2のレートで周期的に第2の信号も送信する

【0013】

本発明の第4の観点は、自身の処理キャパシティに関する情報を発信するためのノードを対象とする。上記ノードは、プロセッサと、上記プロセッサの負荷レベルを示す負荷インジケータとを含む。1つ以上のインターフェースは、ピアノードに向けて信号を送信するよう構成される。制御ロジックは、第1のレートで第1の信号を送信するよう上記1つ以上のインターフェースに要求する。上記制御ロジックは、上記プロセッサの上記負荷レベルを読み取り、及び上記負荷レベルの上記ノードの処理キャパシティの最大量との比較に基づいて第2のレートを算出する。上記制御ロジックは、上記第2のレートで第2の信号を送信するよう上記1つ以上のインターフェースに要求する。

【0014】

本発明の第5の観点は、ピアノードの処理キャパシティに関する情報を取得するためのノードを対象とする。上記ノードは、上記ピアノードから信号を受信する1つ以上のインターフェースを含む。上記ノードは、制御ロジックも含む。上記制御ロジックは、上記1つ以上のインターフェースから第1の信号を複数回受信する。それは、上記第1の信号の第1のレートを決定する。上記制御ロジックはまた、上記1つ以上のインターフェースから第2の信号を複数回受信し、及び上記第2の信号の第2のレートを決定する。上記制御ロジックは、それから上記第2及び第1のレートの間の比率を算出し、並びに上記比率に基づく上記ピアノードの処理キャパシティをピアテーブルに記憶する

【図面の簡単な説明】

【0015】

ここで本発明のより詳細な理解のため、さらなる目的及びその利点について、次の添付の図面と併せて、以下で説明する。

【0016】

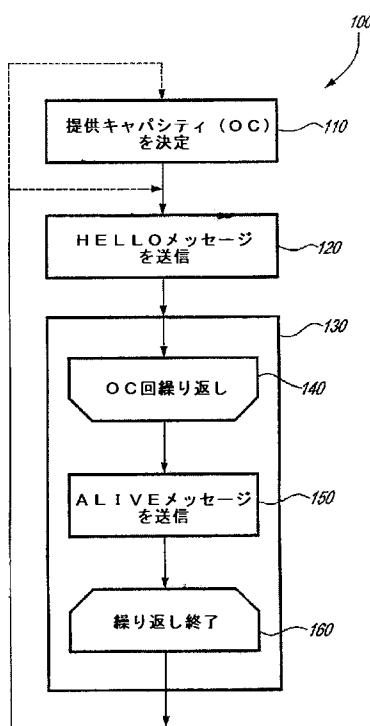

【図1】ノードの処理キャパシティに関する情報を発信(propagate)する一例となる方法を示す。

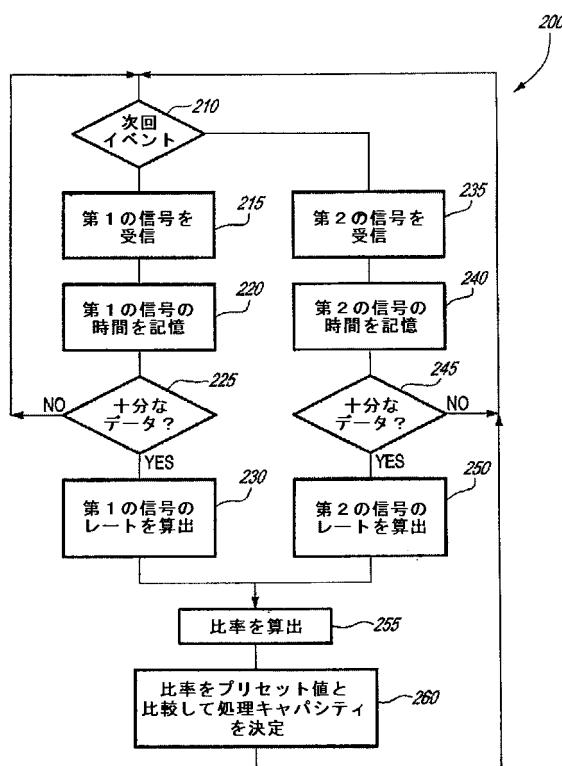

【図2】本発明の他の観点に従って、ピアノードにおいて対象ノード(node of interest)の処理キャパシティに関する情報を取得する一例となる方法を示す。

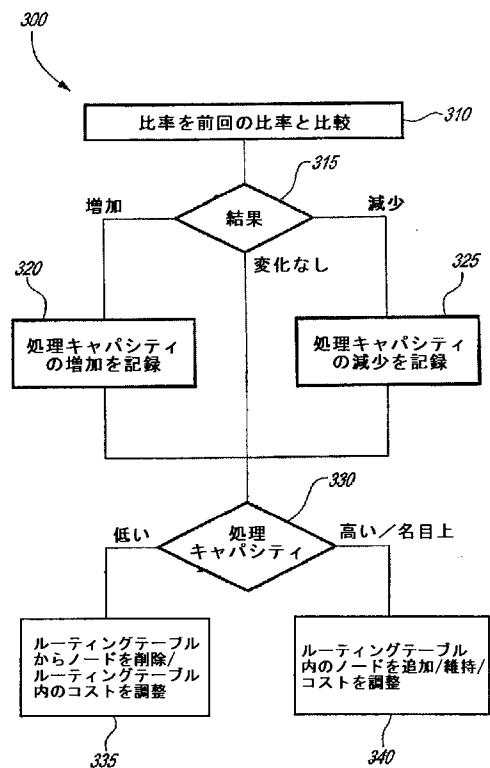

【図3】本発明の方法の追加的観点のステップを示す。

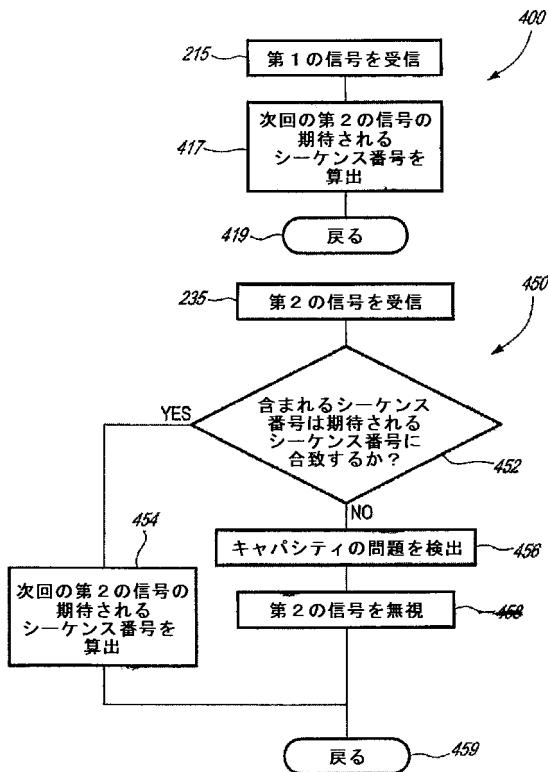

【図4】対象ノードの処理キャパシティを決定する処理においてより精度を上げるためのいくつかの例となる観点を示す。

【図5】本発明の観点に係る一例となるノードを示す。

【図6】本発明のいくつかの観点に係る一例となるピアテーブルを示す。

【発明を実施するための形態】

【0017】

本発明の革新的な教示を、例となる様々な使用及び好適な実施形態の観点を特に参照して説明する。一方、この実施形態が本発明の革新的な教示の多くの有利な使用のうち数例しか提供していないことは、理解されるべきである。概して、本アプリケーションの本明細書における記述は、本発明の主張される様々な観点のいずれをも必ずしも限定しない。さらにいくつかの記述は、発明の特徴のいくつかに適用してもよく、他には適用しなくてもよい。図の説明において、同様の番号は本発明の同様の要素を表す。

【0018】

本発明は、1つのノードの処理キャパシティに関するメトリック情報をノード間において交換するための方法及びノードを提供する。ノードのピアは、このメトリック情報を使

10

20

30

40

50

用して、例えばネットワークの全体キャパシティをより良好に使用するよう、そのルーティングテーブルを調節することができる。対象処理ノードは、例えば10秒毎といった定期的な間隔でHELLOメッセージをブロードキャストする。その後処理ノードは、例えば毎秒1回といったより高いレートでALIVEメッセージをブロードキャストする。ピアノードは、ALIVE及びHELLOメッセージの間の比率を計算し、現在の例では10:1となる。HELLOメッセージは一定のレートで送信される。処理ノードが高い負荷若しくは輻輳を経験している場合、又は何らかの理由でノードにかかるトラフィックの負荷を削減することが望まれている場合、処理ノードはALIVEメッセージをいくらか遅れさせてもよい。処理ノードがダウンしている場合、又は処理ノード及びピアノードのインターフェースの間のパスがダウンしている場合、比率は無限大に近付く。

10

## 【0019】

ピアノードは、比率を使用してそのルーティングテーブルを調節してもよく、それは例えば1より大きい比率を示す処理ノードに向けてのトラフィックの送信を削減し又は回避することによる。いかなる数のピアノードの間においても、ノードのいくつか又は全てを本発明の文脈において対象ノードと考えてもよく、いずれのピアも他のピアの処理キャパシティに関する情報を受信する必要があり得る。そのようなものとして、第1のノードは第2のノードから周期的なHELLO及びALIVEメッセージを受信する一方、それはまた同時に自身の周期的なHELLO及びALIVEメッセージを当該第2のノードに向けて送信し得る。

## 【0020】

20

本発明の文脈において、プロセッサを含み、及びピア要素(peer element)との間で通信するための手段を有する任意の計算要素(computing element)をノードは含み得る。本発明を実装し得るノードの例は、コンピュータ内部のコプロセッサ、ルータ、サーバ、スイッチ等を含む。ピア要素は、例えば同一コンピュータ上の2つのコプロセッサであってもよいという点において互いに類似する要素であってもよく、又は例えばピアとしてのルータを有するサーバ若しくはピアとしての無線基地局を有するセルラ移動体の交換局を含むという点において互いに類似しない要素であってもよい。

## 【0021】

ここで図面を参照すると、図1は、本発明のいくつかの観点に従って、ノードの処理キャパシティに関する情報を発信する一例となる方法を示している。ステップ100のステップは対象ノードにおいて実装されてもよく、当該ノードは例えば通常の又は名目の(nominal)処理キャパシティを有し、ピアノードからの代わりにいくつかの機能の処理を実行するという要求を処理してもよく、及びときどきその処理負荷が予め決定された限界に到達しつつあることを検出してもよい。ステップ110において、対象ノードは提供キャパシティ値(OC)を決定する。提供キャパシティ値は、対象ノードがピアノードに提供し得る処理の最大量を表すプリセット値を超えることはない。対象ノードは、様々なやり方で提供キャパシティを決定し得る。ある実施形態においては、プロセッサの負荷がプリセットの限界の範囲内にとどまる限り、提供キャパシティは名目上の値であるとされてよく、例えばプロセッサの負荷が70パーセント未満であれば、名目の提供キャパシティが導かれ得る。またある実施形態においては、提供キャパシティはプロセッサの負荷の線形表現であってもよく、例えばプロセッサの負荷が10パーセントであるときには提供キャパシティは90パーセントとなり、又はプロセッサの負荷が60パーセントであるときには提供キャパシティは40パーセントとなる。提供キャパシティは、処理の要求で起こり得る急上昇からそのノードを保護するため、対象ノードの実際の処理キャパシティよりも低い値を表してもよい。実際の処理キャパシティと提供キャパシティとの間の非線形な関係を含む他の変化も、本発明から逸脱することなく使用されてもよい。

30

## 【0022】

ステップ120において、対象ノードはノードの1つ以上のインターフェース上で第1の信号、例えばHELLOメッセージを送信する。HELLOメッセージは、対象ノードのID(Identity)を好適に含むが、1つの対象ノードしかその処理キャパシティに関する

40

50

情報を発信しない場合には当該 ID は省略されてもよい。HELLOメッセージは、対象ノードの任意の数のピアノードに向けて送信され、対象ノードのハートビートとして使用される。以下に詳述されるように、シーケンス 100 は、好適に一定のレートである第 1 のレート、又は基本レートで HELLOメッセージが確実に送信されるようにする手法で継続的に繰り返される。その後対象ノードは、ステップ 140 と 150 と 160 とを含むループ 130 において、複数の第 2 の信号、例えば ALIVE メッセージを送信する。ALIVE メッセージも、対象ノードの ID を好適に含む。ステップ 150 において ALIVE メッセージは送信され、対象ノードの同じインターフェース上で全てのピアノードに向けても送信される。提供キャパシティがない場合 (OC は 0 に等しい) には、もちろんステップ 150 において ALIVE 信号は送信されない。ステップ 140 と 160 とにより制御されるループ 130 における繰り返しは、各 HELLO メッセージに続いて ALIVE メッセージが確実に OC の回数 (OC times) 送信されるようにする。その結果、ALIVE メッセージは、提供キャパシティ値の関数である第 2 のレートで送信される。例えば、ALIVE メッセージのレートは、提供キャパシティ値により乗じられる基本レートに等しくてもよい。ループ 130 が完了すると、シーケンス 100 は代わりにステップ 110 又は 120 において継続してもよい。ある実施形態においては、毎回 HELLO メッセージを送信する前に一度、提供キャパシティ値がステップ 110 において決定され得る。またある実施形態においては、対象ノード又はピアノードのアプリケーションに応じて、より少ない頻度で提供キャパシティ値がステップ 110 において決定され得る。シーケンス 100 と同等の、第 2 のレートが提供キャパシティと関連している他のシーケンスを使用して、第 1 及び第 2 のレートで HELLO 及び ALIVE メッセージを送信してもよい。例えば、HELLO メッセージを送信後、ALIVE メッセージの第 1 のインスタンスの前に、提供キャパシティが算出されてもよい。

#### 【0023】

HELLO メッセージを送信する基本レートが一定となるように、シーケンス 100 は一定のレートで好適に実行される。ピアノードが対象ノードの処理キャパシティを HELLO 及び ALIVE メッセージのレートを比較することにより評価できるようにする手段として、ALIVE メッセージのレートは可変である。基本レートがいくらか変化する実施形態において、ピアノードは毎回の HELLO メッセージに続いて受信される ALIVE メッセージの数を比較することによりやはり対象ノードの処理キャパシティを評価し得る。一方、基本レートが実質的に一定である場合、ピアノードは長期間にわたる ALIVE メッセージのレートを HELLO メッセージの固定された基本レートと比較することにより、対象ノードの処理キャパシティの算出結果 (calculations) を有利に平均化してもよい。

#### 【0024】

HELLO 及び ALIVE メッセージの周期性は、それらメッセージを送信し及び受信する様々なノードによりサービス提供されるアプリケーションに従って、ノードの性質に従って、又はノードが接続されている手法に従って、決定され得る。例えば同一のイーサネットリンクに、又は処理ラック (processing rack) 内の同一のバックプレーン上で接続されることにより例えば対象ノードとそのピアノードとが ISO レイヤ 2 レベルでリンクされる場合、HELLO メッセージは例えば毎秒 1 回のレートで送信されてもよく、ALIVE メッセージは、処理キャパシティが名目的であるときには毎秒数回までのレートで送信されてもよい。ノードが ISO レイヤ 3 レベルで接続される場合、並びに HELLO 及び ALIVE メッセージが IP パケット又は ATM フレームとして送信される必要がある場合、HELLO メッセージのレートは数秒毎に 1 回であってもよく、一方 ALIVE メッセージのレートは、処理キャパシティが名目的であるときには毎秒 1 回のオーダであってもよい。1 GHz オーダの処理クロックのスピードを有する同一のパーソナルコンピュータの 2 つ以上のコプロセッサは、毎ミリ秒ほどのオーダで HELLO 及び ALIVE メッセージを送信し得る。あるアプリケーションにおいては、メッセージが送信されるレートはさらにもっと高い又は低くてもよい。

## 【0025】

図1が対象ノードの処理キャパシティに関する情報を発信する一例となる方法を示す一方、図2は、本発明の他の観点に従って、ピアノードにおいて対象ノードの処理キャパシティに関する情報を取得する一例となる方法を示している。シーケンス200のステップは、例えば対象ノードのピアノードにおいて実装されてもよい。これらのステップは、ピアノードにおいて継続的な手法で好適に実行されるが、不定期間隔で、例えばピアノードが対象ノードの処理キャパシティを評価する必要があるときに実行されてもよい。ピアノードが次回のイベントが起こるのを待っているときに、ステップ210において方法が開始する。次回のイベントは、ステップ215において第1のタイプの信号を受信することであってもよく、当該第1の信号は、例えば対象ノードにより送信されるHELLOメッセージである。ステップ220においてピアノードは第1の信号の受信の時間を記憶する(note)。ステップ225において、ピアノードはさらに進むための十分なデータが受信されているか否かを判定する。第1の信号が1回しか受信されていない場合、又はシーケンス200が再開されてから1回しか受信されていない場合、データは不十分であるとみなされ、次回のイベントが期待されるステップ210へ処理は戻る。そうではなく、ステップ215において第1の信号が既に少なくとも2回は受信されている場合、ステップ225においてデータは十分であるとみなされ、第1の信号の到着レートが算出される次のステップ230へ進む。第1の信号が既に複数のインスタンスにおいて受信されている場合、ピアノードは全てのこれらインスタンスをカバーする時間にわたって第1の到着レートを任意に平均化してもよく、又は単純に第1の信号の最後の2つのインスタンスに基いて到着レートを考慮してもよい。第1の到着レートは、対象ノードの処理キャパシティを評価するための基礎として使用されることになるため、原則として一定で稀にしか変化しない。一方、対象ノード又は対象ノードとピアノードとの間の接続リンクが、ダウンしているか、再起動しているか、又はそうでなければそれらの通常の機能を担うことができない場合には、第1の到着レートは変化する可能性がある。ステップ255においてシーケンスは継続し、それについては以下で詳述される。

## 【0026】

ステップ210においてピアノードが待っているときに起こる別の次回のイベントは、ステップ235において第2のタイプの信号を受信することであってもよく、当該第2の信号は、例えば対象ノードにより送信されるALIVEメッセージである。ステップ240においてピアノードは第2の信号の受信の時間を記憶する。ステップ245において、ピアノードはさらに進むための十分なデータが受信されているか否かを判定する。第2の信号が1回しか受信されていない場合、シーケンス200が再開されてから1回しか受信されていない場合、又は設定可能な値よりも少ない数のインスタンスにおいてしか受信されていない場合、データは不十分であるとみなされ、次回のイベントが期待されるステップ210に処理は戻る。そうではなく、ステップ235において第2の信号が既に少なくとも2回受信されている場合、及び好適には第2の信号が設定可能な値に少なくとも等しい回数受信されている場合、ステップ245においてデータは十分であるとみなされ、第2の信号の到着レートが算出される次のステップ250へ進む。ピアノードは、そのような信号の数をカバーする時間にわたって第2の到着レートを好適に平均してもよい。好適な実施形態において、最後の第1の信号が受信されてからの期間にわたる第2の信号の到着レートが算出される。第2の到着レートは、対象ノードの現在の処理キャパシティの指標として使用されることになるため、変化してもよい。ステップ250における算出に続いて、ステップ255においてシーケンスは継続する。

## 【0027】

ステップ230又はステップ250のいずれかに続き得るステップ255において、第1及び第2の信号の到着レートの比率が算出される。第2の信号は、第1の信号と比べてより高い到着レートを通常有していると期待されるため、好適な実施形態は通常の場合において、第2の到着レートを第1の到着レートで除して、1よりも大きい比率を取得する。当業者は、第1のレートの比率を第2のレートで除する別の実施形態が同等の結果をも

たらすことを容易に観察するであろう。もちろん、ステップ 255において、第1及び第2の到着レートのうちの1つしかステップ 230及び250において算出されていない場合、結果として生じる比率はゼロ又は無限大であり得る。そのような結果は、シーケンス 200の文脈において非論理的ではなく、対象ノードの処理キャパシティに関する情報を取得する際に実際に使用され得る。ステップ 260において、ステップ 255において取得される比率がプリセット値と比較される。プリセット値は、ピアノードにおいて前もって設定され、対象ノードが通常の処理キャパシティのレベルである場合は第1及び第2の信号の到着レートの期待される比率に等しい。対象ノードの処理キャパシティは、比較から決定される。例えば、第1の信号の期待されるレートが毎10秒に1回である場合、及び第2の信号の期待されるレートが毎秒1回である場合、プリセット値は10に等しく、当該比率は第2の到着レートを第1の到着レートで除することにより取得される（比率が第1の到着レートを第2の到着レートで除することにより取得される実施形態においては、プリセット値は10分の1（0.1）に等しくなる）。比率がプリセット値の10よりも小さい場合、これは対象ノードが低い処理キャパシティを示すために第2の信号を送信する速度を落としていることを示す。比率がゼロである場合、対象ノードは使用可能な処理キャパシティを有していないとみなされる。10

#### 【0028】

シーケンス 200がごく最近初期化されているとき、特別な場合が起こり得る。ステップ 230において第1の到着レートが算出され、一方でステップ 245において十分なデータが欠如していることにより第2の到着レートが算出できない場合、ステップ 255においてゼロの比率が取得され得る。この場合ピアノードは、対象ノードが使用可能な処理キャパシティを有していないと好適にみなしてよい。対照的にステップ 255において無限大の比率が取得されることは、第1の到着レートがまだ算出されていないことを示し得る。他の変形において、ステップ 225及び245において十分なデータについて検証することなく、ステップ 230及び250において第1及び第2の到着レートをそれぞれ算出することができる。所与のタイプの信号が1回しか受信されていない場合、この信号のタイプについての到着レートは極度に遅いとみなされ、またステップ 255において極値の比率を生じさせるであろう。これらの場合のいずれにおいても、シーケンス 200の継続的な実行により、程なくステップ 225及び245において十分なデータが利用可能となり、ステップ 260において対象ノードの処理キャパシティを適切に決定できることを保証するであろう。20

#### 【0029】

他の場合において、対象ノードに通信の問題があるためステップ 225又は245若しくはその両方において十分なデータが取得されない可能性がある。これにより比率がゼロ又は無限大のいずれに等しくなるとしてもと、これはピアノードに対して対象ノードの処理キャパシティが利用可能でないことを示している。30

#### 【0030】

図3は、本発明の方法の追加的観点のステップを示す。シーケンス 300は、図2のシーケンス 200と並行して実行されてもよい。特に、シーケンス 300は図2のステップ 260に続いて開始してもよく、シーケンス 200の継続中の処理において対象ノードの処理キャパシティが再評価されるときはいつでも実行されてもよい。代わりにシーケンス 300は、不定期間隔で、第1及び第2の信号のレートよりも低いレートで周期的に、又はピアノードの特定の必要性に基づいて必要に応じて、実行されてもよい。40

#### 【0031】

ステップ 260において対象ノードの処理キャパシティが決定された後、ピアノードはさらなるアクションを取り得る。これらアクションのうちのいくつかは補完的であってもよく、ピアノードは、これらアクションのうちのいくつかを他のアクションとは独立してとってもよい。ピアノードは、比率における変化を監視することにより、対象ノードの処理キャパシティにおける変化を監視し得る。ステップ 310において、ステップ 255において取得される比率が、前もって記憶されている比率の値と比較される。ステップ 3150

5において、この比較の結果は3つの異なる値を有し得る。ステップ315における結果が比率の増加を示している場合、ピアノードはステップ320において、対象ノードの処理キャパシティが増加したことを記録(record)し、又は別 の方法でメモリに記憶(take note)する。ステップ315における結果が比率の減少を示している場合、ピアノードはステップ325において、対象ノードの処理キャパシティが減少したことを記録する。ステップ315における結果が比率が変化していないことを示している場合、特定のアクションは取られない。

【0032】

ステップ310～325が実行されるか否かに関わらず、ステップ330においてシーケンスは継続されてよく、ステップ260において決定された対象ノードの処理キャパシティは、予め決定された閾値と比較して評価される。処理キャパシティが閾値よりも低い場合、ステップ335においてピアノードはそのルーティングテーブルから対象ノードを削除してもよい。その結果、ピアノードは対象ノードに向けて信号、メッセージ又は要求を送信することを控えるであろう。もちろん、対象ノードのルーティングテーブルからの削除は、場合によってはトラフィック及びペイロードの交換にのみ適用可能であって、保守(maintenance)シグナリングには適用されなくてもよい。例えば、ピアノードは対象ノードに向けての自身の周期的なHELLO及びALIVE信号の送信を継続してもよい。その代わりに、ピアノードは、そのルーティングテーブルにおいて対象ノードに与えられるコストを、対象ノードに向けてより少ない数の信号、メッセージ又は要求が送信されることを保証するように、より高いコストに調整してもよい。ステップ330において、対象ノードの処理キャパシティが高く又は名目のレベルであるとみなされ得る。例えば、閾値を超える処理キャパシティのレベルは、高いとみなされ得る。代わりに、ステップ255において算出される比率がプリセット値に等しいとわかった場合にのみ、キャパシティは名目上の値であるとされてもよい。処理キャパシティを高い値又は名目上の値とするように決定するためのどのように精緻な基準を使用するとしても、ステップ340において、対象ノードは、ピアノードのルーティングテーブル内に追加され又は維持される。対象ノードの処理キャパシティが高いレベル又は名目のレベルにごく最近戻った場合、ノードはルーティングテーブルに追加される。その代わりに、処理キャパシティが高く又は名目上の値であるとされる場合、ルーティングテーブルにおいて対象ノードに与えられるコストは調整され得る。処理キャパシティがしばらくの間継続的に名目上の値である場合、ノードは既にルーティングテーブル内に存在しており、そこに維持され、ノードに与えられるコストは低い値に維持される。

【0033】

図2のシーケンス200に示されている方法は、対象ノードの処理キャパシティを決定する処理において精度を上げるための追加的観点を含み得る。第1及び第2の信号は、そのインスタンスの全てにおいて、シーケンス番号を伴って送信されてもよい。第1の信号が第1のインスタンスにおいて送信される場合、それは基本シーケンス番号を含む。第1のインスタンスにおいて送信される基本シーケンス番号の実際の値は、多くの実施形態において関連がない。それから第1の信号の次のインスタンスは、式(1)に従ったシーケンス番号を伴う：

【0034】

【数1】

$$SQN_{firstsignal} = F_1(SQN_{previousfirstsignal}) \quad (1)$$

【0035】

10

20

30

40

50

ここで  $F_1$  は、第 1 の信号のシーケンス番号と前回の第 1 の信号のシーケンス番号との間の関係である。

【0036】

最新の第 1 の信号の直後に送信される第 2 の信号の第 1 のインスタンスは、式 (2) に従ったシーケンス番号を伴う：

【0037】

【数 2】

$$SQN_{secondsignal} = F_2(SQN_{latestfirstsignal})$$

10

(2)

【0038】

ここで  $F_2$  は、第 2 の信号のシーケンス番号と最新の第 1 の信号のシーケンス番号との間の関係である。

【0039】

その後次回の第 1 の信号の前に送信される第 2 の信号の他のインスタンスは、式 (3) に従ったシーケンス番号をそれぞれ伴う：

20

【0040】

【数 3】

$$SQN_{secondsignal} = F_3(SQN_{previoussecondsignal})$$

(3)

【0041】

30

ここで  $F_3$  は、第 2 の信号のシーケンス番号と前回の第 2 の信号のシーケンス番号との間の関係である。

【0042】

これらの関数が一義的なシーケンスの計算を可能としている限り、及び対象ノードとピアノードとが同じ関数を使用している限り、第 1 及び第 2 の信号に伴われるシーケンス番号を計算するために、様々な関数  $F_1$ 、 $F_2$ 、及び  $F_3$  の組が使用され得る。

【0043】

関数  $F_1$ 、 $F_2$ 、及び  $F_3$  を使用する単純な一例において、第 1 の信号の第 1 のインスタンスにおいて伴われる基本シーケンス番号は、ゼロに等しい。関数  $F_1$  は、前回の第 1 の信号のシーケンス番号にプリセット値に等しい数を加算し、ここで例えばプリセット値は 10 に等しい。関数  $F_2$  は、最新の第 1 の信号のシーケンス番号に 1 を加算する。関数  $F_3$  は、前回の第 2 の信号のシーケンス番号に 1 を加算する。この例において、第 1 の信号は第 1 のインスタンスにおいて、0 に等しい基本シーケンス番号と共に送信される。一連の第 2 の信号は、それから  $F_2$  を使用して算出される 1 に等しいシーケンス番号と共に、それから  $F_3$  を使用して算出される 2、3、…、10 に等しいシーケンス番号と共に送信される。それから第 1 の信号の次のインスタンスは、 $F_1$  を使用して算出される 10 に等しいシーケンス番号を伴って送信される。

40

【0044】

他の実施形態において、より複雑な関数が使用されてもよい。一例として、 $F_2$  及び  $F_3$  はシーケンス番号に作用する一方向性のハッシュ法の手続きを含んでもよく、一方  $F_1$

50

は、同じ一方向性のハッシュ法をプリセット値に等しい回数シーケンス番号に作用させてよい。

【0045】

図4は、対象ノードの処理キャパシティを決定する処理においてより精度を上げるためのいくつかの例となる観点を示す。シーケンス400及び450は、図2のシーケンス200のステップのうちのいくつかと並行してピアノードにおいて動作し、シーケンス200のオプションとしてのサブルーチンとみなされ得る。サブルーチン400では、図2の前述の説明において示されているように、ステップ215においてピアノードにより第1の信号が受信される。第1の信号は、任意にシーケンス番号を含み得る。そうである場合、ステップ417において次の第2の信号の期待されるシーケンス番号が、関数 $F_2$ を使用して算出される。ステップ419において、サブルーチンは図2におけるステップ215に続くステップ、即ちステップ220に戻る。サブルーチン450では、図2に示されているように、ステップ235において第2の信号がピアノードにより受信される。第2の信号もシーケンス番号を含み得る。ステップ452において、第2の信号に含まれるシーケンス番号が期待されるシーケンス番号に合致するか否かがチェックされる。ある実施形態においては、受信されるシーケンス番号と期待されるシーケンス番号とが等しい場合に、合致しているとされる。またある実施形態においては、受信されるシーケンス番号が期待されるシーケンス番号以上である場合に、合致しているとされ得る。合致している場合には、ステップ454において次の第2の信号に適用可能な別の期待されるシーケンス番号が算出され、ステップ459においてサブルーチンは図2におけるステップ235に続くステップ、即ちステップ240に戻る。ステップ452において第2の信号に含まれるシーケンス番号が期待されるシーケンス番号に合致しないとみなされた場合、ピアノードはこの第2の信号又は別の第2の信号が失われ若しくは遅延していることを検出する。ステップ456において、ピアノードは、キャパシティの問題が起こっていることを検出する。キャパシティの問題は、対象ノードにおける処理キャパシティの問題、又はピアノードと対象ノードとの間の通信リンク上の問題であり得る。ステップ458において、ピアノードは図2のさらなる処理において無視されるべき第2の信号にマークを付ける。それからサブルーチンは、ステップ459において図2のシーケンスに戻る。

【0046】

ある実施形態においては、類似のロジックを使用して次の第1の信号の期待されるシーケンス番号が算出され得る。同等の手法において、次の第1の信号について期待されるシーケンス番号に合致しないシーケンス番号を含む次の第1の信号を受信することは、対象ノードにおける問題又はピアノードと対象ノードとの間の通信リンク上における問題のいずれかを示すであろう。

【0047】

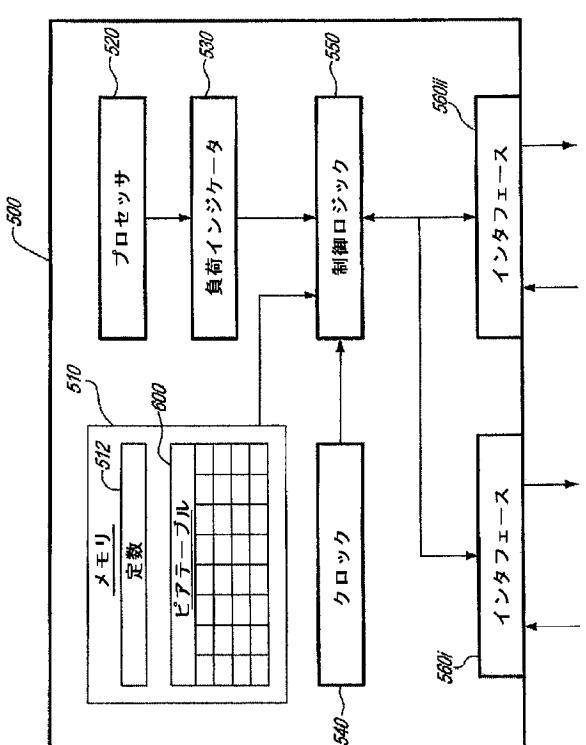

図5は本発明のある観点に係る一例となるノードを示しており、ここで図5を参照しながら一例となるノードの構成を説明する。例となるノード500は、自身の処理キャパシティに関する情報を発信することと、ピアノードの処理キャパシティに関する情報を取得することとの両方を可能とする特徴を含む。他の例となるノードは、これら特徴のいくつか、即ち処理キャパシティの情報の発信又は取得のいずれかのみを可能とすることを含み得ることは理解されるべきである。これら他の例となるノードは、それらが使用されるコンピューティングネットワークアーキテクチャの必要性に従って、例となるノード500の特徴のサブセットを含んでもよい。

【0048】

ノード500は、メモリ510、プロセッサ520、プロセッサの負荷インジケータ530、クロック540、制御ロジック550、及び1つ以上のインターフェース560を含む。インターフェース560の各々は、1つの単独の装置として、又はシグナリング、メッセージ、及びデータを受信（入力）し及び送信（出力）するための異なる装置として実装されてもよい。ノードは、複数のピアノードに向けて接続されており；ピアノードに向けてノードを接続するための手段は、例えはあるピアノードに向けての接続はイーサネット

10

20

30

40

50

リンク上にあってもよく、一方またあるピアノードに向けての接続は非同期転送モード( A T M )リンク上にあってもよいというように、変わってもよい。そのためノード 5 0 0 は、異なるタイプの複数のリンク上で接続するための複数のインターフェース 5 6 0 を含み得る。他の機能をさらに有し得るノードは、そのため当該技術分野において良く知られているようなより多くのコンポーネントを含んでもよい。ある実施形態においては、ノード 5 0 0 は完全なシステム、例えばコンピュータである。またある実施形態においては、ノード 5 0 0 は基本的に、例えばプロセッサ 5 2 0 、負荷インジケータ 5 3 0 、クロック 5 4 0 、及び制御ロジック 5 5 0 を含む単一の処理要素から成る。

#### 【 0 0 4 9 】

メモリ 5 1 0 は、いくつかのその内容のために、例えばランダムアクセスメモリ( R A M )を使用して実装されるテンポラリメモリであってもよい。いくつかの他の観点のために、それは好適に、電気的に消去することができ、再プログラミング可能であり、及び例えばフラッシュメモリ若しくはデータ記憶モジュールとして実装され得る、不揮発性メモリ又は持続性メモリである。メモリ 5 1 0 は、例えば図 2 のシーケンス 2 0 0 におけるステップ 2 6 0 で使用されるノード 5 0 0 において利用可能な処理の最大量を表すプリセット値、及び図 3 のシーケンス 3 0 0 におけるステップ 3 3 0 において使用される予め決定された閾値を含むいくつかの定数 5 1 2 を記憶する。

#### 【 0 0 5 0 】

メモリ 5 1 0 はまた、ピアノードのテーブル 6 0 0 をこれらピアノードの処理キャパシティに関する情報を記憶するために記憶してもよい。図 6 は、本発明のいくつかの観点に係る一例となるピアテーブル 6 0 0 を示す。テーブル 6 0 0 は、複数の行 6 2 0 ~ 6 2 8 を含み、これらはヘッダ行である第 1 の行 6 2 0 を除いて、テーブルを有するノードのピアに関する。テーブルは、ピアのリストにおけるノードの処理キャパシティに関する情報を取得し及び記憶するためにノードにより使用される。ピアテーブル 6 0 0 は、複数の列 6 0 2 ~ 6 1 6 を含み、これらのうちのいくつかはオプションである。第 1 の列 6 0 2 は、ピアの I D P<sub>n</sub> を含む。第 2 の列は、第 1 の信号、例えば H E L L O 信号を受信した最新のインスタンスの時間 T 1<sub>n</sub> を記憶する。第 1 の信号の新たなインスタンスが受信されるたびに、受信の時間を前回の受信の時間 T 1<sub>n</sub> と比較して、列 6 0 6 に記憶される第 1 の信号のレート R 1<sub>n</sub> を計算する。列 6 0 4 において新たな受信の時間は前回の値を上書きする。もちろん、他の同等の実施形態を使用して第 1 の信号の受信のレートを追跡することもできる。ある実施形態においては、列 6 0 6 における第 1 の信号のレートは、単純に第 1 の信号の全ての受信で上書きされる。またある実施形態においては、列 6 0 6 の第 1 の信号のレート R 1<sub>n</sub> は、時間にわたって平均されてもよい。またある実施形態においては、列 6 0 6 に記憶するためのより正確なレート R 1<sub>n</sub> を計算するために、列 6 0 4 において毎行 1 つの T 1<sub>n</sub> の値を記憶するのではなく、第 1 の信号の時間の値の配列を記憶することもできる。列 6 0 8 及び 6 1 0 は同様に、第 2 の信号、例えば A L I V E 信号の受信の時間 T 2<sub>n</sub> 及びレート R 2<sub>n</sub> をそれぞれ記憶する。列 6 1 2 において、2 つの信号のレートの比率が各ピアについて記憶される。例となるピアテーブル 6 0 0 において、比率は第 2 の信号のレート R 2<sub>n</sub> を第 1 の信号のレート R 1<sub>n</sub> で除することにより取得され、1 0 となる比率は名目のレートであることを示す。任意的な列 6 1 4 は、所与の行のピアについてのルーティングのコストを記憶する。コストは数値であり得、低いコストはピアへ向けてのルーティングが好適であることを示す。それは単純に高いか低いかの表示でもあり得る。コストは、ピアへ向かうルーティングが許可されるか否かを示す 2 値表示であってもよい。ある実施形態においては、ルーティングのコストは、ピアテーブル 6 0 0 とは異なる別のルーティングテーブルにおいて記憶されてもよい。別の任意的な列 6 1 6 は、次回の第 2 の信号についての期待されるシーケンス番号( E - S Q N ) E<sub>n</sub> を記憶する。ピアテーブル 6 0 0 は、ノードのピアに関する追加的情報を維持するために他の列( 図示しない ) も含んでもよい。

#### 【 0 0 5 1 】

ピアテーブル 6 0 0 において、行 6 2 2 ~ 6 2 8 上の例となるピア P<sub>1</sub> ~ P<sub>4</sub> は、これ

10

20

30

40

50

ラピアの処理キャパシティに関する様々な状況を示している。行 622 上において、10に等しい比率により示されるように、 $P_1$  の処理キャパシティはその名前のレベルである。トライフィックは  $P_1$  に向けてルーティングされてよく、ルーティングのコストは低い。行 624 上において、 $P_2$  から第1の信号は少なくとも1回受信されたが、第2の信号はまだ受信されていない。 $P_2$  について第2の信号のレートは算出されなくてもよく、従って比率はゼロに等しい。トライフィックは  $P_2$  に向けてルーティングされ得ず、ルーティングのコストは高い。行 626 上において、 $P_3$  から第2の信号しか受信されていない。第1の信号のレート  $R_{1_3}$  は設定されていないため、第1の信号のレートについての空値でレート  $R_{2_3}$  を割った比率は無限大という結果を生じさせる。これもまたルーティングの問題を示しているため、ルーティングのコストは高い。行 628 上において、 $P_4$  についての比率は7に等しく、これは名目の値である10よりも小さい。 $P_4$  の処理キャパシティはいくらか低下しており、そのため中程度のルーティングのコストが割り当てられる。

#### 【0052】

図6においてテーブルの形でピアテーブルの内容が表されているが、その内容がこれに限定されることは留意されるべきである。ピアテーブルは、関連のデータベース、ハードコードされたコンポーネント、マイクロプロセッサ、プログラミングライブラリ等から構成され得る。

#### 【0053】

プロセッサ520は、ノード500において実装される特徴に係るタスクを実行する。負荷インジケータ530は、プロセッサ520上の負荷レベルを継続的に反映する。クロック540は、制御ロジック550におけるシーケンスを周期的に開始する。各シーケンスの始めに、制御ロジック550は負荷インジケータ530からプロセッサの負荷を読み取る。制御ロジック550は、メモリ510における定数512からプリセット値を読み取る。制御ロック550は、第1の信号、例えばHELLOメッセージをシーケンス毎に1回送信するよう1つ以上のインターフェース560に要求する。制御ロジック550は、第1の信号に含めるためのシーケンス番号を任意に生成してもよく、1回のシーケンスの間に送信される第1の信号の1つのインスタンスのシーケンス番号は、先行するシーケンスにおける第1の信号のシーケンス番号に基づいて好適に生成される。それから制御ロジック550は、プロセッサの負荷及びプリセット値からシーケンスの間に送信されるべき第2の信号、例えばALIVEメッセージの数Nを決定する。プロセッサの負荷が低い場合、数Nはプリセット値に等しく設定される。プロセッサの負荷が高いとみなされるべきか低いとみなされるべきかの判定は、メモリ510に記憶されているいくつかの定数512に依存し得る。制御ロジック550は、ALIVEメッセージに含まれるべきシーケンス番号を算出してもよく、連続するシーケンス番号の各々は、前回送信された信号のシーケンス番号に基づいて好適に算出される。制御ロジック550は、決定された数Nの第2の信号を、第1の信号のレートのN倍に相当するレートで送信するよう1つ以上のインターフェース560に要求する。

#### 【0054】

インターフェース560のうちの1つは、現在自身の処理キャパシティに関する情報を発信している対象のピアノード  $P_n$  から一連の第1及び第2の信号を受信し得る。当該インターフェースは、制御ロジック550に情報を提供する。制御ロジック550は、クロック540からタイミング情報を読み取ることにより第1又は第2の信号の受信の時間を読み取り、及びピアテーブル600においてピアノードのID  $P_n$  を含む行上に、第1の信号の時間  $T_{1_n}$  又は第2の信号の時間  $T_{2_n}$  を記憶する。第1又は第2の信号が十分な回数受信されている限り、プロセッサは信号のレート  $R_{1_n}$  と  $R_{2_n}$  とを算出し、及びピアノード  $P_n$  についてそれらを記憶する。両方のレートがピアノード  $P_n$  の処理キャパシティを示す比率を計算し、及びテーブルにおいて列612にそれを記憶する。制御ロジック550は、ピアノード  $P_n$

10

20

30

30

40

50

についてのルーティングのコストの値を任意的に記憶してもよい。第1及び第2の信号は、シーケンス番号を含んでもよい。制御ロジック550は、ピアノード $P_n$ から受信される次の第2の信号に適用可能な期待されるシーケンス番号(E-SQN)を計算し、及びそれを $E_n$ として記憶する。次の第2の信号がピアノード $P_n$ から受信される際、当該次の第2の信号に含まれるシーケンス番号が $E_n$ に適合しない場合、制御ロジック550は当該第2の信号を無視してもよい。

## 【0055】

本発明の方法及びノードの好適な実施形態のいくつかの観点が添付の図面において示され、及び前述の詳細な説明において説明されているが、本発明は開示される実施形態に限定されず、次の特許請求の範囲により説明され及び定義される本発明の精神から逸脱することなく多数の再構成、変更、及び置換が可能であることは理解されるであろう。

10

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

【 义 6 】

---

フロントページの続き

(72)発明者 ロッシ、フレデリック

カナダ ケベック州 エイチ3ティー 1エム3 モントリオール 3793 ラコンベ

審査官 永井 啓司

(56)参考文献 特開2001-075934 (JP, A)

特開2004-171226 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 13/00、

H04L 12/00 - 12/26, 12/50 - 12/955