(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5893351号

(P5893351)

(45) 発行日 平成28年3月23日(2016.3.23)

(24) 登録日 平成28年3月4日(2016.3.4)

(51) Int.Cl.

F 1

H01L 25/10 (2006.01)

H01L 25/10

Z

H01L 25/18 (2006.01)

H01L 25/00

A

H01L 25/00 (2006.01)

請求項の数 2 (全 10 頁)

(21) 出願番号

特願2011-246716 (P2011-246716)

(22) 出願日

平成23年11月10日(2011.11.10)

(65) 公開番号

特開2013-105785 (P2013-105785A)

(43) 公開日

平成25年5月30日(2013.5.30)

審査請求日

平成26年11月10日(2014.11.10)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 池田 真哉

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 小山 和俊

(56) 参考文献 特開2007-189044 (JP, A )

最終頁に続く

(54) 【発明の名称】プリント回路板

## (57) 【特許請求の範囲】

## 【請求項 1】

プリント配線板の第1の表面には、マトリックス状に配置された複数の第1のはんだボール電極を介して第1の半導体パッケージが実装され、プリント配線板の第1の表面の裏面となる第2の表面には、マトリックス状に配置された複数の第2のはんだボール電極を介して第2の半導体パッケージが実装されたプリント回路板において、

前記第1の半導体パッケージに設けられた第1のはんだボール電極の配置はペリフェラル構造であり、前記第2の半導体パッケージは、前記第1の半導体パッケージよりも外形が小さい半導体パッケージであり、

前記プリント配線板の前記第1の半導体パッケージが実装された前記第1の半導体パッケージと対向する領域は、前記第1のはんだボール電極が接合されている第1の領域と、前記第1の領域に囲まれた、前記第1のはんだボール電極が接合されていない第2の領域に分けられており、

前記プリント配線板の前記第2の半導体パッケージが実装された前記第2の半導体パッケージと対向する領域は、前記プリント配線板の前記第2の領域の裏面となる領域内に設けられており、

前記プリント回路板の所定の断面において、前記プリント配線板の前記第1の領域を形成する部分は、前記第1の半導体パッケージとともに、第1の半導体パッケージの両端側が前記第1の半導体パッケージ側に持ち上がるよう反っており、前記プリント配線板の前記第2の領域を形成する部分は、前記第2の半導体パッケージとともに、第2の半導体

10

20

パッケージの両端側が前記第2の半導体パッケージ側に持ち上がるように反っていることを特徴とするプリント回路板。

【請求項2】

プリント配線板の第1の表面には、マトリックス状に配置された複数の第1のはんだボール電極を介して第1の半導体パッケージが実装され、プリント配線板の第1の表面の裏面となる第2の表面には、マトリックス状に配置された複数の第2のはんだボール電極を介して第2の半導体パッケージが実装されたプリント回路板において、

前記第1の半導体パッケージに設けられた第1のはんだボール電極の配置はペリフェラル構造であり、

前記第2の半導体パッケージは、前記第1の半導体パッケージよりも外形が小さい半導体パッケージであり、

前記プリント配線板の前記第1の半導体パッケージが実装された前記第1の半導体パッケージと対向する領域は、前記第1のはんだボール電極が接合されている第1の領域と、前記第1の領域に囲まれた、前記第1のはんだボール電極が接合されていない第2の領域に分けられており、

前記プリント配線板の前記第2の半導体パッケージが実装された前記第2のはんだボール電極が形成されている領域は、前記プリント配線板の前記第2の領域の裏面となる領域内に設けられており、

前記プリント回路板の所定の断面において、前記プリント配線板の前記第1の領域を形成する部分は、前記第1の半導体パッケージとともに、第1の半導体パッケージの両端側が前記第1の半導体パッケージ側に持ち上がるように反っており、前記プリント配線板の前記第2の領域を形成する部分は、前記第2の半導体パッケージとともに、第2の半導体パッケージの両端側が前記第2の半導体パッケージ側に持ち上がるように反っていることを特徴とするプリント回路板。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プリント配線板に半導体パッケージを実装したプリント回路板に関する。特に、プリント配線板の表裏の面に半導体パッケージを対向するように実装した、高密度な部品配置を可能にするプリント回路板に関する。

【背景技術】

【0002】

近年、携帯電話やビデオカメラのような電子機器は、急速に小型化が進んでおり、電子機器に内蔵されるプリント回路板やそれに実装される電子部品は、高機能化及び小型化を余儀なくされている。

【0003】

電子部品では、この要求に対応するために、外周にリード端子を設けたQFP ( Q u a d F l a t P a c k a g e ) と呼ばれる電子部品から、電極を電子部品の裏面にマトリクス状に配置して多ピン化及び小型化した構造へ変化している。このような電子部品としては、ボール電極を用いたBGA ( B a l l G r i d A r r a y ) やCSP ( C h i p S i z e P a c k a g e ) と呼ばれる半導体パッケージが良く知られている。また、プリント回路板では、小型化の要求に対応するために、これらの半導体パッケージをプリント配線板の両面に実装することで小型化を実現している。

【0004】

しかしながら半導体パッケージは、電子機器の電源を入れることにより内部に搭載している半導体素子が発熱する。半導体素子の発熱により、半導体パッケージおよび半導体パッケージを実装しているプリント配線板は膨張し変形する。

【0005】

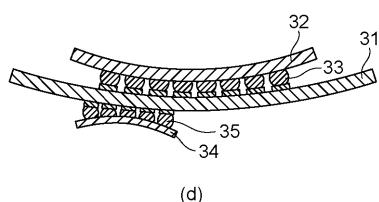

半導体パッケージをプリント配線板の一方の表面にのみ実装したプリント回路板を図6(a)に示す。図6(a)において、21はプリント配線板、22は半導体パッケージ、

10

20

30

40

50

23はプリント配線板21と半導体パッケージ22を接合する接続端子であるはんだボール電極である。この場合、半導体素子の発熱により、半導体パッケージ22とプリント配線板21は膨張する。半導体パッケージ22とプリント配線板21の線膨張係数の差により、はんだボール電極23には応力が加わることとなる。この応力を緩和するため、半導体パッケージおよび半導体パッケージを実装しているプリント配線板は反ることとなる。

#### 【0006】

シリコンからなる半導体素子を実装した半導体パッケージ22の線膨張係数は、ガラスエポキシ樹脂等からなるプリント配線板21に比べて小さい。従って、図6(a)に示したように、半導体パッケージ22およびそれが実装されているプリント配線板21は、共に両端が上側に持ち上がるよう反る(上側に反る)こととなる。

10

#### 【0007】

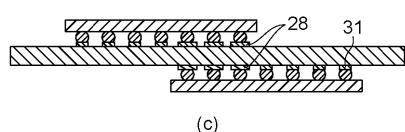

これに対して、2つの同じ半導体パッケージをプリント配線板の両面に対向するように実装したプリント回路板の断面図を図6(b)に示す。図6(b)において、24はプリント配線板、25と26は半導体パッケージ、27はプリント配線板24とそれぞれの半導体パッケージを接合するはんだボール電極である。この場合、半導体パッケージの内部に搭載している半導体素子の発熱により、半導体パッケージ25と26とプリント配線板24は膨張する。半導体パッケージ25、26とプリント配線板24の線膨張係数の差により、はんだボール電極27に応力が加わることとなる。これにより半導体パッケージ25は上側に反り、半導体パッケージ26は下側に反る。しかしながら、プリント配線板24の表裏面から均等に応力が加わった場合、プリント配線板24は反ることができない。従って、ボール電極27に加わった応力は緩和されず、ボール電極27に溜まつたままとなり、ボール電極27の接合信頼性は著しく低下する。

20

#### 【0008】

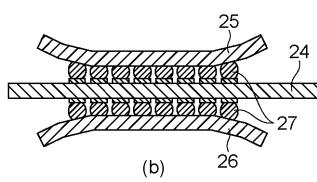

このような状況から、プリント回路板の表裏の面に半導体パッケージを実装する場合、特許文献1に示すように、半導体パッケージがプリント配線板の表裏の面で対向することを避けたプリント回路設計が多用されている(図6(c))。また特許文献1にでは、接続端子の接合寿命を延ばす方法として、表裏の面で対向する接続パッド28の面積を、対向しない接続パッド29の面積よりも大きくすることで、接続端子の接合強度を上昇させ、接合寿命の低下を防ぐことが記載されている。

30

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

#### 【特許文献1】特開2004-273617

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

しかしながら、電子機器は小型化とともに使用する信号の高周波化も図られている。そのため、プリント配線板の表裏の面に実装する半導体パッケージを距離は、極力近くに実装することが要求されている。すなわち、信号の高周波化に伴い、配線の長さによる信号品質の低下が懸念されるため、表裏面の半導体パッケージの距離が近くすることで、半導体パッケージ間を接続する配線を短くし、伝搬する信号の品質を保つことが必要となる。従って、プリント配線板の表裏の面で対向しないように半導体パッケージを配置したり、特許文献1に示すように一部のみを対向することは、信号品質を保つためには、必須の構成となってきたている。

40

#### 【0011】

近年プリント回路板には、従来に比べて極端に大きさの小さいBGAタイプの半導体パッケージが使用されるようになってきている。小型の半導体パッケージは、大型の半導体パッケージと比べて、はんだボール電極の径や接続パッドの面積が小さく、またははんだボール電極の数も少ないため、プリント配線板との接合強度が低くなる。さらに、大型の半導体パッケージに比べて基板の厚さも薄くなるため、半導体パッケージ自体の剛性も低く

50

なる。

#### 【0012】

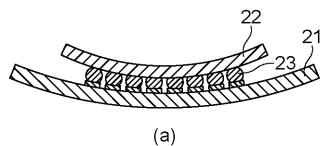

このような小型の半導体パッケージと通常の半導体パッケージとを、プリント配線板の両面に対向するように実装した場合を、図6(d)に示す。図6(d)において、31はプリント配線板、32は通常の半導体パッケージ、33はプリント配線板と半導体パッケージ32を接合する接続端子であるはんだボール電極である。34は小型の半導体パッケージ、35はプリント配線板31と半導体パッケージ34を接合する接続端子であるはんだボール電極である。図6(d)から分かるように、プリント配線板は両端が上になるよう<sup>10</sup>に反っている[上側に反っている]が、小型のプリント配線板34は、両端が下になるよう<sup>10</sup>に反る(下側に反る)ため、ボール電極35には大きな応力が溜まることとなる。従って、図6(d)に示した小型の半導体パッケージが通常の半導体パッケージの裏面に実装した場合、小型の半導体パッケージの接合信頼性が低下し、接合寿命が短くなるという課題があった。

#### 【課題を解決するための手段】

#### 【0013】

前記課題を解決するために本発明では、プリント配線板の第1の表面には、マトリックス状に配置された複数の第1のはんだボール電極を介して第1の半導体パッケージが実装され、プリント配線板の第1の表面の裏面となる第2の表面には、マトリックス状に配置された複数の第2のはんだボール電極を介して第2の半導体パッケージが実装されたプリント回路板において、前記第1の半導体パッケージに設けられた第1のはんだボール電極の配置はペリフェラル構造であり、前記第2の半導体パッケージは、前記第1の半導体パッケージよりも外形が小さい半導体パッケージであり、前記プリント配線板の前記第1の半導体パッケージが実装された前記第1の半導体パッケージと対向する領域は、前記第1のはんだボール電極が接合されている第1の領域と、前記第1の領域に囲まれた、前記第1のはんだボール電極が接合されていない領域と対向する第2の領域に分けられており、前記プリント配線板の前記第2の半導体パッケージが実装された前記第2の半導体パッケージと対向する領域は、前記プリント配線板の前記第2の領域の裏面となる領域内に設けられており、前記プリント回路板の所定の断面において、前記プリント配線板の前記第1の領域を形成する部分は、前記第1の半導体パッケージとともに、第1の半導体パッケージの両端側が前記第1の半導体パッケージ側に持ち上がるよう<sup>20</sup>に反っており、前記プリント配線板の前記第2の領域を形成する部分は、前記第2の半導体パッケージとともに、第2の半導体パッケージの両端側が前記第2の半導体パッケージ側に持ち上がるよう<sup>30</sup>に反っているプリント回路板を提供している。

#### 【発明の効果】

#### 【0014】

本発明によれば、半導体パッケージの接合寿命を低下させずに、プリント回路板の表裏の面で半導体パッケージを対向するように実装した高密度な部品配置が可能となる。

#### 【図面の簡単な説明】

#### 【0015】

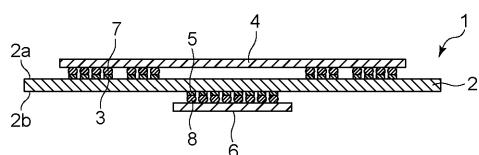

【図1】第1の実施形態におけるプリント回路板の断面図

40

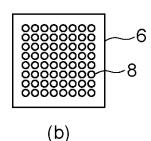

【図2】第1、第2の半導体パッケージの平面図

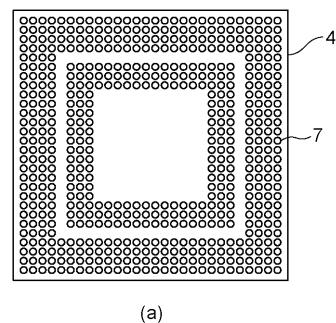

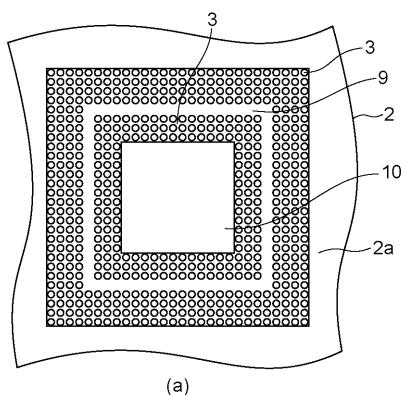

【図3】第1の実施形態におけるプリント配線板の第1、第2の面の平面図

【図4】第1の実施形態におけるプリント回路板の熱変形が生じた様子を示す断面図

【図5】比較例1におけるプリント回路板の断面図と平面図

【図6】従来のプリント回路板断面図

#### 【発明を実施するための形態】

#### 【0016】

(第1の実施の形態)

本発明の第1の実施の形態を、図1乃至図4を参照して説明する。

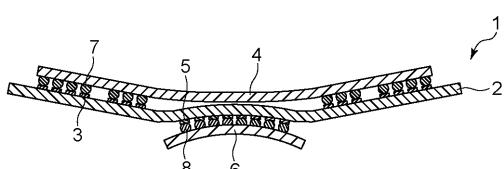

#### 【0017】

50

図1は第1の実施形態におけるプリント回路板1の断面図である。プリント回路板1は、プリント配線板2の第1の表面2aに第1の半導体パッケージ4が実装され、プリント配線板2の第1の表面2aとの裏面となる第2の表面2bに第2の半導体パッケージ6が実装されている。

#### 【0018】

第1の半導体パッケージ4は不図示の半導体素子を搭載しており、はんだボール電極7により、プリント配線板2に形成された第1の接続パッド3に実装されている。また第2の半導体パッケージ6は不図示の半導体素子を搭載しており、はんだボール電極8により、プリント配線板2の第2の接続パッド5に実装されている。

#### 【0019】

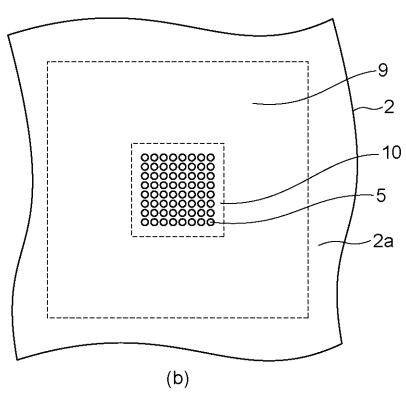

図2(a)は、第1の半導体パッケージ4の下面(プリント配線板2と対向する面)の平面図である。図中7は第1の半導体パッケージ4に設けられた複数のはんだボール電極である。図2(b)は、第2の半導体パッケージ6の上面(プリント配線板2と対向する面)の平面図である。8は第2の半導体パッケージ6に設けられた複数のはんだボール電極である。

#### 【0020】

図3(a)は、プリント配線板2の第1の半導体パッケージ4を実装する第1の表面2aの平面図である。3は第1の半導体パッケージ4のはんだボール電極7と接合される複数の接続パッドである。図3(a)に示すように、第1の面2aの第1の半導体パッケージと対向する領域には、中央部に第1の接続パッド3が設けられていない第2の領域10が形成されており、第2の領域10の周囲には、第1の接続パッド3が設けられた第1の領域9が形成されている。

#### 【0021】

図3(b)は、プリント配線板2の第2の半導体パッケージ6を実装する第2の表面2bの平面図である。5は第1の半導体パッケージ6のはんだボール電極8と接合される複数の接続パッドである。図3(b)において、第2の半導体パッケージと対向する領域は、図3(a)における第1の接続パッド3が設けられていない第2の領域10の、裏面となる領域内に形成されている。なお図3(b)において、理解を容易にするため、図3(a)に示した第1の領域9と第2の領域10と対向する領域を点線で示している。

#### 【0022】

図4は図1に示したプリント回路板1が、半導体パッケージ4と6に搭載された半導体素子の発熱により変形した状態を示す断面図である。プリント配線板2と第1の半導体パッケージ4は、半導体素子の発熱により膨張する。この時、シリコンからなる半導体素子を実装した第1の半導体パッケージ4の線膨張係数は、ガラスエポキシ樹脂等からなるプリント配線板2に比べて小さいため、プリント配線板2と第1の半導体パッケージ4は、両端が上側に持ち上がるよう反ろうとする。この時、はんだボール電極7とプリント配線板2を介して対向する位置には、はんだボール電極8は存在しない。従って前述の図6(a)と同様に、プリント配線板2と第1の半導体パッケージ4は、図4に示すように両端が上側に持ち上がるよう(上側に)反ることとなる。

#### 【0023】

一方、第2の半導体パッケージ6も、半導体素子の発熱により膨張する。シリコンからなる半導体素子を実装した第2の半導体パッケージ6の線膨張係数は、第1の半導体パッケージ4と同様に、プリント配線板2に比べて小さいため、プリント配線板2と第2の半導体パッケージ6は、両端が下側に下がるよう反ろうとする。この時、はんだボール電極8とプリント配線板2を介して対向する位置には、はんだボール電極7は存在しない。従って、プリント配線板2と第2の半導体パッケージ6は、図4に示すように両端が下側に下がるように反る(下側に反る)こととなる。

#### 【0024】

これは、ガラスエポキシ樹脂等からなるプリント配線板2は、第1の半導体パッケージ4、第2の半導体パッケージ6に比べて変形しやすいため、図4に示すような複雑な変形

10

20

30

40

50

も可能となる。すなわち、プリント配線板2の外側領域である第1の領域9においては、プリント配線板2は、第1の半導体パッケージ4とともに変形し、プリント配線板2の内側領域である第2の領域10においては、プリント配線板2は、第2の半導体パッケージ6とともに変形することとなる。

#### 【0025】

本実施の形態では、第1の半導体パッケージ4を実装する第1の領域9と、第2の半導体パッケージ6を実装する第2の領域10の各領域を分離している。これにより、半導体パッケージの反る方向が逆になる形態であっても、それぞれに半導体パッケージを接合するはんだボール電極に加わる応力を十分に開放し、接合信頼性を高め接合寿命を延ばし、高密度な部品配置を可能としている。10

#### 【0026】

なお、本実施の形態では、第1の半導体パッケージ4を実装する第1の領域9を外側に、第2の半導体パッケージ6を実装する第2の領域10を内側中央に配置したが、本発明にそれに限られるものではない。第2の領域10は、必ずしも第1の領域9の内側中央部に設ける必要はない。ただし、内側中央部に設けることにより、それぞれの半導体パッケージに反りの影響を最も受けない形態とすることができますので最も好適である。

#### 【0027】

なお、本実施の形態では、プリント配線板2の第2の半導体パッケージ6を実装する第2の表面2bにおいて、第2の半導体パッケージと対向する領域は、第1の表面2aの接続パッド3が設けられていない第2の領域10の、裏面となる領域内に形成されている。しかしながら本発明では、必ずしも第2の半導体パッケージと対向する領域全体が、第2の領域10の裏面となる領域内に形成されている必要はない。少なとも第2の半導体パッケージを実装する第2のはんだボール電極8と接合される複数の接続パッド5が、第2の領域10の裏面となる領域内に形成されれば良い。20

#### 【0028】

##### (実施例1)

第1の実施の形態に係る実施例1について説明する。

図1におけるプリント配線板2は、電子機器に内蔵される基板として用いられるもので、外形サイズ $110 \times 50\text{ mm}$ 、厚さ $0.8\text{ mm}$ のガラスエポキシ樹脂からなる8層ビルトアップ基板である。30

#### 【0029】

図2(a)に示したプリント配線板2に実装される第1の半導体パッケージ4は、外形が $13.0 \times 13.0\text{ mm}$ 、厚さは $1.3\text{ mm}$ である。はんだボール電極7の間隔は $0.5\text{ mm}$ 、直径が $0.3\text{ mm}$ 、はんだボール電極総数が320ピンである。また、パッケージ中央部に $6.0 \times 6.0\text{ mm}$ のサイズで、はんだボール電極が配置されていない領域(第2の領域10)を有している。このような構造は一般的にペリフェラル構造と呼ばれる。

#### 【0030】

図2(b)に示した第1の半導体パッケージ4の裏面に実装される第2の半導体パッケージ6は、外形が $5.5 \times 5.5\text{ mm}$ 、厚さが $1.1\text{ mm}$ である。はんだボール電極8の間隔は $0.5\text{ mm}$ 、直径は $0.3\text{ mm}$ 、はんだボール電極総数が64ピンの小型の半導体パッケージである。半導体パッケージ6は、プリント配線板2の第2の領域10に対向する領域内に実装されている。すなわち、第2の領域10に対向する領域内に第2の半導体パッケージ6を接続する接続パッド5全体が入るよう実装されている。40

#### 【0031】

プリント回路板1の各ボール電極の耐久性を測定するため、熱ストレス試験を行った。熱ストレス試験は、チャンバーの内部にプリント回路板1を配置し、-25℃で9分間保持、1分かけて雰囲気を125℃に交換し、125℃で再び9分間保持し、1分かけて雰囲気を-25℃に交換する工程を1サイクルとして行った。実施例1のプリント回路板1は380サイクルで、第2の半導体パッケージ6の角部のはんだボール電極8が破断した50

。破断の検知は、各はんだボール電極の抵抗値をオンラインで計測し、抵抗値が10%以上上昇した場合破断と判断した。

#### 【0032】

通常プリント回路板の熱ストレス試験では、260サイクル～310サイクル以上であれば良品と判断される。従って実施例1の形態は、十分にその条件を満足するものであった。なお、熱ストレス試験の良品判定は、JEITA(電子情報技術産業協会)の報告データ(環境調和型先端実装技術成果報告会2011 鉛フリーはんだの熱疲労寿命予測式について)を考慮した。

#### 【0033】

##### (比較例1)

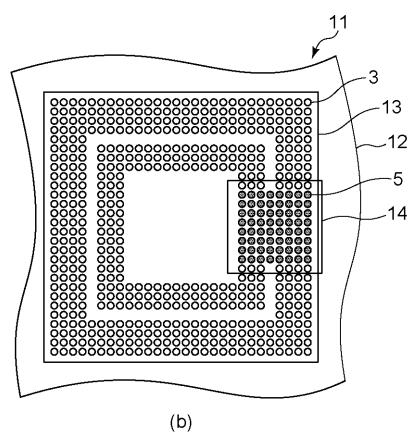

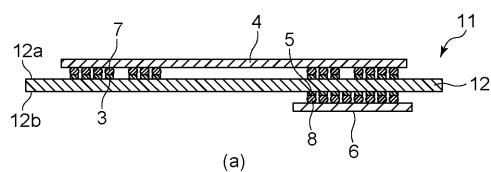

10

図5(a)は比較例1におけるプリント回路板11の断面図である。図5(a)において図1と同じ部材は同じ符号を付している。プリント回路板11は、プリント配線板12の第1の表面12aに第1の半導体パッケージ4が実装され、プリント配線板12の第2の表面12bに第2の半導体パッケージ6が実装されている。第1の半導体パッケージ4は、第1の接続パッド3とはんだボール電極7により、プリント配線板2に実装されている。また第2の半導体パッケージ6は、第2の接続パッド5とはんだボール電極8により、プリント配線板2に実装されている。なお、比較例1において、プリント配線板12、第1の半導体パッケージ4及び第2の半導体パッケージ6の各寸法は、前述の実施例1と同様である。

#### 【0034】

20

図5(b)は、プリント回路板11の接続パッド3と接続パッド5の重なりを第1の半導体パッケージ上面から透視して示した平面図である。12はプリント配線板、13は第1の半導体パッケージの外形、3は第1の接続パッド、14は第2の半導体パッケージの外形、5は第2の接続パッドである。第1の半導体パッケージ4のはんだボール電極7が接合される接続パッド3と、第2の半導体パッケージ6のはんだボール電極8が接合される接続パッド5とは、プリント配線板の表裏の面で対向するように配置されている。第2の接続パッド5の64端子のうち、56端子が第1の接続パッド3と重なっている。

#### 【0035】

比較例1の場合、プリント配線板12は、はんだボール電極7と8に挟まれた領域では、表裏面から拘束されることとなる。そのため、プリント配線板12は、半導体パッケージの伸びと反りに対して追従できないため、応力がかかり耐久性が低下する。

30

#### 【0036】

プリント回路板11の各ボール電極の耐久性を測定するため、実施例1と同様の熱ストレス試験を行った。試験の結果、プリント回路板1は250サイクルで、第2の半導体パッケージ6の角部のはんだボール電極8が破断した。

#### 【符号の説明】

#### 【0037】

- 1、11、15、21、24 プリント回路板

- 2、12、16、22、25、26 プリント配線板

- 3 第1の接続パッド

- 4 第1の半導体パッケージ

- 5 第2の接続パッド

- 6 第2の半導体パッケージ

- 7、8、23、27 はんだボール電極

- 9 第1の領域

- 10 第2の領域

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 01 L 25 / 10

H 01 L 25 / 00

H 01 L 25 / 18