(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

18 May 2006 (18.05.2006)

PCT

(10) International Publication Number

WO 2006/051995 A1

(51) International Patent Classification:

*H01L 29/786 (2006.01) H01L 21/363 (2006.01)*

(72) Inventors; and

(75) Inventors/Applicants (for US only): **SANO, Masafumi** [JP/JP]; c/o CANON KABUSHIKI KAISHA, 3-30-2, Shimomaruko, Ohta-ku, Tokyo, 1468501 (JP). **NAKAGAWA, Katsumi** [JP/JP]; c/o CANON KABUSHIKI KAISHA, 3-30-2, Shimomaruko, Ohta-ku, Tokyo, 1468501 (JP). **HOSONO, Hideo** [JP/JP]; c/o TOKYO INSTITUTE OF TECHNOLOGY, 2-12-1, Ookayama, Meguro-ku, Tokyo, 1528550 (JP). **KAMIYA, Toshio** [JP/JP]; c/o TOKYO INSTITUTE OF TECHNOLOGY, 2-12-1, Ookayama, Meguro-ku, Tokyo, 1528550 (JP). **NOMURA, Kenji** [JP/JP]; c/o TOKYO INSTITUTE OF TECHNOLOGY, 2-12-1, Ookayama, Meguro-ku, Tokyo, 1528550 (JP).

(21) International Application Number:

PCT/JP2005/020982

(74) Agents: **OKABE, Masao** et al.; No. 602, Fuji Bldg., 2-3, Marunouchi 3-chome, Chiyoda-ku, Tokyo 1000005 (JP).

(22) International Filing Date:

9 November 2005 (09.11.2005)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, KE, KG,

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

2004-326683 10 November 2004 (10.11.2004) JP

(71) Applicants (for all designated States except US): **CANON KABUSHIKI KAISHA** [JP/JP]; 3-30-2, Shimomaruko, Ohta-ku, Tokyo, 1468501 (JP). **TOKYO INSTITUTE OF TECHNOLOGY** [JP/JP]; 2-12-1, Ookayama, Meguro-ku, Tokyo, 1528550 (JP).

[Continued on next page]

(54) Title: FIELD EFFECT TRANSISTOR EMPLOYING AN AMORPHOUS OXIDE

(57) Abstract: A novel field-effect transistor is provided which employs an amorphous oxide. In an embodiment of the present invention, the transistor comprises an amorphous oxide layer containing electron carrier at a concentration less than 1 ~10⁻¹⁸/cm³, and the gate-insulating layer is comprised of a first layer being in contact with the amorphous oxide and a second layer different from the first layer.

WO 2006/051995 A1

KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI,

FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

## DESCRIPTION

## FIELD EFFECT TRANSISTOR EMPLOYING AN AMORPHOUS OXIDE

## 5 TECHNICAL FIELD

The present invention relates to a field effect transistor employing an amorphous oxide.

## BACKGROUND ART

10 In recent years, flat panel display (FPD) is commercialized as the results of progress of liquid crystal techniques, electroluminescence (EL), and the related techniques. The FPD is driven by an active matrix circuit comprising a field-effect thin film transistor (TFT) employing an amorphous silicon thin film or polycrystalline silicon thin film as the active layer formed on a glass substrate.

15 For smaller thickness, lighter weight, and higher impact strength of the FPD, use of a lightweight and a flexible resin substrate is investigated in place of the glass substrate. However, the transistor employing the silicon thin film cannot be directly formed on a less heat-resistant resin substrate, since the production of 20 the silicon thin film transistor requires a relatively high-temperature in the process,

25 Therefore, for the TFT, use of an oxide

semiconductor thin film such as a ZnO thin film is actively investigated which enables film formation at a lower temperature (Japanese Patent Application Laid-Open No. 2003-298062).

5        However, a transistor has not been obtained which satisfies simultaneously all of the properties of transparency and electric properties of the TFT, properties of the gate-insulating film, prevention of current leakage, and adhesiveness between the active 10 layer and the substrate.

#### DISCLOSURE OF INVENTION

The present invention intends to provide a novel field effect transistor employing an amorphous 15 oxide.

The present invention intends further to obtain a transistor which is excellent in at least one of the properties of transparency and electric properties of the TFT, properties of the gate- 20 insulating film, prevention of current leakage, and adhesiveness between the active layer and the substrate.

According to the first aspect of the present invention, there is provided a field-effect 25 transistor provided with a source electrode, a drain electrode, a gate insulator, a gate electrode, and an active layer:

the active layer being comprised of an amorphous oxide in which an electron carrier concentration is lower than  $10^{18}/\text{cm}^3$ , or an amorphous oxide in which an electron mobility 5 tends to increase with increase of the electron carrier concentration; and

at least one of the source electrode, the drain electrode and the gate electrode is transparent to visible light.

10 The field-effect transistor preferably has a metal wiring connected to at least one of the source electrode, the drain electrode and the gate electrode.

The amorphous oxide is preferably an oxide containing at least one of In, Zn, and Sn, or an 15 oxide containing In, Zn, and Ga.

According to the second aspect of the present invention, there is provided a field-effect transistor provided with a source electrode, a drain electrode, a gate insulator, a gate electrode, and an 20 active layer:

the active layer being comprised of an amorphous oxide in which an electron carrier concentration is less than  $10^{18}/\text{cm}^3$ , or an amorphous oxide in which an electron mobility tends to increase 25 with increase of the electron carrier concentration; and

having a lamination structure comprised of a

first layer in which at least one of the source electrode, the drain electrode and the gate electrode is transparent to visible light, and a second layer composed of a metal, or

5 having a lamination structure comprised of a first layer in which a wiring connected at least one of the source electrode, the drain electrode and the gate electrode is transparent to visible light, and a second layer composed of a metal.

10 According to the third aspect of the present invention, there is provided a field-effect transistor provided with a source electrode, a drain electrode, a gate-insulating film, a gate electrode, and an active layer,

15 wherein the active layer is comprised of an amorphous oxide transparent to visible light, and at least one of the source electrode, the drain electrode, and the gate electrode is transparent to visible light.

20 The transistor is preferably a normally-off type transistor, using the active layer.

A metal wiring is preferably connected to an electrode transparent to light which belongs to the source electrode, the drain electrode or the gate electrode.

25 According to the fourth aspect of the present invention, there is a field-effect transistor

provided with a source electrode, a drain electrode, a gate-insulating film, a gate electrode, and an active layer:

the active layer being comprised of an

5 amorphous oxide in which an electron carrier

concentration is lower than  $10^{18}/\text{cm}^3$ , and the gate-

insulating film is comprised of a first layer being

in contact with the amorphous oxide and a second

layer different from the first layer and is laminated

10 on the first layer.

The first layer is preferably an insulating

layer comprising  $\text{HfO}_2$ ,  $\text{Y}_2\text{O}_3$ , or a mixed crystal

compound containing  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$ .

The amorphous oxide is preferably an oxide

15 containing at least one of In, Zn, and Sn, or an

oxide containing In, Zn, and Ga.

The first layer is preferably an interface

improvement layer for improving an interfacial

property with the active layer, and the second layer

20 is a current leakage prevention layer for preventing

leakage of electric current.

According to the fifth aspect of the present

invention, there is provided a field effect

transistor provided with a source electrode, a drain

25 electrode, a gate insulator, a gate electrode, and an

active layer,

the active layer being comprised of an

amorphous oxide, and the gate insulator is comprised of a first layer being in contact with the amorphous oxide and a second layer different from the first layer and is laminated on the first layer.

5        The amorphous oxide is preferably any one selected from the group consisting of an oxide containing In, Zn and Sn; an oxide containing In and Zn; an oxide containing In and Sn; and an oxide containing In.

10       The transistor is preferably a normally-off type transistor.

According to the sixth aspect of the present invention, there is provided a field-effect transistor provided with a source electrode, a drain electrode, a gate-insulating film, a gate electrode, and an active layer:

the active layer being comprised of an amorphous oxide in which an electron carrier concentration is less than  $10^{18}/\text{cm}^3$ , or an amorphous oxide in which an electron mobility tends to increase with increase of the electron carrier concentration; and

a passivation layer is provided between the active layer and the gate-insulating layer.

25       The amorphous oxide is preferably an oxide containing at least one of In, Zn, and Sn, or an oxide containing In, Zn, and Ga.

The passivation layer is preferably a current-leakage prevention layer for preventing leakage of electric current.

According to the seventh aspect of the present invention, there is provided a field effect transistor provided with a source electrode, a drain electrode, a gate insulator, a gate electrode, and an active layer,

the active layer being comprised of an amorphous oxide; and

a passivation layer being provided between the active layer and the gate insulator.

According to the eighth aspect of the present invention, there is provided a field-effect transistor provided with a source electrode, a drain electrode, a gate-insulating film, a gate electrode, and an active layer on a substrate:

the active layer being comprised of an amorphous oxide in which an electron carrier concentration is less than  $10^{18}/\text{cm}^3$ , or an amorphous oxide in which an electron mobility tends to increase with increase of the electron carrier concentration; and

a surface-coating layer being provided between the active layer and the substrate.

The amorphous oxide is preferably an oxide containing at least one of In, Zn, and Sn, or an

oxide containing In, Zn, and Ga.

The surface-coating layer is preferably an adhesion-improvement layer for improving the adhesiveness between the substrate and the active 5 layer.

According to the ninth aspect of the present invention, there is provided a field effect transistor provided with a source electrode, a drain electrode, a gate insulator, a gate electrode, and an 10 active layer,

the active layer being comprised of an amorphous oxide; and

a surface-coating layer being provided between the active layer and the substrate.

As the results of investigation on the oxide semiconductors by the inventors of the present invention, it was found that the above-mentioned ZnO is formed in a state of a polycrystalline phase, causing scattering of carriers at the interface 20 between the polycrystalline grains to lower the electron mobility. Further it was found that ZnO is liable to cause oxygen defect therein to produce many carrier electrons, which makes difficult to lower the electrical conductivity. Thereby, even when a gate 25 voltage is not applied to the transistor, a large electric current flow is caused between the source terminal and the drain terminal, making impossible

the normally-off state of the TFT and a larger on-off ratio of the transistor.

The inventors of the present invention investigated the amorphous oxide film

5  $Zn_xM_yIn_zO_{(x+3y/2+3z/2)}$  (M: at least one element of Al and Ga) mentioned in Japanese Patent Application Laid-Open No. 2000-044236. This material contains electron carriers at a concentration not less than  $1 \times 10^{18}/cm^3$ , and is suitable as a simple transparent

10 electrode. However, the oxide containing the electron carrier at a concentration of not less than  $1 \times 10^{18}/cm^3$  used in a channel layer of TFT cannot give a sufficient on-off ratio, and is not suitable for the normally-off TFT. Thus a conventional amorphous

15 oxide film cannot provide a film of a carrier concentration of less than  $1 \times 10^{18}/cm^3$ .

The inventors of the present invention prepared a TFT by use of an amorphous oxide of a carrier concentration of less than  $1 \times 10^{18}/cm^3$  as an active

20 layer of a field-effect transistor. The TFT was found to have desired properties and to be useful for an image display apparatus like a light emission apparatus.

Further, the inventors of the present invention

25 investigated a material  $InGaO_3(ZnO)_m$  and the film forming conditions of this material, and found that the carrier concentration of this material can be

controlled to be less than  $1 \times 10^{18}/\text{cm}^3$  by controlling the oxygen atmosphere conditions in the film formation.

According to the present invention, a novel 5 field-effect transistor is provided by using an amorphous oxide as the active layer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

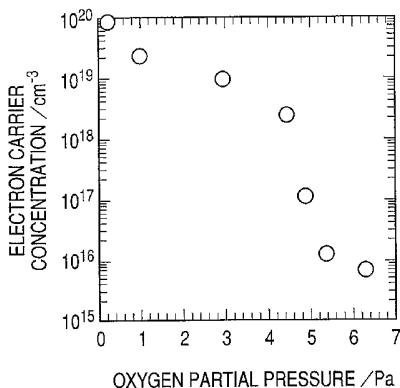

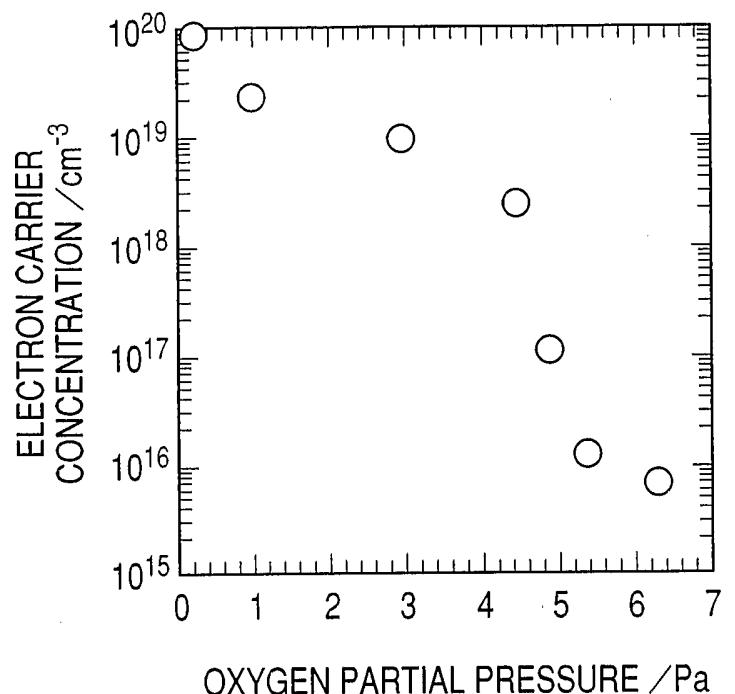

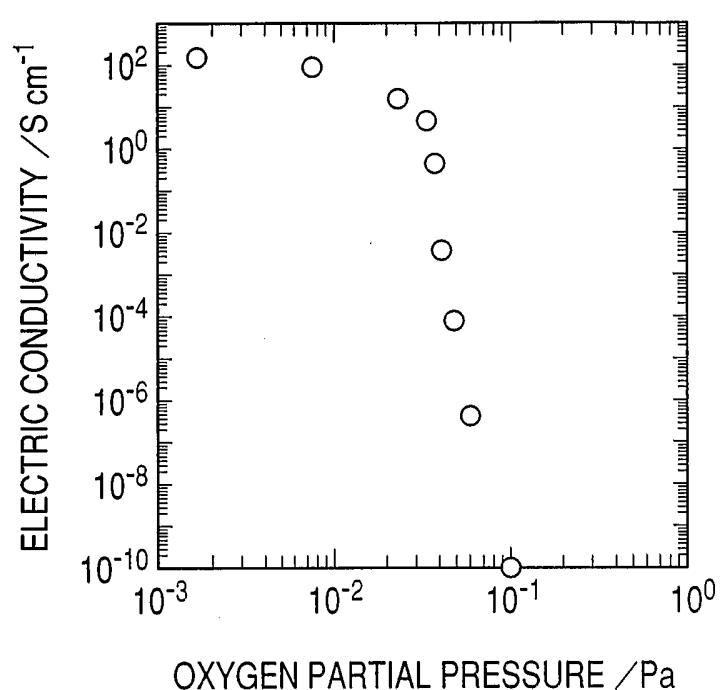

Fig. 1 is a graph showing a dependency of 10 carrier concentration in the In-Ga-Zn-O type amorphous oxide formed by a pulse laser vapor deposition process on the oxygen partial pressure during film formation.

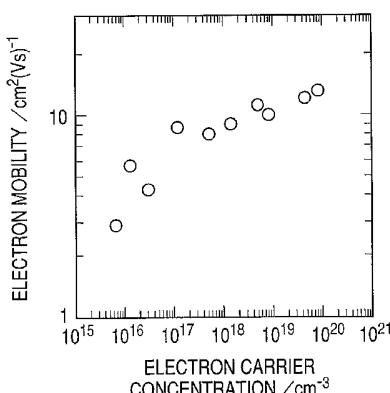

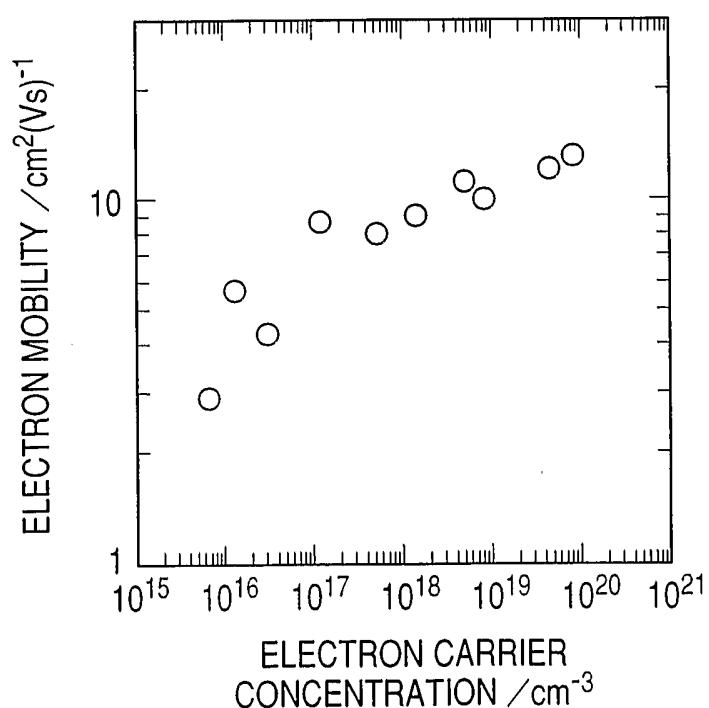

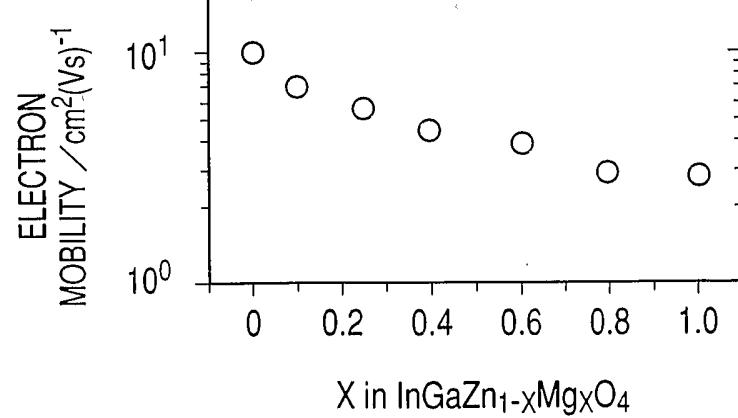

Fig. 2 is a graph dependency of the electron 15 mobility on the carrier concentration of the In-Ga-Zn-O type amorphous oxide formed by a pulse laser vapor deposition process.

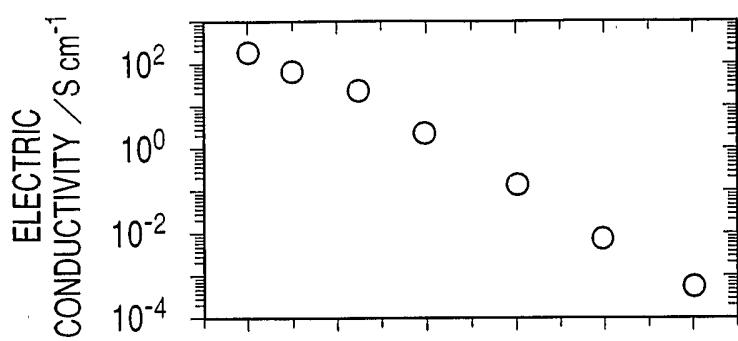

Fig. 3 is a graph showing dependency of the 20 electric conductivity of the In-Ga-Zn-O type amorphous oxide formed by a high-frequency sputtering process employing an argon gas on the oxygen partial pressure during the film formation.

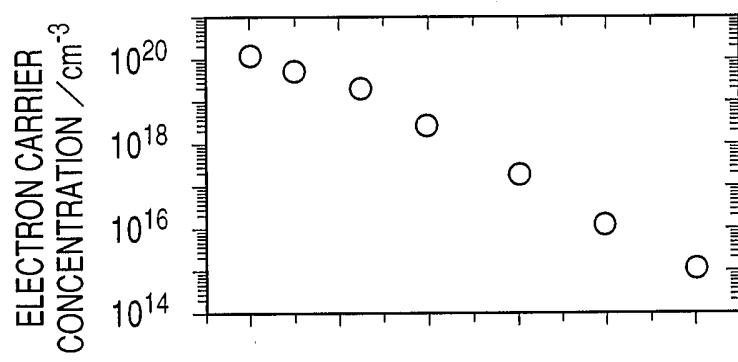

Figs. 4A, 4B, and 4C are graphs showing change 25 of electric conductivity, carrier concentration, and electron mobility depending to the value X of  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_4$  film formed by pulse laser vapor deposition in an atmosphere containing oxygen at a

partial pressure of 0.8 Pa.

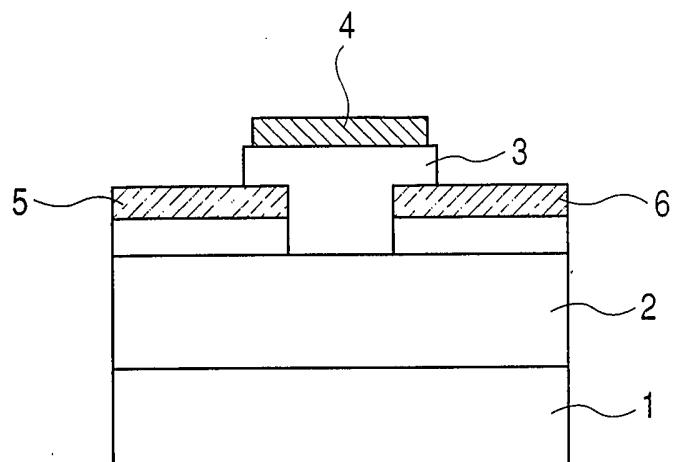

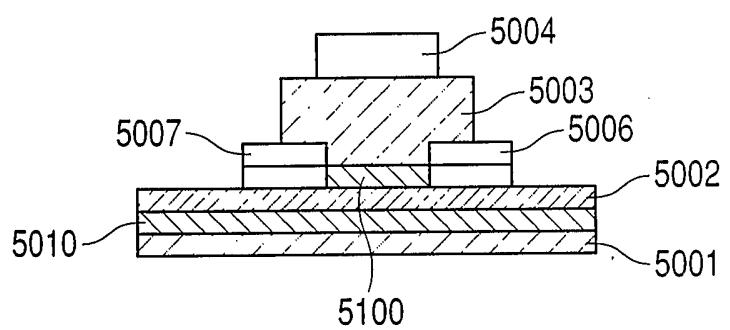

Fig. 5 illustrates schematically a structure of a top gate type TFT element prepared in Examples 6-10.

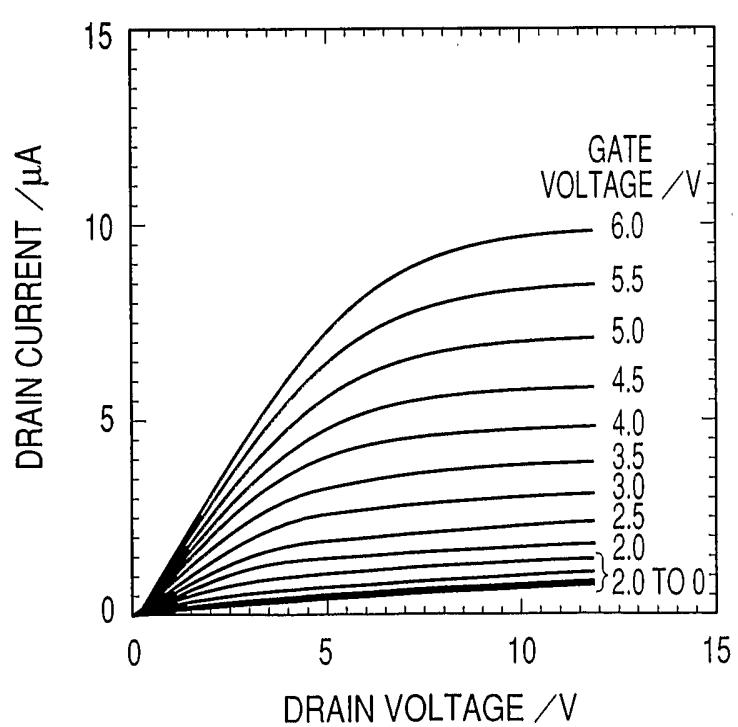

Fig. 6 is a graph showing the electric current-voltage characteristics of a top gate type TFT element employing  $Y_2O_3$  as the gate-insulating film, prepared in Example 6.

Figs. 7A, 7B, 7C, 7D, 7E, and 7F illustrate a first example of the process of production of TFT of the present invention.

Figs. 8A, 8B, 8C, 8D, 8E, and 8F illustrate a second example of the process of production of TFT of the present invention.

Figs. 9G, 9H, 9I, 9J, 9K, and 9L illustrate the second example of the process of production of TFT of the present invention.

Fig. 10 illustrates schematically the structure of the top gate type MISFET element prepared in Example 1.

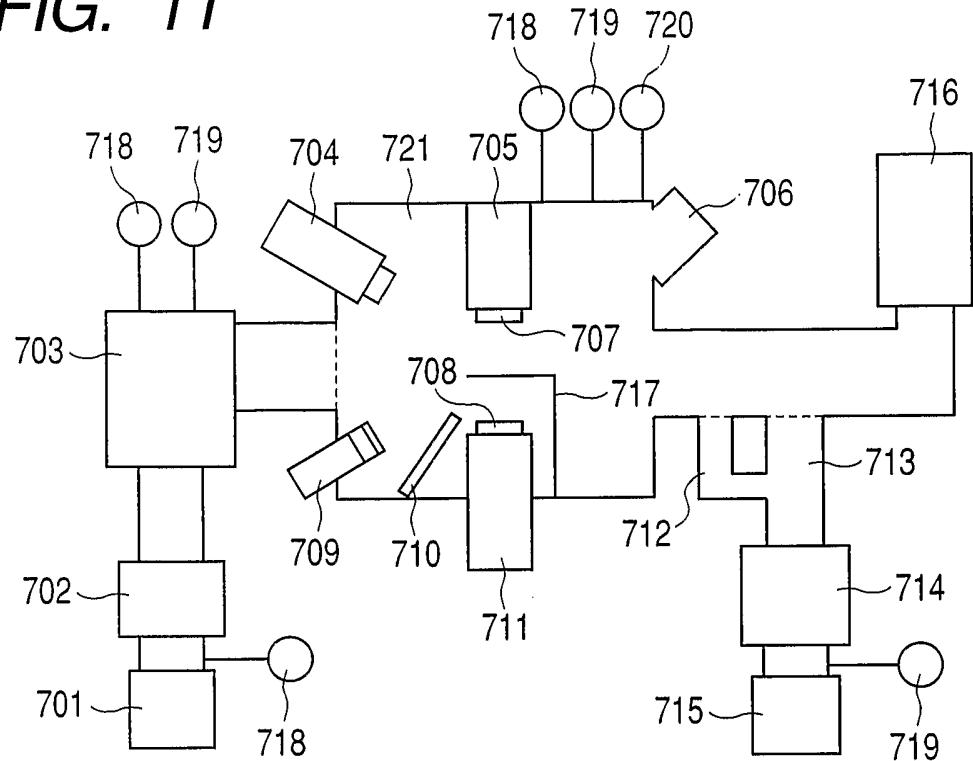

Fig. 11 illustrates schematically an apparatus for film formation by a PLD process.

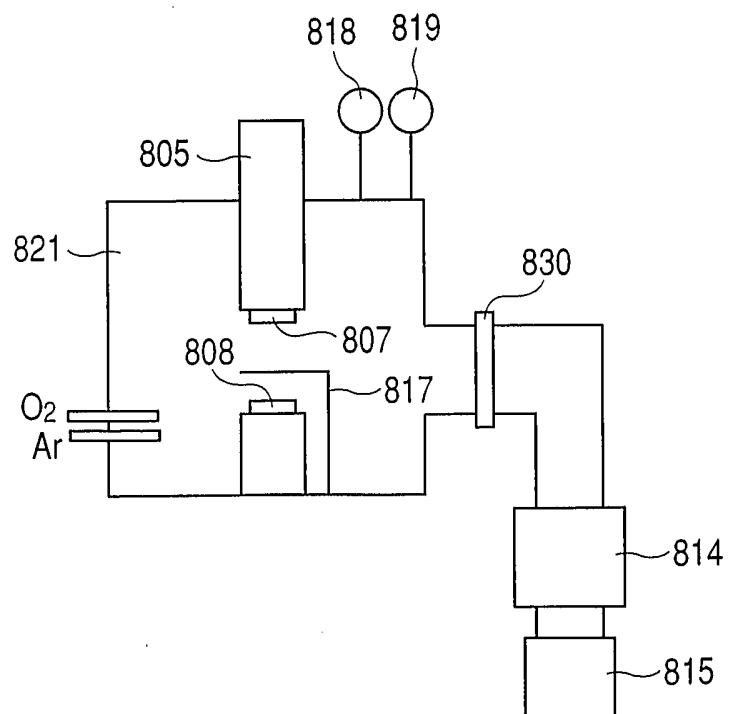

Fig. 12 illustrates schematically an apparatus for film formation by a sputtering process.

## 25 BEST MODES FOR CARRYING OUT THE INVENTION

Firstly the construction of the active layer of the field effect transistor of the present invention

is described.

The inventors of the present invention found that some kinds of amorphous thin films of semi-insulating oxides have characteristics that the 5 electron mobility therein increases with increase in number of conduction electrons, and further found further that a TFT prepared by use of such a film has improved transistor characteristics such as the on-off ratio, the saturation current in a pinch-off 10 state, and the switching rate.

By use of the transparent semi-insulating thin film as the channel layer of a film transistor, the current between the drain terminal and the source terminal in an off-state (no gate voltage applied) 15 can be controlled to be less than 10 microamperes, preferably less than 0.1 microamperes for the electron mobility of higher than  $1 \text{ cm}^2/\text{V.sec}$ , preferably higher than  $5 \text{ cm}^2/\text{V.sec}$  and at the carrier concentration of less than  $1 \times 10^{18}/\text{cm}^3$ , preferably less 20 than  $1 \times 10^{16}/\text{cm}^3$ . Further by use of this thin film, the saturation current after pinch-off can be increased to 10 microampere or more and the on-off ratio can be raised to be higher than  $1 \times 10^3$  for the electron mobility higher than  $1 \text{ cm}^2/\text{V.sec}$ , preferably 25 higher than  $5 \text{ cm}^2/\text{V.sec}$ .

In a pinch-off state of the TFT, a high voltage is being applied to the gate terminal, and electrons

are existing in a high density in the channel. Therefore, according to the present invention, the saturation current can be increased in correspondence with the increase of the electron mobility. Thereby, 5 the nearly all of the transistor characteristics are improved such as increase of the on-off ratio, increase of the saturation current, and increase of the switching rate. In contrast, in a usual compound, the increase in number of electrons decreases the 10 electron mobility owing to collision between the electrons.

The structure of the aforementioned TFT may be a stagger (top gate) structure in which a gate-insulating film and a gate terminal are formed 15 successively on a semiconductor channel layer, or a reversed stagger (bottom gate) structure in which a gate-insulating film and a semiconductor channel layer are formed successively on a gate terminal.

A specific example of the amorphous oxide 20 constituting the active layer is an oxide containing In-Ga-Zn-O, represented by  $\text{InGaO}_3(\text{ZnO})_m$  ( $m$ : a natural number of less than 6) in a crystal state. Another example is an oxide containing In-Ga-Zn-Mg-O, represented by  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  ( $m$ : a natural number 25 of less than 6;  $0 < x \leq 1$ ), containing electron carriers at a concentration of less than  $1 \times 10^{18}/\text{cm}^3$ .

The amorphous oxide films exhibit preferably an

electron mobility of higher than 1 cm<sup>2</sup>/V.sec.

It was found that, by use of the above film as the channel layer, a TFT can be prepared which is normally-off with a gate current of less than 0.1 5 microampere in a transistor off-state, having an on-off ratio of higher than 1×10<sup>3</sup>, and being transparent to visible light and flexible.

In the above transparent film, the electron mobility increases with the increase in number of the 10 conductive electrons. The substrate for forming the transparent film includes glass plates, plastic plates, and plastic films.

In a preferred embodiment employing the above transparent oxide film as the channel layer, a 15 transistor is prepared by forming an electrode layer from at least one of layers constituted of SnO<sub>2</sub>, In<sub>2</sub>O<sub>3</sub>, ITO, Tl<sub>2</sub>O<sub>3</sub>, TlOF, SrTiO<sub>3</sub>, EuO, TiO, or VO as the transparent electrode.

In another preferred embodiment employing the 20 above transparent oxide film as the channel layer, a transistor is prepared by forming an electrode layer from at least one of layers constituted of Au, Ag, Al, or Cu as the electrode.

In still another preferred embodiment employing 25 the above transparent oxide film as the channel layer, a transistor is prepared by forming a gate insulator from at least one of layers constituted of Y<sub>2</sub>O<sub>3</sub> or

$\text{HfO}_2$ , a mixed crystal compound thereof, or  $\text{SiO}_2$ ,  $\text{Si}_3\text{N}_4$ ,  $\text{TiO}_2$ ,  $\text{Ta}_2\text{O}_5$ ,  $\text{PbTiO}_3$ ,  $\text{BaTa}_2\text{O}_6$ ,  $\text{SrTiO}_3$ ,  $\text{MgO}$ , or  $\text{AlN}$ , or an amorphous matter thereof.

In a still another preferred embodiment, the 5 film is formed in an oxygen gas-containing atmosphere without intentional addition of an impurity for increasing the electric resistance.

The process for producing the amorphous oxide film, and the process for producing TFT employing the 10 amorphous oxide are explained more specifically after the description of the first to third embodiments.

The constitutional requirements other than the active layer of the field effect transistor are explained for first to ninth aspects of the present 15 invention by classifying into first to third embodiments.

For the following first to third embodiments, it is preferable to use such an active layer, electrode, gate insulator material and the like as 20 described above. However, the invention of the following embodiments is not limited to the above active layer and the like.

(First Embodiment: Transparent S,D,G Electrodes or Laminated Electrodes)

25 The field-effect transistor of this embodiment belongs to the category of the aforementioned first, second, and third aspects of the invention.

The description "transparent to visible light," signifies a state in which the material is transparent to at least a part of the visible light wavelength region. The transparency signifies a 5 state of not only no light absorption but also penetration of a part of the visible light. In the present invention, the transmittance of visible light is not lower than 40%, more preferably not lower than 60%, still more preferably not lower than 80%.

10 Thus, a highly transparent device is realized by making transparent at least a portion of the electrode or another member constituting the transistor.

Desirably, all of the source electrode, the 15 drain electrode, the gate electrode, and the gate-insulating film are transparent to the visible light.

Examples of electrodes transparent to visible light are those formed from  $\text{SnO}_2$ ,  $\text{In}_2\text{O}_3$ , ITO,  $\text{Ti}_2\text{O}_3$ ,  $\text{TiOF}$ ,  $\text{SrTiO}_3$ ,  $\text{EuO}$ ,  $\text{TiO}$ , or  $\text{VO}$ .

20 Generally, an electrode material transparent to visible light has a low electric conductivity, or a high electric resistance. Therefore, a display device which has wiring formed entirely from such an electrode material will have a high parasitic resistance. Therefore, the wiring is constituted of 25 lamination of a first layer formed from a material transparent to the visible light and a second layer

formed from gold, copper, aluminum, or a like metal, or alloy containing the metal. Specifically, for instance, the transparent first layer is used around the transistor, other portion is formed by lamination 5 of the first layer and the second layer, and the lead-wiring is formed by the second layer having a high electrical conductivity, whereby the parasitic resistance can be decreased. Naturally the aforementioned source electrode, drain electrode, or 10 gate electrode itself may be formed by the lamination structure.

The active layer of the field-effect transistor of the third aspect of the present invention is constituted of the amorphous oxide transparent to 15 visible light as mentioned above. This active layer constitutes preferably a normally-off type transistor.

In view of the invention of the first aspect, according to the third aspect of the present invention, the active layer is formed from an 20 amorphous oxide which contains the carriers at a concentration of not less than  $1 \times 10^{18}/\text{cm}^3$ , not tending to increase the electron mobility with increase of the carrier concentration, and being transparent to visible light, and at least one of the source 25 electrode, drain electrode, and gate electrode is transparent to visible light.

Thus, a device having a broader region of

transparency can be produced by making transparent at least a part of the electrodes or other members constituting the transistor.

(Second Embodiment: Multilayered Gate Insulator

5 The field-effect transistor of this embodiment belongs to the category of the above fourth and fifth aspects of the invention. The active layer of this embodiment is preferably constituted of an transparent amorphous oxide containing at least In-

10 Ga-Zn-O, represented by  $\text{InGaO}_3(\text{ZnO})_m$  (m: a natural number of less than 6) in a crystal state, containing carriers at a concentration of less than  $1 \times 10^{18}/\text{cm}^3$ ; or a transparent amorphous oxide containing In-Ga-Zn-Mg-O, represented by  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  (m: a natural number of less than 6;  $0 < x \leq 1$ ) in a crystal state.

15

The first layer constituting the gate-insulating film is constituted of, for example,  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$ , or a mixed crystal compound thereof. The second layer is constituted, for example, of  $\text{SiO}_2$ ,

20  $\text{Si}_3\text{N}_4$ ,  $\text{TiO}_2$ ,  $\text{Ta}_2\text{O}_5$ ,  $\text{PbTiO}_3$ ,  $\text{BaTa}_2\text{O}_6$ ,  $\text{SrTiO}_3$ ,  $\text{MgO}$ , or  $\text{AlN}$ , or an amorphous structure containing the above substance.

The above materials of the first layer and the second layer are examples, and the materials of the first and the second layers may be used respectively for the second and the first layers.

25

$\text{HfO}_2$  and  $\text{Y}_2\text{O}_3$  are excellent material having a

high current driving ability owing to the high dielectric constant. According to the knowledge of the inventors, use of the  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$  as the gate-insulating film in combination with the channel layer 5 constituted of  $\text{InGaO}_3(\text{ZnO})_m$  or  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  gives a TFT exhibiting a remarkably high mobility and a low threshold. The mechanism thereof is not known, but presumably the  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$  forms an excellent interface with  $\text{InGaO}_3(\text{ZnO})_m$  or  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  to 10 serve to improve the interfacial properties.

The gate-insulating film is further required not to cause gate leakage. The gate leakage is liable to occur at a level-difference portion at the end of source electrode 6 and drain electrode 5 as 15 shown in Fig. 5. Therefore, the thickness of gate-insulating layer 3 is preferably equal to the thickness of source electrode 6 and drain electrode 5, or twice the thickness thereof.

However, since the Hf and Y are expensive, the 20 thick gate-insulating film of  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$  becomes a serious factor of cost increase in production of a large-area TFT panel.

On the other hand,  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$  is capable of forming a satisfactory interface with an amorphous 25 oxide such as  $\text{InGaO}_3(\text{ZnO})_m$  or  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$ . Therefore, such a gate-insulating film is used only around the interface with the channel layer, and

thereon a second gate-insulating layer is formed from an inexpensive material such as  $\text{SiO}_2$  and  $\text{Al}_2\text{O}_3$  in the predetermined thickness. That is, the second gate electrode serves as a current leakage-preventing 5 layer.

In such a manner, the gate leakage can be prevented effectively while the excellent interfacial property of  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$  is sufficiently utilized. Therefore, according to the present invention, even 10 with a smaller amount of Hf or Y, a TFT can be obtained which exhibits a high mobility, a low threshold, and yet has high reliability without gate leakage. Thus the aforementioned constitution is particularly suitable for a large-area TFT panel in 15 view of the high performance and low production cost.

According to the knowledge of the inventors, a problem can arise when an electroconductive layer or the like is formed or etching is conducted on the surface of the channel layer constituted of 20  $\text{InGaO}_3(\text{ZnO})_m$  or  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  before the formation of the gate-insulating layer on the channel layer: the current in the formed TFT is liable to change with time or gate shortage is liable to occur. Although the detailed mechanism therefor is not known, 25 presumably the phenomena may be caused by unexpected diffusion of an impurity in the channel layer, impaired surface flatness, or formation of particles.

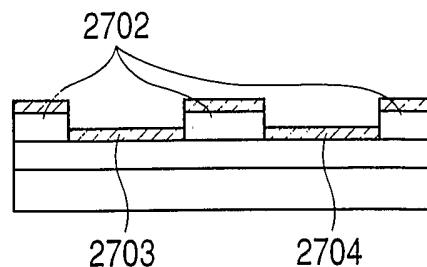

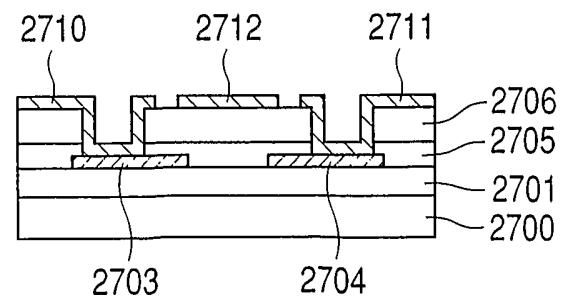

Figs. 7A to 7F show a constitution of a TFT and a process for production thereof to avoid the above problems:

(7A) Channel layer 2701 is formed on substrate 5 2700.

(7B) The surface is covered with mask 2702, and drain electrode 2703 and source electrode 2704 are formed. Mask 2702 is slightly lifted from the surface of channel layer 2701 to prevent contact with 10 the surface of channel layer 2701. Removal of mask 2702 leaves drain electrode 2703 and source electrode 2704.

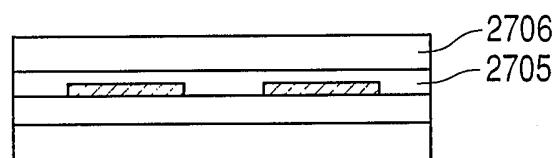

(7C) First gate-insulating film 2705 and second gate-insulating film 2706 are formed. In steps 7A to 15 7C, operations of attaching and detaching of the mask are preferably conducted with interruption of the external air such as in vacuum.

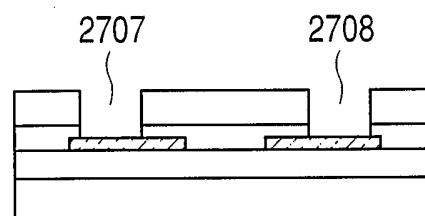

(7D) Through hole 2707 is formed for connection with the drain electrode, and through hole 2708 is 20 formed for connection with the source electrode through gate-insulating films 2705, 2706.

(7E) Conductive layer 2709 is formed.

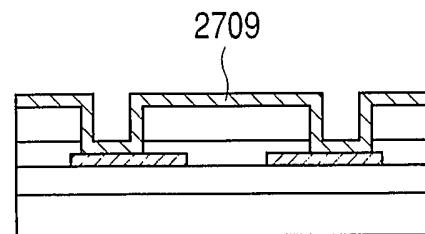

(7F) Conductive film 2709 is patterned to form 25 wiring 2710 for drawing-out from the drain electrode, wiring 2711 for drawing-out from the source electrode, and gate electrode 2712.

In the above steps, the surface of channel

layer 2701 is not damaged by formation of conductive layer and other films and etching, so that a TFT is obtained with high performance and high reliability.

5 Figs. 8A to 8F and Figs. 9G to 9L show a more effective TFT constitution and production thereof for prevention of gate leakage and increasing driving performance of the gate electrode.

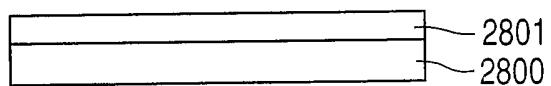

(8A) Channel layer 2801 is formed on substrate 2800.

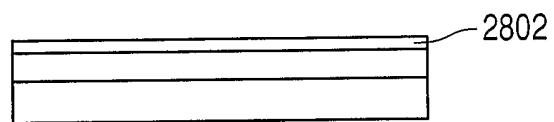

10 (8B) First gate-insulating film 2802 is formed. In steps 8A and 8B, operations are preferably conducted with interruption of the external air; for example, in vacuum.

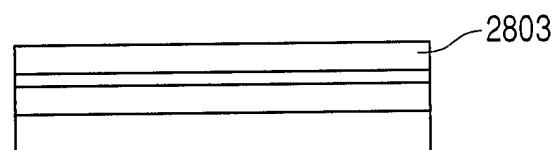

(8C) Photo resist 2803 is applied.

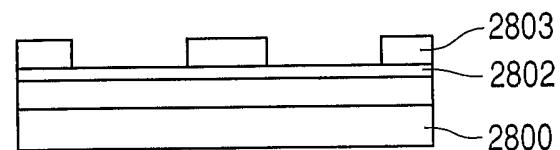

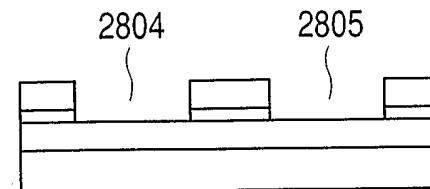

15 (8D) Photo resist 2803 is patterned.

(8E) First gate-insulating film 2802 is etched to form opening 2804 for drain electrode and opening 2805 for source electrode 2805.

(8F) First conductive layer 2806 is formed.

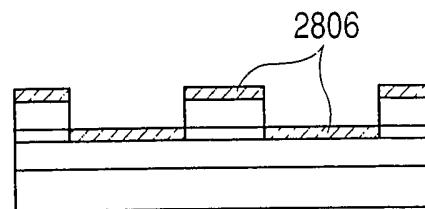

20 (9G) an unnecessary portion of conductive layer 2806 is lifted off in arrow-A direction.

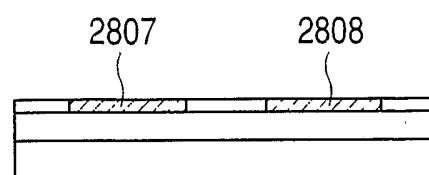

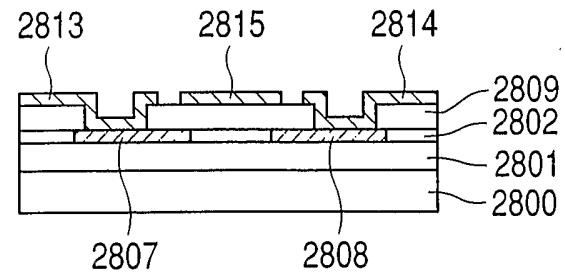

(9H) Drain electrode 2807 and source electrode 2808 are formed.

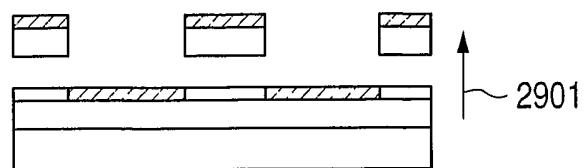

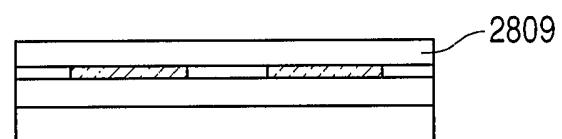

(9I) Second gate-insulating film 2809 is formed.

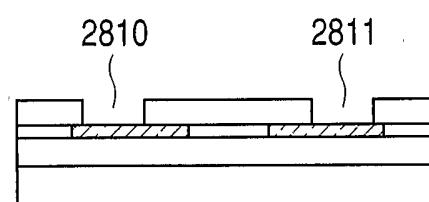

25 (9J) Second gate-insulating film is patterned to form through hole 2810 for connection with the source electrode and through hole 2811 for connection

with the drain electrode.

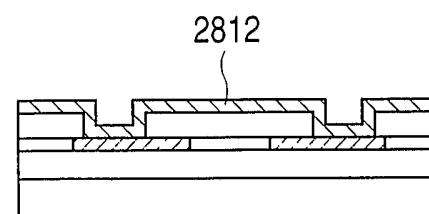

(9K) Second conductive layer 2812 is formed.

(9L) Second conductive film 2812 is patterned to form wiring 2813 for drawing-out from the drain 5 electrode, wiring 2814 for drawing-out from the source electrode, and gate electrode 2815.

In the above process, first gate-insulating layer 2802 covers entirely channel layer 2801, but does not cover drain electrode 2808 and source 10 electrode 2809. Therefore, the heights of the surfaces of first gate-insulating film 2802, drain electrode 2808, and source electrode 2809 are made uniform. Accordingly, the difference in the level of the second gate-insulating film 2809 is little, so 15 that leakage is not caused at the gate, and second gate-insulating film 2809 can be made thin correspondingly to increase the capacity of the gate electrode and to increase the driving performance.

The constitutions and processes shown in Figs. 20 7A to 7F, and Figs. 8A to 8F and Figs. 9G to 9L are expected to be effective for a gate-insulating film constituted of usual insulating material. However, the above constitutions and processes are especially effective for a channel layer employing an 25 aforementioned transparent amorphous oxide containing at least In-Ga-Zn-O, represented by  $\text{InGaO}_3(\text{ZnO})_m$  ( $m$ : a natural number of less than 6) in a crystal state,

containing carriers at a concentration of less than  $1 \times 10^{18}/\text{cm}^3$ , or a transparent amorphous oxide containing In-Ga-Zn-Mg-O, represented by  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  ( $m$ : a natural number of less than 6;  $5 \quad 0 < x \leq 1$ ) in a crystal state; and employing a gate-insulating film constituted of  $\text{HfO}_2$  or  $\text{Y}_2\text{O}_3$ .

Thus, according to the present invention, a TFT can be obtained which exhibits a high mobility and a low threshold, causing less gate leakage, and having 10 stable characteristics. In particular, a large-area TFT panel produced according to the present invention has balanced characteristics with high reliability.

(Third Embodiment: Passivation, Surface-Coating Layer)

15 The field-effect transistor of this embodiment belongs to the category of the above seventh, eighth and ninth aspects of the invention.

The passivation layer in the fifth aspect includes two conceptions. The passivation layer of a 20 first conception is a separate layer provided between the active layer and the gate-insulating layer and constituted of a material different from that of the active layer or the gate-insulating layer. This passivation layer of the first concept is hereinafter referred to as a "passivated layer". The passivated layer is composed, for example, of amorphous silicon oxide, amorphous silicon nitride, titanium oxide, 25

aluminum oxide, magnesium oxide, or the like.

The passivation layer of a second conception is an outermost surface portion of the active layer treated with oxygen plasma. The treatment for 5 formation of the passivation layer of the second conception is hereinafter referred to as "passivation treatment". In this conception, another layer composed of a material different from that of the active layer and the gate-insulating layer is not 10 provided. Naturally, after the passivation treatment, a passivated layer of the first concept composed of amorphous silicon oxide may be further formed.

The passivated layer or the passivation treatment prevents deterioration of the ability of 15 the gate-insulating film: the passivation layer serves as a current leakage-preventing layer.

The surface-coating layer in the field-effect transistor of the sixth aspect of the present invention is formed from amorphous silicon nitride, 20 amorphous silicon oxide, amorphous silicon nitride, titanium oxide, aluminum oxide, magnesium oxide, or a like material. The surface-coating layer may be constituted of the same material as the aforementioned passivation layer or a different 25 material.

The surface-coating layer improves the adhesiveness between the substrate and the active

layer, serving as adhesion-improving layer to prevent film exfoliation, to decrease current leakage, and so forth. Further the surface-coating layer can mitigate projection and depression on the substrate 5 to decrease current leakage and to improve the on-off ratio of the transistor.

In the aforementioned thin film transistor employing a transparent film, the gate-insulating film is preferably constituted of  $\text{Al}_2\text{O}_3$ ,  $\text{Y}_2\text{O}_3$ ,  $\text{HfO}_2$ , or 10 a mixed crystal compound containing two or more thereof. Any defect on the interface between gate-insulating thin film and the thin channel layer decreases the electron mobility and causes hysteresis in transistor characteristics. The current leakage 15 depends largely on the kind of the gate-insulating film. Therefore the gate-insulating film should be selected to be suitable to the channel layer.

The above problems are improved by introduction of an interface passivation layer, enabling use of an 20 insulation layer of a high dielectric constant and to increase the electron mobility. Thus the interfacial passivation layer, which is one aspect of the present invention, enables formation of a TFT in which current leakage and hysteresis are decreased and 25 electron mobility is increased. The TFT can be formed either in a stagger structure or in a reversed stagger structure since the gate-insulating layer and

the channel layer can be formed at a room temperature.

The thin film transistor (TFT) is a three-terminal element having a gate terminal, a source terminal, and a drain terminal. The TFT is an active element which employs a semiconductor film formed on an insulating substrate made of a ceramic material, a glass material, or a plastic material as a channel layer for movement of electrons or holes; and controls the current flowing through the channel layer by applying a voltage to the gate to switch the current between the source terminal and the drain terminal.

The electron carrier concentration can be controlled by controlling the oxygen defect quantity as desired.

In the above first to third embodiments, the quantity of oxygen (oxygen defect quantity) in the transparent oxide film is controlled by forming the film in an atmosphere containing oxygen at a prescribed concentration. Otherwise, the oxygen defect quantity may be controlled (decreased or increased) after the film formation by post treatment of the oxide film in an atmosphere containing oxygen.

For effective control of the oxygen defect quantity, the temperature of the oxygen-containing atmosphere is controlled in a range from 0 to 300°C, preferably from 25 to 250°C, more preferably from 100

to 200°C.

Naturally, film may be formed in an oxygen-containing atmosphere and then post-treated in an oxygen-containing atmosphere. Otherwise the film may

5 be formed without control of the oxygen partial pressure and post-treated in an oxygen-containing atmosphere, insofar as the intended electron carrier concentration (less than  $1\times10^{18}/\text{cm}^3$ ) can be obtained.

The lower limit of the electron carrier 10 concentration in the present invention is, for example,  $1\times10^{14}/\text{cm}^3$ , depending on the kind of the element, circuit, or device employing the produced oxide film.

(Amorphous Oxide)

15 The active layer employed in the above Embodiments 1 to 3 of the invention is explained below.

The electron carrier concentration in the amorphous oxide in the present invention is a value 20 measured at a room temperature. The room temperature is a temperature in the range from 0°C to about 40°C, for example, 25°C. The electron carrier concentration in the amorphous oxide in the present invention need not be less than  $1\times10^{18}/\text{cm}^3$  throughout 25 the entire range from 0 to 40°C. For example, the electron carrier concentration of less than  $10^{18}/\text{cm}^3$  at a temperature of 25°C is acceptable. At a lower

electron carrier concentration, not more than  $1 \times 10^{17}/\text{cm}^3$ , or not more than  $1 \times 10^{16}/\text{cm}^3$ , a normally-off TFT can be produced at a high yield.

In the present specification, the description 5 "less than  $10^{18}/\text{cm}^3$ " means "preferably less than  $1 \times 10^{18}/\text{cm}^3$  and more preferably less than  $1.0 \times 10^{18}/\text{cm}^3$ ".

The electron carrier concentration can be measured by measurement of a Hall Effect.

The amorphous oxide in the present invention is 10 an oxide which exhibits a halo pattern and no characteristic diffraction line in an X-ray diffraction spectrometry.

In the amorphous oxide of the present invention, the lower limit of the electron carrier concentration 15 is, for example,  $1 \times 10^{12}/\text{cm}^3$ , but is not limited insofar as it is applicable as a channel layer of a TFT.

Accordingly, in the present invention, the 20 electron carrier concentration is adjusted by controlling the material, composition ratio, production conditions, and so forth of the amorphous oxide as in the Examples described later to be in the range, for instance, from  $1 \times 10^{12}/\text{cm}^3$  to  $1 \times 10^{18}/\text{cm}^3$ , preferably from  $1 \times 10^{13}/\text{cm}^3$  to  $1 \times 10^{17}/\text{cm}^3$ , more 25 preferably from  $1 \times 10^{15}/\text{cm}^3$  to  $1 \times 10^{16}/\text{cm}^3$ .

The amorphous oxide, other than the InZnGa oxides, can be selected suitably from In oxides,

$In_xZn_{1-x}$  oxides ( $0.2 \leq x \leq 1$ ),  $In_xSn_{1-x}$  oxides ( $0.8 \leq x \leq 1$ ), and  $In_x(Zn, Sn)_{1-x}$  oxides ( $0.15 \leq x \leq 1$ ). The  $In_x(Zn, Sn)_{1-x}$  oxide can also be represented by  $In_x(Zn_ySn_{1-y})_{1-x}$  ( $0 \leq y \leq 1$ ).

5 When the In oxide contains neither Zn nor Sn, the In can be partly substituted by Ga:  $In_xGa_{1-x}$  oxide ( $0 \leq x \leq 1$ ).

An amorphous oxide of an electron carrier concentration of  $1 \times 10^{18}/cm^3$  which is prepared by the inventors of the present invention is described below 10 in detail.

One group of the aforementioned oxides are characteristically constituted of In-Ga-Zn-O, represented by  $InGaO_3(ZnO)_m$  ( $m$ : a natural number of 15 less than 6) in a crystal state, and containing electron carriers at a concentration of less than  $1 \times 10^{18}/cm^3$ .

The other group of the aforementioned oxides are characteristically constituted of In-Ga-Zn-Mg-O, represented by  $InGaO_3(Zn_{1-x}Mg_xO)_m$  ( $m$ : a natural number 20 of less than 6, and  $0 < x \leq 1$ ) in a crystal state, and containing electron carriers at a concentration of less than  $1 \times 10^{18}/cm^3$ .

The film constituted of such an oxide is 25 preferably designed to exhibit preferably an electron mobility of higher than  $1 \text{ cm}^2/\text{V.sec.}$

By use of the above film as the channel layer,

a TFT can be prepared which is normally-off with a gate current of less than 0.1 microampere in a transistor off-state, having an on-off ratio of higher than  $1\times10^3$ , being transparent to visible light 5 and flexible.

In the above film, the electron mobility increases with the increase of the conduction electrons. The substrate for forming the transparent film includes glass plates, plastic plates, and 10 plastic films.

In using the above amorphous oxide film as the channel layer, at least one of layers constituted of  $\text{Al}_2\text{O}_3$ ,  $\text{Y}_2\text{O}_3$  or  $\text{HfO}_2$ , or a mixed crystal compound thereof is useful as the gate-insulating film.

15 In a preferred embodiment, the film is formed in an oxygen gas-containing atmosphere without intentional addition of an impurity for increasing the electric resistance to the amorphous oxide.

The inventors of the present invention found 20 that the amorphous thin films of semi-insulating oxides have characteristics that the electron mobility therein increases with increase in number of conduction electrons, and further found that a TFT prepared by use of the film is improved in transistor 25 characteristics such as the on-off ratio, the saturation current in a pinch-off state, and the switching rate. Thus a normally-off type TFT can be

produced by use of the amorphous oxide.

By use of the amorphous oxide thin film as the channel layer of a film transistor, the electron mobility can be made higher than  $1 \text{ cm}^2/\text{V.sec}$ , 5 preferably higher than  $5 \text{ cm}^2/\text{V.sec}$ . The current between the drain terminal and the source terminal at an off-state (no gate voltage applied) can be controlled to be less than 10 microamperes, preferably less than more than 0.1 microamperes at 10 the carrier concentration of lower than  $1 \times 10^{18}/\text{cm}^3$ , preferably lower than  $1 \times 10^{16}/\text{cm}^3$ . Further by use of this thin film, the saturation current after pinch-off can be raised to 10 microamperes or more and the on-off ratio can be raised to be higher than  $1 \times 10^3$  15 for the electron mobility higher than  $1 \text{ cm}^2/\text{V.sec}$ , preferably higher than  $5 \text{ cm}^2/\text{V.sec}$ .

In a pinch-off state of the TFT, a high voltage is being applied to the gate terminal, and electrons are existing in a high density in the channel.

20 Therefore, according to the present invention, the saturation current can be increased in correspondence with the increase of the electron mobility. Thereby, the transistor characteristics can be improved, such as increase of the on-off ratio, increase of the 25 saturation current, and increase of the switching rate. In contrast, in a usual compound, the increase of electrons decreases the electron mobility owing to

collision between electrons.

The structure of the aforementioned TFT may be a stagger (top gate) structure in which a gate-insulating film and a gate terminal are successively formed on a semiconductor channel layer, or a reversed stagger (bottom gate) structure in which a gate-insulating film and a semiconductor channel layer successively on a gate terminal.

(First Process for Film Formation: PLD Process)

10 The amorphous oxide thin film having the composition  $\text{InGaO}_3(\text{ZnO})_m$  ( $m$ : a natural number of less than 6) in a crystal state is stable up to a high temperature of  $800^\circ\text{C}$  or higher when  $m$  is less than 6, whereas with increase of  $m$ , namely with increase of 15 the ratio of ZnO to  $\text{InGaO}_3$  near to the composition of ZnO, the oxide tends to crystallize. Therefore, the value  $m$  of the oxide is preferably less than 6 for use as the channel layer of the amorphous TFT.

20 The film formation is conducted preferably by a gas phase film formation process by use of a target of a polycrystalline sintered compact having a composition  $\text{InGaO}_3(\text{ZnO})_m$ . Of the gas phase film formation processes, sputtering, and pulse laser vapor deposition are suitable. The sputtering is 25 particularly suitable for the mass-production.

However, in formation of the amorphous film under usual conditions, oxygen defect can occur, so

that the electron carrier concentration of less than  $1 \times 10^{18}/\text{cm}^3$  and electric conductivity of less than  $10 \text{ S/cm}$  cannot be achieved. With such a film, a normally-off transistor cannot be constituted.

5 The inventors of the present invention produced an In-Ga-Zn-O film by a pulse laser vapor deposition by use of the apparatus shown in Fig. 11.

The film-forming was carried out by using such a PLD film-forming apparatus as shown in Fig. 11.

10 In Fig. 11, the numerals indicate the followings: 701, an RP (rotary pump); 702, a TMP (turbo molecular pump); 703, a preliminary chamber; 704, an electron gun for RHEED; 705, a substrate-holding means for rotating and vertically moving the 15 substrate; 706, a laser-introducing window; 707, a substrate; 708, a target; 709, a radical source; 710, a gas inlet; 711, a target-holding means for rotating and vertically moving the target; 712, a by-pass line; 713, a main line; 714, a TMP (turbo molecular 20 pump); 715, an RP (rotary pump); 716, a titanium getter pump; 717, a shutter; 718, an IG (ion manometer); 719, a PG (Pirani gage); 720, a BG (baratron gage); and 721, a growth chamber.

An In-Ga-Zn-O type amorphous oxide 25 semiconductor thin film was deposited on an  $\text{SiO}_2$  glass substrate (Corning Co.: 1737) by a pulse laser vapor deposition employing a KrF excimer laser. As

the pretreatment before the deposition, the substrate was washed ultrasonically for defatting with acetone, ethanol, and ultrapure water each for five minutes, and dried in the air at 100°C.

5        The polycrystalline target was an  $\text{InGaO}_3(\text{ZnO})_4$  sintered compact (size: 20 mm diameter, 5 mm thick), which had been prepared by wet-mixing  $\text{In}_2\text{O}_3$ ,  $\text{Ga}_2\text{O}_3$ , and  $\text{ZnO}$  (each 4N reagent) as the source material (solvent: ethanol), calcining the mixture (1000°C, 2 10 hours), dry-crushing it, and sintering it (1550°C, 2 hours). The target had an electro conductivity of 90 S/cm.

15      The film formation was conducted by controlling the final vacuum of the growth chamber to be  $2 \times 10^{-6}$  Pa, and the oxygen partial pressure during the growth to be 6.5 Pa. The oxygen partial pressure in growth chamber 721 was 6.5 Pa, and the substrate temperature was 25°C. The distance between target 708 and film-holding substrate 707 was 30 mm, the power introduced 20 through introduction window 716 was in the range of 1.5-3 mJ/cm<sup>2</sup>/pulse. The pulse width was 20 nsec, the repeating frequency was 10 Hz, and the irradiation spot size was 1×1 mm square. Under the above conditions, the film was formed at a rate of 7 nm/min.

25      The resulting thin film was examined by small angle X-ray scattered method (SAXS) (thin film method, incidence angle: 0.5°): no clear diffraction peak was

observed. Thus the obtained In-Ga-Zn-O type thin film was judged to be amorphous. From X-ray reflectivity and its pattern analysis, the mean square roughness (Rrms) was found to be about 0.5 nm, 5 and the film thickness to be about 120 nm. From fluorescence X-ray spectrometric analysis (XRF), the metal composition of the film was found to be In:Ga:Zn = 0.98 : 1.02 : 4. The electric conductivity was less than about  $1 \times 10^{-2}$  S/cm. The 10 electron carrier concentration was estimated to be not more than  $1 \times 10^{16}/\text{cm}^3$ . The electron mobility was estimated to be about  $5 \text{ cm}^2/\text{V} \cdot \text{sec}$ . From light absorption spectrum analysis, the optical bandgap energy breadth of the resulting amorphous thin film 15 was estimated to be about 3 eV.

The above results show that the obtained In-Ga-Zn-O type thin film is a transparent flat thin film having an amorphous phase of a composition near to a crystalline  $\text{InGaO}_3(\text{ZnO})_4$ , having less oxygen defect, 20 and having lower electric conductivity.

The above film formation is explained specifically by reference to Fig. 1. Fig. 1 shows dependency of the electron carrier concentration in the formed transparent amorphous oxide thin film on 25 the oxygen partial pressure for the film of a composition of  $\text{InGaO}_3(\text{ZnO})_m$  (m: an integer less than 6) in an assumed crystalline state under the same

film formation conditions as in the above Example.

By formation of the film in an atmosphere having an oxygen partial pressure of higher than 4.5 Pa under the same conditions as in the above Example, 5 the electron carrier concentration could be lowered to less than  $1 \times 10^{18}/\text{cm}^3$  as shown in Fig. 1. In this film formation, the substrate was kept nearly at room temperature without intentional heating. For use of a flexible plastic film as the substrate, the 10 substrate temperature is kept preferably at a temperature lower than 100°C.

The higher oxygen partial pressure enables decrease of the electron carrier concentration. For instance, as shown in Fig. 1, the thin  $\text{InGaO}_3(\text{ZnO})_4$  15 film formed at the substrate temperature of 25°C and the oxygen partial pressure of 5 Pa had a lower electron carrier concentration of  $1 \times 10^{16}/\text{cm}^3$ .

In the obtained thin film, the electron mobility was higher than  $1 \text{ cm}^2/\text{V.sec}$  as shown in Fig. 2. However, the film deposited by the pulse laser 20 vapor deposition at an oxygen partial pressure of higher than 6.5 Pa as in this Example has a rough surface, being not suitable for a channel layer of the TFT.

25 Accordingly, a normally-off type transistor can be constructed by using a transparent thin amorphous oxide represented by  $\text{InGaO}_3(\text{ZnO})_m$  (m: a number less

than 6) in a crystal state formed at an oxygen partial pressure of higher than 4.5 Pa, preferably higher than 5 Pa, but lower than 6.5 Pa by a pulse laser vapor deposition method in the above Example.

5 The above obtained thin film exhibited an electron mobility higher than  $1 \text{ cm}^2/\text{V}$ , and the on-off ratio could be made higher than  $1 \times 10^3$ .

As described above, in formation of an InGaZn oxide film by a PLD method under the conditions shown 10 in this Example, the oxygen partial pressure is controlled in the range preferably from 4.5 Pa to 6.5 Pa.

For achieving the electron carrier concentration of  $1 \times 10^{18}/\text{cm}^3$ , the oxygen partial 15 pressure conditions, the constitution of the film formation apparatus, the kind and composition of the film-forming material should be controlled.

Next, a top-gate type MISFET element as shown in Fig. 5 was produced by forming an amorphous oxide 20 with the aforementioned apparatus at an oxygen partial pressure of 6.5 Pa. Specifically, on glass substrate 1, a semi-insulating amorphous  $\text{InGaO}_3(\text{ZnO})_4$  film of 120 nm thick was formed for use for channel layer 2 by the above method of formation of amorphous 25 thin Ga-Ga-Zn-O film. Further thereon an  $\text{InGaO}_3(\text{ZnO})_4$  film having a higher electro conductivity and a gold film were laminated respectively in a thickness of 30

nm by pulse laser deposition at an oxygen partial pressure of lower than 1 Pa in the chamber. Then drain terminal 5 and source terminal 6 were formed by photolithography and a lift-off method. Finally, a 5  $\text{Y}_2\text{O}_3$  film for gate-insulating film 3 was formed by an electron beam vapor deposition method (thickness: 90 nm, relative dielectric constant: about 15, leak current density:  $1 \times 10^{-3} \text{ A/cm}^2$  at application of 0.5 MV/cm). Thereon, a gold film was formed, and gate 10 terminal 4 was formed by photolithography and lifting-off.

#### Evaluation of Characteristics of MISFET Element

Fig. 6 shows current-voltage characteristics of the MISFET element measured at room temperature. The 15 channel is understood to be an n-type semiconductor from the increase of the drain current  $I_{DS}$  with the increase of the drain voltage  $V_{DS}$ . This is consistent with the fact that an amorphous In-Ga-Zn-O type semiconductor is of an n-type. The  $I_{DS}$  becomes 20 saturated (pinched off) at  $V_{DS}=6\text{V}$ , which is typical behavior of a semiconductor transistor. From examination of the gain characteristics, the threshold value of the gate voltage  $V_{GS}$  under application of  $V_{DS}=4\text{V}$  was found to be about -0.5 V. A 25 current flow of  $I_{DS}=1.0 \times 10^{-5}\text{A}$  was caused at  $V_G=10\text{V}$ . This corresponds to carrier induction by gate bias in the In-Ga-Zn-O type amorphous semiconductor thin film.

The on-off ratio of the transistor was higher than  $1 \times 10^3$ . From the output characteristics, the field effect mobility was calculated to be about 7  $\text{cm}^2(\text{Vs})^{-1}$ . Irradiation of visible light did not 5 change the transistor characteristics of the produced element according to the same measurement.

According to the present invention, a thin film transistor can be produced which has a channel layer containing electron carriers at a lower concentration 10 to achieve higher electric resistance and exhibiting a higher electron mobility.

The above amorphous oxide has excellent characteristics that the electron mobility increases with the increase of the electron carrier 15 concentration, and exhibits degenerate conduction.

In this Example, the thin film was formed on a glass substrate. However, a plastic plate or film is useful as the substrate since the film formation can be conducted at room temperature. Further, the 20 amorphous oxide obtained in this Example, absorbs visible light only little to give transparent flexible TFT.

(Second Process for Film Formation: Sputtering Process (SP Process))

25 Film formation by a high-frequency SP process by use of an argon gas as the atmosphere gas is explained below.

The SP process was conducted by use of the apparatus shown in Fig. 12. In Fig. 12, the numerals indicates the followings: 807, a substrate for film formation; 808, a target; 805, a substrate-holding means equipped with a cooling mechanism; 814, a turbo molecular pump; 815, a rotary pump; 817, a shutter; 818, an ion manometer; 819, a Pirani gage; 821, a growth chamber; and 830, a gate valve.

Substrate 807 for film formation was an  $\text{SiO}_2$  glass substrate (Corning Co.: 1737) which had been washed ultrasonically for defatting with acetone, ethanol, and ultrapure water respectively for 5 minutes, and dried at  $100^\circ\text{C}$  in the air.

The target was a polycrystalline sintered compact having a composition of  $\text{InGaO}_3(\text{ZnO})_4$  (size: 20 nm diameter, 5 mm thick), which had been prepared by wet-mixing  $\text{In}_2\text{O}_3$ ,  $\text{Ga}_2\text{O}_3$ , and  $\text{ZnO}$  (each 4N reagent) as the source material (solvent: ethanol), calcining the mixture ( $1000^\circ\text{C}$ , 2 hours), dry-crushing it, and sintering ( $1550^\circ\text{C}$ , 2 hours). Target 808 had an electro conductivity of 90 S/cm, being semi-insulating.

The final vacuum degree of growth chamber 821 was  $1 \times 10^{-4}$  Torr. During the growth, the total pressure of the oxygen and argon gas was kept constant within the range of 4 to  $0.1 \times 10^{-1}$  Pa. The partial pressure ratio of argon to oxygen was changed

in the range of the oxygen partial pressure from  $1\times10^{-3}$  to  $2\times10^{-1}$  Pa.

The substrate temperature was room temperature. The distance between target 808 and substrate 807 for 5 film formation was 30 mm.

The inputted electric power was RF 180 W, and the film forming rate was 10 nm/min.

The resulting thin film was examined by small angle X-ray scattering method (SAXS) (thin film 10 method, incidence angle:  $0.5^\circ$ ): no clear diffraction peak was observed. Thus the obtained In-Ga-Zn-O type thin film was judged to be amorphous. From X-ray reflectivity and its pattern analysis, the mean square roughness ( $R_{rms}$ ) was found to be about 0.5 nm, 15 and the film thickness to be about 120 nm. From fluorescence X-ray spectrometric analysis (XRF), the metal composition of the film was found to be In:Ga:Zn = 0.98 : 1.02 : 4.

The films were formed at various oxygen partial 20 pressure of the atmosphere, and the resulting amorphous oxide films were measured for electric conductivity. Fig. 3 shows the result.

As shown in Fig. 3, the electric conductivity can be lowered to less than 10 S/cm by conducting the 25 film formation in an atmosphere having an oxygen partial pressure higher than  $3\times10^{-2}$  Pa. The electron carrier number could be decreased by increase of the

oxygen partial pressure.

As shown in Fig.3, for instance, the thin  $\text{InGaO}_3(\text{ZnO})_4$  film formed at the substrate temperature of 25°C and the oxygen partial pressure or  $1 \times 10^{-1}$  Pa had a lower electric conductivity of about  $1 \times 10^{-10}$  S/cm. Further, the thin  $\text{InGaO}_3(\text{ZnO})_4$  film formed at the oxygen partial pressure or  $1 \times 10^{-1}$  Pa had an excessively high electric resistance, having the electric conductivity not measurable. With this film, although the electron mobility was not measurable, the electron mobility was estimated to be about 1  $\text{cm}^2/\text{V.sec}$  by extrapolation from the values of the films of high electron carrier concentration.

Thus, a normally-off transistor having the on-off ratio of higher than  $1 \times 10^3$  could be obtained by use of a transparent thin amorphous oxide film constituted of In-Ga-Zn-O represented in a crystal state by  $\text{InGaO}_3(\text{ZnO})_m$  ( $m$ : a natural number of less than 6) produced by sputtering vapor deposition in an argon atmosphere containing oxygen at a partial pressure of higher than  $3 \times 10^{-2}$  Pa, preferably higher than  $5 \times 10^{-1}$  Pa.

In use of the apparatus and the material employed in this Example, the film formation by sputtering is conducted in the oxygen partial pressure ranging from  $3 \times 10^{-2}$  Pa to  $5 \times 10^{-1}$  Pa.

Incidentally, in the thin film produced by pulse

laser vapor deposition or sputtering, the electron mobility increases with increase in number of the conductive electrons, as shown in Fig. 2.

As described above, by controlling the oxygen 5 partial pressure, the oxygen defect can be decreased, and thereby the electron carrier concentration can be decreased. In the amorphous thin film, the electron mobility can be high, since no grain interface exists essentially in the amorphous state differently from 10 polycrystalline state.

Incidentally, the substitution of the glass substrate by a 200 $\mu\text{m}$ -thick polyethylene terephthalate (PET) film did not change the properties of the amorphous oxide film of  $\text{InGaO}_3(\text{ZnO})_4$  formed thereon.

15 A high-resistance amorphous film  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  ( $m$ : a natural number less than 6;  $0 < x \leq 1$ ) can be obtained by using, as the target, polycrystalline  $\text{InGaO}_3(\text{Zn}_{1-x}\text{Mg}_x\text{O})_m$  even at an oxygen partial pressure less than 1 Pa. For instance, with 20 a target in which 80 atom% of Zn is replaced by Mg, the electron carrier concentration lower than  $1 \times 10^{16}/\text{cm}^3$  (resistance: about  $1 \times 10^{-2} \text{ S/cm}$ ) can be achieved by pulse laser deposition in an atmosphere containing oxygen at a partial pressure of 0.8 Pa. 25 In such a film, the electron mobility is lower than that of the Mg-free film, but the decrease is slight: the electron mobility is about  $5 \text{ cm}^2/\text{V.sec}$  at room

temperature, being higher by about one digit than that of amorphous silicon. When the films are formed under the same conditions, increase of the Mg content decreases both the electric conductivity and the 5 electron mobility. Therefore, the content of the Mg ranges preferably from 20% to 85% ( $0.2 < x < 0.85$ ).

As described above, the oxygen defect are decreased by control of the oxygen partial pressure, and the electron carrier concentration can be 10 decreased without addition of specific impurity ions. In the amorphous thin film, the electron mobility can be high, since no grain interface exists essentially in the amorphous state, being different from polycrystalline state. Further, since the electric 15 conductivity can be decreased without addition of specific impurity ions, the electron mobility can be kept high without scattering by the impurity.

In the thin film transistor employing the above amorphous oxide film, the gate-insulating film 20 contains preferably a mixed crystal compound containing two or more of  $\text{Al}_2\text{O}_3$ ,  $\text{Y}_2\text{O}_3$ ,  $\text{HfO}_2$ , and compounds thereof.

The presence of a defect at the interface 25 between the gate-insulating thin film and the channel layer thin film lowers the electron mobility and causes hysteresis of the transistor characteristics. Moreover, the current leakage depends greatly on the

kind of the gate-insulating film. Therefore the gate-insulating film should be selected to be suitable for the channel layer. The current leakage can be decreased by use of an  $\text{Al}_2\text{O}_3$  film, the 5 hysteresis can be made smaller by use of a  $\text{Y}_2\text{O}_3$  film, and the electron mobility can be increased by use of an  $\text{HfO}_2$  film having a high dielectric constant. By use of the mixed crystal of the above compounds, TFT can be formed which causes smaller current leakage, 10 less hysteresis, and exhibiting a higher electron mobility. Since the gate-insulating film forming process and the channel layer forming process can be conducted at room temperature, the TFT can be formed in a stagger constitution or in a reversed stagger 15 constitution.

The TFT thus formed is a three-terminal element having a gate terminal, a source terminal, and a drain terminal. This TFT is formed by forming a semiconductor thin film on a insulating substrate of 20 a ceramics, glass, or plastics as a channel layer for transport of electrons or holes, and serves as an active element having a function of controlling the current flowing through the channel layer by application of a voltage to the gate terminal, and 25 switching the current between the source terminal and the drain terminal.

In the present invention, it is important that

an intended electron carrier concentration is achieved by controlling the amount of the oxygen defect.

In the above description, the amount of the 5 oxygen in the amorphous oxide film is controlled by controlling the oxygen concentration in the film-forming atmosphere. Otherwise the oxygen defect quantity can be controlled (decreased or increase) by post-treatment of the oxide film in an oxygen-10 containing atmosphere as a preferred embodiment.

For effective control of the oxygen defect quantity, the temperature of the oxygen-containing atmosphere is controlled in the range from 0°C to 300°C, preferably from 25°C to 250°C, more preferably 15 from 100°C to 200°C.

Naturally, a film may be formed in an oxygen-containing atmosphere and further post-treated in an oxygen-containing atmosphere. Otherwise the film is formed without control of the oxygen partial pressure 20 and post-treatment is conducted in an oxygen-containing atmosphere, insofar as the intended electron carrier concentration (less than  $1 \times 10^{18}/\text{cm}^3$ ) can be achieved.

The lower limit of the electron carrier 25 concentration in the present invention is, for example,  $1 \times 10^{14}/\text{cm}^3$ , depending on the kind of the element, circuit, or device employing the produced

oxide film.

(Broader Range of Materials)

After investigation on other materials for the system, it was found that an amorphous oxide composed 5 of at least one oxide of the elements of Zn, In, and Sn is useful for an amorphous oxide film of a low carrier concentration and high electron mobility. This amorphous oxide film was found to have a specific property that increase in number of 10 conductive electrons therein increases the electron mobility. Using this film, a normally-off type TFT can be produced which is excellent in transistor properties such as the on-off ratio, the saturation current in the pinch-off state, and the switching 15 rate.

A complex oxide can be formed by incorporating additionally one of the elements shown below into the above amorphous oxide containing at least one of the elements of Zn, In, and Sn, the additional elements 20 including:

Group-2 elements M2 having an atomic number lower than Zn (Mg, and Ca),

Group-3 elements M3 having an atomic number lower than In (B, Al, Ga, and Y),

25 Group-4 elements M4 having an atomic number lower than Sn (Si, Ge, and Zr),

Group-5 elements M5 (V, Nb, and Ta), and Lu, and W.

In the present invention, an oxide having any one of the characteristics of (a) to (h) below are useful:

- (a) An amorphous oxide which has an electron carrier concentration less than  $1 \times 10^{18}/\text{cm}^3$ ;

- 5 (b) An amorphous oxide in which the electron mobility becomes increased with increase of the electron carrier concentration;

- (The room temperature signifies a temperature in the 10 range from about  $0^\circ\text{C}$  to about  $40^\circ\text{C}$ . The term "amorphous compound" signifies a compound which shows a halo pattern only without showing a characteristic diffraction pattern in X-ray diffraction spectrum.

- 15 The electron mobility signifies the one measured by the Hall effect.)

- (c) An amorphous oxide mentioned in the above items

- (a) or (b), in which the electron mobility at room temperature is higher than  $0.1 \text{ cm}^2/\text{V.sec}$ ;

- (d) An amorphous oxide mentioned, in any of the items 20 (b) to (c), which shows degenerate conduction;

- (The term "degenerate conduction" signifies the state in which the thermal activation energy in temperature dependency of the electric resistance is not higher than 30 meV.)

- 25 (e) An amorphous oxide, mentioned in any of the above item (a) to (d), which contains at least one of the elements of Zn, In, and Sn as the constituting

element;

(f) An amorphous oxide film composed of the amorphous oxide mentioned the above item (e), and additionally at least one of the elements of

5 Group-2 elements M2 having an atomic number lower than Zn (Mg, and Ca),

Group-3 elements M3 having an atomic number lower than In (B, Al, Ga, and Y),

Group-4 elements M4 having an atomic number lower than Sn (Si, Ge, and Zr),

Group-5 elements M5 (V, Nb, and Ta), and Lu, and W to lower the electron carrier concentration;

(The elements of M2, M3, M4 having respectively a lower atomic number than Zn, In, and Sn are highly ionic, thereby less oxygen defect being caused, and the electron carrier concentration being decreased.

The element Lu, which has a higher atomic number than Ga, has a small ionic radius, and highly ionic to

20 serve the same function as M3. M5, which is ionizable to be plus five-valent, being capable of bonding to oxygen strongly, and being less liable to cause oxygen defect. W, which is ionizable to be plus six-valent, being capable of bonding to oxygen

25 strongly, and being less liable to cause oxygen defect.)

(g) An amorphous oxide film, mentioned in any of the

above items (a) to (f), constituted of a single compound having a composition of  $\text{In}_{1-x}\text{M}_{3x}\text{O}_3(\text{Zn}_{1-y}\text{M}_{2y}\text{O})_m$  ( $0 \leq x \leq 1$ ;  $0 \leq y \leq 1$ ;  $m$ : 0 or a natural number of less than 6) in a crystal state, or a mixture of the compounds 5 different in number  $m$ , an example of  $\text{M}_3$  being  $\text{Ga}$ , and an example of  $\text{M}_2$  being  $\text{Mg}$ ; and (h) An amorphous oxide film, mentioned in any of the above items (a) to (g) formed on a plastic substrate or an plastic film.

10 The present invention also provides a field-effect transistor employing the above mentioned amorphous oxide or amorphous oxide film as the channel layer.

A field-effect transistor is prepared which is 15 employs an amorphous oxide film having an electron carrier concentration of less than  $1 \times 10^{18}/\text{cm}^3$  but more than  $1 \times 10^{15}/\text{cm}^3$  as the channel layer, and having a source terminal and a drain terminal, and a gate terminal with interposition of a gate-insulating film.

20 When a voltage of about 5 V is applied between the source and drain terminals without application of gate voltage, the electric current between the source and drain terminals is about  $1 \times 10^{-7}$  amperes.

The electron mobility in the oxide crystal 25 becomes larger with increase of the overlap of the s-orbitals of the metal ions. In an oxide crystal of  $\text{Zn}$ ,  $\text{In}$ , or  $\text{Sn}$  having a higher atomic number, the

electron mobility is in the range from 0.1 to 200 cm<sup>2</sup>/V.sec.

In an oxide, oxygen and metal ions are bonded by ionic bonds without orientation of the chemical 5 bonds, having a random structure. Therefore in the oxide in an amorphous state, the electron mobility can be comparable to that in a crystal state.

On the other hand, substitution of the Zn, In, or Sn with an element of a lower atomic number 10 decreases the electron mobility. Thereby the electron mobility in the amorphous oxide of the present invention ranges from about 0.01 to 20 cm<sup>2</sup>/V.sec.

In the transistor having a channel layer 15 constituted of the above oxide, the gate-insulating film is preferably formed from Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, or a mixed crystal compound containing two or more thereof.

The presence of a defect at the interface 20 between the gate-insulating thin film and the thin channel layer film lowers the electron mobility and causes hysteresis of the transistor characteristics. Moreover, the current leakage depends greatly on the kind of the gate-insulating film. Therefore the gate-insulating film should be selected to be 25 suitable for the channel layer. The current leakage can be decreased by use of an Al<sub>2</sub>O<sub>3</sub> film, the hysteresis can be made smaller by use of a Y<sub>2</sub>O<sub>3</sub> film,

and the electron mobility can be increased by use of an  $\text{HfO}_2$  film having a high dielectric constant. By use of the mixed crystal of the above compounds, TFT can be formed which causes smaller current leakage, 5 less hysteresis, and exhibiting a higher electron mobility. Since the gate-insulating film-forming process and the channel layer-forming process can be conducted at room temperature, the TFT can be formed in a stagger constitution or in a reversed stagger 10 constitution.

The  $\text{In}_2\text{O}_3$  oxide film can be formed through a gas-phase process, and addition of moisture in a partial pressure of about 0.1 Pa to the film-forming atmosphere makes the formed film amorphous.

15         $\text{ZnO}$  and  $\text{SnO}_2$  respectively cannot readily be formed in an amorphous film state. For formation of the  $\text{ZnO}$  film in an amorphous state,  $\text{In}_2\text{O}_3$  is added in an amount of 20 atom%. For formation of the  $\text{SnO}_2$  film in an amorphous state,  $\text{In}_2\text{O}_3$  is added in an amount of 20 atom%. In formation of  $\text{Sn-In-O}$  type amorphous film, gaseous nitrogen is introduced in a partial pressure of about 0.1 Pa in the film formation atmosphere.

25        To the above amorphous film, may be added an element capable of forming a complex oxide, selected from Group-2 elements M2 having an atomic number lower than Zn (Mg, and Ca), Group-3 elements M3

having an atomic number lower than In (B, Al, Ga, and Y), Group-4 elements M4 having an atomic number lower than Sn (Si, Ge, and Zr), Group-5 elements M5 (V, Nb, and Ta), and Lu, and W. The addition of the above 5 element stabilizes the amorphous film at room temperature, and broadens the composition range for amorphous film formation.

In particular, addition of B, Si, or Ge tending to form a covalent bond is effective for amorphous 10 phase stabilization. Addition of a complex oxide constituted of ions having largely different ion radii is effective for amorphous phase stabilization. For instance, in an In-Zn-O system, for formation of a film stable at room temperature, 15 In should be contained more than about 20 atom%.

However, addition of Mg in an amount equivalent to In enables formation of stable amorphous film in the composition range of In of not less than about 15 atom%.

20 In a gas-phase film formation, an amorphous oxide film of the electron carrier concentration ranging from  $1 \times 10^{15}/\text{cm}^3$  to  $1 \times 10^{18}/\text{cm}^3$  can be obtained by controlling the film forming atmosphere.

An amorphous oxide film can be suitably formed 25 by a vapor phase process such as a pulse laser vapor deposition process (PLD process), a sputtering process (SP process), and an electron-beam vapor

composition control, whereas the SP process is suitable in view of the mass production. However, the film-forming process is not limited thereto.

(Formation of In-Zn-Ga-O Type Amorphous Oxide Film by

5 PLD Process)

An In-Zn-Ga-O type amorphous oxide was deposited on a glass substrate (Corning Co.: 1737) by a PLD process employing a KrF excimer laser with a polycrystal sintered compact as the target having a

10 composition of  $\text{InGaO}_3(\text{ZnO})$  or  $\text{InGaO}_3(\text{ZnO})_4$ .

The apparatus shown in Fig. 11 was employed which is mentioned before, and the film formation conditions were the same as mentioned before for the apparatus.

15 The substrate temperature was 25°C.

The resulting two thin films were examined by small angle X-ray scattering method (SAXS) (thin film method, incidence angle: 0.5°): no clear diffraction peak was observed, which shows that the obtained In-

20 Ga-Zn-O type thin films produced with two different targets were both amorphous.

From X-ray reflectivity of the In-Zn-Ga-O type amorphous oxide film of the glass substrate and its pattern analysis, the mean square roughnesses (Rrms) of the thin films were found to be about 0.5 nm, and the film thicknesses to be about 120 nm. From

25 fluorescence X-ray spectrometric analysis (XRF), the

the film thicknesses to be about 120 nm. From fluorescence X-ray spectrometric analysis (XRF), the film obtained with the target of the polycrystalline sintered compact of  $\text{InGaO}_3(\text{ZnO})$  was found to contain 5 the metals at a composition ratio  $\text{In:Ga:Zn} = 1.1 : 1.1 : 0.9$ , whereas the film obtained with the target of the polycrystalline sintered compact of  $\text{InGaO}_3(\text{ZnO})_4$  was found to contain the metals at a composition ratio  $\text{In:Ga:Zn} = 0.98 : 1.02 : 4$ .