(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294815

(P2005-294815A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 29/786

F 1

H01L 29/78 617K

H01L 29/78 617N

H01L 29/78 612C

テーマコード(参考)

5F11O

審査請求 未請求 請求項の数 18 O L (全 39 頁)

(21) 出願番号 特願2005-62667 (P2005-62667)

(22) 出願日 平成17年3月7日 (2005.3.7)

(31) 優先権主張番号 特願2004-71793 (P2004-71793)

(32) 優先日 平成16年3月12日 (2004.3.12)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 荒尾 達也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ及び半導体装置

(57) 【要約】 (修正有)

【課題】 大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子を提供する。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供することを課題とする。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】 ドレイン領域側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極を有し、それぞれのゲート電極が形成するチャネル領域に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極に対応するソース領域とドレイン領域を形成し、一方に電流が流れるチャネル領域と一方向と反対の方向に電流が流れるチャネル領域の数が等しい薄膜トランジスタを提供することで課題を解決することができる。

【選択図】なし

**【特許請求の範囲】****【請求項 1】**

半導体層と絶縁膜とゲート電極よりなる複数のトランジスタを有し、

前記複数のトランジスタにおけるゲート電極同士は電気的に接続しており、

前記ゲート電極は1層目のゲート電極と2層目のゲート電極の2層よりなり、

前記複数のトランジスタにおけるドレイン領域同士は電気的に接続しており、

前記複数のトランジスタにおけるソース領域は同士電気的に接続しており、

前記複数のトランジスタはチャネルを流れる電流の方向が第1の方向であるトランジスタと、チャネルを流れる電流の方向が前記第1の方向と反対の方向である第2の方向のトランジスタとでなり、

前記複数のトランジスタよりなることを特徴とするトランジスタ。

10

**【請求項 2】**

請求項1において、前記半導体層は前記複数のトランジスタ間において共通であることを特徴とするトランジスタ。

**【請求項 3】**

請求項1において、前記半導体層は前記複数のトランジスタ間で異なることを特徴とするトランジスタ。

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、前記ソース領域及び前記ドレイン領域にはn型もしくはp型の不純物元素が高濃度に添加されていることを特徴とするトランジスタ。

20

**【請求項 5】**

請求項4において、前記半導体層における前記ゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されていることを特徴とするトランジスタ。

**【請求項 6】**

請求項1乃至請求項5のいずれか一項において、前記複数のトランジスタにおいて前記第1の方向に電流を流すトランジスタの数と前記第2の方向に電流を流すトランジスタの数は等しく、

前記半導体層における前記2層目のゲート電極と重なっている部分の前記第1の方向又は前記第2の方向に前記基板面内において垂直をなす方向の幅は、前記複数のトランジスタにおいて各々等しいことを特徴とするトランジスタ。

30

**【請求項 7】**

請求項1乃至請求項5のいずれか一項において、前記第1の方向に電流を流す複数のトランジスタの前記半導体層における前記2層目のゲート電極と重なっている部分の、前記第1の方向に前記基板面内において垂直をなす方向における幅の和と、

前記第2の方向に電流を流す複数のトランジスタの前記半導体層における前記2層目のゲート電極と重なっている部分の、前記第2の方向に前記基板面内において垂直をなす方向における幅の和は等しいことを特徴とするトランジスタ。

40

**【請求項 8】**

第1の半導体層とゲート絶縁膜と第1のゲート電極よりなる第1のトランジスタと、

第2の半導体層と前記ゲート絶縁膜と第2のゲート電極よりなる第2のトランジスタとを有し、

前記第1のゲート電極と前記第2のゲート電極とは電気的に接続しており、

前記第1のゲート電極と前記第2のゲート電極は1層目のゲート電極と2層目のゲート電極よりなり、

前記第1のトランジスタにおけるドレイン領域と前記第2のトランジスタにおけるドレイン領域とは電気的に接続しており、

前記第1のトランジスタにおけるソース領域と前記第2のトランジスタにおけるソース領域

50

域とは電気的に接続しており、

前記第1のトランジスタのチャネルを流れる電流の方向と前記第2のトランジスタのチャネルを流れる電流の方向とは反対であり、

前記第1のトランジスタと前記第2のトランジスタよりなることを特徴とするトランジスタ。

#### 【請求項 9】

請求項 8において、前記ソース領域及び前記ドレイン領域にはn型もしくはp型の不純物元素が高濃度に添加されていることを特徴とするトランジスタ。

#### 【請求項 10】

請求項 9において、

前記第1の半導体層における前記第1のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されており、

前記第2の半導体層における前記第2のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されていることを特徴とするトランジスタ。

#### 【請求項 11】

請求項 8乃至請求項 10のいずれか一項において、前記第1のトランジスタ及び前記第2のトランジスタのチャネルをキャリアが流れる方向に基板面内において直交する方向の長さを幅とするとき、

前記第1のゲート電極と重なっている部分の前記第1の半導体層の幅は前記第2のゲート電極と重なっている部分の前記第2の半導体層の幅と同じであることを特徴とするトランジスタ。

#### 【請求項 12】

半導体層とゲート絶縁膜と第1のゲート電極よりなる第1のトランジスタと、

前記半導体層と前記ゲート絶縁膜と第2のゲート電極よりなる第2のトランジスタとを有し、

前記第1のゲート電極と前記第2のゲート電極とは電気的に接続しており、

前記第1のゲート電極と前記第2のゲート電極は1層目のゲート電極と2層目のゲート電極よりなり、

前記第1のトランジスタにおけるドレイン領域と前記第2のトランジスタにおけるドレイン領域とは電気的に接続しており、

前記第1のトランジスタにおけるソース領域と前記第2のトランジスタにおけるソース領域とは電気的に接続しており、

前記第1のトランジスタのチャネルを流れる電流の方向と前記第2のトランジスタのチャネルを流れる電流の方向とは反対であり、

前記第1のトランジスタと前記第2のトランジスタよりなることを特徴とするトランジスタ。

#### 【請求項 13】

請求項 12において、前記ソース領域及び前記ドレイン領域にはn型もしくはp型の不純物元素が高濃度に添加されていることを特徴とするトランジスタ。

#### 【請求項 14】

請求項 13において、

前記半導体層における前記第1のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されており、

前記半導体層における前記第2のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されていることを特徴とするトランジスタ。

#### 【請求項 15】

10

20

30

40

50

請求項 1 2 乃至 請求項 1 4 のいずれか一項において、

前記第1のトランジスタ及び前記第2のトランジスタのチャネルをキャリアが流れる方向に

基板面内において直交する方向の長さを幅とするとき、

前記第1のゲート電極と重なっている部分の前記半導体層の幅は前記第2のゲート電極と重

なっている部分の前記半導体層の幅と同じであることを特徴とするトランジスタ。

【請求項 1 6】

基板上に各々平行に配置された複数の半導体層を形成し、

前記半導体層を覆ってゲート絶縁膜を形成し、

各々が電気的に接続している1層目のゲート電極を前記複数の半導体層それぞれに対応

して複数形成し、

前記複数の半導体層に前記1層目のゲート電極をマスクとしてp型もしくはn型の不純

物を低濃度に添加し、

熱処理によって前記不純物を活性化し、

前記1層目のゲート電極に対応し、前記半導体層の一部と前記1層目のゲート電極を覆

って2層目のゲート電極を複数形成し、

前記複数の半導体層間において各々が前記2層目のゲート電極と重畳している位置の形

状は一致しており、

前記2層目のゲート電極をマスクとして、前記不純物と同じ不純物を前記複数の半導

体層に添加することによって前記複数の半導体層に高濃度に前記不純物が添加されたソース

領域及びドレイン領域を形成し、

前記複数の半導体層、前記2層目のゲート電極及びゲート絶縁膜を覆って層間絶縁膜を

形成し、

前記層間絶縁膜に前記ソース領域及びドレイン領域に達するコンタクトホールを形成し

、

前記層間絶縁膜上に導電膜を形成し、パターニング、エッチングを行って配線、ソース

電極及びドレイン電極を形成することにより前記コンタクトホールを介して前記複数の半

導体層におけるソース領域同士、及びドレイン領域同士を電気的に接続し、

前記半導体層における前記ソース領域とドレイン領域の配置は前記2層目のゲート電極

を中心として右側にソース領域が位置する第1の配置と左側にソース領域が位置する第2の

配置とがあり、

前記第1の配置と前記第2の配置は前記複数の半導体層において半数ずつ存在させること

を特徴とする薄膜トランジスタの作製方法。

【請求項 1 7】

基板上に半導体層を形成し、

前記半導体層を覆ってゲート絶縁膜を形成し、

各々が電気的に接続している複数の1層目のゲート電極を前記半導体層に重ねて形成し

、

前記半導体層に前記1層目のゲート電極をマスクとしてp型もしくはn型の不純物を低

濃度に添加し、

熱処理を行って前記不純物を活性化し、

前記1層目のゲート電極に対応し、前記半導体層の一部と前記1層目のゲート電極を覆

って2層目のゲート電極を複数形成し、

前記半導体層における前記2層目のゲート電極と重畳している位置の形状は一致してお

り、

前記2層目のゲート電極をマスクとして、前記不純物と同じ不純物を前記半導体層に添

加することによって前記半導体層に高濃度に前記不純物が添加されたソース領域及びドレ

イン領域を形成し、

前記半導体層、前記2層目のゲート電極及びゲート絶縁膜を覆って層間絶縁膜を形成し

、

前記層間絶縁膜に前記ソース領域及びドレイン領域に達するコンタクトホールを形成し

10

20

30

40

50

、前記層間絶縁膜上及び前記コンタクトホール内を覆って導電膜を形成し、

前記導電膜にパターニング、エッチングを行って配線、前記ソース領域に電気的に接続するソース電極及び前記ドレイン電極に電気的に接続するドレイン電極を形成し、

前記半導体層における前記ソース領域とドレイン領域の配置は前記2層目のゲート電極を基準として右側にソース領域が位置する第1の配置と左側にソース領域が位置する第2の配置とがあり、

前記第1の配置と前記第2の配置は前記複数の半導体層において半数ずつ存在させるよう前に記配線、前記ソース電極及び前記ドレイン電極を形成することを特徴とする薄膜トランジスタの作製方法。

10

## 【請求項 18】

基板上に第1の半導体層と第2の半導体層を形成し、

前記第1の半導体層及び前記第2の半導体層を覆ってゲート絶縁膜を形成し、

前記ゲート絶縁膜上に前記第1の半導体層と重なった第1の1層目のゲート電極と、前記第2の半導体層と重なった第2の1層目のゲート電極とを形成し、

前記第1の1層目のゲート電極と前記第2の1層目のゲート電極は電気的に接続されており、

前記第1の半導体層及び前記第2の半導体層に前記1層目のゲート電極をマスクとしてp型もしくはn型の不純物を低濃度に添加し、

熱処理を行って前記不純物を活性化し、

前記第1の1層目のゲート電極に対応し、前記第1の半導体層の一部と前記第1の1層目のゲート電極を覆って第1の2層目のゲート電極を形成し、

前記第2の1層目のゲート電極に対応し、前記第2の半導体層の一部と前記第2の1層目のゲート電極を覆って第2の2層目のゲート電極を形成し、

前記第1の半導体層及び前記第2の半導体層における各々が2層目のゲート電極と重なっている位置の形状は一致しており、

前記2層目のゲート電極をマスクとして前記不純物と同じ不純物を前記半導体層に添加することによって前記半導体層に高濃度に前記不純物が添加されたソース領域及びドレイン領域を形成し、

前記第1及び第2の半導体層、前記第1の及び第2の2層目のゲート電極を覆って層間絶縁膜を形成し、

前記層間絶縁膜に前記ソース領域及びドレイン領域に達するコンタクトホールを形成し、

前記層間絶縁膜上及び前記コンタクトホール内を覆って導電膜を形成し、

前記導電膜にパターニング、エッチングを行って配線、前記ソース領域に電気的に接続するソース電極及び前記ドレイン電極に電気的に接続するドレイン電極を形成し、

前記第1の半導体層におけるソース領域とドレイン領域の配置は前記第2の半導体層におけるソース領域とドレイン領域の配置と前記ゲート電極を基準として反対であることを特徴とする薄膜トランジスタの作製方法。

20

30

40

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明はガラス基板上に形成された薄膜素子に関し、また、薄膜素子が形成されたガラス基板に関する。

## 【背景技術】

## 【0002】

ガラス基板は、石英基板と比較して安価であり、大型化が容易であることからフラットパネルディスプレイ用の基板などとして多用されてきている。

## 【0003】

50

しかし、一方でガラス基板は歪み点温度が低く、熱に弱いという特徴を有するため、ガラス基板上に薄膜半導体を形成するプロセスには制約が多い。そのため、ガラス基板上にポリシリコンを形成する場合にはレーザ結晶化によって基板にあまり熱がかからないようなプロセスが採用されることが多い。

#### 【0004】

ところがやはり不純物の活性化など、ある程度の加熱は行わざるを得ず、それにより生じる熱収縮を緩和するために特許文献1や特許文献2など様々な対策が取られている。

【特許文献1】特開2002-175984号公報

【特許文献2】特開2003-335547号公報

【発明の開示】

10

【発明が解決しようとする課題】

#### 【0005】

低成本化やディスプレイの大型化に伴って、ガラス基板はどんどん大型化してきている。そのため、熱収縮による基板の歪みはより深刻なものとなってきており、さらなる対策が求められている。

#### 【0006】

また、デザインルールが縮小されるにつれてマスク位置ずれに対する許容マージンは小さくなっている、どんなに厳密にマスク合わせを行ったとしてもアライメントのずれや基板の歪みによるずれが発生することがある。

#### 【0007】

そこで本発明では大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子を提供することを目的とする。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供する事を特徴とする。

#### 【0008】

さらに、本発明では多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供することを目的とする。また、そのような半導体素子を搭載した薄膜半導体回路及び薄膜半導体装置を提供する事を課題とする。

【課題を解決するための手段】

20

#### 【0009】

そこで本発明では、ドレイン領域側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極を有し、それぞれのゲート電極が形成するチャネル領域に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極に対応するソース領域とドレイン領域を形成し、一方向に電流が流れるチャネル領域と一方向と反対の方向に電流が流れるチャネル領域の数が等しいことを要旨とする。

#### 【0010】

本発明の構成の一つは半導体層上に設けられ、それそれがチャネル領域を形成する複数のゲート電極と、ゲート電極それぞれに対応して半導体層に設けられた一導電型の不純物元素を含むソース領域及びドレイン領域とを有し、半導体層はゲート電極と重なる位置のドレイン側の一部においてそれぞれ低濃度不純物領域を有しており、チャネル領域の任意の一つにおいて電流が流れる方向を基準方向とし、チャネル領域において前記基準方向に電流が流れるチャネル領域の数と前記基準方向とは反対の方向に電流が流れるチャネル領域の数が等しいことを特徴とする薄膜トランジスタである。

30

#### 【0011】

本発明の他の構成は複数の半導体層上に設けられ、それそれがチャネル領域を形成する複数のゲート電極と、ゲート電極それぞれに対応して半導体層に設けられた一導電型の不純物元素を含むソース領域及びドレイン領域とを有し、半導体層はゲート電極と重なる位置のドレイン側の一部においてそれぞれ低濃度不純物領域を有しており、チャネル領域の任意の一つにおいて電流が流れる方向を基準方向とし、チャネル領域において基準方向に電流が流れるチャネル領域の数と基準方向とは反対の方向に電流が流れるチャネル領域の数が等しいことを特徴とする薄膜トランジスタである。

40

50

数が等しいことを特徴とする薄膜トランジスタである。

【0012】

本発明の他の構成は一つの半導体層上に設けられ、それぞれがチャネル領域を形成する複数のゲート電極と、偶数のゲート電極それぞれに対応して半導体層に設けられた一導電型の不純物元素を含むソース領域及びドレイン領域とを有し、半導体層はゲート電極と重なる位置のドレイン側の一部においてそれぞれ低濃度不純物領域を有しており、チャネル領域の任意の一つにおいて電流が流れる方向を基準方向とし、チャネル領域において基準方向に電流が流れるチャネル領域の数と基準方向とは反対の方向に電流が流れるチャネル領域の数が等しいことを特徴とする薄膜トランジスタである。

【0013】

本発明の構成の一つは第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタは半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有し、半導体層にはP型またはN型の不純物元素がドーピングされており、ゲート電極下部に位置する半導体層には少なくとも低濃度不純物領域とチャネル領域が形成されており、当該2つのトランジスタにおけるソース領域同士ドレイン領域同士及びゲート電極同士は各々電気的に接続されており、当該2つのトランジスタにおいて電流が流れる方向は互いに平行であり、当該2つのトランジスタのゲート電極の幅は同じであり、当該2つのトランジスタにおいて前記ゲート電極と半導体層が重なっている部分の半導体層の形状は当該2つのトランジスタ間で同じであり、当該2つのトランジスタにおいて、それぞれの電流が流れる方向は逆方向であることを特徴とする半導体装置である。

【0014】

本発明の他の構成は第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタは半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有し、半導体層にはP型またはN型の不純物元素がドーピングされており、前記ゲート電極下部に位置する半導体層には少なくとも低濃度不純物領域とチャネル領域が形成されており、当該2つのトランジスタの入力はどちらも第1の配線からなされ、当該2つのトランジスタの出力はどちらも第2の配線になされ、当該2つのトランジスタのゲート電極同士は各々電気的に接続されており、当該2つのトランジスタにおいて電流が流れる方向は互いに平行であり、当該2つのトランジスタのゲート電極の幅は同じであり、当該2つのトランジスタにおいて前記ゲート電極と半導体層が重なっている部分の半導体層の形状は当該2つのトランジスタ間で同じであり、当該2つのトランジスタにおいて、それぞれの電流が流れる方向は逆方向であることを特徴とする半導体装置である。

【0015】

本発明の他の構成は第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタは半導体層と、半導体層を覆うゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極とを有し、半導体層にはP型またはN型の不純物元素がドーピングされており、ゲート電極下部に位置する半導体層には少なくとも低濃度不純物領域とチャネル領域が形成されており、前記第1のトランジスタのソース領域とゲート電極との間の寄生容量と、第2のトランジスタのドレイン領域とゲート電極との寄生容量が同じであり、当該2つのトランジスタにおいて電流が流れる方向は互いに平行であり、当該2つのトランジスタのゲート電極の幅は同じであり、当該2つのトランジスタにおいてゲート電極と前記半導体層が重なっている部分の前記半導体層の形状は当該2つのトランジスタ間で同じであり、当該2つのトランジスタにおいて、それぞれの電流が流れる方向は逆方向であることを特徴とする半導体装置である。

【0016】

本発明の他の構成を有するトランジスタは、半導体層と絶縁膜とゲート電極よりなる複数のトランジスタを有し、前記複数のトランジスタにおけるゲート電極は電気的に接続しており、前記ゲート電極は1層目のゲート電極と2層目のゲート電極の2層よりなり、前

10

20

30

40

50

記複数のトランジスタにおけるドレイン領域は電気的に接続しており、前記複数のトランジスタにおけるソース領域は電気的に接続しており、前記複数のトランジスタはチャネルを流れる電流の方向が第1の方向であるトランジスタと、チャネルを流れる電流の方向が前記第1の方向と反対の方向である第2の方向のトランジスタとなり、前記複数のトランジスタよりなることを特徴とする。

【0017】

本発明の他の構成を有するトランジスタは、上記構成において、前記半導体層は前記複数のトランジスタ間において共通であることを特徴とする。

【0018】

本発明の他の構成を有するトランジスタは、上記構成において、前記半導体層は前記複数のトランジスタ間で異なることを特徴とする。

【0019】

本発明の他の構成を有するトランジスタは、上記構成において、前記ソース領域及び前記ドレイン領域にはn型もしくはp型の不純物元素が高濃度に添加されていることを特徴とする。

【0020】

本発明の他の構成を有するトランジスタは、上記構成において、前記半導体層における前記ゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されていることを特徴とする。

【0021】

本発明の他の構成を有するトランジスタは、上記構成において、前記複数のトランジスタにおいて前記第1の方向に電流を流すトランジスタの数と前記第2の方向に電流を流すトランジスタの数は等しく、前記半導体層における前記2層目のゲート電極と重なっている部分の前記第1の方向又は前記第2の方向に前記基板面内において垂直をなす方向の幅は、前記複数のトランジスタにおいて各々等しいことを特徴とする。

【0022】

本発明の他の構成を有するトランジスタは、上記構成において、前記第1の方向に電流を流す複数のトランジスタの前記半導体層における前記2層目のゲート電極と重なっている部分の、前記第1の方向に前記基板面内において垂直をなす方向における幅の和と、前記第2の方向に電流を流す複数のトランジスタの前記半導体層における前記2層目のゲート電極と重なっている部分の、前記第2の方向に前記基板面内において垂直をなす方向における幅の和は等しいことを特徴とする。

【0023】

本発明の他の構成を有するトランジスタは、第1の半導体層とゲート絶縁膜と第1のゲート電極よりなる第1のトランジスタと、第2の半導体層と前記ゲート絶縁膜と第2のゲート電極よりなる第2のトランジスタとを有し、前記第1のゲート電極と前記第2のゲート電極とは電気的に接続しており、前記第1のゲート電極と前記第2のゲート電極は1層目のゲート電極と2層目のゲート電極よりも、前記第1のトランジスタにおけるドレイン領域と前記第2のトランジスタにおけるドレイン領域とは電気的に接続しており、前記第1のトランジスタにおけるソース領域と前記第2のトランジスタにおけるソース領域とは電気的に接続しており、前記第1のトランジスタのチャネルを流れる電流の方向と前記第2のトランジスタのチャネルを流れる電流の方向とは反対であり、前記第1のトランジスタと前記第2のトランジスタよりなることを特徴とする。

【0024】

本発明の他の構成を有するトランジスタは、上記構成において、前記ソース領域及び前記ドレイン領域にはn型もしくはp型の不純物元素が高濃度に添加されていることを特徴とする。

【0025】

本発明の他の構成を有するトランジスタは、上記構成において、前記第1の半導体層に

10

20

30

40

50

おける前記第1のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されており、前記第2の半導体層における前記第2のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されていることを特徴とする。

#### 【0026】

本発明の他の構成を有するトランジスタは、上記構成において、前記第1のトランジスタ及び前記第2のトランジスタのチャネルをキャリアが流れる方向に基板面内において直交する方向の長さを幅とするとき、前記第1のゲート電極と重なっている部分の前記第1の半導体層の幅は前記第2のゲート電極と重なっている部分の前記第2の半導体層の幅と同じであることを特徴とする。10

#### 【0027】

本発明の他の構成を有するトランジスタは、半導体層とゲート絶縁膜と第1のゲート電極よりなる第1のトランジスタと、前記半導体層と前記ゲート絶縁膜と第2のゲート電極よりなる第2のトランジスタとを有し、前記第1のゲート電極と前記第2のゲート電極とは電気的に接続しており、前記第1のゲート電極と前記第2のゲート電極は1層目のゲート電極と2層目のゲート電極よりなり、前記第1のトランジスタにおけるドレイン領域と前記第2のトランジスタにおけるドレイン領域とは電気的に接続しており、前記第1のトランジスタにおけるソース領域と前記第2のトランジスタにおけるソース領域とは電気的に接続しており、前記第1のトランジスタのチャネルを流れる電流の方向と前記第2のトランジスタのチャネルを流れる電流の方向とは反対であり、前記第1のトランジスタと前記第2のトランジスタよりなることを特徴とする。20

#### 【0028】

本発明の他の構成を有するトランジスタは、上記構成において、前記ソース領域及び前記ドレイン領域にはn型もしくはp型の不純物元素が高濃度に添加されていることを特徴とする。

#### 【0029】

本発明の他の構成を有するトランジスタは、上記構成において、前記半導体層における前記第1のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されており、前記半導体層における前記第2のゲート電極と重なっている部分のうち、前記2層目のゲート電極とのみ重なっている部分に前記ソース領域及びドレイン領域に添加されている不純物元素が低濃度に添加されていることを特徴とする。30

#### 【0030】

本発明の他の構成を有するトランジスタは、上記構成において、前記第1のトランジスタ及び前記第2のトランジスタのチャネルをキャリアが流れる方向に基板面内において直交する方向の長さを幅とするとき、前記第1のゲート電極と重なっている部分の前記半導体層の幅は前記第2のゲート電極と重なっている部分の前記半導体層の幅と同じであることを特徴とする。

#### 【0031】

本発明の他の構成を有する薄膜トランジスタの作製方法は、基板上に各々平行に配置された複数の半導体層を形成し、前記半導体層を覆ってゲート絶縁膜を形成し、各々が電気的に接続している1層目のゲート電極を前記複数の半導体層それぞれに対応して複数形成し、前記複数の半導体層に前記1層目のゲート電極をマスクとしてp型もしくはn型の不純物を低濃度に添加し、熱処理によって前記不純物を活性化し、前記1層目のゲート電極に対応し、前記半導体層の一部と前記1層目のゲート電極を覆って2層目のゲート電極を複数形成し、前記複数の半導体層間ににおいて各々が前記2層目のゲート電極と重畳している位置の形状は一致しており、前記2層目のゲート電極をマスクとして、前記不純物と同じ不純物を前記複数の半導体層に添加することによって前記複数の半導体層に高濃度に前記不純物が添加されたソース領域及びドレイン領域を形成し、前記複数の半導体層、前記40

2層目のゲート電極及びゲート絶縁膜を覆って層間絶縁膜を形成し、前記層間絶縁膜に前記ソース領域及びドレイン領域に達するコンタクトホールを形成し、前記層間絶縁膜上に導電膜を形成し、パターニング、エッチングを行って配線、ソース電極及びドレイン電極を形成することにより前記コンタクトホールを介して前記複数の半導体層におけるソース領域同士、及びドレイン領域同士を電気的に接続し、前記半導体層における前記ソース領域とドレイン領域の配置は前記2層目のゲート電極を中心として右側にソース領域が位置する第1の配置と左側にソース領域が位置する第2の配置とがあり、前記第1の配置と前記第2の配置は前記複数の半導体層において半数ずつ存在させることを特徴とする。

### 【0032】

本発明の他の構成を有する薄膜トランジスタの作製方法は、基板上に半導体層を形成し、前記半導体層を覆ってゲート絶縁膜を形成し、各々が電気的に接続している複数の1層目のゲート電極を前記半導体層に重ねて形成し、前記半導体層に前記1層目のゲート電極をマスクとしてp型もしくはn型の不純物を低濃度に添加し、熱処理を行って前記不純物を活性化し、前記1層目のゲート電極に対応し、前記半導体層の一部と前記1層目のゲート電極を覆って2層目のゲート電極を複数形成し、前記半導体層における前記2層目のゲート電極と重畳している位置の形状は一致しており、前記2層目のゲート電極をマスクとして、前記不純物と同じ不純物を前記半導体層に添加することによって前記半導体層に高濃度に前記不純物が添加されたソース領域及びドレイン領域を形成し、前記半導体層、前記2層目のゲート電極及びゲート絶縁膜を覆って層間絶縁膜を形成し、前記層間絶縁膜に前記ソース領域及びドレイン領域に達するコンタクトホールを形成し、前記層間絶縁膜上及び前記コンタクトホール内を覆って導電膜を形成し、前記導電膜にパターニング、エッチングを行って配線、前記ソース領域に電気的に接続するソース電極及び前記ドレイン電極に電気的に接続するドレイン電極を形成し、前記半導体層における前記ソース領域とドレイン領域の配置は前記2層目のゲート電極を中心として右側にソース領域が位置する第1の配置と左側にソース領域が位置する第2の配置とがあり、前記第1の配置と前記第2の配置は前記半導体層において半数ずつ存在させるように前記配線、前記ソース電極及び前記ドレイン電極を形成することを特徴とする。

### 【0033】

本発明の他の構成を有する薄膜トランジスタの作製方法は、基板上に第1の半導体層と第2の半導体層を形成し、前記第1の半導体層及び前記第2の半導体層を覆ってゲート絶縁膜を形成し、前記ゲート絶縁膜上に前記第1の半導体層と重なった第1の1層目のゲート電極と、前記第2の半導体層と重なった第2の1層目のゲート電極とを形成し、前記第1の1層目のゲート電極と前記第2の1層目のゲート電極は電気的に接続されており、前記第1の半導体層及び前記第2の半導体層に前記1層目のゲート電極をマスクとしてp型もしくはn型の不純物を低濃度に添加し、熱処理を行って前記不純物を活性化し、前記第1の1層目のゲート電極に対応し、前記第1の半導体層の一部と前記第1の1層目のゲート電極を覆って第1の2層目のゲート電極を形成し、前記第2の1層目のゲート電極を覆って第2の2層目のゲート電極を形成し、前記第1の半導体層及び前記第2の半導体層における各々が2層目のゲート電極と重なっている位置の形状は一致しており、前記2層目のゲート電極をマスクとして前記不純物と同じ不純物を前記半導体層に添加することによって前記半導体層に高濃度に前記不純物が添加されたソース領域及びドレイン領域を形成し、前記第1及び第2の半導体層、前記第1の及び第2の2層目のゲート電極を覆って層間絶縁膜を形成し、前記層間絶縁膜に前記ソース領域及びドレイン領域に達するコンタクトホールを形成し、前記層間絶縁膜上及び前記コンタクトホール内を覆って導電膜を形成し、前記導電膜にパターニング、エッチングを行って配線、前記ソース領域に電気的に接続するソース電極及び前記ドレイン電極に電気的に接続するドレイン電極を形成し、前記第1の半導体層におけるソース領域とドレイン領域の配置は前記第2の半導体層におけるソース領域とドレイン領域の配置と前記ゲート電極を中心として反対であることを特徴とする。

### 【発明の効果】

10

20

30

40

50

**【 0 0 3 4 】**

本発明を適用することによって、基板の熱収縮やマスクのアライメントずれによって生じてしまっていたトランジスタの寄生容量の変化を抑える事が可能となる。

**【 発明を実施するための最良の形態 】****【 0 0 3 5 】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

**【 0 0 3 6 】**

また、説明は薄膜トランジスタを例にあげて行っているが、薄膜トランジスタに限らず、他のトランジスタにおいても本発明は適用できる。

**【 0 0 3 7 】****( 実施の形態 1 )**

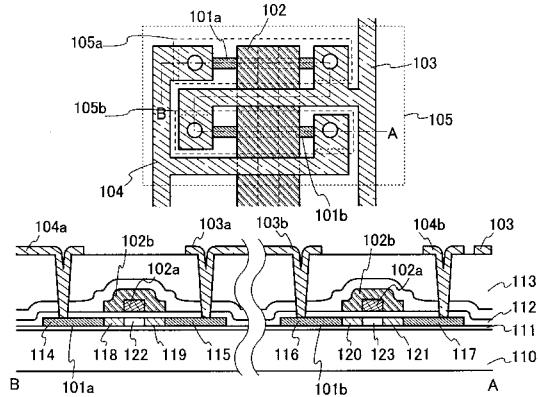

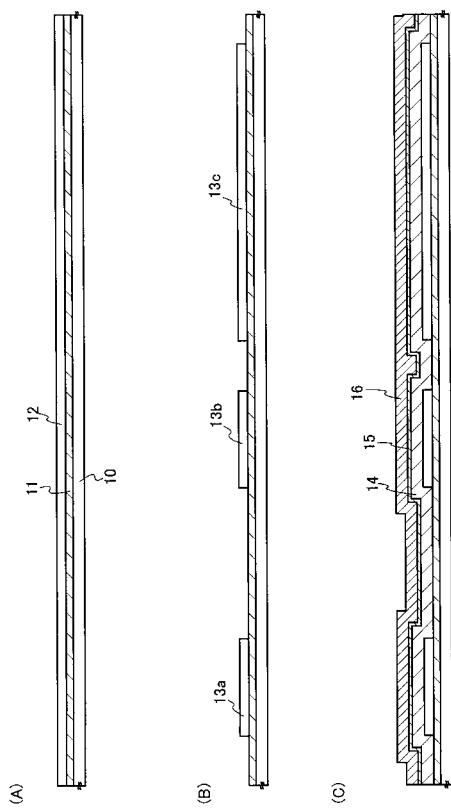

本発明の実施の形態を図1を参照しながら説明する。図1(A)は本発明の半導体装置の上面図であり、半導体層101a、半導体層101b、ゲート電極102、ソース電極と配線103、ドレイン電極と配線104を有している。また、図1(B)は図1(A)中におけるA-Bの断面図であり、基板110、下地絶縁膜111、ゲート絶縁膜112、層間絶縁膜113を有している。また、ゲート電極102は1層目のゲート電極102aと2層目のゲート電極102bとの2層構造となっている。

**【 0 0 3 8 】**

半導体層101aと半導体層101bにはそれぞれP型もしくはN型を示す同一の不純物がドーピングされており、高濃度にそれら不純物がドーピングされた高濃度不純物領域114～117と低濃度に不純物が添加された低濃度不純物領域118～121及びチャネル領域122、123を有している。また、半導体層101aと101bにはゲート絶縁膜112を介してゲート電極102が重なっており、チャネル領域122、123と1層目のゲート電極102aは重なって形成されている。また、2層目のゲート電極102bは1層目のゲート電極102aを覆っており、且つその少なくとも一部は低濃度不純物領域118～121と重なっている。すなわち、低濃度不純物領域118～121上には2層目のゲート電極102bがゲート絶縁膜112を介して重なっている。

**【 0 0 3 9 】**

配線103と配線104は層間絶縁膜113上に形成されており、層間絶縁膜113に開口された高濃度不純物領域114～117まで達する開口部に形成されたソース電極103もしくはドレイン電極104を介して高濃度不純物領域114～117に電気的に接続されている。なお、ソース電極103a、103bは配線103と高濃度不純物領域(ソース領域)115、116に接続し、ドレイン電極104a、104bは配線104と高濃度不純物領域(ドレイン領域)114、117に接続している。

**【 0 0 4 0 】**

すなわち、当該2つの薄膜トランジスタにおけるソース領域同士ドレイン領域同士及びゲート電極同士は各々電気的に接続されている、もしくは当該2つの薄膜トランジスタの入力はどちらも第1の配線からなされ、出力はどちらも第2の配線になされ、ゲート電極同士は各々電気的に接続されているということができる。

**【 0 0 4 1 】**

上記構造により半導体層101aから薄膜トランジスタ105a、半導体層101bから薄膜トランジスタ105bが形成されており、電流の流れる方向を長さ方向、基板平面上で長さ方向に直角をなす方向を幅方向とすると、チャネル領域122、123の幅及び長さは同一であり、低濃度不純物領域118～121の幅は同一である。また、半導体層101aと101bは長さ方向に平行となるように配置されている。なお、本発明において長さ方向、幅方向とは上記の定義を用いることとする。

**【 0 0 4 2 】**

10

20

30

40

50

なお、薄膜トランジスタ 105a と 105b においてソース領域、ドレイン領域及びソース電極、ドレイン電極の配置は薄膜トランジスタ 105a と 105b の電流が流れる方向が互いに平行且つ逆方向となるように配置する。

#### 【0043】

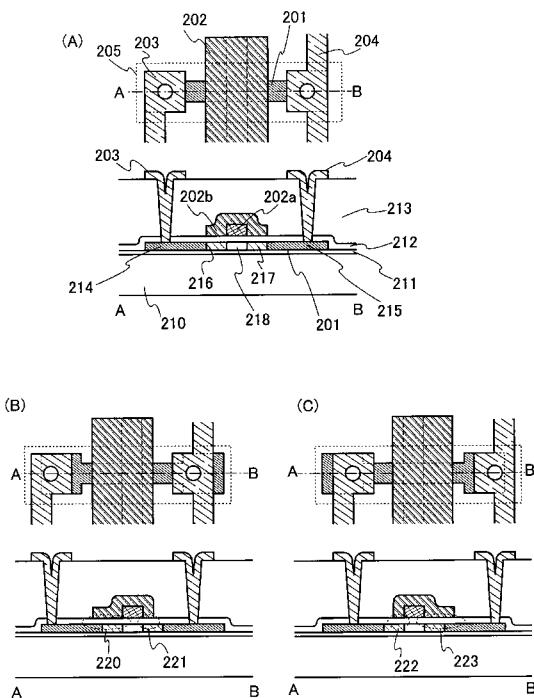

以上が本発明の構成を有する薄膜トランジスタであり、薄膜トランジスタ 105a と薄膜トランジスタ 105b の二つの薄膜トランジスタでもって本発明の薄膜トランジスタ 105 とみなす。この薄膜トランジスタ 105 の特性は、図 20 (A) に示したような従来の薄膜トランジスタの特性とほぼ同様である（ただし図 20 (A) の薄膜トランジスタ 205 のチャネル領域 218 の幅は図 1 における薄膜トランジスタ 105a のチャネル領域 122 の幅または薄膜トランジスタ 105b のチャネル領域 123 の幅の 2 倍、もしくは薄膜トランジスタ 105a のチャネル領域 122 の幅または薄膜トランジスタ 105b のチャネル領域 123 の幅の和に等しい）。

10

#### 【0044】

なお、図 20 の従来の薄膜トランジスタ 205 は、半導体層 201、ゲート電極（1 層目のゲート電極 202a、2 層目のゲート電極 202b）202、配線及びソース電極 203、配線及びドレイン電極 204、基板 210、下地絶縁膜 211、ゲート絶縁膜 212、層間絶縁膜 213、高濃度不純物領域 214 及び 215、低濃度不純物領域 216 及び 217、チャネル領域 218 からなっている。

20

#### 【0045】

ところで、図 1 や図 20 に示したような構造の薄膜トランジスタでは低濃度不純物領域とゲート電極とにより、寄生容量が発生している。図 20 (A) のような従来の薄膜トランジスタの 2 層目のゲート電極 202b を作成する際に、何らかの理由（マスクのアライメントずれ、歪み、基板の収縮など）によってその形成位置が半導体層の長さ方向にずれてしまつたとすると、図 20 (B)、(C) のように、低濃度不純物領域と 2 層目のゲート電極 202b が重なっている部分（Gate Overlapped Lightly doped Drain 領域：GOLD 領域）220～223 の面積が設計時に意図されていた面積と異なってくる。低濃度不純物領域と 2 層目のゲート電極 202b が重なっている部分の面積が異なるということは、先に述べた寄生容量の値も変化してしまい、寄生容量が変化した薄膜トランジスタで形成した回路は回路負荷が異なり動作マージンが厳しくなるなど問題が発生する。

30

#### 【0046】

特に基板の熱収縮を原因とするマスクずれは、基板はその中心に向かって収縮するため、基板の両端では収縮する方向が異なつてくる。すると、基板の一端ではドレイン側の寄生容量が大きくなり、他方ではドレイン側の寄生容量が小さくなるということが起きると考えられる。そのため、本来なら同じ特性を有していなければいけないはずの薄膜トランジスタの寄生容量が基板の両端で大きく異なってしまう恐れがある。これは特に大型基板などで顕著にあらわれ、問題になる。また、同じ繰り返しパターンが続く表示装置のソースドライバーやゲートドライバーでは寄生容量が異なると回路動作も基板の両端で大きく変化してしまうことになる。

30

#### 【0047】

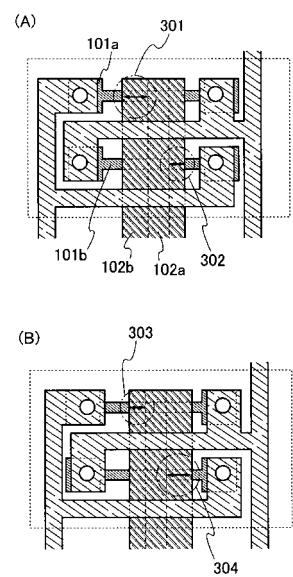

一方、本発明の薄膜トランジスタ 105（図 1）の場合を説明する。本発明の構成を有する薄膜トランジスタ 105 を形成する場合に、図 20 (B)、(C) と同様、長さ方向において 2 層目のゲート電極 102b がずれて形成されてしまったとする（図 2 (A)、(B)）。

40

#### 【0048】

図 2 (A) は 2 層目のゲート電極 102b が本来の位置より図中向かって左にずれてしまつた状態を示している。本発明の薄膜トランジスタ 105 を構成する二つの薄膜トランジスタ 105a と 105b では各々のチャネル領域 122、123 に対するソース領域、ドレイン領域の配置が逆になつてゐるため、2 層目のゲート電極 102b が図中向かって左にずれたことにより薄膜トランジスタ 105a ではドレイン側に位置する 2 層目のゲート電極 102b の半導体層と重なつてゐる面積が増大し、薄膜トランジスタ 105b では

50

逆にドレイン側に位置する2層目のゲート電極102bの半導体層と重なっている面積が減少している。

#### 【0049】

また、薄膜トランジスタ105aと105bは各々のチャネルを流れる電流の方向が反対になるように配置されており、半導体層101aと101bの幅が一致しているため、薄膜トランジスタ105aにおけるドレイン側の2層目のゲート電極102bの面積の増加量と薄膜トランジスタ105bにおけるドレイン側の2層目のゲート電極102bの面積の減少量は等しい。そして、不純物領域と2層目のゲート電極102bが重なっている面積の変化量に合わせて容量も変化するため、105aと105bの二つの薄膜トランジスタを合わせて一つのトランジスタとしてみなしている本発明の薄膜トランジスタ105としてのGOLD領域寄生の容量の変化は0となる。すなわち、本発明の薄膜トランジスタ105はマスクのずれによる容量変化の影響がほぼない構成であることができる。10

#### 【0050】

すなわち、半導体層101aを活性層とする薄膜トランジスタ105aにおいて増加するGOLD領域301の面積と半導体層101bを活性層とする薄膜トランジスタ105bにおいて減少するGOLD領域302の面積が同じであるため、トータルの変化量は相殺されて0となるのである。ソース側の容量も同様である。このような理由により本発明の薄膜トランジスタはマスクのアライメントずれや歪み、基板の収縮などによるマスクずれが引き起こすGOLD領域の容量変化の影響を抑えることが可能となる。結果として形成された薄膜トランジスタが有する寄生容量のバラツキが少なく、当該薄膜トランジスタで形成された回路の回路負荷のバラツキも少ないものとすることができます。20

#### 【0051】

図2(B)は図2(A)とは逆の方向(図中向かって右方向)に2層目のゲート電極102bがずれて形成された場合の図であり、薄膜トランジスタ105aではGOLD領域303の面積が小さくなってしまい、薄膜トランジスタ105bではGOLD領域304の面積が大きくなっている例であるが、この場合もトータルの容量変化は0となる。説明は図2(A)と同様であるので割愛する。

#### 【0052】

これにより、大面积基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子を提供することができる。また、そのような半導体素子を搭載した、薄膜半導体回路及び薄膜半導体装置を提供することができる。30

#### 【0053】

また、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供することが出来る。また、そのような半導体素子を搭載した薄膜半導体回路及び薄膜半導体装置を提供することができるようになる。

#### 【0054】

またさらに、同じパターンが並んでいる方向に長さ方向をあわせこむと、本発明の薄膜トランジスタを配列させることで回路負荷のバラツキの少ない回路を形成することができるようになり望ましい。40

#### 【0055】

なお、本実施の形態では一つの薄膜トランジスタにおいてゲート電極の数は2つであるが、これ以上の数であってもかまわない。好ましくは偶数個形成されていると良い。この際、ゲート電極に対応して半導体層にできるチャネルを流れる電流の向きは第1の方向と、第1の方向に反対の第2の方向の2方向であり、本発明の薄膜トランジスタにおいて、第1の方向に電流が流れるチャネルと第2の方向に電流が流れるチャネルの数はなるべく近いことが望ましい。すなわち、一つのトランジスタにおいて第1の方向に電流が流れるチャネルの数と第2の方向に電流が流れるチャネルの数はチャネルが奇数個出来る場合は1個違い、偶数個である場合は同数であることが望ましい。50

## 【0056】

なお、幅方向へのずれは長さ方向へのずれよりマージンが大きいため、本発明で問題にしているわずかなマスクずれに対しては大きな問題とならず無視できる程度である。

## 【0057】

## (実施の形態2)

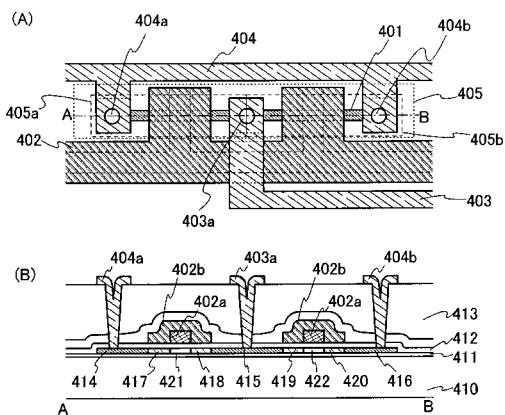

本実施の形態では実施の形態1と異なる様の本発明のトランジスタについて図3を用いて説明する。図3(A)に記載の上面図において、半導体層401、ゲート電極402、ドレイン電極及び配線(このうちドレイン電極403a)403、ソース電極及び配線(この内、ソース電極404a、404b)404でありこれらの構成を有する本発明のトランジスタが薄膜トランジスタ405である。薄膜トランジスタ405はソース電極404aと、ドレイン電極403aからなる薄膜トランジスタ405aと、ソース電極404bと、ドレイン電極403aからなる薄膜トランジスタ405bの2つの薄膜トランジスタより構成されているとみなすことができる。

## 【0058】

図3(B)は図3(A)の上面図中A-Bで切断した場合の断面図である。この断面図において、1層目のゲート電極402a、2層目のゲート電極402b、基板410、下地絶縁膜411、ゲート絶縁膜412、層間絶縁膜413、高濃度不純物領域414~416、低濃度不純物領域417~420、チャネル領域421、422である。なお、1層目のゲート電極402aと2層目のゲート電極402bでゲート電極が形成される。また、半導体層401に重なるゲート電極の幅は薄膜トランジスタ405a、405bとも同じ幅とする。なお、その他の図3(B)における符号は図3(A)と同じであるため説明を省略する。

## 【0059】

本実施の形態における薄膜トランジスタ405は、半導体層401が実施の形態1における半導体層101a及び101bに、薄膜トランジスタ405aと405bが薄膜トランジスタ105a、105bに相当する。本実施の形態の薄膜トランジスタ405は半導体層401が一続きであることが図1における薄膜トランジスタ105と異なるが、薄膜トランジスタ405を構成する薄膜トランジスタ405aと405bはその電流が流れる方向が平行であり、その流れる方向が反対である。

## 【0060】

このため、何らかの理由により2層目のゲート電極402bの形成位置がずれてしまっても薄膜トランジスタ405aにおけるドレイン側の2層目のゲート電極402bの面積の変化量と、薄膜トランジスタ405bにおけるドレイン側の2層目のゲート電極402bの面積の変化量は等しい。不純物領域とゲート電極が重なっている面積の変化量に合わせて容量も変化するため、405aと405bの二つの薄膜トランジスタを合わせて一つのトランジスタとしてみなしている本発明の薄膜トランジスタ405としての寄生容量の変化は0となる。すなわち、本実施の形態における構成の薄膜トランジスタ405は実施の形態1に記載の薄膜トランジスタ105と実質的に同じ構成であり、マスクのずれによる容量変化の影響がほぼない構成であるといふことができる。

## 【0061】

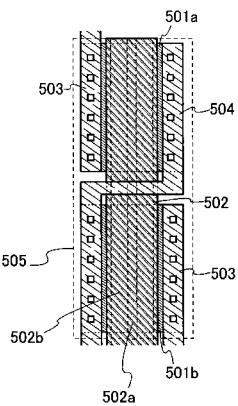

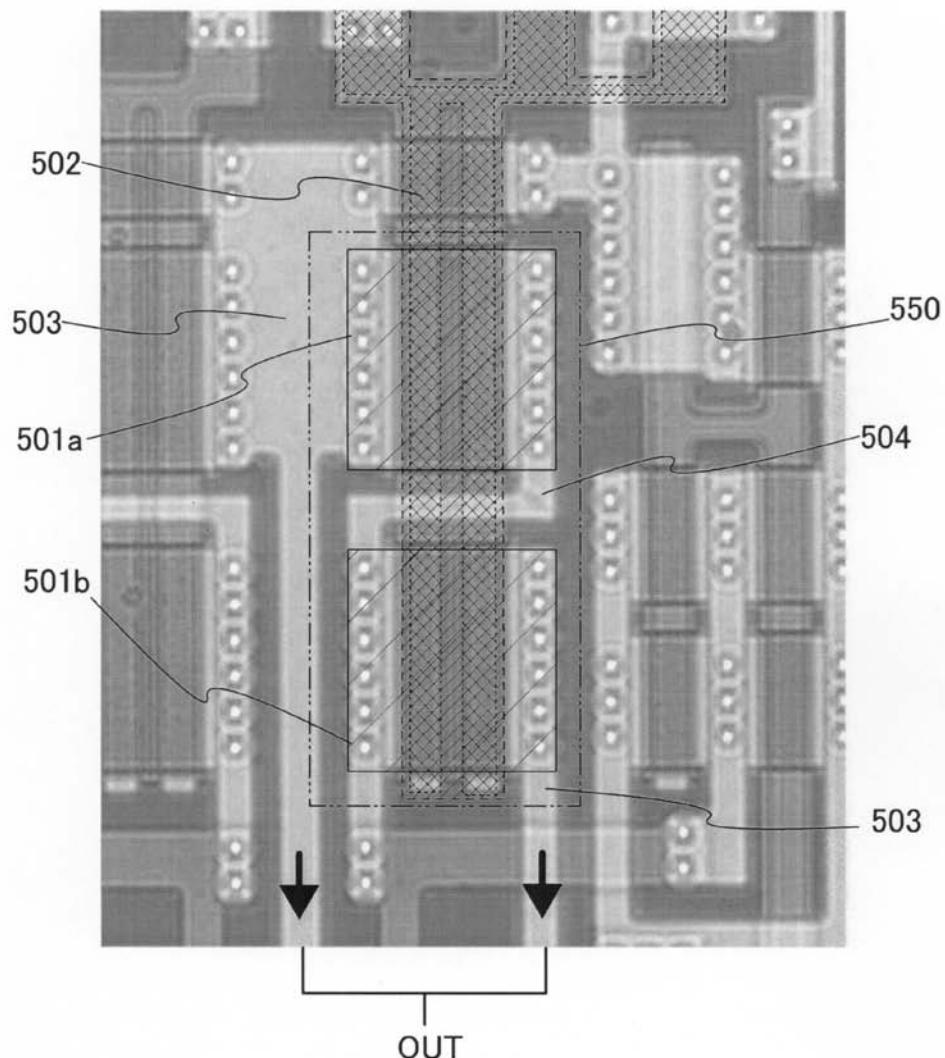

また図4も見た目は異なるが、半導体層501a、502b、1層目のゲート電極502a、2層目のゲート電極502b、ドレイン電極及び配線503、ソース電極及び配線504からなり、全体として薄膜トランジスタ505を形成している。なお、1層目のゲート電極502aと2層目のゲート電極502bでゲート電極が形成される。ドレイン電極503は同じ配線に接続することとし、ゲート電極は2層構造となっており、半導体層501a、501bのうち1層目のゲート電極502aと2層目のゲート電極502bの両方と重なっている位置にチャネル領域を有し、2層目のゲート電極502bのみと重なっている位置に低濃度不純物領域を有し、その他の位置は高濃度不純物領域であるとすると、実施の形態1と同じ構成である。このように一見レイアウトが異なっていても、本発明の構成は適用することができ同様の効果を得る事ができる。

10

20

30

40

50

**【 0 0 6 2 】**

これにより、大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子を提供することができる。また、そのような半導体素子を搭載した、薄膜半導体回路及び薄膜半導体装置を提供することができる。

**【 0 0 6 3 】**

また、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供することが出来る。また、そのような半導体素子を搭載した薄膜半導体回路及び薄膜半導体装置を提供することができるようになる。

**【 0 0 6 4 】**

またさらに、同じパターンが並んでいる方向に長さ方向をあわせこんで、本発明の薄膜トランジスタを配列させると、さらに回路負荷のバラツキの少ない回路を形成することができるようになり望ましい構成である。

**【 0 0 6 5 】**

なお、本実施の形態では一つの薄膜トランジスタにおいてゲート電極の数は2つであるが、これ以上の数であってもかまわない。好ましくは偶数個形成されていると良い。この際、ゲート電極に対応して半導体層にできるチャネルを流れる電流の向きは第1の方向と、第1の方向に反対の第2の方向の2方向であり、本発明の薄膜トランジスタにおいて、第1の方向に電流が流れるチャネルと第2の方向に電流が流れるチャネルの数はなるべく近いことが望ましい。すなわち、一つのトランジスタにおいて第1の方向に電流が流れるチャネルの数と第2の方向に電流が流れるチャネルの数はチャネルが奇数個出来る場合は1個違い、偶数個である場合は同数であることが望ましい。

**【 0 0 6 6 】****(実施の形態3)**

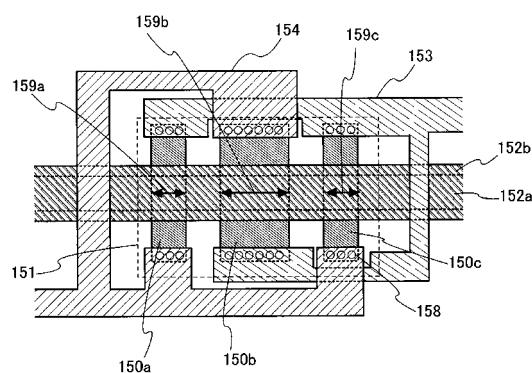

本実施の形態では実施の形態1及び実施の形態2と異なる様様の本発明のトランジスタについて図23を参照しながら説明する。図23に記載の上面図において、半導体層150a、150b及び150c、ゲート電極152(1層目のゲート電極152a及び2層目の導電膜152bより構成される)、ドレイン電極及び配線154、ソース電極及び配線153が示されており、これらの構成を有する本発明のトランジスタ151が示されている。トランジスタ151は半導体層150aを含むトランジスタと、半導体層150bを含むトランジスタと、半導体層150cを含むトランジスタの3つのトランジスタより構成されている。

**【 0 0 6 7 】**

また、半導体層150a～半導体層150cにおいて、1層目のゲート電極152aと重なっている部分にはn型もしくはp型を付与する不純物は実質的に添加されておらず、また、半導体層150a～半導体層150cにおいて2層目のゲート電極152bのみと重なっている部分には低濃度に当該不純物が添加されている。また、半導体層150a～半導体層150cにおいて、それ以外の部分については高濃度に当該不純物が添加されている。

**【 0 0 6 8 】**

この3つのトランジスタには同じソース電極及び配線153とドレイン電極及び配線154がコンタクトホールを介して接続されており、各々半導体層150aを含むトランジスタのチャネルを電流が流れる方向を第1の方向とすると、半導体層150bを含むトランジスタのチャネルを電流が流れる方向は第1の方向と平行且つ逆の第2の方向、半導体層150cを含むトランジスタのチャネルを電流が流れる方向は第1の方向である。また、半導体層150aのゲート電極152と重なっている部分の幅159aと半導体層150cのゲート電極152と重なっている部分の幅159cの幅を足した長さは、半導体層150bがゲート電極152と重なっている部分の幅159bと一致するように形成されている。

**【 0 0 6 9 】**

10

20

30

40

50

以上の構成を有することにより、何らかの理由により2層目のゲート電極の形成位置が長さ方向にずれてしまっても、半導体層150aを含むトランジスタにおけるドレイン側の2層目のゲート電極152bのみと重なっている半導体層150aの面積と半導体層150cを含むトランジスタにおけるドレイン側の2層目のゲート電極152bのみと重なっている半導体層150cの面積の和の増加(減少)量と、半導体層150bを含むトランジスタにおけるドレイン側の2層目のゲート電極152bの面積の減少(増加)量の絶対値は等しい。半導体層の不純物領域とゲート電極が重なっている面積の変化量に合わせて容量も変化するため、当該3つのトランジスタを合わせて一つのトランジスタとしてみなしている本発明のトランジスタ151としての寄生容量の変化は0となる。すなわち、本実施の形態における構成の薄膜トランジスタ151は実施の形態1に記載の薄膜トランジスタ105と実質的に同じ構成であり、マスクのずれによる容量変化の影響がほぼない構成であるということができる。10

#### 【0070】

これにより、大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子を提供することができる。また、そのような半導体素子を搭載した、薄膜半導体回路及び薄膜半導体装置を提供することができる。

#### 【0071】

また、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供することが出来る。また、そのような半導体素子を搭載した薄膜半導体回路及び薄膜半導体装置を提供することができるようになる。20

#### 【0072】

またさらに、同じパターンが並んでいる方向に長さ方向をあわせこんで、本発明の薄膜トランジスタを配列させると、さらに回路負荷のバラツキの少ない回路を形成することができるようになり望ましい構成である。

#### 【0073】

なお、本実施の形態では本発明のトランジスタ151は3つのトランジスタにより構成されているが、本発明はこれに限らず、本発明のトランジスタを構成する、ソース領域同士ドレイン領域同士及びゲート電極同士が各々電気的に接続しているトランジスタのうち、チャネルを第1の方向に電流が流れるトランジスタにおけるゲート電極と重なる半導体層の幅の和とチャネルを第1の方向と平行且つ逆の方向である第2の方向に電流が流れるトランジスタにおけるゲート電極と重なる半導体層の幅の和が等しい構成であれば本発明のトランジスタを構成するトランジスタはいくつであっても構わない。30

#### 【実施例1】

#### 【0074】

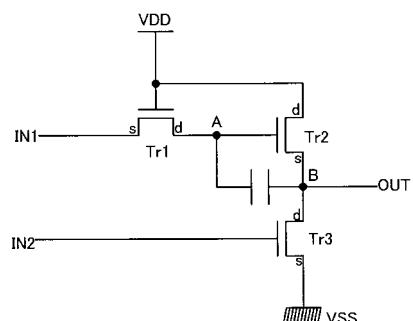

本実施例では、本発明の薄膜トランジスタを用いた例としてブートストラップ法を用いたインバータ回路について説明する。3つあるトランジスタはそれぞれTr1、Tr2、Tr3と、容量をC1と、Tr2のゲート電極に由来する寄生容量をC2と称することにする。

#### 【0075】

ブートストラップ法を用いたインバータ回路の等価回路を図5に示し、その動作について説明する。なお、VDD = 16V、VSS = 0V、各トランジスタのしきい値Vth = 3Vとする。IN1に16V、IN2に0Vが入力されると、Tr1がオンし、A節点の電位が入力電位からTr1のしきい値分下がった電圧(本実施例では16V - 3V = 13V)まで充電される。A節点の電位が13Vまで上昇すると、Tr1はオフし、A節点は浮遊状態となる。40

#### 【0076】

一方、A節点が充電されてゆき、Tr2のしきい値(3V)を超えた段階で、Tr2がオンし、B節点の電圧が上昇し、出力電圧も上昇する。A節点が浮遊状態にあることで、B節点の電圧が上昇すると、容量結合によりA節点の電圧が上昇し、Tr2のゲート電圧50

も上昇する。Tr2のゲート電圧が上昇し、その電圧が19V(16V+3V)以上になるとTr2の出力電圧はTr2の入力電圧と同じ16Vとなる。浮遊状態にあるA節点の電圧の上昇VAはB節点における電圧の上昇をVBとすると $V_A = V_B \times C_1 / (C_1 + C_2)$ で表される。すなわち、回路の動作に薄膜トランジスタにおけるゲート電極由来の寄生容量が関わってくる。

#### 【0077】

このような回路では、何らかの理由(基板の収縮やアライメントのずれ、歪みによるマスクずれなど)により薄膜トランジスタTr2のゲート電極に由来する寄生容量が変化すると、その動作に影響がでてしまい、これを考慮して動作マージンを設定しなければいけなくなる。

10

#### 【0078】

しかし、この回路の少なくともTr2に本発明の薄膜トランジスタを用いると、マスクずれが発生してもゲート電極と低濃度不純物領域との間に発生する寄生容量の変化を抑えることが可能であるため、マスクずれの影響を受けることがほとんどない回路を作製することが可能になる。

#### 【0079】

特に、熱処理などにより発生する基板の熱収縮によるマスクずれは基板の中心に向かって収縮するため、場所によりずれる方向が異なってくる。ずれる方向が異なると、寄生容量が小さくなる場所と大きくなる場所が出てくるため、その動作への影響がさらに大きくなるが、本発明の薄膜トランジスタを用いて作製された回路においては、その影響を抑えることが可能であるため、動作マージンの確保という面で非常に有利である。この場合、基板の収縮によってバラツキが顕著に表れる方向(すなわち、基板の収縮方向に向かって同じパターンが繰り返されている方向)に当該寄生容量の変化が問題となるTr2の長さ方向をあわせこむと、回路負荷のバラツキの少ない回路を作製することができる。

20

#### 【0080】

これにより、大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような薄膜半導体回路及び薄膜半導体装置を提供することができる。

#### 【0081】

また、多少のマスクずれが生じたとしても、その影響を受けずに動作するような薄膜半導体回路及び薄膜半導体装置を提供することができるようになる。

30

#### 【0082】

本実施例と実施の形態1乃至実施の形態3は組み合わせて用いることが可能である。

#### 【実施例2】

#### 【0083】

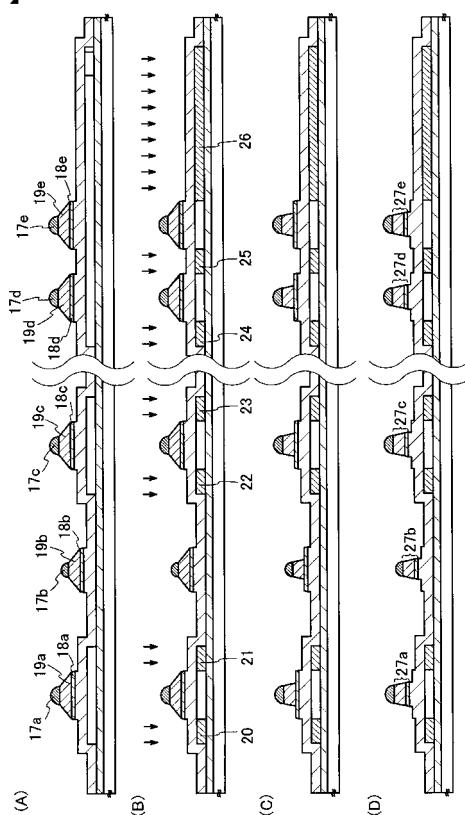

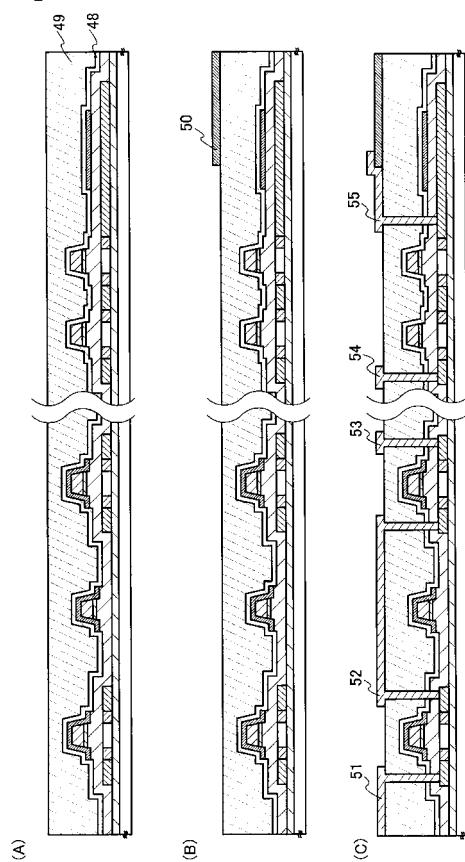

本発明の薄膜トランジスタを作製する方法について図6～図9を用いて説明する。

#### 【0084】

まず、基板10上に下地絶縁膜11を形成してから非晶質ケイ素膜を成膜し、レーザを照射することで結晶質ケイ素膜12とする。

40

#### 【0085】

基板10としてはガラス基板、石英基板、結晶性ガラスなどの絶縁性基板や、セラミック基板、ステンレス基板、金属基板(タンタル、タングステン、モリブデン等)、半導体基板、プラスチック基板(ポリイミド、アクリル、ポリエチレンテレフタレート、ポリカーボネート、ポリアリレート、ポリエーテルスルホン等)等を用いることができるが、少なくともプロセス中に発生する熱に耐えうる材料を使用する。これら基板は必要に応じてCMP等により研磨してから使用してもよい。本実施の形態においてはガラス基板を使用する。

#### 【0086】

下地絶縁膜11は基板10中のアルカリ金属やアルカリ土類金属が、結晶性ケイ素膜中に拡散するのを防ぐために設ける。このような元素は結晶性ケイ素膜の半導体特性に悪影

50

響をおよぼしてしまうためである。材料としては酸化ケイ素、窒化ケイ素、窒化酸化ケイ素及び窒化酸化ケイ素などを用いることができ、単層または積層構造とすることにより形成する。なお、アルカリ金属やアルカリ土類金属の拡散の心配のない基板であれば特に下地絶縁膜は設ける必要がない。

#### 【0087】

本実施例においては下地絶縁膜11は積層構造により形成し、1層目の絶縁膜として窒化酸化ケイ素膜を50nm、2層目の絶縁膜として酸化窒化ケイ素膜を100nmで形成した。なお、窒化酸化ケイ素膜と酸化窒化ケイ素膜はその窒素と酸素の割合が異なっていることを意味しており、前者の方がより窒素の含有量が高いことを示している。どちらもプラズマCVD法を用いて形成すればよい。

10

#### 【0088】

続いて下地絶縁膜上に非晶質ケイ素膜を25～100nm（好ましくは30～60nm）の膜厚で形成する。作製方法としては、公知の方法、例えばスパッタ法、減圧CVD法、またはプラズマCVD法等が使用できる。本実施例では、プラズマCVD法により膜厚50nmに形成する。その後、500、1時間の加熱処理を行って、水素だしを行う。

#### 【0089】

次に、レーザ照射装置を用いて、非晶質ケイ素膜を結晶化して、結晶質半導体膜を形成する。本実施例のレーザ結晶化には、エキシマレーザを使用し、発振されたレーザビームを光学系を用いて長方形状のビームスポットに加工し、半導体膜に照射する。

20

#### 【0090】

結晶化の方法としては他に非晶質ケイ素膜の結晶化を促進する元素を用い、加熱処理を行うことによって行う方法もある。結晶化を促進する元素とは、代表的にはニッケルが挙げられ、このような元素を用いることによって用いない場合に比べて低温、短時間で結晶化が行われるためガラス基板など比較的熱に弱い基板を使用する際に好適に用いることが可能である。このような結晶化を促進する元素としては、ニッケルの他に鉄、パラジウム、スズ、鉛、コバルト、白金、銅、金などがある。この中から一種もしくは複数種を用いればよい。また、この後、さらに結晶性を改善するため、レーザなどを照射しても良い。

#### 【0091】

また、プラズマCVD等で形成した微結晶半導体膜をさらにレーザにより結晶化して結晶質半導体膜として用いても良い。

30

#### 【0092】

続いて、結晶質ケイ素膜に必要に応じてしきい値をコントロールするための微量の不純物を添加する、いわゆるチャネルドーピングを行う。要求されるしきい値を得るために、ボロンもしくはリン等をイオンドーピング法などにより添加する。

#### 【0093】

その後、図6(B)に示すように、所定の形状にパターニングし、島状の結晶質ケイ素膜13a～13cを得る。パターニングは、結晶質ケイ素膜にフォトレジストを塗布し、所定のマスク形状を露光し、焼成して、結晶性半導体膜上にマスクを形成し、このマスクを用いて、ドライエッティング法により結晶質ケイ素膜をエッティングすることで行われる。ドライエッティング法のガスは、CF<sub>4</sub>と、O<sub>2</sub>等を用いて行えば良い。半導体層13a、13bは図1における101a、101bに相当する本発明の薄膜トランジスタの活性層となる半導体層である。図6～図9のA-B部は図1におけるA-Bの断面図に相当する。また、A-B部に形成される薄膜トランジスタは実施の形態2に示したような形状であっても良い。

40

#### 【0094】

続いて、結晶性半導体膜13a～13cを覆うようにゲート絶縁膜14を形成する。ゲート絶縁膜はプラズマCVD法またはスパッタ法を用い膜厚を40～150nmとしてケイ素を含む絶縁膜で形成する。本実施例では、ゲート絶縁膜はプラズマCVD法により酸化ケイ素膜を100nmの厚さに形成する。

#### 【0095】

50

次いで、ゲート絶縁膜上に第1の導電層として膜厚30～60nmの窒化タンタル(TaN)15とその上に第2の導電層として膜厚200～400nmのタンゲステン(W)16を形成する。本実施例では30nmのTaN膜と370nmのW膜を成膜した。TaN膜、W膜共スパッタ法で形成すればよく、TaN膜はTaのターゲットを用いて窒素雰囲気中で、W膜はWのターゲットを用いて成膜すれば良い(図6(C))。

#### 【0096】

次に、前記導電層をエッチングして電極及び配線を形成するため、フォトリソグラフィーにより露光工程を経てレジストからなるマスク17a～17eを形成する。次に、図7(A)に示すようにレジストからなるマスク17a～17eを後退させながら第1の導電膜18a～18e及び第2の導電膜19a～19eをテーパー形状にエッチングする。

10

#### 【0097】

次に図7(B)に示すようにレジストパターン17a～17e及び第2の導電膜19a～19eをマスクとしてソース、ドレイン領域20～25及び容量電極26を形成するための高濃度のN型不純物、例えばリンを半導体層13a～13cにイオンドーピングする。リンのドーピング条件はゲート絶縁膜14の膜厚及び不純物活性化条件により異なるが、本実施例ではゲート絶縁膜を酸化ケイ素膜で100nm形成したため、加速電圧を40kVとし、ドーズ量を $1 \times 10^{15} \sim 8 \times 10^{15}$ atoms/cm<sup>2</sup>とする。

#### 【0098】

この後、図7(C)に示すようにレジストパターン17a～17eをマスクとして第2の導電膜19a～19eのみを選択的にエッチングする。これにより第1の導電膜18a～18eを露出させ、その露出長がチャネル方向に約1μmとなるように第2の導電膜19a～19eが加工される。

20

#### 【0099】

次に図7(D)に示すように、レジストパターン17a～17e及び第2の導電膜19a～19eをマスクとして第1の導電膜18a～18eをエッチングすることにより、第1の導電膜18a～18eの露出した部分が除去され、第1の導電膜18a～18e及び第2の導電膜19a～19eからなる1層目のゲート電極27a～27eが形成される。

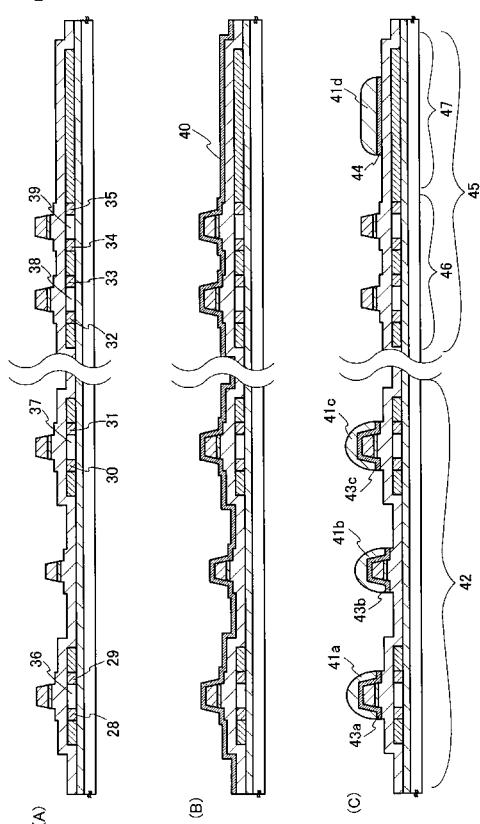

#### 【0100】

次に図8(A)に示すようにレジストパターン17a～17eを除去する。次いで、1層目のゲート電極27a、27c～27eをマスクとしてLDD領域(低濃度不純物領域)28～35を形成するための低濃度のN型不純物、例えばリンを半導体層13a～13cにイオンドーピングする。これによりNチャネル型薄膜トランジスタの各々のチャネル領域36～39は各々のゲート電極とほぼ同じ寸法となり、LDD領域28～35もゲート電極に対して自己整合的に形成される。また、容量素子の形成領域にもリンが導入される。なお、LDD領域は少なくともドレイン領域側に形成されれば良い。

30

#### 【0101】

次いで550の温度で熱処理を施す。この際、ゲート電極が露出した状態であるため、ゲート電極が酸化されないように酸素の少ない雰囲気中で熱処理を行うと良い。この熱処理により、半導体層に導入した不純物が活性化される。また、結晶化を促進する元素を用いて結晶化を行った場合にはチャネル領域に含まれる結晶化を促進する元素が高濃度不純物領域(ソース領域及びドレイン領域)に取り込まれてゲッタリングを行うこともできる。

40

#### 【0102】

この活性化処理において熱をかけるため、基板の収縮が起こる場合がある。この時点ですべてが収縮してしまうと、次から形成される2層目のゲート電極43a～43cの形成位置が意図した場所からずれて形成されてしまう。これがゲート寄生容量の変化となり、薄膜トランジスタの特性や当該薄膜トランジスタを用いて形成された回路の動作に影響を及ぼし、バラツキが発生してしまう恐れがある。特に、表示装置のドライバなどは同じ単位を繰り返し形成するため、そのバラツキが感知されやすくなってしまう。また、基板の一端と反対の一端では熱収縮した場合、ずれる方向が逆となるため、その影響はさらに顕著

50

となる。しかし、本実施例のように本発明の薄膜トランジスタを用いることでそれらの影響を抑えることが可能となり、画質の向上や不良の減少につながる。また、第3の導電膜40を形成した後、2層目のゲート電極43a～43cを形成する為に第3の導電膜40をエッティングする際に単にアライメントがずれてしまう事によって2層目のゲート電極43a～43cの形成位置がずれてしまうことも考えられるが、これによる影響も本発明の薄膜トランジスタや半導体装置を用いることによって同様に緩和することができる。この場合、基板の収縮によってバラツキが顕著に表れる方向（すなわち、基板の収縮方向に向かって同じパターンが繰り返されている方向）に長さ方向をあわせこむと、さらに有効に回路負荷のバラツキの少ない回路を作製することができる。

## 【0103】

また、大型基板になると熱収縮の影響も大きくなる上に、フォトレジストを露光する際、場所毎に複数回に分けて露光（つなぎ露光）する場合がある。つなぎ露光を行う場合は特にマスクのアライメントを合わせることが難しいため、本発明の薄膜トランジスタや半導体装置を適用すると有利である。

## 【0104】

熱処理を行ったら、続いて図8(B)に示すようにゲート電極を含む全面上に低抵抗な材料からなる第3の導電膜40を成膜する。本実施例においては、この時点ですでに不純物の活性化などの工程が終了しており、これ以降の工程において高い熱をかけることがないため、A1によって第3の導電膜40を形成することが可能となる。

## 【0105】

続いて、図8(C)に示すように第3の導電膜40の上にフォトレジスト膜を塗布し、このフォトレジスト膜を露光、現像することにより、第3の導電膜40上にはレジストパターン41a～41dが形成される。次いでこのレジストパターン41a～41dをマスクとして第3の導電膜40をエッティングすることによって、駆動回路部42の薄膜トランジスタのゲート電極27a～27c上には2層目のゲート電極43a～43cが形成され、容量電極となる高濃度不純物拡散層26上にはゲート絶縁膜14を介して第2の容量電極44が形成される。2層目のゲート電極は形成前に活性化の熱処理を行っているため、基板の収縮が起きてしまっている。また、マスクアライメントのずれなどによって実際予定した形成場所と異なる位置に2層目のゲート電極43a～43c及び第2の容量電極44が形成されてしまう場合もある。しかし、本発明を適用することで、その影響による薄膜トランジスタの寄生容量変化が抑制される。

## 【0106】

なお、第3の導電膜40はCu、Agなどでもかまわないがこれらの金属は熱に強いため、第3の導電膜40を形成した後に活性化などの熱処理を行ってもかまわない。この場合は基板の熱収縮による2層目のゲート電極43a～43c及び第2の容量電極44のそれは起こらないのでマスクアライメントのずれの影響を本発明により抑制することができる。

## 【0107】

このようにして駆動回路部42のNチャネル型薄膜トランジスタをゲートオーバーラップLCD構造とし、画素部45のNチャネル型薄膜トランジスタ46をLCD構造とすることができる。ゲートオーバーラップ構造の薄膜トランジスタは電流駆動能力が大きく、電源電圧10～20Vにおけるホットキャリア劣化耐性も良好である。また、同時に形成されるLCD構造の薄膜トランジスタはオフリーク電流の抑制に有効であることが確認されている。つまり、画素信号を容量素子に保持して画素を表示する液晶表示装置では、画素のスイッチング素子としてオフリーク電流の抑制に優れたLCD構造の薄膜トランジスタを使用することが望ましく、周辺の駆動回路部としては電流駆動能力に優れ、ホットキャリア劣化耐性に優れたゲートオーバーラップLCD構造を使用することが好ましい。この点は発光表示装置の場合も同様である。

## 【0108】

2層目のゲート電極43a～43cを構成する材料は低抵抗金属材料が好ましく、低抵

10

20

30

40

50

抗金属材料として Al または Al 合金の単層膜、または Al を主とした積層膜を用いることが好ましい。

#### 【 0 1 0 9 】

本実施例では、ゲート電極が積層構造である薄膜トランジスタの作製方法を説明しているが、本発明の薄膜トランジスタはこの構造に限らず適用することができる。例えば、フォトレジストによるマスクをゲート絶縁膜上に形成し、高濃度不純物領域、及び LDD 領域のドーピングを行い、フォトレジストを除去し、不純物の活性化を行い、その後ゲート電極を形成して作製されたようなゲート電極が 1 層である薄膜トランジスタにおいても本発明の構成は適用できる。そして、この構成においてもゲート電極形成時のマスクずれ、熱処理による基板の収縮などによる不都合を緩和することができる。

10

#### 【 0 1 1 0 】

第 2 の容量電極 44 とゲート絶縁膜 14 と容量電極 26 から容量素子 47 が構成される。容量素子 47 を薄膜トランジスタ構造と同じ構造とし、容量電極 26 をソース及びドレイン領域と同一層とすることによって第 2 の容量電極 44 を 0 V としても安定した容量を得ることができる。また、ゲート絶縁膜 14 を薄くすることによって容量素子 47 の面積を小さくできる。従って、図 7 に示す第 1 の導電膜 18a ~ 18e 及び第 2 の導電膜 19a ~ 19e をエッティングする工程で容量素子形成領域のゲート絶縁膜 14 を薄くすることによってその膜厚を薄くすることが好ましい。これにより、エッティング工程を増やすことなく、容量素子の面積を小さくすることが可能となる。

20

#### 【 0 1 1 1 】

この後、図 9 (A) に示すように 2 層目のゲート電極 43a ~ 43c 及び第 2 の容量電極 44 を含む全面上に水素を含有した絶縁膜例えば窒化ケイ素膜 48 を成膜した後、350 以上の水素化の熱処理を行う。この熱処理により、半導体層（結晶性ケイ素膜）の結晶欠陥部を水素終端することができる。なお、本実施例では、水素を含有した窒化ケイ素 48 を成膜した後に水素化の熱処理を行っているが、酸化ケイ素膜を成膜したのち、3 ~ 100 % の水素含有雰囲気中で 350 度以上の熱処理を行うことで同様の効果を得ることも可能である。窒化ケイ素膜は比誘電率が酸化ケイ素膜の約 2 倍であるため、窒化ケイ素膜を用いた場合に比べて回路動作の負担を小さくする事ができ、電極間の容量を小さくする事ができる。

30

#### 【 0 1 1 2 】

次いで、窒化ケイ素膜 48 の上に自己平坦性のある有機、もしくは無機絶縁膜により層間絶縁膜 49 を形成する。無機絶縁膜としては、CVD 法により形成された酸化ケイ素膜や、SOG (Spin On Glass) 法により塗布された酸化ケイ素膜、また、ケイ素と酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む、または置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも 1 種を有する材料、いわゆるシロキサンの膜などを用いることができ、有機絶縁膜としてはポリイミド、ポリアミド、BCB (ベンゾシクロブテン)、アクリルまたはポジ型感光性有機樹脂、ネガ型感光性有機樹脂等を用いることができる。また、low-k 材料も好適に用いることができる。また、それらの積層構造を用いても良い。本実施例では感光性のポリイミドにより層間絶縁膜 49 を形成した。

40

#### 【 0 1 1 3 】

次に、図 9 (B) に示すように層間絶縁膜 49 の上にITO 等の透明導電膜からなる画素電極 50 を形成する。

#### 【 0 1 1 4 】

次いで図 9 (C) に示すように層間絶縁膜 49、窒化ケイ素膜 48 及びゲート絶縁膜 14 にソース領域及びドレイン領域に到達するコンタクトホール（接続孔）をエッティング法により形成する。次いでコンタクトホール内及び層間絶縁膜 49 上に低抵抗な材料からなる導電膜を成膜し、この導電膜をエッティング加工する。これにより、駆動回路部 42 の N チャネル型薄膜トランジスタ及び画素部の N チャネル型薄膜トランジスタ 46 のそれぞれには導電膜からなるソース電極及びドレイン電極 51 ~ 55 が形成され、ドレイン電極 5

50

5は画素電極50に接続される。なお、ソース電極及びドレイン電極51～55はAl、Cu等の単層電極としても良いが、積層構造としても良く、特に電極材料の半導体層への拡散を防止すると共にストレスマイグレーションなどにより発生するヒロックを防止する場合には、上層からTiN、Al、TiN、Tiが順に積層された積層構造としても良い。

### 【0115】

本実施例により形成される半導体装置は駆動回路部42及び画素部45にはNチャネル型薄膜トランジスタのみが形成されており、Pチャネル型薄膜トランジスタは形成されていないが、Pチャネル型薄膜トランジスタを形成する構成であっても良い。この際、工程の違いは不純物元素の導入工程だけである。

10

### 【0116】

また、容量素子47は、画素スイッチング素子を介して画素に伝えられる画素信号を保持するためのものであり、Nチャネル型薄膜トランジスタ46のソース領域及びドレイン領域と同一層の高濃度不純物領域からなる容量電極と、前記薄膜トランジスタ46のゲート絶縁膜14と第2の容量電極44とからなるものである。

### 【0117】

本実施例によれば、同一基板上にゲートオーバーラップLDD構造の薄膜トランジスタ及びLDD構造の薄膜トランジスタを工程数の増大なしに形成できる。また、LDD構造の薄膜トランジスタを形成した後に不純物活性化のための熱処理を行ってからゲートオーバーラップLDD構造形成用及びゲート電極配線の低抵抗化用の2層目のゲート電極を形成するため、低抵抗で安価ではあるが耐熱性の低いAlを主成分とする材料を使用することができる。これにより大型の画像表示装置においても高速駆動が可能で画像表示性能の優れた画像表示装置を低価格で提供することができる。

20

### 【実施例3】

### 【0118】

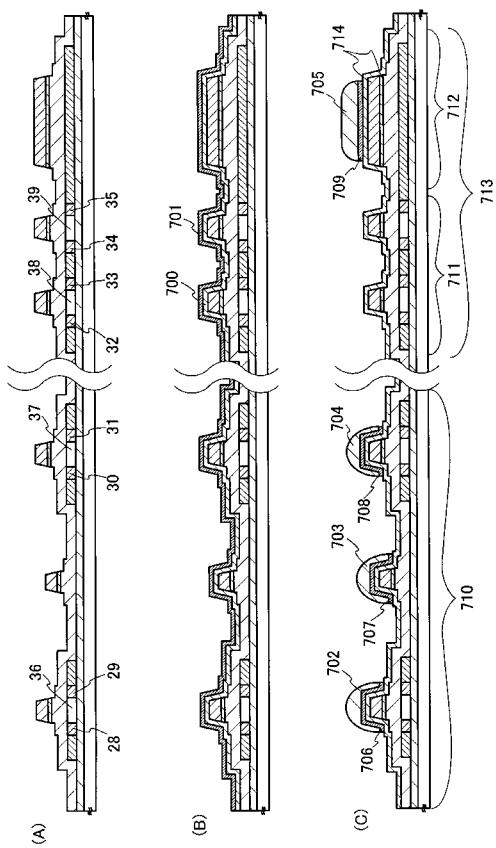

本実施例では、実施例2と異なる構成の薄膜トランジスタに本発明を適用する例を図10を参照しながら説明する。なお、図10に至るまでの工程は図6～図8(A)までと同一であるので、説明を省略する。図10(A)と図8(A)が同一の状態にある。

### 【0119】

図10(A)の状態を得たら、基板全面に絶縁膜700を形成する。絶縁膜は窒化ケイ素や酸素を含む窒化ケイ素膜により単層、もしくは多層で形成する。これらはプラズマCVD法など公知の方法により形成すればよい。

30

### 【0120】

続いて、550℃の温度で熱処理を施す。この際、ゲート電極及び配線が絶縁膜700で覆われているため、ゲート電極及び配線が酸化されるのを防止できる。この熱処理により、半導体層に導入した不純物が活性化されると共に、チャネル領域に含まれるNiが高濃度不純物領域(ソース及びドレイン領域)に取り込まれてゲッタリングが行われる。なお、前記熱処理は、炉アニール法、ランプアニール法、レーザアニール法のいずれの方法を用いても良い。次いで、絶縁膜700の上に低抵抗な材料からなる第3の導電膜701を成膜する。なお、第3の導電膜701は、窒化チタンなどのバリア膜とAlまたはAl合金からなる膜とを積層した積層膜あるいはAlまたはAl合金からなる膜で形成されていても良い。

40

### 【0121】

次に、第3の導電膜701の上にフォトレジスト膜を塗布し、このフォトレジスト膜を露光、現像することにより、第3の導電膜701上にはレジストパターン702～705が形成される。次いで、このレジストパターン702～705をマスクとして第3の導電膜701をエッチングすることにより、図10(C)に示すように、駆動回路部710の薄膜トランジスタのゲート電極上には絶縁膜700を介して2層目のゲート電極706～708が形成され、容量電極714上には絶縁膜700を介して2層目の容量電極709が形成される。2層目の容量電極709と絶縁膜700と容量電極714から容量素子7

50

12が構成される。711と713はそれぞれ画素TFTと画素部に相当する。

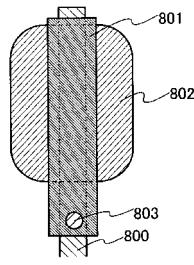

#### 【0122】

この後、図9(A)から示した工程と同様の工程で表示装置を作成することができる。本実施例の構成は、2層目のゲート電極706～708と1層目のゲート電極との間に絶縁膜700があり、図11のように1層目のゲート電極800と2層目のゲート電極801が接続されている。また、2層目のゲート電極706～708と絶縁膜700、1層目のゲート電極により補助容量を形成することが可能な構成となっている。

#### 【実施例4】

#### 【0123】

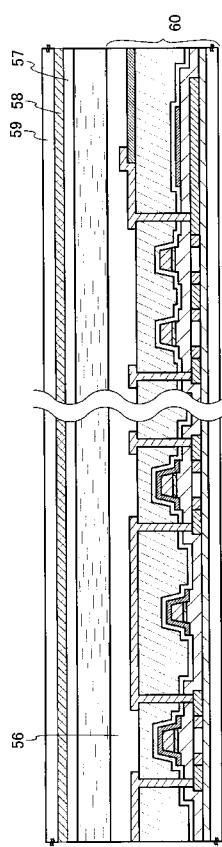

本実施例では、実施例2に記載の方法により作製された基板を用いて液晶表示装置を作成する方法について図12を参照しながら説明する。画素電極50を覆うように、配向膜と呼ばれる絶縁体層56を形成する。なお、絶縁体層56は、スクリーン印刷法やオフセット印刷法を用いれば、選択的に形成することができる。その後、ラビングを行う。続いて、シール材を画素を形成した周辺の領域に形成する。

#### 【0124】

その後、配向膜として機能する絶縁体層57、対向電極として機能する導電体層58が設けられた対向基板59と素子基板60とをスペーサを介して貼り合わせ、その空隙に液晶層を設けることにより液晶表示パネルを作製することができる。シール材にはフィラーが混入されていても良く、さらに対向基板59には、カラーフィルタや遮蔽膜(ブラックマトリクス)などが形成されていても良い。なお、液晶層を形成する方法として、ディスペンサ式(滴下式)や、対向基板59を貼り合わせてから毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いることができる。

#### 【0125】

ディスペンサ方式を採用した液晶滴下注入法は、シール材で閉ループを形成し、その中に液晶を1回もしくは複数回滴下する。続いて、真空中で基板を貼り合わせ、その後紫外線硬化を行って、液晶が充填された状態とする。

#### 【0126】

この後、異方性導電体層を介して、接続用の配線基板を設ける。配線基板は、外部からの信号や電位を伝達する役目を担う。上記工程を経て、液晶表示パネルが完成する。

#### 【0127】

以上の工程により、本発明の薄膜トランジスタ及び半導体装置を有する液晶表示装置を製造することができる。

#### 【実施例5】

#### 【0128】

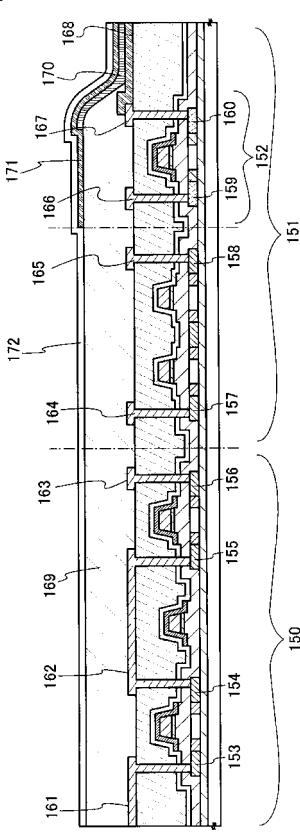

本発明の薄膜トランジスタを用いて、発光表示装置を作成する例について図13を参照しながら説明する。実施例2に示したと同様に基板10上に駆動回路部150及び画素部151の薄膜トランジスタを形成する。薄膜トランジスタのレイアウト及び半導体層に導入する不純物元素については求める性能に応じて適宜変更すればよい。本実施例では、ゲート電極の一部として使用される第2の導電膜をモリブデンで形成し、発光素子の駆動用トランジスタ152をPチャネル型トランジスタとして、層間絶縁膜49を形成するところから説明する。

#### 【0129】

本実施例では、シロキサンにより層間絶縁膜49を形成する。層間絶縁膜49は、シロキサン系ポリマーを全面塗布した後、50～200、10分間の熱処理によって乾燥させ、さらに300～450、1～12時間の焼成処理を行うことで形成する。この焼成により、1μm厚のシロキサンの膜が全面に成膜される。この工程は、シロキサン系ポリマーの焼成を行うと共に、窒化ケイ素膜48中の水素によって、半導体層を水素化及び不純物の活性化をする。

#### 【0130】

この後、層間絶縁膜49を覆うように、CVD法により窒化酸化ケイ素膜または酸化窒

10

20

30

40

50

化ケイ素膜を形成しても良い。この膜は、後に形成される導電膜をエッティングするときに、エッティングストッパーとして働き、層間絶縁膜のオーバーエッティングを防止することができる。また、この酸化窒化ケイ素膜は配線エッティング時に同時にエッティングされて無くなる程度の厚さに形成するとこの後の形成する発光素子の信頼性に対して良い影響を及ぼす。

#### 【0131】

次に、層間絶縁膜49のパターニング及びエッティングを行い、高濃度不純物領域153～160に達するコンタクトホールを形成する。

#### 【0132】

続いて、コンタクトホール中に金属膜を積層し、パターニングしてソース電極及びドレイン電極を形成する。本実施例では、基板側からモリブデン、アルミニウム、モリブデンの三層構造でソース電極、ドレイン電極及び配線161～167を形成する。

#### 【0133】

続いてこれらの半導体素子を用いて発光装置を作成する工程に入る。

#### 【0134】

本実施例で説明する発光装置は一対の電極間に発光する物質を含む層を挟み込み、電極間に電流を流すことによって発光する素子をマトリクス状に配列させたものである。

#### 【0135】

発光素子の励起状態には一重項励起と三重項励起が知られ、発光はどちらの励起状態を経ても可能であると考えられている。故に、素子の特徴によって一つの発光装置内において、一重項励起状態の素子あるいは三重項励起状態の素子を混在させても良い。例えばRGBの三色において、赤に三重項励起状態を取る素子、青と緑に一重項励起状態を取る素子としても良い。また、三重項励起状態を取る素子は一般に発光効率が良いため、駆動電圧の低下にも貢献する。

#### 【0136】

発光素子の材料としては、低分子、高分子、低分子と高分子の間の性質を持つ中分子の発光材料があるが、本実施例では低分子の発光材料を使用する。低分子材料も高分子材料も溶媒に溶かすことでスピンドルコートやインクジェット法により塗布することができる。また、有機材料のみではなく、無機材料との複合材料も使用することができる。

#### 【0137】

前工程によって形成された薄膜トランジスタのドレイン電極167と一部重なるようにして、発光素子の第1の電極168を形成する。第1の電極168は発光素子の陽極、または陰極になる電極であり、陽極とする場合は仕事関数の大きい金属、合金、電気伝導性化合物、及びこれらの混合物などを用いることが好ましい。仕事関数としては仕事関数4.0eV以上がだいたいの目安となる。具体的な材料としては、ITO(indium tin oxide)、酸化インジウムに2～20%の酸化亜鉛(ZnO)を混合したIZO(indium zinc oxide)、酸化亜鉛にガリウムを添加したGZO、酸化インジウムに2～20%の酸化ケイ素(SiO<sub>2</sub>)を混合したITSO、金(Au)、白金(Plt)、ニッケル(Ni)、タンゲステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(TiN)等を用いることができる。

#### 【0138】

陰極として用いる場合は、仕事関数の小さい(仕事関数3.8eV以下が目安)金属、合金、電気伝導性化合物、及びこれらの混合物などを用いることが好ましい。具体的な材料としては、元素周期律の1族または2族に属する元素、すなわちLiやCs等のアルカリ金属、及びMg、Ca、Sr等のアルカリ土類金属、及びこれらを含む合金(Mg-Ag、Al-Li)や化合物(LiF、CsF、CaF<sub>2</sub>)の他、希土類金属を含む遷移金属を用いて形成することができる。但し、本実施例において第2の電極は透光性を有するように形成するため、これら金属、またはこれら金属を含む合金を非常に薄く形成し、ITO、IZO、ITSO、GZOまたはその他の金属(合金を含む)との積層により形成す

10

20

30

40

50

る。

#### 【0139】

本実施例では第1の電極168は陽極とし、ITSOを用いた。電極としてITSOを用いた場合は真空ベークを行うと発光装置の信頼性が向上する。

#### 【0140】

また、本実施例において第1の電極168は薄膜トランジスタのソース電極及びドレイン電極161～167を形成した後に形成されるが、先に第1の電極168を形成しその後薄膜トランジスタの電極を形成してもかまわない。

#### 【0141】

続いて第1の電極168の端部を覆うように絶縁膜169を形成する。この絶縁膜169は土手や隔壁と呼ばれるものである。絶縁膜169としては、無機絶縁膜や有機絶縁膜を用いることができる。無機絶縁膜としては、CVD法により形成された酸化ケイ素膜や、SOG(Spin On Glass)法により塗布された酸化ケイ素膜などを用いることができ、有機絶縁膜としては感光性または非感光性のポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリルまたはポジ型感光性有機樹脂、ネガ型感光性有機樹脂、ケイ素と酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む、または置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料、いわゆるシロキサンの膜を用いることができる。また、それらの積層構造を用いても良い。感光性の有機物を使用して形成すると、開口部の形状が曲率半径が連続的に変化する形状となり電界発光層を蒸着する際に段切れなどが起こりにくいものとなり好適である。本実施例では感光性のポリイミドを使用した。

#### 【0142】

続いて、蒸着装置を用いて、蒸着源を移動させながら発光層170の蒸着を行う。蒸着は真空度が $5 \times 10^{-3}$  Torr(0.665Pa)以下、好ましくは $10^{-4} \sim 10^{-6}$  Torrまで真空排気された成膜室で蒸着を行う。蒸着の際、抵抗加熱により、予め有機化合物は気化されており、蒸着時にシャッターが開くことにより基板の方向へ飛散する。気化された有機化合物は、上方に飛散し、メタルマスクに設けられた開口部を通って基板に蒸着され、発光層170(第1の電極側から正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層)を形成する。なお、発光層170の構成はこのような組み合わせの積層でなく、層の数が少なくて良いし、二つの層の機能を有する複合層でも良い。また単層、混合層で形成されていても良い。

#### 【0143】

本実施例では正孔注入層としてCuPcを20nm、正孔輸送層として-NPBを40nm、発光層としてAlqを50nm、電子注入層としてAl-Liを10nm形成する。

#### 【0144】

発光層170を形成したら、第2の電極171を発光層170に接して形成する。本実施例では第1の電極168が陽極であるため、第2の電極171は陰極として形成する。陰極材料は先に述べたような材料を使用すれば良く、本実施例ではアルミニウム膜を150nm形成することで第2の電極(陰極)171とする。

#### 【0145】

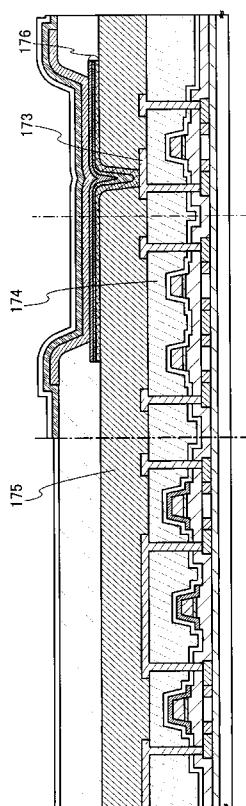

本実施例では第1の電極168のみ透光性を有する材料で形成されているため、基板の下面方向より光を取り出す構造である。図14は上面発光の構成の1例であり、画素電極176と薄膜トランジスタのソース電極及びドレイン電極161～165、167、173を異なる層に形成した例である。第1の絶縁膜174及び第2の層間絶縁膜175は図13における絶縁膜169と同様の材料で形成することができ、その組み合わせも自由に行えるが、今回はどちらの層もシロキサンにより形成する。画素電極176は第2の層間絶縁膜175側からAl-Si、TiN、ITSOの順に積層して形成したが、もちろん単層でもかまわないし、2層、あるいは4層以上の積層構造でもかまわない。

#### 【0146】

10

20

30

40

50

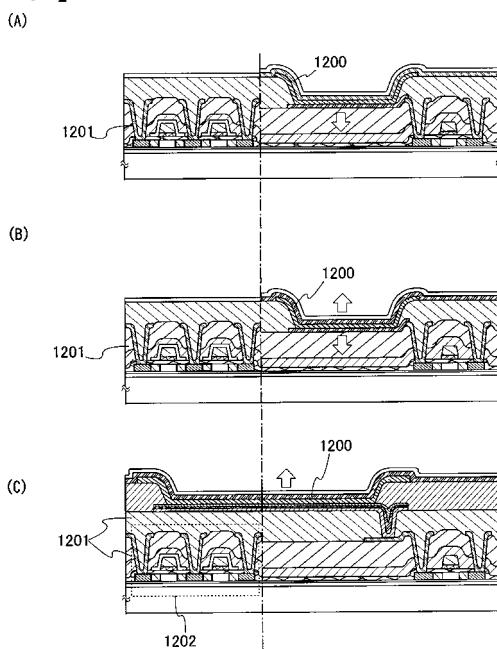

図15には下面発光、両面発光、上面発光の例を示した。本実施例に記載の下面から光を取り出す構造は図15(A)の構造に相当する。第2の電極1200の下にLiを含む材料を薄く(透光性を有する程度に)形成し、ITOやITSO、IZOなど透光性を有する材料を第2の電極として形成することで図15(B)のように両面より光を取り出すことのできる両面発光の発光表示装置を得ることが可能となる。なお、アルミニウムや銀など厚膜で形成すると非透光性であるが、薄膜化すると透光性を有するようになるため、アルミニウムや銀の透光性を有する程度の薄膜で第2の電極1200を形成すると両面発光とすることができます。

#### 【0147】

図15(C)は上面発光の発光装置の一例であるが、図14に相当する。上面発光はこのように層間絶縁膜1201を図15(A)(B)よりも多く形成すると、薄膜トランジスタ1202の上部にも発光素子を設けることができ、開口率の点で有利な構成となる。

#### 【0148】

ところで、両面発光や上面発光の場合に用いられる透明電極であるITOやITSOは抵抗加熱による蒸着が困難であるためスパッタ法、もしくは電子ビーム蒸着による成膜が行われる。第2の電極171をスパッタリング法にもしくは電子ビーム蒸着により形成する場合、電子注入層の表面もしくは電子注入層と電子輸送層の界面にダメージが入ってしまうことがある、発光素子の特性に悪影響を及ぼす可能性がある。これを防ぐためには、このようなダメージを受けにくい材料を第2の電極171に最も近い位置に設けるとよい。このようなダメージを受けにくい材料で、電界発光層170に用いることができる材料としては酸化モリブデン(MoO<sub>x</sub>)が挙げられる。しかし、MoO<sub>x</sub>は正孔注入層として好適な物質であるため、第2の電極171に接して設けるには第2の電極171を陽極とする必要がある。

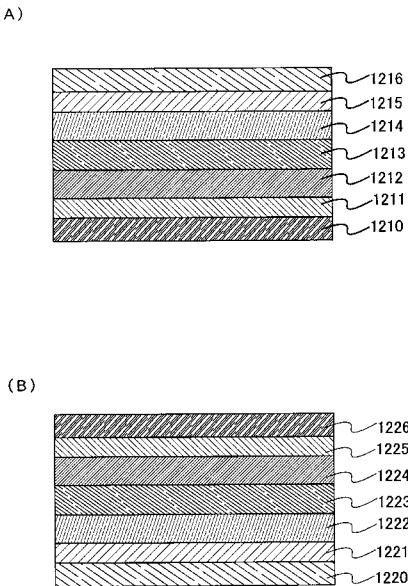

#### 【0149】

そこで、この場合は本実施例のように図16(A)の順(陽極1210、正孔注入層1211、正孔輸送層1212、発光層1213、電子輸送層1214、電子注入層1215、陰極1216)で形成するのではなく、図16(B)のように第1の電極168を陰極1220として形成し、その後順に、電子注入層1221、電子輸送層1222、発光層1223、正孔輸送層1224、正孔注入層(MoO<sub>x</sub>)1225、第2の電極(陽極)1226と形成する。また、画素の駆動用薄膜トランジスタはNチャネル型とする必要がある。本実施例の場合、発光素子駆動用のトランジスタ152はPチャネル型トランジスタを使用しているが、このような素子を用いることで基板上のトランジスタ全てをNチャネル型トランジスタとすることも可能となる。

#### 【0150】

MoO<sub>x</sub>は蒸着法により形成し、x = 3以上のものが好適に使用できる。また、MoO<sub>x</sub>層は銅フタロシアニン(CuPc)などの有機金属錯体や有機物と共に蒸着することで有機、無機の混合層としても良い。上記したような第1の電極168を陰極とする発光素子を用いた場合、画素部の薄膜トランジスタはもともとN型であるa-Si:Hを半導体層としたトランジスタを用いると工程が簡略化されて好適である。駆動回路部が同一基板上に形成されている場合は駆動回路部のみレーザ等を照射することで結晶化して用いるといい。

#### 【0151】

その後、プラズマCVD法により窒素を含む酸化ケイ素膜をパッシベーション膜172として形成した。窒素を含む酸化ケイ素膜を用いる場合には、プラズマCVD法でSiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>から形成される酸化窒化ケイ素膜、またはSiH<sub>4</sub>、N<sub>2</sub>Oから形成される酸化窒化ケイ素膜、あるいはSiH<sub>4</sub>、N<sub>2</sub>OをArで希釈したガスから形成される酸化窒化ケイ素膜を形成すれば良い。また、パッシベーション膜172としてSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>から形成される酸化窒化水素化ケイ素膜を適用しても良い。もちろん、パッシベーション膜172は単層構造に限定されるものではなく、他のケイ素を含む絶縁膜を単層構

10

20

30

40

50

造、もしくは積層構造として用いても良い。また、窒化炭素膜と窒化ケイ素膜の多層膜やスチレンポリマーの多層膜、窒化ケイ素膜やダイヤモンドライクカーボン膜を窒素を含む酸化ケイ素膜の代わりに、もしくはそれらとの積層構造として形成してもよい。

### 【0152】

続いて電界発光素子を水など劣化を促進する物質から保護するために、表示部の封止を行う。対向基板を封止に用いる場合は、絶縁性のシール剤により、外部接続部が露出するように貼り合わせる。対向基板と素子基板との間の空間には乾燥した窒素などの不活性気体を充填しても良いし、シール剤を画素部全面に塗布しそれにより対向基板を形成しても良い。シール剤には紫外線硬化樹脂などを用いると好適である。シール剤には乾燥剤やギャップを一定に保つための粒子を混入しておいても良い。続いて外部接続部にフレキシブル配線基板を貼り付けることによって、電界発光パネルが完成する。10

### 【0153】

このような電界発光パネルには単色、エリアカラー、フルカラーなどの表示方法があるが、フルカラーにはさらに、RGBの3色塗り分け法、白色光源をカラーフィルタによりRGB化する方法、短波長の色を色変換フィルタを使用して長波長の色に変換する方法などがある。また、色純度を向上させるために、カラーフィルタを用いる場合もある。

### 【0154】

なお、表示機能を有する本発明の発光表示装置には、アナログのビデオ信号、デジタルのビデオ信号のどちらを用いてもよい。デジタルのビデオ信号を用いる場合はそのビデオ信号が電圧を用いているものと、電流を用いているものとに分けられる。発光素子の発光時において、画素に入力されるビデオ信号は、定電圧のものと、定電流のものがあり、ビデオ信号が定電圧のものには、発光素子に印加される電圧が一定のものと、発光素子に流れる電流が一定のものとがある。またビデオ信号が定電流のものには、発光素子に印加される電圧が一定のものと、発光素子に流れる電流が一定のものとがある。この発光素子に印加される電圧が一定のものは定電圧駆動であり、発光素子に流れる電流が一定のものは定電流駆動である。定電流駆動は、発光素子の抵抗変化によらず、一定の電流が流れる。本発明の発光表示装置及びその駆動方法には、ビデオ信号の電圧を利用して駆動する方法もしくはビデオ信号の電流を用いて駆動する方法のどちらを用いてもよく、また定電圧駆動、定電流駆動のどちらを用いてもよい。20

### 【0155】

これにより、大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような表示装置を提供することができる。30

### 【実施例6】

### 【0156】

本実施例では、画素回路、保護回路及びそれらの動作について説明する。

### 【0157】

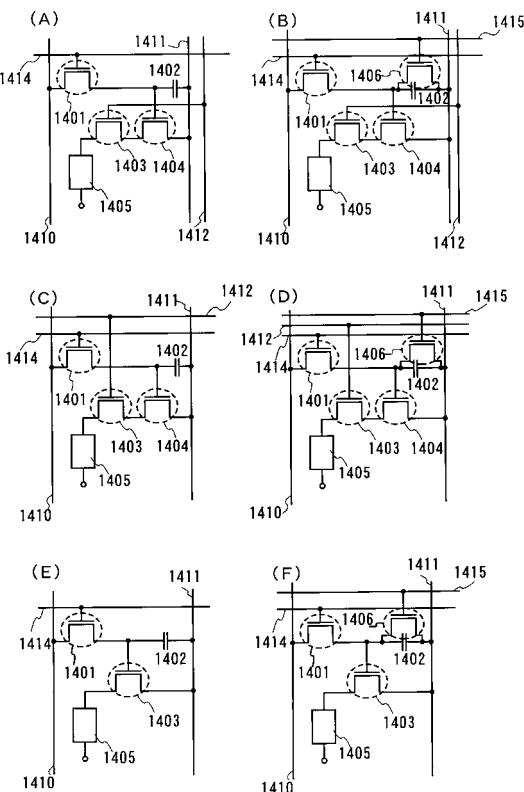

図17(A)に示す画素は、列方向に信号線1410及び電源線1411、1412、行方向に走査線1414が配置される。また、スイッチング用TFT1401、駆動用TFT1403、電流制御用TFT1404、容量素子1402及び発光素子1405を有する。40

### 【0158】

図17(C)に示す画素は、TFT1403のゲート電極が、行方向に配置された電源線1412に接続される点が異なっており、それ以外は図17(A)に示す画素と同じ構成である。つまり、図17(A)(C)に示す両画素は、同じ等価回路図を示す。しかしながら、行方向に電源線1412が配置される場合(図17(A))と、列方向に電源線1412が配置される場合(図17(C))とでは、各電源線は異なるレイヤーの導電膜で形成される。ここでは、駆動用TFT1403のゲート電極が接続される配線に注目し、これらを形成するレイヤーが異なることを表すために、図17(A)(C)として分けて記載する。

### 【0159】

10

20

30

40

50

図17(A)(C)に示す画素の特徴として、画素内にTFT1403、1404が直列に接続されており、TFT1403のチャネル長L(1403)、チャネル幅W(1403)、TFT1404のチャネル長L(1404)、チャネル幅W(1404)は、 $L(1403)/W(1403) : L(1404)/W(1404) = 5 \sim 6000 : 1$ を満たすように設定するとよい。

#### 【0160】

なお、TFT1403は、飽和領域で動作し発光素子1405に流れる電流値を制御する役目を有し、TFT1404は線形領域で動作し発光素子1405に対する電流の供給を制御する役目を有する。両TFTは同じ導電型を有していると作製工程上好ましく、本実施例ではnチャネル型TFTとして形成する。またTFT1403には、エンハンスマント型だけでなく、ディプリーション型のTFTを用いてもよい。上記構成を有する本発明は、TFT1404が線形領域で動作するために、TFT1404のVgsの僅かな変動は、発光素子1405の電流値に影響を及ぼさない。つまり、発光素子1405の電流値は、飽和領域で動作するTFT1403により決定することができる。上記構成により、TFTの特性バラツキに起因した発光素子の輝度ムラを改善して、画質を向上させた表示装置を提供することができる。

#### 【0161】

図17(A)～(D)に示す画素において、TFT1401は、画素に対するビデオ信号の入力を制御するものであり、TFT1401がオンとなると、画素内にビデオ信号が入力される。すると、容量素子1402にそのビデオ信号の電圧が保持される。なお図17(A)(C)には、容量素子1402を設けた構成を示したが、本発明はこれに限定されず、ビデオ信号を保持する容量がゲート容量などでまかぬうことが可能な場合には、容量素子1402を設けなくてもよい。

#### 【0162】

図17(B)に示す画素は、TFT1406と走査線1416を追加している以外は、図17(A)に示す画素構成と同じである。同様に、図17(D)に示す画素は、TFT1406と走査線1416を追加している以外は、図17(C)に示す画素構成と同じである。

#### 【0163】

TFT1406は、新たに配置された走査線1416によりオンまたはオフが制御される。TFT1406がオンとなると、容量素子1402に保持された電荷は放電し、TFT1404がオフとなる。つまり、TFT1406の配置により、強制的に発光素子1405に電流が流れないと状態を作ることができる。そのためTFT1406を消去用TFTと呼ぶことができる。従って、図17(B)(D)の構成は、全ての画素に対する信号の書き込みを待つことなく、書き込み期間の開始と同時に点灯期間を開始することができるため、デューティ比を向上することが可能となる。

#### 【0164】

図17(E)に示す画素は、列方向に信号線1410、電源線1411、行方向に走査線1414が配置される。また、スイッチング用TFT1401、駆動用TFT1403、容量素子1402及び発光素子1405を有する。図17(F)に示す画素は、TFT1406と走査線1415を追加している以外は、図17(E)に示す画素構成と同じである。なお、図17(F)の構成も、TFT1406の配置により、デューティ比を向上することが可能となる。

#### 【0165】

以上のように、多様な画素回路を採用することができる。特に、非晶質半導体膜から薄膜トランジスタを形成する場合、駆動用TFTの半導体膜を大きくすると好ましい。そのため、上記画素回路において、電界発光層からの光が封止基板側から射出する上面発光型とすると好ましい。

#### 【0166】

このようなアクティブマトリクス型の発光装置は、画素密度が増えた場合、各画素にT

10

20

30

40

40

50

F Tが設けられているため低電圧駆動でき、有利であると考えられている。

#### 【0167】

本実施例では、一画素に各TFTが設けられるアクティブマトリクス型の発光装置について説明したが、一列毎にTFTが設けられるパッシブマトリクス型の発光装置を形成することもできる。パッシブマトリクス型の発光装置は、各画素にTFTが設けられていないため、高開口率となる。発光が電界発光層の両側へ射出する発光装置の場合、パッシブマトリクス型の表示装置を用いると透過率が高まる。

#### 【0168】

続いて、図17(E)に示す等価回路を用い、走査線及び信号線に保護回路としてダイオードを設ける場合について説明する。

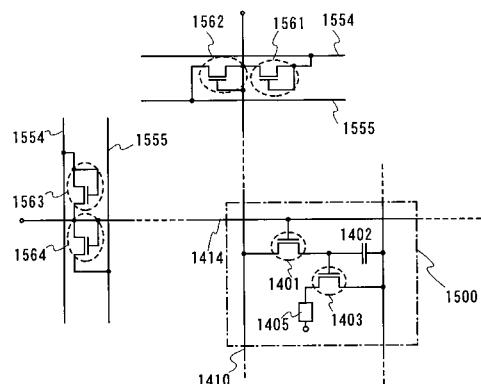

#### 【0169】

図18には、画素部1500にTFT1401、1403、容量素子1402、発光素子1405が設けられている。信号線1410には、ダイオード1561と1562が設けられている。ダイオード1561と1562は、TFT1401または1403と同様に、上記実施例に基づき形成され、ゲート電極、半導体層、ソース電極及びドレイン電極等を有する。ダイオード1561と1562は、ゲート電極と、ドレイン電極またはソース電極とを接続することによりダイオードとして動作させている。

#### 【0170】

ダイオードと接続する共通電位線1554、1555はゲート電極と同じレイヤーで形成している。従って、ダイオードのソース電極またはドレイン電極と接続するには、ゲート絶縁層にコンタクトホールを形成する必要がある。

#### 【0171】

走査線1414に設けられるダイオード1563、1564も同様な構成である。

#### 【実施例7】

#### 【0172】

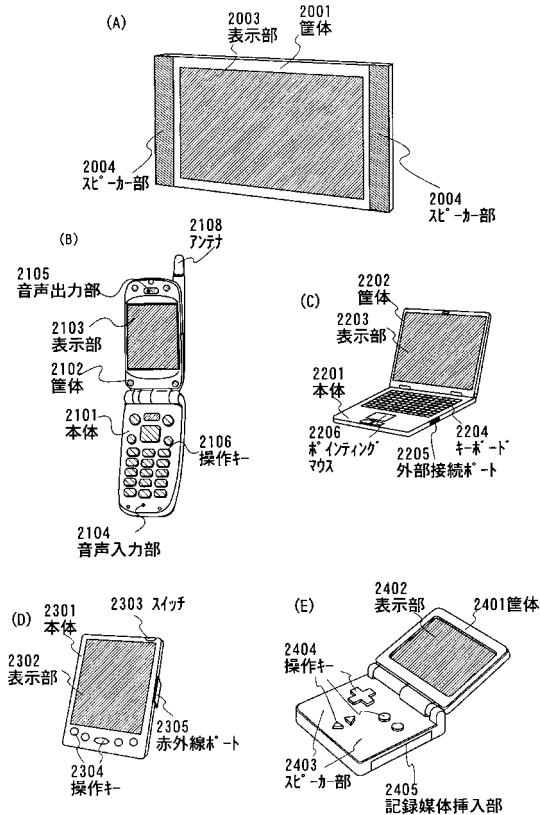

本発明が適用される電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を図19に示す。

#### 【0173】

図19(A)は発光表示装置でありテレビ受像器などがこれに当たる。筐体2001、表示部2003、スピーカー部2004等を含む。本発明は、表示部2003に適用される。本発明を使用することにより、歩留まりが向上し、表示の品質も向上する。画素部にはコントラストを高めるため、偏光板、または円偏光板を備えるとい。例えば、封止基板へ1/4板、1/2板、偏光板の順にフィルムを設けるとい。さらに偏光板上に反射防止膜を設けてもよい。

#### 【0174】

図19(B)は携帯電話であり、本体2101、筐体2102、表示部2103、音声入力部2104、音声出力部2105、操作キー2106、アンテナ2108等を含む。本発明の発光装置をその表示部2103に用いることによ形成される。本発明を使用することにより、歩留まりが向上し、表示の品質も向上する。

#### 【0175】

図19(C)はノート型パソコンコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。本発明は、表示部2203に適用することができる。本発明を使用することにより、歩留まりが向上し、表示の品質も向上する。

#### 【0176】

10

20

30

40

50

図19(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明は、表示部2302に適用することができる。本発明を使用することにより、歩留まりが向上し、表示の品質も向上する。

#### 【0177】

図19(E)は携帯型のゲーム機であり、筐体2401、表示部2402、スピーカー部2403、操作キー2404、記録媒体挿入部2405等を含む。本発明は表示部2402に適用することができる。本発明を使用することにより、歩留まりが向上し、表示の品質も向上する。

#### 【0178】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、マスクがずれてしまった事による表示への影響を抑えることができるため歩留まりが向上し、安く製品を提供できるようになる上、画質の良い表示装置を提供することが可能となる。

#### 【実施例8】

#### 【0179】

本発明を実際に使用して作製した半導体装置の写真を図21、22に示す。

#### 【0180】

図21に示した写真は図4に模式図で示した本発明のトランジスタを実際に作製し、撮影を行った写真である。図中示した符号は図4に示した符号と一致している。

#### 【0181】

本発明のトランジスタ550は半導体層501aからなるトランジスタと、半導体層501bからなるトランジスタの2つのトランジスタにより構成され、当該二つのトランジスタはゲート電極502同士、ソース電極504同士、ドレイン電極503同士がそれぞれ電気的に接続されている。ドレイン電極503は写真中では繋がっていないが、当該写真の範囲外において合流し、電気的に接続されている。なお、半導体層501aと半導体層501bの幅は同じである。また、ソース電極504は半導体層501aよりなるトランジスタにおいては半導体層501aのゲート電極を中心として向かって右側にコンタクトホールを介して電気的に接続し、半導体層501bよりなるトランジスタにおいては半導体層501bのゲート電極を中心として向かって左側にコンタクトホールを介して電気的に接続しており、ドレイン電極及び配線はそれぞれの半導体層の対辺側に接続されている。

#### 【0182】

ゲート電極502は1層目のゲート電極と2層目のゲート電極との2層で形成され、各々の半導体層における1層目のゲート電極とは重ならず且つ2層目のゲート電極と重なる位置にp型もしくはn型の不純物が低濃度に添加されている。また、各々の半導体層において1層目のゲート電極と2層目のゲート電極の両方が重なった位置にはp型もしくはn型の不純物は実質的に添加されていない。上述した以外の位置の半導体層には高濃度に当該不純物が添加されている。

#### 【0183】

このようなトランジスタを用いて回路を作製することによって2層目のゲート電極とその下部に位置する低濃度に不純物が添加された半導体層との間で発生する寄生容量のバラツキが低減され、回路の動作マージンの確保が容易となる。また、回路の信頼性や当該回路を用いた電子機器の信頼性も向上する。

#### 【0184】

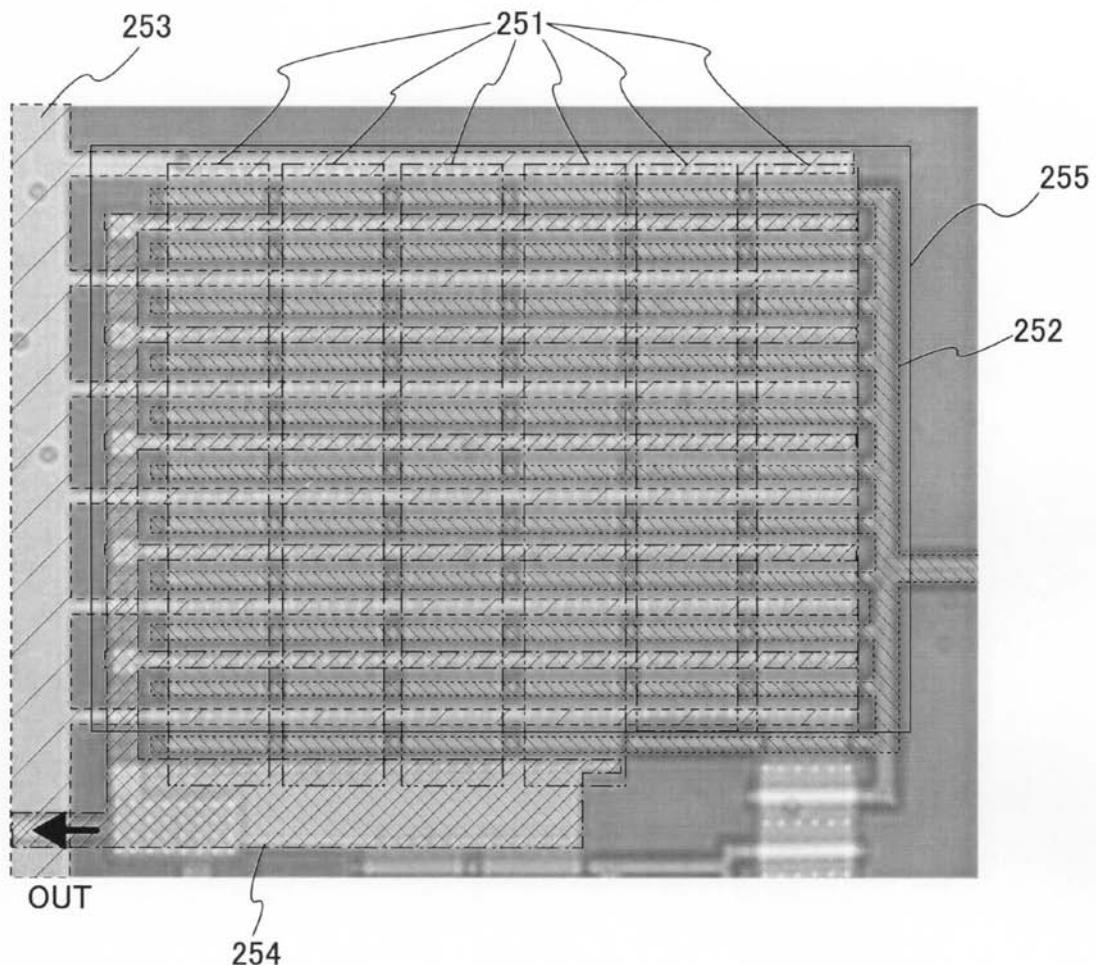

続いて、図22は他のレイアウト例を用いて作製した本発明のトランジスタの写真である。図22では本発明のトランジスタ255は半導体層251と2層でなるゲート電極252とソース電極及び配線253とドレイン電極及び配線254とからなる、60個のトランジスタで構成されている。

#### 【0185】

10

20

30

40

50

ゲート電極 252、ソース電極 253 及びドレイン電極 254 は各々当該 60 個のトランジスタにおいて電気的に接続しており、当該 60 個のトランジスタには同じ信号が入力され同じ配線に出力がなされる。当該 60 個のトランジスタは図中第 1 の方向に電流が流れるトランジスタと第 2 の方向に電流が流れるトランジスタの 2 種類のトランジスタが同数ずつで構成されている。また、第 1 の方向に電流が流れるトランジスタの半導体層が 2 層目のゲート電極とのみ重なっている部分の幅の和と第 2 の方向に電流が流れるトランジスタにおいての半導体層が 2 層目のゲート電極とのみ重なっている部分の幅の和は概略一致している。このような構成を有する本発明のトランジスタは、第 1 の方向及び第 2 の方向へ 2 層目のゲート電極のズレに対して回路における動作マージンの確保に対して従来の構成より許容が大きいトランジスタとすることができます。

10

20

30

【図面の簡単な説明】

【0186】

【図 1】本発明の半導体装置の一例を示す図。

【図 2】本発明の半導体装置の一例を示す図。

【図 3】本発明の半導体装置の一例を示す図。

【図 4】本発明の半導体装置の一例を示す図。

【図 5】本発明の半導体装置の一例を示す図。

【図 6】本発明の半導体装置を作製するプロセス例を示す図。

【図 7】本発明の半導体装置を作製するプロセス例を示す図。

【図 8】本発明の半導体装置を作製するプロセス例を示す図。

【図 9】本発明の半導体装置を作製するプロセス例を示す図。

【図 10】本発明の半導体装置を作製するプロセス例を示す図。

【図 11】本発明の半導体装置の上面図。

【図 12】本発明の半導体装置を用いて作製された液晶表示装置の断面図。

【図 13】本発明の半導体装置を用いて作製された発光表示装置の断面図。

【図 14】本発明の半導体装置を用いて作製された発光表示装置の断面図。

【図 15】発光装置の構成と発光方向を示す図。

【図 16】発光素子の素子構成例を示す図。

【図 17】発光装置の画素回路例を示す図。

【図 18】発光装置の保護回路例を示す図。

【図 19】本発明が適用可能な電子機器の例示。

【図 20】従来の半導体装置の一例を示す図。

【図 21】本発明の半導体装置の上面写真。

【図 22】本発明の半導体装置の上面写真。

【図 23】本発明の半導体装置の一例を示す図。

【 図 1 】

【 図 2 】

【 図 3 】

【 図 5 】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図23】

【図21】

【図22】

---

フロントページの続き

F ターム(参考) 5F110 AA30 BB02 BB04 CC02 DD01 DD02 DD03 DD05 DD13 DD14

DD15 DD17 EE01 EE03 EE04 EE14 EE23 EE24 EE25 EE37

EE44 FF02 FF28 FF30 GG02 GG13 GG25 GG32 GG43 GG45

GG47 HJ01 HJ04 HJ12 HJ23 HL01 HL03 HL04 HL12 HM15

HM19 NN03 NN23 NN24 NN27 NN35 NN72 NN73 NN77 NN78

PP03 PP06 PP34 PP35 QQ11 QQ19 QQ23 QQ24 QQ28