(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6638340号

(P6638340)

(45) 発行日 令和2年1月29日(2020.1.29)

(24) 登録日 令和2年1月7日(2020.1.7)

(51) Int.CI.

HO3B 5/32 (2006.01)

F 1

HO3B 5/32

A

請求項の数 15 (全 31 頁)

(21) 出願番号 特願2015-221729 (P2015-221729)

(22) 出願日 平成27年11月12日 (2015.11.12)

(65) 公開番号 特開2017-92744 (P2017-92744A)

(43) 公開日 平成29年5月25日 (2017.5.25)

審査請求日 平成30年11月6日 (2018.11.6)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 福澤 晃弘

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 石田 昌敏

最終頁に続く

(54) 【発明の名称】回路装置、発振器、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

外部電源が供給され、トランジスターの仕事関数差に基づき生成された基準電圧を生成する少なくとも1つの基準電圧生成回路を有し、前記基準電圧生成回路により生成された前記基準電圧を電源電圧として供給する電源回路と、

前記電源回路から前記電源電圧が供給されて動作し、発振周波数の温度特性を補償するための多項式に基づいて前記発振周波数の温度補償処理を行うデジタル温度補償発振回路と、

前記多項式の係数を記憶する記憶部と、

を含み、

10

前記デジタル温度補償発振回路は、

温度センサー部からの温度検出電圧のA/D変換を行い、温度検出データを出力するA/D変換部と、

前記温度検出データと、前記記憶部に記憶された前記係数とに基づいて前記温度補償処理を行い、前記発振周波数の周波数制御データを出力する処理部と、

前記処理部からの前記周波数制御データと振動子を用いて、前記周波数制御データにより設定される前記発振周波数の発振信号を生成する発振信号生成回路と、

を有し、

前記記憶部は、

前記基準電圧の温度特性による前記発振周波数の変動を含む前記発振周波数の温度特性

20

を補償するための前記多項式の前記係数を記憶することを特徴とする回路装置。

**【請求項 2】**

請求項 1 に記載の回路装置において、

前記記憶部は、

各温度における前記温度検出データと前記周波数制御データの関係に対して前記多項式によるフィッティングが行われることで決定された前記係数を記憶し、

前記処理部は、

前記係数が適用された前記多項式を用いて、前記温度検出データから前記周波数制御データを求めるることを特徴とする回路装置。

**【請求項 3】**

請求項 1 又は 2 に記載の回路装置において、

前記発振信号生成回路は、

前記周波数制御データの D / A 変換を行い、前記発振周波数の周波数制御電圧を出力する D / A 変換部と、

前記振動子を発振させる発振回路と、

を有し、

前記電源回路は、

前記少なくとも 1 つの前記基準電圧生成回路として、

前記仕事関数差に基づき生成された第 1 の基準電圧を、第 1 の電源電圧として前記 A / D 変換部に供給する第 1 の基準電圧発生回路と、

前記仕事関数差に基づき生成された第 2 の基準電圧を、第 2 の電源電圧として前記処理部に供給する第 2 の基準電圧発生回路と、

前記仕事関数差に基づき生成された第 3 の基準電圧を、第 3 の電源電圧として前記 D / A 変換部に供給する第 3 の基準電圧発生回路のうちの、少なくとも 1 つを有することを特徴とする回路装置。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一項に記載の回路装置において、

前記基準電圧に基づいて基準電流を生成する基準電流生成回路を含み、

前記発振信号生成回路は、

前記基準電流に基づく駆動電流により前記振動子を発振させる発振回路を有することを特徴とする回路装置。

**【請求項 5】**

請求項 4 に記載の回路装置において、

前記基準電流生成回路は、

高電位側電源ノードと第 1 のノードの間に設けられる第 1 のトランジスターと、

前記第 1 のノードと第 2 のノードの間に設けられる第 2 のトランジスターと、

前記基準電圧が第 1 の入力ノードに入力され、第 2 の入力ノードが前記第 2 のノードに接続され、出力ノードが前記第 1 のトランジスターのゲートに接続される第 1 の演算増幅器と、

前記第 1 のノードの電圧を設定するための所定電圧が第 1 の入力ノードに入力され、第 2 の入力ノードが前記第 1 のノードに接続され、出力ノードが前記第 2 のトランジスターのゲートに接続される第 2 の演算増幅器と、

を有することを特徴とする回路装置。

**【請求項 6】**

請求項 1 乃至 5 のいずれか一項に記載の回路装置において、

前記少なくとも 1 つの前記基準電圧生成回路は、

第 3 のトランジスターと、

前記第 3 のトランジスターとはゲート電極の導電性が異なる第 4 のトランジスターと、

前記第 3 のトランジスター及び前記第 4 のトランジスターに電流を供給するカレントミラー回路と、

10

20

30

40

50

前記第3のトランジスターと前記第4のトランジスターとの仕事関数差電圧に対応する電圧が一端に印加される第1の抵抗と、

電源用ノードと前記第1の抵抗の前記一端との間に設けられ、前記第4のトランジスターのドレイン電圧に基づきゲート電圧が制御される第5のトランジスターと、

を有し、

前記第1の抵抗の前記一端の電圧を前記基準電圧として出力することを特徴とする回路装置。

【請求項7】

請求項6に記載の回路装置において、

前記電源用ノードは、高電位側電源ノードであることを特徴とする回路装置。

10

【請求項8】

請求項6に記載の回路装置において、

前記少なくとも1つの前記基準電圧生成回路は、

第6のトランジスターと、

前記第6のトランジスターとはゲート電極の導電性が異なる第7のトランジスターと、

前記第6のトランジスター及び前記第7のトランジスターに電流を供給するカレントミラー回路と、

前記第6のトランジスターと前記第7のトランジスターとの仕事関数差電圧に対応する電圧が一端に印加される第2の抵抗と、

高電位側電源ノードと前記第2の抵抗の前記一端との間に設けられ、前記第7のトランジスターのドレイン電圧に基づきゲート電圧が制御される第8のトランジスターと、

を有し、

前記第2の抵抗の前記一端の電圧を前記電源用ノードに出力することを特徴とする回路装置。

【請求項9】

請求項6に記載の回路装置において、

前記少なくとも1つの前記基準電圧生成回路は、

第9のトランジスターと、

前記第9のトランジスターとはゲート電極の導電性が異なる第10のトランジスターと、

前記第9のトランジスター及び前記第10のトランジスターに電流を供給するカレントミラー回路と、

30

高電位側電源ノードと前記第10のトランジスターのゲートとの間に設けられ、前記第10のトランジスターのドレイン電圧に基づきゲート電圧が制御される第11のトランジスターと、

を有し、

前記第9のトランジスターと前記第10のトランジスターとの仕事関数差電圧に対応する電圧である前記第11のトランジスターのドレイン電圧を、前記電源用ノードに出力することを特徴とする回路装置。

【請求項10】

請求項8又は9に記載の回路装置において、

前記第5のトランジスターはデプレッション型のトランジスターであることを特徴とする回路装置。

40

【請求項11】

請求項6乃至10のいずれか一項に記載の回路装置において、

前記少なくとも1つの前記基準電圧生成回路は、

前記第5のトランジスターのゲートノードと低電位側電源ノードとの間に設けられるキヤパシターを有することを特徴とする回路装置。

【請求項12】

請求項1乃至11のいずれか一項に記載の回路装置と、

50

前記振動子と、

を含むことを特徴とする発振器。

【請求項 1 3】

請求項 1 乃至 1 1 のいずれか一項に記載された回路装置を含むことを特徴とする電子機器。

【請求項 1 4】

請求項 1 3 に記載された電子機器において、

前記外部電源を供給するスイッチングレギュレーターを含むことを特徴とする電子機器

。

【請求項 1 5】

請求項 1 乃至 1 1 のいずれか一項に記載の回路装置を含むことを特徴とする移動体。 10

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、回路装置、発振器、電子機器及び移動体等に関する。

【背景技術】

【0 0 0 2】

従来より、T C X O ( temperature compensated crystal oscillator ) と呼ばれる温度補償型発振器が知られている。このT C X O は、例えば携帯通信端末、G P S 関連機器、ウェアラブル機器、又は車載機器などにおける基準信号源等として用いられている。 20

【0 0 0 3】

このT C X O には、アナログ方式の温度補償型発振器であるA T C X O と、デジタル方式の温度補償型発振器であるD T C X O がある。A T C X O の従来技術としては特許文献 1 に開示される技術が知られている。D T C X O の従来技術としては特許文献 2 に開示される技術が知られている。

【先行技術文献】

【特許文献】

【0 0 0 4】

【特許文献 1】特開 2 0 1 2 - 1 9 9 6 3 1 号公報

【特許文献 2】特開昭 6 4 - 8 2 8 0 9 号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 5】

T C X O 等の発振器は、非常に高い周波数精度が要求されるため、低ノイズや低温度特性といった特性をもつ電源が用いられている。従来、A T C X O 等のアナログ方式の発振器では、外部電源としてL D O ( Low Drop-Out ) 方式等のリニアレギュレーターを用い、内部の電源回路は、バンドギャップリファレンス回路の出力をリファレンス電圧とするL D O 方式等のリニアレギュレーターで構成される。このような回路構成では、低ノイズで低温度特性の電源が得られる一方で、低消費電力化が難しい。例えば、外部電源として用いるリニアレギュレーターは、スイッチングレギュレーターに比べて消費電力が大きい。一方、外部電源としてスイッチングレギュレーターを用いれば消費電力を下げることができるが、リニアレギュレーターに比べてノイズが大きいため、内部の電源回路には高いP S R R ( Power Supply Rejection Ratio ) が要求される。内部の電源回路に用いられるバンドギャップリファレンス回路は、消費電流を下げていくと高いP S R R を維持することが難しく、低ノイズのまま低消費電力化することが難しい。 40

【0 0 0 6】

本発明の幾つかの態様によれば、電源の低消費電力化が可能なD T C X O 等のデジタル方式の発振器を実現できる回路装置、発振器、電子機器及び移動体等を提供できる。

【課題を解決するための手段】

【0 0 0 7】

50

本発明の一態様は、外部電源が供給され、トランジスターの仕事関数差に基づき生成された基準電圧を生成する少なくとも1つの基準電圧生成回路を有し、前記基準電圧生成回路により生成された前記基準電圧を電源電圧として供給する電源回路と、前記電源回路から前記電源電圧が供給されて動作するデジタル温度補償発振回路と、を含み、前記デジタル温度補償発振回路は、温度センサー部からの温度検出電圧のA/D変換を行い、温度検出データを出力するA/D変換部と、前記温度検出データに基づいて発振周波数の温度補償処理を行い、前記発振周波数の周波数制御データを出力する処理部と、前記処理部からの前記周波数制御データと振動子を用いて、前記周波数制御データにより設定される前記発振周波数の発振信号を生成する発振信号生成回路と、を有する回路装置に係する。

#### 【0008】

10

本発明の一態様によれば、トランジスターの仕事関数差に基づいて基準電圧が生成され、その基準電圧が電源電圧としてデジタル温度補償発振回路に供給される。トランジスターの仕事関数差に基づいて基準電圧を生成することで、例えばバンドギャップリファレンス回路等を用いる場合に比べて消費電流を低下させつつ、高いPSRRを維持できる。これにより、電源の低消費電力化が可能なDTCXO等のデジタル方式の発振器を実現できる。

#### 【0009】

20

また本発明の一態様では、前記発振信号生成回路は、前記周波数制御データについてのD/A変換を行い、前記発振周波数の周波数制御電圧を出力するD/A変換部と、前記周波数制御電圧に基づいて前記発振周波数で振動子を発振させる発振回路と、を有し、前記電源回路は、前記少なくとも1つの前記基準電圧生成回路として、前記仕事関数差に基づき生成された第1の基準電圧を、第1の電源電圧として前記A/D変換部に供給する第1の基準電圧発生回路と、前記仕事関数差に基づき生成された第2の基準電圧を、第2の電源電圧として前記処理部に供給する第2の基準電圧発生回路と、前記仕事関数差に基づき生成された第3の基準電圧を、第3の電源電圧として前記D/A変換部に供給する第3の基準電圧発生回路のうちの、少なくとも1つを有してもよい。

#### 【0010】

30

本発明の一態様によれば、A/D変換部、処理部、D/A変換部のそれぞれに対応する第1の基準電圧生成回路、第2の基準電圧生成回路、第3の基準電圧生成回路のうち少なくとも1つの基準電流生成回路が設けられる。これにより、各部の電源ラインを分離できるので、電源ラインを介したノイズの伝搬を抑制し、発振信号の精度（例えば位相ノイズ特性）を向上できる。また本発明の一態様では、デジタル温度補償発振回路により温度補償を行うので、電源の温度特性が発振周波数の温度特性に与える影響を含めて温度補償できる。

#### 【0011】

また本発明の一態様では、回路装置は、前記基準電圧に基づいて基準電流を生成する基準電流生成回路を含み、前記発振信号生成回路は、前記基準電流に基づく駆動電流により前記振動子を発振させる発振回路を有してもよい。

#### 【0012】

40

本発明の一態様によれば、発振回路に対応して基準電流生成回路が設けられる。これにより、処理部等の他の回路の電源ラインから発振回路を分離できるので、電源ラインを介したノイズの伝搬を抑制し、発振信号の精度（例えば位相ノイズ特性）を向上できる。また本発明の一態様では、デジタル温度補償発振回路により温度補償を行うので、電源の温度特性が発振周波数の温度特性に与える影響を含めて温度補償できる。

#### 【0013】

また本発明の一態様では、前記基準電流生成回路は、高電位側電源ノードと第1のノードの間に設けられる第1のトランジスターと、前記第1のノードと第2のノードの間に設けられる第2のトランジスターと、前記基準電圧が第1の入力ノードに入力され、第2の入力ノードが前記第2のノードに接続され、出力ノードが前記第1のトランジスターのゲートに接続される第1の演算増幅器と、前記第1のノードの電圧を設定するための所定電

50

圧が第1の入力ノードに入力され、第2の入力ノードが前記第1のノードに接続され、出力ノードが前記第2のトランジスターのゲートに接続される第2の演算増幅器と、を有してもよい。

【0014】

本発明の一態様によれば、第2の演算増幅器によるフィードバック制御で、第1のノードの電圧が所定電圧に設定され、第1の演算増幅器によるフィードバック制御で、第2のノードの電圧が基準電圧に設定される。このように第1のノードの電圧と第2のノードの電圧が固定されることによって、高電位側電源ノードの電圧変動の影響を受けにくくなり、高安定な基準電流を生成できる。

【0015】

また本発明の一態様では、前記少なくとも1つの前記基準電圧生成回路は、第3のトランジスターと、前記第3のトランジスターとはゲート電極の導電性が異なる第4のトランジスターと、前記第3のトランジスター及び前記第4のトランジスターに電流を供給するカレントミラー回路と、前記第3のトランジスターと前記第4のトランジスターとの仕事関数差電圧に対応する電圧が一端に印加される第1の抵抗と、電源用ノードと前記第1の抵抗の前記一端との間に設けられ、前記第4のトランジスターのドレイン電圧に基づきゲート電圧が制御される第5のトランジスターと、を有し、前記第1の抵抗の前記一端の電圧を前記基準電圧として出力してもよい。

【0016】

本発明の一態様によれば、第3のトランジスター及び第4のトランジスターにより差動対が構成され、その差動対の出力が第5のトランジスターを介して第4のトランジスターのゲートにフィードバックされる。これにより、第5のトランジスターの一端（第1の抵抗の一端）に、第3のトランジスターと第4のトランジスターとの仕事関数差電圧に対応する電圧（基準電圧）を出力できる。

【0017】

また本発明の一態様では、前記電源用ノードは、高電位側電源ノードであってもよい。

【0018】

電源用ノードは、上記の第3～第5のトランジスターと第1の抵抗とを含む仕事関数差アンプの電源電圧が供給されるノードである。本発明の一態様によれば、電源用ノードが高電位側電源ノードであることで、基準電流生成回路を1段の仕事関数差アンプで構成できる。

【0019】

また本発明の一態様では、前記少なくとも1つの前記基準電圧生成回路は、第6のトランジスターと、前記第6のトランジスターとはゲート電極の導電性が異なる第7のトランジスターと、前記第6のトランジスター及び前記第7のトランジスターに電流を供給するカレントミラー回路と、前記第6のトランジスターと前記第7のトランジスターとの仕事関数差電圧に対応する電圧が一端に印加される第2の抵抗と、高電位側電源ノードと前記第2の抵抗の前記一端との間に設けられ、前記第7のトランジスターのドレイン電圧に基づきゲート電圧が制御される第8のトランジスターと、を有し、前記第2の抵抗の前記一端の電圧を前記電源用ノードに出力してもよい。

【0020】

本発明の一態様によれば、第6～第8のトランジスターと第2の抵抗とを含む第1の仕事関数差アンプが生成した基準電圧が、第3～第5のトランジスターと第1の抵抗とを含む第2の仕事関数差アンプの電源用ノードに供給される。これにより、基準電流生成回路を2段の仕事関数差アンプで構成できる。

【0021】

また本発明の一態様では、前記少なくとも1つの前記基準電圧生成回路は、第9のトランジスターと、前記第9のトランジスターとはゲート電極の導電性が異なる第10のトランジスターと、前記第9のトランジスター及び前記第10のトランジスターに電流を供給するカレントミラー回路と、高電位側電源ノードと前記第10のトランジスターのゲート

10

20

30

40

50

との間に設けられ、前記第10のトランジスターのドレイン電圧に基づきゲート電圧が制御される第11のトランジスターと、を有し、前記第9のトランジスターと前記第10のトランジスターとの仕事関数差電圧に対応する電圧である前記第11のトランジスターのドレイン電圧を、前記電源用ノードに出力してもよい。

## 【0022】

本発明の一態様によれば、第9～第11のトランジスターを含む第1の仕事関数差アンプが生成した基準電圧が、第3～第5のトランジスターと第1の抵抗とを含む第2の仕事関数差アンプの電源用ノードに供給される。このような構成によっても、基準電流生成回路を2段の仕事関数差アンプで構成できる。

## 【0023】

また本発明の一態様では、前記第5のトランジスターはデプレッション型のトランジスターであってもよい。

## 【0024】

基準電流生成回路を2段の仕事関数差アンプで構成した場合、第2の仕事関数差アンプの電源電圧と出力電圧が、共に仕事関数差に基づく基準電圧となる。そのため、第2の仕事関数差アンプの出力電圧を出力する第5のトランジスターのゲート-ソース間電圧が非常に小さくなる。この点、本発明の一態様によれば、第5のトランジスターがデプレッション型のトランジスターであることで、第5のトランジスターを動作させることができる。

## 【0025】

また本発明の一態様では、前記少なくとも1つの前記基準電圧生成回路は、前記第5のトランジスターのゲートノードと低電位側電源ノードとの間に設けられるキャパシターを有してもよい。

## 【0026】

第5のトランジスターは、第3のトランジスター及び第4のトランジスターにより構成される差動対の出力を第4のトランジスターのゲートにフィードバックするトランジスターである。この第5のトランジスターのゲートノードと低電位側電源ノードとの間にキャパシターが設けられることで、PSRRの周波数特性を向上できる。

## 【0027】

また本発明の他の態様は、上記のいずれかに記載の回路装置と、前記振動子と、を含む発振器に関係する。

## 【0028】

また本発明の更に他の態様は、上記のいずれかに記載された回路装置を含む電子機器に関係する。

## 【0029】

また本発明の更に他の態様では、電子機器は、前記外部電源を供給するスイッチングレギュレーターを含んでもよい。

## 【0030】

また本発明の更に他の態様は、上記のいずれかに記載の回路装置を含む移動体に関係する。

## 【図面の簡単な説明】

## 【0031】

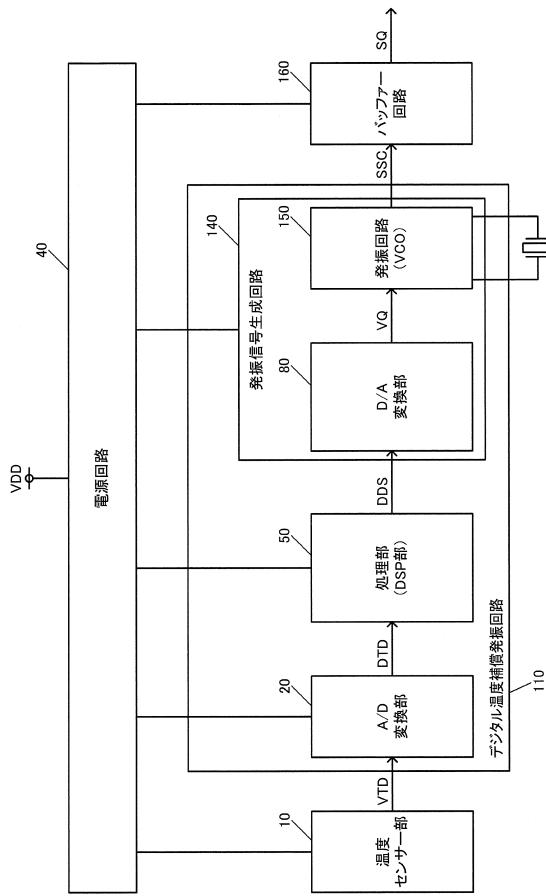

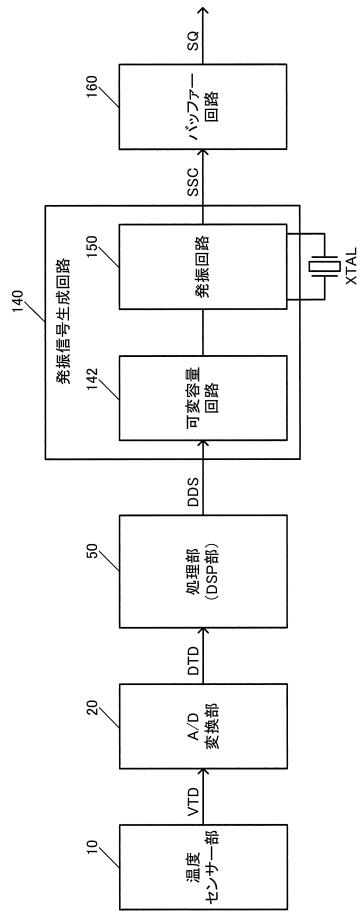

【図1】回路装置の構成例。

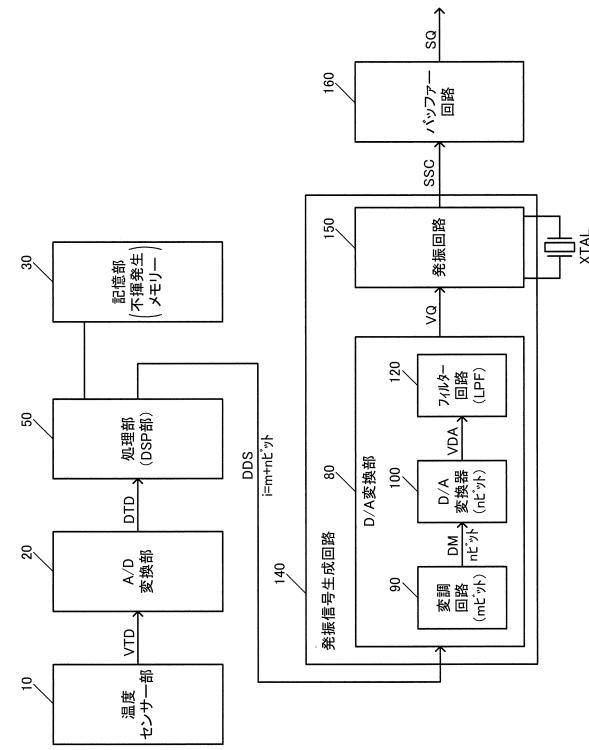

【図2】回路装置の詳細な構成例。

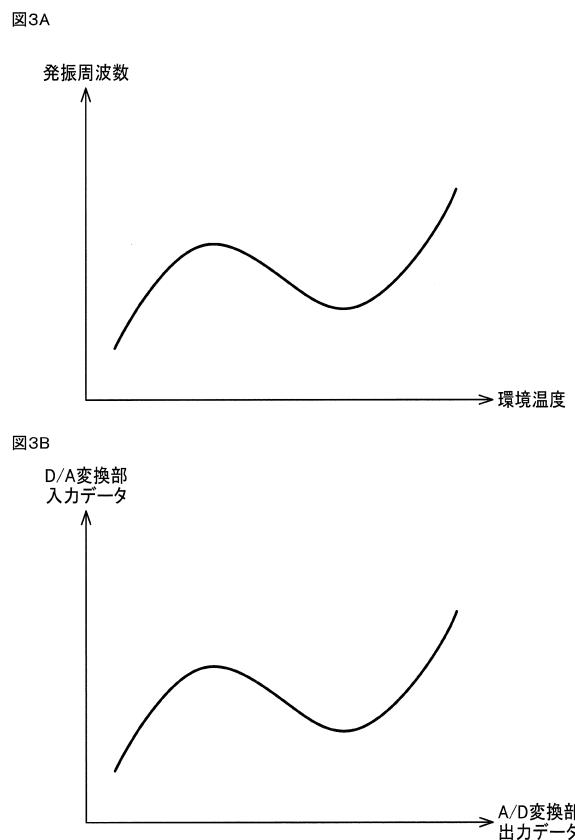

【図3】図3Aは、発振周波数の温度依存性の例。図3Bは、処理部の入力データと処理部の出力データとの間の関係の例。

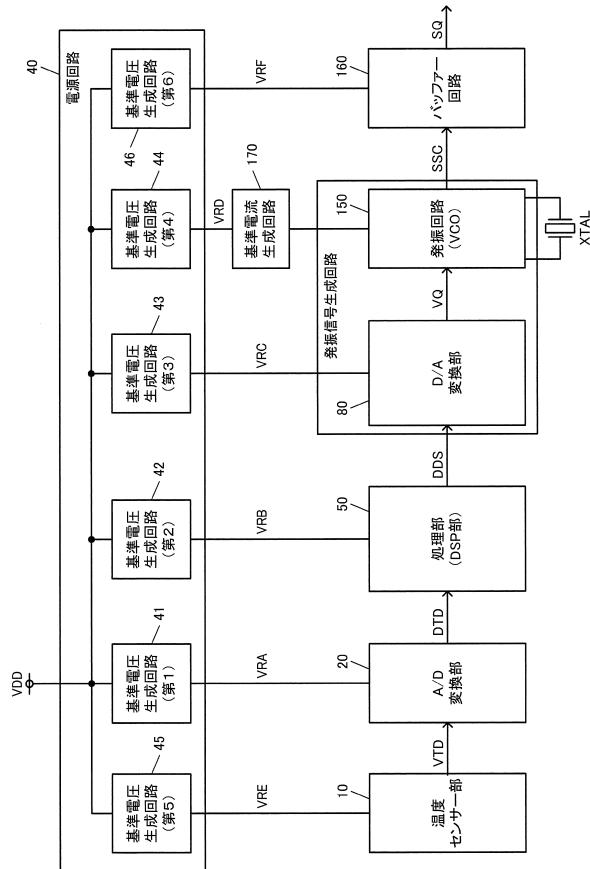

【図4】回路装置の第2の詳細な構成例。

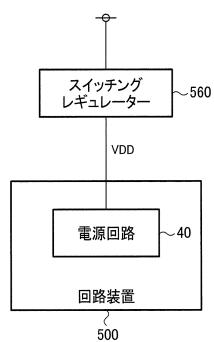

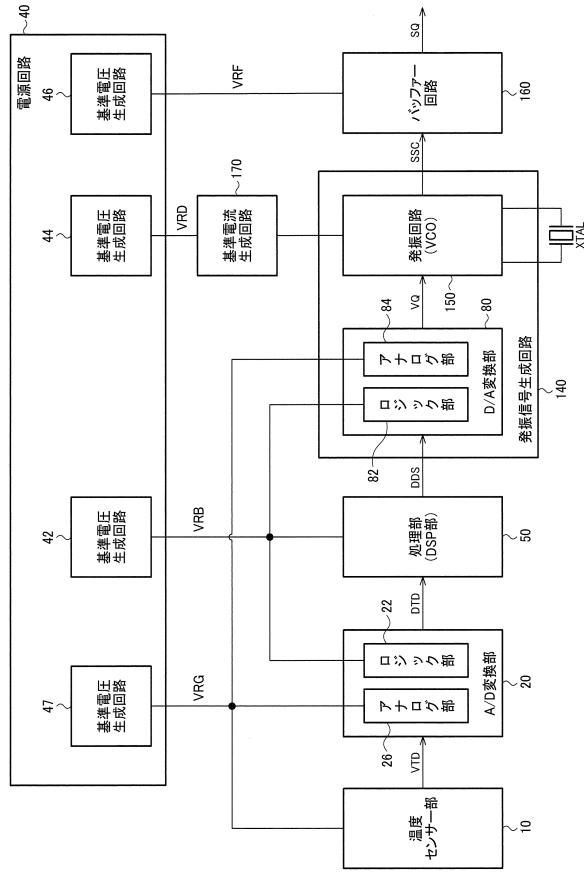

【図5】電子機器の基本構成例。

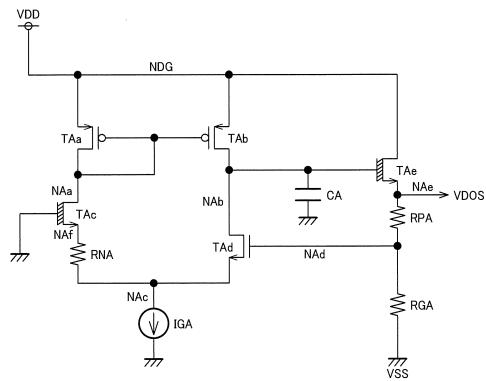

【図6】基準電圧生成回路の第1の詳細な構成例。

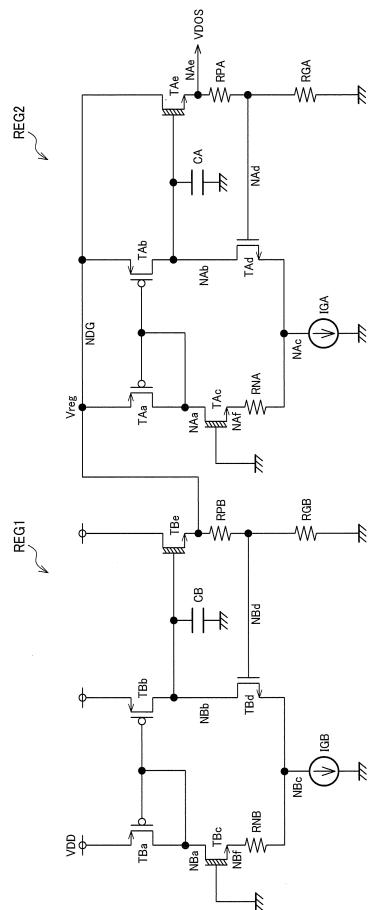

【図7】基準電圧生成回路の第2の詳細な構成例。

10

20

30

40

50

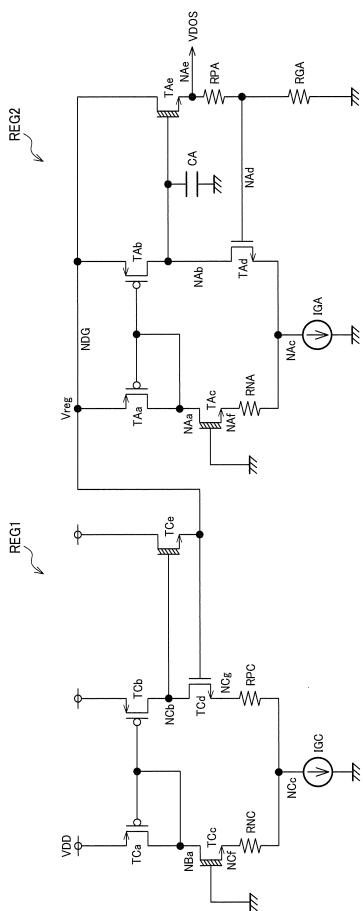

【図8】基準電圧生成回路の第3の詳細な構成例。

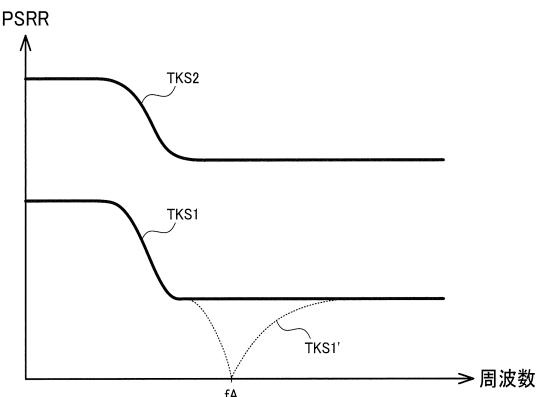

【図9】基準電圧生成回路のP S R Rの周波数特性の模式図。

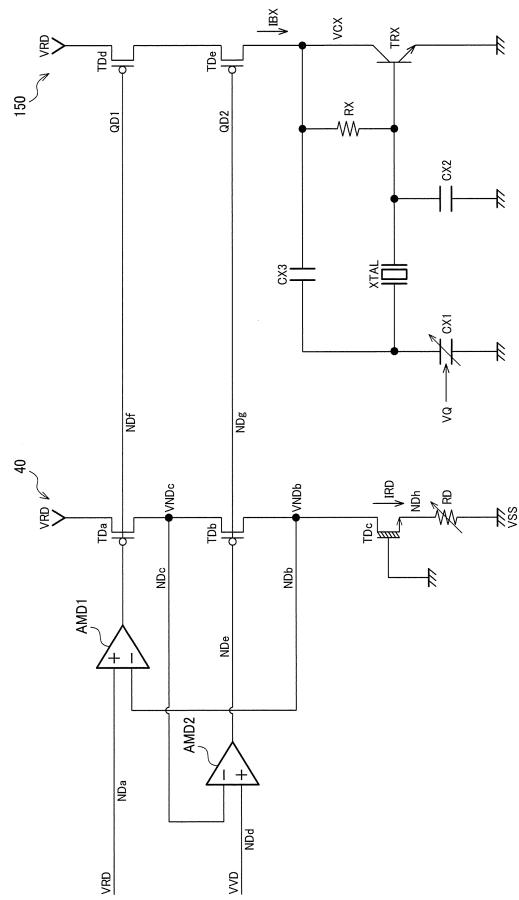

【図10】基準電流生成回路、発振回路の詳細な構成例。

【図11】D / A 変換部の詳細な構成例。

【図12】図12Aは、温度センサー部の第1の構成例。図12Bは、温度センサー部の第2の構成例。図12Cは、温度センサー部の温度特性の例。

【図13】A / D 変換部の詳細な構成例。

【図14】回路装置の第1の変形構成例。

【図15】回路装置の第2の変形構成例。

【図16】図16Aは、発振器の構成例。図16Bは、電子機器の構成例。図16Cは、10移動体の例。

【発明を実施するための形態】

【0032】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0033】

### 1. 構成

図1に本実施形態の回路装置の基本構成例を示す。この回路装置は、D T C X O やO C X O (oven controlled crystal oscillator) 等のデジタル方式の発振器を実現する回路装置(半導体チップ)である。例えばこの回路装置と振動子X T A Lをパッケージに収納することで、デジタル方式の発振器が実現される。20

【0034】

図1の回路装置は、デジタル温度補償発振回路110、電源回路40を含む。デジタル温度補償発振回路110は、A / D 変換部20、処理部50、発振信号生成回路140を含む。また回路装置は温度センサー部10、バッファー回路160を含むことができる。なお回路装置の構成は図1の構成には限定されず、その一部の構成要素(例えば温度センサー部、バッファー回路、A / D 変換部等)を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0035】

振動子X T A Lは、例えば水晶振動子等の圧電振動子である。振動子X T A Lは恒温槽内に設けられるオープン型振動子(O C X O)であってもよい。振動子X T A Lは共振器(電気機械的な共振子又は電気的な共振回路)であってもよい。振動子X T A Lとしては、圧電振動子、S A W (Surface Acoustic Wave) 共振子、M E M S (Micro Electro Mechanical Systems) 振動子等を採用できる。振動子X T A Lの基板材料としては、水晶、タンタル酸リチウム、ニオブ酸リチウム等の圧電単結晶や、ジルコン酸チタン酸鉛等の圧電セラミックス等の圧電材料、又はシリコン半導体材料等を用いることができる。振動子X T A Lの励振手段としては、圧電効果によるもの用いてもよいし、クーロン力による静電駆動を用いてもよい。

【0036】

温度センサー部10は、温度検出電圧V T Dを出力する。具体的には、環境(回路装置)の温度に応じて変化する温度依存電圧を、温度検出電圧V T Dとして出力する。温度センサー部10の具体的な構成例については後述する。

【0037】

A / D 変換部20は、温度センサー部10からの温度検出電圧V T DのA / D 変換を行って、温度検出データD T Dを出力する。例えば温度検出電圧V T DのA / D 変換結果に対応するデジタルの温度検出データD T D(A / D 結果データ)を出力する。A / D 変換部20のA / D 変換方式としては、例えば逐次比較方式や逐次比較方式に類似する方式などを採用できる。なおA / D 変換方式はこのような方式には限定されず、種々の方式(計数型、並列比較型又は直並列型等)を採用できる。

10

20

30

40

50

## 【0038】

処理部50（DSP部：デジタル信号処理部）は種々の信号処理を行う。例えば処理部50（温度補償部）は、温度検出データDTDに基づいて発振周波数（発振信号の周波数）の温度補償処理を行う。そして発振周波数の周波数制御データDDSを出力する。具体的には処理部50は、温度に応じて変化する温度検出データDTD（温度依存データ）と、温度補償処理用の係数データ（近似関数の係数のデータ）などに基づいて、温度変化があった場合にも発振周波数を一定にするための温度補償処理を行う。この処理部50は、ゲートアレイ等のASIC回路により実現してもよいし、プロセッサー（例えばCPU、MPU等）とプロセッサー上で動作するプログラムにより実現してもよい。

## 【0039】

発振信号生成回路140は発振信号SSCを生成する。例えば発振信号生成回路140は、処理部50からの周波数制御データDDSと振動子XTALを用いて、周波数制御データDDSにより設定される発振周波数の発振信号SSCを生成する。一例としては、発振信号生成回路140は、周波数制御データDDSにより設定される発振周波数で振動子XTALを発振させて、発振信号SSCを生成する。

## 【0040】

なお発振信号生成回路140は、ダイレクト・デジタル・シンセサイザー方式で発振信号SSCを生成する回路であってもよい。例えば振動子XTAL（固定発振周波数の発振源）の発振信号をリファレンス信号として、周波数制御データDDSで設定される発振周波数の発振信号SSCをデジタル的に生成してもよい。

## 【0041】

発振信号生成回路140は、D/A変換部80と発振回路150を含むことができる。但し発振信号生成回路140は、このような構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

## 【0042】

D/A変換部80は、処理部50からの周波数制御データDDS（処理部の出力データ）のD/A変換を行う。D/A変換部80に入力される周波数制御データDDSは、処理部50による温度補償処理後の周波数制御データ（周波数制御コード）である。D/A変換部80のD/A変換方式としては例えば抵抗ストリング型（抵抗分割型）を採用できる。但し、D/A変換方式はこれには限定されず、抵抗ラダー型（R-2Rラダー型等）、容量アレイ型、又はパルス幅変調型などの種々の方式を採用できる。またD/A変換部80は、D/A変換器以外にも、その制御回路や変調回路やフィルター回路などを含むことができる。

## 【0043】

発振回路150は、D/A変換部80の出力電圧VQと振動子XTALを用いて、発振信号SSCを生成する。発振回路150は、第1、第2の振動子用端子（振動子用パッド）を介して振動子XTALに接続される。例えば発振回路150は、振動子XTAL（圧電振動子、共振子等）を発振させることで、発振信号SSCを生成する。具体的には発振回路150は、D/A変換部80の出力電圧VQを周波数制御電圧（発振制御電圧）とした発振周波数で、振動子XTALを発振させる。例えば発振回路150が、電圧制御により振動子XTALの発振を制御する回路（VCO）である場合には、発振回路150は、周波数制御電圧に応じて容量値が変化する可変容量キャパシター（バリキャップ等）を含むことができる。

## 【0044】

なお、前述のように発振回路150はダイレクト・デジタル・シンセサイザー方式により実現してもよく、この場合には振動子XTALの発振周波数はリファレンス周波数となり、発振信号SSCの発振周波数とは異なる周波数になる。

## 【0045】

バッファー回路160は、発振信号生成回路140（発振回路150）で生成された発振信号SSCのバッファリングを行って、バッファリング後の信号SQを出力する。即ち

10

20

30

40

50

、外部の負荷を十分に駆動できるようにするためのバッファリングを行う。信号 S Q は例えばクリップドサイン波信号である。但し信号 S Q は矩形波信号であってもよい。或いはバッファー回路 160 は、信号 S Q としてクリップドサイン波信号と矩形波信号の両方の出力が可能な回路であってもよい。

【 0046 】

電源回路 40 は、回路装置の外部から供給される電源電圧 V DD に基づいて、回路装置の各部に供給する電源電圧を生成する。電源回路 40 は、1 又は複数の基準電圧生成回路（仕事関数差アンプ）を含んでおり、その基準電圧生成回路がトランジスターの仕事関数差に基づいて基準電圧を生成し、電源回路 40 は、その基準電圧を各部の電源電圧として供給する。電源回路 40 は、1 つの基準電圧生成回路を含み、その基準電圧生成回路が回路装置の全体に電源電圧を供給してもよい。或いは、電源回路 40 は、複数の基準電圧生成回路を含み、各基準電圧生成回路が、回路装置のいずれか 1 つの部に電源電圧を供給してもよい。或いは、電源回路 40 が複数の基準電圧生成回路を含む場合において、1 以上の部に電源電圧を供給する基準電圧生成回路があってもよい。

10

【 0047 】

基準電圧生成回路は、例えばデプレッション型のトランジスターとエンハンスマント型のトランジスターで差動対が構成されるアンプ回路であり、デプレッション型のトランジスターとエンハンスマント型のトランジスターのしきい値電圧の差を基準電圧として出力する。なお、基準電圧生成回路はこの構成に限定されず、ゲート電極と基板の間の仕事関数が異なるトランジスターを組み合わせて、その仕事関数差により基準電圧を生成する回路であればよい。

20

【 0048 】

図 2 に本実施形態の回路装置の詳細な構成例を示す。なお図 2 では電源回路 40 の図示を省略している。図 2 の回路装置は、記憶部 30（不揮発性メモリー）、温度センサー部 10、A / D 変換部 20、処理部 50、発振信号生成回路 140、バッファー回路 160 を含む。また D / A 変換部 80 が、変調回路 90 と D / A 変換器 100 とフィルター回路 120 を含む。

【 0049 】

記憶部 30 は、発振周波数の温度特性を補償するための多項式の係数を記憶している。例えば、発振器の出荷前検査等において発振周波数の温度特性をテスト装置により測定し、その測定された温度特性に基づいてテスト装置が多項式の係数を求め、その係数がテスト装置により記憶部 30 に書き込まれる。多項式は、温度検出データ DTD (A / D 変換部 20 の出力データ) と周波数制御データ DDS (D / A 変換部 80 の入力データ) を対応付けるものである。記憶部 30 は、例えば EEPROM (Electrically Erasable Programmable Read-Only Memory) 等の不揮発性メモリーである。或いは、RAM (Random Access memory) やレジスターであってもよい。処理部 50 は、記憶部 30 から係数を読み出し、その係数を適用した多項式に温度検出データ DTD を代入し、その多項式の演算結果に基づいて周波数制御データ DDS を生成し、その周波数制御データ DDS を D / A 変換部 80 に出力する。

30

【 0050 】

D / A 変換部 80 の変調回路 90 は、処理部 50 から  $i = (n + m)$  ビットの周波数制御データ DDS を受ける ( $i, n, m$  は 1 以上の整数)。一例としては  $i = 20, n = 16, m = 4$  である。そして変調回路 90 は、周波数制御データ DDS の  $m$  ビット（例えば 4 ビット）のデータに基づいて、周波数制御データ DDS の  $n$  ビット（例えば 16 ビット）のデータを変調する。具体的には変調回路 90 は、周波数制御データ DDS の PWM 変調を行う。なお変調回路 90 の変調方式は PWM 変調（パルス幅変調）には限定されず、例えば PDM 変調（パルス密度変調）等のパルス変調であってもよく、パルス変調以外の変調方式であってもよい。例えば周波数制御データ DDS の  $n$  ビットのデータに対して、 $m$  ビットのディザー処理（ディザリング処理）を行うことでビット拡張（ $n$  ビットから  $i$  ビットへのビット拡張）を実現してもよい。

40

50

## 【0051】

D/A変換器100は、変調回路90により変調されたnビットのデータのD/A変換を行う。例えばn=16ビットのデータのD/A変換を行う。D/A変換器100のD/A変換方式としては、例えば抵抗ストリング型や抵抗ラダー型などを採用できる。

## 【0052】

フィルター回路120は、D/A変換器100の出力電圧VDAを平滑化する。例えばローパスフィルター処理を行って出力電圧VDAを平滑化する。このようなフィルター回路120を設けることで、例えばPWM変調された信号のPWM復調が可能になる。このフィルター回路120のカットオフ周波数は、変調回路90のPWM変調の周波数に応じて設定できる。即ちD/A変換器100からの出力電圧VDAの信号は、PWM変調の基本周波数及び高調波成分のリップルを含むため、フィルター回路120により、このリップルを減衰させる。なおフィルター回路120としては、例えば抵抗又はキャパシター等の受動素子を用いたパッシブフィルターを採用できる。但しフィルター回路120としてS

10

## 【0053】

なおD/A変換部80の分解能はi=20ビットには限定されず、20ビットよりも高い分解能であってもよいし、低い分解能であってもよい。また変調回路90の変調のビット数もm=4ビットには限定されず、4ビットよりも大きくてよいし（例えばm=8ビット）、小さくてもよい。

## 【0054】

20

また図2では、D/A変換部80の前段に、温度補償処理等のデジタル信号処理を行う処理部50が設けられていることを、有効活用している。即ち、処理部50は、例えば浮動小数点演算などにより、高精度で、温度補償処理等のデジタル信号処理を実行している。従って、例えば浮動小数点演算の結果の仮数部の下位ビットも有効なデータとして扱って、バイナリーデータに変換すれば、例えばi=m+n=20ビットというような高いビット数での周波数制御データDDSも、容易に出力できる。図2ではこの点に着目し、このような高いビット数であるi=m+nビットの周波数制御データDDSを、D/A変換部80に供給し、mビットの変調回路90とnビットのD/A変換器100を用いて、i=m+nビットというような高分解能のD/A変換の実現に成功している。

## 【0055】

30

DTCXOやOCXOなどのデジタル方式の発振器では、発振周波数に対して非常に高い周波数精度が要求される。例えば前述のTDD方式では、上がりと下りで同じ周波数を用いて時分割でデータが送受信され、各機器に割り当てられたタイムスロットの間にはガードタイムが設定されている。このため、適正な通信を実現するためには、各機器において時刻同期を行う必要があり、正確な絶対時刻の計時が要求される。例えば基準信号（GPS信号やインターネットを介した信号）が消失又は異常となるホールドオーバーが発生した場合には、基準信号が無い状態で発振器側が正確に絶対時刻を計時する必要がある。このため、このような機器（GPS関連機器、基地局等）に用いられる発振器には、非常に高い発振周波数精度が要求される。

## 【0056】

40

このような要求を実現するために、例えば各機器に原子時計などを設ける手法を採用すると、機器の高コスト化や大規模化を招く。また、高い周波数精度の発振器を実現したとしても、発振器に用いられる回路装置が大規模化したり、消費電力が非常に大きくなってしまうのは望ましくない。

## 【0057】

この点、図2の回路装置の構成によれば、D/A変換部80に、変調回路90やフィルター回路120を設けるだけで、例えばi=20ビットとなるような非常に高い分解能のD/A変換部80を実現でき、このように分解能が高くなることで、発振周波数の高精度化を実現できる。そして、このような変調回路90やフィルター回路120を設けることによる回路装置のチップサイズの増加や消費電力の増加は、それほど大きくなない。更に処

50

理部 50 では浮動点小数点演算などにより温度補償処理を実行しているため、例えば i 20 ビットとなるような周波数制御データ D D S を D / A 変換部 80 に出力することも容易である。従って、図 2 の回路装置の構成は、発振周波数の高精度化と、回路装置の規模や消費電力の増加の抑制とを、両立して実現できるという利点がある。

#### 【 0 0 5 8 】

なお図 1、図 2 の回路装置は、基準信号（G P S 信号やインターネットを介した信号）と発振信号に基づく入力信号を比較する位相比較回路を有する P L L 回路における、発振用 I C としても用いることができる。この場合には、例えば当該位相比較回路からの周波数制御データに対して、処理部 50 が温度補償処理やエージング補正処理等を行って、発振信号生成回路 140 により発振信号を生成すればよい。

10

#### 【 0 0 5 9 】

##### 2. 電源回路

以下、電源回路 40 について詳細に説明する。

#### 【 0 0 6 0 】

上述したように、本実施形態の回路装置は、電源回路 40 と、電源回路 40 から電源電圧が供給されて動作するデジタル温度補償発振回路 110 と、を含む。デジタル温度補償発振回路 110 は、温度センサー部 10 からの温度検出電圧の A / D 変換を行い、温度検出データを出力する A / D 変換部 20 と、温度検出データに基づいて発振周波数の温度補償処理を行い、発振周波数の周波数制御データを出力する処理部 50 と、処理部 50 からの周波数制御データと振動子 X T A L を用いて、周波数制御データにより設定される発振周波数の発振信号を生成する発振信号生成回路 140 と、を有する。

20

#### 【 0 0 6 1 】

そして、電源回路 40 には外部電源（電源電圧 V D D ）が供給され、電源回路 40 は、トランジスターの仕事関数差に基づき生成された基準電圧を生成する少なくとも 1 つの基準電圧生成回路を有する。電源回路 40 は、基準電圧生成回路により生成された基準電圧を電源電圧として供給する。

#### 【 0 0 6 2 】

本実施形態によれば、トランジスターの仕事関数差に基づいて基準電圧が生成され、その基準電圧が電源電圧としてデジタル温度補償発振回路 110 に供給される。これにより、電源の低消費電力化が可能な D T C X O 等のデジタル方式の発振器を実現できる。

30

#### 【 0 0 6 3 】

従来、基準電圧生成回路として用いられたバンドギャップリファレンス回路は、バンドギャップ電圧の温度依存性をキャンセルするために複数のバイポーラトランジスター（バイポーラトランジスターに含まれる P N 接合）を用いており、それらに流すバイアス電流等によって、比較的消費電流が大きい回路となっている。そのため、高い P S R R を維持しつつ、消費電流を絞ることが難しいという課題がある。電源のノイズ特性は発振信号の精度（例えば位相ノイズ特性）に影響するため、高い P S R R が必要であり、この点からバンドギャップリファレンス回路を用いた電源回路では低消費電力化に限界がある。

#### 【 0 0 6 4 】

この点、本実施形態ではトランジスターの仕事関数差に基づいて基準電圧を生成することで、バンドギャップリファレンス回路を用いる場合に比べて消費電流を低下させつつ、高い P S R R を維持できる。例えば図 6 で後述するように、ゲート電極と基板の間の仕事関数が異なるトランジスター T A c とトランジスター T A d で差動対を構成し、その差動対の出力をトランジスター T A e により差動対にフィードバックすることで、基準電圧を生成できる。このように、仕事関数差を用いた場合には簡素な構成で基準電圧生成回路を構成できるので、バイアス電流を小さくすることが容易である。

40

#### 【 0 0 6 5 】

しかしながら、トランジスターの仕事関数差に基づき生成された基準電圧は温度特性（例えば負の温度特性）を有する。このような基準電圧が電源電圧として回路装置の各部に供給された場合、その電源電圧の温度依存性が発振周波数の温度特性に影響を与える（電

50

源電圧に温度依存性が無い場合に比べて、発振周波数の温度特性が変わる）。この点、本実施形態ではデジタル温度補償発振回路110により温度補償を行っており、デジタル温度補償発振回路110では、電源電圧の温度依存性を含めて包括的に発振周波数を温度補償できる。これにより、トランジスターの仕事関数差に基づき生成された基準電圧を利用することが可能となっている。

#### 【0066】

そして、低消費電力でありながら高いP S R Rが得られることによって、回路装置に内蔵された電源回路40を低消費電力化すると共に、位相ノイズが少ない高精度な発振信号が得られる。また、高いP S R Rが得られることから、より上流側の外部電源としてスイッチングレギュレーターを用いることが可能となる。これにより、回路装置の外部電源を低消費電力化できる。以上のように、トランジスターの仕事関数差に基づいて基準電圧を生成し、その基準電圧を電源電圧としてデジタル温度補償発振回路110に供給することで、回路装置の内部電源或いは外部電源を含めたシステム全体の電源を低消費電力化できる。

10

#### 【0067】

D T C X O等のデジタル方式の発振器において、電源電圧の温度依存性を含めて包括的に発振周波数を温度補償できる点について、より詳細に説明する。

#### 【0068】

まず、本実施形態の比較例としてA T C X O等のアナログ方式の発振器を考える。A T C X Oは、発振周波数の温度依存性を補償して高精度な発振周波数を得ているが、その温度補償を行う前の発振周波数は、例えば図3Aに示すような温度依存性を有している。A T C X Oでは、恒温槽でいくつかの環境温度を設定し、各環境温度での発振周波数を測定し、その測定された温度依存性をキャンセルする多項式の係数を決定し、その係数を不揮発性メモリー等に書き込んでおく。そして、温度補償の際には不揮発性メモリーから係数を読み出して温度センサーの出力に対応する周波数制御電圧を生成して、発振周波数の温度依存性を補償する。

20

#### 【0069】

このように、A T C X Oの温度補償では、温度センサーの出力と周波数制御電圧との間の関係が多項式により決定されているが、係数決定の際には、得られる関係は環境温度と発振周波数の間の関係である。そのため、係数決定のアルゴリズムでは、例えば環境温度に対してどのような温度センサーの出力が得られるか、或いは温度センサーの出力に対して関数発生回路がどのような周波数制御電圧を出力するか、は前提として仮定されている。この前提が崩れた場合、アルゴリズムが正確な係数を決定できなくなる。例えば、温度センサーは温度依存性の無い電圧と温度依存性がある電圧との差分で温度を検出しているが、これらの電圧が電源電圧の温度依存性の影響を受けると、環境温度に対して期待したセンサー出力（差分電圧）にならない。しかし、係数決定のアルゴリズムでは、環境温度とセンサー出力の対応が、期待通りの特性になっているという前提で係数を演算している。そのため、環境温度とセンサー出力の対応が変動すると、正確な温度補償ができなくなる。このような理由から、A T C X Oでは温度依存性が無い高安定の電源電圧が要求される。

30

#### 【0070】

温度センサーの一例としてはバンドギャップリファレンス回路を用いるものがあるが、一般にバンドギャップリファレンス回路は電源電圧に依らずに一定電圧を出力する回路とされている。しかしながら、バンドギャップリファレンス回路にもわずかに電源電圧依存性があり、非常に高精度な発振周波数が要求されるT C X O等の発振器では、そのわずかな変動が問題となる。

40

#### 【0071】

一方、本実施形態のようなD T C X O等のデジタル方式の発振器では、図3Bに示すように、温度検出データD T D（処理部50の入力データ）と周波数制御データD D S（処理部50の出力データ）との間の関係が得られる。例えば、温度検出データD T Dと周波

50

数制御データDDSは処理部50のレジスターに格納されており、不図示のデジタルインターフェースを介して外部から読み出される。温度補償の係数を決定する際には、恒温槽でいくつかの環境温度を設定し、各環境温度での温度検出データDTDと周波数制御データDDSを取得し、多項式によるフィッティングを行って温度補償用の多項式の係数を決定する。

【0072】

温度補償を行う際には、処理部50が係数を記憶部30（不揮発性メモリー）から読み出して、温度検出データDTD（A/D変換部20の出力データ）に対応する周波数制御データDDS（D/A変換部80の入力データ）を生成する。即ち、DTCXO等のデジタル方式の発振器では、係数決定の際にも温度補償の際にも、温度検出データDTDと周波数制御データDDSとの間の関係を使っている。このため、ATCxoのようなアルゴリズムの前提が必要なく、処理部50の前段或いは後段に温度依存性（例えば電源電圧の温度特性による温度センサーの出力変動）があったとしても、その温度特性は、温度検出データDTDと周波数制御データDDSとの間の関係に包含されている。これにより、振動子の発振周波数の温度特性だけでなく、回路装置の各部の温度依存性を含めて包括的に温度補償を行うことができる。

【0073】

また、ATCxo等のアナログ方式の発振器において仕事関数差に基づく基準電圧を電源電圧として用いた場合、電源電圧の絶対値変動が大きい、電源電圧の温度傾斜の変動が大きい、アナログ温度補償回路と仕事関数差の特性変数が別々にばらつく、等の問題がある。そのため、量産時において特性調整のためのトリミング工程等が増えてしまい、チップサイズや検査コストの面でデメリットがある。

【0074】

この点、本実施形態のようなDTCXO等のデジタル方式の発振器では、あらゆる温度依存性を含めて包括的に温度補償を行うことができるので、上記のような問題を生じずに、仕事関数差に基づく基準電圧を電源電圧として用いることが可能となる。特に、アナログ温度補償回路と仕事関数差の特性変数が別々にばらつく影響に対処することは困難であり、この点の考慮が不要になることは大きなメリットである。

【0075】

以下、更に詳細な電源回路40の構成について説明する。図4に、回路装置の第2の詳細な構成例を示す。図4の回路装置は基準電流生成回路170、電源回路40、温度センサー部10、A/D変換部20、処理部50、発振信号生成回路140、バッファーリード回路160を含む。また図4では、電源回路40が第1～第6の基準電圧生成回路41～46を含む。

【0076】

第1の基準電圧生成回路41は、仕事関数差に基づき生成された第1の基準電圧を、第1の電源電圧VRAとしてA/D変換部20に供給する。第2の基準電圧生成回路42は、仕事関数差に基づき生成された第2の基準電圧を、第2の電源電圧VRBとして処理部50に供給する。第3の基準電圧生成回路43は、仕事関数差に基づき生成された第3の基準電圧を、第3の電源電圧VRCとしてD/A変換部80に供給する。

【0077】

なお、電源回路40は、第1の基準電圧生成回路41、第2の基準電圧生成回路42、第3の基準電圧生成回路43の全てを含む必要はなく、これらのうちいずれか1つ又は2つだけを含んでもよい。

【0078】

このように、A/D変換部20、処理部50、D/A変換部80のそれぞれに対応して第1の基準電圧生成回路41、第2の基準電圧生成回路42、第3の基準電圧生成回路43を設けることで、各部の電源ラインを分離できる。これにより、電源ラインを介したノイズの伝搬を抑制し、発振信号の精度（例えば位相ノイズ特性）を向上できる。

【0079】

10

20

30

40

50

例えば、デジタル回路のノイズは、発振回路 150 による振動子 X T A L の発振に影響を与える、位相ノイズ特性等を悪化させる。この点、本実施形態では、処理部 50 に対応する第 2 の基準電圧生成回路 42 が設けられているので、発振回路 150 の電源ラインから、デジタル回路である処理部 50 の電源ラインを分離できる。これにより、発振回路 150 へのデジタル回路のノイズの伝搬を抑制できる。或いは、A / D 変換部 20 や D / A 変換部 80 に処理部 50 や発振回路 150 からのノイズが入力された場合、そのノイズにより A / D 変換部 20 の変換精度が低下して温度補償の精度に影響したり、D / A 変換部 80 の出力電圧 VQ のノイズが増加して位相ノイズ特性等が悪化したりする可能性がある。この点、本実施形態では、A / D 変換部 20 に対応する第 1 の基準電圧生成回路 41 が設けられ、或いは D / A 変換部 80 に対応する第 3 の基準電圧生成回路 43 が設けられるので、A / D 変換部 20 や D / A 変換部 80 へのノイズの伝搬を抑制できる。10

#### 【0080】

また、本実施形態では温度特性を有する仕事関数差を用いて電源電圧 VRA、VRB、VRC を生成しているが、その影響はデジタル温度補償処理により包括的に補償できる。即ち、電源電圧 VRA、VRC が温度特性をもつことによって A / D 変換部 20 や D / A 変換部 80 の変換結果に温度特性が生じる可能性があるが、この温度特性も含めてデジタル温度補償処理により補償される。

#### 【0081】

また、図 6 ~ 図 8 に示すように、仕事関数差により基準電圧を生成する仕事関数差アンプは、MOS トランジスターや抵抗で構成することが可能であり、構成も簡素であるため、バイポーラートランジスターを用いるバンドギャップリファレンス回路よりもレイアウト面積が小さい。そのため、各部のそれぞれに基準電圧生成回路を設けてもレイアウト面積の増加が抑えられ、仕事関数差アンプは電源ラインを分離する構成に適している。20

#### 【0082】

基準電流生成回路 170 は、基準電圧に基づいて基準電流を生成する。そして、発振回路 150 は、基準電流に基づく駆動電流により振動子 X T A L を発振させる。

#### 【0083】

具体的には、第 4 の基準電圧生成回路 44 が仕事関数差に基づいて基準電圧を生成し、その基準電圧を第 4 の電源電圧 VRD として基準電流生成回路 170 に出力する。そして、図 10 で後述するように、基準電流生成回路 170 は、基準電圧（電源電圧 VRD）に基づいて基準電流 IRD を生成し、その基準電流 IRD に対応したバイアス電圧 QD1、QD2 を発振回路 150 に出力し、発振回路 150 はバイアス電圧 QD1、QD2 をトランジスター T D d、T D e により駆動電流 IBX に変換し、駆動電流 IBX が供給されたバイポーラートランジスター TRX が振動子 X T A L を駆動する。30

#### 【0084】

このように、発振回路 150 に対応して基準電流生成回路 170 を設けることで、処理部 50 等の他の回路の電源ラインから発振回路 150 を分離できる。これにより、電源ラインを介したノイズの伝搬を抑制し、発振信号の精度（例えば位相ノイズ特性）を向上できる。また、本実施形態では温度特性を有する仕事関数差を用いて基準電圧を生成しているが、その影響はデジタル温度補償処理により包括的に補償できる。即ち、基準電圧が温度特性をもつことによって発振回路 150 の発振周波数特性に温度特性が生じる可能性があるが、この温度特性も含めてデジタル温度補償処理により補償される。40

#### 【0085】

第 5 の基準電圧生成回路 45 は、仕事関数差に基づき生成された第 5 の基準電圧を、第 5 の電源電圧 VRE として温度センサー部 10 に供給する。また、第 6 の基準電圧生成回路 46 は、仕事関数差に基づき生成された第 6 の基準電圧を、第 6 の電源電圧 VRF としてバッファー回路 160 に供給する。

#### 【0086】

このようにすれば、温度センサー部 10 やバッファー回路 160 の電源ラインを分離でき、電源ラインを介したノイズの伝搬を抑制できる。また、基準電圧の温度特性が温度セ50

ンサー部 10 のセンサー特性等に影響したとしても、その影響をデジタル温度補償処理により包括的に補償できる。

【0087】

図 5 に、本実施形態の回路装置を含む電子機器の基本構成例を示す。なお、図 16 B で後述するように電子機器は処理部 520 等の構成要素を含むことができるが、ここでは図示を省略している。

【0088】

図 5 の電子機器は、スイッチングレギュレーター 560 (外部電源回路) と、回路装置 500 を含む。回路装置 500 は電源回路 40 を含んでおり、電源回路 40 には、スイッチングレギュレーター 560 から外部電源 (電源電圧 VDD) が供給される。

10

【0089】

スイッチングレギュレーター 560 は、例えばトランジスター等のスイッチ素子とインダクター、キャパシター、ダイオード等で構成される。そして、スイッチ素子がオンになるオン期間では、電源とインダクターの一端がスイッチ素子を介して接続されてインダクターが駆動されると共にキャパシターに電荷が供給される。スイッチ素子がオフになるオフ期間では、電源とインダクターの一端が遮断され、インダクターに蓄えられたエネルギーが放電されてダイオードを介したキャパシターに電荷が供給される。スイッチングレギュレーター 560 の出力電圧をフィードバックすることにより、オン期間とオフ期間のデューティーが制御され、出力電圧が一定に保たれる。

【0090】

20

なお、スイッチングレギュレーター 560 の構成はこれに限定されず、スイッチ素子のオンオフにより断続的に電源を接続及び遮断する (ショッピングを行う) DC - DC コンバーターであればよい。

【0091】

このようなスイッチングレギュレーター 560 は、リニアレギュレーターのような抵抗による電力ロスがほとんどないため、リニアレギュレーターに比べて低消費電力である。一方、スイッチ素子によりショッピングを行うため、リニアレギュレーターに比べて外部電源 (電源電圧 VDD) のノイズが大きい。この点、本実施形態によれば、仕事関数差に基づき基準電圧を生成することで、電源回路 40 の消費電力を抑えつつ高 PSRR を実現することが可能であり、スイッチングレギュレーター 560 と電源回路 40 を含めた電源システム全体として低消費電力化できる。

30

【0092】

3. 基準電圧生成回路

図 6 に、基準電圧生成回路の第 1 の詳細な構成例を示す。なお、図 6 の基準電圧生成回路は、第 1 ~ 第 6 の基準電圧生成回路 41 ~ 46 のいずれにも適用できる。図 6 の基準電圧生成回路は、トランジスター TAa、TAb、TAc、TAd、TAE、抵抗 RNA、RPA、RGA (抵抗素子)、キャパシター CA、電流源 IGA を含む。

【0093】

トランジスター TAa とトランジスター TAb は、カレントミラー回路を構成し、トランジスター TAa (第 3 のトランジスター) とトランジスター TAd (第 4 のトランジスター) に電流を供給する。トランジスター TAa とトランジスター TAd は差動対を構成する。電流源 IGA は、差動対にバイアス電流を供給する。トランジスター TAa、TAb は例え P 型トランジスター (広義には第 1 導電型のトランジスター) であり、トランジスター TAc、TAd は N 型トランジスター (広義には第 2 導電型のトランジスター) である。またトランジスター TAa、TAb、TAd はエンハンスメント型のトランジスターであり、トランジスター TAc はデプレッショントランジスターである。

40

【0094】

トランジスター TAa、TAb は、電源用ノード NDG とノード NAA、NAb との間に設けられる。図 6 の構成例では、電源用ノード NDG は高電位側電源ノード (電源電圧 VDD のノード) である。トランジスター TAa、TAb のソースには電源用ノード ND

50

G の電圧 ( 電源電圧 V D D ) が供給され、トランジスター T A a 、 T A b のゲート電極はトランジスター T A a のドレインのノード N A a に接続される。

【 0 0 9 5 】

トランジスター T A c 、 T A d は、ノード N A a 、 N A b とノード N A f 、 N A c との間に設けられる。またノード N A f とノード N A c との間には抵抗 R N A が設けられる。トランジスター T A c のゲート電極には、電源電圧 V S S ( 低電位側電源電圧 ) が入力される。トランジスター T A d のゲート電極は、ノード N A d に接続される。電流源 I G A は、ノード N A c と電源電圧 V S S のノードとの間に直列に設けられる。

【 0 0 9 6 】

トランジスター T A e ( 第 5 のトランジスター ) はデプレッショニ型の N 型トランジスターである。トランジスター T A e は、電源用ノード N D G ( 高電位側電源ノード ) と出力ノード N A e ( 抵抗 R P A の一端 ) との間に設けられ、そのゲート電極に差動対の出力ノード N A b が接続される。即ち、トランジスター T A e は、トランジスター T A d のドレイン電圧に基づきゲート電圧が制御される。キャパシター C A は、ノード N A b と電源電圧 V S S のノード ( 低電位側電源ノード ) との間に設けられる。抵抗 R P A ( 第 1 の抵抗 ) は、出力ノード N A e とノード N A d ( トランジスター T A d のゲートノード ) の間に設けられ、一端 ( ノード N A e ) の電圧 V D O S を基準電圧として出力する。抵抗 R G A は、ノード N A d と電源電圧 V S S のノードとの間に設けられる。

【 0 0 9 7 】

トランジスター T A d は、トランジスター T A c とはゲート電極の導電性が異なるトランジスターになっている。例えばトランジスター T A c のゲート電極は N 型であり、トランジスター T A d のゲート電極は P 型となっている。例えばトランジスター T A c と T A d は、基板の不純物濃度やチャネルの不純物濃度は同じであるが、ゲート電極の導電性が異なっており、ゲート電極の不純物濃度が異なっている。

【 0 0 9 8 】

具体的には、 M O S トランジスターのしきい値電圧は、  $V_{th} = \frac{Q_{ss}}{C_{ox}} - \frac{Q_D}{C_{ox}} - V_F$  と表すことができる。ここで  $Q_{ss}$  は、ゲート電極と基板の仕事関数差であり、  $Q_{ss}$  は酸化膜内の固定電荷であり、  $C_{ox}$  はゲート酸化膜の単位面積当たりの容量であり、  $V_F$  はフェルミ準位であり、  $Q_D$  は空乏層内の電荷である。トランジスター T A c の N 型ゲート電極の不純物濃度と、トランジスター T A d の P 型ゲート電極の不純物濃度の設定により、デプレッショニ型のトランジスター T A c のしきい値電圧 V T N は例えば - 0 . 5 2 V に設定されており、エンハンスマント型のトランジスター T A d のしきい値電圧 V T P は例えば 0 . 4 5 V に設定されている。従って、基準電圧生成回路の出力ノード N A e には、  $V_{TP} - V_{TN} = 0 . 9 7 V$  の基準電圧 V D O S ( 電源電圧 ) が output されるようになる。即ち、電源電圧 V D D が変動した場合にも、一定電圧の基準電圧 V D O S を供給することが可能になる。

【 0 0 9 9 】

図 7 に、基準電圧生成回路の第 2 の詳細な構成例を示す。なお、図 7 の基準電圧生成回路は、第 1 ~ 第 6 の基準電圧生成回路 4 1 ~ 4 6 のいずれにも適用できる。図 7 の基準電圧生成回路は、第 1 の仕事関数差アンプ R E G 1 、第 2 の仕事関数差アンプ R E G 2 を含む。第 1 の仕事関数差アンプ R E G 1 は、トランジスター T B a 、 T B b 、 T B c 、 T B d 、 T B e 、抵抗 R N B 、 R P B 、 R G B ( 抵抗素子 ) 、キャパシター C B 、電流源 I G B を含む。第 2 の仕事関数差アンプ R E G 2 は、トランジスター T A a 、 T A b 、 T A c 、 T A d 、 T A e 、抵抗 R N A 、 R P A 、 R G A 、キャパシター C A 、電流源 I G A を含む。

【 0 1 0 0 】

第 2 の仕事関数差アンプ R E G 2 の構成は、図 6 の基準電圧生成回路の構成と同じであるが、図 7 では電源用ノード N D G に第 1 の仕事関数差アンプ R E G 1 の出力電圧 V r e g が入力される。

【 0 1 0 1 】

10

20

30

40

50

第 1 の仕事関数差アンプ REG 1 の構成を説明する。

【0102】

トランジスター TBa とトランジスター T B b は、カレントミラー回路を構成し、トランジスター TBc (第 6 のトランジスター) とトランジスター T Bd (第 7 のトランジスター) に電流を供給する。トランジスター TBc とトランジスター T Bd は差動対を構成する。電流源 IGB は、差動対にバイアス電流を供給する。トランジスター TBa、TBb は例えは P 型トランジスターであり、トランジスター TBc、TBd は N 型トランジスターである。またトランジスター TBa、TBb、TBd はエンハンスメント型のトランジスターであり、トランジスター TBc はデプレッショント型のトランジスターである。

【0103】

トランジスター TBa、TBb は、高電位側電源ノード (電源電圧 VDD のノード) とノード N Ba、N Bb との間に設けられる。トランジスター TBa、TBb のソースには電源電圧 VDD が供給され、トランジスター TBa、TBb のゲート電極はトランジスター TBa のドレインのノード N Ba に接続される。

【0104】

トランジスター TBc、TBd は、ノード N Ba、N Bb とノード N Bf、N Bc との間に設けられる。またノード N Bf とノード N Bc との間には抵抗 RN B が設けられる。トランジスター TBc のゲート電極には、電源電圧 VSS が入力される。トランジスター TBd のゲート電極は、ノード N Bd に接続される。電流源 IGB は、ノード N Bc と電源電圧 VSS のノードとの間に直列に設けられる。

【0105】

トランジスター TBe (第 8 のトランジスター) はデプレッショント型の N 型トランジスターである。トランジスター TBe は、高電位側電源ノードと出力ノード NBe (抵抗 RP B の一端) との間に設けられ、そのゲート電極に差動対の出力ノード NBb が接続される。即ち、トランジスター TBe は、トランジスター TBd のドレイン電圧に基づきゲート電圧が制御される。キャパシター CB は、ノード NBb と電源電圧 VSS のノードとの間に設けられる。抵抗 RP B (第 2 の抵抗) は、出力ノード NBe とノード NBd (トランジスター TBd のゲートノード) の間に設けられ、その一端には、トランジスター TBc、TBd の仕事関数差電圧に対応する電圧 Vreg が印加される。抵抗 RP B は、その一端の電圧 Vreg を第 1 の仕事関数差アンプ REG 1 の電源用ノード NDG に出力する。抵抗 RG B は、ノード NBd と電源電圧 VSS のノードとの間に設けられる。

【0106】

トランジスター TBd は、トランジスター TBc とはゲート電極の導電性が異なるトランジスターになっている。例えはトランジスター TBc のゲート電極は N 型であり、トランジスター TBd のゲート電極は P 型となっている。例えはトランジスター TBc と TBd は、基板の不純物濃度やチャネルの不純物濃度は同じであるが、ゲート電極の導電性が異なっており、ゲート電極の不純物濃度が異なっている。

【0107】

図 8 に、基準電圧生成回路の第 3 の詳細な構成例を示す。なお、図 8 の基準電圧生成回路は、第 1 ~ 第 6 の基準電圧生成回路 41 ~ 46 のいずれにも適用できる。図 8 の基準電圧生成回路は、第 1 の仕事関数差アンプ REG 1、第 2 の仕事関数差アンプ REG 2 を含む。第 1 の仕事関数差アンプ REG 1 は、トランジスター TCa、TCb、TCc、TCd、T Ce、抵抗 RNC、RPC (抵抗素子)、電流源 IGC を含む。第 2 の仕事関数差アンプ REG 2 は、トランジスター TAa、TAb、TAc、TAd、T Ae、抵抗 RNA、RPA、RGA、キャパシター CA、電流源 IGA を含む。

【0108】

第 2 の仕事関数差アンプ REG 2 の構成は、図 6 の基準電圧生成回路の構成と同じであるが、図 8 では電源用ノード NDG に第 1 の仕事関数差アンプ REG 1 の出力電圧 Vreg が入力される。

【0109】

10

20

30

40

50

第 1 の仕事関数差アンプ R E G 1 の構成を説明する。

【 0 1 1 0 】

トランジスター T C a とトランジスター T C b は、カレントミラー回路を構成し、トランジスター T C c ( 第 9 のトランジスター ) とトランジスター T C d ( 第 10 のトランジスター ) に電流を供給する。トランジスター T C c とトランジスター T C d は差動対を構成する。電流源 I G C は、差動対にバイアス電流を供給する。トランジスター T C a 、 T C b は例えば P 型トランジスターであり、トランジスター T C c 、 T C d は N 型トランジスターである。またトランジスター T C a 、 T C b 、 T C d はエンハンスメント型のトランジスターであり、トランジスター T C c はデプレッション型のトランジスターである。

【 0 1 1 1 】

トランジスター T C a 、 T C b は、高電位側電源ノード ( 電源電圧 V D D のノード ) とノード N C a 、 N C b との間に設けられる。トランジスター T C a 、 T C b のソースには電源電圧 V D D が供給され、トランジスター T C a 、 T C b のゲート電極はトランジスター T C a のドレインのノード N C a に接続される。

【 0 1 1 2 】

トランジスター T C c 、 T C d は、ノード N C a 、 N C b とノード N C f 、 N C g との間に設けられる。またノード N C f 、 N G g とノード N B c との間には抵抗 R N C 、 R P C が設けられる。トランジスター T C c のゲート電極には、電源電圧 V S S が入力される。トランジスター T C d のゲート電極は、トランジスター T C e のドレイン ( 電源用ノード N D G ) に接続される。電流源 I G C は、ノード N C c と電源電圧 V S S のノードとの間に直列に設けられる。

【 0 1 1 3 】

トランジスター T C e ( 第 11 のトランジスター ) はデプレッション型の N 型トランジスターである。トランジスター T C e は、高電位側電源ノードとトランジスター T C d のゲートノード ( 電源用ノード N D G ) との間に設けられる。即ち、トランジスター T C e は、トランジスター T C d のドレイン電圧に基づきゲート電圧が制御される。トランジスター T C d のドレイン電圧は、トランジスター T C c 、 T C d の仕事関数差電圧に対応する電圧 V r e g であり、その電圧 V r e g が電源用ノード N D G に出力される。

【 0 1 1 4 】

トランジスター T C d は、トランジスター T C c とはゲート電極の導電性が異なるトランジスターになっている。例えばトランジスター T C c のゲート電極は N 型であり、トランジスター T C d のゲート電極は P 型となっている。例えばトランジスター T C c と T C d は、基板の不純物濃度やチャネルの不純物濃度は同じであるが、ゲート電極の導電性が異なっており、ゲート電極の不純物濃度が異なっている。

【 0 1 1 5 】

図 7 、図 8 のように、第 1 の仕事関数差アンプ R E G 1 と第 2 の仕事関数差アンプ R E G 2 を直列に接続することによって、図 6 のような 1 段の仕事関数差アンプよりも更に P S R R を向上できる。図 9 は、基準電圧生成回路の P S R R の周波数特性の模式図である。図 9 では、縦軸、横軸は共に対数軸である ( P S R R は例えばデシベル ) 。 T K S 1 は 1 段の仕事関数差アンプの P S R R の周波数特性であり、 T K S 2 は 2 段の仕事関数差アンプの P S R R の周波数特性である。 T K S 2 に示すように、 2 段の仕事関数差アンプの場合、各段の P S R R が加算されるので、 1 段の仕事関数差アンプに比べて約 2 倍の P S R R が得られる。

【 0 1 1 6 】

また図 7 、図 8 において、トランジスター T A e ( 第 5 のトランジスター ) はデプレッション型のトランジスターである。

【 0 1 1 7 】

2 段の仕事関数差アンプでは、例えば第 1 の仕事関数差アンプ R E G 1 が電圧 V r e g = 0.97 V を出力し、第 2 の仕事関数差アンプ R E G 2 が電圧 V r e g = 0.97 V を電源として電圧 V D O S = 0.9 V を出力する。トランジスター T A e は N 型トランジス

10

20

30

40

50

ターであり、そのソースは電圧  $V_{DOS} = 0.9V$  であることから、非常に小さいゲート-ソース間電圧しか取ることができず、エンハンスマント型のトランジスターではオンさせることができない。この点、本実施形態ではトランジスター T A e がデプレッション型のトランジスターであることで、N型トランジスターであってもオンさせることが可能となる。

#### 【0118】

また、図 6 ~ 図 8において、仕事関数差アンプの出力段のトランジスター T A e、T B e、T C e は、N型トランジスターである。これにより、P型トランジスターを採用した場合に比べて P S R R の向上が期待できる。例えば図 6 のトランジスター T A e を例にとって説明する。トランジスター T A e に P型トランジスターを採用した場合、P型トランジスターのソースは電源電圧  $V_{DD}$  となる。そのためゲート-ソース間電圧は電源電圧  $V_{DD}$  のノイズの影響を受けるが、アンプの帯域内ではアンプのゲインによって P S R R が保たれる。しかしながら、アンプの帯域外の高周波帯域では電源電圧  $V_{DD}$  のノイズの影響を受けて P S R R が低下する。一方、トランジスター T A e に N型トランジスターを採用することによって、トランジスター T A e のソースは出力電圧  $V_{DOS}$  となり、ゲート-ソース間電圧は電源電圧  $V_{DD}$  のノイズの影響を受けにくくなる。しかしながら、上述のようにオンさせにくいという問題が生じるので、デプレッション型のトランジスターを用いることによって、これを解決している。

#### 【0119】

また図 6 ~ 図 8において、キャパシター C A が、トランジスター T A e ( 第 5 のトランジスター ) のゲートノード N A b と低電位側電源ノードとの間に設けられる。また図 7において、キャパシター C B が、トランジスター T B e ( 第 8 のトランジスター ) のゲートノード N B b と低電位側電源ノードとの間に設けられる。

#### 【0120】

これにより、高周波領域における P S R R を更に向かうことができる。図 9 の T K S 1' は、キャパシター C A ( C B ) を設けなかった場合の仕事関数差アンプの P S R R の周波数特性であり、T K S 1 は、キャパシター C A ( C B ) を設けた場合の仕事関数差アンプの P S R R の周波数特性である。キャパシター C A を設けなかった場合の周波数特性 T K S 1' は、低周波領域と高周波領域では、キャパシター C A を設けた場合の周波数特性 T K S 1 と同じである。低周波領域では、アンプの D C ゲインとほぼ同じ P S R R が得られ、高周波領域ではキャパシター C A の容量とトランジスター T A e のソース-ドレイン間の寄生容量との比で P S R R が決まる。キャパシター C A を設けなかった場合の周波数特性 T K S 1' では、低周波領域と高周波領域の間に P S R R が非常に低くなる ( ゼロになる ) 周波数  $f_A$  が存在する。この周波数  $f_A$  の付近では、電源のノイズが基準電圧に伝搬するため、位相ノイズ特性の悪化の原因となる。

#### 【0121】

この点、本実施形態では、キャパシター C A ( C B ) を設けることによって、周波数  $f_A$  付近での P S R R を向かうことができる。これにより、広い帯域にわたって高い P S R R を得ることができ、位相ノイズ特性を向かうことができる。

#### 【0122】

##### 4. 基準電流生成回路、発振回路

図 10 に、基準電流生成回路 170、発振回路 150 の詳細な構成例を示す。

#### 【0123】

基準電流生成回路 170 は、トランジスター T D a、T D b、T D c、演算増幅器 A M D 1、A M D 2、抵抗 R D を含む。

#### 【0124】

トランジスター T D a ( 第 1 のトランジスター ) は、高電位側電源ノード ( 電源電圧  $V_{RD}$  のノード ) と第 1 のノード N D c の間に設けられる。トランジスター T D b ( 第 2 のトランジスター ) は、第 1 のノード N D c と第 2 のノード N D b の間に設けられる。トランジスター T D a、T D b は、例えばエンハンスマント型の P型トランジスターである。

10

20

30

40

50

## 【0125】

演算増幅器AMD1(第1の演算増幅器)の第1の入力ノードNDa(正極性入力ノード、非反転入力ノード)には、電源電圧VRDが入力され、演算増幅器AMD1の第2の入力ノード(負極性入力ノード、反転入力ノード)は、第2のノードNDbに接続され、演算増幅器AMD1の出力ノードNDfは、トランジスターTDAのゲートに接続される。

## 【0126】

演算増幅器AMD2(第2の演算増幅器)の第1の入力ノードNDd(正極性入力ノード、非反転入力ノード)には、第1のノードNDcの電圧VNDcを設定するための所定電圧VVDが入力され、演算増幅器AMD2の第2の入力ノード(負極性入力ノード、反転入力ノード)は、第1のノードNDcに接続され、演算増幅器AMD2の出力ノードNDgは、トランジスターTDbのゲートに接続される。

## 【0127】

トランジスターTDCは、ノードNDbとノードNDhの間に設けられ、そのゲートには電源電圧VSSが入力される。トランジスターTDCは、例えばデプレッション型のN型トランジスターである。抵抗RDは、ノードNDhと低電位側電源ノードの間に設けられる。抵抗RDは可変抵抗であり、例えばスイッチによりタップを選択することで抵抗値が可変に制御できるラダー抵抗等で構成できる。トランジスターTDCと抵抗RDは、トランジスターTDA、TDbにバイアス電流を供給する電流源である。抵抗RDの抵抗値を調整することで、基準電流IRDが調整できる。

## 【0128】

所定電圧VVDは、例えば $VVD = VRD - 0.2V$ に設定され、演算増幅器AMD2のフィードバック制御により、第1のノードNDcの電圧は $VNDc = VVD = VRD - 0.2V$ となる。また、演算増幅器AMD1のフィードバック制御により、第2のノードNDbの電圧は $VNDb = VRD$ となる。このように第1のノードNDcの電圧VNDcと第2のノードNDbの電圧VNDbが固定されることによって、高電位側電源(電源電圧VRD)の変動の影響を受けにくくなり、高安定な基準電流IRDを生成することができる。

## 【0129】

発振回路150は、トランジスターTDD、TDe、バイポーラートランジスターTRX、抵抗RX、可変容量キャパシターCX1、キャパシターCX2、CX3を含む。

## 【0130】

トランジスターTDD、TDeには、基準電流生成回路170のトランジスターTDA、TDbのゲート電圧(バイアス電圧QD1、QD2)が入力される。即ち、トランジスターTDD、TDeは、基準電流IRDを所定比でミラーし、バイポーラートランジスターTRXのコレクターに駆動電流IBX(バイアス電流)を供給する。抵抗RXは、バイポーラートランジスターTRXのコレクターとベースの間に設けられる。

## 【0131】

容量が可変である可変容量キャパシターCX1の一端は、振動子XTALの一端に接続される。具体的には、可変容量キャパシターCX1の一端は、回路装置の第1の振動子用端子(振動子用パッド)を介して振動子XTALの一端に接続される。キャパシターCX2の一端は、振動子XTALの他端に接続される。具体的には、キャパシターCX2の一端は、回路装置の第2の振動子用端子(振動子用パッド)を介して振動子XTALの他端に接続される。キャパシターCX3は、その一端が振動子XTALの一端に接続され、その他端がバイポーラートランジスターTRXのコレクターに接続される。

## 【0132】

バイポーラートランジスターTRXには、振動子XTALの発振により生じたベース・エミッター間電流が流れる。そしてベース・エミッター間電流が増加すると、バイポーラートランジスターTRXのコレクター・エミッター間電流が増加し、駆動電流IBXのうち抵抗RXに分岐するバイアス電流が減少するので、コレクター電圧VCXが低下する。

10

20

30

40

50

一方、バイポーラートランジスターTRXのベース・エミッター間電流が減少すると、コレクター・エミッター間電流が減少し、駆動電流IBXのうち抵抗RXに分岐するバイアス電流が増加するので、コレクター電圧VCXが上昇する。このコレクター電圧VCXはキャパシターCX3を介して振動子XTALにフィードバックされる。

【0133】

振動子XTALの発振周波数は温度特性（例えば図3A、図3Bの温度特性）を有しており、この温度特性は、D/A変換部80の出力電圧VQ（周波数制御電圧）により補償される。即ち、出力電圧VQは可変容量キャパシターCX1に入力され、出力電圧VQにより可変容量キャパシターCX1の容量値が制御される。可変容量キャパシターCX1の容量値が変化すると、発振ループの共振周波数が変化するので、振動子XTALの温度特性による発振周波数の変動が補償される。可変容量キャパシターCX1は、例えば可変容量ダイオード（バラクター）などにより実現される。

10

【0134】

なお、本実施形態の発振回路150は、図10の構成に限定されず、種々の変形実施が可能である。例えば図10ではCX1を可変容量キャパシターとする場合を例に説明したが、CX2又はCX3を、出力電圧VQで制御される可変容量キャパシターとしてもよい。また、CX1～CX3のうち複数を、VQで制御される可変容量キャパシターとしてもよい。

【0135】

5. D/A変換部

20

図11に、D/A変換部80の詳細な構成例を示す。D/A変換部80は、変調回路90とD/A変換器100とフィルター回路120を含む。

【0136】

D/A変換器100は、上位側のD/A変換器DACAと、下位側のD/A変換器DACPと、ボルテージフォロワー接続されたオペアンプ（演算増幅器）OPA、OPB、OPCを含む。

【0137】

上位側のD/A変換器DACAには、変調回路90からのnビット（ $n = q + p$ ）のデータDMのうちの上位のqビットのデータが入力され、下位側のD/A変換器DACPには下位のpビット（例えば $p = q = 8$ ）のデータが入力される。これらの上位側のD/A変換器DACA、下位側のD/A変換器DACPは、例えば直列接続された複数の抵抗により電圧分割された複数の分割電圧の中から、入力データに対応する電圧を選択する抵抗ストリング型のD/A変換器である。

30

【0138】

上位側のD/A変換器DACAは、電源電圧VRC（基準電圧）のノードと電圧VSSのノードとの間に直列接続された複数の抵抗を含む。上位側のD/A変換器DACAは、複数の抵抗のうち上位qビットのデータにより特定される抵抗の両端の分割電圧のうち、一方の分割電圧をオペアンプOPAの非反転入力端子に出力し、他方の分割電圧をオペアンプOPBの非反転入力端子に出力する。これにより、当該一方の電圧が、ボルテージフォロワー接続されたオペアンプOPAによりインピーダンス変換されて、電圧VXとして下位側のD/A変換器DACPに供給される。また当該他方の電圧が、ボルテージフォロワー接続されたオペアンプOPBによりインピーダンス変換されて、電圧VYとして下位側のD/A変換器DACPに供給される。

40

【0139】

下位側のD/A変換器DACPは、電圧VXのノードと電圧VYのノードとの間に直列接続された複数の抵抗を含む。下位側のD/A変換器DACPは、複数の抵抗による複数の分割電圧のうち、下位pビットのデータにより選択された1つの分割電圧を選択電圧として、ボルテージフォロワー接続されたオペアンプOPCの非反転入力端子に出力する。これにより、当該選択電圧が、D/A変換器100の出力電圧VDAとして出力されるようになる。

50

## 【0140】

## 6. 温度センサー部、発振回路

図12Aに温度センサー部10の第1の構成例を示す。図12Aの温度センサー部10は、電流源ISTと、電流源ISTからの電流がコレクターに供給されるバイポーラートランジスターTRTを有する。バイポーラートランジスターTRTは、そのコレクターとのベースが接続されるダイオード接続となっており、バイポーラートランジスターTRTのコレクターのノードに、温度特性を有する温度検出電圧VTDが outputされる。温度検出電圧VTDの温度特性は、バイポーラートランジスターTRTのベース・エミッター間電圧の温度依存性によって生じる。図12Cに示すように温度検出電圧VTDは、負の温度特性（負の勾配を有する1次の温度特性）を有する。

10

## 【0141】

図12Bに温度センサー部10の第2の構成例を示す。図12Bでは、図12Aの電流源ISTが抵抗RTにより実現される。そして抵抗RTの一端は電源電圧のノードに接続され、他端はバイポーラートランジスターTRT1のコレクターに接続される。またバイポーラートランジスターTRT1のエミッターは、バイポーラートランジスターTRT2のコレクターに接続される。そしてバイポーラートランジスターTRT1、TRT2は共にダイオード接続されており、バイポーラートランジスターTRT1のコレクターのノードに出力される電圧VTSQは、図12Cのように負の温度特性（負の勾配を有する1次の温度特性）を有している。

20

## 【0142】

また図12Bの温度センサー部10では、オペアンプOPDと抵抗RD1、RD2が更に設けられている。オペアンプOPDの非反転入力端子には、電圧VTSQが入力され、反転入力端子には、抵抗RD1の一端及び抵抗RD2の一端が接続される。そして抵抗RD1の他端には基準温度電圧VTA0が供給され、抵抗RD2の他端はオペアンプOPDの出力端子に接続される。

30

## 【0143】

このようなオペアンプOPD及び抵抗RD1、RD2により、基準温度電圧VAT0を基準として電圧VTSQを正転増幅する増幅アンプが構成される。これにより、温度検出電圧 $VTD = VAT0 + (1 + RD2 / RD1) \times (VTSQ - VAT0)$ が、温度センサー部10から出力されるようになる。そして基準温度電圧VAT0を調整することにより、基準温度T0の調整が可能になる。

## 【0144】

## 7. A/D変換部

図13に、A/D変換部20の詳細な構成例を示す。A/D変換部20は、処理部23、レジスター部24、D/A変換器DACE、DACF、比較部27を含む。また温度センサー部用アンプ28を含むことができる。処理部23、レジスター部24は、ロジック部22として設けられ、D/A変換器DACE、DACF、比較部27、温度センサー部用アンプ28は、アナログ部26として設けられる。

30

## 【0145】

レジスター部24は、A/D変換の途中結果や最終結果などの結果データを記憶する。このレジスター部24は、例えば逐次比較方式における逐次比較結果レジスターに相当する。D/A変換器DACE、DACFは、レジスター部24の結果データをD/A変換する。これらのDACE、DACFとしては図11と同様の構成のD/A変換器を採用できる。比較部27は、D/A変換器DACE、DACFの出力電圧と、温度検出電圧VTD（温度センサー部用アンプ28による増幅後の電圧）との比較を行う。比較部27は例えばチョッパー型比較器などにより実現できる。処理部23は、比較部27の比較結果に基づいて判定処理を行い、レジスター部24の結果データの更新処理を行う。そして、当該更新処理により求められた最終的な温度検出データDTDが、温度検出電圧VTDのA/D変換結果として、A/D変換部20から出力される。このような構成により、例えば逐次比較方式のA/D変換や、逐次比較方式に類似する方式のA/D変換などを実現できる

40

50

。

## 【0146】

## 8. 回路装置の変形構成例

図14に本実施形態の回路装置の第1の変形構成例を示す。

## 【0147】

図14の回路装置は、電源回路40、温度センサー部10、A/D変換部20、処理部50、発振信号生成回路140、バッファーレジスタ回路160を含む。

## 【0148】

図14では、電源回路40が、基準電圧生成回路42、44、46、47を含む。またA/D変換部20が、アナログ部26、ロジック部22を含み、D/A変換部80が、ロジック部82、アナログ部84を含む。A/D変換部20のアナログ部26、ロジック部22は、図13のアナログ部26、ロジック部22に対応する。D/A変換部80のロジック部82は、図2、図11の変調回路90に対応し、アナログ部84は、図2、図11のD/A変換器100とフィルター回路120に対応する。

10

## 【0149】

基準電圧生成回路47は、トランジスターの仕事関数差に基づき生成した基準電圧を電源電圧VRGとして、温度センサー部10、A/D変換部20のアナログ部26、D/A変換部80のアナログ部84に供給する。基準電圧生成回路42は、トランジスターの仕事関数差に基づき生成した基準電圧を電源電圧VRBとして、A/D変換部20のロジック部22、処理部50、D/A変換部80のロジック部82に供給する。

20

## 【0150】

図4等で説明したように、電源回路40は、仕事関数差に基づき生成された第1の基準電圧を第1の電源電圧としてA/D変換部20に供給する第1の基準電圧発生回路と、仕事関数差に基づき生成された第2の基準電圧を第2の電源電圧として処理部50に供給する第2の基準電圧発生回路と、仕事関数差に基づき生成された第3の基準電圧を第3の電源電圧としてD/A変換部80に供給する第3の基準電圧発生回路のうちの、少なくとも1つを有すればよい。

20

## 【0151】

図4では、第1～第3の基準電圧生成回路を設ける場合を図示している。一方、図14では第1～第3の基準電圧生成回路のうち2つの基準電圧生成回路を設ける場合に相当する。即ち、図14の基準電圧生成回路47は、第1の基準電圧発生回路又は第3の基準電圧発生回路に対応すると考えられるので、図14の電源回路40は、第1の基準電圧発生回路及び第2の基準電圧生成回路を含む場合、或いは、第2の基準電圧生成回路及び第3の基準電圧生成回路を含む場合の変形構成例である。

30

## 【0152】

図15に本実施形態の回路装置の第2の変形構成例を示す。

## 【0153】

図15の回路装置は、温度センサー部10からの温度検出電圧VTDのA/D変換を行い、温度検出データDTDを出力するA/D変換部20と、温度検出データDTDに基づいて発振周波数の温度補償処理を行い、発振周波数の周波数制御データDDDSを出力する処理部50と、発振信号生成回路140を含む。なお図15では電源回路40の図示を省略している。

40

## 【0154】

発振信号生成回路140は、処理部50からの周波数制御データDDDSと振動子XTALを用いて、周波数制御データDDDSにより設定される発振周波数の発振信号SSCを生成する。即ち図15では、図1、図2、図4とは異なり、発振信号生成回路140にD/A変換部80が設けられていない。そして発振信号生成回路140により生成される発振信号SSCの発振周波数が、処理部50からの周波数制御データDDDSに基づいて、直接に制御される。即ちD/A変換部を介さずに発振信号SSCの発振周波数が制御される。

## 【0155】

50

例えば図15では、発振信号生成回路140が、可変容量回路142と発振回路150を有する。この発振信号生成回路140には図1、図2、図4のD/A変換部80は設けられていない。そして図10の可変容量キャパシターCX1の代わりに、この可変容量回路142が設けられ、可変容量回路142の一端が振動子XTALの一端に接続される。

#### 【0156】

この可変容量回路142は、処理部50からの周波数制御データDDSに基づいて、その容量値が制御される。例えば可変容量回路142は、複数のキャパシター（キャパシターアレイ）と、周波数制御データDDSに基づき各スイッチ素子のオン、オフが制御される複数のスイッチ素子（スイッチアレイ）を有する。これらの複数のスイッチ素子の各スイッチ素子は、複数のキャパシターの各キャパシターに電気的に接続される。そして、これらの複数のスイッチ素子がオン又はオフされることで、複数のキャパシターのうち、振動子XTALの一端に、その一端が接続されるキャパシターの個数が変化する。これにより、可変容量回路142の容量値が制御されて、振動子XTALの一端の容量値が変化する。従って、周波数制御データDDSにより、可変容量回路142の容量値が直接に制御されて、発振信号SSCの発振周波数を制御できるようになる。

#### 【0157】

##### 9. 発振器、電子機器、移動体

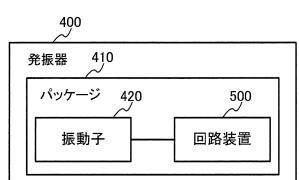

図16Aに、本実施形態の回路装置500を含む発振器400の構成例を示す。図16Aに示すように、発振器400は、振動子420と回路装置500を含む。振動子420と回路装置500は、発振器400のパッケージ410内に実装される。そして振動子420の端子と、回路装置500（IC）の端子（パッド）は、パッケージ410の内部配線により電気的に接続される。

#### 【0158】

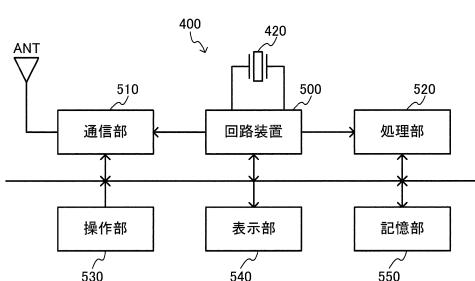

図16Bに、本実施形態の回路装置500を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置500、水晶振動子等の振動子420、アンテナANT、通信部510、処理部520を含む。また操作部530、表示部540、記憶部550を含むことができる。振動子420と回路装置500により発振器400が構成される。なお電子機器は図16Bの構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【0159】

図16Bの電子機器としては、例えばGPS内蔵時計、生体情報測定機器（脈波計、歩数計等）又は頭部装着型表示装置等のウェアラブル機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノートPC又はタブレットPC等の携帯情報端末（移動端末）や、コンテンツを配信するコンテンツ提供端末や、デジタルカメラ又はビデオカメラ等の映像機器や、或いは基地局又はルーター等のネットワーク関連機器などの種々の機器を想定できる。

#### 【0160】

通信部510（無線回路）は、アンテナANTを介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部520は、電子機器の制御処理や、通信部510を介して送受信されるデータの種々のデジタル処理などを行う。この処理部520の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。

#### 【0161】

操作部530は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部540は、各種の情報を表示するものであり、液晶や有機ELなどのディスプレイにより実現できる。なお操作部530としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが操作部530及び表示部540の機能を兼ねることになる。記憶部550は、データを記憶するものであり、その機能はRAMやROMなどの半導体メモリーやHDD（ハードディスクドライブ）などにより実現できる。

#### 【0162】

10

20

30

40

50

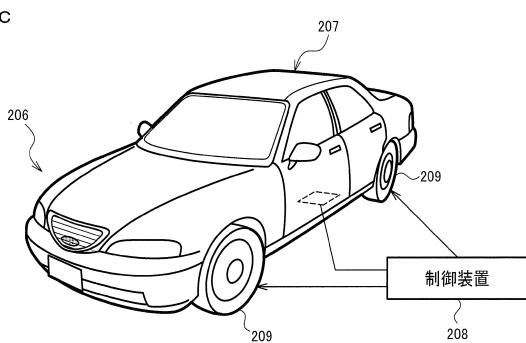

図16Cに、本実施形態の回路装置を含む移動体の例を示す。本実施形態の回路装置(発振器)は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器(車載機器)を備えて、地上や空や海上を移動する機器・装置である。図16Cは移動体の具体例としての自動車206を概略的に示している。自動車206には、本実施形態の回路装置と振動子を有する発振器(不図示)が組み込まれる。制御装置208は、この発振器により生成されたクロック信号により動作する。制御装置208は、例えば車体207の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪209のブレーキを制御する。例えば制御装置208により、自動車206の自動運転を実現してもよい。なお本実施形態の回路装置や発振器が組み込まれる機器は、このような制御装置208には限定されず、自動車206等の移動体に設けられる種々の機器(車載機器)に組み込むことが可能である。

10

#### 【0163】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また回路装置、発振器、電子機器、移動体の構成・動作等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。

20

#### 【符号の説明】

#### 【0164】

10 ... 温度センサー部、20 ... A / D 変換部、22 ... ロジック部、23 ... 処理部、

24 ... レジスター部、26 ... アナログ部、27 ... 比較部、

28 ... 温度センサー部用アンプ、30 ... 記憶部、40 ... 電源回路、

41 ... 第1の基準電圧生成回路、42 ... 第2の基準電圧生成回路、

43 ... 第3の基準電圧生成回路、44 ... 第4の基準電圧生成回路、

45 ... 第5の基準電圧生成回路、46 ... 第6の基準電圧生成回路、

50 ... 処理部、80 ... D / A 変換部、90 ... 变調回路、100 ... D / A 変換器、

110 ... デジタル温度補償発振回路、120 ... フィルター回路、

140 ... 発振信号生成回路、142 ... 可変容量回路、150 ... 発振回路、

160 ... バッファーレジスタ回路、170 ... 基準電流生成回路、206 ... 自動車、

207 ... 車体、208 ... 制御装置、209 ... 車輪、400 ... 発振器、

410 ... パッケージ、420 ... 振動子、500 ... 回路装置、510 ... 通信部、

520 ... 処理部、530 ... 操作部、540 ... 表示部、550 ... 記憶部、

560 ... スイッチングレギュレーター、

AMD1 ... 第1の演算増幅器、AMD2 ... 第2の演算増幅器、CA ... キャパシター、

DDS ... 周波数制御データ、DTD ... 温度検出データ、IBX ... 駆動電流、

IRD ... 基準電流、NDG ... 電源用ノード、NDb ... 第2のノード、

NDc ... 第1のノード、RPA ... 第1の抵抗、RPB ... 第2の抵抗、

SSC ... 発振信号、TAc ... 第3のトランジスター、TAd ... 第4のトランジスター、

TAe ... 第5のトランジスター、TBe ... 第6のトランジスター、

TBd ... 第7のトランジスター、TBe ... 第8のトランジスター、

TCc ... 第9のトランジスター、TCd ... 第10のトランジスター、

TCe ... 第11のトランジスター、TDa ... 第1のトランジスター、

TDb ... 第2のトランジスター、VRA ... 第1の電源電圧、VRB ... 第2の電源電圧、

VRC ... 第3の電源電圧、VTD ... 温度検出電圧、VVD ... 所定電圧、

XTAL ... 振動子

10

20

30

40

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 4 】

【図15】

## 【 図 1 6 】

図16A

図16B

図16C

---

フロントページの続き

(56)参考文献 特開2011-120058(JP,A)

特開2015-035706(JP,A)

特開平10-290118(JP,A)

特開2013-207363(JP,A)

特表2011-507105(JP,A)

特開2008-152632(JP,A)

特開2010-004621(JP,A)

特開2015-104035(JP,A)

特開2009-265955(JP,A)

特開2011-192272(JP,A)

特開2005-317948(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03B 5/00 - 5/42

H03L 1/00 - 7/26