(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-106902

(P2016-106902A)

(43) 公開日 平成28年6月20日(2016.6.20)

| (51) Int.Cl.            | F 1           |         | テーマコード (参考) |

|-------------------------|---------------|---------|-------------|

| A 6 1 B 1/04 (2006.01)  | A 6 1 B 1/04  | 3 6 2 J | 2 H 0 4 0   |

| G 0 2 B 23/24 (2006.01) | A 6 1 B 1/04  | 3 7 2   | 4 C 1 6 1   |

| H 0 4 N 5/225 (2006.01) | G 0 2 B 23/24 | B       | 5 C 0 5 4   |

| H 0 4 N 7/18 (2006.01)  | H 0 4 N 5/225 | C       | 5 C 1 2 2   |

|                         | H 0 4 N 7/18  | M       |             |

審査請求 未請求 請求項の数 6 O L (全 15 頁)

|           |                              |            |                                               |

|-----------|------------------------------|------------|-----------------------------------------------|

| (21) 出願番号 | 特願2014-248315 (P2014-248315) | (71) 出願人   | 000113263<br>HO Y A 株式会社<br>東京都新宿区西新宿六丁目10番1号 |

| (22) 出願日  | 平成26年12月8日 (2014.12.8)       | (74) 代理人   | 100090169<br>弁理士 松浦 孝                         |

|           |                              | (74) 代理人   | 100124497<br>弁理士 小倉 洋樹                        |

|           |                              | (72) 発明者   | 小林 敦至<br>東京都新宿区中落合2丁目7番5号 HO<br>Y A 株式会社内     |

|           |                              | (72) 発明者   | 水口 直志<br>東京都新宿区中落合2丁目7番5号 HO<br>Y A 株式会社内     |

|           |                              | F ターム (参考) | 2H040 CA09 CA11 CA12 CA23 GA02<br>GA11        |

最終頁に続く

(54) 【発明の名称】 内視鏡装置

## (57) 【要約】

【課題】内視鏡装置において、簡易な構成で同期ずれの影響なく画素データを高速シリアル伝送する。

【解決手段】、画素データを抽出後にノイズなどの影響で同期ずれが生じた場合、ブランкиング期間を検出し、22ビットのセグメントデータ幅でシリアルデータを区切りながら、1ビットずつ区切り範囲を順次シフトさせて22個の同期検出用のパラレルデータを生成する。そして、ブランкиング期間に埋め込まれた同期検出用データとデータ配列が等しいパラレルデータを選択し、出力する。

【選択図】図6

**【特許請求の範囲】****【請求項 1】**

スコープ先端部に設けられた撮像素子と、

スコープ先端部に設けられ、前記撮像素子から読み出される画素信号をデジタルシリアル化した画素データに対し、プランキング期間に同期検出用プランキングデータを埋め込み、また、所定のデータ幅に従って同期データを埋め込んでシリアルデータを出力する送信部と、

スコープ基端側もしくは内視鏡プロセッサに設けられており、受信したシリアルデータにおける画素データを抽出する受信部とを備え、

前記受信部が、前記データ幅に前記同期データのビット数を加えたセグメントデータ幅に従い、プランキング期間のシリアルデータを区切り、データ区切り範囲を所定ビットずつシフトさせた複数の同期検出用データを生成し、そして、前記複数の同期検出用データの中から、前記プランキングデータに相当する同期検出用データを選択することを特徴とする内視鏡装置。10

**【請求項 2】**

前記送信部が、ビットデータ「1」のビット列およびビットデータ「0」のビット列を交互に配置させた同期検出用プランキングデータを、プランキング期間に埋め込むことを特徴とする請求項1に記載の内視鏡装置。

**【請求項 3】**

前記送信部が、ビットデータ「1」ビットデータ「0」が交互に繰り返される同期検出用プランキングデータを、プランキング期間に埋め込むことを特徴とする請求項1に記載の内視鏡装置。20

**【請求項 4】**

前記受信部が、映像信号規格に従ってプランキング期間に付加されている規格コードを検出することによって、プランキング期間を検出することを特徴とする請求項1乃至3のいずれかに記載の内視鏡装置。

**【請求項 5】**

前記受信部が、同期検出用データの選択後、前記受信部において同期ずれが生じているか否かを検出し、同期ずれが生じている場合、同期検出用データを再び選択することを特徴とする請求項1乃至4のいずれかに記載の内視鏡装置。30

**【請求項 6】**

前記受信部が、複数の同期検出データをパラレルデータとして生成することを特徴とする請求項1乃至5のいずれかに記載の内視鏡装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、スコープ(内視鏡)によって器官内壁などの被写体を観察、処置等する内視鏡装置に関し、特に、スコープ先端部に設けられた撮像素子から読み出される画素信号のシリアル伝送に関する。

**【背景技術】****【0002】**

電子内視鏡装置においては、撮像素子がビデオスコープ先端部に設けられており、撮像素子から読み出されたアナログ画像信号は、ビデオスコープ内部に配線された信号線によってスコープ基端側/プロセッサ側へ伝送される。そして、スコープコネクタ部あるいはプロセッサ内部に設けられた画像処理回路においてデジタル化され、画像信号が生成される。

**【0003】**

C C Dを使用する場合、アナログ画素信号をスコープ先端部からプロセッサ側へ伝送する。このとき、信号線が比較的長いために信号減衰や外乱ノイズの影響により、観察画像の画質を低下させる。一方、C M O Sを使用する場合、撮像素子に信号処理回路を内蔵で40

きるため、スコープ先端部において画素信号をデジタル化し、パラレル／シリアル変換してからシリアル画素データをプロセッサ側へシリアル伝送することが容易に可能である（特許文献1参照）。

#### 【0004】

シリアル伝送としては、8 b / 10 bと呼ばれる変調方式を用いたシリアル伝送方式が一般的に採用される。8 b / 10 b変調を用いることによって、変調されたシリアル信号にクロックを埋め込む事ができる。具体的には、撮像素子から読み出される画像データをパラレル／シリアル変換部においてシリアルデータに変換し、さらに、8 b / 10 bのデータ変換表に基づき、8ビット毎に10ビットに変換したシリアル信号を出力する。

#### 【0005】

受信側では、送られてきた8 b / 10 bによる変調シリアル信号から、特定のクロック・データ・リカバリ（CDR）手法を用いてRefクロックを抽出（再生）する。さらに、CDRにより再生されたRefクロックによってシリアル信号をリタイミングすることにより、8 b / 10 b変調状態の画素データを生成する。そして、リタイミングしたシリアル信号を10ビット毎に10b / 8b逆変換し、その後、シリアル／パラレル変換部によってシリアルデータをパラレルデータに変換することにより、元の画像信号を生成する。

#### 【0006】

8 b / 10 b伝送方式のような高速シリアル伝送方式の場合、送信側、受信側にデータ量の大きい変換テーブルをもつデータ変換処理回路を設ける必要がある。このような専用回路を内視鏡システムのスコープ先端部に設けることは、スコープ先端部をできる限り細径化することへの障害となる。また、変換処理回路を撮像素子傍に設けることで、画素信号を撮像素子から読み出すとき、ノイズを発生させる恐れがある。

#### 【0007】

そこで、画素データをパラレル／シリアル変換する際、決まったデータ単位（例えばパラレル信号が10bitであれば10bit）に対してその前後にスタートビット（S）、エンドビット（E）を付けた基本単位であるワード（例えば12bit）を生成し、生成したワードを繋げてシリアル化する方法が知られている（特許文献2、3参照）。

#### 【0008】

そこでは、8 b / 10 b変調のようにクロックの埋め込みを行う代わりに、Refクロック抽出（再生）のため、周期一定のスタートビット／エンドビット（S/E）の遷移エッジを利用してRefクロックを抽出する。Refクロック抽出にはスタートビット／エンドビット（S/E）遷移周期と同じ周期、位相のイニシャルパターン信号をスコープ先端部側から送信する。

#### 【0009】

受信（プロセッサ、またはスコープ基部）側では、スコープ起動時、先端側から送られてくるイニシャルパターンに同期クロックを同期させ、Refクロックを生成する。同期完了に従って先端部へ同期完了信号を送ると、スコープ先端部は、イニシャルパターンからシリアル映像信号に送信する信号を切り替える。イニシャルパターンとシリアル映像信号のS/Eの遷移エッジの位相は一致していることから、イニシャルパターンから生成した同期クロックによって画素データ（映像データ）が抽出され、パラレル／シリアル変換される。

#### 【先行技術文献】

#### 【特許文献】

#### 【0010】

【特許文献1】特開2009-201540号公報

【特許文献2】特開2014-110843号公報

【特許文献3】特開2014-110855号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

10

20

30

40

50

## 【0011】

特許文献2、3に記載された画素データの転送方法では、イニシャルパターンの送信が必須となり、イニシャルデータから映像用画素データの切り替えのためにも、スコープ先端部送信側と受信側との間で相互通信する必要がある。また、ノイズなど外乱によって信号が乱れ同期が外れた場合、イニシャルパターンに切り替えて再同期させる必要がある。しかしながら、イニシャルパターンに切り替えると、画像データをスコープ先端部からの画像データ送信が中断されることになる。このような事態が内視鏡術中に発生し、再同期、画像表示復元に時間が掛かると、内視鏡作業に悪影響を与える。特に、ワード単位の同期クロックを再生するのには時間がかかってしまう。

## 【0012】

したがって、簡素な回路構成によって、同期ずれなく安定して画素データをスコープ先端部からプロセッサ側へ高速にシリアル伝送し、また同期ずれが生じても速やかに再同期できることが求められる。

## 【課題を解決するための手段】

## 【0013】

本発明の内視鏡装置は、スコープ先端部に設けられた撮像素子と、スコープ先端部に設けられ、撮像素子から読み出される画素信号をデジタルシリアル化した画素データに対し、プランキング期間に同期検出用プランキングデータを埋め込み、また、所定のデータ幅に従って同期データを埋め込んでシリアルデータを出力する送信部と、スコープ基端側もしくは内視鏡プロセッサに設けられており、受信したシリアルデータにおける画素データを抽出する受信部とを備え、受信部が、データ幅に同期データのビット数を加えたセグメントデータ幅に従い、プランキング期間のシリアルデータを区切り、データ区切り範囲を所定ビットずつシフトさせた複数の同期検出用データを生成し、そして、複数の同期検出用データの中から、プランキングデータに相当する同期検出用データを選択する。例えば受信部が、複数の同期検出データをパラレルデータとして生成する

## 【0014】

送信部は、ビットデータ「1」のビット列およびビットデータ「0」のビット列を交互に配置させた同期検出用プランキングデータを、プランキング期間に埋め込むことが可能である。あるいは、送信部は、ビットデータ「1」ビットデータ「0」が交互に繰り返される同期検出用プランキングデータを、プランキング期間に埋め込むことが可能である。受信部は、映像信号規格に従ってプランキング期間に付加されている規格コードを検出することによって、プランキング期間を検出してよい。

## 【0015】

受信部は、同期検出用データの選択後、受信部において同期ずれが生じているか否かを検出し、同期ずれが生じている場合、同期検出用データを再び選択することが可能である。

## 【発明の効果】

## 【0016】

このように本発明によれば、内視鏡装置において、同期ずれの影響なく画素データを高速シリアル伝送することができる。

## 【画面の簡単な説明】

## 【0017】

【図1】第1の実施形態である電子内視鏡装置のブロック図である。

【図2】コープ先端側の撮像ユニットと、プロセッサ接続側の受信部の詳細なブロック図である。

【図3】送信部の一部構成を示す論理回路図である。

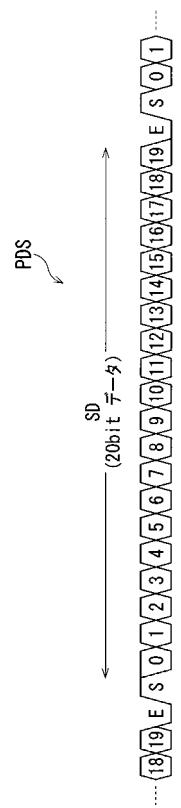

【図4】送信されるシリアルデータをワード単位で示した図である。

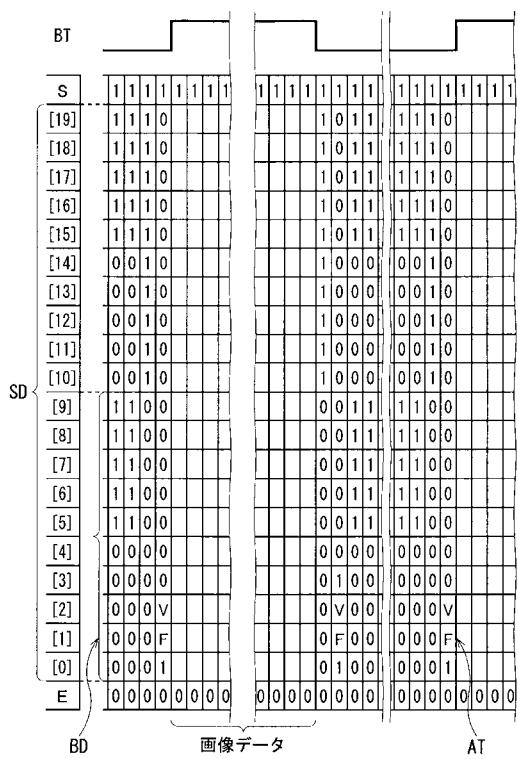

【図5】送信されるシリアルデータを1フレーム/フィールド単位に示した図である。

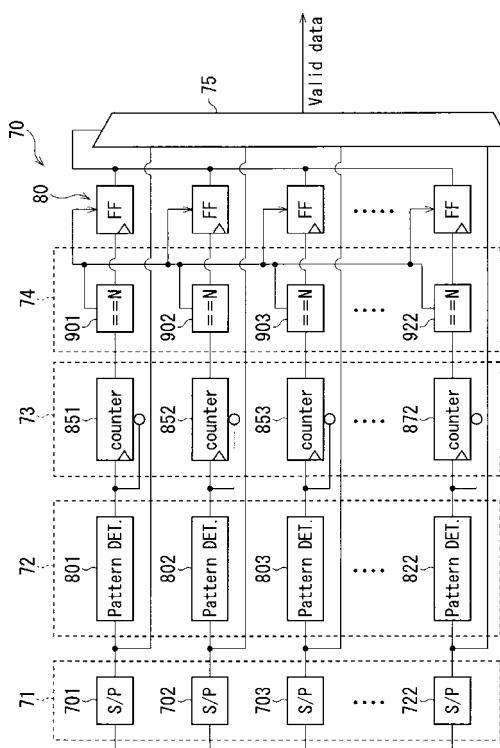

【図6】図4に示した受信回路の詳細なブロック図である。

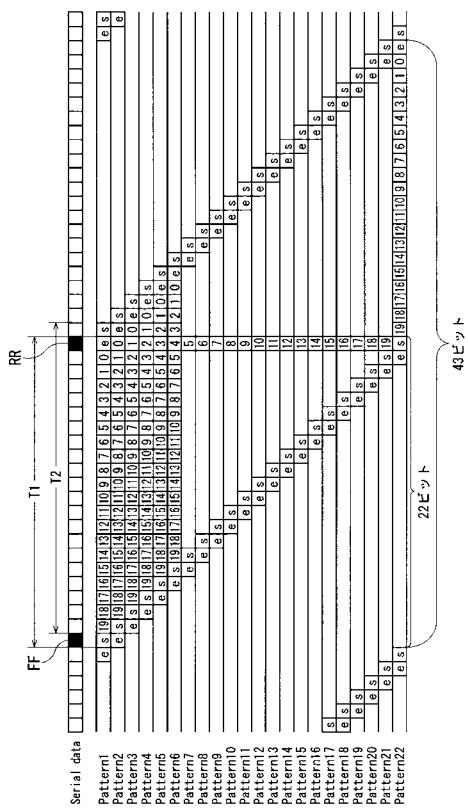

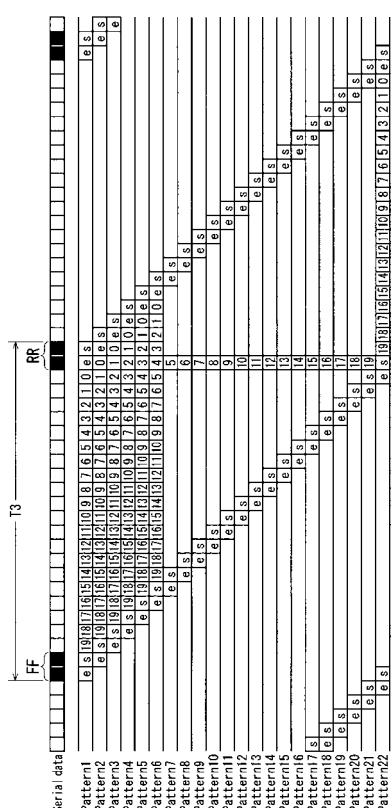

【図7】同期判別用に生成される複数の同期検出用データを示した図である。

10

20

30

40

50

【図8】同期判別用に生成される複数の同期検出用データを示した図である。

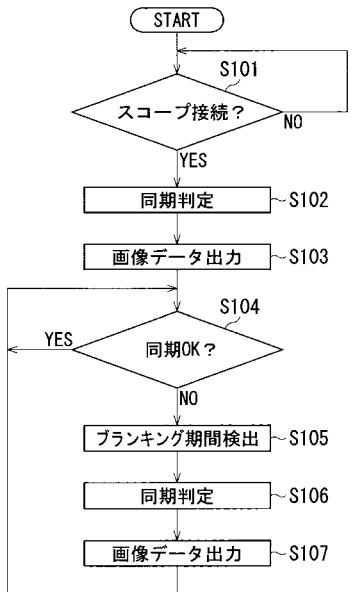

【図9】画素データ再同期処理のフローを示した図である。

【発明を実施するための形態】

【0018】

以下では、図面を参照して本実施形態である電子内視鏡装置について説明する。

【0019】

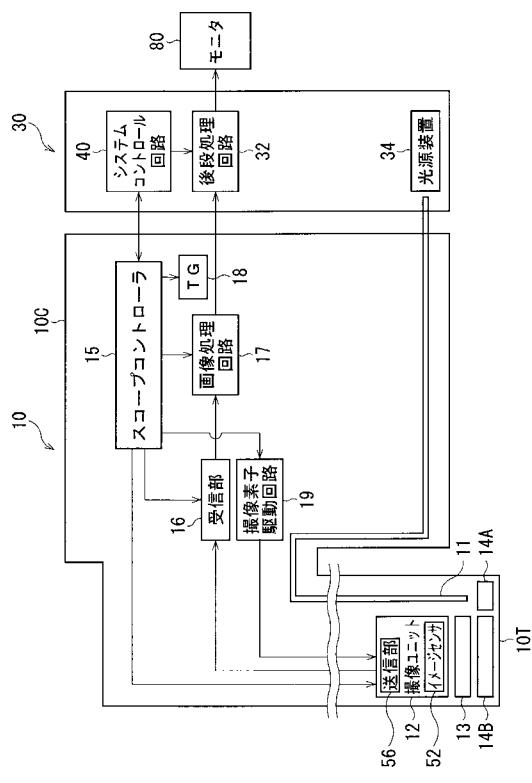

図1は、本実施形態である電子内視鏡装置のブロック図である。

【0020】

電子内視鏡装置は、その挿入部分が体内へ挿入されるビデオスコープ10と、プロセッサ30とを備え、ビデオスコープ10はプロセッサ30に着脱自在に接続される。プロセッサ30には、モニタ80が接続されている。10

【0021】

プロセッサ30は、放電ランプなどで構成される光源装置34を備える。光源装置34から放射される照明光は、集光レンズ(図示せず)を介して、ビデオスコープ10内に設けられたライトガイド11に入射する。ライトガイド11に入射した光は、ライトガイド11内部を通ってスコープ先端部10Tから射出し、配光レンズ14Aを介して被写体(観察対象)に照射される。

【0022】

被写体に反射した照明光は、スコープ先端部に設けられたカバーガラス14B、対物レンズ13通り、これによって、対物レンズ13後方に位置する撮像ユニット12のイメージセンサ52に被写体像が形成される。20

【0023】

イメージセンサ52は、X-Yアドレス型撮像素子であり、ここではCMOSセンサによって構成されている。イメージセンサ52で生じる1フィールドもしくは1フレーム分の画像信号は、撮像素子駆動回路19によって所定の読み出し時間間隔(例えば、1/60秒もしくは1/30秒間隔)に従い読み出される。イメージセンサ52には、C<sub>y</sub>、Y<sub>e</sub>、G、M<sub>g</sub>、あるいはR、G、Bなどの複数の色要素を配列させた色フィルタが配設されており、カラー撮像方式として同時单板式が適用されている。

【0024】

イメージセンサ52から読み出された画素信号は、デジタル化された後にシリアル信号に変換され、シリアルデータが、送信部56からビデオスコープ10の基端側(プロセッサ接続側)のコネクタ部10Cへ向けて送信される。30

【0025】

コネクタ部10Cには、スコープコントローラ15、受信部16、画像処理回路17、タイミングジェネレータ18、撮像素子駆動回路19などが設けられている。CPU、RAM、ROMなどを含むスコープコントローラ15は、コネクタ部10C内の各回路、そしてスコープ先端側の撮像ユニット12へ制御信号を送信し、スコープ動作全体を制御する。スコープ動作制御プログラムは、ROMに格納されている。

【0026】

受信部16では、受信したシリアルデータをパラレルデータに変換するとともに、シリアルデータから画素データを取り出し、コネクタ部10Cの同期タイミングで再同期する。画像処理回路17では、送られてきたデジタル画素信号に対してホワイトバランス処理、ガンマ補正処理などの信号処理が施される。これにより、カラーデジタル画像信号が生成される。カラーデジタル画像信号は、プロセッサ30の後段処理回路32へ送られる。なお、プロセッサ30側に受信部を設け、画像処理するように構成してもよい。40

【0027】

後段処理回路32では、輪郭強調などの画像処理が施される。そして、後段処理回路32から出力された画像信号が映像信号としてモニタ80に出力されることにより、観察画像が動画像としてモニタ80に表示される。

【0028】

10

20

30

40

50

C P U、R O M、R A Mなどを含むシステムコントロール回路40は、光源装置34などへ制御信号を出力し、プロセッサ30全体の動作を制御する。プロセッサ制御に関するプログラムは、R O Mにあらかじめ格納されている。また、システムコントロール回路40は、スコープコントローラ15との間で相互通信可能である。

#### 【0029】

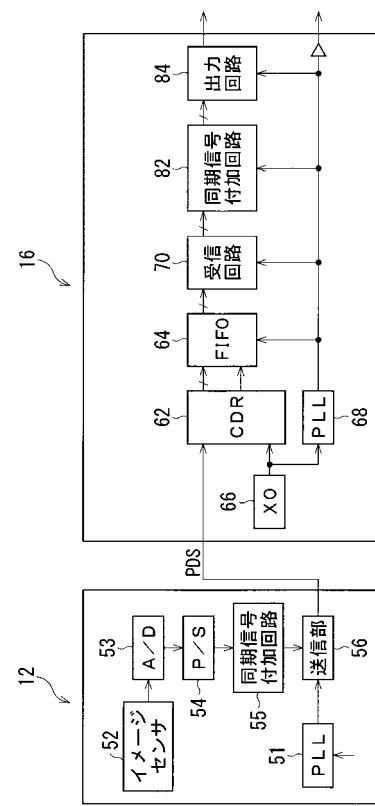

次に、図2～5を用いて、ビデオスコープの先端側に設けられた送信部、プロセッサ側に設けられた受信部の構成を説明する。

#### 【0030】

図2は、スコープ先端側の撮像ユニットと、プロセッサ接続側の受信部の詳細なブロック図である。図3は、送信部の一部構成を示す論理回路図である。10

#### 【0031】

撮像ユニット12は、C M O S型のイメージセンサ52、A / D変換器53、パラレル/シリアル変換器54、同期信号付加回路55、送信部56を備え、1つのデバイスとして構成される。P L L回路51は、位相検出器、L P F、V O C、分周器を備えており、所定の周波数でクロック信号を出力可能である。P L L回路51は、受信部16に設けられたP L L回路68から出力される基準クロック信号に基づき、所定周波数のクロック信号を撮像ユニット12へ出力する。

#### 【0032】

イメージセンサ52から読み出された1フィールド/フレーム分のアナログ画素信号は、A / D変換器53によって所定ビット数のデジタルパラレル画素信号に変換される。そして、デジタルパラレル画素信号は、パラレル/シリアル変換器54によってデジタルシリアル信号に変換され、同期信号付加回路55において映像規格関連の同期信号が付加される。20

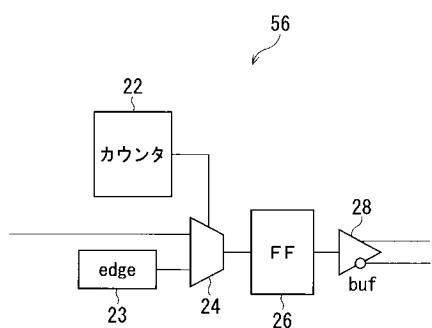

#### 【0033】

図3に示すように、送信部56は、カウンタ22、エッジ出力部23、セレクタ24、フリップフロップ26、バッファ回路28を備える。送信部56では、入力された一連のデジタルシリアル画素データの間に、所定のデータ幅(ビット数)の間隔で同期用のクロックデータ(以下、同期クロックという)E Sを埋め込む。ここでは、20ビット間隔で同期クロックE Sを埋め込む。

#### 【0034】

同期クロックE Sは、データ値「1」であるスタートビット(以下、同期データE DのS信号という)と、データ値「0」であるエンドビット(以下、同期データE DのE信号という)から構成され、周期が一定となるS信号、E信号の遷移エッジを検出することによって、受信側で画素データ抽出が可能となる。30

#### 【0035】

同期クロックE Sは、エッジを形成するデータによって構成されるデータであり、ここでは2ビットデータ「01」で構成される。シリアル画素データは、同期クロックE Sによって20ビットずつに区分され、これによりワード境界が規定される。同期クロックE Sの埋め込みは、カウンタ22によるビットカウントおよびセレクタ24による出力選択動作によって行われる。

#### 【0036】

具体的には、伝送されるシリアル画素データを20ビット分カウントする度に、エッジ出力部23から同期クロックE Sを出力してビットデータ「01」を挿入し、エンベディットクロックのシリアルデータP D Sを生成する。シリアルデータP D Sは、高速の伝送レート(例えば600M b p s)で伝送される。

#### 【0037】

一方、シリアルデータP D Sを受信する受信部16は、C D R(Clock Data Recovery)回路62、F I F O 64、受信回路70、同期信号付加回路82、出力回路84を備え、各回路は、水晶発振器66と接続されたP L L回路68から出力されるクロック信号に従って動作する。C D R回路62では、シリアルデータP D Sの各ビットデータに対する40

同期再生が行われる。

【0038】

CDR回路62から出力されたシリアルデータPDSは、 FIFO64を介して受信回路70へ送られる。受信回路70では、シリアルデータPDSがパラレルデータに変換されるとともに、シリアルデータPDSの中で20ビットから成るパラレル画素データの抽出処理が実行される。

【0039】

同期信号付加回路82では、抽出されたパラレル画素データに対して同期信号付加回路82において再同期されるとともに、同期信号が付加される。これによって、デジタル画像信号が出力回路84を経由して画像処理回路17に出力される。

10

【0040】

図4は、送信される1区画分のシリアルデータを示した図である。図5は、送信される1フレーム／フィールド分のシリアルデータを示した図である。ただし、図5では、1区画ずつ分けたパラレルデータ形式でシリアルデータを列表記している。

【0041】

上述したように、シリアルデータPDSは、20ビットの画素データ（ここでは、0～19番の番号を付けている）を1ブロックデータとし、その前後にスタートビット／エンドビット（S/E）を付けたデータ配列構造となっている。データ値「1」である同期データEDのS信号は、データ配列順に沿って20ビット画素データの前端に隣接する。一方、データ値「0」である同期データEDのE信号は、データ後端に隣接している。

20

【0042】

図5に示すように、シリアルデータPDSには、1フレーム／フィールド分の画像に相当する画素データと、プランキング期間BTにおける画素データが含まれてあり、プランキング期間BTの一部には、「1」のビット列（5ビット）と「0」のビット列（5ビット）とを合わせたシリアルデータBDを並べて埋め込んでいる。シリアルデータBDは、撮像ユニット12の同期信号付加回路55、あるいは送信部56において埋め込まれる。また、プランキング期間BTには、ITU-BT656などの映像信号規格に従ったAVコードATが挿入されている。

【0043】

シリアルデータPDSが送信部56から受信部16へ出力されると、受信部16では、シリアルデータPDSの中から同期データEDを検出し、シリアル画素データを抽出する必要がある。すなわち、1区画分の画素データSDの境界を、シリアルデータPDSの中で判別しなければならない。

30

【0044】

本実施形態では、S信号、E信号を含めた22ビットのビットデータ（同期検出用データ）を複数作成し、ビットデータの前端、後端に同期クロックESのE信号、S信号がそれぞれ存在するビットデータを、画素データ抽出対象のビットデータと判断する。以下、具体的に説明する。

【0045】

図6は、図2に示した受信回路の詳細なブロック図である。図7、図8は、同期判別用に生成される複数の同期検出用データを示した図である。ただし、図7、図8では、E信号、S信号を英小文字e、sで表している。

40

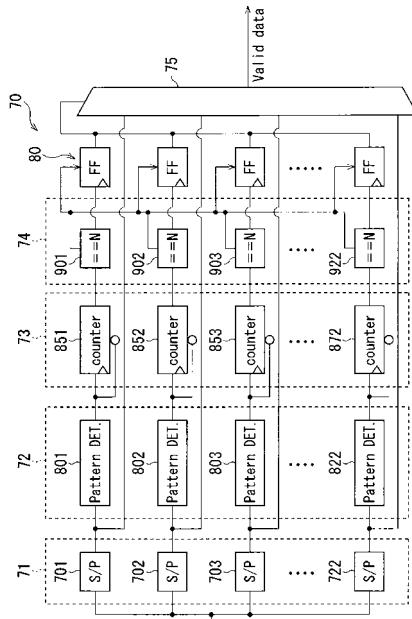

【0046】

受信回路70は、シリアル／パラレル変換部71、同期判別部72、カウンタ73、閾値判別部74、セレクタ75を備えている。シリアル／パラレル変換部71、同期判別部72、カウンタ73、閾値判別部74は、それぞれ、22個のサブシリアル／パラレル変換回路701～722、サブ同期判別器801～822、サブカウンタ851～872、サブ閾値判別回路901～922から構成される。サブ同期判別器801～822は、例えば、FPGAなどによって構成される。

【0047】

50

シリアル／パラレル変換部 7 1 では、あらかじめ定められたデータ幅（以下、セグメントデータ幅という）で FIFO 6 4 から送られてくるシリアルデータを区切り、パラレルデータ変換処理が実行される。このとき、サブシリアル／パラレル変換回路 7 0 1 ~ 7 2 2 では、シリアルデータの区切りを 1 ビットずつ順にシフトさせた上でパラレル変換処理が実行される。

#### 【0048】

図 7 には、サブシリアル／パラレル変換回路 7 0 1 ~ 7 2 2 からサブ同期判別器 8 0 1 ~ 8 2 2 に送られるパラレルデータが図示されており、各同期判定器におけるシリアルデータの区分け範囲がわかる。セグメントデータ幅は、データバス幅などに対応して定めることが可能である。ここでは、シリアル画素データの 2 0 ビットと、同期クロック（データ）ES の 2 ビットとを合わせた 2 2 ビットのデータ幅に定められている。10

#### 【0049】

サブ同期判別器 8 0 1 とサブ同期判別器 8 0 2 とを比較すると、サブ同期判別器 8 0 1 のデータ区画 T 1 に対し、サブ同期判別器 8 0 2 のデータ区画 T 2 は 1 ビットずれている。同様に、サブ同期判定器 8 0 3 ~ 8 2 2 において、順にデータ区画が 1 ビットずれている。

#### 【0050】

ところで、受信回路 7 0 では、送信部 5 6 側の同期クロック ES の挿入タイミングを知らされていないため、送られてくるシリアルデータの同期クロック ES の位置がどこに存在するか確定できない。しかしながら、あるタイミングで 4 3 ビットから成るデータを切り出し、そのデータから、データパターンの区切り範囲を 1 ビットずつ順次シフトさせた 2 2 通りのデータパターンを作成すれば、いずれか 1 つのデータ両端には、S 信号と E 信号がそれぞれ位置する。20

#### 【0051】

すなわち、同期データ ED の S 信号、E 信号がデータ両端にそれぞれ位置するパラレルデータが、サブ同期判別器 8 0 1 ~ 8 2 2 のいずれかに存在し、そのタイミングのパラレルデータを選択することによって、画素データを再同期、出力させることができる。例えば、シリアルデータのビット位置 FF、RR にそれぞれ S 信号、E 信号が位置する場合、サブ同期判別器 8 0 1 のシリアル画素データを再同期対象の画素データとして抽出すればよい。30

#### 【0052】

同期データ ED がデータ前端、後端に位置するか否かの判断は、データ前端、後端のデータ値が、それぞれ「1」、「0」であるか否かを判断すればよい。しかしながら、画素データがデータ両端に位置している場合であっても、すなわち同期データ両端のビットデータ値が「1」、「0」である可能性もあり、一度の判定だけで同期データ ED であると判定することはできない。

#### 【0053】

一方、サブ同期判別器 8 0 1 ~ 8 2 2 には、セグメントデータ幅に応じてパラレルデータが 2 2 ビットごと順次送られてくる。それらのパラレルデータも、シリアルデータに対する区分け範囲が 1 ビットずつずれている。したがって、サブ同期判別器 8 0 1 ~ 8 2 2 の各々が、同期データ ED の判定を繰り返し行い、データ両端のデータ値が同期データ ED のデータ値と常に同一であれば、データ両端に同期データ ED が位置しているパラレルデータとみなすことができる。40

#### 【0054】

ここでは、サブ同期判別器 8 0 1 ~ 8 2 2 各々が、送られてくるパラレルデータのデータ両端が同期データ ED に対応したデータ値であるか否かを、2 2 ビットのパラレルデータ変換の度に判断し、一致する場合の回数をカウントする。そして、サブ閾値判別回路 9 0 1 ~ 9 2 2 は、カウント数が基準カウント数を超えているか否かを判断する。

#### 【0055】

基準カウント数は、例えば、2 2 ビットのパラレルデータに合わせて 2 2 回に設定する

10

20

30

40

50

ことも可能であり、あるいはその半分の 11 ~ 22 回の範囲、あるいは半分の 11 回以下にすることも可能である。内視鏡システムの構成やシリアルデータの伝送特性などに応じてあらかじめ基準カウント数を調整しながらシリアル画素データの抽出程度を実験的に確認し、好みの基準カウント数を定めればよい。

#### 【0056】

セレクタ 75 は、基準カウント数を超えたパラレルデータのみ出力する。これによって同期データ E D の S 信号、E 信号をそれぞれデータ前端、後端にもつシリアルデータが同期信号付加回路 82 (図 2) へ送信される。その結果、同期ずれなく画素データが再同期されて出力される。

#### 【0057】

なお、データ両端の一方が S 信号、他方が E 信号であるか否かを判別する代わりに、データ前端部分、後端部分 2 ビットにおいて、同期データ E D が存在するか否かを判別するようにしてもよい。この場合、所定のタイミングで 45 ビットのデータを区切り、データ両端が 1 ビットずつ順次シフトしている 22 通りのデータパターンが作成される。図 8 には、そのように作成された一連のデータパターンにおいて、24 ビットのパラレルデータの区切り範囲 T3 を示している。この場合、データ両端の 2 ビットが同期クロック E S と同じデータ値をもつか否か、すなわち、データ値「01」であるか否かを判断する。

10

#### 【0058】

以上のように、内視鏡装置の使用開始時、すなわち、プロセッサが電源 ON となってビデオスコープ 10 がプロセッサ 30 に接続される、あるいはビデオスコープ 10 がプロセッサ 30 に接続されてからプロセッサ 30 の電源が ON 状態になると、シリアルデータが撮像ユニット 12 から受信部 16 に送信され、シリアルデータの中から画素データが抽出され、受信部 16 において再同期された画素データに基づく画像データが生成される。

20

#### 【0059】

しかしながら、電気メス使用といった内視鏡作業に起因してノイズが発生すると、受信部 16 において同期が外れる恐れがある。その場合、同期判定によって再同期させて画素データを再び抽出し、同期ずれを解消させなければならない。

#### 【0060】

画素データの再抽出を行う場合、同期クロック E S を用いるのではなく、ブランкиング期間に埋め込まれた同期検出用のブランкиングデータに基づいて同期判定を行う。すなわち、同期判別部 72 において、ブランкиング期間のシリアルデータに含まれる A V コード AT (図 5 参照) を検出し、これをトリガーとして同期判定を行う。

30

#### 【0061】

サブ同期判別器 801 ~ 822 は、A V コード検出によってブランкиング期間を検出した後、ブランкиング期間 BT のシリアルデータを対象に同期判定を行う。具体的には、22 ビットの同期検出用ブランкиングデータと同一であるか否か、すなわち、2 つ並んだシリアルデータ BD を間に挟んでデータ両端に E 信号、S 信号が位置するデータ配列と等しいか否かをサブ同期判別器 801 ~ 822 において判断する。

#### 【0062】

なお、同期検出用ブランкиングデータの情報は、スコープコントローラ 15 から受信部 16 に送られており、これに基づいて同一性を判断する。また、スコープコントローラ 15 の制御によって、サブ同期判定器 801 ~ 802 の動作を、同期データの位置判定からブランкиングデータとの同一性判断に切り替える。なお、また、最初の画素データ抽出処理用の受信回路と、同期ずれ後の画素データ再抽出用受信回路とを、別々に設ける構成にしてもよい。

40

#### 【0063】

そして、同期検出用ブランкиングデータと同一のデータ配列となるパラレルデータの場合、その回数をカウントする。そして、カウント数が基準閾値を超えた場合、そのパラレルデータがセレクタ 75 を経由して出力される。この場合、基準閾値は 2 である。ただし、カウントせずに 1 回の同期判定だけ行うことも可能である。

50

**【 0 0 6 4 】**

このように同期判定することにより、同期ずれなく画素データが再同期して出力される。なお、ここでは、ランキング期間の所定の 22 ビットデータを対象にして同期判定を行っているが、ランキング期間において他のデータサイズ、データ配列を対象にして同一性判断を行うことも可能であり、例えば、同期データ E D を除くデータ配列を対象にすることも可能であり、あるいは、10 ビットデータ B T を対象に同一性を判断してもよい。

**【 0 0 6 5 】**

シリアルデータ B D のデータ配列以外も同期判定可能であり、特に、「1」と「0」が交互に連続的に繰り返されるデータに基づいて同期判断することも可能である。

10

**【 0 0 6 6 】**

図 9 は、画素データ再同期処理のフローを示した図である。

**【 0 0 6 7 】**

ビデオスコープ 10 がプロセッサ 30 に接続されると、図 7、8 を用いて説明した同期データ検出に基づいた同期判定処理が実行開始される。同期判定が終了するまでの間、すなわち、セレクタ 75 からパラレルデータが出力されない間、ブラック画面に対応した画像データを出力させ、オペレータを待機状態にする。そして、同期が確立されると、画像データ出力によって観察画像がモニタに表示される (S 1 0 1 ~ S 1 0 3)。

**【 0 0 6 8 】**

画像データが出力されると、同期ずれが生じているか否かを検出すため、パラレルデータが出力されているサブパターン判別器において、データ両端に同期データ E D が位置しているかモニタリングされる (S 1 0 4)。そして、同期データ E D と一致しないことが検出されると、ランキング期間を検出し、ランキング期間内におけるシリアルデータの配列と同一のデータ配列をもつパラレルデータを出力し、再同期させる (S 1 0 5、S 1 0 6)。

20

**【 0 0 6 9 】**

ただし、同期判定を行っている間、ブラック画面に応じた画像データを出力する代わりに、フレームメモリに記憶させた同期ずれ前の画像データを表示させようにもよい。

30

**【 0 0 7 0 】**

このように本実施形態によれば、ビデオスコープ 10 の先端部に設けられたイメージセンサ 52 から読み出される画素信号をデジタルシリアル化し、送信部 56 においては、20 ビットのシリアル画素データの間に同期データ E D として同期信号 S、同期信号 E から成る同期用クロックデータ E S を埋め込み、シリアルデータをスコープコネクタ部 10 C へ送信する。

**【 0 0 7 1 】**

一方、受信部 16 の受信回路 70 では、22 ビットのセグメントデータ幅でシリアルデータを区切り、1 ビットずつ区切り範囲を順次シフトさせた 22 個の同期検出用のパラレルデータを生成する。そして、受信回路 70 は、22 個のパラレルデータの中から、同期データ E D がデータ両端に位置するパラレルデータを選択、出力し、選択されたパラレルデータが再同期される。なお、22 ビットのセグメントデータ幅で一度にシリアルデータを区切り、それから 22 個のパラレルデータを作成する代わりに、1 ビットずつデータ潜り範囲を順次シフトさせながら、22 個のパラレルデータを異なるタイミングで作成してもよい。

40

**【 0 0 7 2 】**

8 b / 10 b 伝送方式のような変換テーブルを用いることなく、埋め込んだ同期クロックを正確に検知し、シリアル画素データを取り出すことができる。特に、スコープ先端部における回路構成としてはセレクタ等を設けるだけでよいため、スコープ先端部の回路構成が簡素化できる。また、受信部において、ワードアライナなどのワード境界を検知する回路を設ける必要がない。

50

## 【0073】

一方、受信部における同期判定は、PLL回路を利用した構成とは相違するため、位相ロックのためのテスト用パターンを受信部へ向けて送信する必要もなく、さらに、シリアルデータと並走して同期クロックを送る必要もない。また、再同期させた後にノイズなどの影響で同期ずれが生じても、テスト用パターンの送信など、同期修正のための切り替え処理などをする必要がなく、瞬時に画像データ出力を回復することが可能となっている。

## 【0074】

また、同期データ一致の回数をカウントし、最も早く閾値を超えるパラレルデータを選択するため、確実に同期データEDが両端に位置するパラレルデータを画素データとして抽出することができる。

10

## 【0075】

複数のパラレルデータを同期検出用データとして生成し、その中から1つのパラレルデータを選択する回路構成を採用することにより、簡易な回路構成でデータ処理速度を落とすことなく画像信号処理を行うことができる。

## 【0076】

また、本実施形態によれば、画素データを抽出後にノイズなどの影響で同期ずれが生じた場合、ブランкиング期間を検出し、22ビットのセグメントデータ幅でシリアルデータを区切りながら、1ビットずつ区切り範囲を順次シフトさせて22個の同期検出用のパラレルデータを生成する。そして、ブランкиング期間に埋め込まれた同期検出用データとデータ配列が等しいパラレルデータを選択し、出力する。

20

## 【0077】

シリアル画素データのデータ配列は、観察画像の輝度、色相に依存するが、内視鏡観察画像の場合、偏った輝度レベル、色合いの画像エリアによって占められており、シリアル画素データの配列に偏りが生じることが多い。

## 【0078】

しかしながら、上述したように、ブランкиング期間のシリアル画素データは、「1」のビット列と「0」のビット列を並べたシリアルデータBDに基づいた構成されている。そのため、DCバランスが安定し、シリアル画素データを対象に同期判定する場合に比べて、効果的に同期ずれを瞬時に解消することができる。特に、ビットデータ「1」ビットデータ「0」が交互に連続して繰り返されるデータを埋め込む場合、DCバランスの安定性は顕著であり、極めて有効である。また、再同期を行った後の同期判定であって観察画像を表示している状態のため、ブランкиング期間を検出しやすい。

30

## 【0079】

なお、1ビットずつ順次シフトさせるだけでなく、所定ビット数ずつ区切りをシフトさせて複数のデータを生成するようにしてもよい。また、プロセッサ接続時と途中で同期ずれが生じた場合いずれにおいても、同期データを用いて再同期してもよく、あるいは、ブランкиング期間のデータを用いて再同期させてもよい。

## 【符号の説明】

## 【0080】

- |     |             |    |

|-----|-------------|----|

| 1 0 | ビデオスコープ     | 40 |

| 1 2 | 撮像ユニット      |    |

| 1 6 | 受信部         |    |

| 3 0 | プロセッサ       |    |

| 5 6 | 送信部         |    |

| 7 0 | 受信回路        |    |

| E   | 同期信号（同期データ） |    |

| S   | 同期信号（同期データ） |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

F ターム(参考) 4C161 AA00 BB00 CC06 DD00 FF45 JJ19 NN03 SS03 UU09

5C054 CC07 EA03 EC03 HA12

5C122 DA26 EA68 GC86 HA34 HB01 HB02