(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6012230号

(P6012230)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

(51) Int.Cl.

H04N 7/01 (2006.01)

G06T 7/60 (2006.01)

F 1

H04N 7/01

G06T 7/60G

250Z

請求項の数 13 (全 27 頁)

(21) 出願番号 特願2012-87468 (P2012-87468)

(22) 出願日 平成24年4月6日 (2012.4.6)

(65) 公開番号 特開2013-219490 (P2013-219490A)

(43) 公開日 平成25年10月24日 (2013.10.24)

審査請求日 平成27年4月6日 (2015.4.6)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100085006

弁理士 世良 和信

(74) 代理人 100100549

弁理士 川口 嘉之

(74) 代理人 100106622

弁理士 和久田 純一

(74) 代理人 100131532

弁理士 坂井 浩一郎

(74) 代理人 100125357

弁理士 中村 剛

(74) 代理人 100131392

弁理士 丹羽 武司

最終頁に続く

(54) 【発明の名称】エッジ方向判定装置、エッジ方向判定装置の制御方法、及び、画像処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画像の注目点におけるエッジの方向を判定するエッジ方向判定装置であって、

エッジの方向の候補である複数の方向のそれぞれについて、注目点を通るその方向の直

線上に、同じサイズの領域である n 個 (n は 2 以上の整数) のブロックを設定する設定手

段と、

前記複数の方向のそれぞれについて、前記設定手段で設定された n 個のブロック間の画

像の類似度を算出し、類似度が最も高い方向を、前記注目点におけるエッジの方向として

判定する判定手段と、

を有し、

10

前記設定手段は、エッジの方向の候補である前記方向毎に、

その方向に対して設定する n 個のブロックのうちの少なくとも 1 つのブロックについ

て、そのブロックの設定位置である前記直線上の位置における、所定方向の位置の変化に

対する画素値の変化の勾配を算出し、

勾配が大きいときよりも、勾配が小さいときのほうが、前記所定方向の長さが長くな

るように、前記設定する n 個のブロックのサイズを制御する

ことを特徴とするエッジ方向判定装置。

## 【請求項 2】

前記設定手段は、勾配が所定値以上の場合に、前記設定する n 個のブロックのサイズを

第 1 のサイズとし、勾配が前記所定値未満の場合に、前記設定する n 個のブロックのサイ

20

ズを前記第1のサイズよりも大きい第2のサイズとする

ことを特徴とする請求項1に記載のエッジ方向判定装置。

**【請求項3】**

前記設定手段は、

前記設定するn個のブロックのうちの複数のブロックのそれぞれについて勾配を算出し、

前記複数のブロックについて算出した複数の勾配の代表値に応じて、前記設定するn個のブロックのサイズを制御する

ことを特徴とする請求項1または2に記載のエッジ方向判定装置。

**【請求項4】**

前記代表値は、前記複数の勾配の最大値である

ことを特徴とする請求項3に記載のエッジ方向判定装置。

**【請求項5】**

前記勾配は、ブロックの設定位置における画素値と、当該設定位置から前記所定方向に所定距離離れた位置における画素値との差、及び、ブロックの設定位置における画素値と、当該設定位置から前記所定方向の反対方向に所定距離離れた位置における画素値との差のうち、大きい方の値である

ことを特徴とする請求項1～4のいずれか1項に記載のエッジ方向判定装置。

**【請求項6】**

前記ブロックは、前記所定方向に沿った長辺を有する矩形状の領域である

ことを特徴とする請求項1～5のいずれか1項に記載のエッジ方向判定装置。

**【請求項7】**

インターレース画像信号を補間にによりプログレッシブ画像信号に変換する画像処理装置であって、

請求項1～6のいずれか1項に記載のエッジ方向判定装置と、

前記エッジ方向判定装置で判定されたエッジの方向に基づいて、フィールド内補間にによる補間画素を生成する補間画素生成手段と、

を有することを特徴とする画像処理装置。

**【請求項8】**

画像の注目点におけるエッジの方向を判定するエッジ方向判定装置の制御方法であって

、

エッジの方向の候補である複数の方向のそれぞれについて、注目点を通るその方向の直線上に、同じサイズの領域であるn個(nは2以上の整数)のブロックを設定する設定ステップと、

前記複数の方向のそれぞれについて、前記設定ステップで設定されたn個のブロック間の画像の類似度を算出し、類似度が最も高い方向を、前記注目点におけるエッジの方向として判定する判定ステップと、

を有し、

前記設定ステップでは、エッジの方向の候補である前記方向毎に、

その方向に対して設定するn個のブロックのうちの少なくとも1つのブロックについて、そのブロックの設定位置である前記直線上の位置における、所定方向の位置の変化に対する画素値の変化の勾配が算出され、

勾配が大きいときよりも、勾配が小さいときのほうが、前記所定方向の長さが長くなるように、前記設定するn個のブロックのサイズが制御される

ことを特徴とするエッジ方向判定装置の制御方法。

**【請求項9】**

前記設定ステップでは、勾配が所定値以上の場合に、前記設定するn個のブロックのサイズが第1のサイズとされ、勾配が前記所定値未満の場合に、前記設定するn個のブロックのサイズが前記第1のサイズよりも大きい第2のサイズとされる

ことを特徴とする請求項8に記載のエッジ方向判定装置の制御方法。

10

20

30

40

50

**【請求項 10】**

前記設定ステップでは、

前記設定する n 個のブロックのうちの複数のブロックのそれぞれについて勾配が算出され、

前記複数のブロックについて算出した複数の勾配の代表値に応じて、前記設定する n 個のブロックのサイズが制御される

ことを特徴とする請求項 8 または 9 に記載のエッジ方向判定装置の制御方法。

**【請求項 11】**

前記代表値は、前記複数の勾配の最大値である

ことを特徴とする請求項 10 に記載のエッジ方向判定装置の制御方法。

10

**【請求項 12】**

前記勾配は、ブロックの設定位置における画素値と、当該設定位置から前記所定方向に所定距離離れた位置における画素値との差、及び、ブロックの設定位置における画素値と、当該設定位置から前記所定方向の反対方向に所定距離離れた位置における画素値との差のうち、大きい方の値である

ことを特徴とする請求項 8 ~ 11 のいずれか 1 項に記載のエッジ方向判定装置の制御方法。

。

**【請求項 13】**

前記ブロックは、前記所定方向に沿った長辺を有する矩形状の領域である

ことを特徴とする請求項 8 ~ 12 のいずれか 1 項に記載のエッジ方向判定装置の制御方法

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、エッジ方向判定装置、エッジ方向判定装置の制御方法、及び、画像処理装置に関する。

**【背景技術】****【0002】**

インターレース画像信号を補間によりプログレッシブ画像信号に変換する方法として、動き適応型 IP (インターレース - プログレッシブ) 変換と呼ばれる方法がある。これは、補間画素の生成位置での画像の動き (動き情報) を検出し、その動き情報に応じて、補間画素としてフィールド内補間画素を生成するか、フィールド間補間画素を生成するかを適応的に切り換える方法である。

30

**【0003】**

動き適応型 IP 変換では、「動きあり」と判定された位置に対して、同一フィールド内において該位置の垂直方向に隣接する画素を用いて補間画素が生成される。そのため、斜め方向のエッジ部分 (斜めエッジ部分) では、ジャギーと呼ばれるギザギザが発生することとなり、画像品位 (画質) が著しく劣化してしまう。

**【0004】**

ジャギーの発生を抑制する技術として、入力されたインターレース画像信号の画素情報からエッジの方向を判定し、エッジの方向に応じた画素を用いて補間画素を生成する方法が提案されている。

40

そのような方法は、例えば、特許文献 1 に開示されている。

具体的には、特許文献 1 には、予め決められた斜め方向のリファレンスパターンと入力画像信号とのパターンマッチングにより、エッジの方向を判定することが開示されている。また、リファレンスパターンのサイズ (ブロックサイズ) を大きくすることで、より角度の浅いエッジの方向が判定可能となることが開示されている。

**【先行技術文献】****【特許文献】****【0005】**

50

【特許文献1】特開2008-182725号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した従来の技術では、エッジの方向を精度良く判定することができず、エッジの方向の誤判定が発生してしまうことがある。例えば、ブロックサイズが大きい場合には、角度が深い斜めエッジ部分において、斜めエッジ部分以外の画像がパターンマッチングに大きな影響を与えててしまうことがある。そのため、大きなブロックサイズでのパターンマッチングによりエッジの方向を判定する構成では、角度の深いエッジの方向を精度良く判定することができない。また逆に、小さなブロックサイズでのパターンマッチングによりエッジの方向を判定する構成では、角度の浅いエッジの方向を精度良く判定することができない。エッジの方向の誤判定があると、エッジの方向の判定結果に基づく画像処理を行った際に、画質が劣化してしまう。例えば、上述したジャギー等の視覚的な妨害のある画像が生成されてしまう。

【0007】

本発明は、エッジの方向を精度良く判定することのできる技術を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の第1の態様は、

画像の注目点におけるエッジの方向を判定するエッジ方向判定装置であって、エッジの方向の候補である複数の方向のそれぞれについて、注目点を通るその方向の直線上に、同じサイズの領域であるn個（nは2以上の整数）のブロックを設定する設定手段と、

前記複数の方向のそれぞれについて、前記設定手段で設定されたn個のブロック間の画像の類似度を算出し、類似度が最も高い方向を、前記注目点におけるエッジの方向として判定する判定手段と、

を有し、

前記設定手段は、エッジの方向の候補である前記方向毎に、

その方向に対して設定するn個のブロックのうちの少なくとも1つのブロックについて、そのブロックの設定位置である前記直線上の位置における、所定方向の位置の変化に対する画素値の変化の勾配を算出し、

勾配が大きいときよりも、勾配が小さいときのほうが、前記所定方向の長さが長くなるように、前記設定するn個のブロックのサイズを制御することを特徴とする。

【0010】

本発明の第2の態様は、

インターレース画像信号を補間にによりプログレッシブ画像信号に変換する画像処理装置であって、

上記エッジ方向判定装置と、

前記エッジ方向判定装置で判定されたエッジの方向に基づいて、フィールド内補間にによる補間画素を生成する補間画素生成手段と、

を有することを特徴とする。

【0012】

本発明の第3の態様は、

画像の注目点におけるエッジの方向を判定するエッジ方向判定装置の制御方法であって、

エッジの方向の候補である複数の方向のそれぞれについて、注目点を通るその方向の直線上に、同じサイズの領域であるn個（nは2以上の整数）のブロックを設定する設定ステップと、

10

20

30

40

50

前記複数の方向のそれぞれについて、前記設定ステップで設定されたn個のブロック間の画像の類似度を算出し、類似度が最も高い方向を、前記注目点におけるエッジの方向として判定する判定ステップと、

を有し、

前記設定ステップでは、エッジの方向の候補である前記方向毎に、

その方向に対して設定するn個のブロックのうちの少なくとも1つのブロックについて、そのブロックの設定位置である前記直線上の位置における、所定方向の位置の変化に対する画素値の変化の勾配が算出され、

勾配が大きいときよりも、勾配が小さいときのほうが、前記所定方向の長さが長くなるように、前記設定するn個のブロックのサイズが制御される

ことを特徴とする。

10

### 【発明の効果】

#### 【0013】

本発明によれば、エッジの方向を精度良く判定することができる。

### 【図面の簡単な説明】

#### 【0014】

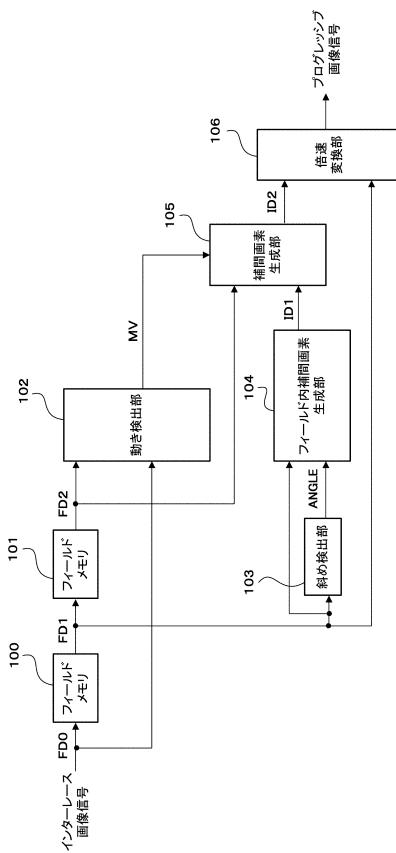

【図1】実施例1に係る画像処理装置の構成の一例を示す図

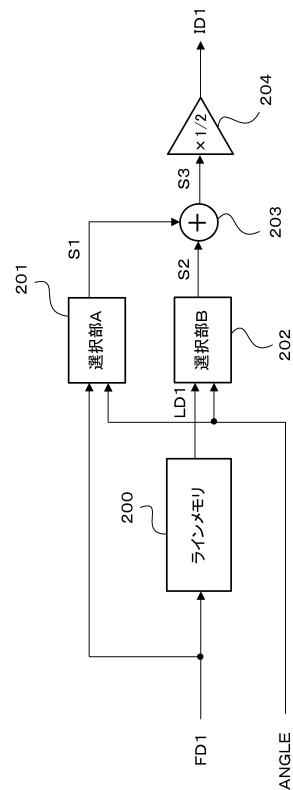

【図2】実施例1に係るフィールド内補間画素生成部の構成の一例を示す図

20

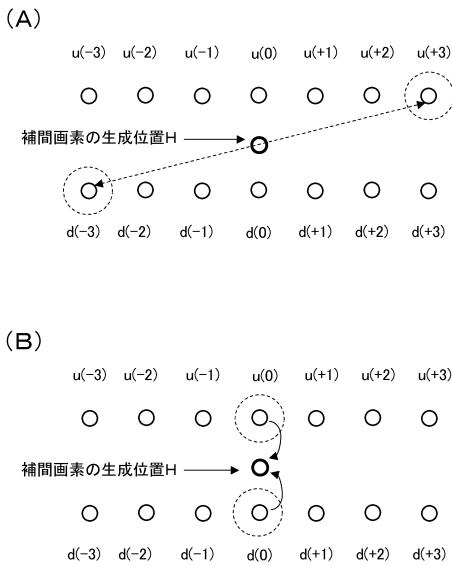

【図3】実施例1に係る角度情報に応じた画素の選択方法の一例を示す図

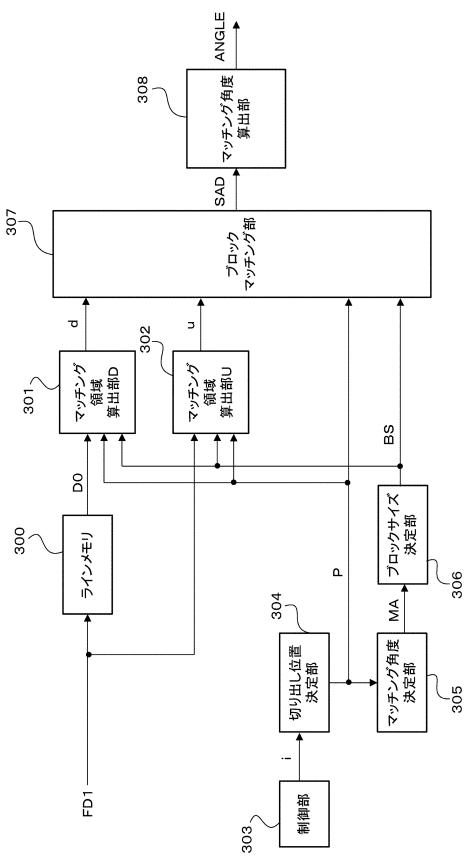

【図4】実施例1に係る斜め検出部の構成の一例を示す図

【図5】実施例1に係る斜め検出部の処理の流れの一例を示すフローチャート

【図6】実施例1に係るブロックの中心位置の一例を示す図

【図7】実施例1に係る角度とブロックサイズの対応関係の一例を示す図

【図8】実施例1に係るブロックマッチング部の処理の一例を示す図

【図9】実施例1に係るブロックマッチング部の処理の一例を示す図

【図10】実施例1に係る角度とブロックサイズの対応関係の一例を示す図

【図11】実施例1に係るSAD値算出の具体例を示す図

【図12】実施例2に係る斜め検出部の構成の一例を示す図

30

【図13】実施例2に係る斜め検出部の処理の流れの一例を示すフローチャート

【図14】実施例2に係るブロックの中心位置の一例を示す図

【図15】実施例2に係るSAD値算出の具体例を示す図

【図16】実施例3に係る斜め検出部の構成の一例を示す図

【図17】実施例3に係る勾配算出部の動作の具体例を示す図

【図18】実施例3に係るブロックサイズ補正部の動作の一例を示すフローチャート

【図19】実施例4に係るブロックマッチングの様子の一例を示す図

### 【発明を実施するための形態】

#### 【0015】

##### <実施例1>

以下、本発明の実施例1に係るエッジ方向判定装置、エッジ方向判定装置の制御方法、及び、画像処理装置について、図面を用いて説明する。本実施例では、エッジ方向判定装置を有する画像処理装置が、IP変換（具体的には動き適応型IP変換）を行う画像処理装置である場合の例について説明するが、本発明のエッジ方向判定装置（及びその制御方法）は、画像の注目点におけるエッジの方向を判定するいかなる装置にも適用することができる。IP変換は、インターレース画像信号を補間にによりプログレッシブ画像信号に変換する処理である。動き適応型IP変換は、補間画素の生成位置での画像の動き（動き情報）を検出し、その動き情報に応じて、補間画素としてフィールド内補間画素を生成するか、フィールド間補間画素を生成するかを適応的に切り換えるIP変換である。

40

#### 【0016】

図1は、本実施例に係る画像処理装置の構成を示すブロック図である。

50

図1において、フィールドメモリ100, 101はフィールド単位で装置に入力されるインターレース画像信号を蓄積し、該インターレース画像信号を1フィールド分だけ遅延させて出力する。即ち、画像処理装置にN番目のフィールド(Nフィールド)の画像信号FD0が入力された時に、フィールドメモリ100からは、N-1番目のフィールド(N-1フィールド)の画像信号FD1が出力される。フィールドメモリ101からは、N-2番目のフィールド(N-2フィールド)の画像信号FD2が出力される。本実施例では、N-1フィールドの画像信号FD1に対して補間画素が生成される。

#### 【0017】

動き検出部102は、補間画素の生成位置での画像の動きを検出する。本実施例では、動き検出部102は、Nフィールド信号FD0及びN-2フィールド信号FD2の2つのフィールドの画像信号を用いて、補間画素の生成位置での画像の動き(動き情報MV)を検出する。具体的には、動き検出部102は、画素毎に、2つのフィールド間の画素値の差分値を閾値と比較することにより、動きの有無を判定する。差分値が閾値以上の場合は、画像の動きがある(MV=1(動き))と判定され、差分値が閾値未満の場合には、画像の動きがない(MV=0(静止))と判定される。そして、この判定結果(画素毎のMVの値)が動き情報として補間画素生成部105へ出力される。なお、動きの検出方法はこれに限らない。例えば、ブロックマッチングにより動きが検出されてもよい。

#### 【0018】

斜め検出部103は、補間画素の生成位置(注目点)におけるエッジの方向を判定する(エッジ方向判定装置)。具体的には、斜め検出部103は、補間画素の生成位置がエッジ部分か否かを判定する。そして、斜め検出部103は、補間画素の生成位置がエッジ部分であると判定した場合に、該エッジの方向を表す情報をフィールド内補間画素生成部104へ出力する。本実施例では、エッジの方向を表す情報として、当該方向の水平方向に対する傾斜角度を表す角度情報ANGLEが出力される。本実施例では、角度情報ANGLEは、-15~+15の値を取り得るものとする。斜め検出部103が本実施例に係るエッジ方向判定装置に相当する。斜め検出部103の動作の詳細については、後述する。

#### 【0019】

フィールド内補間画素生成部104は、角度情報ANGLEに基づいて、フィールド内補間による補間画素(フィールド内補間画素)を生成して出力する。具体的には、フィールド内補間画素生成部104は、フィールド内補間画素の画素値ID1を算出し、出力する。フィールド内補間画素は、画像の動きのある位置に生成するのに適した補間画素であり、補間画素の生成の対象となるN-1フィールド信号FD1の画素値を用いて生成される補間画素である。

#### 【0020】

フィールド内補間画素生成部104は、例えば、図2に示すような構成を有する。

フィールド内補間画素生成部104に入力されたN-1フィールド信号FD1は、ラインメモリ200と選択部A201に入力される。

ラインメモリ200は、入力されたN-1フィールド信号FD1を1H(1水平走査期間)だけ遅延させ、当該遅延させた信号を1H遅延信号LD1として選択部B202に出力する。

選択部A201は、補間画素の生成位置毎に、N-1フィールド信号FD1(補間画素の生成位置の1つ下のラインの画像信号)から、角度情報ANGLEに応じた画素を選択し、その画素の画素値S1を出力する。

選択部B202は、補間画素の生成位置毎に、1H遅延信号LD1(補間画素の生成位置の1つ上のラインの画像信号)から、角度情報ANGLEに応じた画素を選択し、その画素の画素値S2を出力する。

#### 【0021】

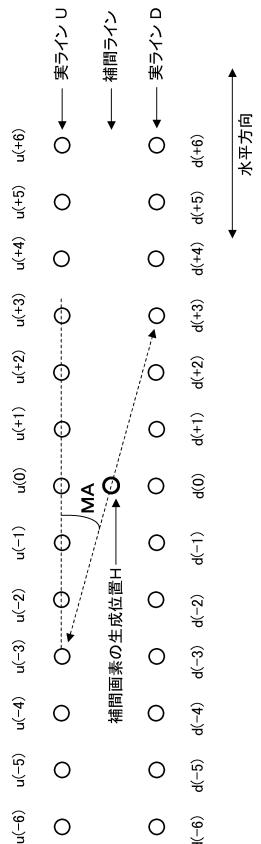

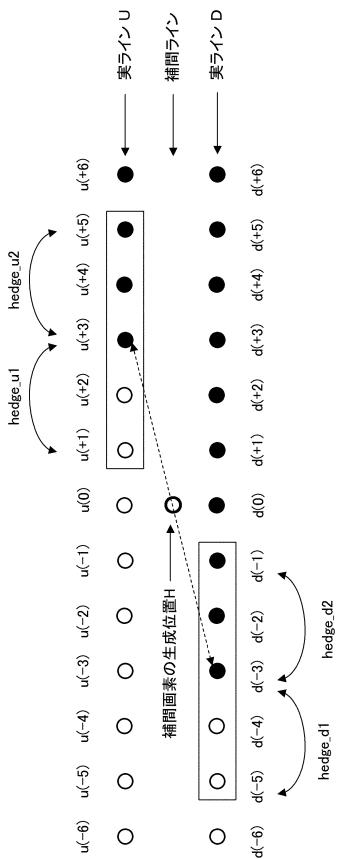

選択部A201及び選択部B202における画素の選択方法について、図3(A)を用いて説明する。

図3(A)において、画素u(x)は、補間画素の生成位置Hの1つ上のライン上の画

10

20

30

40

50

素であり、図2における1H遅延信号LD1で表される画素である。画素d(x)は、補間画素の生成位置Hの1つ下のライン上の画素であり、図2におけるN-1フィールド信号FD1で表される画素である。xは、補間画素の生成位置に対する画素u(x), d(x)の位置の水平方向のずれ量(補間画素の生成位置を基準とする画素u(x), d(x)の水平方向の位置を示す値)である。xの値が負の値である場合には、画素u(x), d(x)の水平方向の位置は、補間画素の生成位置に対して左側へ|x|画素ずれた位置となる。xの値が正の値である場合には、画素u(x), d(x)の水平方向の位置は、補間画素の生成位置に対して右側へ|x|画素ずれた位置となる。

#### 【0022】

本実施例では、斜め検出部103は、角度情報ANGLEとして、上述したxの値を出力する。また、斜め検出部103は、補間画素の生成位置がエッジ部分でない場合には、角度情報ANGLE=0を出力する。10

角度情報ANGLE=+A(Aは自然数)の場合は、選択部A201でu(+A)が選択され、選択部B202でd(-A)が選択される。図3(A)は、補間画素の生成位置Hに対する角度情報ANGLEが+3の場合の例である。この場合、選択部A201でu(+3)が選択され、選択部B202でd(-3)が選択される。また、角度情報ANGLE=0の場合には、図3(B)に示すように、選択部A201でu(0)が選択され、選択部B202でd(0)が選択される。

#### 【0023】

加算器203は、選択部A201から出力された画素値S1と選択部B202から出力された画素値S2とを足し合わせることにより画素値S3を算出し、乗算器204へ出力する。20

乗算器204は、画素値S3を1/2倍し、その結果(画素値S3を1/2倍した値)を、フィールド内補間画素の画素値ID1(フィールド内補間値)として出力する。

これにより、N-1フィールド信号FD1において、エッジ部分の補間画素の画素値として、そのエッジの方向に隣接する2画素の画素値の平均値を得ることができる。また、エッジ部分以外の位置の補間画素の画素値として、垂直方向に隣接する2画素の画素値の平均値を得ることができる。

#### 【0024】

補間画素生成部105は、補間画素の生成位置毎に、動き情報MVに応じて補間方法を切り換え、補間画素を生成する(補間画素の画素値ID2を決定する)。即ち、補間画素生成部105は、動き適応型IP変換により補間画素を生成する。具体的には、補間画素の生成位置において画像の動きがない場合(MV=0である場合)には、補間画素生成部105は、該生成位置に対し、N-2フィールド信号FD2の画素値を画素値ID2として用いて、補間画素(フィールド間補間画素)を生成する。画像の動きがある場合(MV=1である場合)には、補間画素生成部105は、該生成位置に対し、フィールド内補間値ID1を画素値ID2として用いて、補間画素(フィールド内補間画素)を生成する。そして、補間画素生成部105は、各補間画素の画素値ID2を倍速変換部106へ出力する。なお、フィールド間補間画素は、画像の動きのない位置に生成するのに適した補間画素であって、N-2フィールド信号の画素値(補間画素の生成位置と同じ位置の画素値)と同じ画素値を有する補間画素である。30

#### 【0025】

倍速変換部106は、各補間画素の画素値ID2と、N-1フィールド信号FD1とを合成してプログレッシブ画像信号(プログレッシブ画像の1フレームの画像信号)として出力する。具体的には、倍速変換部106は、N-1フィールド信号FD1と、各補間画素の画素値ID2とを、インターレース画像信号が入力される速度の2倍の速度でライン毎に交互に読み出す。これにより、N-1フィールド信号FD1のオリジナルライン(N-1フィールドのインターレース画像を構成する画素からなるライン)のデータと、画素値ID2を有する補間画素からなるライン(補間ライン)のデータとがライン毎に交互に読み出される。そして、倍速変換部106は、データを読み出す度に、読み出したデータ4050

をプログレッシブ画像信号（プログレッシブ画像の1ラインのデータ）として出力する。

#### 【0026】

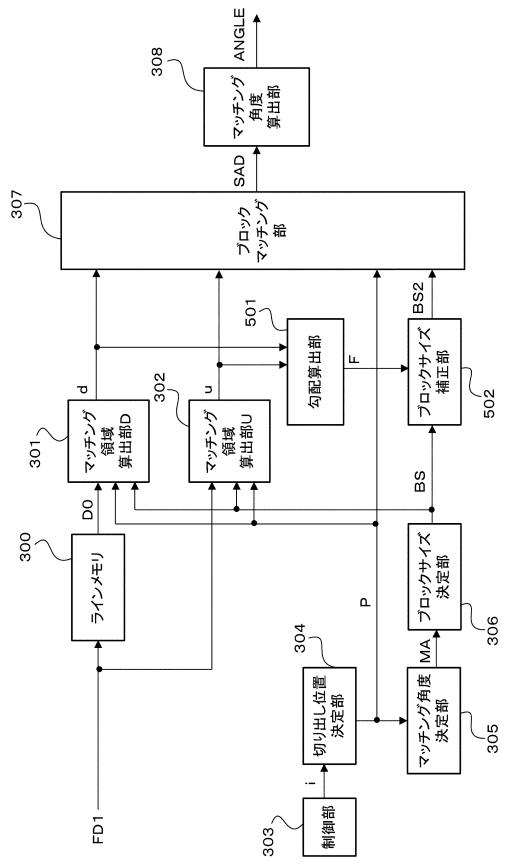

次に、斜め検出部103の構成について説明する。図4は、本実施例に係る斜め検出部103の内部構成を示すブロック図である。図4に示すように、本実施例に係る斜め検出部103は、ラインメモリ300、マッチング領域算出部D301、マッチング領域算出部U302、制御部303、切り出し位置決定部304、マッチング角度決定部305、ブロックサイズ決定部306、ブロックマッチング部307、マッチング角度算出部308などを備える。

#### 【0027】

ラインメモリ300は、入力されたN-1フィールド信号FD1を1H(1水平走査期間)だけ遅延させ、当該遅延させた信号を1H遅延信号D0として出力する。

#### 【0028】

マッチング領域算出部D301とマッチング領域算出部U302は、エッジの方向の候補である複数の方向（候補方向）のそれぞれについて、注目点を通るその方向の直線上にn個（nは2以上の整数）のブロックを設定する。n個のブロックは、同じサイズのn個の領域である。ブロックは、所定方向（本実施例では水平方向）に沿った長辺を有する矩形状の領域である。

具体的には、マッチング領域算出部D301には、1H遅延信号D0（補間画素の生成位置の1つ下のラインの画素値）が入力される。マッチング領域算出部D301は、上記n個のブロックのうちの1つとして、補間画素の生成位置の1つ下のライン上の複数の画素からなる領域を設定する。そして、マッチング領域算出部D301は、設定したブロック内の1H遅延信号D0の画素値を、ブロックマッチング部307に出力する。即ち、ブロック内の画素値として、画素d(x)の画素値が出力される。

マッチング領域算出部U302には、N-1フィールド遅延信号FD1（補間画素の生成位置の1つ上のラインの画素値）が入力される。マッチング領域算出部U302は、上記n個のブロックのうちの1つとして、補間画素の生成位置の1つ上のライン上の複数の画素からなる領域を設定する。そして、マッチング領域算出部U302は、設定したブロック内のN-1フィールド遅延信号FD1の画素値を、ブロックマッチング部307に出力する。即ち、ブロック内の画素値として、画素u(x)の画素値が出力される。

#### 【0029】

ブロック（画素u(x)のxの範囲および画素d(x)のxの範囲）は、切り出し位置決定部304から出力されたPと、ブロックサイズ決定部306から出力されたBSとから決定される。Pは、候補方向を表す値である。本実施例では、Pは、注目点（補間画素の生成位置）を通る候補方向の直線上の画素u(x)の水平方向位置xである。注目点を通る候補方向の直線上の画素d(x)の水平方向位置xは-Pとなる。BSはブロックの所定方向（本実施例では水平方向）のサイズ（画素数）である。画素u(x)のxの範囲（水平範囲）および画素d(x)のxの範囲は以下の算出式で算出される。なお、以下の式において、int(B/2)は、その値が整数であることを意味する。本実施例では、int(B/2)は、B/2の小数点以下を切り捨てた値である。

$$u \text{ の範囲} : (P - \text{int}(B/2)) \sim (P + \text{int}(B/2))$$

$$d \text{ の範囲} : (-P - \text{int}(B/2)) \sim (-P + \text{int}(B/2))$$

#### 【0030】

ブロックマッチング部307は、複数の候補方向のそれぞれについて、設定されたn個（本実施例では2つ）のブロック間の画像の類似度を算出する。

マッチング角度算出部308は、複数の候補方向のうち、類似度が最も高い方向を、注目点（補間画素の生成位置）におけるエッジの方向として判定する。

#### 【0031】

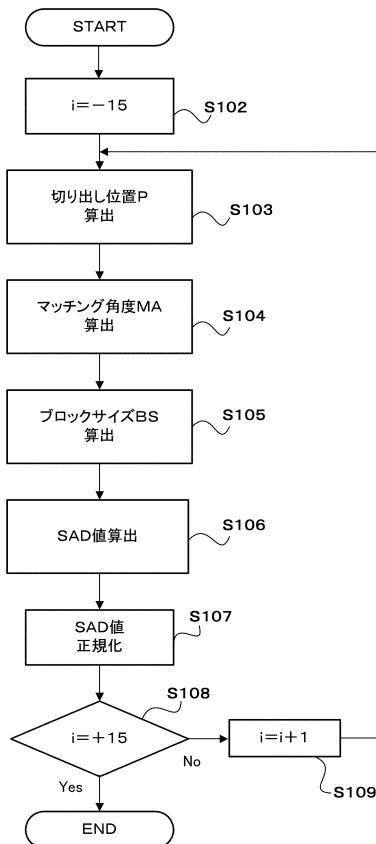

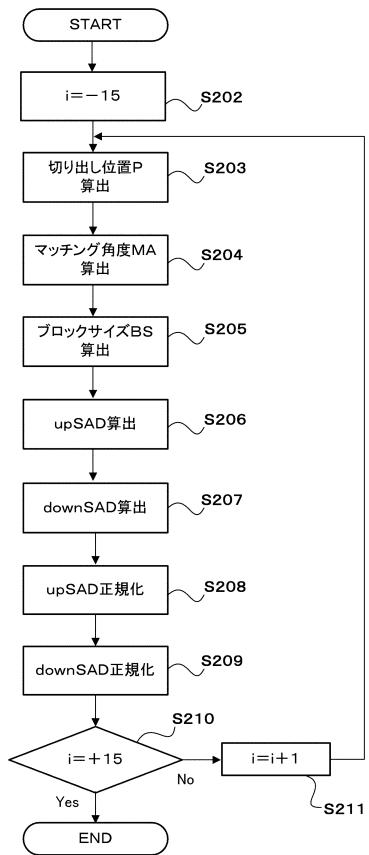

次に、本実施例に係る斜め検出部103の処理の流れを図5のフローチャートを用いて説明する。

まず、S102で、制御部303が、iの初期化を行い、iの初期値を切り出し位置決

10

20

30

40

50

定部 304 に出力する。*i* は、候補方向を表す値である。本実施例では、*i* は、注目点(補間画素の生成位置)を通る候補方向の直線上の画素 *u* (x) の水平方向位置 *x* であり、-15 ~ 15 の値が設定される。本実施例では、初期値として *i* = -15 が設定される。

#### 【0032】

次に、S103 で、切り出し位置決定部 304 が、切り出し位置 *P* を決定し、マッチング領域算出部 D301、マッチング領域算出部 U302、マッチング角度決定部 305、及び、ブロックマッチング部 307 に出力する。具体的には、切り出し位置決定部 304 は、制御部 303 から入力された *i* を切り出し位置 *P* として出力する。図 6 に示すように、マッチング領域算出部 D301 とマッチング領域算出部 U302 において、決定された *P* の値から、設定するブロックの中心位置が判断される。具体的には、マッチング領域算出部 U302 では、画素 *u* (P) の位置が中心位置として判断される。マッチング領域算出部 D301 では、画素 *d* (-P) の位置が中心位置として判断される。画素 *u* (P) は、補間画素の生成位置 *H* を中心として画素 *d* (-P) と点対称の位置にある。図 6 は、*P* = -3 の例である。

#### 【0033】

そして、S104 で、マッチング角度決定部 305 が、S103 で決定された切り出し位置 *P* に基づいて、マッチング角度 *MA* を算出する。マッチング角度決定部 305 は、算出したマッチング角度 *MA* を、ブロックサイズ決定部 306 に出力する。マッチング角度 *MA* は、図 6 に示すように、切り出し位置 *P* で表される候補方向の、所定方向(本実施例では水平方向)に対する角度である。換言すれば、マッチング角度 *MA* は、画素 *u* (P) と画素 *d* (-P) とを結ぶ直線と、水平方向とのなす角度である。本実施例では、切り出し位置 *P* 每のマッチング角度 *MA* を表すテーブルが予め用意されており、当該テーブルを用いて、S103 で決定された切り出し位置 *P* からマッチング角度 *MA* が決定される。

#### 【0034】

次に、S105 で、ブロックサイズ決定部 306 が、S104 で算出されたマッチング角度 *MA* に基づいて、ブロックサイズ *BS* を算出する。具体的には、マッチング角度 *MA* が大きい候補方向について設定するブロックよりも、マッチング角度 *MA* が小さい候補方向について設定するブロックのほうが、所定方向(本実施例では水平方向)の長さが長くなるように、ブロックサイズ *BS* が算出される。本実施例では、マッチング角度毎(若しくはマッチング角度 *MA* の範囲毎)のブロックサイズ *BS* を表すテーブルが予め用意されており、当該テーブルを用いて、S104 で算出されたマッチング角度 *MA* からブロックサイズ *BS* が決定される。テーブルの一例を図 7 に示す。

ブロックサイズ決定部 306 は、算出したブロックサイズ *BS* を、マッチング領域算出部 D301、マッチング領域算出部 U302、及び、ブロックマッチング部 307 に出力する。その後、マッチング領域算出部 D301 とマッチング領域算出部 U302 において、上記決定されたブロックサイズ *BS* のブロックが設定され、ブロック内の画素値がブロックマッチング部 307 に出力される。

このように、本実施例では、マッチング角度 *MA* に基づいて、設定する *n* 個のブロックのサイズが制御される。

#### 【0035】

そして、S106 で、ブロックマッチング部 307 が、S103 で算出された切り出し位置 *P*、S105 で算出されたブロックサイズ *BS*、マッチング領域算出部 D301 とマッチング領域算出部 U302 から出力された画素値を用いて、ブロックマッチングを行う。ブロックマッチングは、マッチング領域算出部 D301 で設定されたブロック内の画素値と、マッチング領域算出部 U302 で設定されたブロック内の画素値とを比較する処理である。ブロックマッチングにより、SAD 値(差分絶対値和)が算出される。

#### 【0036】

図 8 に、設定されたブロックの一例を示す。図 8 は、切り出し位置 *P* が -3 であり、ブロックサイズ *BS* が 5 である場合に設定されるブロックを示す。図 8 の例では、実ライン *U* の画素 *u* (-1) ~ *u* (-5) の領域と、実ライン *D* の画素 *d* (+1) ~ *d* (+5) の

10

20

30

40

50

領域とが、それぞれブロックとして設定されている。実ラインUは、補間画素の生成位置Hの1つ上のラインであり、実ラインDは、補間画素の生成位置の1つ下のラインである。また、図8中の補間ラインは補間画素が生成されるラインである。画素d(+1)～d(+5)は、補間画素の生成位置Hを中心として、画素u(-1)～u(-5)と点対称の位置にある。

#### 【0037】

図8に示すブロックが設定された場合、実ラインUの画素u(-1)～u(-5)と、実ラインDの画素d(+1)～d(+5)の値とを用いて、SAD値が算出される。SAD値は、以下の式を用いて算出される。

#### 【数1】

$$SAD(P) = \sum_{Shift=-\text{int}(BS/2)}^{\text{int}(BS/2)} |u(-P+Shift) - d(P+Shift)|$$

#### 【0038】

例えば、図8の例では、SAD値は以下の演算により算出される。なお、以下の式において、u(x)、d(x)はその画素の画素値を表す。

$$\begin{aligned} SAD(-3) = & |u(-5) - d(+1)| \\ & + |u(-4) - d(+2)| \\ & + |u(-3) - d(+3)| \\ & + |u(-2) - d(+4)| \\ & + |u(-1) - d(+5)| \end{aligned}$$

#### 【0039】

S106の次に、S107で、ブロックマッチング部307が、SAD値の正規化を行う。上述したように、本実施例では、ブロックサイズが一定ではない（候補方向によって変化する）。複数のブロックサイズで得られた複数のSADは、同じ基準で扱うことはできない。そこで、本ステップでは、或るブロックサイズに対応する値となるように、S106で算出したSAD値を正規化する。本実施例では、一番小さなブロックサイズに対応する値となるように、S106で算出したSAD値を正規化する。例えば、ブロックサイズの最小値が3であり、ブロックサイズを15としてSAD値が算出された場合には、算出されたSAD値に3/15を乗算することにより、正規化後のSAD値が得られる。なお、SAD値が一番小さくなるブロックサイズに対応する値となるように、SAD値が正規化されてもよいし、SAD値が一番大きくなるブロックサイズに対応する値となるように、SAD値が正規化されてもよい。

#### 【0040】

次に、S108で、制御部303が、i=+15か否かを判定する。この判定により、複数の候補方向の全てについてSAD値が算出されたか否かを判定することができる。つまり、i=+15の場合には、制御部303が、複数の候補方向の全てについてSAD値が算出されたと判断し、本フローが終了される。i=+15でない場合には、制御部303が、複数の候補方向の全てについてのSAD値の算出が完了していないと判断し、S109でiを1インクリメントする。そして、S103へ処理が戻され、i=+15となるまで、S103～S107の処理が繰り返される。

#### 【0041】

ブロックマッチング部307は、上記処理フローにより得られた複数のSAD値をマッチング角度算出部308に出力する。上記複数のSAD値は、P=-15～+15に対応する31個のSAD値（正規化された値）である。正規化されたSAD値は、ブロック間の画像の類似度に対応する（非類似度を表す）。そして、マッチング角度算出部308は、上記31個のSAD値から、エッジの方向を判定する（詳細は後述する）。

以上述べた処理は、補間画素の生成位置毎に行われる。

なお、図5では、iの値をカウントして、候補方向毎にSAD値を算出する例を示したが、複数の候補方向に対応する複数のSAD値が並列に算出されてもよい。

10

20

30

40

50

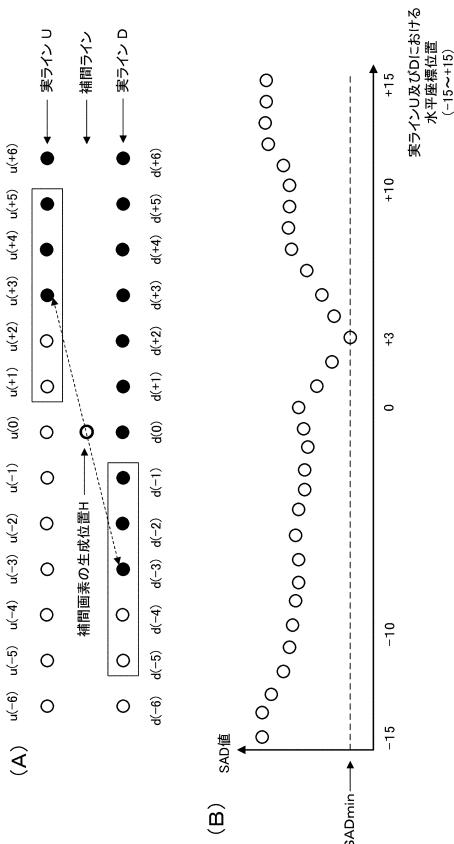

## 【0042】

マッチング角度算出部308は、ブロックマッチング部307で算出された31個のSAD値（正規化された値）から、補間画素の生成位置でのエッジの方向を判定し、判定結果を角度情報ANGLEとして出力する。本実施例では、複数（31個）の候補方向のうち、ブロック間の画像の類似度が最も高い方向が、注目点（補間画素の生成位置）におけるエッジの方向として判定される。SAD値は、ブロック間の画像の類似度が高いほど小さくなる。そのため、本実施例では、マッチング角度算出部308は、上記31個のSAD値の最小値に対応するPの値が、補間画素の生成位置でのエッジの方向を表す値であると判定される。SAD値の最小値（SADM<sub>in</sub>）は以下の式で算出される。なお、以下の式において、Pは-15～15であり、MINは最小値を算出する関数である。

10

$$SADM_{in} = \text{MIN}(SAD(P))$$

マッチング角度算出部308は、 $SADM_{in} = SAD(P)$ となるPの値を角度情報ANGLEとして出力する。なお、 $SADM_{in}$ が所定の閾値以上である場合には、補間画素の生成位置がエッジ部分ではないと判定されてもよい。補間画素の生成位置がエッジ部分ではないと判定された場合には、角度情報ANGLEとして0が出力される。

## 【0043】

例えば、図9(A)に示すような画素構成の画像（斜めエッジ部分の画像）を表す信号が入力された場合には、補間画素の生成位置Hに対して算出された31個のSAD値の分布は図9(B)のようになる。図9(B)の例では、実ラインUのu(+3)の位置（P=+3の位置）に対応するSAD値が最小値SADM<sub>in</sub>となっている。そのため、マッチング角度算出部308からは、角度情報ANGLE=+3が出力される。

20

## 【0044】

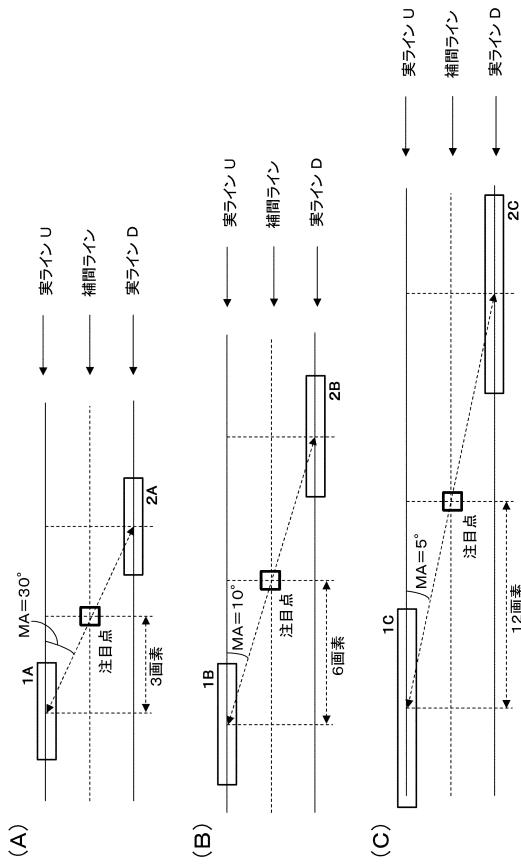

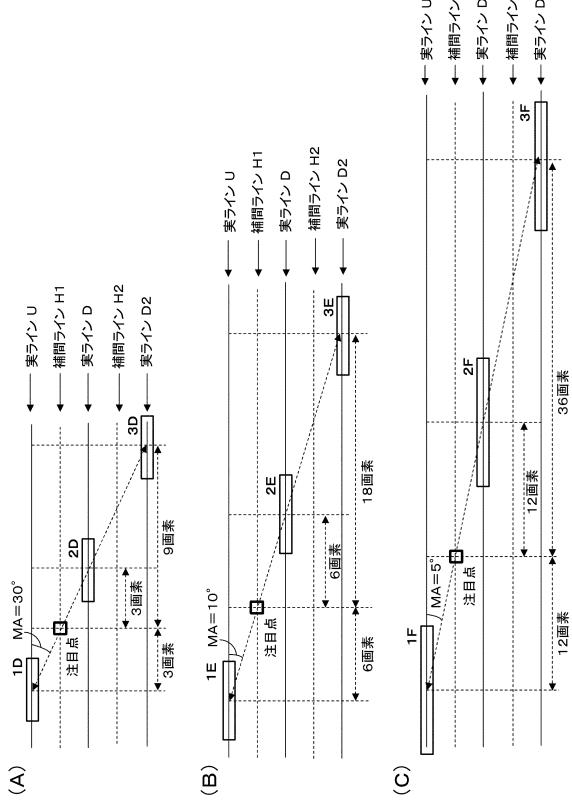

次に、マッチング角度MAが30°、10°、5°の場合における、SAD値算出の具体例を説明する。

マッチング角度MAとブロックサイズBSの関係の一例を図10に示す。マッチング角度MAとブロックサイズBSの関係が図10に示す関係であった場合、MA=30°のときにBS=5となり、MA=10°のときにBS=9となり、MA=5°のときにBS=15となる。

## 【0045】

図11(A)を用いて、MA=30°の場合の例について詳細に説明する。

30

図11(A)の例では、実ラインUと実ラインDのそれぞれについて、補間ライン上に位置する注目点（補間画素の生成位置）を通り、MA=30°を満たす直線上の画素を中心として、水平方向5画素分の領域がブロックとして設定される。実ラインUに対して設定されたブロックをブロック1A、実ラインDに対して設定されたブロックをブロック2Aと記載する。

具体的には、切り出し位置決定部304においてP=-3とされ、マッチング角度決定部305においてMA=30°とされ、ブロックサイズ決定部306において図10の関係からBS=5とされる。そのため、実ラインUについては、注目点から左側に3画素離れた画素（実ラインU上の画素）を中心とする水平方向5画素分の領域が、ブロック1Aとして設定される。実ラインDについては、注目点から右側に3画素離れた画素（実ラインD上の画素）を中心とする水平方向5画素分の領域が、ブロック2Aとして設定される。ブロック1Aは、注目点を中心としてブロック2Aと点対称の位置にある。

40

そして、ブロックマッチング部307において、ブロック1Aの画素値と、ブロック2Aの画素値とが比較されて、SAD値が算出される。

## 【0046】

図11(B)を用いて、MA=10°の場合の例について詳細に説明する。

図11(B)の例では、実ラインUと実ラインDのそれぞれについて、補間ライン上に位置する注目点（補間画素の生成位置）を通り、MA=10°を満たす直線上の画素を中心として、水平方向9画素分の領域がブロックとして設定される。実ラインUに対して設定されたブロックをブロック1B、実ラインDに対して設定されたブロックをブロック2

50

Bと記載する。

具体的には、切り出し位置決定部304において $P = -6$ とされ、マッチング角度決定部305において $MA = 10^\circ$ とされ、ブロックサイズ決定部306において図10の関係から $BS = 9$ とされる。そのため、実ラインUについては、注目点から左側に6画素離れた画素（実ラインU上の画素）を中心とする水平方向9画素分の領域が、ブロック1Bとして設定される。実ラインDについては、注目点から右側に6画素離れた画素（実ラインD上の画素）を中心とする水平方向9画素分の領域が、ブロック2Bとして設定される。ブロック1Bは、注目点を中心としてブロック2Bと点対称の位置にある。

そして、ブロックマッチング部307において、ブロック1Bの画素値と、ブロック2Bの画素値とが比較されて、SAD値が算出される。

ここで、SAD値が $BS = 5$ に対応する値に正規化されるものとすると、上記算出されたSAD値（正規化前のSAD値；9画素SAD）は以下の式により正規化される。以下の式において、5画素SADは正規化後のSAD値である。

$$5\text{画素SAD} = 9\text{画素SAD} \times (5/9)$$

#### 【0047】

図11(C)を用いて、 $MA = 5^\circ$ の場合の例について詳細に説明する。

図11(C)の例では、実ラインUと実ラインDのそれぞれについて、補間ライン上に位置する注目点（補間画素の生成位置）を通り、 $MA = 5^\circ$ を満たす直線上の画素を中心として、水平方向15画素分の領域がブロックとして設定される。実ラインUに対して設定されたブロックをブロック1C、実ラインDに対して設定されたブロックをブロック2Cと記載する。

具体的には、切り出し位置決定部304において $P = -12$ とされ、マッチング角度決定部305において $MA = 5^\circ$ とされ、ブロックサイズ決定部306において図10の関係から $BS = 15$ とされる。そのため、実ラインUについては、注目点から左側に12画素離れた画素（実ラインU上の画素）を中心とする水平方向15画素分の領域が、ブロック1Cとして設定される。実ラインDについては、注目点から右側に12画素離れた画素（実ラインD上の画素）を中心とする水平方向15画素分の領域が、ブロック2Cとして設定される。ブロック1Cは、注目点を中心としてブロック2Cと点対称の位置にある。

そして、ブロックマッチング部307において、ブロック1Cの画素値と、ブロック2Cの画素値とが比較されて、SAD値が算出される。

ここで、SAD値が $BS = 5$ に対応する値に正規化されるものとすると、上記算出されたSAD値（正規化前のSAD値；15画素SAD）は以下の式により正規化される。以下の式において、5画素SADは正規化後のSAD値である。

$$5\text{画素SAD} = 15\text{画素SAD} \times (5/15)$$

#### 【0048】

以上述べたように、本実施例によれば、エッジの方向の候補である候補方向の、所定方向（本実施例では水平方向）に対する角度に依ってブロックサイズが変更される。具体的には、所定方向に対する角度が大きい候補方向について設定するブロックよりも、所定方向に対する角度が小さい候補方向について設定するブロックのほうが、所定方向の長さが長くなるように、ブロックのサイズが制御される。即ち、本実施例では、エッジ方向が上記角度の浅い方向である可能性の度合いを算出する際に、ブロックのサイズが大きくされ、エッジ方向が上記角度の深い方向である可能性の度合いを算出する際に、ブロックのサイズが小さくされる。それにより、エッジの方向を精度良く判定することができる。なお、上記可能性の度合いは、ブロック間の画像の類似度である。

具体的には、ブロックの所定方向の長さが長い場合、エッジ方向が上記角度の浅い方向である可能性の度合いを精度良く算出することができるが、エッジ方向が上記角度の深い方向である可能性の度合いは精度良く算出することができない。一方、ブロックの所定方向の長さが短い場合、エッジ方向が上記角度の深い方向である可能性の度合いを精度良く算出することができるが、エッジ方向が上記角度の浅い方向である可能性の度合いは精度良く算出することができない。本実施例では、上述したようにブロックのサイズを制御す

10

20

30

40

50

ることにより、エッジ方向が上記角度の浅い方向である可能性の度合いと、エッジ方向が上記角度の深い方向である可能性の度合いとの両方を精度良く算出することができる。それにより、エッジの方向を精度良く判定することができ、ひいては、正確な補間画素を生成することができ、ジャギーの発生を抑制することができる。

#### 【0049】

なお、本実施例では、注目点が補間画素の生成位置である場合の例を示したが、注目点はこれに限らない。例えば、注目点は実ライン上の画素位置であってもよい。

なお、本実施例では、画像の類似度に対応する値として S A D 値（正規化された S A D 値）である場合の例を説明したが、類似度に対応する値は S A D 値に限らない。例えば、ブロック毎に画像のパターンが解析され、ブロック間のパターンの差が、類似度に対応する値（非類似度）として算出されてもよい。また、 S A D 値の逆数が類似度として算出されてもよい。10

なお、本実施例では、注目点の上下に隣接するライン上にブロックが設定されるものとしたが、注目点から離れたライン上にブロックが設定されてもよい。また、本実施例では、ブロックの垂直方向のサイズが 1 画素であるものとしたが、垂直方向のサイズは複数画素分のサイズであってもよい。ブロックは注目点を含む領域であってもよい。

#### 【0050】

##### <実施例 2 >

以下、本発明の実施例 2 に係るエッジ方向判定装置、エッジ方向判定装置の制御方法、及び、画像処理装置について、図面を用いて説明する。実施例 1 では、候補方向毎に 2 つのブロックを設定する例について説明した。本実施例では、候補方向毎に 3 つのブロックを設定する例について説明する。なお、実施例 1 と同様の機能や構成については極力説明を省略する。20

本実施例に係る画像処理装置の大まかな構成は実施例 1 ( 図 1 ) と同様のため、その説明は省略する。

#### 【0051】

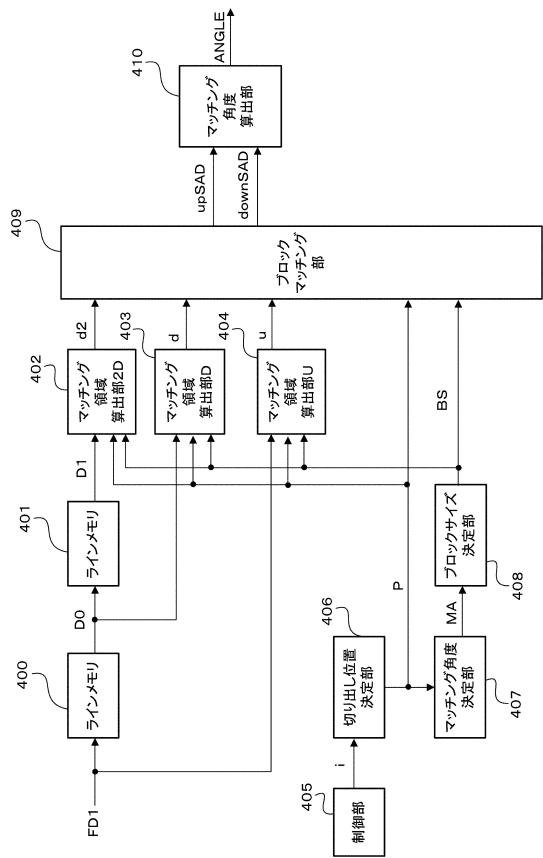

本実施例では、斜め検出部の内部構成が実施例 1 と異なる。図 1 2 は、本実施例に係る斜め検出部の内部構成を示すブロック図である。

#### 【0052】

ラインメモリ 4 0 0 は、入力された N - 1 フィールド信号 F D 1 を 1 H ( 1 水平走査期間 ) だけ遅延させ、当該遅延させた信号を 1 H 遅延信号 D 0 として出力する。30

ラインメモリ 4 0 1 は、入力された 1 H 遅延信号 D 0 を 1 H だけ遅延させ、当該遅延させた信号を 2 H 遅延信号 D 1 として出力する。2 H 遅延信号 D 1 は、N - 1 フィールド信号 F D 1 を 2 H だけ遅延させた信号である。

#### 【0053】

マッチング領域算出部 2 D 4 0 2 、マッチング領域算出部 D 4 0 3 、及び、マッチング領域算出部 U 4 0 4 は、複数の候補方向のそれぞれについて、注目点を通るその方向の直線上に 3 つのブロックを設定する。

具体的には、マッチング領域算出部 2 D 4 0 2 には、2 H 遅延信号 D 1 ( 補間画素の生成位置の 3 つ下のラインの画素値 ) が入力される。マッチング領域算出部 2 D 4 0 2 は、上記 3 つのブロックのうちの 1 つとして、補間画素の生成位置の 3 つ下のライン上の複数の画素からなる領域を設定する。そして、マッチング領域算出部 2 D 4 0 2 は、設定したブロック内の 2 H 遅延信号 D 1 の画素値を、ブロックマッチング部 4 0 9 に出力する。本実施例では、補間画素の生成位置の 3 つ下のライン上の画素を d 2 と記載する。40

マッチング領域算出部 D 4 0 3 には、1 H 遅延信号 D 0 ( 補間画素の生成位置の 1 つ下のラインの画素値 ) が入力される。マッチング領域算出部 D 4 0 3 は、上記 3 つのブロックのうちの 1 つとして、補間画素の生成位置の 1 つ下のライン上の複数の画素からなる領域を設定する。そして、マッチング領域算出部 D 4 0 3 は、設定したブロック内の 1 H 遅延信号 D 0 の画素値を、ブロックマッチング部 4 0 9 に出力する。即ち、ブロック内の画素値として、画素 d ( x ) の画素値が出力される。50

マッチング領域算出部 U 4 0 4 には、N - 1 フィールド遅延信号 F D 1 (補間画素の生成位置の 1 つ上のラインの画素値) が入力される。マッチング領域算出部 U 4 0 4 は、上記 3 つのブロックのうちの 1 つとして、補間画素の生成位置の 1 つ上のライン上の複数の画素からなる領域を設定する。そして、マッチング領域算出部 U 4 0 4 は、設定したブロック内の N - 1 フィールド遅延信号 F D 1 の画素値を、ブロックマッチング部 4 0 9 に出力する。即ち、ブロック内の画素値として、画素 u (x) の画素値が出力される。

#### 【0054】

ブロック (画素 u (x) の x の範囲、画素 d (x) の x の範囲、及び、画素 d 2 (x) の x の範囲) は、切り出し位置決定部 4 0 6 から出力された P と、ブロックサイズ決定部 4 0 8 から出力された B S とから決定される。画素 u (x) の x の範囲 (水平範囲)、画素 d (x) の x の範囲、及び、画素 d 2 (x) の x の範囲は以下の算出式で算出される。

10

$$u \text{ の範囲} : (P - \text{int}(BS / 2)) \sim (P + \text{int}(BS / 2))$$

$$d \text{ の範囲} : (-P - \text{int}(BS / 2)) \sim (-P + \text{int}(BS / 2))$$

$$d_2 \text{ の範囲} : (-3P - \text{int}(BS / 2)) \sim (-3P + \text{int}(BS / 2))$$

#### 【0055】

次に、本実施例に係る斜め検出部の処理の流れを図 1 3 のフローチャートを用いて説明する。

まず、S 2 0 2 で、制御部 4 0 5 が、i の初期化を行い、i の初期値を切り出し位置決定部 4 0 6 に出力する。本実施例では、実施例 1 と同様に、i の値として、- 1 5 ~ 1 5 の値が設定される。本実施例では、初期値として i = - 1 5 が設定される。

20

#### 【0056】

次に、S 2 0 3 で、切り出し位置決定部 4 0 6 が、実施例 1 と同様に、切り出し位置 P を決定する。決定された切り出し位置 P は、マッチング領域算出部 2 D 4 0 2、マッチング領域算出部 D 4 0 3、マッチング領域算出部 U 4 0 4、マッチング角度決定部 4 0 7、及び、ブロックマッチング部 4 0 9 に出力される。図 1 4 に示すように、マッチング領域算出部 2 D 4 0 2、マッチング領域算出部 D 4 0 3、及び、マッチング領域算出部 U 4 0 4 において、決定された P の値から、設定するブロックの中心位置が判断される。具体的には、マッチング領域算出部 U 4 0 4 では、画素 u (P) の位置が中心位置として判断される。マッチング領域算出部 D 4 0 3 では、画素 d (-P) の位置が中心位置として判断される。マッチング領域算出部 2 D 4 0 2 では、画素 d (-3P) の位置が中心位置として判断される。画素 u (P) は、補間画素の生成位置 H を中心として画素 d (-P) と点対称の位置にある。画素 d (-3P) は、画素 u (P) と画素 d (-P) を通る直線上の画素である。図 1 4 は、P = - 1 の例である。

30

#### 【0057】

そして、S 2 0 4 で、マッチング角度決定部 4 0 7 が、S 2 0 3 で決定された切り出し位置 P に基づいて、マッチング角度 M A を算出する。算出方法は実施例 1 と同じである。

#### 【0058】

次に、S 2 0 5 で、ブロックサイズ決定部 4 0 8 が、S 2 0 4 で算出されたマッチング角度 M A に基づいて、ブロックサイズ B S を算出する。算出方法は実施例 1 と同じである。算出されたブロックサイズ B S は、マッチング領域算出部 2 D 4 0 2、マッチング領域算出部 D 4 0 3、マッチング領域算出部 U 4 0 4、及び、ブロックマッチング部 4 0 9 に出力される。その後、マッチング領域算出部 2 D 4 0 2、マッチング領域算出部 D 4 0 3、及び、マッチング領域算出部 U 4 0 4 において、上記決定されたブロックサイズ B S のブロックが設定され、ブロック内の画素値がブロックマッチング部 4 0 9 に出力される。

40

#### 【0059】

そして、S 2 0 6 で、ブロックマッチング部 4 0 9 が、S 2 0 3 で算出された切り出し位置 P、S 2 0 5 で算出されたブロックサイズ B S、マッチング領域算出部 D 4 0 3 とマッチング領域算出部 U 4 0 4 から出力された画素値を用いて、ブロックマッチングを行う。具体的には、マッチング領域算出部 D 4 0 3 で設定されたブロック内の画素値と、マッチング領域算出部 U 4 0 4 で設定されたブロック内の画素値とから、実施例 1 と同様の方

50

法で S A D 値が算出される。本ステップで算出される S A D 値を、 u p S A D と記載する。

#### 【 0 0 6 0 】

次に、 S 2 0 7 で、 ブロックマッチング部 4 0 9 が、 S 2 0 3 で算出された切り出し位置 P 、 S 2 0 5 で算出されたブロックサイズ B S 、 マッチング領域算出部 2 D 4 0 2 とマッチング領域算出部 D 4 0 3 から出力された画素値を用いて、 ブロックマッチングを行う。具体的には、 マッチング領域算出部 2 D 4 0 2 で設定されたブロック内の画素値と、 マッチング領域算出部 D 4 0 3 で設定されたブロック内の画素値とから、 実施例 1 と同様の方法で S A D 値が算出される。本ステップで算出される S A D 値を、 d o w n S A D と記載する。

10

#### 【 0 0 6 1 】

そして、 S 2 0 8 で、 ブロックマッチング部 4 0 9 が u p S A D の正規化を行い、 S 2 0 9 で、 ブロックマッチング部 4 0 9 が d o w n S A D の正規化を行う。正規化を行う理由、 及び、 正規化の方法は実施例 1 と同様である。

#### 【 0 0 6 2 】

次に、 S 2 1 0 で、 制御部 4 0 5 が、 i = + 1 5 か否かを判定する。 i = + 1 5 の場合には、 制御部 4 0 5 が、 複数の候補方向の全てについて S A D 値 ( u p S A D 、 d o w n S A D ) が算出されたと判断し、 本フローが終了される。 i = + 1 5 でない場合には、 制御部 4 0 5 が、 複数の候補方向の全てについての S A D 値の算出が完了していないと判断し、 S 2 1 1 で i を 1 インクリメントする。そして、 S 2 0 3 へ処理が戻され、 i = + 1 5 となるまで、 S 2 0 3 ~ S 2 0 9 の処理が繰り返される。

20

#### 【 0 0 6 3 】

ブロックマッチング部 4 0 9 は、 上記処理フローにより得られた複数の S A D 値をマッチング角度算出部 4 1 0 に出力する。上記複数の S A D 値は、 P = - 1 5 ~ + 1 5 に対応する 3 1 個の u p S A D ( 正規化された値 ) 、 及び、 P = - 1 5 ~ + 1 5 に対応する 3 1 個の d o w n S A D ( 正規化された値 ) である。そして、 マッチング角度算出部 4 1 0 は、 上記 6 2 個の S A D 値から、 エッジの方向を判定する ( 詳細は後述する ) 。

#### 【 0 0 6 4 】

マッチング角度算出部 4 1 0 は、 ブロックマッチング部 4 0 9 で算出された 3 1 個の u p S A D 値 ( 正規化された値 ) と、 3 1 個の d o w n S A D ( 正規化された値 ) とから、 補間画素の生成位置でのエッジの方向を判定する。そして、 マッチング角度算出部 4 1 0 は、 判定結果を角度情報 A N G L E として出力する。本実施例では、 u p S A D の最小値に対応する P の値、 または、 d o w n S A D の最小値に対応する P の値が、 補間画素の生成位置でのエッジの方向を表す値であると判定される。そして、 補間画素の生成位置でのエッジの方向を表す値であると判定された P の値が、 角度情報 A N G L E として出力される。また、 u p S A D の最小値に対応する P の値と、 d o w n S A D の最小値に対応する P の値との差が所定の閾値以上である場合には、 補間画素の生成位置がエッジ部分ではないと判定され、 角度情報 A N G L E として 0 が出力される。

30

#### 【 0 0 6 5 】

以下、 マッチング角度算出部 4 1 0 の処理について、 式を用いて説明する。

40

まず、 以下の式により、 u p S A D の最小値 ( u p S A D m i n ) と d o w n S A D の最小値 ( d o w n S A D m i n ) が算出される。なお、 以下の式において、 P は - 1 5 ~ 1 5 であり、 M I N は最小値を算出する関数である。

$$u p S A D m i n = M I N ( u p S A D ( P ) )$$

$$d o w n S A D m i n = M I N ( d o w n S A D ( P ) )$$

そして、 以下の条件式を満たす場合には、 u p S A D m i n = u p S A D ( P ) となる P の値、 または、 d o w n S A D m i n = d o w n S A D ( P ) となる P の値が角度情報 A N G L E として出力される。以下の条件式を満たさない場合には、 角度情報 A N G L E として 0 が出力される。なお、 以下の式において、 u p P は、 u p S A D m i n = u p S A D ( P ) となる P の値であり、 d o w n P は、 d o w n S A D m i n = d o w n S A D

50

( P ) となる P の値である。

$$| \text{upP} - \text{downP} | < \text{閾値}$$

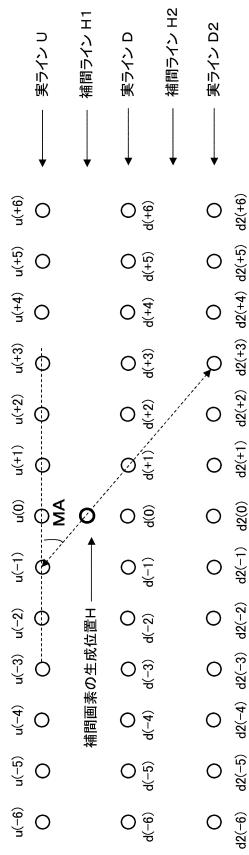

#### 【 0 0 6 6 】

次に、マッチング角度 MA が 30°、10°、5° の場合における、S A D 値算出の具体例を説明する。マッチング角度 MA とブロックサイズ BS の関係は、図 10 に示す関係であるものとする。

#### 【 0 0 6 7 】

図 15 ( A ) を用いて、MA = 30° の場合の例について詳細に説明する。

図 15 ( A ) の例では、実ライン U、実ライン D、実ライン D 2 のそれぞれについて、補間ライン上に位置する注目点（補間画素の生成位置）を通り、MA = 30° を満たす直線上の画素を中心として、水平方向 5 画素分の領域がブロックとして設定される。実ライン U に対して設定されたブロックをブロック 1 D、実ライン D に対して設定されたブロックをブロック 2 D、実ライン D 2 に対して設定されたブロックをブロック 3 D と記載する。

10

具体的には、切り出し位置決定部 406において P = -3 とされ、マッチング角度決定部 407において MA = 30° とされ、ブロックサイズ決定部 408において BS = 5 とされる。そのため、実ライン U については、注目点から左側に 3 画素離れた画素（実ライン U 上の画素）を中心とする水平方向 5 画素分の領域が、ブロック 1 D として設定される。実ライン D については、注目点から右側に 3 画素離れた画素（実ライン D 上の画素）を中心とする水平方向 5 画素分の領域が、ブロック 2 D として設定される。実ライン D 2 については、注目点から右側に 9 画素離れた画素（実ライン D 2 上の画素）を中心とする水平方向 5 画素分の領域が、ブロック 3 D として設定される。ブロック 1 D は、注目点を中心としてブロック 2 D と点対称の位置にある。ブロック 3 D の中心は、ブロック 1 D の中心とブロック 2 D の中心とを通る直線（注目点を通る直線）上に位置する。

20

そして、ブロックマッチング部 409において、ブロック 1 D の画素値と、ブロック 2 D の画素値とが比較されて、up S A D が算出される。また、ブロック 2 D の画素値と、ブロック 3 D の画素値とが比較されて、down S A D が算出される。

#### 【 0 0 6 8 】

図 15 ( B ) を用いて、MA = 10° の場合の例について詳細に説明する。

図 15 ( B ) の例では、実ライン U、実ライン D、実ライン D 2 のそれぞれについて、補間ライン上に位置する注目点（補間画素の生成位置）を通り、MA = 10° を満たす直線上の画素を中心として、水平方向 5 画素分の領域がブロックとして設定される。実ライン U に対して設定されたブロックをブロック 1 E、実ライン D に対して設定されたブロックをブロック 2 E、実ライン D 2 に対して設定されたブロックをブロック 3 E と記載する。

30

具体的には、切り出し位置決定部 406において P = -6 とされ、マッチング角度決定部 407において MA = 10° とされ、ブロックサイズ決定部 408において BS = 9 とされる。そのため、実ライン U については、注目点から左側に 6 画素離れた画素（実ライン U 上の画素）を中心とする水平方向 9 画素分の領域が、ブロック 1 E として設定される。実ライン D については、注目点から右側に 6 画素離れた画素（実ライン D 上の画素）を中心とする水平方向 9 画素分の領域が、ブロック 2 E として設定される。実ライン D 2 については、注目点から右側に 18 画素離れた画素（実ライン D 2 上の画素）を中心とする水平方向 9 画素分の領域が、ブロック 3 E として設定される。ブロック 1 E は、注目点を中心としてブロック 2 E と点対称の位置にある。ブロック 3 E の中心は、ブロック 1 E の中心とブロック 2 E の中心とを通る直線（注目点を通る直線）上に位置する。

40

そして、ブロックマッチング部 409において、ブロック 1 E の画素値と、ブロック 2 E の画素値とが比較されて、up S A D が算出される。また、ブロック 2 E の画素値と、ブロック 3 E の画素値とが比較されて、down S A D が算出される。実施例 1 と同様に、算出された up S A D と down S A D が、BS = 5 に対応する値に正規化される。

#### 【 0 0 6 9 】

図15(C)を用いて、MA = 5°の場合の例について詳細に説明する。

図15(C)の例では、実ラインU、実ラインD、実ラインD2のそれぞれについて、補間ライン上に位置する注目点(補間画素の生成位置)を通り、MA = 5°を満たす直線上の画素を中心として、水平方向5画素分の領域がブロックとして設定される。実ラインUに対して設定されたブロックをブロック1F、実ラインDに対して設定されたブロックをブロック2F、実ラインD2に対して設定されたブロックをブロック3Fと記載する。

具体的には、切り出し位置決定部406においてP = -12とされ、マッチング角度決定部407においてMA = 5°とされ、ブロックサイズ決定部408においてBS = 15とされる。そのため、実ラインUについては、注目点から左側に12画素離れた画素(実ラインU上の画素)を中心とする水平方向15画素分の領域が、ブロック1Fとして設定される。実ラインDについては、注目点から右側に12画素離れた画素(実ラインD上の画素)を中心とする水平方向15画素分の領域が、ブロック2Fとして設定される。実ラインD2については、注目点から右側に36画素離れた画素(実ラインD2上の画素)を中心とする水平方向15画素分の領域が、ブロック3Fとして設定される。ブロック1Fは、注目点を中心としてブロック2Fと点対称の位置にある。ブロック3Fの中心は、ブロック1Fの中心とブロック2Fの中心とを通る直線(注目点を通る直線)上に位置する。

そして、ブロックマッチング部409において、ブロック1Fの画素値と、ブロック2Fの画素値とが比較されて、upSADが算出される。また、ブロック2Fの画素値と、ブロック3Fの画素値とが比較されて、downSADが算出される。実施例1と同様に、算出されたupSADとdownSADは、BS = 5に対応する値に正規化される。

#### 【0070】

以上述べたように、本実施例では、1つの候補方向に対して実施例1より多くのブロックが設定され、設定されたブロックを比較してエッジの方向が判定される。それにより、実施例1よりも高精度にエッジの方向を判定することができる。

なお、本実施例では、注目点の上側に1つのブロックを設定し、注目点の下側に2つのブロックを設定する場合の例を示したが、設定するブロックの位置はこれに限らない。例えば、注目点の上側に2つのブロックを設定し、注目点の下側に1つのブロックが設定されてもよい。注目点の上側と下側の一方に3つのブロックが設定されてもよい。具体的には、補間画素の生成位置の上側に隣接する3つの実ラインのそれぞれにブロックが設定されてもよい。

また、3つより多くのブロックが設定されてもよい。例えば、注目点の上側に2つのブロックを設定し、注目点の下側に2つのブロックが設定されてもよい。

#### 【0071】

##### <実施例3>

以下、本発明の実施例3に係るエッジ方向判定装置、エッジ方向判定装置の制御方法、及び、画像処理装置について、図面を用いて説明する。本実施例では、ブロックの設定位置である直線上(候補方向の直線上)の位置における、所定方向の位置の変化に対する画素値の変化の勾配に応じて、対応する候補方向に対して設定するn個のブロックのサイズを制御する(補正する)例を説明する。本実施例では、上記所定方向が水平方向である場合の例について説明する。なお、実施例1, 2と同様の機能や構成については極力説明を省略する。

本実施例に係る画像処理装置の大まかな構成は実施例1(図1)と同様のため、その説明は省略する。

#### 【0072】

本実施例では、斜め検出部の内部構成が実施例1, 2と異なる。具体的には、本実施例に係る斜め検出部は、実施例1, 2(図4, 12)に示す機能部の他に、勾配算出部501とブロックサイズ補正部502を更に有する。図16は、本実施例に係る斜め検出部の内部構成を示すブロック図である。図16は、実施例1に本実施例の特徴である構成を加えた場合の例を示すが、実施例2に本実施例の特徴である構成が加えられてもよい。

10

20

30

40

50

以下、図16を用いて、本実施例に係る斜め検出部について説明する。なお、実施例1と同様の機能部には同じ符号を付し、その説明は省略する。

#### 【0073】

勾配算出部501は、候補方向毎に、その候補方向に対して設定するn個のブロックのうちの少なくとも1つのブロックについて、上記勾配を算出する。

本実施例では、勾配算出部501には、各マッチング領域算出部（マッチング領域算出部D301とマッチング領域算出部U302）から出力された画素値が入力される。なお、本実施例では、マッチング領域算出部は、マッチング領域算出部で判断されたブロックよりも大きい領域内の画素値を出力する。例えば、マッチング領域算出部D301は、注目点（補間画素の生成位置）の1つ下のラインの全ての画素値を出力する。マッチング領域算出部U302は、注目点の1つ上のラインの全ての画素値を出力する。10

そして、勾配算出部501は、設定するn個（2つ）のブロックのそれぞれについて勾配を算出し、2つのブロックについて算出した2つの勾配の代表値を表すフラグ（勾配フラグF）をブロックサイズ補正部502に出力する。

#### 【0074】

勾配算出部501の動作の具体例について、図17を用いて説明する。図17は、P=3の場合の例である。P=3の場合、画素u(P)を中心とするブロック（実ラインU上の画素からなる領域）と、画素d(-P)を中心とするブロック（実ラインD上の画素からなる領域）とが設定される。

#### 【0075】

勾配算出部501は、上記2つのブロックのそれぞれについて、以下の式により勾配を算出する。即ち、本実施例では、第1の差と第2の差が算出される。そして、第1の差と第2の差のうち大きい方の差が、勾配として算出される。第1の差は、ブロックの設定位置における画素値と、当該設定位置から左方向に所定距離離れた位置における画素値との差である。第2の差は、ブロックの設定位置における画素値と、当該設定位置から右方向（左方向の反対方向）に所定距離離れた位置における画素値との差である。なお、以下の式において、u(x), d(x)は、その画素の画素値（例えば輝度や色差）を表す。MAXは、最大値を算出する関数である。20

##### [実ラインU上に設定されたブロックについて]

$$\text{第1の差 } \text{hedge\_u1} = | u(P) - u(P-2) |$$

$$\text{第2の差 } \text{hedge\_u2} = | u(P) - u(P+2) |$$

$$\text{勾配 } \text{hedge\_u} = \text{MAX}(\text{hedge\_u1}, \text{hedge\_u2})$$

##### [実ラインD上に設定されたブロックについて]

$$\text{第1の差 } \text{hedge\_d1} = | d(-P) - d(-P-2) |$$

$$\text{第2の差 } \text{hedge\_d2} = | d(-P) - d(-P+2) |$$

$$\text{勾配 } \text{hedge\_d} = \text{MAX}(\text{hedge\_d1}, \text{hedge\_d2})$$

なお、上記例は、上記所定距離が2画素分の距離である場合の例であるが、上記所定距離は2画素分の距離に限らない。例えば、上記所定距離は1, 3, 5画素分の距離であってもよい。

また、勾配の算出方法は上記方法に限らない。例えば、第1の差または第2の差のいずれか一方が勾配として算出されてもよい。垂直方向の位置が互いに等しい、ブロックの設定位置の画素を含む3つ以上の画素の画素値から、最小二乗法などを用いて勾配が算出されてもよい。40

#### 【0076】

そして、勾配算出部501は、以下の条件式を満たす場合に、水平方向に対する角度が大きいエッジ部分である可能性が高いと判断し、勾配フラグF=0を出力する。また、勾配算出部501は、以下の条件式を満たさない場合に、水平方向に対する角度が小さいエッジ部分である可能性が高いと判断し、勾配フラグF=1を出力する。即ち、本実施例では、2つのブロックについて算出した2つの勾配のうち、値が大きいものが代表値とされる。そして、代表値が所定値以上（閾値以上）の場合に勾配フラグF=0とされ、代表値50

が所定値未満（閾値未満）の場合に勾配フラグ  $F = 1$  とされる。

( hedge\_u 閾値 ) または ( hedge\_d 閾値 )

#### 【0077】

ブロックサイズ補正部 502 は、勾配が大きいときよりも、勾配が小さいときのほうが、水平方向の長さが長くなるように、対応する候補方向に対して設定する  $n$  個のブロックのサイズを制御する（補正する）。そして、ブロックサイズ補正部 502 は、補正後のブロックサイズ BS2（ブロックの水平方向の画素数）をブロックマッチング部 307 に出力する。

本実施例では、ブロックサイズ補正部 502 は、2つのブロックについて算出した2つの勾配の代表値に基づいて、設定する2つのブロックのサイズを制御する。具体的には、ブロックサイズ補正部 502 は、勾配フラグ  $F (P)$  に応じて、位置  $P$  で表される候補方向に対して設定する2つのブロックのサイズを制御する。10

#### 【0078】

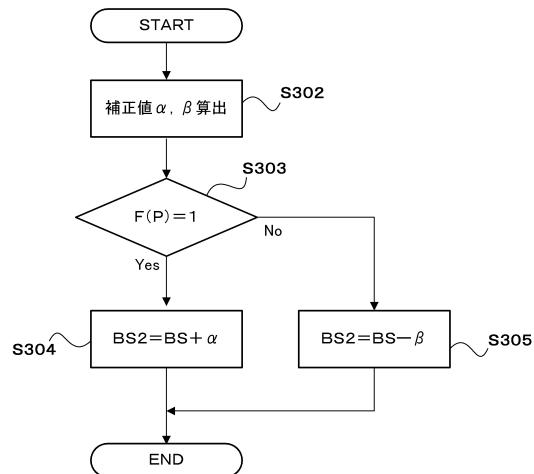

ブロックサイズ補正部 502 の動作の具体例について図 18 のフローチャートを用いて説明する。

まず、S302 で、ブロックサイズ補正部 502 が、補正值  $,$  を算出する。補正值  $$  は、ブロックサイズ BS を第 2 のサイズに変換する補正值である。補正值  $$  は、ブロックサイズ BS を第 1 のサイズに変換する補正值である。第 2 のサイズは、第 1 のサイズよりも大きい。補正值  $,$  は、ブロックサイズ BS の値に応じて決まる。例えば、ブロックサイズが  $X, Y, Z (X < Y < Z)$  の 3 種類の値のいずれかであるものとする。そして、第 1 のサイズが  $X$ 、第 2 のサイズが  $Z$  であるものとする。この場合、 $= Z - BS$ 、 $= BS - X$  により、 $$  と  $$  が算出される。例えば、 $BS = Y$  のとき、 $= Z - Y$ 、 $= Y - X$  となる。また、 $BS = Z$  のとき、 $= Z - Z = 0$ 、 $= Z - X$  となる。 $BS = X$  のとき、 $= Z - X = 0$ 、 $= X - X = 0$  となる。20

#### 【0079】

S303 で、ブロックサイズ補正部 502 が、勾配フラグ  $F (P) = 1$  か否かを判定する。 $F (P) = 1$  である場合には、S304 で、ブロックサイズ補正部 502 が、ブロックサイズ BS2 として第 2 のサイズを設定する。S304 では、BS に  $$  を加算することにより BS2 が算出される。そのため、 $BS = X, Y$  のときには、ブロックサイズが  $Z$  に大きくされる。 $BS = Z$  のときには、ブロックサイズはそのままとされる。 $F (P) = 0$  である場合には、S305 で、ブロックサイズ補正部 502 が、ブロックサイズ BS2 として第 1 のサイズを設定する。S305 では、BS から  $$  を減算することにより BS2 が算出される。即ち、 $BS = Y, Z$  のときには、ブロックサイズが  $X$  に小さくされる。 $BS = X$  のときには、ブロックサイズはそのままとされる。30

#### 【0080】

ブロックマッチング部 307 は、BS2 に基づいて、入力された複数の画素値からブロック内の画素値を選択し、ブロックマッチングを行う。具体的には、マッチング領域算出部 D301 から出力された画素値から、画素  $d (P)$  を中心とし、ブロックサイズが BS2 であるブロック内の画素値が選択される。また、マッチング領域算出部 U302 から出力された画素値から、画素  $u (P)$  を中心とし、ブロックサイズが BS2 であるブロック内の画素値が選択される。ブロックマッチングの方法は実施例 1 と同様のため、説明は省略する。40

#### 【0081】

以上述べたように、本実施例によれば、ブロックの設定位置である直線上（候補方向の直線上）の位置における、所定方向の位置の変化に対する画素値の変化の勾配に応じて、対応する候補方向に対して設定する  $n$  個のブロックのサイズが制御される。具体的には、勾配が大きいときよりも、勾配が小さいときのほうが、水平方向の長さが長くなるように、対応する候補方向に対して設定する  $n$  個のブロックのサイズが制御される。勾配が大きい場合には水平方向に対する角度が大きいエッジ部分である可能性が高く、勾配が小さい場合には水平方向に対する角度が小さいエッジ部分である可能性が高い。そのため、上記50

構成により、エッジ方向が上記角度の浅い方向である可能性の度合いと、エッジ方向が上記角度の深い方向である可能性の度合いとの両方をより精度良く算出することができ、エッジの方向をより精度良く判定することができる。

#### 【0082】

なお、本実施例では、候補方向毎に、複数のブロックのそれぞれについて勾配を算出し、算出した複数の勾配の代表値に基づいてブロックサイズを制御する構成としたが、この構成に限らない。例えば、候補方向毎に、1つのブロックの勾配を算出し、算出した1つの勾配に基づいてブロックサイズが制御されてもよい。また、本実施例では、1つの候補方向に対して設定する全てのブロック（ $n$ 個のブロックのそれぞれ）について勾配を算出する構成としたが、この構成に限らない。 $n$ 個のブロックのうちの一部のブロックについて勾配が算出されてもよい。例えば、実施例2のように1つの候補方向に対して3つのブロックが設定される場合には、3つのブロックのうちの1つまたは2つのブロックについて勾配が算出されてもよい。

なお、本実施例では、複数の勾配の代表値が、当該複数の勾配の最大値である場合の例を示したが、代表値はこれに限らない。例えば、代表値は、複数の勾配の最小値、最頻値、平均値などであってもよい。

なお、本実施例では、勾配に基づいて、ブロックサイズが第1のサイズまたは第2のサイズとされる場合の例を示したが、この構成に限らない。例えば、勾配が小さいほど水平方向の長さが長くなるように、ブロックサイズが連続的または段階的に変更されてもよい。

10

20

なお、本実施例では、算出した角度に基づいて決定されたブロックサイズを補正する例を示したが、その構成に限らない。例えば、角度の算出、及び、算出した角度に基づくブロックサイズの決定を行わずに、勾配のみに基づいてブロックサイズが決定されてもよい。

#### 【0083】

##### <実施例4>

以下、本発明の実施例4に係るエッジ方向判定装置、エッジ方向判定装置の制御方法について、図面を用いて説明する。実施例1～3では、所定方向（ブロックサイズBSを決定する際に用いる角度を定義するための方向；ブロックの長辺の方向）が水平方向である場合の例を示した。本実施例では、所定方向が垂直方向である場合の例を説明する。また、実施例1～3では、入力画像信号がインターレース画像信号である場合の例を示した。本実施例では、入力画像信号がプログレッシブ画像信号である場合の例を説明する。

30

本実施例に係る斜め検出部の構成は他の実施例と同様のため、その説明は省略する。

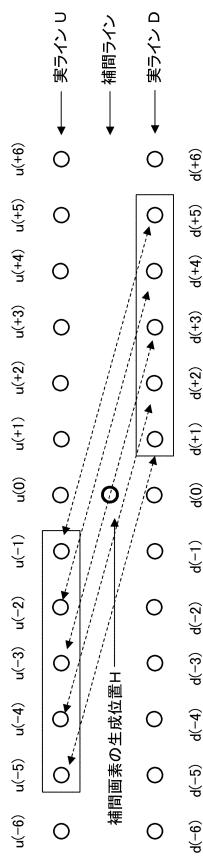

#### 【0084】

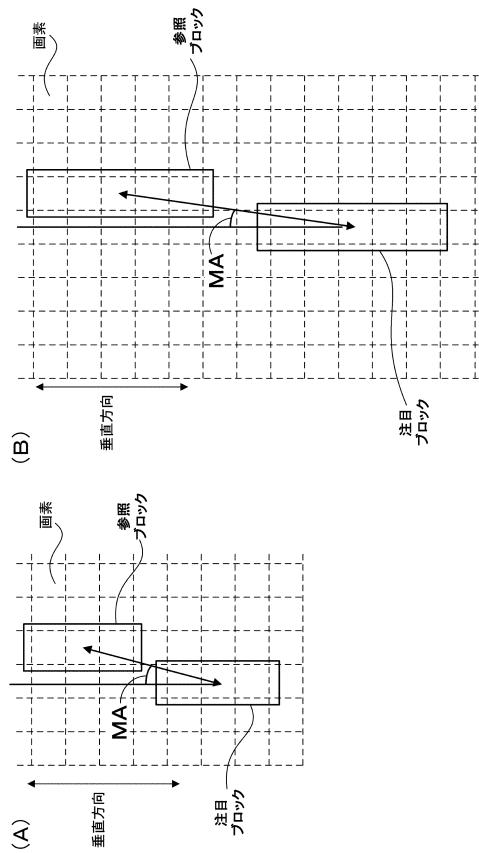

図19(A), (B)に、マッチング領域算出部で設定されるブロックの一例を示す。本実施例では、複数の候補方向のそれぞれについて、注目点を含むブロック（注目ブロック）と、注目点を含まないブロック（参照ブロック）とが設定され、注目ブロックと参照ブロックの間のブロックマッチングが行われるものとする。そして、候補方向毎のブロックマッチングの結果（SAD値）から、注目点におけるエッジの方向が判定される。

図19(A), (B)において、角度MAはマッチング角度である。本実施例では、マッチング角度MAは、候補方向の垂直方向に対する角度である。即ち、マッチング角度MAは、注目ブロックの中心位置と、参照ブロックの中心位置とを通る直線の、垂直方向に対する角度である。

40

図19(A)は、マッチング角度MAが大きい場合の例あり、図19(B)は、マッチング角度MAが小さい場合の例である。図19(A), (B)において、破線で囲まれた領域は画素を示す。図19(A), (B)に示すように、マッチング角度MAが大きいときのほうが、マッチング角度MAが小さいときよりも、ブロックの垂直方向の長さが長くなっている。具体的には、図19(A)では、ブロックサイズ（ブロックの垂直方向の長さ）は3画素分の長さとされており、図19(B)では、ブロックサイズは5画素分の長さとされている。なお、ブロックサイズは、他の実施例と同様の方法で決定される。なお

50

、ブロックサイズは、3画素分の長さ、5画素分の長さに限らない。

このように、ブロックサイズを制御することにより、他の実施例と同様に、エッジの方向を精度良く判定することが可能となる。

( 0 0 8 5 )

以上述べたように、本実施例では、垂直方向に対する角度が大きい候補方向について設定するブロックよりも、垂直方向に対する角度が小さい候補方向について設定するブロックのほうが、垂直方向の長さが長くなるように、ブロックのサイズが制御される。それにより、他の実施例と同様に、エッジの方向を精度良く判定することが可能となる。

なお、実施例1～4では、所定方向が水平方向の場合と、所定方向が垂直方向である場合とを例示したが、所定方向は斜め方向であってもよい。

## 【符号の説明】

[ 0 0 8 6 ]

- |               |                |

|---------------|----------------|

| 3 0 1 , 4 0 3 | マッチング領域算出部 D   |

| 3 0 2 , 4 0 4 | マッチング領域算出部 U   |

| 3 0 4 , 4 0 6 | 位置決定部          |

| 3 0 5 , 4 0 7 | マッチング角度決定部     |

| 3 0 6 , 4 0 8 | ブロックサイズ決定部     |

| 3 0 7 , 4 0 9 | ブロックマッチング部     |

| 3 0 8 , 4 1 0 | マッチング角度算出部     |

| 4 0 2         | マッチング領域算出部 2 D |

| 5 0 1         | 勾配算出部          |

| 5 0 2         | ブロックサイズ補正部     |

10

30

〔 四 1 〕

【 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

| マッチング角度MA                   | ブロックサイズBS |

|-----------------------------|-----------|

| $MA < A^\circ$              | X画素       |

| $A^\circ \leq MA < B^\circ$ | Y画素       |

| ...                         | ...       |

| $C^\circ \leq MA$           | Z画素       |

【図9】

【図8】

【図10】

| マッチング角度MA                    | ブロックサイズBS |

|------------------------------|-----------|

| $MA < 8^\circ$               | 15画素      |

| $8^\circ \leq MA < 20^\circ$ | 9画素       |

| $20^\circ \leq MA$           | 5画素       |

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 山岸 正治

東京都大田区下丸子3丁目30番2号 キヤノン株式会社 内

審査官 佐野 潤一

(56)参考文献 特開2009-212851(JP,A)

特開2008-263399(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 04 N 7 / 01

G 06 T 7 / 60