(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6071524号

(P6071524)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月13日(2017.1.13)

(51) Int.Cl.

F 1

**H01L 27/115 (2017.01)**

**H01L 21/336 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

H01L 27/10 434

H01L 29/78 371

請求項の数 11 (全 15 頁)

(21) 出願番号

特願2012-277254 (P2012-277254)

(22) 出願日

平成24年12月19日 (2012.12.19)

(65) 公開番号

特開2014-120735 (P2014-120735A)

(43) 公開日

平成26年6月30日 (2014.6.30)

審査請求日

平成27年9月14日 (2015.9.14)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100117787

弁理士 勝沼 宏仁

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100103263

弁理士 川崎 康

(74) 代理人 100107582

弁理士 関根 肇

(74) 代理人 100118843

弁理士 赤岡 明

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体領域と、

前記半導体領域上に設けられたシリコン酸化膜と、

前記シリコン酸化膜上に設けられた電荷蓄積膜と、

前記電荷蓄積膜上に設けられた水素拡散防止膜と、

前記水素拡散防止膜上に設けられたランタンアルミシリコン酸化膜と、

前記ランタンアルミシリコン酸化膜上に設けられた制御ゲート電極と、

前記制御ゲート電極上に設けられた水素放出膜と、

前記シリコン酸化膜、前記電荷蓄積膜、前記水素拡散防止膜、前記ランタンアルミシリコン酸化膜、および前記制御ゲート電極を含む積層構造の側面に設けられ、水素の拡散を防止する材料を含む側壁と、

を備えている不揮発性半導体記憶装置。

## 【請求項 2】

前記電荷蓄積膜は、浮遊ゲート電極である請求項1記載の不揮発性半導体記憶装置。

## 【請求項 3】

前記水素拡散防止膜および前記側壁は、密度が $2.6 \text{ g/cm}^3$ より高いシリコン窒化膜である請求項1または2記載の不揮発性半導体記憶装置。

## 【請求項 4】

前記水素拡散防止膜および前記側壁は、ボロンを含むシリコン窒化膜である請求項1ま

たは 2 記載の不揮発性半導体記憶装置。

**【請求項 5】**

前記水素拡散防止膜および側壁は、T i、Z r、H f、L aからなる群から選択された少なくとも 1 つの元素と、N i、M n、C r、Vからなる群から選択された少なくとも 1 つの元素を含む合金である請求項 1 乃至 4 のいずれかに記載の不揮発性半導体記憶装置。

**【請求項 6】**

前記水素放出膜は、密度が  $2.6 \text{ g / cm}^3$  以下のシリコン窒化膜である請求項 1 乃至 5 のいずれかに記載の不揮発性半導体記憶装置。

**【請求項 7】**

前記水素放出膜上に設けられた窒化シリコンを含む保護膜を更に備え、前記窒化シリコンは、シリコン S i と窒素 Nとの組成比を S i / N とすると、

$$0.7 < S i / N < 0.9$$

の条件を満たす請求項 1 乃至 6 のいずれかに記載の不揮発性半導体記憶装置。

**【請求項 8】**

前記水素放出膜上に設けられたシリコン窒化膜を含む保護膜を更に備え、前記シリコン窒化膜の空隙率 P は、前記半導体層の側で P > 0.175 であり、前記半導体層と反対の表面側 P < 0.3 である請求項 1 乃至 6 のいずれかに記載の不揮発性半導体記憶装置。

**【請求項 9】**

制御ゲート電極と電極間絶縁膜が交互に積層され、貫通孔を有する積層構造と、前記貫通孔内に設けられ前記貫通孔の延在する方向に延在する半導体領域と、前記半導体領域と前記積層構造との間に設けられたシリコン酸化膜と、前記シリコン酸化膜と前記積層構造との間に設けられた電荷蓄積膜と、前記電荷蓄積膜と前記積層構造との間に設けられたランタンアルミシリコン酸化膜と、前記積層構造の外周面に前記貫通孔の延在する方向に沿って設けられた水素放出膜と、を備えている不揮発性半導体記憶装置。

**【請求項 10】**

基板上に設けられ、第 1 制御ゲート電極と第 1 電極間絶縁膜が交互に積層され、第 1 貫通孔を有する第 1 積層構造と、

前記第 1 貫通孔内に設けられ前記第 1 貫通孔の延在する方向に延在する第 1 半導体領域と、

前記第 1 半導体領域と前記第 1 積層構造との間に設けられた第 1 シリコン酸化膜と、

前記第 1 シリコン酸化膜と前記第 1 積層構造との間に設けられた第 1 電荷蓄積膜と、

前記第 1 電荷蓄積膜と前記第 1 積層構造との間に設けられた第 1 ランタンアルミシリコン酸化膜と、

前記基板上に前記第 1 積層構造と離間して設けられ、第 2 制御ゲート電極と第 2 電極間絶縁膜が交互に積層され、第 2 貫通孔を有する第 2 積層構造と、

前記第 2 貫通孔内に設けられ前記第 2 貫通孔の延在する方向に延在する第 2 半導体領域と、

前記第 2 半導体領域と前記第 2 積層構造との間に設けられた第 2 シリコン酸化膜と、

前記第 2 シリコン酸化膜と前記第 2 積層構造との間に設けられた第 2 電荷蓄積膜と、

前記第 2 電荷蓄積膜と前記第 2 積層構造との間に設けられた第 2 ランタンアルミシリコン酸化膜と、

前記基板に設けられ、前記第 1 半導体領域と前記第 2 半導体領域を接続する接続部と、

前記第 1 積層構造と前記第 2 積層構造との間に設けられた水素放出膜と、

を備えている不揮発性半導体記憶装置。

**【請求項 11】**

前記水素放出膜は、密度が  $2.6 \text{ g / cm}^3$  以下のシリコン窒化膜である請求項 9 または 10 に記載の不揮発性半導体記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

10

20

30

40

50

**【0001】**

本発明の実施形態は、不揮発性半導体記憶装置に関する。

**【背景技術】****【0002】**

不揮発性半導体メモリの一種としてNAND型フラッシュメモリが知られており、NAND型フラッシュメモリのセル構造は、半導体層上に、第1絶縁膜、電荷蓄積膜、第2絶縁膜、および制御ゲート電極がこの順に積層された積層ゲート構造を有している。第1絶縁膜は、「トンネル絶縁膜」ともよばれる。第2絶縁膜は、電荷蓄積膜が多結晶シリコンからなる浮遊ゲート電極の場合は「ゲート間絶縁膜」とも呼ばれ、電荷蓄積膜が電荷を蓄積する絶縁膜からなる場合には「ブロック絶縁膜」と呼ばれる。

10

**【0003】**

従来、第1絶縁膜および第2絶縁膜にはシリコン酸化物もしくはシリコン酸素窒化物が用いられてきた。しかし、フラッシュメモリの微細化かつ大容量化に伴い、ロケット型セルではセル間干渉が顕著になる。このため、ロケット型セルの代わりに平面型のセル構造の検討がなされている。この平面型のセル構造の場合、カップリング比の確保し、かつ浮遊ゲート電極もしくは電荷蓄積膜と、制御ゲート電極との絶縁性を保つためには、第2絶縁膜として、従来のシリコン酸化物もしくはシリコン酸素窒化物では限界がある。このため、更に高い誘電率材料の使用が必要となっている。また第2絶縁膜として適切な材料として、高い誘電率、広いバンドギャップ、耐熱性の観点から、ランタンアルミシリコン酸化膜の適用が進められている。

20

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2009-54951号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかし、第2絶縁膜としては、リーク電流が低いだけでなく、耐圧が高いこと、電荷をトラップすることが可能な電荷トラップの量が少ないことが求められており、第2絶縁膜として用いる高誘電率材料の信頼性を上げることは重要である。また、第2絶縁膜の信頼性を確保するのと同時に、メモリセルそのものの信頼性を上げるために書き込み、消去による第1絶縁膜の劣化を抑制する必要がある。このように、メモリセルとして高い信頼性を有する不揮発性半導体記憶装置が求められている。

30

**【0006】**

本実施形態は、メモリセルとして高い信頼性を有する不揮発性半導体記憶装置を提供する。

**【課題を解決するための手段】****【0007】**

本実施形態の不揮発性半導体記憶装置は、半導体領域と、前記半導体領域上に設けられた第1絶縁膜と、前記第1絶縁膜上に設けられた電荷蓄積膜と、前記電荷蓄積膜上に設けられた水素拡散防止膜と、前記水素拡散防止膜上に設けられた第2絶縁膜と、前記第2絶縁膜上に設けられた制御ゲート電極と、前記制御ゲート電極上に設けられた水素放出膜と、前記第1絶縁膜、前記電荷蓄積膜、前記水素拡散防止膜、前記第2絶縁膜、および前記制御ゲート電極を含む積層構造の側面に設けられ、水素の拡散を防止する材料を含む側壁と、を備えていることを特徴とする。

40

**【図面の簡単な説明】****【0008】**

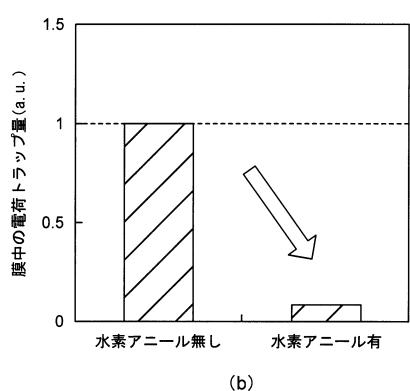

【図1】図1(a)、1(b)は、水素アニールを施した場合および施さない場合のランタンアルミシリコン酸化膜の絶縁破壊耐圧および膜中の電荷トラップ量を示す図。

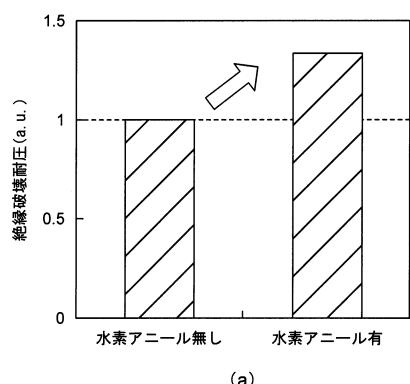

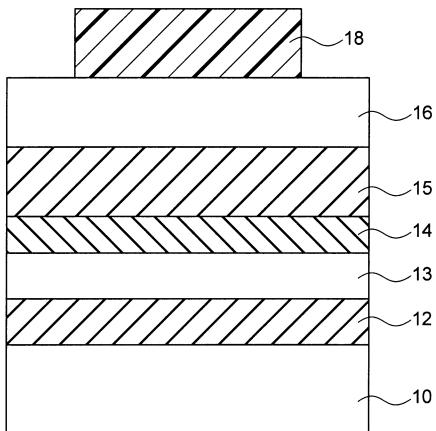

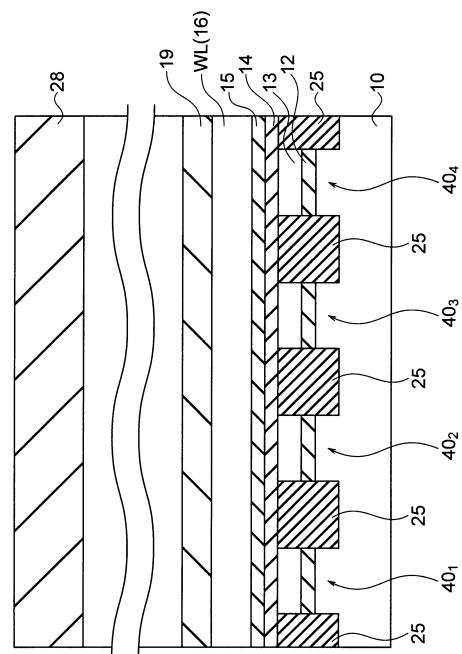

【図2】第1実施形態に係るメモリセルを示す断面図。

50

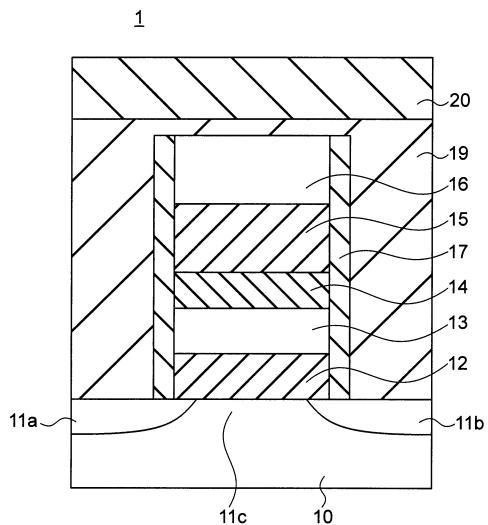

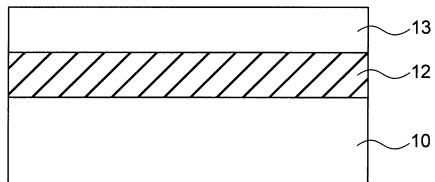

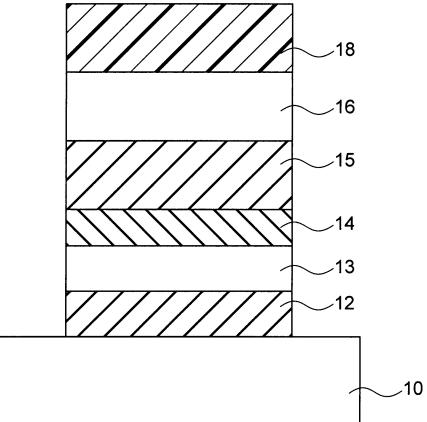

【図3】シリコン窒化膜が下のシリコン酸化膜へ及ぼす影響を調べるために用いた積層構造の断面図。

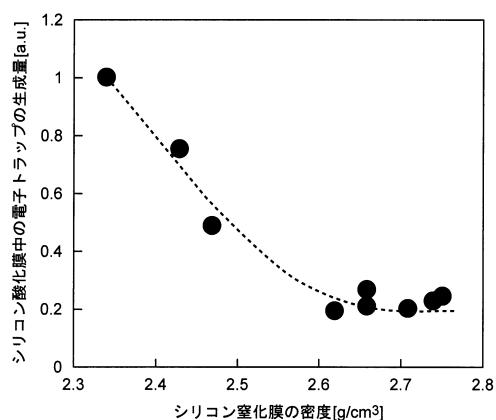

【図4】シリコン窒化膜の密度とシリコン酸化膜の劣化量との相関を示す図。

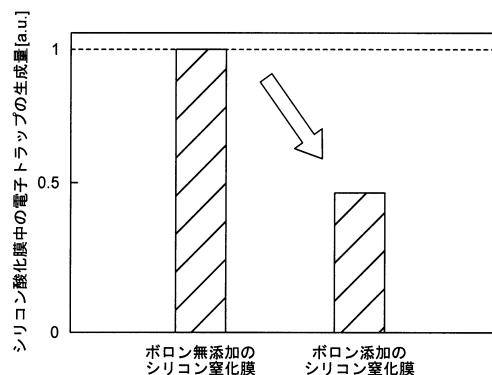

【図5】シリコン窒化膜にボロンを添加した際のシリコン酸化膜の劣化量を示す図。

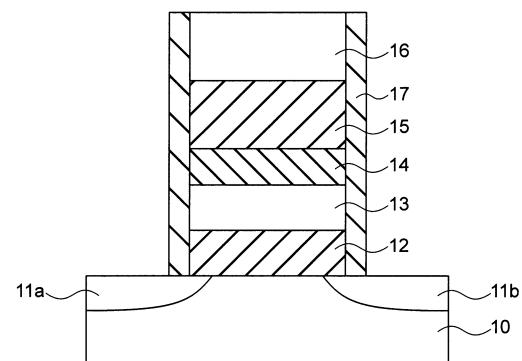

【図6】第1実施形態による不揮発性半導体記憶装置の製造方法を示す断面図。

【図7】第1実施形態による不揮発性半導体記憶装置の製造方法を示す断面図。

【図8】第1実施形態による不揮発性半導体記憶装置の製造方法を示す断面図。

【図9】第1実施形態による不揮発性半導体記憶装置の製造方法を示す断面図。

【図10】第1実施形態による不揮発性半導体記憶装置の製造方法を示す断面図。

【図11】第1実施形態による不揮発性半導体記憶装置の製造方法を示す断面図。

【図12】第1実施形態の一変形例による不揮発性半導体記憶装置を示す断面図。

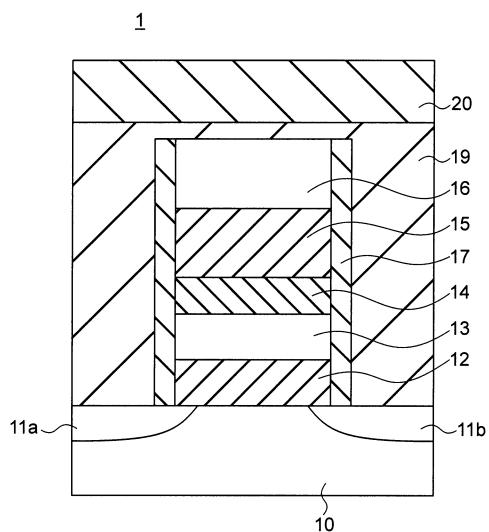

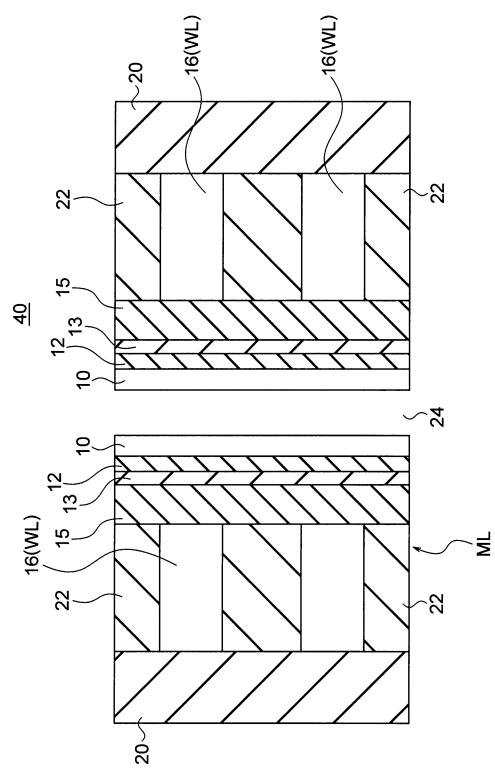

【図13】第2実施形態による不揮発性半導体記憶装置を示す断面図。

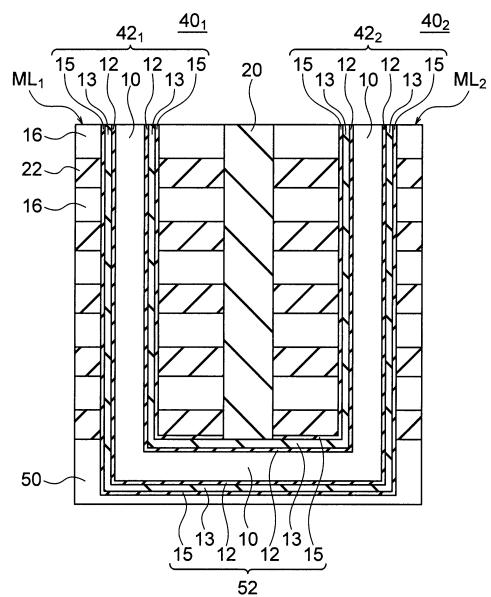

【図14】第3実施形態による不揮発性半導体記憶装置を示す断面図。

【発明を実施するための形態】

【0009】

本実施形態を説明する前に、本実施形態に至った経緯について説明する。

【0010】

水素アニールを施した場合および施さない場合のランタンアルミシリコン酸化膜（LaAlSiO膜）の絶縁破壊耐圧および電荷をトラップすることが可能な膜中の電荷トラップ量の変化を図1に示す。図1(a)、1(b)からわかるように、水素アニールを施すことにより、絶縁破壊耐圧が約35%程度高くなり、トラップ量も10分の1以下に減少する。この結果はランタンアルミシリコン酸化膜中の欠陥を水素で終端したためと考えられ、特にラジカル状態の水素が膜中に入ってくることで、より効率的に膜中の欠陥を終端することができると考えられる。ここで、ランタンアルミシリコン酸化膜中に一様に水素が入っていると仮定し、水素によって減少したランタンアルミシリコン酸化膜中の電荷トラップ量から計算される、ランタンアルミシリコン酸化膜中の水素の体積密度は $9.3 \times 10^{20}$ 個/cm<sup>3</sup>程度である。

【0011】

一方、ラジカル状態の水素がシリコン酸化膜からなるトンネル絶縁膜に入ると、シリコン酸化膜中のシリコンと水素の結合を切斷してしまうため、シリコン酸化膜を劣化させることが報告されている。そのため、メモリセルの信頼性を向上されるには、ゲート間絶縁膜であるランタンアルミシリコン酸化膜には水素を入れ、シリコン酸化膜からなるトンネル絶縁膜には水素が入らない構造にすることが必要である。

【0012】

そこで、本発明達は、高信頼なフラッシュメモリの構造として、以下のようないべく構造を考えた。このゲート構造は、制御ゲート電極の上部に水素を放出しやすい水素放出膜を有し、ゲート間絶縁膜であるランタンアルミシリコン膜と浮遊ゲート電極との間に水素をブロックし下への拡散を防ぐ水素ブロック膜、もしくは水素を吸収する水素吸収膜を有する。また、セルの周りから水素が拡散し、トンネル絶縁膜に入るのを抑制するために、制御ゲート電極、ゲート間絶縁膜、水素ブロック膜、浮遊ゲート電極、トンネル絶縁膜の側壁にも水素をブロックする層が設けられている。このような構造にすることで、トンネル絶縁膜の劣化を抑制しつつ、ゲート間絶縁膜の欠陥を水素で終端でき、書き込み、消去特性の改善、およびデータリテンションの劣化を抑制でき、メモリセル全体の信頼性の向上を可能にする。

【0013】

以下、図面を参照しつつ、実施形態について詳細に説明する。なお、以後の説明では、共通の構成に同一の符号を付すものとし、重複する説明は省略する。また、各図は模式図であり、その形状や寸法、比などは実際の装置と異なる個所があるが、実際の装置を製造する際は、以下の説明と公知の技術を参照して判断することができる。

【0014】

10

20

30

40

50

(第1実施形態)

第1実施形態による不揮発性半導体記憶装置(以下、記憶装置ともいう)について図2を参照して説明する。この第1実施形態の記憶装置は、少なくとも1個のメモリセルを有し、このメモリセルの断面を図2に示す。図2は、メモリセル1のチャネル長方向の断面を示す。この第1実施形態に係るメモリセル1は、電荷蓄積膜が浮遊ゲート電極であるFG(Floating Gate)型メモリセルである。このメモリセル1は、p型半導体層(半導体領域)10に離間して設けられたソース領域11aおよびドレイン領域11bと、ソース領域11aとドレイン領域11bとの間のp型半導体層10の領域(チャネル領域11c)上に設けられたトンネル絶縁膜12と、トンネル絶縁膜12上に設けられた電荷蓄積膜13と、電荷蓄積膜13上に設けられた水素拡散防止膜(水素プロック膜)14と、水素拡散防止膜14上に設けられたゲート間絶縁膜15と、ゲート間絶縁膜上に設けられた制御ゲート電極16と、を備えている。更に、トンネル絶縁膜12、電荷蓄積層13、ゲート間絶縁膜15、および制御ゲート電極16を有するゲート積層構造の側面に、ゲート側壁17が設けられている。また、制御ゲート電極16上には層間絶縁膜19が設けられている。なお、層間絶縁膜19上に水素放出膜20が形成されていることが好ましい。また、層間絶縁膜19は、上記ゲート積層構造およびゲート側壁17を覆うように設けられている。なお、本実施形態においては、トンネル絶縁膜12は例えばシリコン酸化膜であり、電荷蓄積膜13は例えば多結晶シリコン膜であり、ゲート間絶縁膜15は例えばランタンアルミシリコン酸化膜であり、水素拡散防止膜14、ゲート側壁17、および水素放出膜20は、水素をブロックする例えばシリコン窒化膜である。また、水素放出膜20は制御ゲート電極16上に直接に設けてよい。

【0015】

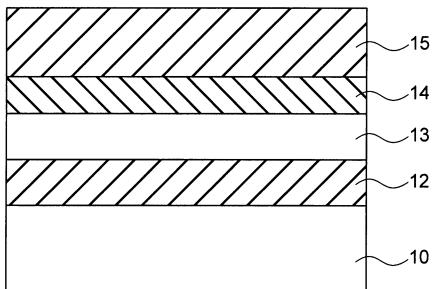

次に、水素拡散防止膜14、ゲート側壁17、および水素放出膜20に使用する好適なシリコン窒化膜について図3乃至図5を参照して説明する。まず、図3に示すように、シリコン半導体層30上にシリコン酸化膜32、ポリシリコン電極34、層間絶縁膜36、およびシリコン窒化膜38をこの順序で堆積した積層構造を作製する。この積層構造を窒素雰囲気下において400度20分のアーニールを行い、ポリシリコン電極34に電圧を印加することによりシリコン酸化膜32にストレスを印加したときの劣化量を調べた。ここで、シリコン酸化膜の劣化量とは、シリコン酸化膜にストレスを印加した際に膜中に生成される電子トラップ量を意味する。図4にシリコン窒化膜38の密度とシリコン酸化膜32の劣化量の相関図を示す。図4において、横軸はシリコン窒化膜38の密度を示し、縦軸はシリコン酸化膜32中に生成した電子トラップ量を示す。この電子トラップは、シリコン窒化膜38から拡散してくる水素が原因で生成されると考えられる。図4に示す結果から、シリコン窒化膜38の膜密度が $2.6 \text{ g/cm}^3$ 以下の場合は水素が多く放出され、シリコン酸化膜32の劣化が促進されることがわかる。また、シリコン窒化膜38の密度が $2.6 \text{ g/cm}^3$ より高い場合は、水素の放出が抑制され、シリコン酸化膜32の劣化も抑制されていることがわかる。

【0016】

のことから、図1に示す第1実施形態に係るメモリセル1の水素放出膜20としては密度が $2.6 \text{ g/cm}^3$ 以下のシリコン窒化膜を用いることが望ましい。この理由は、以下の通りである。第1実施形態に係るメモリセル1において、水素放出膜20から放出された水素は下方に拡散し、ゲート間絶縁膜15であるランタンアルミシリコン酸化膜中に入る。ここで、ランタンアルミシリコン酸化膜15中の欠陥(たとえば酸素空孔)を水素が終端することにより、ゲート間絶縁膜15の膜質を改善し、メモリセルの信頼性を向上させることができる。

【0017】

また、電荷蓄積膜13とゲート間絶縁膜15の間に設けられた水素拡散防止膜14は、高密度のシリコン窒化膜を用いる。ここで高密度とは $2.6 \text{ g/cm}^3$ より高い密度である。シリコン窒化膜からなる水素拡散防止膜14を高密度にすることによって、上方から拡散してきた水素をブロックし、トンネル絶縁膜12に入らないように防止することが可

能となり、メモリセルの信頼性を向上させることができる。

#### 【0018】

また、図3に示す積層構造のシリコン窒化膜38にボロン(B)を添加し、シリコン酸化膜32にストレスを印加した際のシリコン酸化膜32の劣化量について図5を参照して説明する。ここで、シリコン窒化膜38に添加されたボロンの量は約2at%である。図5からわかるように、シリコン窒化膜38にボロンを添加することにより、水素放出を抑制する効果があることがわかる。この効果は、ボロンを導入することで、B-N結合がシリコン窒化膜38の中の空隙表面にあるN-H結合を置換することによると考えられる。そのため、水素拡散防止膜14であるシリコン窒化膜も、ボロンを添加することによって、水素放出を抑制する効果があると考えられる。10

#### 【0019】

また、電荷蓄積膜13として、ボロンを添加したp型多結晶シリコンを用いる場合、熱工程によって、電荷蓄積膜13である多結晶シリコン膜中のボロンが抜けてしまい、電荷蓄積膜13の不純物濃度が薄くなってしまうことが問題となる。しかし、本実施形態のように、水素拡散防止膜14としてボロンが添加されたシリコン窒化膜を使うことにより、電荷蓄積膜13より上側にボロンが抜けることを抑制し、電荷蓄積膜13の多結晶シリコンの不純物濃度の低下を防ぐことができる。

#### 【0020】

本実施形態では、水素拡散防止膜14としてシリコン窒化膜を用いた。しかし、水素拡散防止膜14とし、水素を吸着する材料であるTi、Zr、Hf、Laの群から選択された少なくとも1つの元素と、Ni、Mn、Cr、Vの群から選択された少なくとも1つの元素とを含む合金を使用することによっても、トンネル絶縁膜12へ水素が拡散することを抑制できる。20

#### 【0021】

また、側壁17として、高密度シリコン窒化膜すなわち $2.6\text{ g/cm}^3$ より高い密度を有するシリコン窒化膜、もしくはボロンを添加したシリコン窒化膜を用いることによって、通常のシリコン酸化膜で作成された側壁に比べて、ゲート間絶縁膜15であるランタンアルミシリコン酸化膜へのシリコンの拡散が抑制でき、ランタンアルミシリコン酸化膜の組成を安定化することが可能であるという効果も得られる。

#### 【0022】

次に、第1実施形態による不揮発性半導体装置の製造方法について図6乃至図11を参考して説明する。図6乃至図11はチャネル長方向に沿う断面図である。

#### 【0023】

まず図6に示すように、シリコン層10上にトンネル絶縁膜12および電荷蓄積膜13を順次形成する。トンネル絶縁膜12は、シリコン層10を熱酸化することによって形成することができ、電荷蓄積膜13としては、例えば多結晶シリコンを用い、CVD(Chemical Vapor Deposition)法によって形成することができる。

#### 【0024】

続いて図7に示すように、電荷蓄積膜13上に、水素拡散防止膜14としてシリコン窒化膜を堆積する。このシリコン窒化膜14はプラズマCVD法、熱CVD法、ALD法(Atomic Layer Deposition)法、スパッタ法など公知の成膜技術を用いて形成することができる。その上にゲート間絶縁膜15としてランタンアルミシリコン酸化膜を堆積する。このランタンアルミシリコン酸化膜15はスパッタ法、CVD法、ALD法など公知の成膜技術を用いて形成することができる。また、水素拡散膜14上に堆積したシリコン酸化膜の上にランタンアルミ酸化膜を堆積し、たとえば窒素雰囲気中において950度で30秒の熱工程を施すことによっても、ランタンアルミシリコン酸化膜を形成することができる。なお、この熱工程はランタンアルミ酸化膜を堆積した直後でなくても良い。

#### 【0025】

続いて、図8に示すように、ゲート間絶縁膜15の上に制御ゲート電極16を形成し、制御ゲート電極16上にフォトレジストからなるゲート形状のレジストパターン18を形4050

成する。

**【0026】**

次に図9に示すように、レジストパターン18をマスクとし、反応性イオンエッティング(RIE)法を用いて、制御ゲート電極16、ゲート間絶縁膜15、水素拡散防止膜14、電荷蓄積膜13、およびトンネル絶縁膜12を順次エッティングすることによりパターニングし、トンネル絶縁膜12、電荷蓄積膜13、水素拡散防止膜14、ゲート間絶縁膜15、および制御ゲート電極からなるゲート積層構造を形成する。その後、レジストパターン18を除去する。

**【0027】**

次に図10に示すように、パターニングされた制御ゲート電極16、ゲート間絶縁膜15、水素拡散防止膜14、電荷蓄積膜13、およびトンネル絶縁膜12の側面に、窒化シリコンからなる側壁17を形成する。このとき、制御ゲート電極16上にも窒化シリコンが形成されるが、制御ゲート電極16上の窒化シリコンはRIEによって除去する。

10

**【0028】**

続いて、上記ゲート積層構造および側壁17をマスクとしてn型不純物イオンの注入を行い、シリコン半導体層にソース領域11aおよびドレイン領域11bを形成する。

**【0029】**

次に図11に示すように、上記ゲート積層構造および側壁17を覆うように、層間絶縁膜19を形成する。その後、層間絶縁膜19上に水素放出膜20として、低密度なシリコン窒化膜20を堆積する。このシリコン窒化膜はプラズマCVD法、熱CVD法、ALD法)、スパッタ法など公知の成膜技術を用いて形成することができる。この水素放出膜20を堆積したのち、例えば窒素雰囲気中において400度で20分の熱工程を加える。またこの工程は水素放出膜20を堆積した直後でなくともよい。このようにして、第1実施形態に係るメモリセル1を形成することができる。

20

**【0030】**

以上説明したように、第1実施形態によれば、電荷蓄積膜とゲート間絶縁膜との間に水素拡散防止膜を設けたことにより、トンネル絶縁膜へ水素が拡散することを抑制することが可能となり、トンネル絶縁膜が劣化するのを防止することができ、メモリセルの信頼性を向上させることができるとなる。

**【0031】**

30

また、制御ゲート電極上に水素放出膜を設けたことにより、ランタンアルミシリコン酸化膜からなるゲート間絶縁膜の膜質を改善し、メモリセルの信頼性を向上させることができる。

**【0032】**

なお、第1実施形態に係るメモリセル1を複数個、直列に接続してNANDストリングを形成し、第1実施形態の不揮発性半導体記憶装置を周知のNAND型フラッシュメモリとすることができる。一般にNAND型フラッシュメモリは複数個のNANDストリングを備えている。また、1つのNANDストリングにおいて、隣接するメモリセル1は、ソース領域またはドレイン領域を共有する構造を有している。

**【0033】**

40

(変形例)

第1実施形態の一変形例による記憶装置について図12を参照して説明する。この変形例の記憶装置は、マトリクス状に配列された複数のNANDストリングを有し、各NANDストリングは、第1実施形態で説明したメモリセルが直列に接続された構成を有している。同一行に配置された複数のNANDストリングにおいては、同じ行に位置する複数のメモリセルの制御ゲート電極が同一のワード線WLを構成する。すなわち、同じ行に位置する複数のメモリセルの制御ゲート電極16は共通に接続されてワード線WLを構成する。

**【0034】**

図12はこの変形例の記憶装置の、ワード線WL方向に沿って切断した断面図である。

50

この変形例の記憶装置においては、メモリセルは、平面型のセル構造を有している。なお、図12においては、4個のNANDストリング $40_1 \sim 40_4$ が示されており、これらのNANDストリングはそれぞれ、STI(Shallow Trench Isolation)25によって素子分離されている。各NANDストリングを構成するメモリセルは、トンネル絶縁膜12と、浮遊ゲート電極13と、水素拡散防止膜14と、ゲート間絶縁膜15と、制御ゲート電極16と、を備えている。水素拡散防止膜14およびゲート間絶縁膜15は制御ゲート電極16とともに、ワード線WL方向に延在している。NANDストリング $40_1 \sim 40_4$ を覆うように層間絶縁膜19が設けられる。この層間絶縁膜19上に図示しない配線層が設けられる。この配線上に、保護膜28として、シリコン窒化膜が設けられる。

## 【0035】

10

この保護膜28となるシリコン窒化膜は、外部からの水などに対するバリア性を保ちつつ、かつ膜剥がれを起こさせないために内部応力を小さくする必要がある。

## 【0036】

本発明者等は、周知の堆積法で作成されたシリコン窒化膜の内部応力 $\sigma$ が、シリコン窒化膜を構成するSiとNの元素組成比 $x$ (=Si/N)と、膜密度との関数としてほぼ以下の(1)式で表されることを見出した。

## 【0037】

$$(1 - P - p_c) \quad (1)$$

上記式は、パーコレーション理論に基づいて導かれたものであり、Pは空隙率を表し、 $p_c$ は浸透閾値であって $p_c = 0.55 \pm 0.05$ と表され、 $\alpha$ は臨界指数であって $\alpha = 3.55 \pm 0.45$ と表される。空隙率Pは実際の膜密度 $\rho$ と、組成比xにおける空隙が無い場合の密度 $\rho_0(x)$ とを用いて、以下の(2)式で表される。

20

## 【0038】

$$P = 1 - \frac{1}{\rho_0(x)} \quad (2)$$

そして、 $\rho_0(x)$ は、以下の(3)式で表される。

## 【0039】

$$\rho_0(x) = s_i \times (b + a \times (1 - b) / (x + a)) \quad (3)$$

ここで、 $s_i$ はSi結晶の密度(g/cm<sup>3</sup>)、a、bはSiとNの各原子量と、常温、常圧下におけるSiと窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)の各結晶の密度から求められるパラメータであって、a=6.43、b=3.21である。

30

## 【0040】

上記(1)式からわかるように、シリコン窒化膜の内部応力を小さくするためには空隙率Pを大きくすれば良い。

## 【0041】

本発明者等は、外部からの水などに対するバリア性についても検討を行い、一般に空隙率Pによってシリコン窒化膜のバリア性を記述できることを見出した。この関係性から、バリア性を高めるには空隙率Pを小さくすれば良い。

## 【0042】

以上のことより、保護膜28として用いられるシリコン窒化膜は、シリコン窒化膜20の表面側の方が半導体層10側よりも空隙率Pが小さいことが望ましく、組成比xが以下の条件

$$0.7 < x < 0.9$$

を満たすことが望ましい。また、空隙率Pはシリコン窒化膜の表面側で0.3よりも小さく、半導体層10の側で0.175よりも大きいことが保護膜として好ましいことが本発明者等の知見によりわかった。

40

## 【0043】

なお、この変形例においては、NANDストリングを構成するメモリセルは第1実施形態で説明したメモリセルであったが、水素拡散防止膜14を設けない周知のメモリセルの場合でも、空隙率Pが上記条件を満たすシリコン窒化膜を保護膜として用いれば、外部からの水などに対するバリア性を保ちつつ、かつ膜剥がれが生じるのを防止することができ

50

る。

【0044】

また、この変形例による不揮発性半導体記憶装置も、第1実施形態と同様の効果を得ることができる。

【0045】

なお、この変形例において、第1実施形態で説明した水素放出膜20を層間絶縁膜19上に設けてもよい。

【0046】

また、第1実施形態およびその変形例においては、メモリセルの電荷蓄積膜13は浮遊ゲート電極であったが、電荷をトラップする絶縁体からなる電荷トラップ膜であってよい。10

【0047】

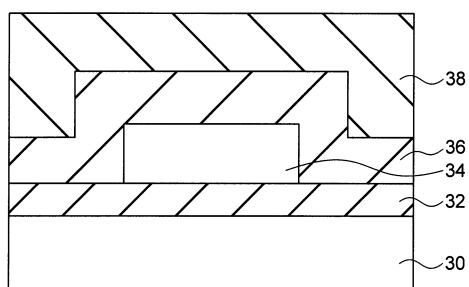

(第2実施形態)

第2実施形態による不揮発性半導体記憶装置について図13を参照して説明する。図13は、第2実施形態の不揮発性半導体記憶装置に係るメモリセル積層構造40の断面図である。このメモリセル積層構造40が1つのNANDストリングを構成する。この不揮発性半導体記憶装置は、3次元積層メモリであって、制御ゲート電極膜16と電極間絶縁膜22が交互に積層された積層構造MLを有している。この積層構造MLの中央部に、積層構造MLを貫通する貫通孔24が設けられている。貫通孔24内に、貫通孔24の延在する方向に延在する円筒形状の半導体層(半導体領域)10が設けられ、この半導体層10と積層構造MLとの間に、貫通孔24の延在する方向に延在する円筒形状のトンネル絶縁膜12が設けられている。このトンネル絶縁膜12と積層構造MLとの間に、貫通孔24の延在する方向に延在する円筒形状の電荷蓄積膜13が設けられている。この電荷蓄積膜13と積層構造MLとの間に、貫通孔24の延在する方向に延在する円筒形状の絶縁膜15が設けられている。絶縁膜15の外周は積層構造MLの内周に接している。そして、積層構造MLの外周を覆うように水素放出膜20が設けられている。20

【0048】

本実施形態においては、積層構造MLの内壁を覆うように円筒形状のゲート間絶縁膜15が設けられ、ゲート間絶縁膜15の内壁を覆うように円筒形状の電荷蓄積膜13が設けられている。電荷蓄積膜13の内壁を覆うように円筒形状のトンネル絶縁膜12が設けられ、トンネル絶縁膜12の内壁を覆うように円筒形状の半導体層10が設けられている、なお、半導体層10は円筒形状でなく、円柱形状であってもよい。この場合、図13に示す貫通孔24は、半導体層10で埋め込まれた構成となる。30

【0049】

トンネル絶縁膜12としては、シリコン酸化膜の他に、他の材料を用いることができる。例えば、ONO(Oxide-Nitride-Oxide)構造のトンネル絶縁膜を用いることができる。ONO構造を用いた場合は、書き込みおよび消去特性の向上が期待できる。また、ONOO構造を2個さらに積層したONONO(Oxide-Nitride-Oxide-Nitride-Oxide)構造、Siドット層をN層の代わりに挿入したOSO(Oxide-Silicon-Oxide)構造、OSOSO(Oxide-Silicon-Oxide-Silicon-Oxide)構造を用いることも可能である。ONONO構造、OSO構造、またはOSOSO構造を用いた場合は、ONO構造以上に書き込みおよび消去特性の向上が期待できる。これは、電荷蓄積膜側に蓄積膜からの電子の放出を補助するバンド構造が出来るために、正孔の注入に加えて電子放出という形で消去することになり、消去の高速化が図れることによる。なお、第1実施形態においても、トンネル絶縁膜12として、第2実施形態と同様に、ONO(Oxide-Nitride-Oxide)構造、ONONO構造、OSO構造、またはOSOSO構造のトンネル絶縁膜を用いることができる。40

【0050】

電荷蓄積膜13としては、シリコンリッチな窒化シリコンが用いられる。シリコンリッチな窒化シリコンとは、窒化シリコンをSi<sub>x</sub>Nと表したとき、xが0.75よりも大きいことを意味する。50

**【 0 0 5 1 】**

絶縁膜 15 としては、ランタンアルミシリコン酸化膜が用いられる。また、制御ゲート電極 16 としては、 $n^+$  ポリシリコンが用いられる。電極間絶縁膜 22 としては、TEOS (Tetra Ethyl Ortho Silicate) が用いられる。

**【 0 0 5 2 】**

また、半導体層 10 としては、例えば、アモルファスシリコンを結晶化させたシリコン層が用いられる。

**【 0 0 5 3 】**

水素放出膜 20 は、第1実施形態で説明した水素放出膜 20 と同じ材料が用いられる。

また水素放出膜 20 は、積層構造 ML の外表面を全て覆う必要はなく、貫通孔 24 の延在する方向に沿って設けられていればよい。 10

**【 0 0 5 4 】**

この第2実施形態も、第1実施形態と同様に、ランタンアルミシリコン酸化膜からなるゲート間絶縁膜の膜質を改善し、メモリセルの信頼性を向上させることができる。また、電荷蓄積膜として、シリコンリッチなシリコン窒化膜が用いられるため、高密度のシリコン窒素膜となり、絶縁膜 15 から拡散してきた水素をブロックし、トンネル絶縁膜 12 に入らないように防止することが可能となり、メモリセルの信頼性を向上させることができる。

**【 0 0 5 5 】****( 第3実施形態 )**

20

第3実施形態による不揮発性半導体記憶装置について図14を参照して説明する。図14は、第3実施形態の不揮発性半導体記憶装置の断面図である。この不揮発性半導体記憶装置は、3次元積層メモリであって、第2実施形態で説明したメモリセル積層構造 40<sub>1</sub>、40<sub>2</sub> が2個、基板 50 上に離間して設けられ、これら2つのメモリセル積層構造 40<sub>1</sub>、40<sub>2</sub> が基板 50 に設けられた接続部 40<sub>3</sub> を介して接続され、1つのNANDストリングを構成する。

**【 0 0 5 6 】**

各メモリセル積層構造 40<sub>i</sub> ( $i = 1, 2$ ) は、制御ゲート電極膜 16 と電極間絶縁膜 22 が交互に積層された積層構造 ML<sub>i</sub> を有している。各積層構造 ML<sub>i</sub> ( $i = 1, 2$ ) の中央部に、積層構造 ML<sub>i</sub> を貫通するピラー 42<sub>i</sub> ( $i = 1, 2$ ) が設けられている。各ピラー 42<sub>i</sub> ( $i = 1, 2$ ) は、円柱形状の半導体層 10 と、積層構造 ML<sub>i</sub> と半導体層 10 との間に設けられた円筒形状のトンネル絶縁膜 12 と、積層構造 ML<sub>i</sub> とトンネル絶縁膜 12 との間に設けられた円筒形状の電荷蓄積膜 13 と、積層構造 ML<sub>i</sub> と電荷蓄積膜 13 との間に設けられた円筒形状の絶縁膜 15 と、を備えている。 30

**【 0 0 5 7 】**

また、接続部 52 は、円柱形状の半導体層 10 と、この半導体層 10 の外表面を覆う円筒形状のトンネル絶縁膜 12 と、トンネル絶縁膜 12 の外表面を覆う円筒形状の電荷蓄積膜 13 と、電荷蓄積膜 13 の外表面を覆う円筒形状の絶縁膜 15 と、を備えている。

**【 0 0 5 8 】**

そして、本実施形態においては、2つのメモリセル積層構造 40<sub>1</sub>、40<sub>2</sub> 間に水素放出膜 20 が設けられている。 40

**【 0 0 5 9 】**

この第3実施形態も第2実施形態と同様に、ランタンアルミシリコン酸化膜からなるゲート間絶縁膜の膜質を改善し、メモリセルの信頼性を向上させることができる。また、電荷蓄積膜として、シリコンリッチなシリコン窒化膜が用いられるため、高密度のシリコン窒素膜となり、絶縁膜 15 から拡散してきた水素をブロックし、トンネル絶縁膜 12 に入らないように防止することが可能となり、メモリセルの信頼性を向上させることができる。

**【 0 0 6 0 】**

以上説明したように、各実施形態によれば、絶縁膜 15 の膜中の欠陥を低減し、絶縁破

50

壊耐圧を改善することにより、メモリセルの書き込み、消去の耐圧、書き込み飽和、消去飽和の改善を可能とすることができる。また、トンネル絶縁膜の劣化を抑制することによりデータ保持特性の劣化を抑制することが可能となり、メモリセルの信頼性の向上を図ることができる。

#### 【0061】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これらの実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

10

#### 【符号の説明】

#### 【0062】

- 1 メモリセル

- 1 0 半導体層（半導体領域）

- 1 1 a ソース領域

- 1 1 b ドレイン領域

- 1 2 トンネル絶縁膜

- 1 3 電荷蓄積膜

- 1 4 水素拡散防止膜

- 1 5 ゲート間絶縁膜

- 1 6 制御ゲート電極

- 1 7 側壁

- 1 8 フォトレジスト

- 1 9 層間絶縁膜

- 2 0 水素放出膜

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 平野 泉

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 三谷 祐一郎

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 宮田 正靖

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 中崎 靖

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 加藤 弘一

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 松下 大介

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 高島 章

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 諸田 美砂子

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 加藤 俊哉

(56)参考文献 特開2000-353757(JP,A)

特開2007-305966(JP,A)

特開2011-187794(JP,A)

特開2010-182963(JP,A)

特開平07-321237(JP,A)

特開2008-177343(JP,A)

特開2011-071334(JP,A)

特開2003-243625(JP,A)

特開2007-184323(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 21/336

H01L 27/115

H01L 29/788

H01L 29/792