(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4453463号

(P4453463)

(45) 発行日 平成22年4月21日(2010.4.21)

(24) 登録日 平成22年2月12日(2010.2.12)

(51) Int.Cl.

H03K 4/06 (2006.01)

H03F 3/217 (2006.01)

F 1

H03K 4/06

H03F 3/217

Z

請求項の数 4 (全 9 頁)

(21) 出願番号 特願2004-197384 (P2004-197384)

(22) 出願日 平成16年7月2日 (2004.7.2)

(65) 公開番号 特開2006-20177 (P2006-20177A)

(43) 公開日 平成18年1月19日 (2006.1.19)

審査請求日 平成19年5月31日 (2007.5.31)

(73) 特許権者 000004075

ヤマハ株式会社

静岡県浜松市中区中沢町10番1号

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(72) 発明者 辻 信昭

静岡県浜松市中沢町10番1号 ヤマハ株

式会社内

審査官 宮島 郁美

最終頁に続く

(54) 【発明の名称】三角波生成回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号をパルス幅変調して得られるパルス幅変調出力をスイッチング増幅するスイッチング増幅段を備えたD級増幅器において使用される三角波生成回路であって、

前記スイッチング増幅段の正電源電圧に比例した第1の定電流を出力する第1の定電流手段と、

前記スイッチング増幅段の負電源電圧に比例した第2の定電流を出力する第2の定電流手段と、

高インピーダンス素子をもって第1および第2の定電流を周期的かつ交互に選択する定電流選択手段と、

選択された定電流により充電される容量を増幅器の入力端および出力端間に介挿してなり積分出力を三角波として出力する第1の積分手段と、

第1の積分手段の出力を積分し三角波の位相補正指示として第1の積分手段の入力端に負帰還する第2の積分手段とを備えたことを特徴とする三角波生成回路。

## 【請求項 2】

前記第1および第2の定電流に比例した成分を生成し、生成した成分を重ね合わせて重畠成分を生成し、この重畠成分をオフセット指示として前記第1の積分手段の入力端に対し出力するオフセット指示手段を備えたことを特徴とする請求項1記載の三角波生成回路。

## 【請求項 3】

10

20

前記オフセット指示手段は、第1の定電流に比例した第3の定電流を生成する第3の定電流手段と、

第2の定電流に比例した第4の定電流を生成する第4の定電流手段とを備え、第3の定電流手段および第4の定電流手段を直列接続し、その接続端を前記第2の積分手段の入力端に接続したことを特徴とする請求項2記載の三角波生成回路。

#### 【請求項4】

前記第1および第2の定電流手段は、正電源電圧および負電源電圧が印加される抵抗回路と、この抵抗回路と同一の電流を発生するカレントミラー回路とからなり、前記定電流選択手段は、前記カレントミラー回路に配置され、外部から供給されるクロックパルスをゲート入力とする電界効果トランジスタからなることを特徴とする請求項1ないし請求項3記載の三角波生成回路。10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、主としてオーディオ信号の電力増幅に用いられるD級増幅器に係り、特にアナログオーディオ信号をパルス信号に変換する際に用いられる三角波を生成する技術に関する。

##### 【背景技術】

##### 【0002】

従来、安定化電源を用いずに電源回路規模の簡素化を図ったD級増幅器において、アナログオーディオ信号をパルス信号に変換する際に用いられる三角波を制御し、電源電圧の変動に追従して三角波の波高を変動することにより、増幅利得の変動を抑止する技術がある（特許文献1参照）。20

##### 【0003】

図4は、この種の従来の三角波生成回路を示す回路図である。この図において、符号21は基準クロックパルスCKが入力される端子である。22はデジタル位相比較回路であり、基準入力端INへ入力されるクロックパルスCKの位相と比較入力端REFの信号NFBの位相を比較し、比較結果に従って出力端UPまたは出力端DWから”H”レベルの信号を出力する。23はループフィルタであり、位相比較回路22の出力をアナログ信号PLLCに変換して出力する。24はコンデンサ25、26および抵抗27から構成され、ループフィルタ23とでローパスフィルタを構成し、ループフィルタ23の出力の高周波成分を除去する。30

##### 【0004】

30は演算増幅器であり、その非反転入力端ヘループフィルタ23の出力PLLCが入力され、反転入力端がFET（電界効果トランジスタ）32のソースに接続され、その出力端がFET32のゲートに接続されている。また、FET32のソースは抵抗31を介して接地され、ドレンは負荷回路33を介して負電源（-5V）に接続されている。負荷回路33はFET32の負荷となる回路であり、1個のFETによって構成されている。上記演算増幅器30、FET32および抵抗31は、負荷回路33を流れる電流を、ループフィルタ23の出力PLLCのレベルに応じて制御する回路である。40

##### 【0005】

34、35は定電流回路であり、その電流値は負荷回路33を流れる電流によって制御され、負荷回路33と同一の電流が流れる。36、37はスイッチ素子であり、信号NFBによってオン／オフ制御される。すなわち、信号NFBが”L”レベルの時はスイッチ素子36がオン、37がオフとなり、”H”レベルの時はスイッチ素子36がオフ、37がオンとなる。39は演算増幅器であり、その非反転入力端は接地され、反転入力端はスイッチ素子36、37の接続点に接続され、出力端が出力端子46に接続されている。40は演算増幅器39の反転入力端および出力端間に介挿されたコンデンサである。そして、上記演算増幅器39およびコンデンサ40によって積分回路が構成されている。

##### 【0006】

50

4 1 は比較回路であり、その反転入力端に演算増幅器 3 9 の出力が入力されている。非反転入力端には、電源電圧 V P X を抵抗 R 1 , R 2 によって分圧した電圧が入力されている。4 2 も比較回路であり、その反転入力端に演算増幅器 3 9 の出力が入力され、非反転入力端には、電源電圧 V M X を抵抗 R 3 , R 4 によって分圧した電圧が入力されている。抵抗 R 1 , R 3 の抵抗値は同一であり、また、抵抗 R 2 , R 4 の抵抗値も同一である。

## 【 0 0 0 7 】

そして、比較回路 4 1 出力が NAND ドア 4 4 の一方の入力端へ入力され、比較回路 4 2 の出力がインバータ 4 3 を介して NAND ドア 4 5 の一方の入力端へ入力されている。NAND ドア 4 4 、 4 5 は R S ( セット / リセット ) フリップフロップを構成しており、その出力が前述した信号 N F B としてスイッチ素子 3 6 、 3 7 および位相比較回路 2 2 へ出力される。

10

## 【 0 0 0 8 】

上述した構成をもって、この三角波生成回路は P L L ( フェイズロックループ ) 構成をとる。そして比較回路 4 1 , 4 2 の各非反転入力端へは、数 1 、数 2 なる電圧が入力される。ここで、 V P X , V M X は電源電圧、 a は正の定数であり、数 3 に示されるようになる。なお、 R 8 2 ~ R 8 4 はそれぞれ抵抗 R 2 ~ R 4 の抵抗値である。

## 【 0 0 0 9 】

## 【 数 1 】

$$V1 = VPX/a$$

20

## 【 数 2 】

$$V2 = VMX/a$$

## 【 数 3 】

$$\begin{aligned} a &= R82/(R81+R82) \\ &= R84/(R83+R84) \end{aligned}$$

30

## 【 0 0 1 0 】

これにより、出力端子 4 6 から出力される三角波の最大値 V P 、最小値 V M は各々上記電圧 V 1 、 V 2 となり、この結果、上記 (1) 式の利得 G は数 4 のようになる。すなわち利得 G は、電源電圧 V P X 、 V M X に影響されない値となって、電源電圧 V P X 、 V M X が変動しても利得 G が変動することはない。

## 【 0 0 1 1 】

## 【 数 4 】

$$\begin{aligned} G &= (VPX - VMX)/(VP - VM) \\ &= (VPX - VMX)/(VPX/a - VMX/a) \\ &= a \end{aligned}$$

40

## 【 0 0 1 2 】

また従来、 P L L 回路を用いずに三角波を生成する回路も提供されている（特許文献 2 参照）。同文献記載の三角波生成回路では、電圧 + V , - V の矩形波を交互に発生し、この矩形波を積分回路により積分して三角波を生成する。積分回路の出力端と入力端の間に積分器と反転増幅器を直装してなる閉ループを構成する。この積分器により三角波を積分してオフセット電圧を生成し、このオフセット電圧を反転増幅器により前記の積分回路の

50

入力端に負帰還することにより、正負対象の三角波を得るものである。

【特許文献 1】特開 2004 - 7324 号公報

【特許文献 2】特開平 1 - 318424 号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

しかしながら、特許文献 1 に記載される三角波生成回路にあっては、PLL 回路を用いているため、安定して位相固定を行えるように設計上留意しなければならず、その位相固定動作の安定性を高めようとすると、ループフィルタの回路構成が大規模化してしまう問題がある。またジッタが多くなって D 級増幅器の出力波形に歪を生じる問題がある。

10

【0014】

一方、特許文献 2 に記載される三角波生成回路にあっては、PLL 回路を用いないから回路規模は簡素化できるが、オペアンプを 2 段直装してなる閉ループを用いるため、その安定動作を得るために設計上の困難性を伴う。また電源電圧 V<sub>PX</sub> と V<sub>MX</sub> の変動に追従できないため、安定化電源を用いない D 級増幅器に適用すると利得が不安定になる問題がある。

【0015】

本発明は、このような事情に鑑みてなされたもので、その目的は、主としてオーディオ信号の電力増幅に用いられる D 級増幅器において、電源電圧の変動に対処して増幅利得のロバスト性を確保しつつ、PLL 回路を不要として三角波生成回路の回路規模を簡素化できる技術を提供することにある。

20

【課題を解決するための手段】

【0016】

上述した課題を解決するために、請求項 1 記載の発明は、入力信号をパルス幅変調して得られるパルス幅変調出力をスイッチング増幅するスイッチング増幅段を備えた D 級増幅器において 使用される三角波生成回路であって、前記スイッチング増幅段の正電源電圧に比例した第 1 の定電流を出力する第 1 の定電流手段と、前記スイッチング増幅段の負電源電圧に比例した第 2 の定電流を出力する第 2 の定電流手段と、高インピーダンス素子をもって第 1 および第 2 の定電流を周期的かつ交互に選択する定電流選択手段と、選択された定電流により充電される容量を増幅器の入力端および出力端間に介挿してなり積分出力を三角波として出力する第 1 の積分手段と、第 1 の積分手段の出力を積分し三角波の位相補正指示として第 1 の積分手段の入力端に負帰還する第 2 の積分手段とを備えたことを特徴とする。

30

【0017】

また、請求項 2 記載の発明は、請求項 1 記載の三角波生成回路において、前記第 1 および第 2 の定電流に比例した成分を生成し、生成した成分を重ね合わせて重畠成分を生成し、この重畠成分をオフセット指示として前記第 1 の積分手段の入力端に対し出力するオフセット指示手段を備えたことを特徴とする。

【0018】

また請求項 3 記載の発明は、請求項 2 記載の三角波生成回路において、オフセット指示手段として、第 1 の定電流に比例した第 3 の定電流を生成する第 3 の定電流手段と、第 2 の定電流に比例した第 4 の定電流を生成する第 4 の定電流手段を備え、第 3 の定電流手段および第 4 の定電流手段を直列接続し、その接続端を前記第 2 の積分手段の入力端に接続したことを特徴とする。

40

【0019】

また請求項 4 記載の三角波生成回路は、請求項 1 ないし請求項 3 記載の三角波生成回路について、前記第 1 および第 2 の定電流手段は、正電源電圧および負電源電圧が印加される抵抗回路と、この抵抗回路と同一の電流を発生するカレントミラー回路とからなり、前記定電流選択手段は、前記カレントミラー回路に配置され、外部から供給されるクロックパルスをゲート入力とする電界効果トランジスタからなることを特徴とする。

50

**【発明の効果】**

**【0020】**

以上説明したように、請求項1記載の三角波生成回路によれば、スイッチング増幅段の正電源電圧および負電源電圧に比例した第1および第2の定電流を基に積分を行って三角波を生成するので、電源電圧に変動が生じた場合であっても、D級増幅器の利得Gを一定に維持することが可能である。また第1および第2の定電流は、高インピーダンス素子をもって選択されるので、その選択動作にあたってノイズが生じることがなく、適正な三角波が得られる。また第1および第2の定電流の選択動作に位相ずれが含まれていても、第2の積分手段の位相補正指示により三角波の位相ずれを抑制することが可能である。さらにかかる構成においてPLL回路は不要であるので、PLL動作によるジッタが生じる懸念を回避し、しかも回路規模を簡素化できる利点がある。10

**【0021】**

また請求項2記載の三角波生成回路によれば、正電源電圧および負電源電圧にアンバランスが生じた場合であっても、アンバランス成分を検出して三角波のオフセットを調整することで、D級増幅器の利得Gを一定に維持することが可能となる。

**【0022】**

また請求項3記載の三角波生成回路によれば、第1および第2の定電流に比例した第3および第4の定電流を生成する定電流手段を直列接続し、その接続端を前記第2の積分手段の入力端に接続する簡素な構成により、オフセット指示手段を実現できる。20

**【0023】**

また請求項4記載の三角波生成回路によれば、正電源電圧および負電源電圧が印加される抵抗回路と、この抵抗回路と同一の電流を発生するカレントミラー回路とから第1および第2の定電流手段を構築すると共に、カレントミラー回路に配置される電界効果トランジスタにクロックパルスをゲート入力として与える構成により定電流選択手段を構築することにより、簡素な回路構成で済む利点がある。

**【発明を実施するための最良の形態】**

**【0024】**

以下、図面を参照し、本発明の実施形態を説明する。

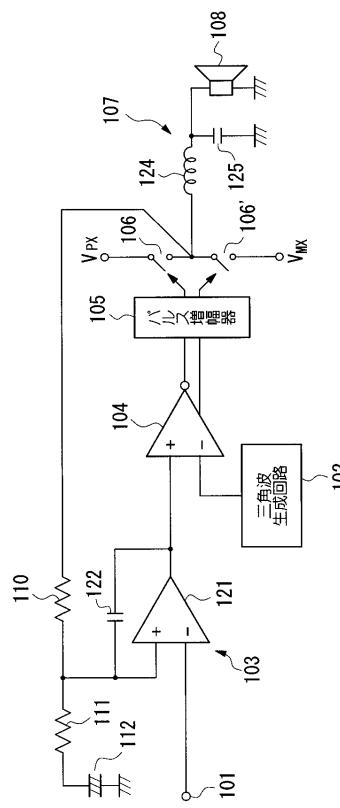

図1は、この発明の実施形態におけるD級増幅器の構成を示す概略ブロック図である。

この図において、符号101はアナログ信号入力端子、102は三角波生成回路、103は積分器である。この積分器103は、演算増幅器121および演算増幅器121の反転入力端および出力端間に介挿されたコンデンサ122から構成される。30

**【0025】**

104は積分器103の出力と三角波生成回路102の出力を比較する電圧比較器、105はパルス増幅器、106、106'はパルス増幅器105の出力によってオン／オフ制御されるスイッチング素子、V<sub>PX</sub>、V<sub>MX</sub>は+および-電源である。また、110はスイッチング素子106、106'の接続点Qに得られるPWM信号を積分器103に帰還する抵抗であり、抵抗111とで帰還量が定まる。コンデンサ112は直流遮断用のコンデンサである。また、107はコイル124およびコンデンサ125から構成されるLPF(ローパスフィルタ)、108は負荷である。40

**【0026】**

同図に示すように、アナログ入力信号は積分器103を介して電圧比較器104へ供給され、この電圧比較器104において三角波生成回路102の出力S1と比較され、ここでPWM変調されたパルス信号に変換される。次いで、パルス増幅器105で増幅され、スイッチング素子106、106'によってスイッチング増幅される。そして、スイッチング増幅後の信号がLPF107によってアナログ信号に戻され、負荷108へ出力される。

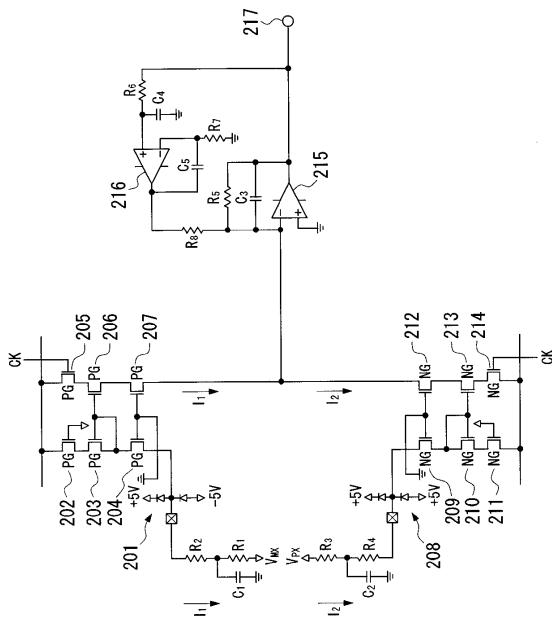

**【0027】**

図2は、この発明の第1の実施形態に係る三角波生成回路の具体的構成例を示す回路図である。同図において、符号NG、PGは各々FETのNチャネルゲート、Pチャネルゲ

ートを示している。R<sub>1</sub>, R<sub>2</sub>は直列に接続された抵抗、C<sub>1</sub>は両抵抗R<sub>1</sub>, R<sub>2</sub>の接続端と接地間に接続されるコンデンサであり、これらにより電源電圧V<sub>MX</sub>の実際の電圧値に比例した定電流I<sub>1</sub>を発生する。201は定電流I<sub>1</sub>の入力端であり、過電流入力時には過電流分を吸収するようになっている。

#### 【0028】

202～207はFET（電界効果トランジスタ）であり、FET202～204とFET205～206はそれぞれ直列接続回路を構成する。FET202のゲートには-電源電圧が印加され、FET205のゲートにはクロックパルスが印加される。FET203のソースはFET203, 206のゲートに接続される。FET204, 207のゲートは接地されている。FET204のソースは入力端201に接続されている。これにより、FET203～204の直列接続回路とFET205～206の直列接続回路がカレントミラー回路を構成し、したがって両回路には同じ電流I<sub>1</sub>が流れる。10

#### 【0029】

同様に、R<sub>3</sub>, R<sub>4</sub>は直列に接続された抵抗、C<sub>2</sub>は両抵抗R<sub>3</sub>, R<sub>4</sub>の接続端と接地間に接続されるコンデンサであり、これらにより電源電圧V<sub>PX</sub>に比例した定電流I<sub>2</sub>を発生する。208は電流I<sub>2</sub>の入力端であり、過電流入力時には過電流分を吸収するようになっている。

#### 【0030】

209～214はFETであり、FET209～211とFET212～214はそれぞれ直列接続回路をなし、上記と同様にFET209～211の直列接続回路とFET212～214の直列接続回路がカレントミラー回路を構成し、両回路には同じ電流I<sub>2</sub>が流れる。20

#### 【0031】

215は演算増幅器であり、その反転入力端へ電流I<sub>1</sub>およびI<sub>2</sub>が印加され、非反転入力端は接地されている。コンデンサC<sub>3</sub>および抵抗R<sub>5</sub>は、演算増幅器215の反転入力端および出力端間にそれぞれ介挿されている。これらにより積分回路が構成されている。さらに演算増幅器215の出力端は、三角波出力端217に接続されている。

#### 【0032】

216は演算増幅器であり、その非反転入力端は抵抗R<sub>6</sub>を介して演算増幅器215の出力端に接続されている。C<sub>4</sub>は演算増幅器216の非反転入力端および接地間に介挿されるコンデンサ、C<sub>5</sub>は演算増幅器216の出力端および反転入力端間に介挿されるコンデンサ、R<sub>7</sub>は演算増幅器216の反転入力端および接地間に介挿される抵抗である。R<sub>8</sub>は演算増幅器216の出力端および演算増幅器215の反転入力端間に介挿される抵抗である。これらにより、演算増幅器215の出力を負帰還させるサーボ閉ループが構成されている。30

#### 【0033】

次にこの三角波生成回路の動作を説明する。FET205, 214のゲートに外部からクロックパルスCKが印加されており、クロックパルスCKのLレベル時にFET205～207の直流接続回路に定電流I<sub>1</sub>が流れ、クロックパルスCKのHレベル時にFET212～214の直流接続回路に定電流I<sub>2</sub>が流れ。これらの回路は高インピーダンスなFETで構成されているので、電流切替時にノイズを生じることがない。40

#### 【0034】

FET205～207の直列接続回路およびFET212～214の直列接続回路の定電流I<sub>1</sub>, I<sub>2</sub>によりコンデンサC<sub>3</sub>が充電され、演算増幅器215およびコンデンサC<sub>3</sub>の積分動作により三角波が発生する。クロックパルスのデューティ比のずれなどにより電流I<sub>1</sub>, I<sub>2</sub>の印加タイミングに位相ずれが生じる可能性があるが、演算増幅器216によるサーボ動作によりこの位相ずれを抑制している。三角波の立ち上がり傾斜は、抵抗R<sub>6</sub>, R<sub>7</sub>の抵抗値とコンデンサC<sub>4</sub>, C<sub>5</sub>の容量値を適宜設定することにより調整する。三角波の頂点の丸め度合いは、抵抗R<sub>8</sub>の抵抗値を適宜設定することにより調整する。頂点を丸める必要がない場合は、抵抗R<sub>8</sub>がなくても（ショートされていても）よい。50

角波の立ち下り傾斜は、抵抗値 R 5 の抵抗値とコンデンサ C 3 の容量値を適宜設定することにより調整する。

#### 【0035】

このようにして得られた三角波の最大電圧値と最小電圧値はそれぞれ、電源電圧 V P X , V M X と比例関係にあるので、電源電圧 V P X , V M X に変動が生じた場合であっても、D 級増幅器の利得 G は一定に維持される。

#### 【0036】

図 3 は、この発明の第 2 の実施形態に係る三角波生成回路の具体的構成例を示す回路図である。同図において、図 2 と同様の部分は同一の符号を付してその説明を省略する。301 ~ 303 は F E T であり直列接続回路を構成する。F E T 301 のゲートには - 電源電圧が印加され、F E T 302 , 303 のゲートはそれぞれ F E T 203 , 204 のソースに接続されている。F E T 203 のソースは F E T 203 , 206 のゲートに接続されている。F E T 301 ~ 303 の直列接続回路には、F E T 205 ~ 207 の直列接続回路の定電流 I 1 に比例した定電流 I 1 - 1 が流れる。

10

#### 【0037】

同様に F E T 304 ~ 306 も直列接続回路を構成し、F E T 212 ~ 214 の直列接続回路の定電流 I 2 に比例した定電流 I 2 - 1 が流れる。

F E T 301 ~ 303 の直列接続回路と F E T 304 ~ 306 の直列接続回路は直列に接続され、両回路の接続端は演算增幅器 216 の非反転入力端に接続されている。

20

#### 【0038】

この三角波生成回路の動作を説明する。電源電圧 V P X 、 V M X の絶対値が等しい場合、定電流 I 1 - 1 と定電流 I 2 - 1 は等しくなって演算增幅器 216 への電流成分は生じず、したがって図 2 に示す三角波生成回路と同様の動作をもって、三角波が生成される。

#### 【0039】

もし電源電圧 V P X 、 V M X がアンバランスとなって両者の絶対値に差が生じた場合、その差分に比例した差分が定電流 I 1 - 1 と定電流 I 2 - 1 の間に生じ、この差分が演算增幅器 216 の非反転入力端に印加される。これにより三角波のオフセットが補正され、三角波の最大電圧値および最小電圧値を電源電圧 V P X , V M X に正確に追従させることができる。

#### 【0040】

30

以上、この発明の第 1 および第 2 の実施形態を詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計等も含まれる。

#### 【図面の簡単な説明】

#### 【0041】

【図 1】この発明の実施形態における D 級増幅器の構成を示す概略ブロック図。

【図 2】この発明の第 1 の実施形態に係る三角波生成回路の具体的構成例を示す回路図。

【図 3】この発明の第 2 の実施形態に係る三角波生成回路の具体的構成例を示す回路図。

【図 4】この種の従来の三角波生成回路を示す回路図。

#### 【符号の説明】

#### 【0042】

40

101 ~ アナログ信号入力端子、102 ~ 三角波生成回路、103 ~ 積分器

、104 ~ 電圧比較器、105 ~ パルス増幅器、106 , 106' ~ スイッチング素子、108 ~ 負荷、110 , 111 ~ 抵抗、112 ~ コンデンサ

、124 ~ コイル、125 ~ コンデンサ、121 ~ 演算増幅器、122 ~ コンデンサ、201 ~ 定電流 I 1 の入力端、202 ~ 207 , 209 ~ 214 , 301 ~ 306 ~ F E T 、208 ~ 電流 I 2 の入力端、215 , 216 ~ 演算増幅器、217 ~ 三角波出力端、V P X , V M X ~ + および - 電源、R 1 ~ R 8 ~ 抵抗、C 1 ~ C 5 ~ コンデンサ、I 1 ~ 電源電圧 V M X に比例した定電流、I 2 ~ 電源電圧 V P X に比例した定電流、I 1 - 1 ~ 定電流 I 1 に比例した定電流、I 2 - 1 ~ 定電流 I 2 に比例した定電流

50

【図1】

【図2】

---

フロントページの続き

(56)参考文献 特開昭57-63930(JP,A)

特開昭62-104308(JP,A)

特開昭63-224410(JP,A)

特開2004-007324(JP,A)

特開平07-231226(JP,A)

特開2004-128750(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 4/06

H03F 3/217