【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成17年3月10日(2005.3.10)

【公開番号】特開2004-112014(P2004-112014A)

【公開日】平成16年4月8日(2004.4.8)

【年通号数】公開・登録公報2004-014

【出願番号】特願2002-267869(P2002-267869)

【国際特許分類第7版】

H 0 3 M 1/66

【F I】

H 0 3 M 1/66 C

【手続補正書】

【提出日】平成16年4月1日(2004.4.1)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0 0 0 2

【補正方法】変更

【補正の内容】

【0 0 0 2】

【従来の技術】

デジタルオーディオ機器においては、デジタル化された音響信号をアナログ信号に変換するD A変換器として、例えばラダー抵抗型D A変換器や積分型D A変換器などが知られ、使用されている。これら周知のD A変換器は、離散的にサンプリングされてデジタル化されたデジタル信号の各サンプリング値(デジタル値)を単純にアナログ値に変換するものであるため、その出力信号波形は階段状の波形となり、原信号にはない不要な高周波成分を含むものとなる。このため、一般に、D A変換器の後段にアナログローパスフィルタを設けて不要な高周波成分を除去して滑らかなアナログ信号を得るようにしている。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0 0 0 6

【補正方法】変更

【補正の内容】

【0 0 0 6】

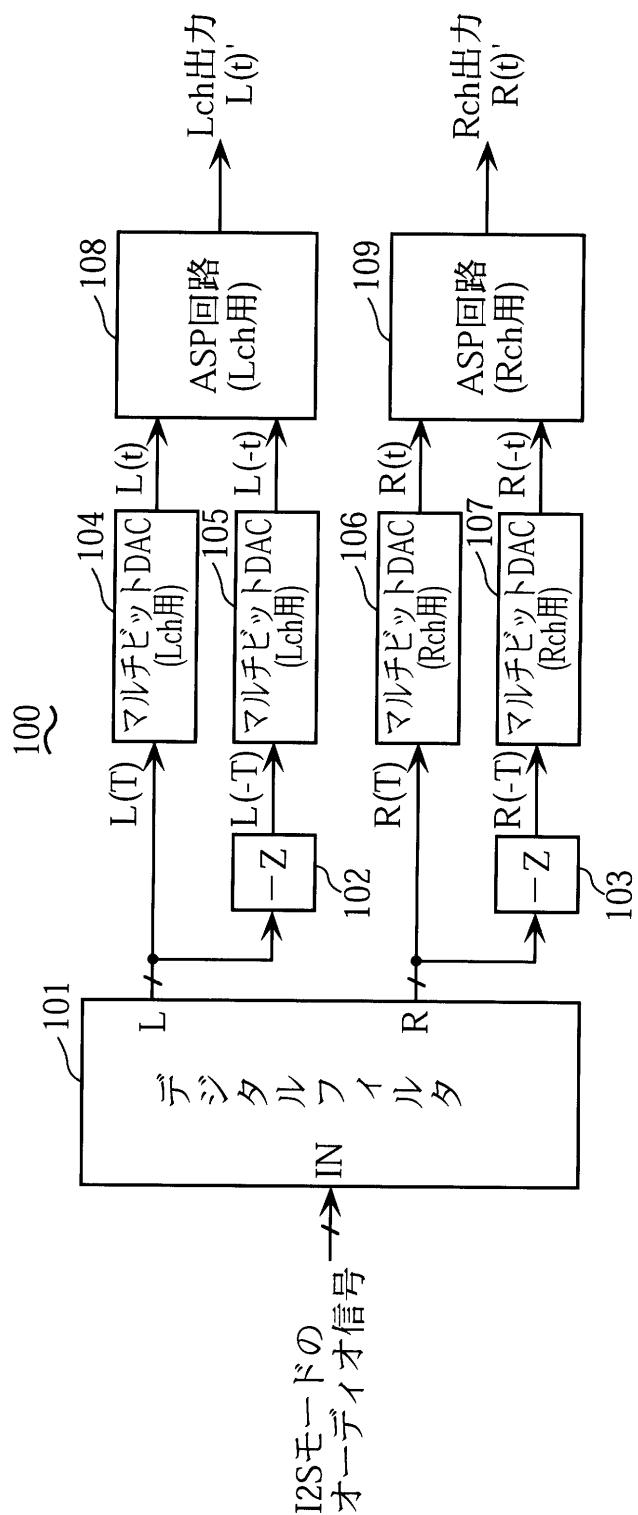

D A変換器1 0 0は、デジタルフィルタ1 0 1、2個の遅延回路1 0 2、1 0 3、4個のマルチビットD A変換器(以下、マルチビットD A Cという。)1 0 4~1 0 7および2個のアナログ信号処理回路(以下、A S P回路という。)1 0 8、1 0 9を備えている。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0 0 1 7

【補正方法】変更

【補正の内容】

【0 0 1 7】

上記構成において、オペアンプO P 1の-端子と+端子には、それぞれ各サンプリング点の第1のアナログ信号S(t)とこのアナログ信号S(t)より1サンプリング時間だけ遅延した第2のアナログ信号S(-t)とが入力され、オペアンプO P 1からは第2のアナログ信号S(-t)を基準電圧とした第1のアナログ信号S(t)の基準電圧に対する差分値の電圧が電流に変換されて出力される。そして、この電流により積分回路S CのコンデンサC 2が時定数C 2·r 6で充電され、このコンデンサC 2の充電電圧は、バッファアンプ(オペア

ンプ O P 2 ) 及び抵抗 r 5 を介して次に入力される第 2 のアナログ信号 S (-t) に加算される。

#### 【手続補正 4】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 4

【補正方法】変更

【補正の内容】

#### 【0 0 4 4】

ラッチ回路 2 1 2 は L R C K 信号の入力端子 I N 2 と出力端子 O U T 3 との間に接続され、反転回路 2 0 4 は B C L K 信号の入力端子 I N 3 と出力端子 O U T 4 との間に接続されている。ラッチ回路 2 1 0 , 2 1 1 , 2 1 2 は、遅延回路 2 0 7 を介してスイッチ回路 2 0 8 から出力される L チャンネルのデータとスイッチ回路 2 0 9 から出力される R チャンネルのデータと L R C K 信号とを同期させてそれぞれ L チャンネル出力端子 O U T 1 、 R チャンネル出力端子 O U T 2 、 L R C K 出力端子 O U T 3 から出力させるものである。ラッチ回路 2 1 0 , 2 1 1 , 2 1 2 にはそれぞれ B C L K 信号が入力され、ラッチ回路 2 1 0 , 2 1 1 は B C L K 信号を用いてデータを構成する各ビットのラッチ処理を行い、ラッチ回路 2 1 2 は B C L K 信号を用いて L R C K 信号のラッチ処理を行う。

#### 【手続補正 5】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 5

【補正方法】変更

【補正の内容】

#### 【0 0 4 5】

反転回路 2 0 4 は、 B C L K 信号を反転させて B C L K 出力端子 O U T 4 から出力することにより、 L チャンネル出力端子 O U T 1 、 R チャンネル出力端子 O U T 2 及び L R C K 出力端子 O U T 3 からそれぞれ出力される L チャンネルデータ、 R チャンネルデータ及び L R C K 信号に対する B C L K 信号のタイミングを調整するものである。

#### 【手続補正 6】

【補正対象書類名】明細書

【補正対象項目名】0 0 4 9

【補正方法】変更

【補正の内容】

#### 【0 0 4 9】

A N D 回路 2 0 1 は、 L R C K 信号が L レベルのとき、 D A T A 入力端子 I N 1 から I 2 S モードで入力される D A T A 信号を出力し、 A N D 回路 2 0 2 は、 L R C K 信号が H レベルのとき、 D A T A 入力端子 I N 1 から I 2 S モードで入力される D A T A 信号を出力するから、図 7 に示す信号波形より、 A N D 回路 2 0 1 からは L チャンネルのワードデータ D L i ( i = 1 , 2 , ... m ) が出力され、 A N D 回路 2 0 2 からは R チャンネルのワードデータ D R i ( i = 1 , 2 , ... m ) が出力される。

#### 【手続補正 7】

【補正対象書類名】明細書

【補正対象項目名】0 0 5 3

【補正方法】変更

【補正の内容】

#### 【0 0 5 3】

スイッチ回路 2 0 8 から出力される L チャンネルのワードデータ D L i とスイッチ回路 2 0 9 から出力される R チャンネルのワードデータ D R i とは同一サインプリング位置のデータであるが、 I 2 S モードによる D A T A 入力のフォーマットにより L チャンネルのワードデータ D L i が R チャンネルのワードデータ D R i よりも T / 2 だけ早く出力される。 S D F 変換回路 2 からは L チャンネルのワードデータ列 D L 1 , D L 1 , D L 2 , D L

2 , ... D L i , D L i , D L i+1 , D L i+1 , ... のシリアル信号と R チャンネルのワードデータ列 D R 1 , D R 1 , D R 2 , D R 2 , ... D R i , D R i , D R i+1 , D R i+1 , ... のシリアル信号とは同相で出力させる必要があるため、スイッチ回路 208 から出力される L チャンネルのワードデータ D L i は遅延回路 207 により T / 2 だけ遅延されて R チャンネルのワードデータ D R i の出力タイミングに調整される。

【手続補正 8】

【補正対象書類名】明細書

【補正対象項目名】0064

【補正方法】変更

【補正の内容】

【0064】

【発明の効果】

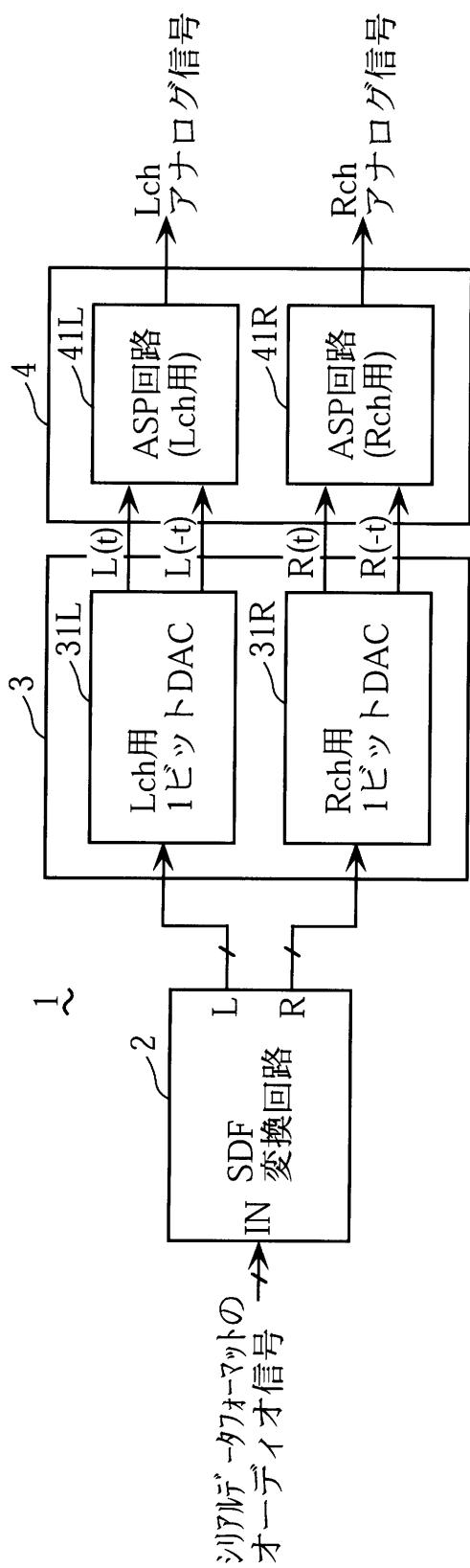

以上説明したように、本発明によれば、各種モードにより入力されるデジタルオーディオ信号のデータのフォーマットを、入力されたデータとこの入力データに対して 1 サンプリング時間だけ遅延した遅延データとをワード単位で交互にシリアルに配列してなるデータのフォーマットに変換し、フォーマット変換後のデータを用いてワンビット D A 変換手段により元のオーディオデータを D A 変換した第 1 のアナログ信号とこの第 1 のアナログ信号を 1 サンプリング時間だけ遅延した第 2 のアナログ信号とを生成し、両アナログ信号を用いてサンプリング点間の信号レベルを結んだアナログ信号を生成してアナログオーディオ信号として出力するようにしたので、マルチビット D A C を用いた従来の D A 変換器に比して回路構成の簡素な低コストの D A 変換器を実現することができる。

【手続補正 9】

【補正対象書類名】図面

【補正対象項目名】図 1

【補正方法】変更

【補正の内容】

【図1】

【手続補正10】

【補正対象書類名】図面

【補正対象項目名】図6

【補正方法】変更

【補正の内容】

【図6】