(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7232001号**

**(P7232001)**

(45)発行日 令和5年3月2日(2023.3.2)

(24)登録日 令和5年2月21日(2023.2.21)

(51)国際特許分類

*H 0 4 N 25/773 (2023.01)*

F I

*H 0 4 N 25/773*

請求項の数 9 (全14頁)

(21)出願番号 特願2018-158571(P2018-158571)

(22)出願日 平成30年8月27日(2018.8.27)

(65)公開番号 特開2020-36092(P2020-36092A)

(43)公開日 令和2年3月5日(2020.3.5)

審査請求日 令和3年8月12日(2021.8.12)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

弁理士法人大塚国際特許事務所

堀川 洋平

東京都大田区下丸子3丁目30番2号

(72)発明者 キヤノン株式会社内

審査官 鈴木 明

最終頁に続く

(54)【発明の名称】 撮像素子及びその制御方法、プログラム、記憶媒体

**(57)【特許請求の範囲】****【請求項1】**

光を受光する受光部と、該受光部に入射した光子の数を計数する計数手段と、をそれぞれ有する複数の画素と、

前記画素の信号の初期値を生成する初期化信号生成手段と、

を備え、

前記複数の画素の少なくとも一部の画素について、該少なくとも一部の画素のそれぞれが有する前記計数手段同士が接続され、接続された複数の計数手段のうちの最初の計数手段に前記初期化信号生成手段が接続されていることを特徴とする撮像素子。

**【請求項2】**

前記計数手段は、前記受光部が光子の入射に伴って発生する電荷に基づいてパルスを発生する発生手段と、該発生手段が発生したパルスを計数するカウンタとを有することを特徴とする請求項1に記載の撮像素子。

**【請求項3】**

前記計数手段は、前記画素からの信号の読み出し制御、もしくは前記画素のリセット制御において、シフトレジスタ動作を行うことを特徴とする請求項1または2に記載の撮像素子。

**【請求項4】**

前記初期化信号生成手段は、一律の固定値を出力することを特徴とする請求項1乃至3のいずれか1項に記載の撮像素子。

**【請求項 5】**

前記初期化信号生成手段は、画素ごとに個別の値を出力することを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の撮像素子。

**【請求項 6】**

前記撮像素子の偶数行の画素に対応する計数手段同士が接続され、奇数行の画素に対応する計数手段同士が接続されることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像素子。

**【請求項 7】**

前記撮像素子の偶数列の画素に対応する計数手段同士が接続され、奇数列の画素に対応する計数手段同士が接続されることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像素子。

10

**【請求項 8】**

前記受光部は、1つのマイクロレンズの下に射出瞳を分割する少なくとも 2 つの副画素を有することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像素子。

**【請求項 9】**

前記複数の画素のうちの間引いて読み出される画素に対応したそれぞれの計数手段同士が接続されることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像素子。

**【発明の詳細な説明】****【技術分野】****【0001】**

20

本発明は、撮像素子及びその制御方法に関する。

**【背景技術】****【0002】**

近年、特許文献 1 に記載されているように、画素毎に 1 b i t 型の A D 変換器とカウンタが設けられた固体撮像素子が提案されている。特許文献 1 に記載された固体撮像素子では、受光画素毎に A D 変換が行われ、その後、走査回路によって全画素の出力データが順次出力される。そのため、従来の列毎に A D 変換を行う固体撮像素子に比較して、走査線数と読み出し速度のトレードオフを解消することが可能である。

**【0003】**

この方式においては、受光素子に一定の電荷が蓄積されるたびにリセットされるため、光電変換素子が飽和することがない。そして、検出可能な光量は、蓄積容量の電圧が基準電圧と一致したときに出力されるパルスを数えるカウンタの上限により定まる。

30

**【先行技術文献】****【特許文献】****【0004】****【文献】特開 2015 - 173432 号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、特許文献 1 で提案されている技術においては、半導体パターンの微細化により配線部のショートが発生する可能性がある。このような場合、撮像素子の製造歩留まりが低下し、撮像素子のコストが高くなるという課題があった。

40

**【0006】**

本発明は上述した課題に鑑みてなされたものであり、その目的は、製造歩留まりが高く、コストを抑えることが可能な撮像素子を提供することである。

**【課題を解決するための手段】****【0007】**

本発明に係わる撮像素子は、光を受光する受光部と、該受光部に入射した光子の数を計数する計数手段と、をそれぞれ有する複数の画素と、前記画素の信号の初期値を生成する初期化信号生成手段と、を備え、前記複数の画素の少なくとも一部の画素について、該少

50

なくとも一部の画素のそれぞれが有する前記計数手段同士が接続され、接続された複数の計数手段のうちの最初の計数手段に前記初期化信号生成手段が接続されていることを特徴とする。

**【発明の効果】**

**【0008】**

本発明によれば、製造歩留まりが高く、コストを抑えることが可能な撮像素子を提供することが可能となる。

**【図面の簡単な説明】**

**【0009】**

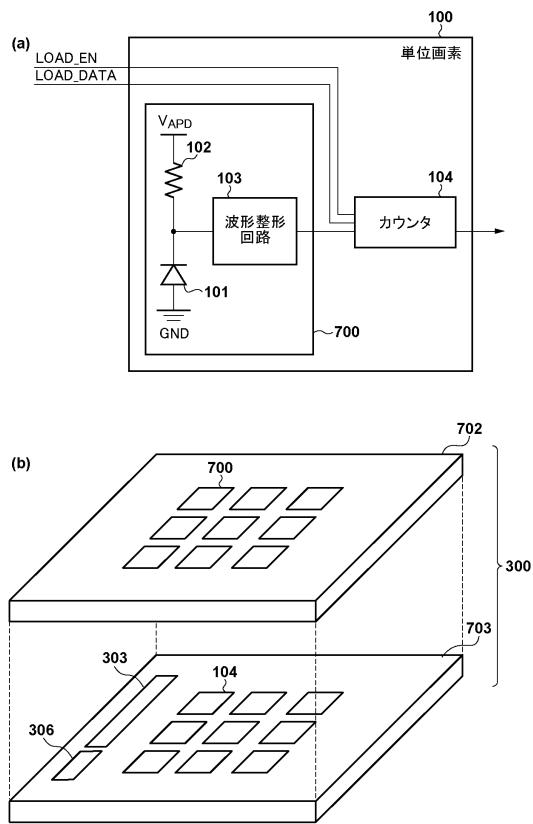

【図1】第1の実施形態における撮像素子の構成を示す図。

10

【図2】本発明の第1の実施形態の撮像素子における単位画素の構成を示す図。

【図3】第1の実施形態における単位画素が有するカウンタの構成を示す図。

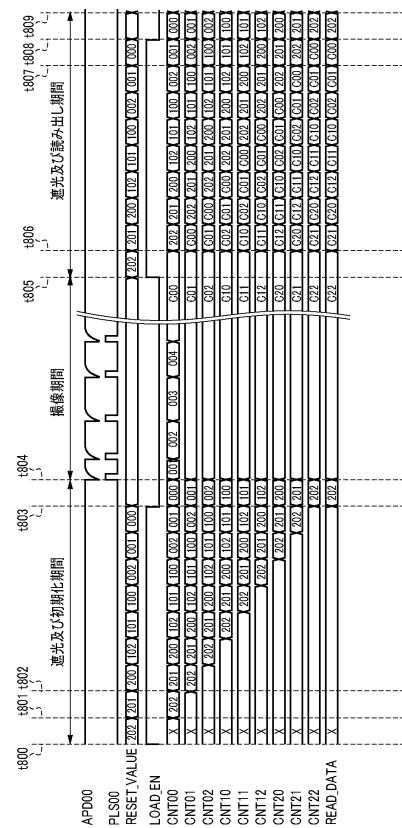

【図4】第1の実施形態における単位画素の駆動を示すタイミングチャート。

【図5】撮像素子の積層構造を示す図。

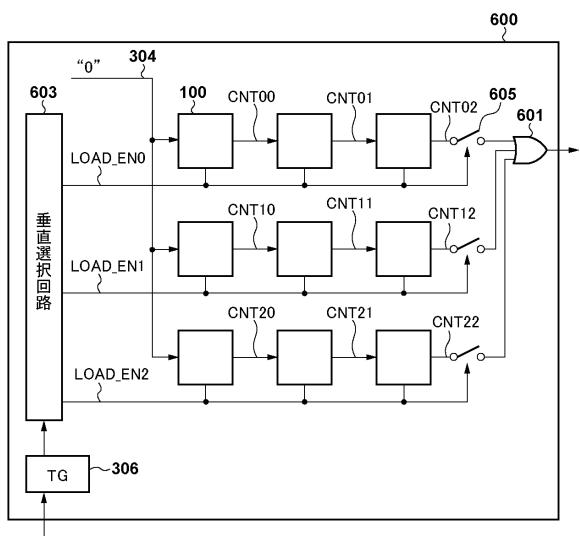

【図6】第2の実施形態における撮像素子の構成を示す図。

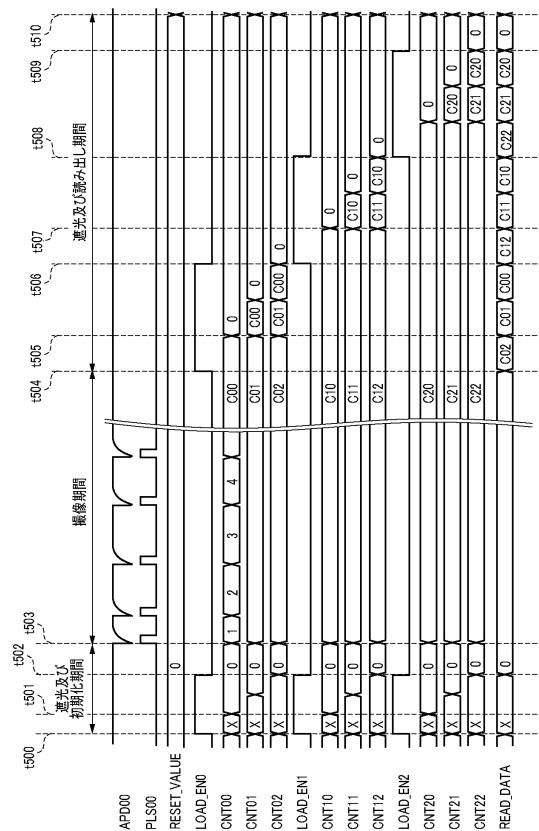

【図7】第2の実施形態における単位画素の駆動を示すタイミングチャート。

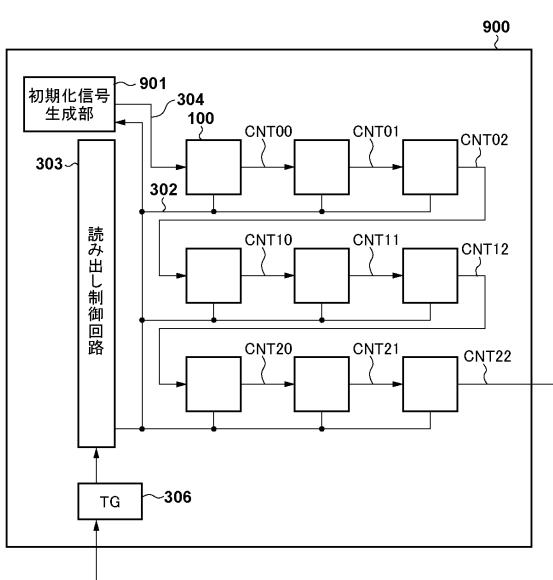

【図8】第3の実施形態における撮像素子の構成を示す図。

【図9】第3の実施形態における単位画素の駆動を示すタイミングチャート。

**【発明を実施するための形態】**

**【0010】**

以下、本発明の実施形態について、添付図面を参照して詳細に説明する。なお、以下に説明する実施形態は单なる例示であり、本発明は以下の実施形態の構成に限定されるものではない。

20

**【0011】**

<第1の実施形態>

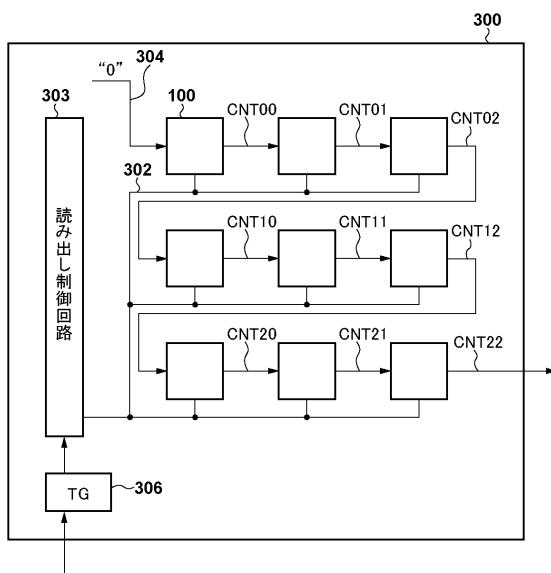

図1は、本発明の第1の実施形態における撮像素子300の構成を示す図である。撮像素子300は、単位画素100が2次元状に多数配置されているが、説明を分かりやすくするために、図1では3個×3個の単位画素100が配列されているものとして説明する。

**【0012】**

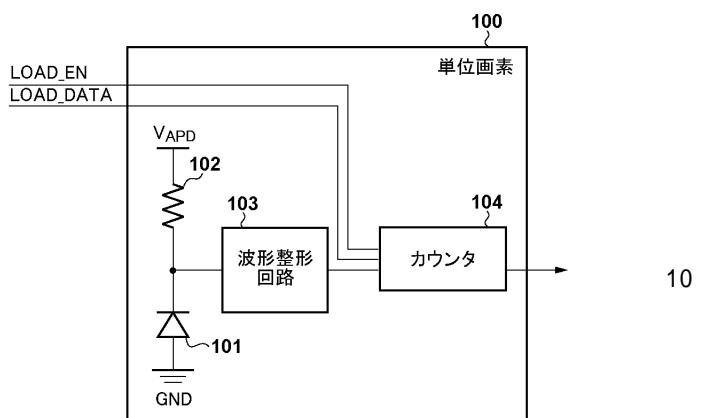

図2は、撮像素子300における単位画素100の構成を示す図である。単位画素100は、アバランシェフォトダイオード(以下、APD)101と、クエンチ抵抗102と、波形整形回路103と、計数部としてのカウンタ104とを備えて構成されている。以下、単位画素100の各々の構成要素について説明する。

30

**【0013】**

APD101は、クエンチ抵抗102を介して逆バイアス電圧VAPDと接続されており、光子が入射するとアバランシェ増倍による電荷を発生させる。APD101で発生した電荷はクエンチ抵抗102を介して排出される。波形整形回路103は、光子の入射に応じた電荷の生成と排出による電位の変化に対して、增幅とエッジ検出を行うことにより、電圧パルスを生成する。

**【0014】**

このようにAPD101(受光部)と、クエンチ抵抗102と、波形整形回路103とは、光子の入射の有無を電圧パルスに変換することにより、1bit型AD変換器として機能する。

40

**【0015】**

カウンタ104は、波形整形回路103により生成された電圧パルスの数を計数するカウンタであって、計数結果を出力することにより露光期間中の画素値を多ビットで出力する。カウンタ104は、単位画素100に入力される制御信号LOAD\_ENとデータ信号LOAD\_DATAとに基づいて、後述するフリップフロップ400にデータを設定する。

**【0016】**

50

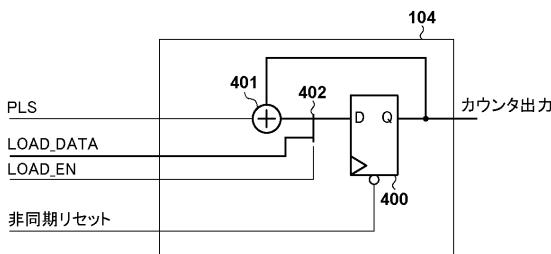

図3は、カウンタ104の具体的な構成を示す図である。カウンタ104は、データを保持するフリップフロップ400と、計数を行う加算部401と、カウンタ選択部402とを備える。

#### 【0017】

カウンタ選択部402は、制御信号LOAD\_ENに基づいてカウンタの値をデータ信号LOAD\_DATAに設定するか、加算部401の出力に設定するかを決定する。

#### 【0018】

フリップフロップ400は、非同期リセット信号によって、クロックに非同期で初期値0に初期化される。なお、本実施形態ではクロック信号及び非同期リセット信号は、撮像素子の撮像部全体で共通の信号である。

10

#### 【0019】

図1に示すような3個×3個の単位画素の配列において、一番左上の単位画素100(最初の画素)のデータ信号LOAD\_DATAに初期値データ304が入力される。そして、以降の単位画素100のデータ信号LOAD\_DATAには、各単位画素100のカウンタの出力が接続されている。すなわち、各単位画素100のカウンタ同士(計数手段同士)が接続されている。

#### 【0020】

各単位画素100の出力は、図1の左から右に向かって1行目をCNT00、CNT01、CNT02、2行目をCNT10、CNT11、CNT12、3行目をCNT20、CNT21、CNT22とする。全ての単位画素100の制御信号LOAD\_ENは読み出し制御回路303の出力によって制御され、シフトレジスタのように動作する(シフトレジスタ動作)。なお、本実施形態では初期値データ304の値として0を設定する。

20

#### 【0021】

タイミングジェネレータ(以下、TG)306は、不図示のカウンタに基づいて、撮像期間や転送期間などのタイミングを生成し、読み出し制御回路303に通知する。読み出し制御回路303は、TG306によって通知されたタイミングに基づいて、制御信号LOAD\_ENを発行する。

#### 【0022】

制御信号LOAD\_ENは、初期化期間及び読み出し期間に発行され、単位画素100が3個×3個配列されている場合には、同期して動作するクロック9サイクル分発行される。このサイクル数は、初期値データ304の値が出力CNT22に伝搬するまでの期間である。

30

#### 【0023】

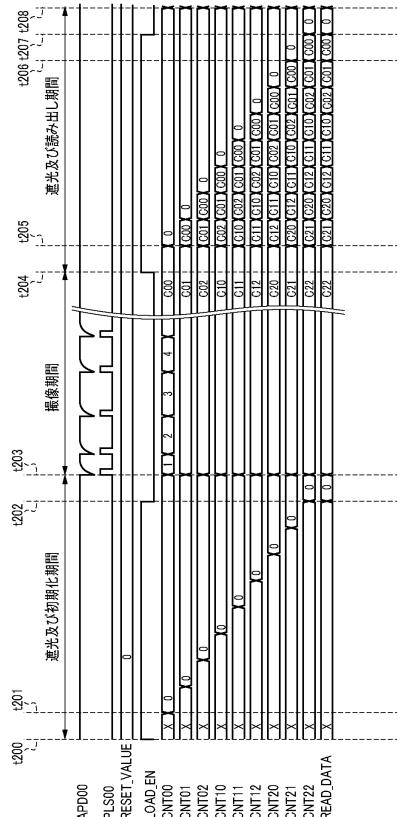

次に、図4は、撮像素子300の動作を示すタイミングチャートである。図4は、1つの単位画素100における撮像駆動を示しており、この駆動を複数の単位画素100において並列して行うことにより、光学像をデジタル信号に変換する。

#### 【0024】

図4において、APD00は、CNT00を出力する単位画素100におけるAPD101及びクエンチ抵抗102により生成される波形であり、PLS00は、同じ単位画素100における波形整形回路103の出力である。また、RESET\_VALUEは初期値データ、READ\_DATAは制御信号LOAD\_ENがHの期間有効となる撮像素子300からの出力データである。

40

#### 【0025】

続いて単位画素100の駆動について説明する。

#### 【0026】

時刻t200において、単位画素100のフリップフロップ400の値の初期化を開始し、制御信号LOAD\_ENがHになる。このとき、出力CNT00～CNT22の値はX(不定)である。また、不図示の遮光手段によってAPD101に光が入射しないように制御される。

#### 【0027】

50

時刻  $t_{201}$ において、初期値データ RESET\_VALUE の値が不図示のクロックに同期して出力 CNT00 にロードされる。以降、時刻  $t_{202}$ までの間、初期値データ RESET\_VALUE の値が出力 CNT00 から出力 CNT22 へと伝搬するまで、制御信号 LOAD\_EN は H になる（リセット制御）。

#### 【0028】

時刻  $t_{202}$ において、制御信号 LOAD\_EN が L になり、さらに出力 CNT22 が 0 となって初期化が完了する。

#### 【0029】

時刻  $t_{203}$ において、不図示の遮光手段による単位画素 100 の遮光を終了する。そして、APD101 に光が入射され、波形整形回路 103 の出力 PLSS00 が立ち上がることで、略同一のタイミングで出力 CNT00 は初期値に対して 1 を加算した値に変化する。

10

#### 【0030】

出力 CNT00 の値は、時刻  $t_{204}$ までの撮像期間の間、APD101 に光子が 1 個入射することに 1 ずつ増加する。出力 CNT01 から CNT22 においても対応する画素の APD101 の変化によって同様の処理が行われる。

#### 【0031】

時刻  $t_{204}$ において、出力 CNT00 ~ CNT22 の値が計数結果 C00 ~ C22 となって撮像期間が終了し、不図示の遮光手段が APD101 への光の入射を遮断する。略同一のタイミングで制御信号 LOAD\_EN が H となって、読み出し期間が開始され、出力 CNT22 の計数結果 C22 が出力データ READ\_DATA として撮像素子 300 から出力される。

20

#### 【0032】

時刻  $t_{205}$ は、時刻  $t_{204}$ に対して不図示のクロックで 1 サイクル経過したタイミングであり、初期値データ RESET\_VALUE の値が出力 CNT00 に伝搬される。また、出力 CNT00 の値は出力 CNT01 へ伝搬され、出力 CNT01 ~ CNT21 の値も同様に出力 CNT02 ~ CNT22 まで同様に伝搬される。このタイミングでは、出力 CNT22 に伝搬した計数結果 C21 が出力データ READ\_DATA として撮像素子 300 から出力される。

30

#### 【0033】

このように、出力 CNT22 の計数結果 C22 が初めに出力データとして出力され、次に計数結果 C21、次に計数結果 C20 という順番で、計数結果が出力データ READ\_DATA として撮像素子 300 から出力される。つまり、シフトレジスタのように順番に画素値が出力されることとなる。

#### 【0034】

時刻  $t_{206}$ において、出力 CNT00 の計数結果 C00 が出力 CNT22 に伝搬し、出力データ READ\_DATA として出力される。

#### 【0035】

時刻  $t_{207}$ において、制御信号 LOAD\_EN が L になり、初期値データ RESET\_VALUE が CNT22 に伝搬し、出力 CNT00 ~ CNT22 を出力する単位画素 100 の初期化が完了する。時刻  $t_{208}$ 以降は、時刻  $t_{203}$ から時刻  $t_{208}$ までの期間と同様に撮像期間と読み出し期間を繰り返す。

40

#### 【0036】

なお、本実施形態では制御信号 LOAD\_EN が H の期間、出力データ READ\_DATA が有効となるが、本発明はそれに限定されるものではない。例えば、制御信号 LOAD\_EN とは別に出力データ READ\_DATA の有効を示す信号を個別に設けてよい。このようにすることで、後述の初期化処理中の出力データ READ\_DATA を無効データとして取り扱うことが可能となる。また、波形整形回路 103 の出力に基づいて出力 CNT00 ~ 22 は計数動作を行うが、計数期間を制御する制御信号を個別に設けてよい。

50

**【 0 0 3 7 】**

なお、本発明は撮像素子 100 の物理的な構成について限定するものではない。例えば、アナログ信号を扱う回路部と、デジタル信号を扱う回路部を別の基板で形成し、積層構造を取ってもよい。

**【 0 0 3 8 】**

図 5 を用いて、積層構造の具体的な構成について説明する。図 5 ( a ) は、アナログ信号を扱う回路部とデジタル信号を扱う回路部に単位画素 100 の機能を分けて示した図である。また、図 5 ( b ) は、撮像素子 300 の積層構成を説明する図である。

**【 0 0 3 9 】**

図 5 ( a ) のアナログ信号処理部 700 は、A P D 102 と波形整形回路 103 を有する。カウンタ 104 は、デジタル信号化されたパルスを計数するデジタル回路部である。

10

**【 0 0 4 0 】**

図 5 ( b ) に示すように、上部基板 702 にはアナログ信号処理部 700 が 2 次元状に配列されている。また、下部基板 703 には、同様にカウンタ 104 が 2 次元状に配列されるとともに、読み出し制御回路 303 及び T G 306 などのデジタル回路が配置されている。

**【 0 0 4 1 】**

一般的にアナログ信号はデジタル信号に比べてノイズに弱いため、このようにデジタル信号に変換した上で下部基板 703 に伝送することによってノイズに対する堅牢性を保つことが可能となる。

20

**【 0 0 4 2 】**

また、カウンタ 104 のように出力ビット数が増えるほど回路規模が増大する部分を下部基板 703 に配置することにより、集積率を上げることが可能となる。このような場合においても、配線や制御線を削減したほうが、故障率が低下することは言うまでもない。

**【 0 0 4 3 】**

以上説明したように、本実施形態によれば、各画素が 1 b i t 型 A D 変換器とカウンタとを有する撮像素子において、撮像素子から読み出しを行うための配線及び制御線を簡略化することが可能となり、撮像素子の製造コストを抑えることが可能となる。

**【 0 0 4 4 】**

## &lt; 第 2 の実施形態 &gt;

30

第 1 の実施形態では、各単位画素の記憶素子であるフリップフロップ間をシフトレジスタのように配置し、カウンタ同士を接続することにより、配線及び制御線を簡略化する構成について説明した。しかしながら、全ての単位画素のカウンタ同士を接続する構成にしなければ効果がないわけではない。第 2 の実施形態では、一部の単位画素間のカウンタ同士を接続する構成とした場合の撮像素子の構造について説明する。

**【 0 0 4 5 】**

図 6 は、第 2 の実施形態における撮像素子 600 の構成を示す図である。本実施形態の撮像素子 600 では、各行ごとに単位画素 100 の制御信号 L O A D \_ E N 0 、 L O A D \_ E N 1 、 L O A D \_ E N 2 が供給される。また、伝送用の読み出しひスイッチ 605 が各行ごとに設けられるとともに、O R ゲート素子 601 が加えられている。さらに、第 1 の実施形態の読み出し制御回路 303 の代わりに、垂直選択回路 603 を備える。

40

**【 0 0 4 6 】**

垂直選択回路 603 は、蓄積を完了した 1 行目の単位画素 100 のカウンタ 104 の出力を読み出すタイミングにおいて、制御信号 L O A D \_ E N 0 を H にする。同様に 2 行目の単位画素 100 のカウンタ 104 の出力を読み出すタイミングにおいて、制御信号 L O A D \_ E N 1 を H にし、3 行目においては、制御信号 L O A D \_ E N 2 を H にする。

**【 0 0 4 7 】**

制御信号 L O A D \_ E N 0 が H になることにより、1 行目の読み出しひスイッチ 605 が導通する。同様に、制御信号 L O A D \_ E N 1 が H になることにより、2 行目の読み出しひスイッチ 605 が導通し、制御信号 L O A D \_ E N 2 が H になることにより、3 行目の読

50

み出しスイッチ 605 が導通する。そして、OR ゲート素子 601 の出力が撮像素子 600 の出力となる。なお、OR ゲート素子はオーブンドレインによるワイヤード OR で構成してもよい。

#### 【0048】

図 7 は、第 2 の実施形態における撮像素子 600 の動作を示すタイミングチャートである。

#### 【0049】

時刻 t500において、単位画素 100 のフリップフロップ 400 の値の初期化を開始し、制御信号 LOAD\_EN0、LOAD\_EN1、LOAD\_EN2 が H となる。このとき、出力 CNT00～CNT22 の値は X ( 不定 ) である。また、不図示の遮光手段によって APD101 に光が入射しないように制御される。10

#### 【0050】

時刻 t501において、初期値データ RESET\_VALUE の値が不図示のクロックに同期して出力 CNT00、CNT10、CNT20 にロードされる。以降、時刻 t502 までの間、初期値データ RESET\_VALUE の値が CNT02、CNT12、CNT22 の各々に伝搬するまで、制御信号 LOAD\_EN0、LOAD\_EN1、LOAD\_EN2 は H になる。

#### 【0051】

時刻 t502において、制御信号 LOAD\_EN0、LOAD\_EN1、LOAD\_EN2 が L になり、さらに出力 CNT02、CNT12、CNT22 が 0 となって初期化が完了する。20

#### 【0052】

時刻 t503において、不図示の遮光手段による遮光が終了する。そして、APD101 に光が入射され、波形整形回路 103 の出力 PLS00 が立ち上がりことで、略同一のタイミングで出力 CNT00 は初期値に対して 1 を加算した値に変化する。

#### 【0053】

出力 CNT00 の値は、時刻 t504までの撮像期間の間、APD101 に光子が 1 個入射することに 1 ずつ増加する。出力 CNT01 から CNT22 においても対応する画素の APD101 の変化によって同様の処理が行われる。

#### 【0054】

時刻 t504において、出力 CNT00～CNT22 の値が計数結果 C00～C22 となって撮像期間が終了し、不図示の遮光手段が APD101 への光の入射を遮断する。略同一のタイミングで制御信号 LOAD\_EN0 が H になり、読み出し期間が開始され、出力 CNT02 の計数結果 C02 が OR ゲート素子 601 を介して出力データ READ\_DATA として出力される。30

#### 【0055】

時刻 t505 は、時刻 t504 に対して不図示のクロックで 1 サイクル経過したタイミングであり、初期値データ RESET\_VALUE の値が出力 CNT00 に伝搬される。また、出力 CNT00 の値は CNT01 へ伝搬され、出力 CNT01 の値は CNT02 に伝搬される。このタイミングでは出力 CNT02 に伝搬した計数結果 C01 が出力データ READ\_DATA として出力される。40

#### 【0056】

時刻 t506において、制御信号 LOAD\_EN0 は L となり 1 行目の読み出し制御が完了する。また、初期値データ RESET\_VALUE の値が出力 CNT02 に伝搬され、初期化が完了する。略同一のタイミングで LOAD\_EN1 が H になり、2 行目の読み出しが開始され、出力 CNT12 の計数結果 C12 が OR ゲート素子 601 を介して出力データ READ\_DATA として出力される。

#### 【0057】

時刻 t507 は、時刻 t506 に対して不図示のクロックで 1 サイクル経過したタイミングであり、初期値データ RESET\_VALUE の値が出力 CNT10 に伝搬される。50

また、出力 CNT10 の値は CNT11 へ伝搬され、出力 CNT11 の値は CNT12 に伝搬される。このタイミングでは出力 CNT12 に伝搬した計数結果 C11 が出力データ READ\_DATA として出力される。

#### 【0058】

時刻 t508において、時刻 t506と同様に2行目の読み出し及び初期化の制御が完了する。また、時刻 t506と同様に LOAD\_EN2 が H になって、3行目の読み出しが開始され、出力 CNT22 の計数結果 C22 が OR ゲート素子 601 を介して出力データ READ\_DATA として出力される。

#### 【0059】

時刻 t509において、LOAD\_EN2 が L になり、初期値データ RESET\_VALUE が CNT22 に伝搬して全行の読み出しが完了するとともに、全行の初期化も完了する。

#### 【0060】

時刻 t510以降は、時刻 t503から時刻 t510までの期間と同様に撮像期間と読み出し期間を繰り返す。

#### 【0061】

以上のように処理を行うことにより、一部の単位画素間でカウンタ同士を接続するように構成した場合においても、撮像素子から読み出しを行うための配線及び制御線を簡略化することが可能となり、撮像素子の製造コストを抑えることが可能となる。

#### 【0062】

なお、本実施形態では奇数行と偶数行の行単位で複数の単位画素のカウンタ同士を接続する構成を取ったが、これに限定されるものではなく、例えば奇数列と偶数列のように列方向に複数の単位画素のカウンタ同士を接続する構成を取ってもよい。

#### 【0063】

また、公知の技術であるマイクロレンズの下に射出瞳を 2 分割した副画素を配置するような技術においても適用することが可能である。例えば分割された左側の画素の計数結果を右側の画素の計数結果に伝搬するように構成してもよい。このように処理を行うことにより、読み出しじゃイッチを制御する制御線を削減することが可能となる。

#### 【0064】

また、CCD センサのフィールド読み出しのように画素を一定間隔で間引いて読むようなモードを備える場合において、間引き読みの単位で複数の単位画素のカウンタ同士を接続するように構成してもよい。つまり、本発明は複数の単位画素のカウンタ同士を接続する構成を取る単位について何ら限定をあたえるものではない。

#### 【0065】

また、第 1 の実施形態では 3 行目、2 行目、1 行目の順番で画素値を出力したのに対して、本実施形態では 1 行目、2 行目、3 行目の順番で画素値を出力した。本発明はこのような出力順序に限定されるものではなく、接続関係及び制御信号 LOAD\_EN の出力順番を異ならせることで任意の順番で出力を行うことが可能となる。また、制御信号 LOAD\_EN を複数持ち、制御手順で出力順序を決定してもよい。

#### 【0066】

##### <第 3 の実施形態>

第 1 及び第 2 の実施形態では、初期値データ RESET\_VALUE を一律な固定値の 0 とし、計数を開始する前にロードする方法について説明した。しかしながら、初期値は固定値とする必要はない。例えばあらかじめ各画素単位に初期値を個別に設定することにより、画素値の OB クランプ補正や画素ごとのリミッタ処理に活用することが可能となる。

#### 【0067】

OB クランプ補正やリミッタ処理を撮像素子の中で行う場合には、補正值を保持するためのフリップフロップを個別に持つ必要があるが、本実施形態のようにカウンタの初期値に補正值を設定することにより、補正值保持用のフリップフロップが不要となる。第 3 の実施形態では、各画素別に単位画素 100 のフリップフロップ 400 に初期値を設定する

10

20

30

40

50

方法について説明する。

#### 【0068】

図8は、第3の実施形態における撮像素子900の構成を示す図である。撮像素子900では、第1の実施形態で説明した撮像素子300に対して、初期化信号生成部901が加えられている。

#### 【0069】

初期化信号生成部901は、内部に初期値のパターンを生成するパターン生成回路やS

R A Mに代表される記憶素子を有し、各画素単位の初期値を出力する回路である。初期化

信号生成部901は、読み出し制御回路303から出力される制御信号L O A D \_ E Nに

応じて、単位画素100の初期値を切り替えながら出力する。

10

#### 【0070】

具体的な動作について図9を用いて説明する。図9は撮像素子900の動作を示すタイ

ミングチャートである。

#### 【0071】

時刻t800において、単位画素100のフリップフロップ400の値の初期化を開始

し、制御信号L O A D \_ E NがHになる。このとき、出力C N T 0 0 ~ C N T 2 2の値は

X(不定)である。また、不図示の遮光手段によってA P D 1 0 1に光が入射しないよう

に制御される。また、初期化信号生成部901は、出力C N T 2 2用の補正值202を初

期値データR E S E T \_ V A L U Eとして出力する。

20

#### 【0072】

時刻t801において、初期値データR E S E T \_ V A L U Eの値が不図示のクロック

に同期して出力C N T 0 0にロードされると同時に、初期化信号生成部901は出力C N

T 2 1を補正するための補正值201を初期値データR E S E T \_ V A L U Eとして出力

する。

#### 【0073】

時刻t802において、出力C N T 0 0の値が不図示のクロックに同期してC N T 0 1

にロードされると同時に、初期値データR E S E T \_ V A L U Eの値が出力C N T 0 0に

ロードされる。また、初期化信号生成部901はC N T 2 0を補正するための補正值20

0を初期値データR E S E T \_ V A L U Eとして出力する。

30

#### 【0074】

以降、時刻t803までの期間、初期化信号生成部901は、順次各単位画素100の

カウンタ104の初期値を生成し、シフトレジスタ構成によって各カウンタ104のフリ

ップフロップ400にロードする。

#### 【0075】

時刻t803において、制御信号L O A D \_ E NがLになり、さらに出力C N T 2 2に

補正值202がロードされると初期化が完了する。このとき、出力C N T 0 0 ~ C N T 2

2には補正值000~202がロードされている。

40

#### 【0076】

時刻t804において、不図示の遮光手段による遮光を終了する。そして、A P D 1 0

1に光が入射され、波形整形回路103の出力P L S 0 0が立ち上がることで、略同一の

タイミングで出力C N T 0 0は初期値に対して1を加算した値に変化する。

出力C N T 0 0の値は、時刻t805までの撮像期間の間、A P D 1 0 1に光子が1個入

射するごとに1ずつ増加する。出力C N T 0 1からC N T 2 2においても対応する画素の

A P D 1 0 1の変化によって同様の処理が行われる。

#### 【0077】

時刻t805において、出力C N T 0 0 ~ C N T 2 2の値が計数結果C 0 0 ~ C 2 2と

なって撮像期間が終了し、不図示の遮光手段がA P D 1 0 1への光の入射を遮断する。略

同一のタイミングで制御信号L O A D \_ E NがHとなって、読み出し期間が開始され、出

力C N T 2 2の計数結果C 2 2が出力データR E A D \_ D A T Aとして撮像素子900か

ら出力される。

50

**【 0 0 7 8 】**

このとき、計数結果 C 0 0 から C 2 2 は、初期化信号生成部 9 0 1 により生成された初期値に対して波形生成部 1 0 3 の出力 P L S を計数した結果を加算した値である。つまり、初期値に O B クランプを行うためのオフセット値の反転信号を設定することで、撮像素子 9 0 0 の出力に対する O B クランプ補正を行う回路を設ける必要がなくなる。

**【 0 0 7 9 】**

時刻 t 8 0 6 は、時刻 t 8 0 5 に対して不図示のクロックで 1 サイクル経過したタイミングであり、初期値データ R E S E T \_ V A L U E の値が出力 C N T 0 0 に伝搬される。この初期値データ R E S E T \_ V A L U E の値は、時刻 t 8 0 1 の説明と同様に初期化信号生成部 9 0 1 の出力に基づいて生成される。

10

**【 0 0 8 0 】**

また、出力 C N T 0 0 の値は C N T 0 1 へ伝搬され、出力 C N T 0 1 ~ C N T 2 1 の値も同様に出力 C N T 0 2 ~ C N T 2 2 まで同様に伝搬される。このタイミングでは、出力 C N T 2 2 に伝搬した計数結果 C 2 1 が出力データ R E A D \_ D A T A として撮像素子 9 0 0 から出力される。

**【 0 0 8 1 】**

以降、時刻 t 8 0 7 、 t 8 0 8 、 t 8 0 9 では、時刻 t 2 0 6 、 t 2 0 7 、 t 2 0 8 と同様の処理が行われる。

**【 0 0 8 2 】**

以上説明したように、カウンタが有するフリップフロップの初期値を任意に設定することにより、補正值を保持するためのフリップフロップを個別に持つ必要がなくなり、回路規模を削減することが可能となる。

20

**【 0 0 8 3 】**

なお、本実施形態では O B クランプ補正について説明したが、他の用途に用いてよい。例えば水平像高別にリミッタ値を変更したい場合に、各画素の出力にリミッタを設けるためには、リミッタの閾値設定用フリップフロップ、比較用のコンパレータ及び出力制御用セレクタが必要となる。

**【 0 0 8 4 】**

一方、初期値に閾値の符号反転信号を予め設定することにより、計数結果が 0 以上となつた際に 0 を出力するように構成すればよい。一般的に可変リミッタに比べ、0 と比較するリミッタは回路規模を小さく構成することが可能である。このような場合は、出力結果に対してフリップフロップに設定した像高別の初期値を加算することにより本来の計数結果を復元することが可能となる。

30

**【 0 0 8 5 】****( その他の実施形態 )**

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、A S I C ）によっても実現可能である。

40

**【 符号の説明 】****【 0 0 8 6 】**

1 0 0 : 単位画素、1 0 1 : アバランシェフォトダイオード ( A P D ) 、1 0 2 : クエンチ抵抗、1 0 3 : 波形整形回路、1 0 4 : カウンタ、3 0 0 : 撮像素子

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図 9】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 特表2001-502424(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79