(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 15 291 T2 2007.05.10

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 320 105 B1

(51) Int Cl.<sup>8</sup>: G11C 29/00 (2006.01)

(21) Deutsches Aktenzeichen: 602 15 291.7

(96) Europäisches Aktenzeichen: 02 028 008.7

(96) Europäischer Anmeldetag: 13.12.2002

(97) Erstveröffentlichung durch das EPA: 18.06.2003

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 11.10.2006

(47) Veröffentlichungstag im Patentblatt: 10.05.2007

(30) Unionspriorität:

**2001381412      14.12.2001      JP**

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**Kabushiki Kaisha Toshiba, Tokio/Tokyo, JP**

(72) Erfinder:

**Taura, Intell. Property Division, Tadayuki,

Minato-ku, Tokyo 105-8001, JP; Atsumi, Intell.

Property Division, Shigeru, Minato-ku, Tokyo

105-8001, JP; Maeda, Intell. Property Division,

Shuji, Minato-ku, Tokyo 105-8001, JP**

(74) Vertreter:

**HOFFMANN & EITLE, 81925 München**

(54) Bezeichnung: **Halbleiter Speicheranordnung**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung beschreibt eine Halbleiterspeichervorrichtung und insbesondere einen Defektrettungsschaltkreis bzw. Defektsicherungsschaltkreis zum Einstellen von verschiedenen Arten von Defektwiederherstellungseinheiten, deren Größe unterschiedlich ist.

**[0002]** Eine Halbleiterspeichereinheit, die eine redundante Struktur aufweist, ist in EP 0 504 434 A offenbart. Die Speichereinheit umfasst eine Vielzahl von Speicherzellenblöcken, von denen jeder eine Vielzahl von Speicherzellen umfasst, ein erstes redundantes Zellenfeld, welches für jeden der Speicherzellenblöcke verfügbar ist, wobei das erste redundante Zellenfeld so konfiguriert ist, um ein defektes Zellenfeld in jedem Speicherzellenblock zu retten. Ein redundanter Zellenblock steht für die Mehrzahl von Speicherzellenblock zur Verfügung und ist so konfiguriert, um einen defekten Block in den Speicherzellenblöcken zu retten. Ein zweites Redundanzzellenfeld steht für den redundanten Zellenblock zur Verfügung, wobei der zweite redundante Zellenblock so konfiguriert ist, um ein defektes Zellenfeld in dem redundanten Zellenblock zu retten. Ein erster Defektrettungsschaltkreis ist in der Speichereinheit vorgesehen, wobei der Rettungsschaltkreis einen ersten Adressspeicherschaltkreis und einen ersten Adresserkennungsschaltkreis aufweist, wobei der erste Adressspeicherschaltkreis so konfiguriert ist, um eine Adresse des defekten Zellenfeldes in den Speicherzellenblöcken zu speichern, und wobei der erste Adresserkennungsschaltkreis so konfiguriert ist, um ein Signal der gespeicherten Adresse und ein Adresssignal von außerhalb zu vergleichen und ein Ersatzsignal zum Ersetzen des defekten Zellenfeldes in den Speicherzellenblöcken durch das erste redundante Zellenfeld auszugeben. Weiterhin ist ein zweiter Defektrettungsschaltkreis vorgesehen, der einen zweiten Adressspeicherschaltkreis und einen zweiten Adresserkennungsschaltkreis aufweist, wobei der zweite Adressspeicherschaltkreis so konfiguriert ist, um eine Adresse des defekten Blockes der Mehrzahl von Speicherzellenblöcken zu speichern, und wobei der Adresserkennungsschaltkreis so konfiguriert ist, um ein Signal der gespeicherten Adresse des defekten Blockes mit einem Adresssignal von außerhalb zu vergleichen, um ein Ersatzsignal zum Ersetzen des defekten Blockes in der Mehrzahl der Speicherzellenblöcke durch den redundanten Zellenblock auszugeben.

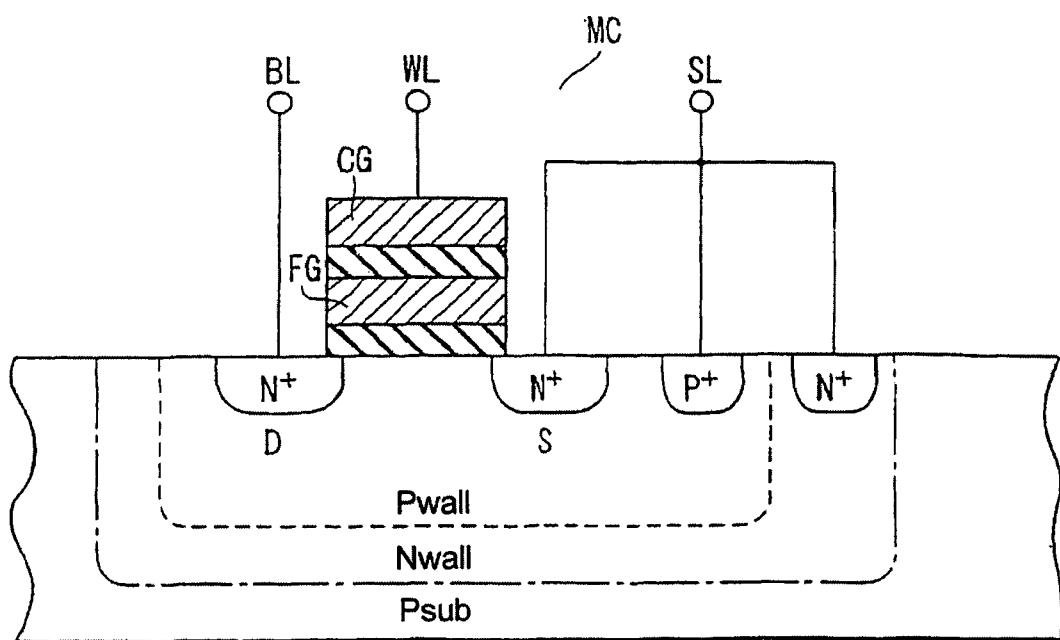

**[0003]** Als Speicherzellen eines EEPROM für elektrisch lösrbare/wiederbeschreibbare Daten wird beispielsweise eine nicht flüchtigen Speicherzelle MC genutzt, die eine NMOS-Transistorstruktur – wie in [Fig. 6](#) dargestellt – aufweist. Eine Doppelwallstruktur ist in einem p-Typ-Halbleitersubstrat (P<sub>sub</sub>) ausgebildet. Eine n-Typ-Wallregion (N<sub>wall</sub>) ist in der

Doppelwallstruktur ausgebildet und eine p-Typ-Wallregion (P<sub>wall</sub>) ist in der n-Typ-Wallregion (N<sub>wall</sub>) ausgebildet. Eine n-Typ-Diffusionsschicht, die eine Source (S) des NMOS-Transistors bildet und eine n-Typ-Diffusionsschicht, die ein Drain (D) des NMOS-Transistors bildet, sind in den p-Typ-Wallregion ausgebildet. Ein Floating-Gate (FG) in den NMOS-Transistor und ein Control-Gate (CG) in dem NMOS-Transistor sind in der p-Typ-Wallregion (P<sub>wall</sub>) ausgebildet. Das Floating-Gate (FG) ist in einer polykristallinen Siliziumschicht ausgebildet, die eine erste Level-Schicht ist, und ein Control-Gate (CG) ist in einer polykristallinen Siliziumschicht ausgebildet, welche eine zweite Level-Schicht darstellt. das Floating-Gate (FG) und das Control-Gate (CG) sind durch einen dazwischen ausgebildeten Isolationsfilm separiert.

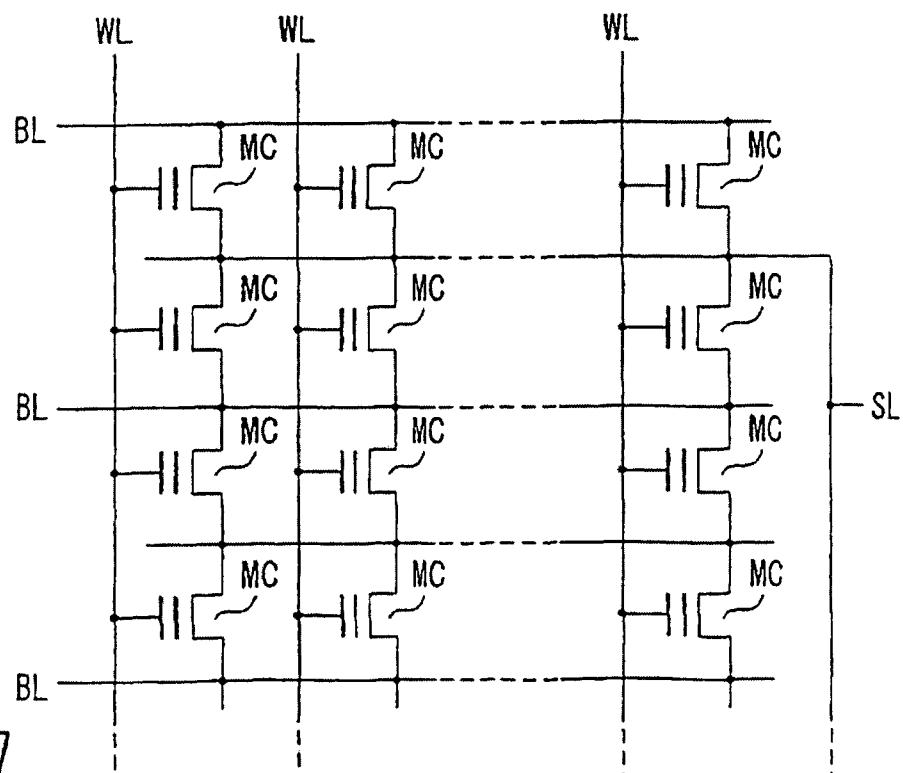

**[0004]** In einem typischen EEPROM enthält ein Speicherzellenfeld eine Vielzahl von Speicherzellen MC, die in einer Matrix, die in einer Wallregion ausgebildet sind, angeordnet ist. [Fig. 7](#) zeigt einen Äquivalenzschaltkreis eines Speicherzellenfeldes, welches eine NOR-Gate-artige Struktur aufweist. In dem Speicherzellenfeld wird eine der Speicherzellen durch eine Mehrzahl von Zeilenleitungen (Wort-Leitungen) WL und einer Vielzahl von Spaltenleitungen (Bit-Leitungen) BL ausgewählt. Die Mehrzahl der Zeilen Leitungen (Wort-Leitungen) WL ist an die Control-Gates CG der entsprechenden Speicherzellen MC angeschlossen und die Mehrzahl der Spaltenleitungen (Bit-Leitungen) BL ist an den Drain-Anschluss D der entsprechenden Speicherzellen MC angeschlossen. Die Sources D und der N<sub>wall</sub> und der P<sub>wall</sub> aller Speicherzellen MC sind gemeinsam an eine gemeinsame Source-Leitung SL angeschlossen.

**[0005]** Der Betrieb der Speicherzelle MC geschieht wie folgt. Beispielsweise wird ein Löschen von Daten dadurch ausgeführt, dass 10 V an die Sources (S), N<sub>wall</sub> und P<sub>wall</sub> aller Speicherzellen MC in dem Speicherfeld, das in einer p-Typ-Wallregion ausgebildet ist, angelegt wird, und durch Anlegen von beispielsweise -7V an alle Wort-Leitungen WL. Die Bit-Leitungen BL werden in einem Floating-Zustand belassen. Auf diese Weise werden Elektronen in den Floating-Gates (FG) der Speicherzellen MC durch Tunneln in die Kanäle emittiert, so dass die Schwellspannungen der Speicherzellen niedrig werden. Dieser Zustand bedeutet beispielsweise Daten von "1" (gelöschter Zustand).

**[0006]** Ein Schreiben von Daten wird durch das Anlegen von beispielsweise 9V an die ausgewählte Wort-Leitung WL und durch Anlegen von beispielsweise 5V an die ausgewählte Bit-Leitung BL ausgeführt. Die Source-Leitung SL wird auf 0V gesetzt. Zu diesem Zeitpunkt werden in der ausgewählten Speicherzelle MC – bedingt durch die Injektionen von hei-

ßen Elektronen – Elektronen in das Floating-Gate (FG) injiziert, so dass die Schwellspannung der ausgewählten Speicherzelle hoch wird. Dieser Zustand bedeutet Daten von "0" (beschriebener Zustand).

**[0007]** Ein Lesen von Daten wird ausgeführt durch ein Anlegen einer Lesespannung von beispielsweise 5v an die ausgewählte Wort-Leitung WL. Die Bit-Leitung BL wird auf eine niedrige Spannung von beispielsweise 0,7V gesetzt. Die Source-Leitung wird auf 0v gesetzt. Wenn die ausgewählte Speicherzelle "0" ist (beschriebener Zustand), fließt zu diesem Zeitpunkt kein Strom, wobei die Speicherzelle nicht eingeschaltet ist. Wenn die ausgewählte Speicherzelle "1" (gelöschter Zustand) ist, wird die Speicherzelle eingeschaltet und es fließt ein elektrischer Strom von ungefähr 40 µA durch die ausgewählte Speicherzelle. Ein Lesen wird ausgeführt durch eine Verstärkung der Amplitude des elektrischen Stroms durch einen Erkennungsverstärkerschaltkreis.

**[0008]** In so einem EEPROM können – bedingt durch Herstellungsprobleme (Staub oder Ähnliches) – defekte Zellen in dem Speicherzellenfeld existieren. Um ein Speicherzellenfeld zu einem guten Produkt zu machen, stehen verschiedene Defektrettungsschaltkreise (redundante Schaltkreise) zum Retten von defekten Zellen in dem EEPROM zur Verfügung, auch wenn es nur einige defekte Zellen gibt. Beispielsweise wird eine Rettung von Einheiten von Spalten (Spaltenredundanz) ausgeführt, wenn es Kurzschlüsse zwischen Bit-Leitungen oder einen Speicherzellendefekt gibt. Eine Blockrettung (Blockredundanz) wird in Daten löschen Einheiten ausgeführt, wenn es einen Kurzschluss zwischen Wort-Leitungen und den Source-Leitungen (Source/P-Wall oder ähnlichem) gibt, weil ein Kurzschluss zwischen den Wort-Leitungen und den Source-Leitungen einen Defekt in allen Speicherzellen in dem Block bedeutet, für den der p-Typ-Wall gleichermaßen benutzt wird, wobei es sich hier um eine Datenlöscheinheit handelt.

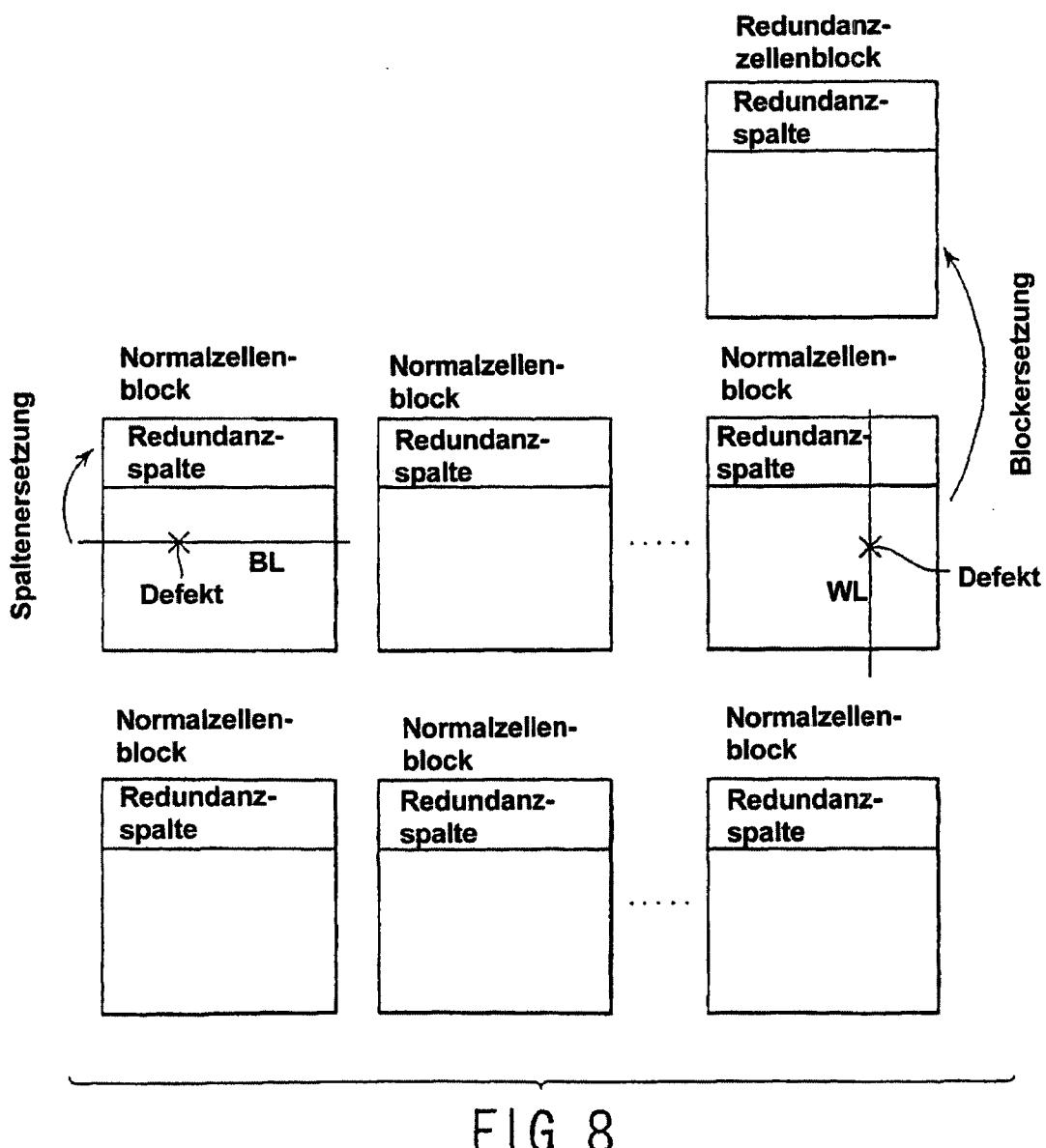

**[0009]** [Fig. 8](#) stellt eine Beziehung zwischen der Spaltenrettung und der oben beschriebenen Blockrettung dar. Wie in [Fig. 8](#) dargestellt, steht ein redundantes Spaltenzellenfeld zur Spaltenrettung in jeder der Mehrzahl von normalen Speicherblöcken (Kernen) zur Verfügung. Es ist möglich, eine Spaltersetzung entsprechend einer defekten Bit-Leitung auszuführen, die durch ein x-Kennzeichen bezeichnet ist, wobei ein redundantes Spaltenzellenfeld genutzt wird. Es steht auch ein redundanter Zellenblock (Kern) hinsichtlich Defekten von normalen Zellenblöcken zur Verfügung. Es ist möglich, eine Blockersetzung für einen Blockdefekt auszuführen, der durch ein x-Kennzeichen bezeichnet ist, wie ein Wort-Leitungskurzschluss mit einer Source-Leitung, wobei der redundante Zellenblock genutzt wird.

**[0010]** Insbesondere wird ein Test eines Memory-Chips ausgeführt, um eine Defektrettung auszuführen, und eine defekte Adresse wird in einen Defektadressespeicherschaltkreis auf der Basis der Testergebnisse in den Chip programmiert. Wenn der Defektadressespeicherschaltkreis unter Nutzung einer Sicherung – beispielsweise einer Laser ausgelösten Sicherung - ausgeführt wird, muss die Sicherungsschaltkreisprogrammierung, nach der Beendigung aller Tests ausgeführt werden, weil der Testprozess und der Sicherungsschaltkreisprogrammierprozess durch Laserblitze komplett separat sind.

**[0011]** Allerdings besteht im Fall eines EEPROM die Möglichkeit für eine Testsequenz, bei der die defekten Adressen nacheinander – jedes Mal wenn durch den Testprozess ein Defekt erkannt wird – programmiert werden, wobei als Speicherelement eine Speicherzelle genutzt wird, die der Speicherzelle gleich ist, die für das EEPROM-Zellenfeld in einem defekten Adressspeicherschaltkreis genutzt wird. Das ist der Grund dafür, dass das Schreiben der defekten Adresse durch Nutzung des Testschaltkreises – wie er ist – ausgeführt werden kann. Die Testzeit kann durch die Nutzung einer solchen Testsequenz verkürzt werden. Der Grund ist der folgende. Wenn ein Versuch gemacht wird, den bestehenden Test bis zu dem Zeitpunkt, zu dem Testresultate vorliegen, fortzuführen, entsteht eine Situation, in der beispielsweise die Schreiboperation in dem defekten Bereich nie endet, so dass für den Test eine lange Zeit benötigt wird, selbst wenn ein defekter Bereich in dem EEPROM gefunden wurde. So eine Situation kann vermieden werden, wenn eine sequentielle Defektersetzungssteuerung ausgeführt wird, bei der die defekte Adresse direkt nachdem ein Defekt gefunden wurde, programmiert wird, so dass die Testzeit verkürzt werden kann.

**[0012]** Wenn ein Verfahren verwendet wird, bei dem zwei Arten von Defektrettungsschaltkreisen wie ein Spaltenredundanzschaltkreis und ein Blockredundanzschaltkreis vorhanden sind, und eine Defektadresse in einem Testprozess sequenziell programmiert wird, gibt es dennoch ein Problem, wie es im Folgenden beschrieben wird. Es besteht die Möglichkeit, dass eine Situation entsteht, bei der ein Bit-Leitungsdefekt in einem gegebenen Block gefunden wird, und eine Wort-Leitung des Blockes, der bereits "spaltenrepariert" wurde, in dem Testprozess defekt wird, nachdem die Spaltenrettung ausgeführt wurde. Auf diese Weise wird angenommen, dass, wenn die Rettungsregionen der Spaltenrettung und der Blockrettung überlappen, und angenommen, dass der Ersatz der defekten Spalte in dem defekten Block, der entlastet (bzw. repariert) werden soll, in dem redundanten Block gültig ist, und weiterhin der Fall angenommen, bei dem eine defekte Spalte zusätzlich in dem redundanten Block gefunden wird, die Möglichkeit besteht, dass es keine Möglichkeit mehr gibt,

eine Rettung einer defekten Spalte auszuführen.

**[0013]** Beispielsweise wird angenommen, dass zwei Sätze eines Spaltenrettungssatzes in jedem der Blöcke verfügbar sind. Es sei angenommen, dass Spaltendefekte in den beiden Sätzen in einem Hauptblock (normaler Zellenblock) vor der Blockrettung existieren, und dass eine Spaltenrettung durchgeführt wurde, und danach ein Blockdefekt in dem Hauptblock gefunden wird, um die Rettung auszuführen. In solch einem Fall ist eine Rettung unmöglich, wenn ein Satz von Spaltendefekten erneut in dem Redundanzblock auftritt, weil es keinen weiteren Spaltenrettungssatz gibt, und der Speicher ein defektes Produkt ist.

**[0014]** Entsprechend der vorliegenden Erfindung wird eine HalbleiterSpeichervorrichtung vorgestellt, die Folgendes aufweist: eine Mehrzahl von Speicherzellenblöcken, von denen jeder eine Mehrzahl von Speicherzellen aufweist; ein erstes Redundanzzellenfeld, das für jeden der Speicherzellenblöcke verfügbar ist, wobei das erste Redundanzzellenfeld so konfiguriert ist, um ein defektes Zellenfeld in jedem Speicherzellenblock zu retten; eine Redundanzzellenblock, der für jede der Mehrzahl der Speicherzellenblöcke verfügbar ist, wobei der Redundanzblock so konfiguriert ist, um einen defekten Block der Speicherzellenblöcke zu retten; ein zweites Redundanzzellenfeld, das für jeden Redundanzzellenblock verfügbar ist, wobei das zweite Redundanzzellenfeld so konfiguriert ist, um ein defektes Zellenfeld in dem Redundanzzellenblock zu retten; einen ersten Defektrettungsschaltkreis, der einen ersten Adressspeicherschaltkreis und einen ersten Adresserkennungsschaltkreis aufweist, wobei der erste Adressspeicherschaltkreis so konfiguriert ist, um eine Adresse des defekten Zellenfeldes des Speicherzellenblocks zu speichern, und vorbei der erste Adresserkennungsschaltkreis so konfiguriert ist, um ein Signal der gespeicherten Adresse und ein Signal von außerhalb zu vergleichen und ein Ersatzsignal zum Ersetzen des defekten Zellenfeldes in den Speicherzellenblöcken durch das erste redundante Zellenfeld auszugeben; und einen zweiten Defektrettungsschaltkreis, der einen zweiten Adressspeicherschaltkreis aufweist, wobei der zweite Adressspeicherschaltkreis so konfiguriert ist, um eine Adresse des defekten Blocks aus der Mehrzahl der Speicherzellenblöcke zu speichern, wobei der zweite Adresserkennungsschaltkreis so konfiguriert ist, um ein Signal der gespeicherten Adresse des defekten Blocks mit einem Adresssignal von außerhalb zu vergleichen, um ein Ersatzsignal zum Ersetzen des defekten Blocks aus der Mehrzahl der Speicherzellenblöcke durch den redundanten Zellenblock zu erzeugen, dadurch gekennzeichnet, dass der erste Defektrettungsschaltkreis einen Gate-Schaltkreis aufweist, welcher das Ersatzsignal ausgibt, welches von dem ersten Adresserkennungsschaltkreis als gültig an einer

Adresse ausgegeben wurde, an welcher der zweite Defektrettungsschaltkreis nicht aktiv ist, um eine Blockrettung auszuführen, und welcher ein Signal ausgibt, welches darauf hinweist, welcher Block ein defekter Block ist, was durch den zweiten Defektrettungsschaltkreis als gültig bei einer Adresse ausgegeben wurde, bei welcher der zweite Defektrettungsschaltkreis aktiviert wurde, um eine Blockrettung auszuführen, und wobei der erste Defektrettungsschaltkreis den Gate-Schaltkreis derart steuert, dass durch das Ersetzungssignal, welches durch den zweiten Defektrettungsschaltkreis ausgegeben wurde, das Ersetzungssignal, das durch den ersten Adresserkennungsschaltkreis hinsichtlich des defekten Blocks ausgegeben wurde, für gültig erklärt wird, und ein Ersetzungssignal, das durch den ersten Adresserkennungsschaltkreis hinsichtlich des redundanten Blocks zum Ersetzen des defekten Blocks ausgegeben wurde, für gültig erklärt wird.

**[0015]** Die Erfindung kann vollständiger aus der folgenden, detaillierten Beschreibung zusammen mit den begleitenden Zeichnungen verstanden werden, für die Folgendes gilt:

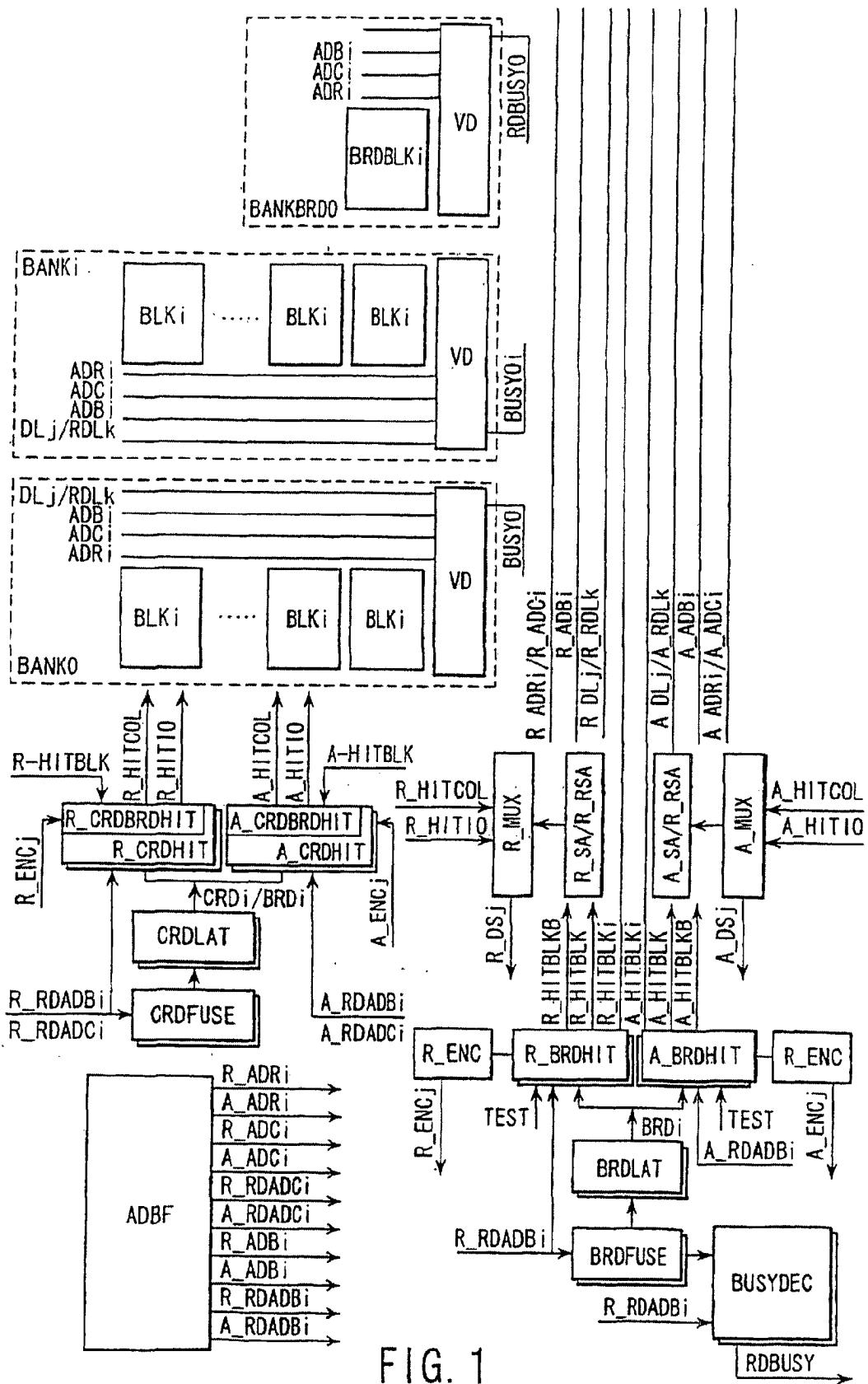

**[0016]** [Fig. 1](#) ist ein Diagramm, das eine Konfiguration eines EEPROM entsprechend eines Ausführungsbeispiels der vorliegenden Erfindung darstellt.

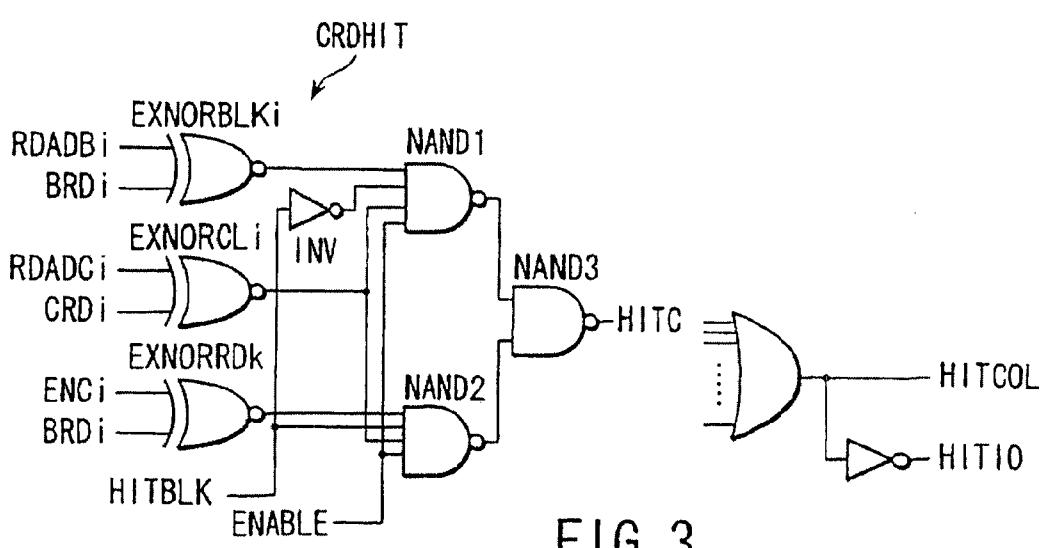

**[0017]** [Fig. 2](#) ist ein Diagramm, dass eine konkrete Konfiguration eines Spalten bezogenen Rettungsanteils des Ausführungsbeispiels der vorliegenden Erfindung darstellt.

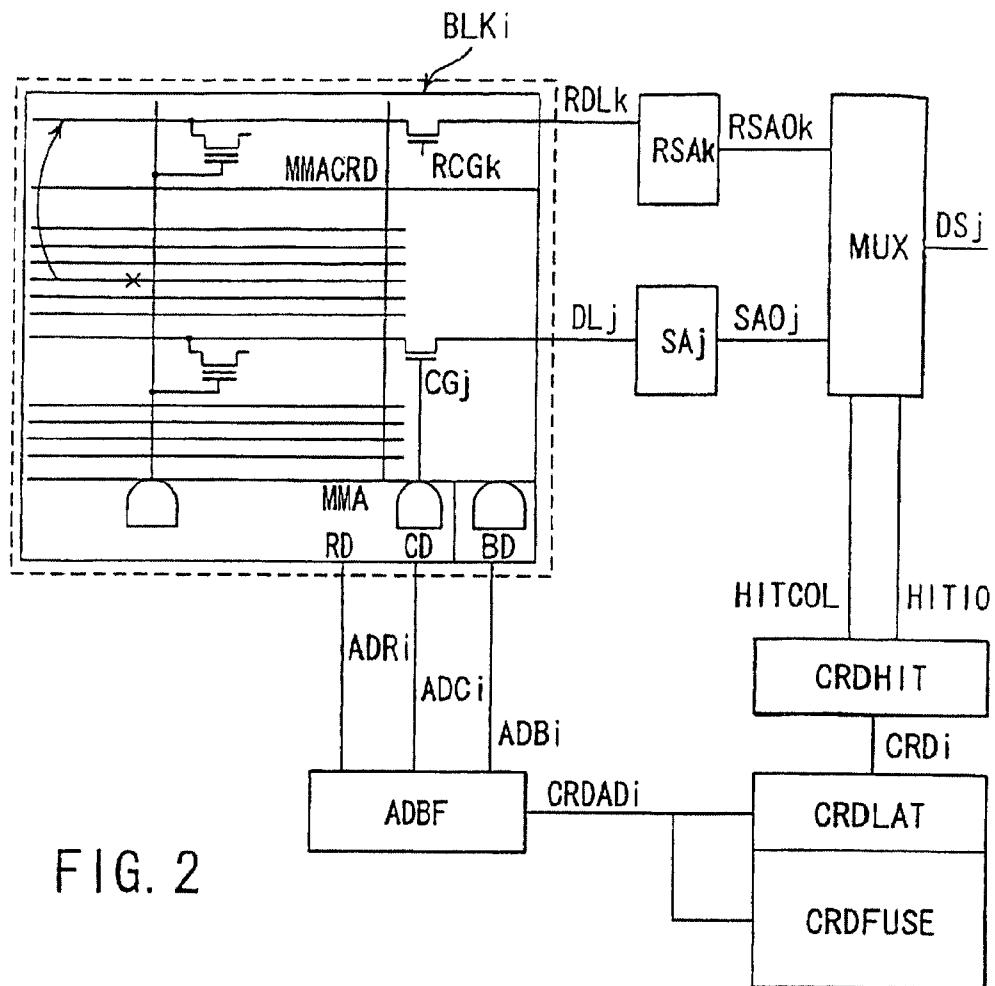

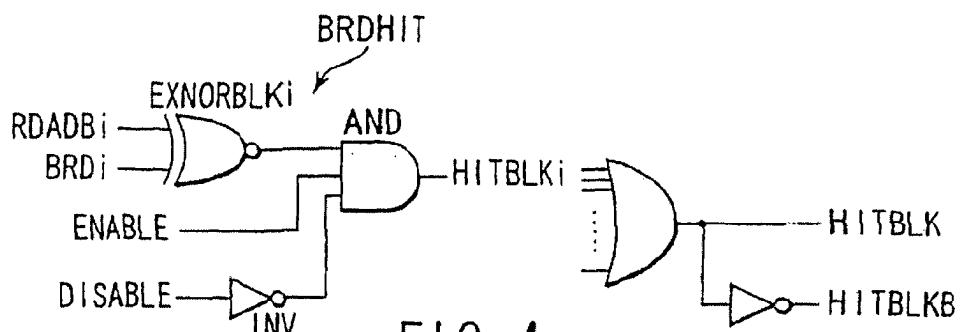

**[0018]** [Fig. 3](#) ist ein Diagramm, das eine Konfiguration eines Adresserkennungsschaltkreises für defekte Spalten des Ausführungsbeispiels der vorliegenden Erfindung darstellt.

**[0019]** [Fig. 4](#) ist ein Diagramm, das eine Konfiguration eines Adresserkennungsschaltkreises für defekte Blöcke des Ausführungsbeispiels der vorliegenden Erfindung darstellt.

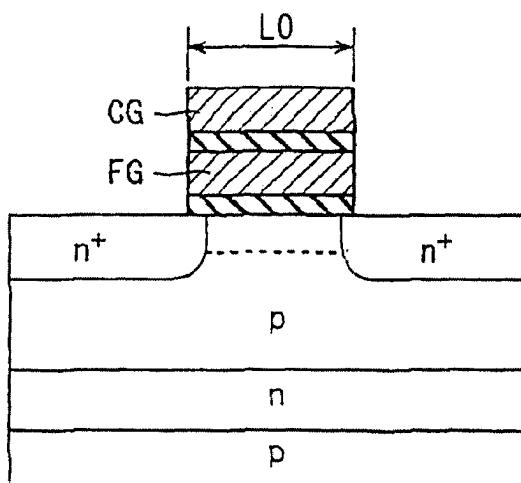

**[0020]** [Fig. 5A](#) ist eine Querschnittstruktur eines Speichertransistors zur Nutzung in einer Speicherzelle des Ausführungsbeispiels der vorliegenden Erfindung.

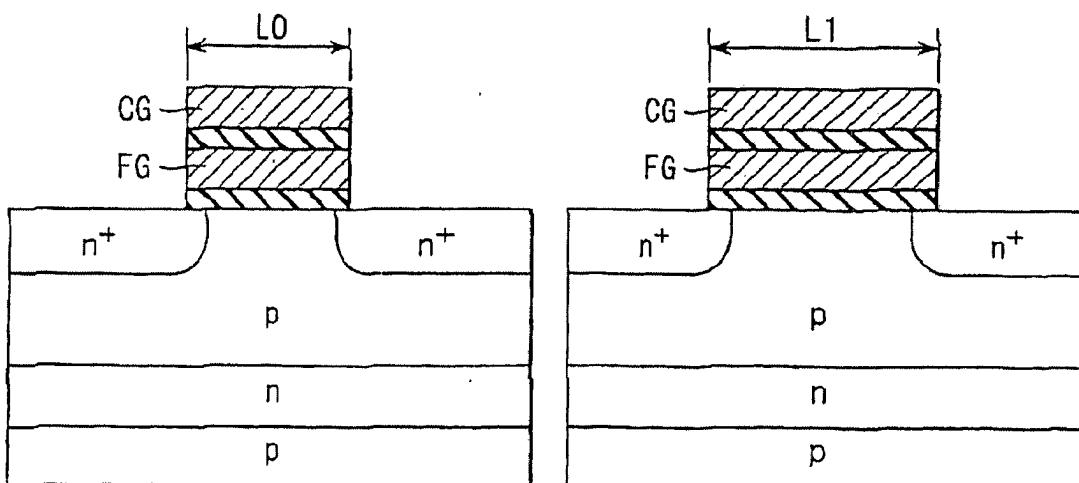

**[0021]** [Fig. 5B](#) und [Fig. 5C](#) sind Diagramme, die Querschnittstrukturen von Speichertransistoren zur Nutzung in einem Defektdressspeicherschaltkreis zur Nutzung in der Speicherzelle des Ausführungsbeispiels der vorliegenden Erfindung darstellen.

**[0022]** [Fig. 6](#) ist ein Diagramm, das eine Struktur einer nichtflüchtigen Speicherzelle eines EEPROM darstellt.

**[0023]** [Fig. 7](#) ist ein Diagramm, das eine Konfigura-

tion eines Speicherfeldes eines EEPROM darstellt.

**[0024]** [Fig. 8](#) ist ein Diagramm zur Erklärung der Prinzipien der Spaltenrettung und der Blockrettung bei einem konventionellen EEPROM.

**[0025]** Im Folgenden wird ein Ausführungsbeispiel der vorliegenden Erfindung unter Zuhilfenahme der Figuren beschrieben.

**[0026]** [Fig. 1](#) ist ein Schaltplan, der eine Konfiguration eines EEPROM entsprechend einem Ausführungsbeispiel der vorliegenden Erfindung darstellt. Hier wird ein Beispiel dargestellt, bei welchem eine so genannte Doppelfunktion realisiert wurde, bei dem ein Speicherzellenfeld beispielsweise zwei Bänke BANK0 und BANKi aufweist, und ein Lesen aus einer Bank BANKi während der Ausführung eines Schreibens/Löschen während der anderen Bank BANK0 ist möglich. Um eine solche Doppelfunktion zu realisieren, ist das EEPROM so konfiguriert, dass ein Adresssignal, ein Erkennungsverstärkerschaltkreis, ein Erkennungsschaltkreis für defekte Adressen usw. zum Lesen und für Auto entsprechend verfügbar sind, und sie werden durch Hinzufügen von "R" zu den entsprechenden Namen der Schaltkreise und Signale für das Lesen, und durch Hinzufügen von "A" zu den entsprechenden Namen der Schaltkreise und Signale für Auto unterschieden.

**[0027]** Jeder der normalen (Hauptteil) Bänke BANK, BANKi wird durch eine Mehrzahl von Blöcken (Kernen) BLKi gebildet. Jeder der Blöcke BLKi ist eine Einheit zum Datenlöschen. Um Defekte in den Blöcken BLKi in diesem Bänken BANK0, BANKi, aufzuheben, steht eine Rettungsbank (Ersatzbank, Redundanzbank) BANKBRD0 zur Verfügung, die mindestens einen, vorzugsweise eine Mehrzahl von Rettungsblöcken (Ersatzblock, Redundanzblock) BRD-BLK aufweist.

**[0028]** [Fig. 2](#) zeigt eine konkrete Konfiguration jedes der Blöcke BLKi und die Konfiguration der zugehörigen Peripherieschaltkreise. Der Hauptblock (normaler Zellenblock) BLKi umfasst ein Hauptspeicherzellenfeld MMA. Der Hauptblock BLKi umfasst weiterhin eine Rettungsspeicherzellenspalte (Ersatzspaltenzellenfeld, das heißt Redundanzspaltenretzungsfeld) MMACRD zur Rettung einer defekten Spalte in dem Speicherzellenfeld MMA in Einheiten von einer oder mehreren Spalten. Wie in [Fig. 7](#) dargestellt ist, ist das Hauptspeicherzellenfeld MMA durch Anordnung von Speicherzellen MC in Matrixform konfiguriert. Die Bit-Leitungsauswahl wird durch einen Spaltenauswahldecoder (Spaltendecoder) CD und ein Spaltenauswahl-Gate (Spalten-Gate) CG ausgeführt, und eine Wort-Auswahl wird durch einen Zeilenauswahldecoder (Zeilendecoder) RD ausgeführt.

**[0029]** Die Rettungsspeicherspalte MMARCD wird in Einheiten von mehreren Spalten (beispielsweise in Einheiten von vier Spalten) entsprechend beispielsweise des Staumfanges vorgesehen, und es werden mehrere Sätze (beispielsweise zwei Sätze) der Rettungsspeicherspalten MMACRD vorgesehen. Die Rettungsspeicherzellenspalte MMACRD wird durch ein Rettungspaltnauswahl-Gate (zusätzliches Spalten-Gate) RCG und den Spaltendecoder RD ausgewählt. Weiterhin werden Blockdecoder BD zur Blockauswahl BD für entsprechende Blockkerne BLKi vorgesehen.

**[0030]** Das Hauptspeicherzellenfeld MMA ist an den Erkennungsverstärkerschaltkreis SAj über Spalten-Gates CGj und Datenleitungen DLj angeschlossen. Der Erkennungsverstärkerschaltkreis SAj führt eine Leseoperation aus, so dass SAOj ausgegeben wird. In dem EEPROM stehen j Erkennungsverstärkerschaltkreise SAj, j Spalten-Gates CGj und j Datenleitungen DLj zur Verfügung. Darüber hinaus ist die Rettungsspeicherzellenspalte MMACRD an den Rettungserkennungsverstärkerschaltkreis RSAk über zusätzliche Spalten-Gates RCGk und Datenleitungen RDLk angeschlossen. Der Erkennungsverstärker führt eine Leseoperation aus, so dass RSA0k ausgegeben wird. In dem EEPROM stehen k Rettungserkennungsverstärkerschaltkreise RSAk, k zusätzliche Spalten-Gates RCGk und k Datenleitungen RDLk zu Verfügung.

**[0031]** Der Rettungsblock BRDBLK ([Fig. 1](#)) hat die gleiche Konfiguration wie der Hauptblock BLKi.

**[0032]** Zurückkommend auf [Fig. 1](#) erkennt man, dass die Energieversorgungsdecoder VD, die für die entsprechenden Bänke BANK0, BANKi zur Verfügung stehen, Decoderschaltkreise zum Schalten der internen Spannung zur Schreib- und Löschzeit und zur Auswahl der entsprechenden Speicherzellen enthalten. Das Schalten zwischen "For-Read" und "For-Auto" ist so konfiguriert, dass Busy-Signale Busy0 und Busyi, die während der Ausführung des Schreibens und Löschen "H" sind, an die Eingänge der Energieversorgungsdecoder der Bänke BANK0 und BANKi gelegt werden; und wenn BUSY = "L", ist "For-Read" ausgewählt, und wenn BUSY = "H", ist "For-Auto" ausgewählt.

**[0033]** Information über defekte Adressen zur Spaltenrettung ist in einem Adressspeicherschaltkreis für defekte Spalten CRDFUSE gespeichert. Die Adressinformationen, die in dem Adressspeicherschaltkreis für defekte Spalten CDRFUSE gespeichert ist, wird beispielsweise zu einem Zeitpunkt des Einschaltens ausgelesen und in einem Zwischenspeicherschaltkreis (Latch) für eine defekte Adresse CRDLAT zwischengespeichert.

**[0034]** Die Adressinformationen über defekte Blö-

cke zum Retten von Hauptblöcken ist in einem Adressspeicherschaltkreis für einen defekten Block BRDFUSE gespeichert ([Fig. 1](#)). Die Adresse, die in dem Adressspeicherschaltkreis für eine defekte Adresse BRDFUSE gespeichert ist, wird in einem Adresszwischenspeicherschaltkreis (Latch) BRDLAT gespeichert, wenn das Einschalten der Spannungsversorgung festgestellt wird.

**[0035]** Ein Spaltenadresssignal ADCi, ein Zeilenaadresssignal ADRi und ein Blockadresssignal ADBi werden von einem Adresspuffer ADBF ausgegeben, und dieses Spaltenadresssignal ADCi, dieses Zeilenaadresssignal ADRi und dieses Blockadresssignal ADBi werden entsprechend zu dem Spaltendecoder CD, dem Zeilendecoder RD und dem Blockdecoder BD geleitet. Ein Spaltenadresssignal RDADCi (welches das gleiche wie das ADCi sein kann, aber dessen Ausgabe-Timing geändert sein kann) zum Vergleich mit einer defekten Spaltenadresse wird von dem Adresspuffer ADBF ausgegeben. Ein Adresserkennungsschaltkreis für defekte Spalten CRDHIT vergleicht einen Ausgangswert CDRI des Zwischenspeicherschaltkreises für defekte Adressen CDRLAT mit einem Ausgabewert RDADCi des Adresspuffers ADBF und gibt ein Ersetzungssignal HITCOL "H" aus, wenn eine defekte Adresse festgestellt wird. Weiterhin gibt der Adresserkennungsschaltkreis für defekte Spalten CDRHIT Defekt-IO-Informationen von einem HITIO aus.

**[0036]** Das Ersetzungssignal HITCOL und das HITIO werden von einem Multiplexer MUX empfangen, um den Ausgangswert des Erkennungsverstärkerschaltkreises SAj durch einen Ausgabewert RSAk eines vorher bestimmten Rettungserkennungsverstärkerschaltkreises zu ersetzen und RSAj als DSj auszugeben. DSj wird über einen externen Anschluss über einen nicht dargestellten Ausgangspuffer ausgegeben, und es ist möglich, defekte Adressen in Einheiten von Spalten zu ersetzen.

**[0037]** Ein Blockadresssignal RDADBi, welches das gleiche wie ADBi sein kann, aber dessen Ausgabe-Timing geändert sein kann) zum Vergleich mit einer defekten Block Adresse wird von dem Adresspuffer ADBF ausgegeben. Ein Adresserkennungsschaltkreis für einen defekten Block BRDHIT vergleicht ein Ausgabesignal BRDi des Adresszwischenspeicherschaltkreises für einen defekten Block BRDLAT mit dem Ausgabewert RDADBi von dem Adresspuffer ADBF und gibt ein Ersetzungssignal HITBLKi = "H" und HITBLKB = "L" aus, wenn ein defekter Adressblock erkannt wird. Der HITBLKB ist ein Disable-Signal für den defekten Block. Das Disable-Signal HITBLKB wird an die Blockdecoder des Hauptblocks BLKi weitergeleitet und zwingt den Hauptblock in einen nicht ausgewählten Zustand. Darüber hinaus wird der redundante Block durch das Ersetzung Signal HITBLKi in einen ausgewählten Zustand versetzt,

welches dem Blockdecoder des Rettungs-(Redundanz-)Blockes BRDBLK zugeführt wird.

**[0038]** In Speicherschaltkreisen für defekte Adressen CRDFUSE und BRDFUSE wird ein nichtflüchtiger Speichertransistor, der die gleiche Struktur wie eine nicht flüchtige Speicherzelle des Speicherzellenfeldes aufweist, als Speicherelement genutzt. Es können die Speicherelemente der Speicherschaltkreise für defekte Adressen CRDFUSE und BRDFUSE aber auch unabhängig von den Hauptspeicherzellen gestaltet sein. Obwohl beispielsweise die gespeicherte Information durch den Zwischenspeicherschaltkreis für defekte Adressen zu der Zeit, wenn die Spannungsversorgung eingeschaltet wird, zwischengespeichert wird, gibt es Fälle, bei denen beispielsweise dieses Mal als Wortleitungsspannung die Versorgungsspannung genutzt wird. Wenn in diesem Fall die Energieversorgungsspannung Low ist (beispielsweise 2V), besteht die Notwendigkeit, die Schwellspannung einer Zelle, die sich in einem gelöschten Zustand befindet, Low zu setzen. Vorzugsweise ist die Schwellspannung des Speichertransistors, der das Speicherelement des Speicherschaltkreises für defekte Adressen ist, geringer als für die Hauptzelle, weil die Zeit, die zur Herstellung der niedrigen Schwellspannung für den gelöschten Zustand von der Schwellspannung einer Zelle in einem neutralen Zustand abhängt.

**[0039]** [Fig. 5](#) zeigt einen Vergleich der Hauptspeicherzelle und des Speichertransistors des Speicherschaltkreises für defekte Adressen, bei denen diese Umstände berücksichtigt wurden.

**[0040]** Wie in [Fig. 5A](#) dargestellt ist, wird eine Kanal-Ionen-Injektion (channel ion injection) zur Erhöhung der Schwellspannung für die Hauptspeicherzelle ausgeführt.

**[0041]** Auf der anderen Seite wird für den Speichertransistor des Speicherschaltkreises für defekte Adressen eine Kanal-Ionen-Injektion nicht ausgeführt, so dass die Schwellspannung gering gehalten wird, wie es in [Fig. 5B](#) dargestellt ist. Trotzdem kann eine leichte Kanal-Ionen-Injektion für den Speichertransistor des Speicherschaltkreises für defekte Adressen ausgeführt werden, so dass die Schwellspannung leicht erhöht wird. Für diese Fälle besteht für den Speichertransistor des Speicherschaltkreises für defekte Adressen die Möglichkeit, dass ein Punch-Trough-Durchbruch (ein Leck in einem Transistor) ein Problem für das Speicherelement des Speicherschaltkreises für defekte Adressen wird. Wie es in [Fig. 5C](#) dargestellt ist, ist es, um dieses Problem zu lösen, effektiv, eine Gate-Länge L1 vorzusehen, die größer ist als die Gate-Länge (Kanallänge) L0 der Hauptzelle.

**[0042]** Ein Busy-Decoder BUSYDEC ist ein Deko-

dierungsschaltkreis der ausgehend von den BRDFU-SE-Informationen Informationen erzeugt, die ausdrücken, zu welcher Bank der ersetzende Rettungsblock gehört, und der ein Signal RDBUSYi erzeugt, welches mit einem erwünschten Busy-Signal BUSY synchronisiert ist.

**[0043]** Als eine Gegenmaßnahme in diesem Ausführungsbeispiel für einen Fall, bei denen Rettungsregionen der Blockrettung und der Spaltenrettung einander überlappen, wird eine Konfiguration vorgenommen, so dass ein Rettungsblockerkennungsschaltkreis CRDBRDHIT in einem Erkennungsschaltkreis für defekte Adressen CDRHIT der Spalten enthalten ist. Gleichzeitig ist ein Encoderschaltkreis ENC des defekten Blockes für den Erkennungsschaltkreis für defekte Adressen BRDHIT des Blockes vorgesehen. In der gleichen Art und Weise und wie bei dem Adresserkennungsschaltkreis für defekte Adressen BRDHIT, wird das Blockadresssignal RDADBi und der Ausgang BRDi des Zwischenspeicherschaltkreises für gerettete Adressen BRDLAT des Blockes als Eingabewert an den Rettungsblockerkennungsschaltkreis CRDBRDHIT geleitet. Darüber hinaus wird ein HIT-Signal der Blockrettung und ein Ausgangssignal ENCi des Encoderschaltkreises ENC an den Rettungsblockerkennungsschaltkreis CRDBRDHIT geleitet. Der Encoderschaltkreis entschlüsselt das Ausgangssignal des Adresserkennungsschaltkreises für defekte Blöcke BRDHIT und gibt ein Ausgangssignal ENCi aus, welches darauf hinweist, welcher Block defekt ist.

**[0044]** In diesem Ausführungsbeispiel wird zum Zeitpunkt der Spaltenrettung der Vergleich der defekten Spaltenadresse RDADBi, die bereits programmiert wurde, gültig, wenn das HIT-Signal der Blockrettung, das in den Adresserkennungsschaltkreis für defekte Spalten CRDBRDHIT eingegeben wurde, in dem Adresserkennungsschaltkreis für defekte Spalten CRDBRDHIT "L" ist (wenn die Blockrettung nicht ausgeführt wird), so dass der Adresserkennungsschaltkreis für defekte Spalten CRDBRDHIT ein Ersetzungssignal für eine Spaltenrettung ausgibt.

**[0045]** Wenn auf der anderen Seite das HIT-Signal der Blockrettung in dem Blockerkennungsschaltkreis für defekte Blöcke CRDBRDHIT "H" ist (wenn eine Blockrettung ausgeführt wird), wird der Vergleich mit dem Ausgangssignal ENCi des Encoderschaltkreises ENC gültig. Darüber hinaus wird eine Kontrolle darüber ausgeführt, dass das Ersetzungssignal der Spaltenrettung, das bereits für den Rettungsblock programmiert wurde, für gültig erklärt wird, und dass ein Ersetzungssignal für eine Spaltenrettung, die neu programmiert wurde, wenn es hinsichtlich eines redundanten Blockes, der in Einheiten von Blöcken ersetzt wird, einen Spaltendefekt gibt, für gültig erklärt wird.

**[0046]** [Fig. 3](#) ist eine Konfiguration eines Adresserkennungsschaltkreises für defekte Spalten CRDHIT. EXNORBLKi bezeichnet eine Mehrzahl von EXNOR-Gattern, die als ein Blockadressenvergleichsschaltkreis dienen, die für jedes Bit das Blockadresssignal RDADBi mit dem Ausgangssignal BRDi des Adresszwischenspeicherschaltkreises für defekte Blöcke BRDHIT vergleicht. EXNORCLI beschreibt eine Mehrzahl von EXNOR-Gattern, die als ein Spaltenadressvergleichsschaltkreis wirken, welche das Spaltenadresssignal RDACi mit dem Ausgangssignal CRDi des Adresszwischenspeicherschaltkreises für defekte Spalten CRDLAT vergleicht.

**[0047]** Weiterhin bezeichnet EXNORRDk EXNOR-Gatter, die als ein Rettungsblockerkennungsschaltkreis dienen, der die Ausgangssignale ENCi des Encoderschaltkreises ENC, der zu dem Erkennungsschaltkreis für defekte Blockadressen hinzugefügt ist, mit den Ausgangssignalen BRDi der Adresszwischenspeicherschaltkreise BRDLAT für defekte Blockadressen vergleicht.

**[0048]** Die Ausgangssignale der Gatter EXNORBLKi werden als Eingangssignale für ein erstes NAND-Gatter NAND1 genutzt, und die Ausgangssignale der Gatter EXNORBRDk werden als Eingangssignale für ein zweites NAND-Gatter NAND2 genutzt. Die Ausgangssignale der Gatter EXNORCLI werden als Eingangssignale für die NAND-Gatter NAND1 und NAND2 genutzt. Hierbei sind die Gatter EXNORBLKi und EXNORCLI die Hauptanteile der Adresserkennungsschaltkreise für defekte Spalten CRDHIT in [Fig. 1](#), und das Gatter EXNORRDk entspricht dem Erkennungsschaltkreis für defekte Blöcke CRDBRDHIT, der zu dem Adresserkennungsschaltkreis für defekte Spalten hinzugefügt ist.

**[0049]** Für die Adresse, für die eine Blockrettung ausgeführt wird (BLKHIT = "L"), ist das erste NAND-Gatter NAND1 in den aktiven Zustand versetzt. Somit wird ein HIT-Signal zur Ausführung einer Spaltenersetzung in Abhängigkeit des Vergleichsergebnisses der Gatter EXNORBLKi und EXNORCLI ausgegeben. Weiterhin wird bei einer Adresse, bei der eine Blockrettung ausgeführt wird (HITBLK = "H"), das erste NAND-Gatter NAND1 inaktiv. Im Ergebnis wird der Ausgangswert des HIT-Signals der Spaltenersetzung ungültig, wenn ein Block, der einer defekten Spaltenadresse entspricht, die bereits programmiert wurde, nachträglich defekt wird.

**[0050]** Wenn weiterhin das HIT-Signal "H" ist, wird das zweite NAND-Gatter NAND2 anstelle des ersten NAND-Gatter NAND1 in den aktiven Zustand versetzt, und das HIT-Signal HITC wird in Abhängigkeit von dem festgestellten Ergebnis der Gatter EXNORCLI und EXNORRDk ausgegeben. Mit anderen Worten gibt das NAND-Gatter NAND2 das HIT-Signal HITC in Übereinstimmung mit dem Ausgangswert

des Gatters EXNOTRDk aus, welches den Rettungsblock erkennt, und der Ausgabewert des Gatters EX-NORCLi basiert auf dem Ergebnis der Programmierung des Adressspeicherschaltkreises CRDFUSE der defekten Spaltenadresse in dem Redundanzblock, der die Defektblockrettung ausführt.

**[0051]** In einer tatsächlichen Halbleiterspeichervorrichtung ist eine Vielzahl von Schaltkreisen CRDHIT in der Speichervorrichtung enthalten, und OR-Signale der entsprechenden HITC-Signale sind die Signale HITCOL zur Aktivierung des Erkennungsverstärkers RSA der redundanten Spalten. HITIO, welches eine Defect-IO-Information ist, ist ein Signal zur Ersetzung des Erkennungsverstärkers des defekten IO. Es sei darauf hingewiesen, dass ein Enable-Signal ENABLE, welches an die NAND-Gatter NAND1 und NAND2 gelegt wird, separat in dem Speicherschaltkreis für defekte Adressen CRDFUSE von den Adressdaten programmiert ist, um den Fall zu vermeiden, bei dem der Speicherschaltkreis für defekte Adressen CRDFUSE fälschlicherweise einem "ALLE-1-Zustand" als gültig behandelt, der noch nicht programmiert wurde.

**[0052]** [Fig. 4](#) stellt eine konkrete Konfiguration des Adresserkennungsschaltkreises für defekte Blöcke BRDHIT dar. EXNORBLKi beschreibt eine Mehrzahl von EXNOR-Gattern die als ein Adressvergleischaltkreis dienen, welcher bitweise das Blockadressensignal mit dem Ausgangssignal BRDi des Adresszwischenspeicherschaltkreises für defekte Blöcke BRDLAT vergleicht. Wenn alle Ausgangssignale des Gatters EXNORBLKi "H" werden, wird das HIT-Signal HITBLKi als ein Rettungsblockauswahlsignal von einem AND-Gatter AND ausgegeben.

**[0053]** Das Enable-Signal ENABLE ist ein Signal zur Aktivierung des Schaltkreises. Das Disable-Signal DISABLE ist ein Signal, das den Defekt in „H“ versetzt, wenn es gewünscht wird, das Aktivsignal des Schaltkreises zurückzusetzen, wenn ein Defekt neu in dem Redundanzblock gefunden wird oder in einer ähnlichen Zustand, nachdem der Schaltkreis aktiviert wurde. Dieses Enable-Signal ENABLE und Disable-Signal DISABLE werden zusammen mit den defekten Adressen in die Adressspeicherschaltkreis BRDFUSE programmiert.

**[0054]** In einem tatsächlichen Speicher ist eine Mehrzahl von diesen Schaltkreisen enthalten, und die OR-Signale der entsprechenden HITBLKi werden als Ersetzungssignale HITBLK ausgegeben, und die invertierten Signale sind die Signale HITBLKB zur Deaktivierung des Hauptblockes.

**[0055]** Wie oben beschrieben wird entsprechend dem derzeitigen Modus die vorherige Spaltenrettung für ungültig erklärt, wenn es nach einer Spaltenersetzungsaktion eine defekte Spalte in einem Rettungs-

block (Redundanzblock) gibt, und es kann eine Defektspaltenrettung in dem Redundanzblock ausgeführt werden. Dadurch ist die Defektrettung des EEPROM verbessert werden.

**[0056]** Es sei darauf hingewiesen, dass in dem vorliegenden Ausführungsbeispiele vorzugsweise ein Testschaltkreis vorgesehen wird, der aktiv das Ersetzungssignal HITBLKi des Rettungsblockes „H“ setzt, so dass der Redundanzblock BRDBLK aktiv selektiert werden kann. Genauer – wie in [Fig. 1](#) dargestellt – ist ein Testmodus zur Ausführung eines Tests des Redundanzblockes BRDBLK vorgesehen, welcher ein Testsignal TEST von außen auf den Adresserkennungsschaltkreis für defekte Blöcke lenkt und der aktiv das Ersetzungssignal HITBLKi „H“ setzt. Dementsprechend ist der Grad der Freiheit eines Selektions-tests für gute Bauteile noch größer, wenn ein Spaltendefekt in dem Redundanzblock BRDBLK im Voraus gefunden wird und eine Spaltenrettung durch Programmierung des Spaltendefektes ausgeführt wird.

**[0057]** Darüber hinaus wurde an diesem Ausführungsbeispiel erklärt, wie eine Kombination der Spaltenrettung und der Blockrettung gemacht wird, die eine Rettung des Spaltenzellenfeldes jeder Einheit in dem Block durchführt. Die vorliegende Erfindung ist effektiv bei Halbleiterspeichervorrichtungen, die Rettungsverfahren nutzen, die zwei oder mehr Arten von Rettungsschaltkreisen haben, deren Rettungsregionen überlappen und bei denen die Größe der Rettungsbereiche unterschiedlich sind, wie es bei einer Kombination von Zeilenrettung und Blockrettung der Fall ist, die eine Rettung für das Zeilenzellenfeld jeder Einheit (eine oder mehrere Zeilen) innerhalb des Blocks ausführt.

**[0058]** Die vorliegende Erfindung kann nicht nur auf EEPROMs angewendet werden, sondern kann auch auf andere Halbleiterspeicher wie DRAM oder ähnliche in ähnlicher Weise angewendet werden.

**[0059]** Darüber hinaus kann als Speicherschaltkreis für defekte Adressen anstelle eines Speicherlements, das ähnlich einer nichtflüchtigen Speicherzelle ist, auch eine elektrische Sicherung verwendet werden.

**[0060]** Wie oben beschrieben wird entsprechend der vorliegenden Erfindung ein Halbleiterspeicher vorgestellt, bei dem eine hohe Defektrettungseffizienz ermöglicht wird, wenn zwei Arten von Rettungsschaltkreisen verwendet werden, deren Rettungsregionen unterschiedlich sind, ohne eine Beeinträchtigung der Rettungseffizienz infolge von Interferenzen zwischen den Rettungsschaltkreisen.

## Patentansprüche

1. Eine Halbleiterspeichervorrichtung mit

- einer Mehrzahl von Speicherzellenblöcken (BLKi), jeder mit einer Mehrzahl von Speicherzellen;

- einem ersten Redundanzzellenfeld (MMACRD), das für jedes der Speicherzellenblöcke (BLKi) verfügbar ist, wobei das erste Redundanzzellenfeld konfiguriert ist, um ein defektes Zellenfeld in dem ersten Speicherzellenblock abzusichern;

- einem Redundanzzellenblock (BRDBKLi), der für die Mehrzahl der Speicherzellenblöcke (BLKi) verfügbar ist, wobei der Redundanzblock konfiguriert ist, um einen defekten Block der Speicherzellenblöcke (BLKi) abzusichern;

- einem zweiten Redundanzzellenfeld (MMACRD), das für den Redundanzzellenblock (BRDBKLi) verfügbar ist, wobei das zweite Redundanzzellenfeld konfiguriert ist, um ein defektes Zellenfeld in dem Redundanzzellenblock abzusichern;

- einem ersten Defektsicherungsschaltkreis (CRDFUSE, CRDHIT), der einen ersten Speicheradressensschaltkreis (CRDFUSE) und einen ersten Adresserkennungsschaltkreis (CRDHIT) aufweist, wobei der erste Speicheradressensschaltkreis (CRDFUSE) konfiguriert ist, um eine Adresse des defekten Zellenfeldes in dem Speicherzellenblock zu speichern, und wobei der erste Adresserkennungsschaltkreis (CRDHIT) konfiguriert ist, um ein Signal der gespeicherten Adresse und ein Adresssignal von extern zu vergleichen und ein Ersatzsignal zum Ersetzen des defekten Zellenfeldes in den Speicherzellenblöcken durch das erste Redundanzzellenfeld zu ersetzen; und

- einem zweiten Defektsicherungsschaltkreis (BRDFUSE, BRDHIT), der einen zweiten Speicheradressensschaltkreis (CRDFUSE) und einen zweiten Adresserkennungsschaltkreis (BRDHIT) aufweist, wobei der zweite Speicheradressensschaltkreis (BRDFUSE) konfiguriert ist, um eine Adresse des defekten Speicherblockes der Mehrzahl der Speicherzellenblöcke zu speichern, und wobei der Adresserkennungsschaltkreis (BRDHIT) konfiguriert ist, um ein Signal der gespeicherten Adresse des defekten Blockes und ein Adresssignal von extern zu vergleichen, um ein Ersatzsignal zum Ersetzen des defekten Blockes aus der Mehrzahl der Speicherzellenblöcke durch den Redundanzzellenblock zu ersetzen, **dadurch gekennzeichnet**, dass

- der ersten Defektsicherungsschaltkreis (CDRFUSE, CRDHIT) einen Gate-Schaltkreis aufweist,

- welcher das Ersatzsignal, das von dem ersten Adresserkennungsschaltkreis (CRTHIT) als gültig ausgegeben wurde, an eine Adresse ausgibt, an welcher der zweite Defektsicherungsschaltkreis nicht aktiviert ist, um eine Blockabsicherung auszuführen, und

- welcher ein Signal ausgibt, das darauf hinweist, welcher Block ein defekter Block ist, der durch den zweiten Defektsicherungsschaltkreis (BRDFUSE,

BRDHIT) als gültig bei einer Adresse ausgegeben wurde, bei welcher der zweite Defektsicherungsschaltkreis aktiviert ist, um eine Blocksicherung auszuführen; und

– wobei der erste Defektsicherungsschaltkreis (BRDFUSE, BRDHIT) den Gate-Schaltkreis derart steuert, dass durch das Ersatzsignal, das durch den zweiten Defektsicherungsschaltkreis ausgegeben wurde, das Ersatzsignal, das durch den ersten Adresserkennungsschaltkreis hinsichtlich des defekten Blockes ausgegeben wurde, ungültig gemacht wird, und ein Ersatzsignal, das durch den ersten Adresserkennungsschaltkreis hinsichtlich des Ersetzens des defekten Blockes durch den Redundanzblock gültig gemacht wird.

2. Eine Halbleiterspeichervorrichtung nach Anspruch 1, dadurch gekennzeichnet, dass der erste Defektsicherungsschaltkreis (CRDFUSE; CRDHIT) einen ersten Defektblock-Erkennungsschaltkreis aufweist, der den Gate-Schaltkreis derart steuert, dass der defekte Block auf der Basis des Ersatzsignals erkannt wird, das von dem zweiten Defektsicherungsschaltkreis (BRDFUSE, BRDHIT) ausgegeben wird, und dem Signal, das darauf hinweist, welcher Block ein defekter Block ist, das durch den zweiten Defektsicherungsschaltkreis (BRDFUSE, BRDHIT) basierend auf dem erkannten Ergebnis gültig gemacht und ausgegeben wird.

3. Eine Halbleiterspeichervorrichtung nach Anspruch 1, dadurch gekennzeichnet, dass die Speicherzellen (MC) elektrisch löschenbare und wiederbeschreibbare, nichtflüchtige Speicherzellen sind.

4. Eine Halbleiterspeichervorrichtung nach Anspruch 3, dadurch gekennzeichnet, dass die Speicherzellen (MC) des ersten und zweiten Speicheradressschaltkreises (CRDFUSE, BRDFUSE) elektrisch löschenbare und wiederbeschreibbare, nichtflüchtige Speichertransistoren sind, die die gleiche Struktur wie die nichtflüchtigen Speicherzellen aufweisen.

5. Eine Halbleiterspeichervorrichtung nach Anspruch 4, dadurch gekennzeichnet, dass die nichtflüchtigen Speichertransistoren auf eine niedrigere Schwellspannung gesetzt sind als die der nichtflüchtigen Speicherzellen.

6. Eine Halbleiterspeichervorrichtung nach Anspruch 5, dadurch gekennzeichnet, dass die nichtflüchtigen Speichertransistoren eine Kanallänge aufweisen, die länger ist als die der nichtflüchtigen Speicherzellen.

7. Eine Halbleiterspeichervorrichtung nach Anspruch 1, dadurch gekennzeichnet, dass die Mehrzahl der Blöcke (BLKi) in eine Mehrzahl von Bänken (BANK0, BANK1) gruppiert ist, und während ein Lö-

schen oder Schreiben von Daten auf eine gegebenen Bank ausgeführt wird, das Lesen von Daten aus einer anderen Bank möglich ist.

8. Eine Halbleiterspeichervorrichtung nach Anspruch 1, dadurch gekennzeichnet, dass in einem Testmodus der Redundanzblock (BRDBLK<sub>i</sub>) durch Eingabe eines Testsignals gesetzt wird, um die Ersatzsignalausgabe von dem zweiten Defektsicherungsschaltkreis (BRDFUSE, BRDHIT) zu erzwingen.

Es folgen 5 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6

FIG. 7