(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) . Int. Cl.

G11C 11/41 (2006.01)

(11) 공개번호 10-2007-0038015

(43) 공개일자 2007년04월09일

(21) 출원번호 10-2006-0097245

(22) 출원일자 2006년10월02일

심사청구일자 없음

(30) 우선권주장 JP-P-2005-00290889 2005년10월04일 일본(JP)

(71) 출원인 가부시끼가이샤 르네사스 테크놀로지

일본 100-6334 도쿄도 지요다구 마루노우찌 2-조메 4-1

(72) 발명자 야마오카 마사나오

일본국 도쿄토 치요다쿠 마루노우치 1쵸메6반1고 가부시끼가이샤히타치

세이사쿠쇼 지테키자이산肯혼부나이

가와하라 타카유키

일본국 도쿄토 치요다쿠 마루노우치 1쵸메6반1고 가부시끼가이샤히타치

세이사쿠쇼 지테키자이산肯혼부나이

(74) 대리인 특허법인 원전

전체 청구항 수 : 총 20 항

(54) 반도체기억장치

(57) 요약

본 발명은, 미세화된 트랜지스터를 사용한 저소비 전력SRAM에 있어서, 드레인 전극으로부터 기판전극에 흐르는 리크 전류 및 서브 스레숄드 리크전류를 저감하는 것에 의해 LSI원로 전체의 소비 전력을 저감하는 동시에, 메모리 셀의 기록·판독시의 동작 안정성을 향상시키는 기술의 제공에 있다.

또한, 트랜지스터의 수를 증가 등에 의한 메모리 셀의 증가를 억제하고, 칩 면적의 증대를 억제하는 기술의 제공에 있다.

박스층을 구비하는 SOI 또는 FD-SOI 트랜지스터를 사용해서 구성된 SRAM 메모리 셀에 있어서, 구동 트랜지스터의 박스 충하의 웰 전위를 제어함으로써 트랜지스터의 문턱치전압을 제어해서 전류를 증가시켜서, 메모리 셀의 안정 동작을 가능하게 한다.

대표도

도 1

특허청구의 범위

## 청구항 1.

데이터를 기억하는 래치부와, 상기 데이터를 전송하는 전송부를 구비하여 이루어지는 스태틱형의 메모리 셀을 구비하고, 상기 래치부 및 상기 전송부는,

채널 부분이 절연막으로 이루어지는 박스층에 의해 기판부분과 절연된 SOI층을 구비하는 트랜지스터를 포함하고,

상기 메모리 셀의 데이터의 기록 동작시와 데이터의 판독 동작시에 상기 메모리 셀 내의 적어도 하나의 트랜지스터의 문턱치전압을 변화시키는 것을 특징으로 하는 반도체기억장치.

## 청구항 2.

제 1항에 있어서,

상기 래치부는, 접지 전위선에 그 소스 전극이 접속된 제1의 도전형 채널을 구비하는 구동 트랜지스터 쌍과, 상기 접지선의 전위보다 높은 전위가 되는 제1의 전원선에 그 소스 전극이 접속된 제2의 도전형 채널을 구비하는 부하 트랜지스터 쌍을 포함하여 구성되며,

상기 전송부는, 상기 메모리 셀에 액세스하기 위한 비트선과 정보를 유지하는 기억 노드의 사이에 접속된 제1의 도전형 채널을 구비하는 전송 트랜지스터 쌍을 포함해서 구성되는 것을 특징으로 하는 반도체기억장치.

## 청구항 3.

제 2항에 있어서,

상기 메모리를 구성하는 트랜지스터의 적어도 하나는, SOI층이 완전히 공핍화한 FD-SOI구조를 구비하는 것을 특징으로 하는 반도체기억장치.

## 청구항 4.

제 2항에 있어서,

상기 래치부를 구성하는 트랜지스터의 문턱치전압을 변화시키는 것을 특징으로 하는 반도체기억장치.

## 청구항 5.

제 2항에 있어서,

상기 전송부를 구성하는 트랜지스터 쌍의 문턱치전압을 변화시키는 것을 특징으로 하는 반도체기억장치.

## 청구항 6.

제 2항에 있어서,

상기 메모리 셀의 데이터의 기록 동작시와 데이터의 판독 동작시에 상기 박스층아래에 설치된 도전층으로 이루어지는 웨일층에 적절히 전압을 인가하기 위한 제2의 전원선을 구비하고,

상기 제2의 전원선이 상기 비트선에 병행하는 방향으로 설치되는 것을 특징으로 하는 반도체기억장치.

### 청구항 7.

제 2항에 있어서,

상기 메모리 셀의 데이터의 기록 동작시와 데이터의 판독 동작시에 상기 박스층아래로 설치된 도전층으로 이루어지는 웨爾층에 적절히 전압을 인가하기 위한 제2의 전원선을 구비하고, 상기 제2의 전원선이 상기 비트선과 교차하는 방향으로 설치되는 것을 특징으로 하는 반도체기억장치.

### 청구항 8.

제 2항에 있어서,

상기 메모리 셀은, 기록시에 있어서의 상기 부하 트랜지스터의 문턱치전압이 판독시의 문턱치전압보다 높은 값으로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 9.

제 2항에 있어서,

상기 메모리 셀은, 기록시에 있어서의 상기 전송 트랜지스터의 문턱치전압이 판독시의 문턱치전압보다 높은 값으로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 10.

제 2항에 있어서,

상기 메모리 셀은, 기록시에 있어서의 상기 구동 트랜지스터의 문턱치전압이 판독시의 문턱치전압보다 낮은 값으로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 11.

제 6항에 있어서,

상기 메모리 셀은, 기록시의 부하 트랜지스터의 웨爾 전위가, 판독시의 상기 부하 트랜지스터의 웨爾 전위보다 높은 전압으로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 12.

제 6항에 있어서,

상기 메모리 셀은, 기록시의 전송 트랜지스터의 웨爾 전위가, 판독시의 상기 전송 트랜지스터의 웨爾 전위보다 낮은 전압으로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 13.

제 6항에 있어서,

상기 메모리 셀은, 기록시의 구동 트랜지스터의 웰 전위가, 판독시의 상기 구동 트랜지스터의 웰 전위보다 낮은 전압으로 제어되는 것을 특징으로 하는 반도체기억장치.

#### 청구항 14.

제 6항에 있어서,

데이터 유지 상태에 있는 메모리 셀로의 액세스가 없는 스탠바이 상태에서,

상기 부하 트랜지스터의 웰 전위는, 상기 제1의 전원선의 전위보다 높은 전위로 제어되는 것을 특징으로 하는 반도체기억장치.

#### 청구항 15.

제 6항에 있어서,

데이터 유지 상태에 있는 메모리 셀로의 액세스가 없는 스탠바이 상태에서,

상기 구동 및 전송 트랜지스터의 웰 전위는, 접지선의 전위보다 낮은 부(負)의 전위로 제어되는 것을 특징으로 하는 반도체기억장치.

#### 청구항 16.

반도체기판에 형성된 도전층으로 이루어지는 웰층과, 상기 웰층 위로 형성된 절연막으로 이루어지는 박스층과, 상기 박스층 위로 형성된 소스층, 드레인층 및 상기 소스층과 드레인층에 끼워져서 형성된 채널층과, 상기 채널층 위로 게이트 절연막을 통해서 형성된 게이트 전극을 구비하는 SOI형 트랜지스터를 복수 구비하여 이루어지고, 스탠드Off형 메모리 셀로서 기능하는 반도체기억장치이며,

접지 전위선에 그 소스 전극이 접속되어, 상기 SOI형 트랜지스터로 이루어지는 제1의 도전형 채널을 구비하는 구동 트랜지스터 쌍과, 상기 접지선의 전위보다 높은 전위가 되는 제1의 전원선에 그 소스 전극이 접속되고, 드레인 전극을 통해서 상기 구동 트랜지스터와 접속된 상기 SOI형 트랜지스터로 이루어지는 제2의 도전형 채널을 구비하는 부하 트랜지스터 쌍과,

상기 메모리 셀에 액세스하기 위한 비트선과 정보를 유지하는 기억 노드의 사이에 접속되며, 상기 SOI형 트랜지스터로 이루어지는 제1의 도전형 채널을 구비하는 전송 트랜지스터 쌍을 구비하고,

상기 구동 트랜지스터 쌍의 한쪽이 형성되는 웰층과, 상기 전송 트랜지스터 쌍의 한쪽이 형성되는 웰층이, 공통의 제1웰층 위로 설치되며,

상기 부하 트랜지스터 쌍의 한쪽과, 상기 부하 트랜지스터 쌍의 다른 쪽이 공통인 제2웰층위로 설치되며,

상기 제1웰층과 상기 제2웰층이 서로 전기적으로 분리되는 것을 특징으로 하는 반도체기억장치.

#### 청구항 17.

제 16항에 있어서,

상기 부하 트랜지스터 쌍의 한쪽과, 상기 부하 트랜지스터 쌍의 다른 쪽이, 다른 웨이터에 형성되는 것을 특징으로 하는 반도체기억장치.

### 청구항 18.

복수의 트랜지스터를 포함해서 이루어지는 스탠드형 메모리 셀이 열(列)방향 및 행(行)방향으로 배열되어 이루어지고, 메모리 셀 어레이로서 기능하는 반도체기억장치이며,

상기 메모리 셀에 액세스하기 위한 비트선을 복수 구비하고,

상기 복수의 비트선의 하나에 접속된 복수의 메모리 셀을 구성하는 동일한 열(列)내에 형성된 각각의 트랜지스터가 공통되어 설치되는 제1웨이터,

상기 복수의 비트선의 다른 선에 접속된 복수의 메모리 셀을 구성하는 동일한 열내에 형성된 각각의 트랜지스터가 공통되어 설치된 제2웨이터를 구비하고, 상기 제1웨이터의 전위가 상기 제2웨이터의 전위와 다른 전위로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 19.

제 18항에 있어서,

데이터를 기록하기 위해서 액세스된 메모리 셀이 존재하는 열에 접속된 메모리 셀내에 형성된 제2의 도전형 채널을 구비하는 트랜지스터의 웨이터는, 액세스되는 메모리 셀이 존재하지 않는 열에 접속된 메모리 셀내에 형성된 제2의 도전형 채널을 구비하는 트랜지스터의 웨이터보다 낮은 전위로 제어되는 것을 특징으로 하는 반도체기억장치.

### 청구항 20.

제 18항에 있어서,

데이터를 기록하기 위해서 액세스된 메모리 셀이 존재하는 열에 접속된 메모리 셀 내에 형성된 제1의 도전형 채널을 구비하는 트랜지스터의 웨이터는, 액세스되는 메모리 셀이 존재하지 않는 열에 접속된 메모리 셀내에 형성된 제1의 도전형 채널을 구비하는 트랜지스터의 웨이터보다 낮은 전위로 제어되는 것을 특징으로 하는 반도체기억장치.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 스탠드 메모리(SRAM)회로가 반도체 칩 상에 접속된 반도체집적회로에 관한 것이고, 특히, SRAM집적회로장치의 동작에 필요한 동작 마진을 넓히는 구성에 관한 것이다.

최근, 반도체장치, 예컨대 SRAM 회로 등의 반도체장치에 대하여는, 고속화 및 저소비 전력화가 강하게 요청되고 있다.

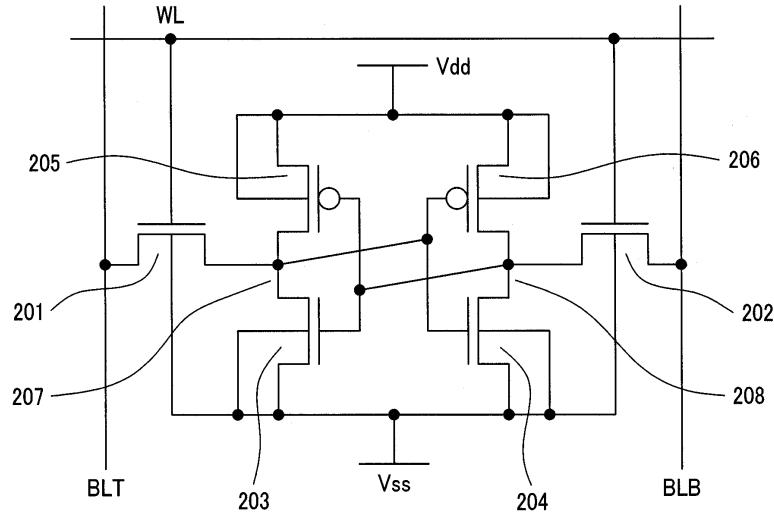

도 32에 종래의 SRAM 메모리 셀 회로를 나타낸다. 여기에서, BLT 및 BLB은 비트선, WL은 워드선, Vdd는 하이레벨의 전원선, Vss는 접지 전위선, 201 및 202는 메모리 셀에 액세스하기 위한 전송 트랜지스터, 203 및 204는 메모리 셀의 데이터를 유지하기 위해서 기억 노드를 구동하는 구동 트랜지스터, 205 및 206는 메모리 셀 데이터를 유지하기 위해서 전하를 공급하는 부하 트랜지스터, 207 및 208은 기억 노드이다.

SRAM 회로의 소비 전력을 저감하기 위해서는 전원전압을 저하시키는 것이 가장 단순하고 효과가 큰 방법이다.

그러나, 낮은 전원전압에서는 트랜지스터의 동작에 필요한 동작 마진이 저하하고, 동작이 불안정해진다. 이 문제의 해결을 겨냥한 기술로서, 특허문헌1(특개평11-39879호)에서는, SRAM 셀을 구성하는 트랜지스터의 기판전위를 제어하고, 기록시의 고속화와 판독시의 소비 전력을 저감하는 기술이 개시된다. 또한, 특허문헌2(특개 2003-151277호)에서는, 1개의 메모리 셀에 2종류의 Vth를 가질 트랜지스터를 사용하며, 고속·저전압동작을 가능하게 하는 회로기술이 개시된다. 더욱이, 특허문헌3(특개 2003-86713호)에서는, SRAM 메모리 셀을 구성하는 트랜지스터의 게이트 폭을 좌우의 기억 노드에 접속되는 트랜지스터로 비대칭으로 하는 것으로써 동작시의 데이터 파괴를 막아 저전압동작을 가능하게 하는 기술이 개시된다.

[특허문헌1]특개평11-39879호 공보

[특허문헌2]특개 2003-151277호 공보

[특허문헌3]특개 2003-86713호 공보

### 발명이 이루고자 하는 기술적 과제

LSI (Large Scale (in)tegrated circuit: 대규모 집적회로)의 저소비 전력화 및 LSI중의 트랜지스터의 미세화에 의해, LSI의 전원전압이 저하된다. 예를 들면, 90nm 프로세스에서는, 전원전압 1.2V에서 동작하는 LSI가 제조된다. 전원전압이 하강하면, SRAM 회로에 있어서는 기록·판독의 동작시의 동작 안정성이 저하하고, 동작이 어렵게 된다. 메모리 셀을 구성하는 각 트랜지스터의 구동력 즉 전류가 변화되면 기록, 판독의 안정성 및 동작속도의 각 성능이 변화된다.

따라서, 메모리 셀을 구성하는 각 트랜지스터의 성능을 적절하게 제어할 수가 있으면 각각의 성능을 향상할 수가 있다. 또 전원전압을 저하시키면 트랜지스터의 구동 전류가 내려가기 때문에, 회로의 동작속도가 저하된다. 이 동작속도의 저하를 억제하기 위해서는 트랜지스터의 문턱치전압(Vth)을 낮게 해서 전원전압이 저하해도 동작 전류의 저하를 억제하는 방법이 얻어진다.

그러나, 트랜지스터의 Vth를 저하시키면 서브 스레숄드 리크(sub threshold leak)전류로 불리는 off된 트랜지스터의 소스드레인간을 흐르는 리크 전류가 증가하고, 비동작 상태에서의 소비 전력이 증가한다는 문제가 있다. 특허문헌1의 예에서는, SRAM 메모리 셀 중의 적절한 트랜지스터의 기판전위를 제어함으로써 트랜지스터의 성능을 제어하고, 비동작시의 저전력을 실현하는 기술이 개시된다. n채널형 벌크 CMOS트랜지스터의 백 게이트에 소스 전극보다 낮은 전압을 인가하면 트랜지스터의 Vth를 높게 제어하는 것으로써 가능하며, 트랜지스터의 서브 스레숄드 리크를 억제할 수 있다.

그러나, 제조 프로세스 90nm이하의 미세화된 벌크 CMOS 트랜지스터의 백 게이트를 제어하면, 접합 리크 전류로 불리는 드레인 전극으로부터 기판전극에 흐르는 리크 전류가 증가하고, 서브 스레숄드 리크전류는 저하되어 있지만, 트랜지스터 전체에서 본 리크 전류는 증가하여 회로전체의 소비 전력을 저감할 수 없다는 문제가 있다.

특허문헌2의 예에서는, 1개의 메모리 셀을 구성하는 트랜지스터의 수를 증가시키는 동시에 2종류의 Vth를 가질 트랜지스터를 사용하는 것으로써 메모리 셀 내의 트랜지스터의 구동력을 적절하게 설정하고, 메모리 셀의 기록·판독시의 동작 안정성을 향상시키고 있다.

그러나, 메모리 셀의 소자수가 증가하기 때문에 크게 메모리 셀 면적이 증가해버린다. 메모리 회로는 될 수 있는 한 많은 용량을 탑재해야 한다는 요구가 있기 때문에, 면적이 증가하는 메모리 셀을 사용하는 것은 어렵다는 문제가 있다.

특허문헌3의 예에서는, 원래 대상이어야 할 메모리 셀 내의 트랜지스터의 게이트 폭에 비대칭성을 갖게 하는 것으로써 메모리 셀 내의 트랜지스터의 구동력을 적절하게 설정하고, 이것에 의해 메모리 셀이 가질 기록·판독시의 동작 안정성을 향상시켜 있다.

그러나, 게이트 폭을 좌우로 변화시키기 위해서 메모리 셀의 대칭성을 상실한다. 메모리 셀을 제조할 때에는, 같은 메모리 셀을 대량으로 반복하여 배치할 수 있다는 규칙성이 높고 대칭적인 메모리 셀을 사용한다는 대칭성이 높아서 정밀도가 높은 메모리 셀을 만들고 있지만, 대칭성이 무너져버리면 이 제조 정밀도가 저하해서, 성능이 저하한다는 문제가 있다. 또한 다른 게이트 폭을 사용하는 것은 메모리 셀 면적이 증대한다는 문제도 악화되어 있어, 이것은 특허문현2의 예와 같은 면적 증가라는 문제에 이른다.

본 발명이 해결하고자 하는 문제는, 미세화된 트랜지스터를 사용한 저소비 전력SRAM에 있어서, 드레인 전극으로부터 기판전극에 흐르는 리크 전류 및 서브 스레숄드 리크전류를 저감하는 것에 의해 LSI 회로전체의 소비 전력을 저감하는 기술을 제공하는 점에 있다.

또한, 메모리 셀의 기록·판독시의 동작 안정성을 향상시키는 기술의 제공에 있다.

더욱이, 트랜지스터의 수를 증가 등에 의한 메모리 셀의 증가를 억제하고, 칩 면적의 증대를 억제하는 기술의 제공에 있다.

#### [문제를 해결하기 위한 수단]

본 발명의 대표적인 것의 하나의 예를 게시하면, 아래와 같다. 즉, 본 발명의 반도체기억장치는, 데이터를 기억하는 래치부와, 데이터를 전송하는 전송부를 구비하여 이루어지는 스태틱형의 메모리 셀을 구비하고, 그 래치부 및 전송부는, 채널부분이 절연막으로 이루어지는 박스충에 의해 기판부분과 절연된 SOI충을 구비하는 트랜지스터를 포함하고, 메모리 셀의 데이터의 기록 동작시와 데이터의 판독 동작시에, 메모리 셀 내의 적어도 하나의 트랜지스터의 문턱치전압을 변화시키는 것을 특징으로 하는 것이다.

이에 의해서, 스태틱형의 메모리 셀을 SOI 트랜지스터로 구성하고, 각 트랜지스터의 매립 산화막(박스:Buried OXide)충의 아래쪽의 웨일충의 전위를 적절하게 제어함으로써 각 트랜지스터의 전류를 변화시켜 SRAM의 각 성능을 향상시키는 것이 가능해진다. 웨일충은 박스충에 의해 트랜지스터가 형성되는 SOI충과는 전기적으로 절연되기 때문에 여분인 리크 전류는 증가하지 않는다.

또한, 본 발명의 반도체기억장치는, 반도체기판에 형성된 도전층으로 이루어지는 웨일충과, 그 웨일충 위로 형성된 절연막으로 이루어지는 박스충과, 박스충위로 형성된 소스충, 드레인충 및 소스충과 드레인충에 끼워져 있어서 형성된 채널충과, 그 채널충 위로 게이트 절연막을 통해서 형성된 게이트 전극을 구비하는 SOI형 트랜지스터를 복수 구비해서 이루어지고, 스태틱형 메모리 셀로서 기능하는 반도체기억장치이며, 접지 전위선에 그 소스 전극이 접속되어, SOI형 트랜지스터로 이루어지는 제1의 도전형 채널을 구비하는 구동 트랜지스터 쌍과, 접지선의 전위보다 높은 전위가 되는 제1의 전원선에 그 소스 전극이 접속되어, 드레인 전극을 통해서 상기 구동 트랜지스터와 접속된 SOI형 트랜지스터로 이루어지는 제2의 도전형 채널을 구비하는 부하 트랜지스터 쌍과, 메모리 셀에 액세스하기 위한 비트선과 정보를 유지하는 기억 노드의 사이에 접속되며, SOI형 트랜지스터로 이루어지는 제1의 도전형 채널을 구비하는 전송 트랜지스터 쌍을 구비하고, 구동 트랜지스터 쌍의 한쪽이 형성되는 웨일충과, 전송 트랜지스터 쌍의 한쪽이 형성되는 웨일충이, 공통의 제1웨일충 위로 설치되어, 부하 트랜지스터 쌍의 한쪽과, 상기 부하 트랜지스터 쌍의 다른 쪽이 공통인 제2웨일충 위로 설치되어, 제1웨일충과 제2웨일충이 서로 전기적으로 분리되는 것을 특징으로 하는 것이다.

이것에 의해, 적절하게 웨일콘택트를 형성하면, 메모리 셀 면적도 증가하지 않는다.

더욱이, 본 발명의 반도체기억장치는, 복수의 트랜지스터로 이루어지는 스태틱형 메모리 셀이 열방향 및 행방향으로 배열되어 이루어지고, 메모리 셀 어레이로서 기능하는 반도체기억장치이며, 메모리 셀에 액세스하기 위한 비트선을 복수 구비하고, 복수의 비트선의 하나에 접속된 복수의 메모리 셀을 구성하는 동일한 열내에 형성된 각각의 트랜지스터가 공통되어 설치되는 제1웨일충과, 복수의 비트선의 다른 선에 접속된 복수의 메모리 셀을 구성하는 동일한 열내에 형성된 각각의 트랜지스터가 공통되어 설치된 제2웨일충을 구비하고, 제1웨일충의 전위가 상기 제2웨일충의 전위와 다른 전위로 제어되는 것을 특징으로 하는 것이다.

이것에 의해, 2종류의 전압의 전원을 메모리내의 특정한 노드에 선택적으로 인가하는 것으로써 트랜지스터의 전류를 변화시켜서 각 성능을 향상시키는 것이 가능해진다.

#### 발명의 구성

이하에서, 본 발명을, 도면을 사용해서 상세하게 설명한다.

<실시예1>

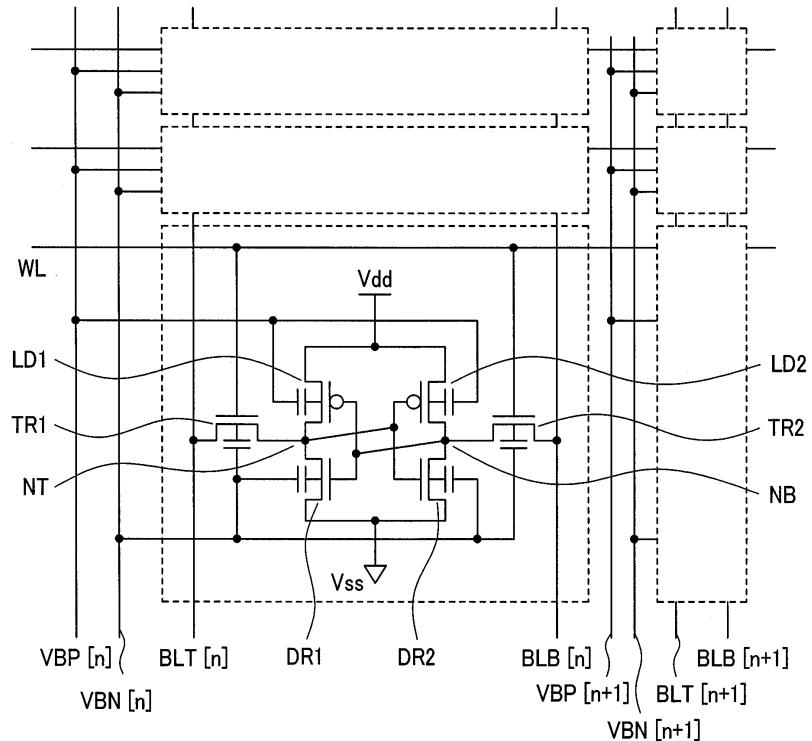

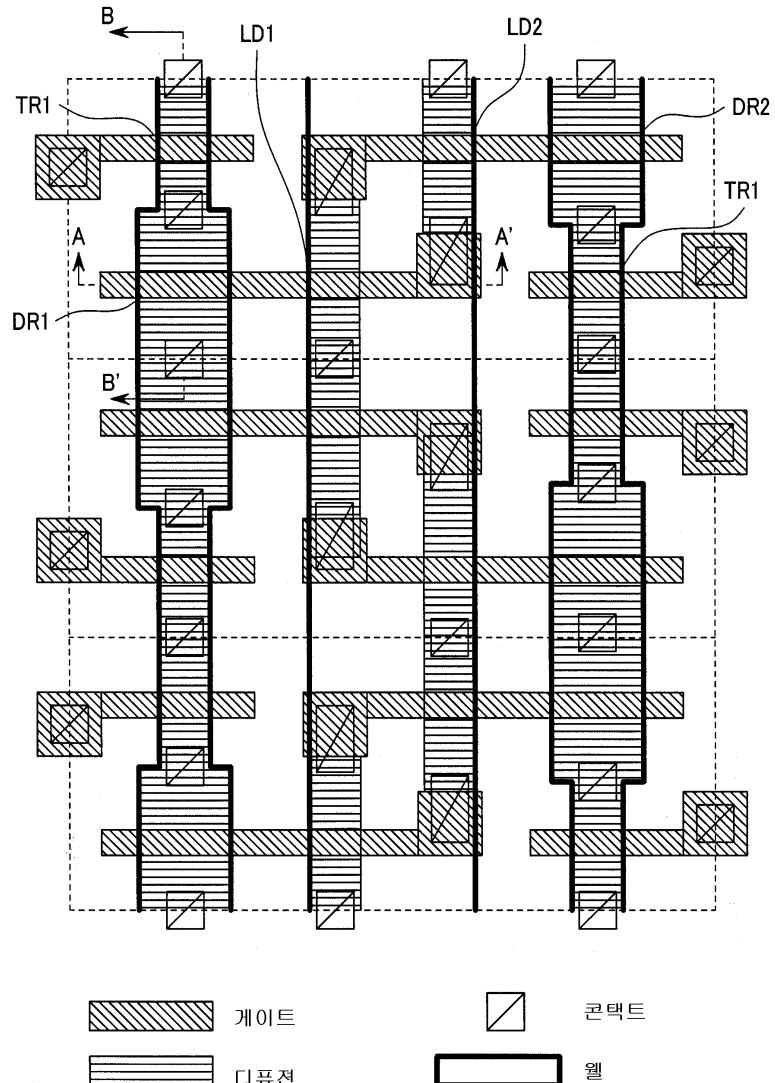

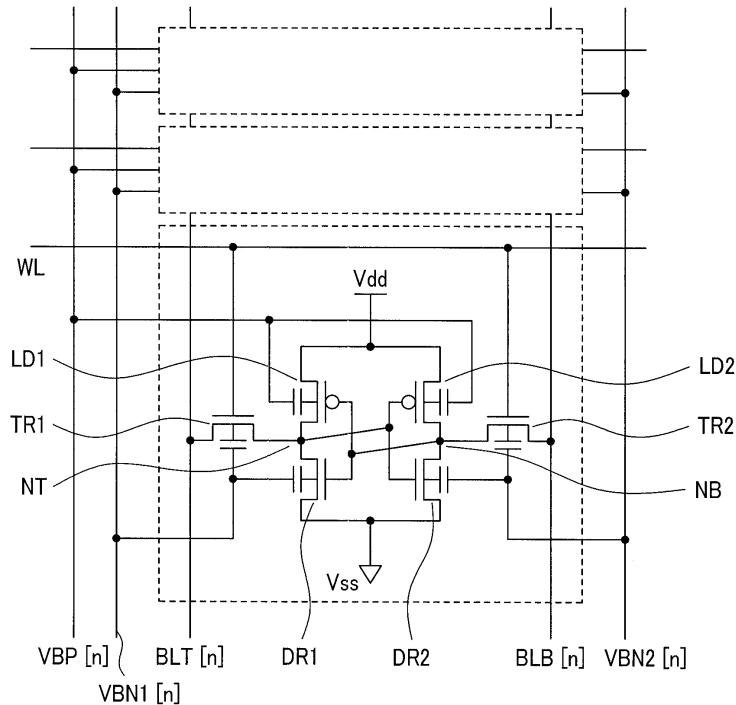

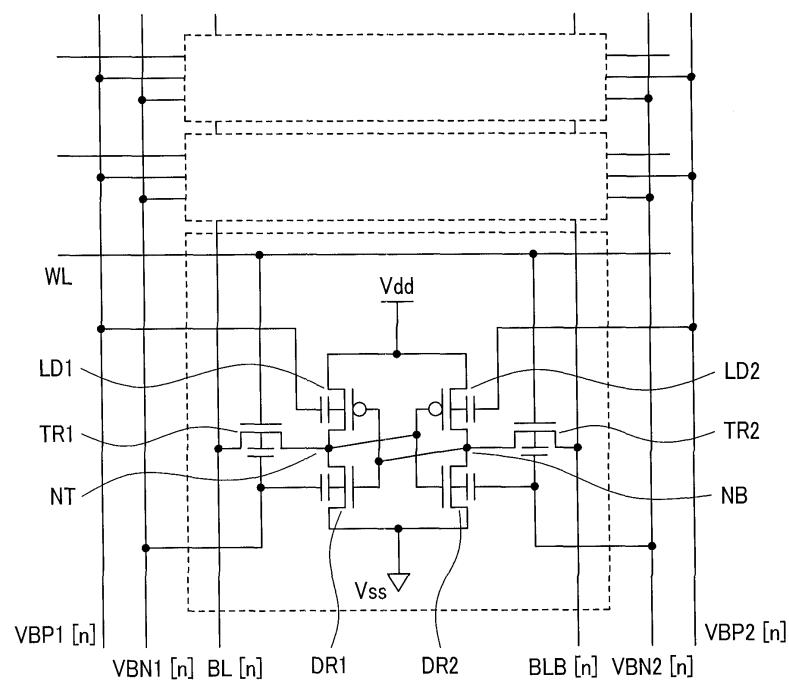

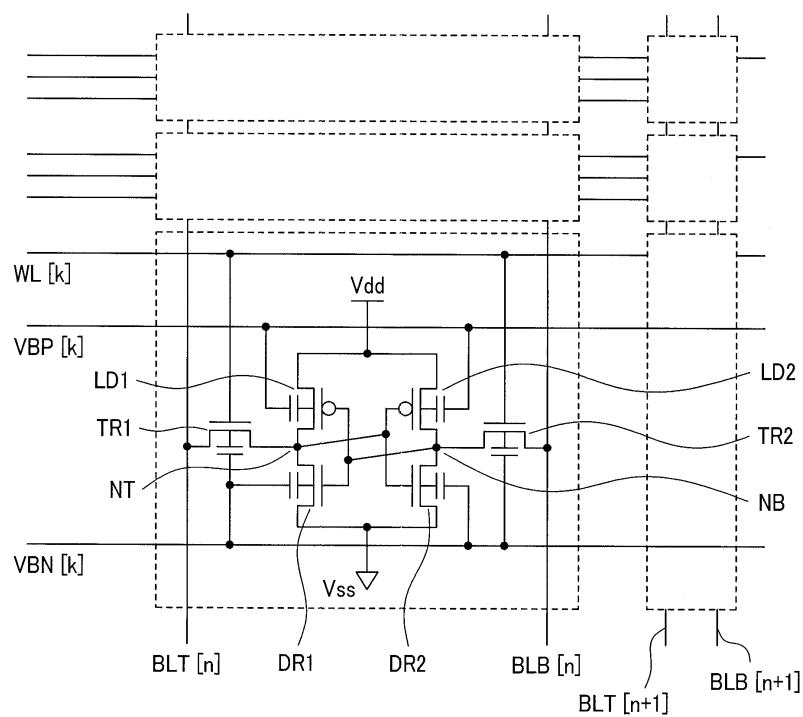

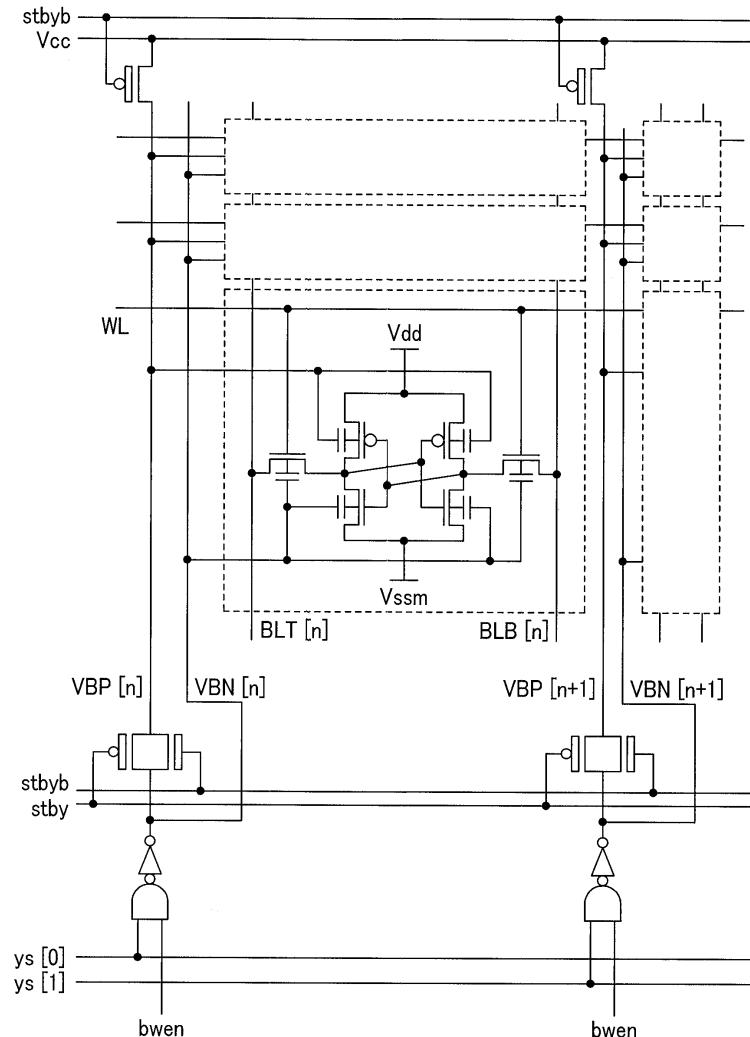

도 1에 본 발명을 사용한 SRAM 회로의 회로도를 나타낸다. 도 1에 있어서, [n]은 n열째로 공통된 것을 나타내고, 동일하게 [n+1]은 n+1열째로 공통된 것을 나타낸다. 이후로, 열(列)에 의해 특별히 구별할 필요가 없을 경우는 []을 빼고 나타내고, 열마다 특징이 있는 점에 관해서는 []을 붙여서 설명을 한다. 도 1에 있어서, BLT 및 BLB은 비트선, WL은 워드선, Vdd는 하이레벨의 전원선, Vss는 접지 전위선, NT 및 NB은 데이터를 기억하는 데이터 유지 노드, TR1 및 TR2은 비트선과 데이터 유지 노드를 접속하는 전송 트랜지스터, DR1 및 DR2은 데이터 유지 노드를 로우레벨로 구동하는 구동 트랜지스터, LD1 및 LD2은 데이터 유지 노드에 전하를 공급하는 부하 트랜지스터, VBN [n]은 n열째의 메모리 셀 내의 nMOS 트랜지스터의 웨爾 노드가 모두 접속된 노드, VBP[n]은 n열째의 메모리 셀 내의 pMOS 트랜지스터의 웨爾 노드가 모두 접속된 노드이다. 예를 들면, Vdd는 1.2V, Vss는 0V의 전위가 된다. 본 실시예는, 일반적으로 횡장(橫長) 셀로 불리는 워드선 방향으로 긴 직사각형의 메모리 셀을 사용한 SRAM 회로에 알맞은 회로구성의 예이다. 횡장 셀은, 워드선과 수직방향으로 긴 n웨爾과 p웨爾이 교대로 워드선 방향으로 반복해서 나란한 것에 의해 메모리 셀의 형상이 워드선 방향으로 긴 직사각형이 되는 것이다. 그 셀 형상에 기인하여, VBN[k] 및 VBP[k]은, WL에 수직, 즉 비트선에 평행하게 연신하도록 배치된다.

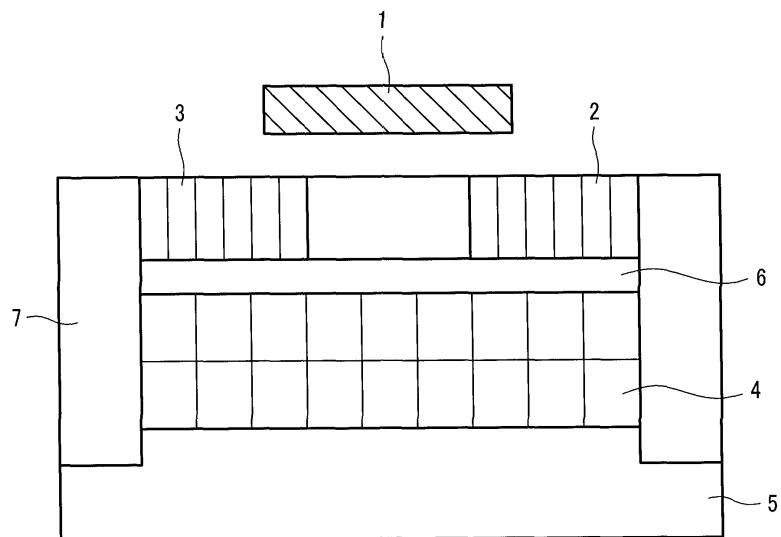

도 1의 회로중에서 사용된 트랜지스터의 단면의 개략도를 도 3에 나타낸다. 여기에서 사용되는 트랜지스터는, 채널 부분이 박스층에 의해 기판부분과 절연되는 SOI 트랜지스터이다. 도 3 중에서, 1은 게이트, 2은 드레인, 3은 소스, 4은 박스층 하의 웨爾층, 5은 지지기판, 6은 매립 산화막(박스)층, 7은 소자분리 영역이다. 본 트랜지스터는 완전공핍형SOI (FD-SOI:Fully Depleted SOI) 트랜지스터 구조가 되어, 웨爾층의 전위를 제어함으로써, 벌크 CMOS 트랜지스터의 백 게이트 전위를 제어했을 때와 같이 트랜지스터의 Vth를 제어하는 것이 가능하다. 특히 박스층의 두께가 얕으면 얕을수록, 웨爾층의 전위를 바꾸었을 때의 Vth의 변화도 커진다. 본 발명에서는, 특히 매립 산화막의 막두께가 20nm 이하인 10nm 정도를 상정하고 있다. 그러나, 매립 산화막의 막두께가 20nm 이상인 SOI 트랜지스터에서도, 웨爾층의 전위를 바꾸었을 때의 Vth의 변화의 정도는 작아지는 것이며, 같은 Vth 제어의 효과를 얻을 수 있다. 또 웨爾층은, 트랜지스터의 소스 및 드레인등의 확산층과는 절연막인 박스층에 의해 분리되기 때문에, 웨爾의 전위를 변화시켜도 웨爾과 확산층간에 전류는 흐르지 않는다.

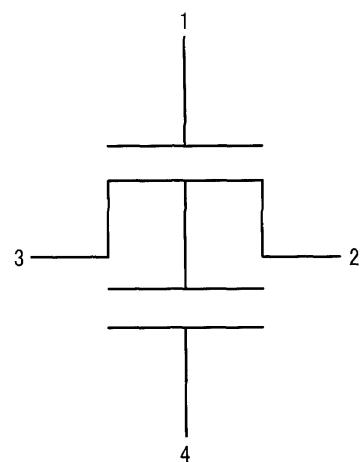

도 4에서, 도 3의 트랜지스터 구조의 등가 회로를 나타낸다. 1은 게이트, 2은 드레인, 3은 소스, 4은 웨爾을 나타내고 있으며, 웨爾과 트랜지스터의 백 게이트는 박스층에 의한 용량에 의해 분리된다. 도 1에서는 이 구조의 트랜지스터가 사용되고 있다.

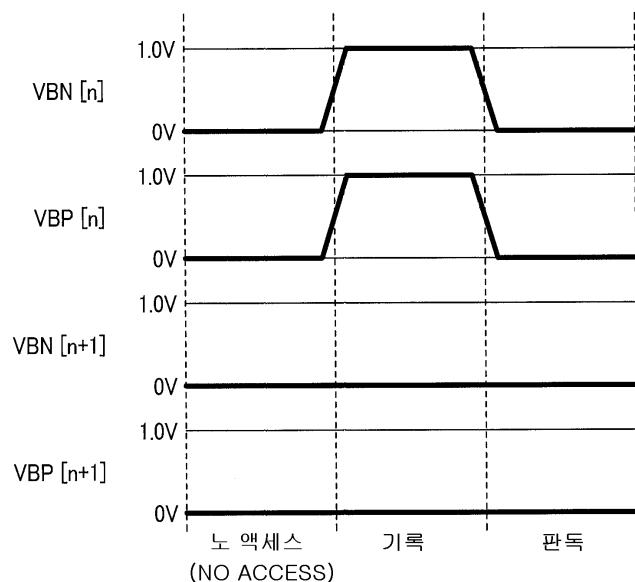

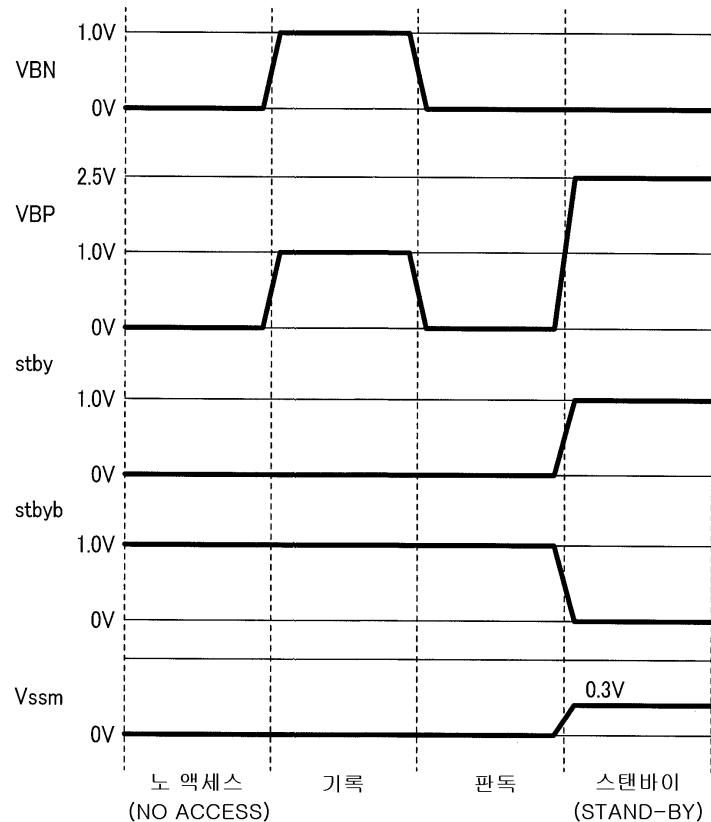

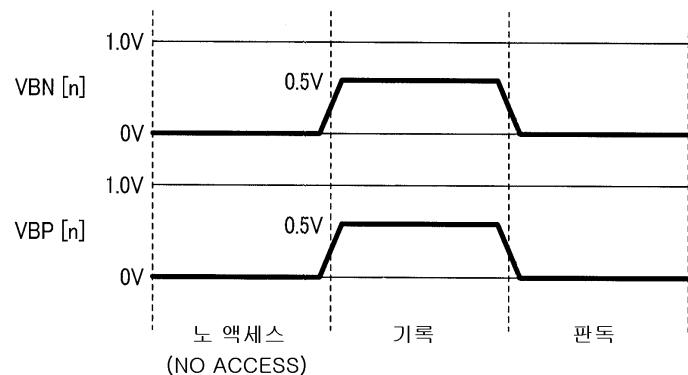

도 2에서, 각각의 열의 웨爾 전위의 변화를 나타낸다. VBN [n] 및 VBP[n]은 액세스되는 열의 웨爾 노드의 전위를 나타내고, VBN [n+1] 및 VBP[n+1]은 액세스되지 않고 있는 열의 웨爾 노드의 전위를 나타내고 있다. SRAM에서는 열(列)선택 액세스가 행하여지는 것이 일반적이기 때문에, 여기에서는 액세스되는 열과 액세스되지 않는 열의 전위를 나타내고 있다. 열선택 액세스가 행하여지지 않고, 모든 열이 액세스될 경우는, 모든 열의 웨爾 노드의 전위가 VBN [n] 및 VBP[n]에서 나타나 있는 전위와 동일해진다. 판독이 행하여질 경우 및 액세스되지 않고 있을 경우에는 nMOS의 웨爾 노드 및 pMOS의 웨爾 노드전위 모두 로우레벨로 제어된다. 또한, 기록이 행하여질 경우에는, nMOS 및 pMOS의 웨爾 노드의 전위가 하이레벨로 제어된다.

도 32의 메모리 셀에 있어서, 기억 노드(207)에 로우의 데이터가, 기억 노드(208)에 하이의 데이터가 기억되어 있을 경우의 판독 동작에 대해서 설명한다. 판독을 할 경우에는, 비트선(BLT 및 BLB)이 하이 전위로 프리챠지된다. 프리챠지 완료 후에 워드선(WL)이 하이 전위가 되는 것으로 전송 트랜지스터(201 및 202)이 on이 되고, 하이로 되는 비트선(BLT)의 전하가 전송 트랜지스터(201)로부터 기억 노드(207), 구동 트랜지스터(203)를 통과시켜서 디스챠지되어, (BLT)의 전위가 감지 증폭기에 의해 증폭할 수 있는 레벨이 된 시점에서, 도면에는 나타나지 않고 있지만 비트선에 접속되는 감지 증폭기를 기동하는 것으로써 메모리 셀의 데이터가 증폭되어 출력된다. 여기서 비트선의 전하가 디스챠지되는 경로에 차단하면, 기억 노드(207)는 판독 동작 시작 직전까지는 로우레벨인 0V이지만, 판독 동작이 시작되면 기억 노드(207)는 비트선(BLT)과 (Vss)사이를 전송 트랜지스터(201)와 구동 트랜지스터(203)에 의해 저항 분할한 상태가 되기 때문에, 기억 노드(207)의 전위는 0.3V등 정(正)의 전위가 된다. 여기에서 이 전위가 높아지면, 기억 노드(207)가 게이트에 접속되는 nMOS 트랜지스터의 컨덕턴스가 높아짐과 동시에, 기억 노드(207)가 게이트에 접속되는 pMOS 트랜지스터의 컨덕턴스가 저하하기 때문에 하이레벨이던 기억 노드(208)의 전위가 저하한다. 더욱이 이 기억 노드(208)의 전위상승은 기억 노드(207)에 피드백되어 이 반복에 의해 메모리 셀에 기억되는 데이터가 파괴된다. 보통 메모리 셀에서는 구동 트랜지스터의 컨덕턴스와 전송 트랜지스터의 컨덕턴스의 비가 1. 5등의 큰 값을 가지도록 설계되어, 메모리 셀에 기억되는 데이터가 파괴될 때까지 기억 노드(207)의 전위가 상승하는 경우는 없다.

그러나, 최근의 트랜지스터 제조 프로세스의 미세화에 의해 트랜지스터 성능의 불균일이 커지는 경향에 있고, 설계시의 컨덕턴스 비(比)를 하회하는 메모리 셀이 제조되어서, 판독시의 동작 안정성이 저하하는 경향이 있다. 또한, 저소비 전력화 때문에 전원전압을 내리면 기억 노드(207)가 게이트에 접속되는 nMOS 트랜지스터 및 pMOS 트랜지스터로 구성되는 인버터의 논리 문턱치전압이 저하하고, 데이터를 파괴하는 피드백이 일어나 쉬워져서, 이것에 의해도 판독시의 동작 안정성이 저하한다.

도 1의 본 발명의 회로에 있어서 같이 기억 노드(NT)에 로우의 데이터, 기억 노드(NB)에 하이의 데이터가 기억되어 있을 경우의 판독 동작을 생각하면, 도 32와 거의 같은 동작을 한다. 이 안에서, 부하 트랜지스터((LD1) 및 (LD2))의 웨爾 전위는 로우전위가 되기 때문에, 종래의 트랜지스터의 상태와 비교하면 (LD1) 및 (LD2)의  $V_{th}$ 가 낮은 상태가 되어, 부하 트랜지스터의 구동력 즉 컨덕턴스는 커지고 있다. 구동 트랜지스터(DR2)의 웨爾 전위는 소스 전위와 동등하기 때문에, 부하 트랜지스터(LD2)와 구동 트랜지스터(DR2)로 구성되는 인버터의 논리 문턱치전압은, 부하 트랜지스터(LD2)의 웨爾 전위가 하이인 상태와 비교하면 높은 상태가 된다. 따라서, 기억 노드(NT)의 전위가 상승했을 경우에도 데이터를 파괴하는 피드백이 일어나기 어려운 상태가 된다.

이렇게, 부하 트랜지스터의 웨爾 전위가 로우가 되는 상태는 판독시의 동작 안정성이 높다, 즉 판독 동작의 마진이 높은 상태가 되며, 불균일이 적으면서 저전압에서의 동작에 적합하다. 더욱이 본 발명에서는, pMOS 트랜지스터의 웨爾 전위에 로우의 전위를 인가했을 경우에도 절연막에 의해 웨爾로부터 확산층에 전류가 흐르지 않기 때문에, 0.5V 이상의 PN 접합을 on 시키는 것 같은 높은 전압에서도 소비 전력의 증가 없이 적용하는 것이 가능해진다.

도 32의 메모리 셀에 있어서, 기억 노드(207)에 하이의 데이터가, 기억 노드(208)에 로우의 데이터가 기억되어 있을 경우에 반대의 데이터를 기록할 경우의 동작에 대해서 설명한다. 비트선(BLT)를 로우레벨로, 비트선((BLB))을 하이레벨로 하는 동시에 위드선 전위를 "H" 레벨로 하고, 전송 트랜지스터를 on 시킨다. 기억 노드(207)의 전하는 전송 트랜지스터(201)를 통과시켜서 디스챠지되어, 기억 노드(207)의 전위는 하이레벨로부터 저하한다. 207의 전위가 부하 트랜지스터(206)와 구동 트랜지스터(204)로 구성되는 인버터의 논리 문턱치보다도 낮아지면, 로우레벨이었던 기억 노드(208)의 전위가 상승하고, 기억 노드간의 피드백도 작용하고, 새로운 데이터가 메모리 셀에 기록된다.

이렇게 SRAM 메모리 셀에서는 하이레벨의 기억 노드의 전하를 전송 트랜지스터에 의해 디스챠지함으로써 기록이 행하여지지만, 전송 트랜지스터에 의해 전하가 디스챠지됨과 동시에 부하 트랜지스터로부터 전하가 공급되기 때문에, 기록 동작을 끝내기 위해서는, 전송 트랜지스터가 부하 트랜지스터가 공급하는 이상으로 전하를 인출할 필요가 있다. 따라서, 부하 트랜지스터의 컨덕턴스가 커지면 기록에 필요한 시간이 길어지고, 또 불균일 등의 원인에서 설계치를 넘어서 커질 것 같은 경우에는 기록을 할 수 없는 경우가 있다. 이것들을 보상하기 위해서는, 부하 트랜지스터의 컨덕턴스를 작게 하거나, 전송 트랜지스터의 컨덕턴스를 크게 해야 한다.

100321본 실시예에서는, 종래로 같은 동작에서 메모리 셀에 새로운 데이터의 기록이 행하여진다.

도 1의 회로에서 기록이 행하여지는 열에서는, 부하 트랜지스터((LD1) 및 (LD2))의 웨爾 전위가 하이로 제어되고, 액세스되지 않고 있을 경우 또는 판독이 행하여질 경우와 비교해서 부하 트랜지스터의  $V_{th}$ 은 상승하고, 구동력은 저하한다. 동시에 메모리 셀중의 nMOS 트랜지스터의 웨爾 전위가 하이로 제어되어 nMOS 트랜지스터의  $V_{th}$ 는 낮아져 구동력이 높아진다. 따라서, 기록전의 상태에서 하이의 레벨이었던 기억 유지 노드의 전위를 저하시키는 전류를 전송 트랜지스터의 구동력이 높아지는 동시에 하이레벨을 유지하려고 하는 부하 트랜지스터의 구동력이 낮아져, 이에 따라 기록 동작이 행해지기 쉬워진다. 즉 기록시의 동작 마진이 증가하고, 불균일이 적으면서 저전압에서의 동작에 적합하다. 더욱이 본 발명에서는, nMOS 트랜지스터의 웨爾 전위에 하이의 전위를 인가했을 경우에도 절연막에 의해 웨爾로부터 확산층으로 전류가 흐르지 않기 때문에, 0.5V 이상의 PN 접합을 on 시키는 것 같은 높은 전압에서도 소비 전력의 증가 없이 적용하는 것이 가능해진다.

이상과 같이, 기록 및 판독의 각각의 동작에서 메모리 셀을 구성하는 트랜지스터의 웨爾 전위를 적절하게 변화시키는 것으로써 기록 및 판독의 각각의 동작의 동작 마진을 증가시킬 수 있고, 불균일이 적고 저전압에서의 동작에 알맞은 메모리 셀 동작을 할 수 있다.

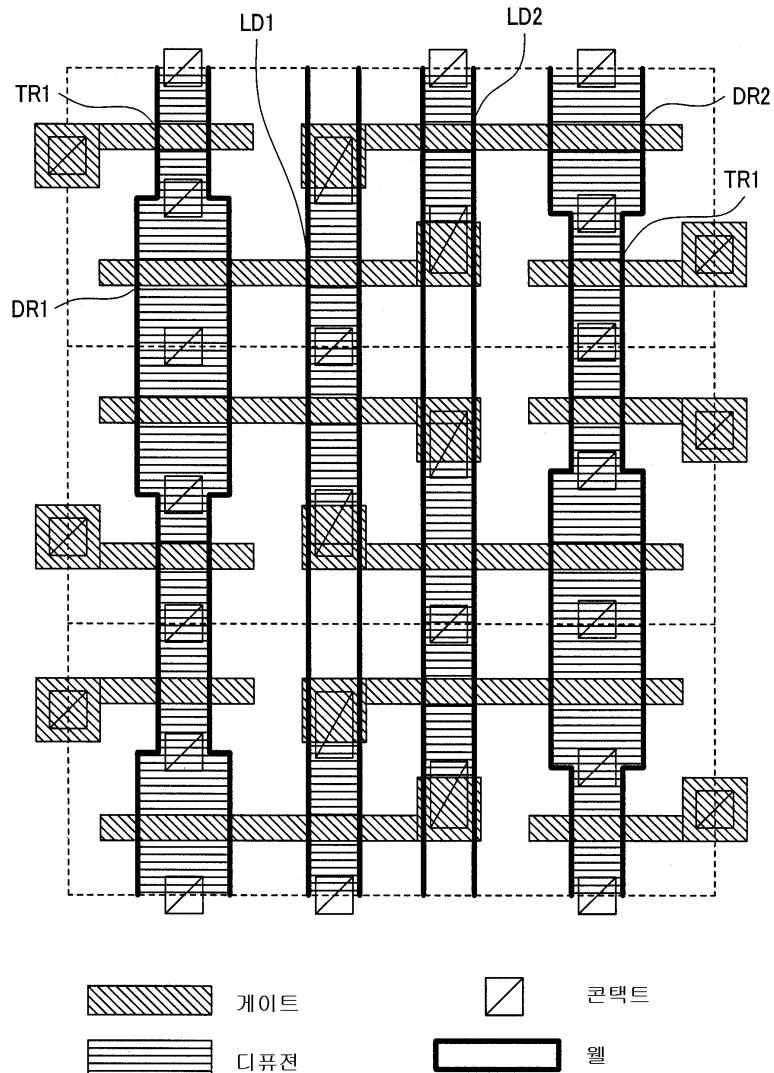

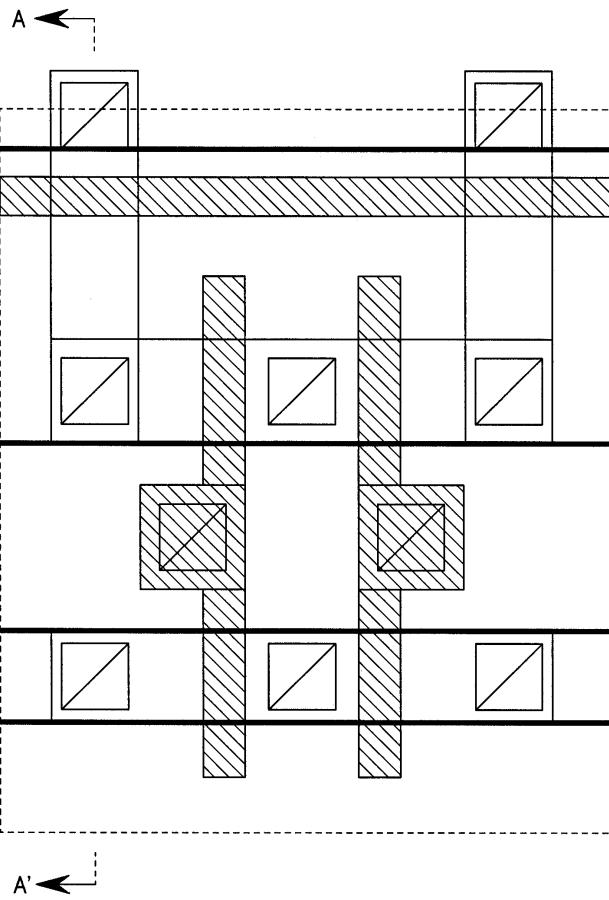

도 5에 본 메모리 셀의 레이아웃도를 나타낸다. 도 5에 있어서, TR1 및 TR2은 전송 트랜지스터, DR1 및 DR2은 구동 트랜지스터, LD1 및 LD2은 부하 트랜지스터, 게이트(Gate)는 트랜지스터의 게이트 전극을 구성하는 폴리 실리콘층, 디퓨전(Diffusion)은 확산층, 콘택트(Contact)은 확산층 및 폴리 실리콘층과 메탈 배선을 접속하기 위한 콘택트, 웨爾(Well)이 트랜지스터의 웨爾층이며, 점선에서 둘러싸여진 범위가 1개의 메모리 셀이다. 도 5 중에는 동일한 열(列)인 3개의 메모리 셀이 그려져 있다. 동일한 열로 나란히 서는 메모리 셀의 nMOS 및 pMOS 트랜지스터의 웨爾층이 접속되어, 동일한 전위로 제어

되는 것을 알 수 있다. 또한 더욱이 이웃한 열의 트랜지스터와는 웨이터가 분리되어 별개의 전위로 제어되는 것을 알 수 있다. 이 메모리 셀은, 일반적으로 횡장 셀로 불리는 워드선 방향으로 긴 직사각형의 형상을 가진 메모리 셀이다. 횡장 셀은, 워드선과 수직방향으로 긴 n웨이와 p웨이 교대로 워드선 방향으로 반복해서 나란한 것에 의해 메모리 셀의 형상이 워드선 방향으로 긴 직사각형이 되는 것이다. 이 셀 형상에 기인하고, 횡장 셀의 SRAM 회로도는 도 1에 도시한 바와 같이 VBN[k] 및 VBP[k]이 워드선(WL)에 수직, 즉 비트선에 평행하게 연신하는 구성이 된다.

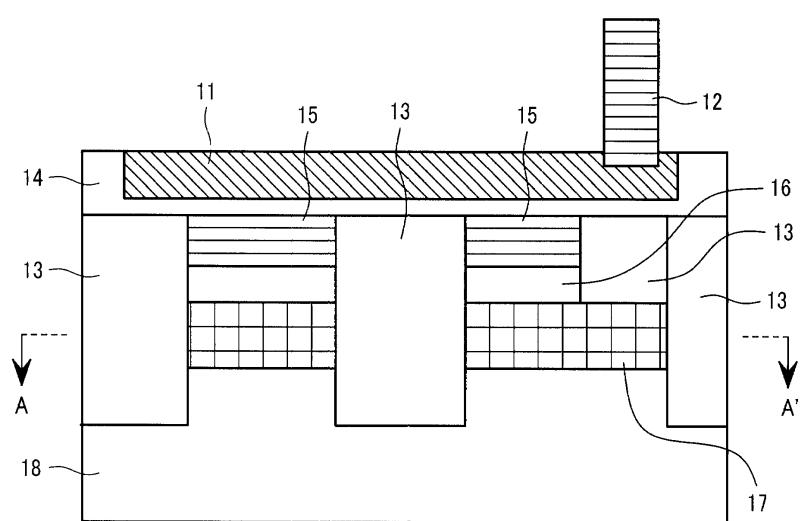

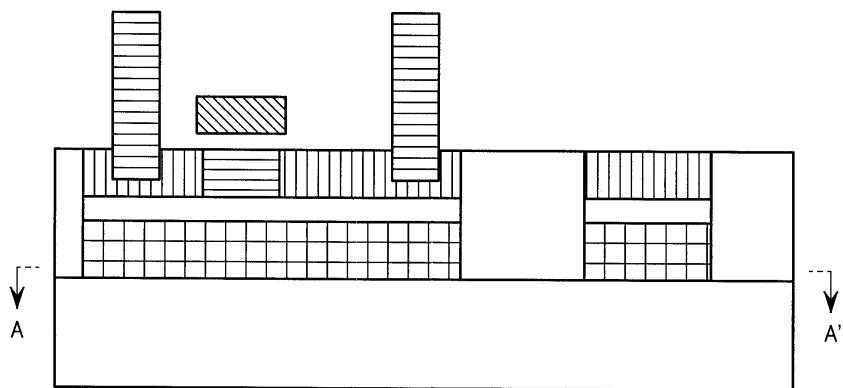

도 6에 도 5중의 A-A'로 절단했을 경우의 단면의 개략을 나타낸다. 도 6에 있어서, 11은 게이트 전극, 12은 콘택트, 13은 소자분리층, 14은 게이트 절연막층, 15은 SOI층, 16은 박스막, 17은 웨이터, 18은 지지기판이다. 채널이 형성되는 SOI층은 매립 산화막에 의해 웨이터으로부터 절연된다. 이것에 의해, 웨이터에 벌크 CMOS 트랜지스터에서의 순방향 바이어스가 인가되어도 웨이터로부터 소스 전류가 흐르는 경우는 없다. 또한, 소자분리층에 의해, SOI층 및 웨이터는 이웃의 트랜지스터와는 분리된다.

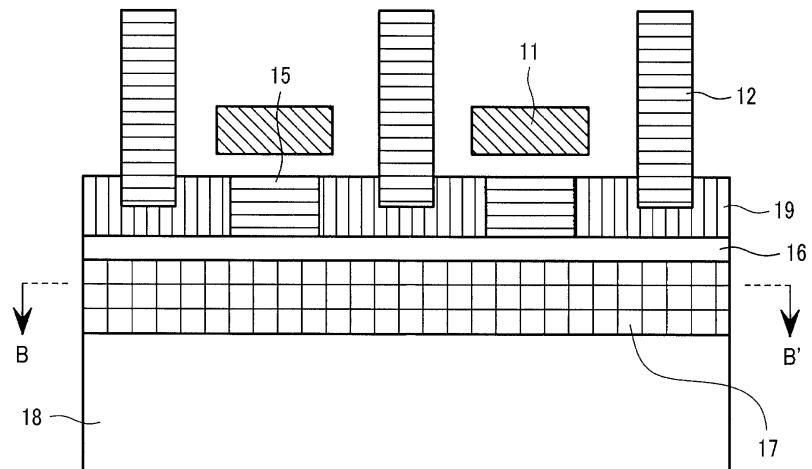

도 7에 도 5중의 B-B'로 절단했을 경우의 단면의 개략을 나타낸다. 도 7에 있어서, 11은 게이트 전극, 12은 콘택트, 13은 소자분리층, 15은 SOI층, 16은 박스막, 17은 웨이터, 18은 지지기판, 19는 확산층이다. 동일한 열 상에 나란히 서는 트랜지스터의 웨이터가 접속되어서 동 전위로 제어되는 구조가 되는 것을 알 수 있다.

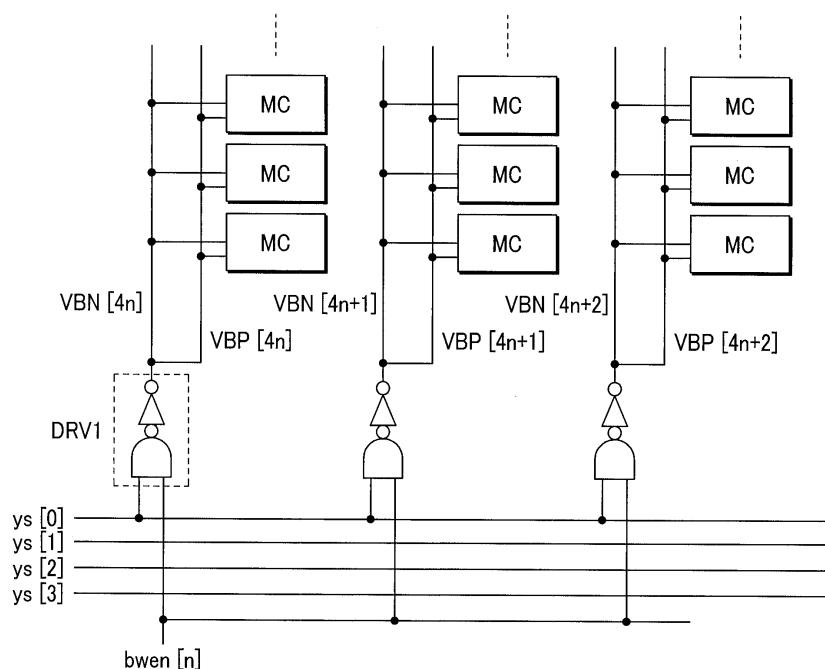

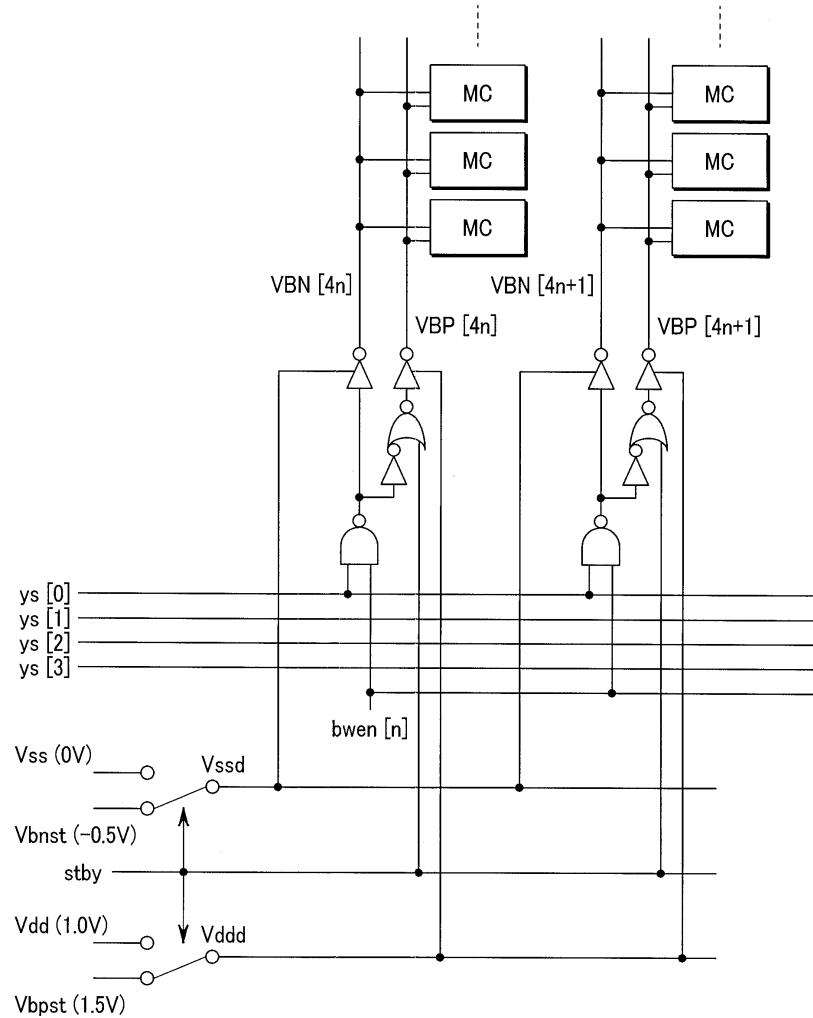

도 8에 도 2에 기재한 웨이터 전위의 제어를 하기 위한 회로를 나타낸다. 도 8에 있어서, VBN[4n]로부터 VBN[4n+2]은 각각의 열의 nMOS 트랜지스터의 웨이터 전극, VBP[4n]로부터 VBP[4n+2]은 각각의 열의 pMOS 트랜지스터의 웨이터 전극, DRV1은 웨이터 전위를 구동하는 구동 회로, ys[0]로부터 ys[3]은 열을 선택하기 위한 열선택 신호, bwen[n]은 그 컬럼에 기록이 행하여지는 것을 나타내는 기록 신호이다. 열선택 신호 및 기록 신호에 의해 선택된 열에 기록이 행하여지고, 도 8의 회로에서는 각각의 신호의 논리곱이 웨이터 노드에 입력되어, 기록이 행하여질 경우에는 nMOS 및 pMOS의 웨이터 전위가 하이에, 기록이 행하여지지 않을 경우에는 nMOS 및 pMOS의 웨이터 전위가 로우로 제어되어, 도 2에 기재한 전위제어가 가능해진다.

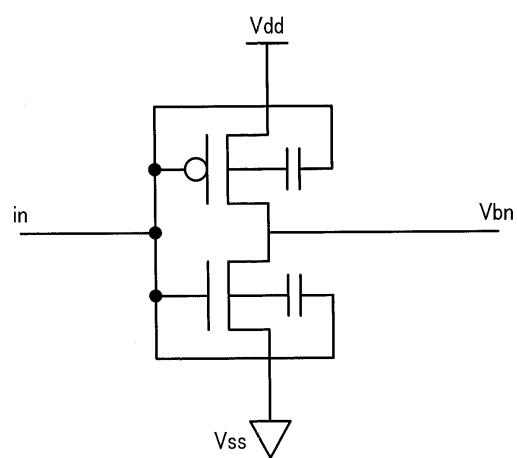

도 9에 웨이터 노드를 구동하는 회로(DRV1)의 최종단의 인버터 회로의 하나의 예를 나타낸다. 도 9에 있어서, Vdd 및 Vss는 전원 노드, (in)은 입력 신호, Vbn은 본인버터 회로의 출력을 나타내고 있다. 본 실시예에 있어서 해당하는 열이 선택되지 않고 있을 경우에는, (in)에 하이의 전위가 인가되어 있고, 해당하는 열에 기록이 행하여질 경우에 (in)의 전위가 로우가 된다. 이것에 의해, 출력(Vbn)은 하이가 되고, 기록 특성을 향상시킨다. 도 9의 회로중의 pMOS 트랜지스터의 웨이터 노드는 게이트와 접속되어, (in)의 전위가 하이로부터 로우로 변화되면 pMOS 트랜지스터의 웨이터 노드전위가 로우가 되어서 Vth가 저하해서 구동력이 향상하고, 구동하는 메모리 셀 열의 웨이터 노드의 전위를 민첩하게 하이로 변화시키는 것이 가능해진다.

또한, nMOS트랜지스터의 웨이터 노드도 게이트 전극과 접속되고 있으며, 해당 메모리 셀 열의 웨이터 전위를 민첩하게 로우전위로 변화시키는 것이 가능해진다. 동작속도가 중요하지 않을 경우에는, 각각의 웨이터 전위를 소스 전위에 접속하는 것도 가능하다. 또한, 서브 스레숄드 리크전류가 문제가 안될 경우에는, nMOS 트랜지스터의 웨이터를 Vdd에, pMOS 트랜지스터의 웨이터를 Vss에 접속해서 항상 각각의 트랜지스터의 Vth를 낮은 상태로서 두어 동작속도를 향상시킬 수도 있다. 또한, 출력 즉 메모리 셀 내의 웨이터 노드를 하이로 하는 속도만이 중요해서, 로우로 하는 속도는 느려도 좋을 경우에는, pMOS의 웨이터 노드뿐 게이트 전극이나 Vss에 접속해서 고속화를 실현하는 것도 가능하다.

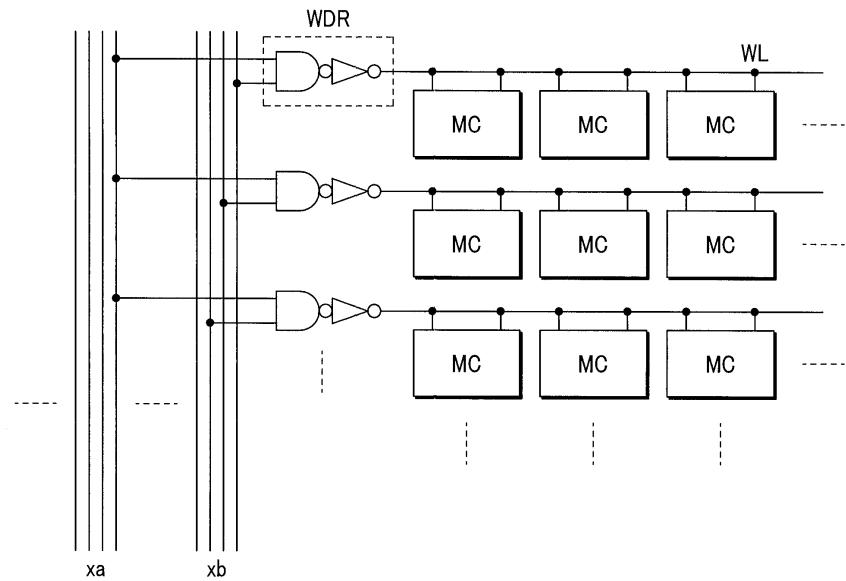

도 10에 본 SRAM 회로의 워드선을 제어하는 회로의 하나의 예를 나타낸다. 도 10에 있어서, MC은 메모리 셀, WL은 워드선, WDR는 워드선 드라이버, xa 및 xb은 어드레스를 디코드한 신호를 나타낸다. 본 회로구성에서는, xa 및 xb에서 선택된 1개의 워드선이 워드 드라이버 회로에 의해 하이가 되고, 메모리 셀에 액세스된다.

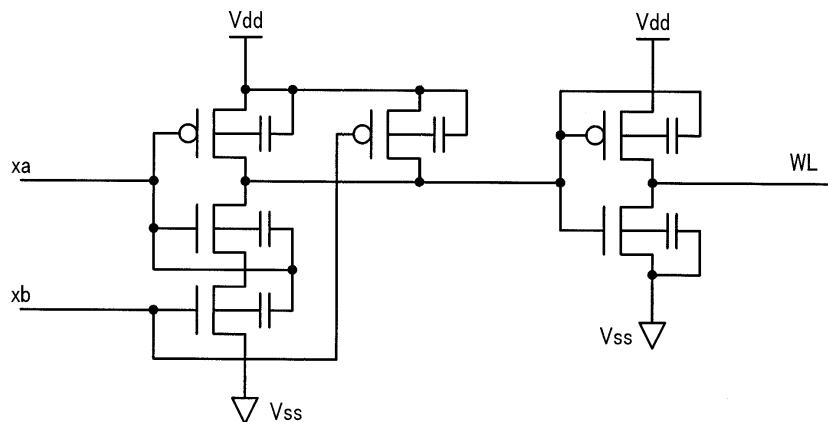

도 11에 도 10 중의 워드 드라이버 회로의 하나의 예를 나타낸다. 이 회로는 xa 및 xb이 입력되는 NAND회로와, 그 출력의 반전 신호를 워드선 전위로서 출력하는 인버터 회로로 구성되어, xa 및 xb의 쌍방이 하이가 되었을 경우에 워드선 전위를 하이로 한다. 보통, 메모리 셀의 동작속도는 워드선의 상승시간에 크게 영향을 받는다. 따라서, 워드선을 로우로부터 하이로 하는 경로를 빨리 하면 크게 메모리의 동작속도를 향상할 수 있다. 본 회로에서는, NAND회로중의 nMOS 트랜지스터와 인버터 회로중의 pMOS 트랜지스터의 웨이터 노드가 각각 게이트 전극에 접속된다. 따라서, 각각의 트랜지스터는 on이 될 때에 Vth가 저하하고, 구동력이 증가해 동작속도가 커진다. 워드선 전위가 로우로부터 하이가 될 경우에는, NAND회로 중의 nMOS 트랜지스터가 모두 on 하고, 더욱이 인버터 회로의 pMOS 트랜지스터가 on 할 경우이기 때문에, 이렇게 웨이터 노드와 게이트 노드를 접속하는 것으로써 워드선 전위를 변화시키는 속도가 향상하고, 메모리 전체의 고속화에 기여한다. 또한, 동작속도의 향상이 중요하지 않을 경우에는, 각각의 웨이터 전위를 소스 전위에 접속하는 것도 가능하다. 또한, 서브 스레숄드 리크전류가 문제가 안될 경우에는, nMOS 트랜지스터의 웨이터를 Vdd에, pMOS 트랜지스터의 웨이터를 Vss에 접속해서 항상 각각의 트랜지스터의 Vth를 낮은 상태로서 두어 동작속도를 향상시킬 수도 있다.

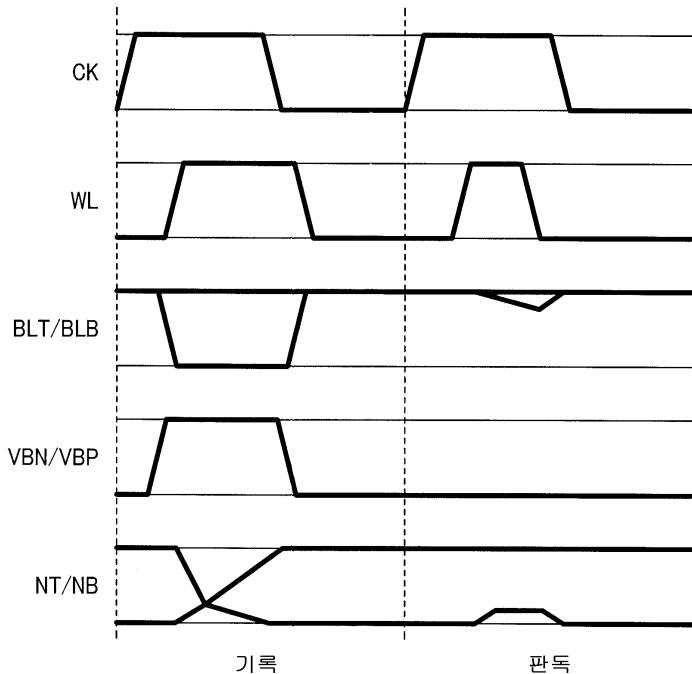

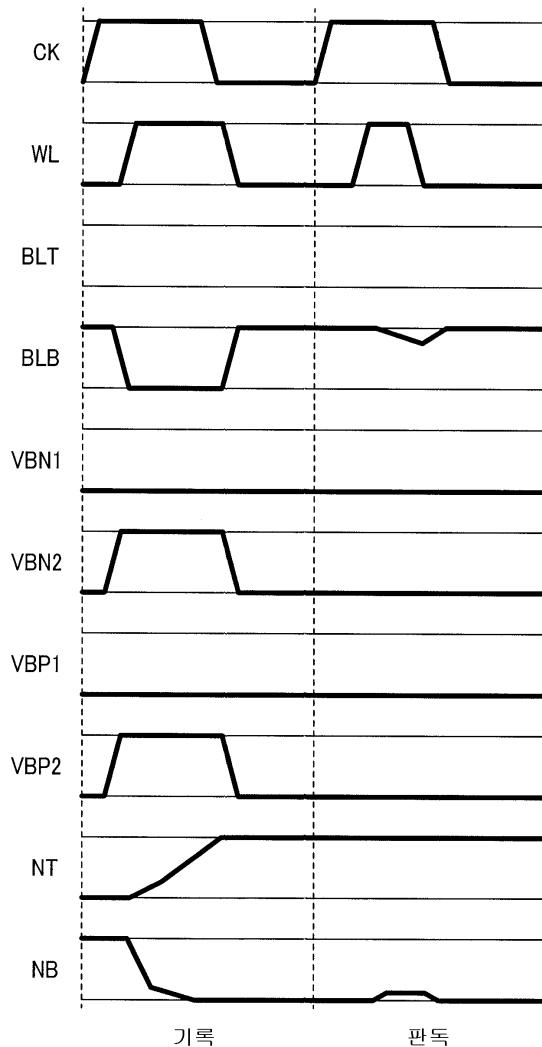

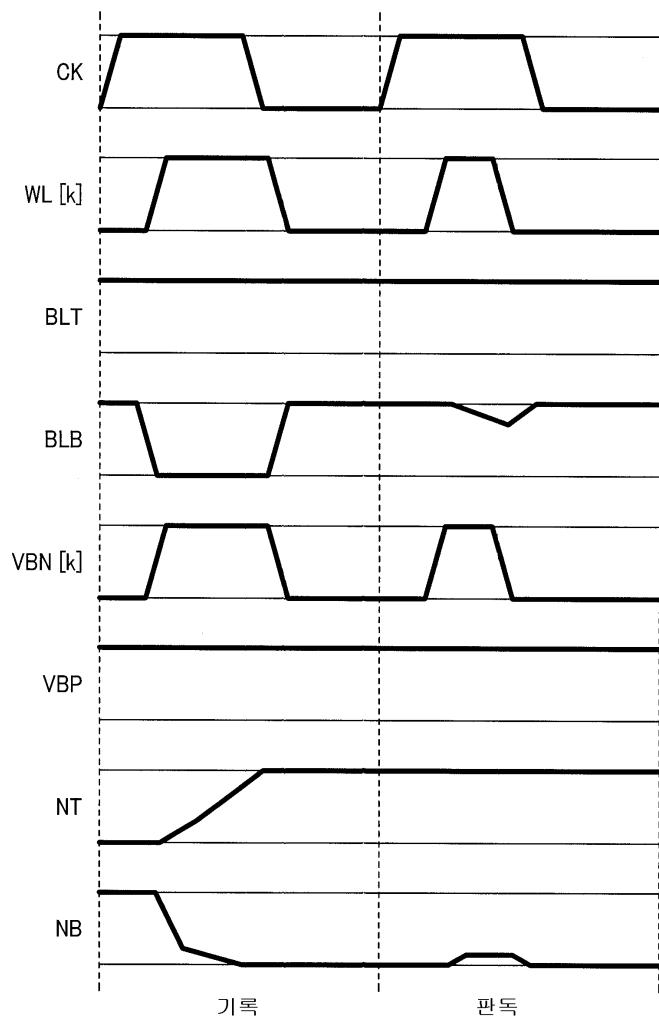

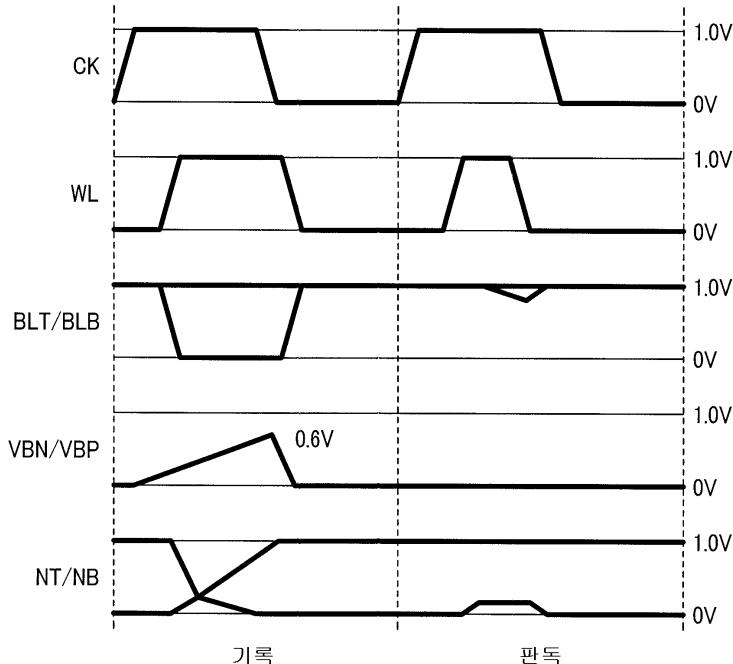

도 12에 본 실시예의 회로를 사용했을 경우의 회로 각 부분의 동작 전압의 변화를 나타낸다. 도 12 중에서, CK은 클록 신호, WL은 워드선, BLT 및 BLB은 비트선, VBN 및 VBP은 액세스되는 메모리 셀 내의 트랜지스터의 웰 노드, NT 및 NB은 액세스되는 메모리 셀 내의 기억 유지 노드이며, 기록(Write) 및 판독(Read)가 기록 및 판독 동작을 나타낸다. 기록시에는, 클록 신호의 상승과 함께 메모리 셀에 기록되는 데이터가 비트선 상에 입력된다. 또한, 거의 동시에 웰의 전위가 기록 동작에 알맞은 전위로 제어된다. 여기에서, 워드선 전위가 로우로부터 하이로 상승하고, 메모리 셀 내의 기억 노드 전위가 반전하고, 새로운 데이터가 메모리 셀에 기록된다. 판독시에는 클록 신호의 상승에 의해 워드선 전위가 하이가 된다. 이것에 의해 데이터 유지 노드의 데이터가 비트선에 출력되어서 판독이 행하여진다.

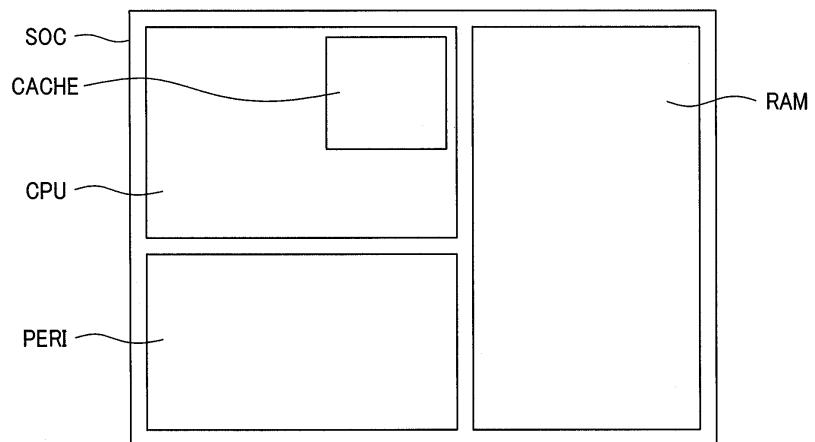

도 33에, 본 발명의 SRAM 메모리를 사용한 SoC(System-on-a Chip)의 예를 나타낸다. SoC은, CPU 코어인 CPU와 그 밖의 특정한 기능을 가진 회로를 블록(PERI), 및 여러가지의 회로로부터 액세스되는 비교적 대용량의 메모리RAM으로 구성된다. 또 CPU 코어의 중에는, 캐시 메모리(CACHE)가 탑재된다. 본 발명의 SRAM 메모리는, SoC중의 대용량 메모리 및 캐시 메모리로서 사용하는 것이 가능하다.

#### <실시예2>

도 13에 본 발명을 사용한 SRAM 메모리셀 웰전위의 제어 방법의 하나의 예를 나타낸다. 또 이후의 실시예에 있어서, 제1의 실시예와 같은 것에 관해서는 동일한 기호를 사용하고, 다른 것에 관해서만 설명한다. 본 메모리 셀의 트랜지스터 레벨의 회로구성은 도 1과 동등한 회로가 된다. 도 13 중에서, 도 2의 웰 상태와 다른 것은, 메모리에 액세스의 없는 노 액세스(NO access)의 상태에서, pMOS의 웰 전위가 하이레벨이 되는 것이다. 액세스되지 않고 있는 상태, 특히 스템바이 상태라고 하는 메모리 셀이 데이터는 유지하고 있지만 액세스는 되지 않는 상태에서는, 메모리 셀의 리크 전류가 문제가 될 경우가 있다.

이 경우에, pMOS의 웰 전위가 로우가 되면 pMOS의 Vth가 내려 간 상태가 되고, 큰 리크 전류가 흐른다. 도 13의 상태에서는 pMOS의 웰 전위가 하이가 되고, pMOS의 Vth가 저하하지 않고 리크 전류를 낮게 억제할 수 있다.

#### <실시예3>

도 14에 본 발명을 사용한 SRAM 회로의 회로도를 나타낸다. 본 실시예에서는, 실시예1과 달리, 메모리 셀 내의 nMOS 트랜지스터의 웰 노드가, 메모리 셀 내의 좌측 즉 비트선(BLT)로부터 (VSS)까지 직렬로 접속되는 nMOS와, 메모리 셀 내의 오른쪽 즉 비트선((BLB))으로부터 (VSS)까지 직렬로 접속되는 nMOS로 별개의 노드((VBM)과 (VBN2))가 되는 것이다. 메모리 셀의 레이아웃은 도 5로 같지만 이미 좌우의 nMOS의 웰 노드는 별개로 접속되기 때문에 메모리 셀의 레이아웃을 변경할 필요는 없다.

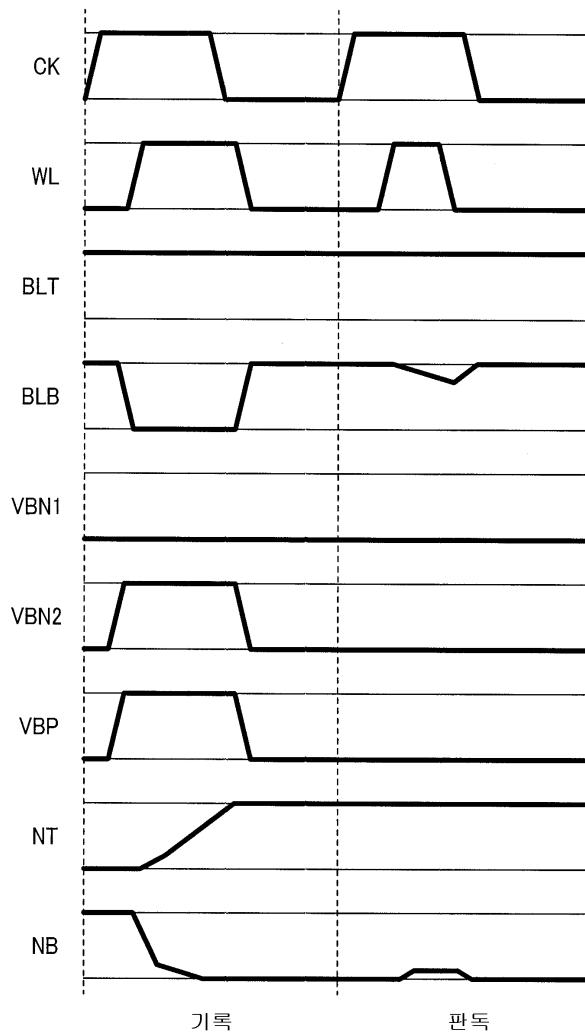

도 15에 본 실시예의 회로를 사용했을 경우의 회로 각부의 동작 과형을 나타낸다. 실시예1과 다른 것은, 기록시에 (VBN1)과 (VBN2)이 각각인 전위로 제어되는 것이다. 도 15 중에서, 기록시에 (VBN1)은 로우전위인 채이며, (VBN2)은 하이 전위로 제어된다. 이것은, 기록 데이터가 입력되는 비트선 전위와 관계가 있고, (BLT)에 하이의 데이터가, (BLB)에 로우의 데이터가 입력되어 있을 경우는, 도 15의 전위관계가 되어 (VBN1)은 로우전위로, (VBN2)은 하이 전위로 제어된다. 여기서 SRAM 메모리 셀에 데이터를 기록할 때의 동작을 생각한다. 실시예1의 설명에서 쓴 대로, SRAM에 데이터를 기록하는 동작은 하이의 데이터를 유지하고 있는 기억 유지 노드의 전위를, 전송 트랜지스터를 통과시켜서 전류를 흘려서 로우전위로 함으로써 실현된다. (BLB)에 로우의 데이터가 입력되었을 경우에는, 전송 트랜지스터(TR2)를 통과시켜서 큰 전류를 흘릴 수 있으면 기록 특성을 개선할 수 있다. 여기에서, TR2의 웰 노드는 (VBN2)이며, 따라서 (VBN2)의 전위를 하이로 제어하면, 전송 트랜지스터(TR2)의 구동력을 높여서 기록 특성이 개선한다. 여기에서는 도시하지 않고 있지만, (BLT)에 로우의 데이터가 입력되었을 경우에는 당연히 (VBN1)이 하이로 제어되어서 기록 특성이 개선된다.

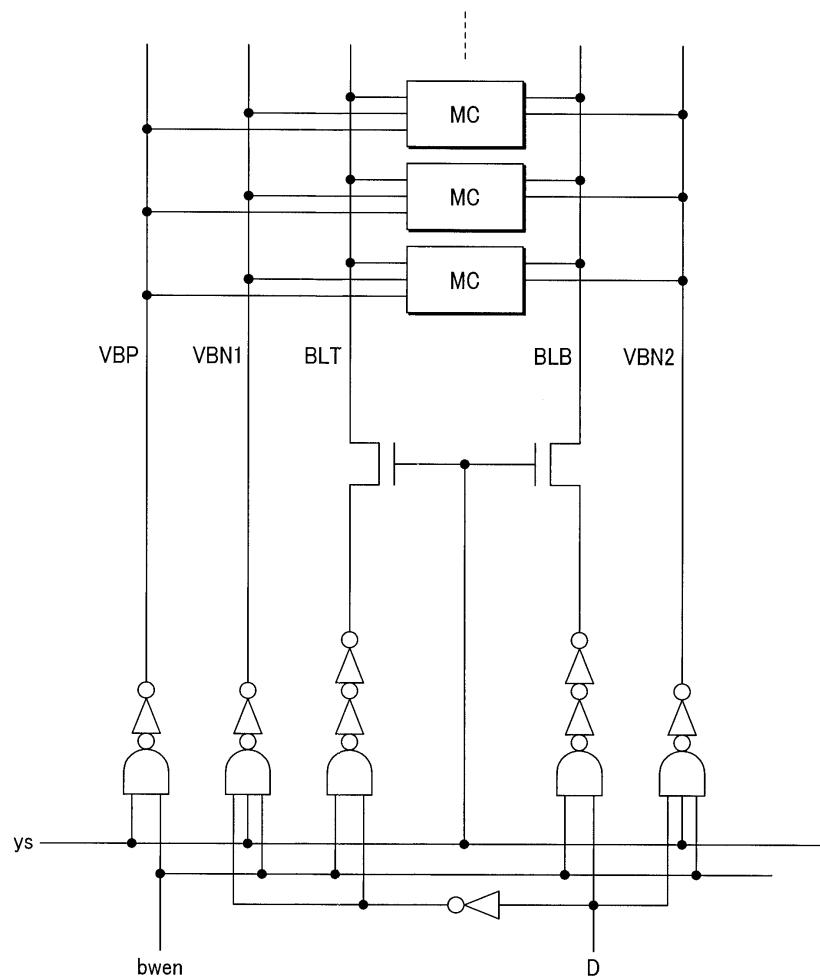

도 16에, 도 15의 과형을 실현하기 위한 제어 회로의 회로도를 나타낸다. D는 기록하기 위해서 입력된 데이터 신호이다. D의 값이 비트선(BLT 및 BLB)에 입력되는 동시에, 웰 전위(VBN1)과 (VBN2)이 각각인 전위로 제어할 수 있는 것을 알 수 있다. 이 구성을 취하면, 제어되는 웰이 감소하기 때문에 충방전되는 전하의 양이 감소하고, 기록시의 동작 특성을 동등 레벨로 유지한 채, 소비 전력을 저감하는 것이 가능해진다.

#### <실시예4>

도 17에 본 발명을 사용한 SRAM 회로의 회로도를 나타낸다. 본 실시예에서는, 실시예3로부터 더욱이 메모리 셀 내의 좌우의 pMOS의 웰 노드의 제어도 별개로 분할한 구성을이다.

도 18에 본 실시예의 회로를 사용했을 경우의 회로 각부의 동작 과형을 나타낸다. 실시예3과 달리, 기록시에 (VBM)과 (VBN2)에 더하여, (VBP1)과 (VBP2)이 각각인 전위로 제어된다. 도 18 중에서, 기록시에 (VBN1) 및 (VBP1)는 로우전위인 채이며, (VBN2) 및 (VBP2)은 하이 전위로 제어된다. 이것은, 기록 데이터가 입력되는 비트선 전위와 관계가 있고, (BLT)에 하이의 데이터가, (BLB)에 로우의 데이터가 입력되어 있을 경우는, 도 18의 전위관계가 되어 (VBN1) 및 (VBP1)은 로우전위에, (VBN2) 및 (VBP2)은 하이 전위로 제어된다.

여기에서, SRAM 메모리 셀에 데이터를 기록할 때의 동작을 생각한다. 실시예1의 설명에서 기록한 대로, SRAM에 데이터를 기록하는 동작은 하이의 데이터를 유지하고 있는 기억 유지 노드의 전위를, 전송 트랜지스터를 통과시켜서 전류를 흘려서 로우전위에 함으로써 실현된다.(BLB)에 로우의 데이터가 입력되었을 경우에는, 전송 트랜지스터(TR2)을 통과시켜서 큰 전류를 흘리는 동시에, 기억 유지 노드(NB)에 전하를 공급하고 있는 부하 트랜지스터(LD2)의 구동 능력을 저감하면, 기억 유지 노드(NB)의 전위가 하이로부터 로우로 변화되기 쉬워져, 기록 특성을 개선한다. 여기에서, (TR2)의 웰 노드는 (VBN2)이며, 따라서 (VBN2)의 전위를 하이로 제어하면, 전송 트랜지스터(TR2)의 구동력을 높여서 기록 특성이 개선된다. 또 (LD2)의 웰 노드는 (VBP2)이며, 따라서 (VBP2)의 전위를 하이로 제어하면, 부하 트랜지스터(LD2)의 구동력이 하강하여 기록 특성이 개선된다. 여기에서는 도시하지 않고 있지만, (BLT)에 로우의 데이터가 입력되었을 경우에는 당연 (VBM) 및 (VBP1)의 전위가 하이로 제어되는 것에 따라 기록 특성이 개선된다.

도 19에 본 실시예의 제어를 가능하게 하는 메모리 셀 레이아웃을 나타낸다. 실시예1에서 사용할 수 있는 메모리 셀 레이아웃을 나타내는 도 5와 다른 것은, 부하 트랜지스터의 웰 노드가 2개로 분할되어서 별개의 제어가 가능해지는 것이다.

이 구성은 취하면, 제어되는 웰이 감소하기 때문에 충방전되는 전하의 양이 감소하고, 기록시의 동작 특성을 동등 레벨로 유지한 채, 소비 전력을 저감하는 것이 가능해진다. 더욱이, 기록 동작은, 하이의 기억 노드 전위를 로우로 함으로써 실행되지만, 이 때 로우전위이었던 기억 유지 노드의 전위는 하이로 쳐지될 필요가 있다.

이 기억 유지 노드를 하이로 쳐지하는 것은 그 노드에 드레인 전극이 접속되는 부하 트랜지스터의 역할이다.

즉, 상기한 바와 같이 기억 유지 노드(NB)의 전위를 하이로부터 로우로 하는 기록을 할 경우에는, 기억 유지 노드(NT)의 전위를 로우로부터 하이로 쳐지해야 하고, 이것은 부하 트랜지스터(LD1)의 전류에 의해 실행된다. (LD1) 및 (LD2)의 웰 전위가 같은 전위로 제어되어 있을 경우에는 (LD1)의 구동력도 저하되기 때문에, 기억 유지 노드(NT)의 전위를 하이로 하기 위해서 시간이 걸리게 된다. 이것은, 기록 시간이 엄한 조건하에서는, 동작속도를 저하시키는 요인이 되는 가능성이 있다. 그러나, 도 17의 구성으로 하면, 부하 트랜지스터(LD1)의 Vth는 저하하고, 로우전위의 기억 유지 노드의 전위를 하이로 하기 위해서 필요한 시간이 단축되어, 동작속도를 향상시키는 것이 가능해진다.

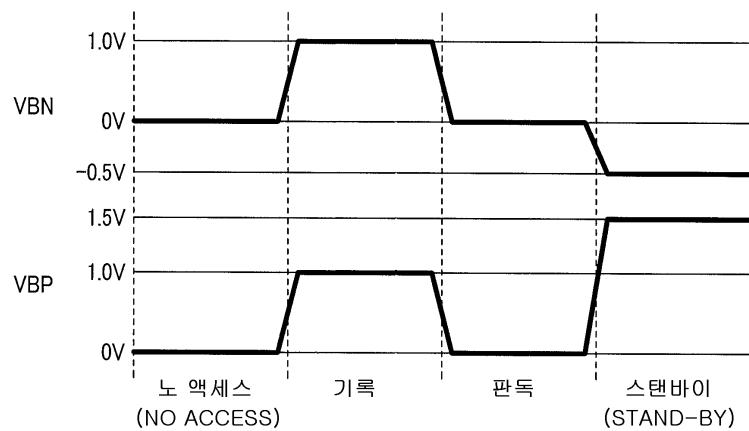

<실시예5>

도 20에 본 발명을 사용한 SRAM 메모리 셀 웰전위의 제어 방법의 하나의 예를 나타낸다. 도 20에서는 실시예1과 달리, 스텐바이(Stand -by)라 하는 스텐바이 모드의 상태가 추가된다. 이 상태에서는, 메모리 셀에서는 데이터를 유지해야 하지만 액세스되지 않는 상태이며, 트랜지스터의 리크 전류를 저감하는 것이 전체의 전력을 감하기 위해서 필요하다. 스텐바이 상태에서는, nMS의 웰 전위가 부(負)의 전위인  $-0.5V$ 로, pMOS의 웰 전위가 하이의 전원전압(Vdd)보다 높은  $1.5V$ 로 제어된다. 이 상태에서는, nMOS 및 pMOS의 Vth가, 각각의 웰 전위가 소스 전위로 동등한 전위로 제어될 경우보다도 높게 제어되어 서브 스레숄드 리크로 불리는 소스 드레인간에 흐르는 리크 전류가 크게 저감할 수 있다. 여기에서는, nMOS의 웰 전위로서  $-0.5V$ 을, pMOS의 웰 전위로서  $1.5V$ 의 예를 들고 있지만, 더욱이 Vth를 변동시키도록 nMOS의 웰 전위를  $-0.5V$ 보다 낮은 전위에, 또 pMOS의 웰 전위를  $1.5V$ 보다 높은 전위로 하는 것도 가능하다.

도 21에 도 20의 전위상태를 실현하기 위한 SRAM 회로구성의 회로도를 나타낸다. 도 21 중에서, Vssd는 메모리 셀 내의 트랜지스터의 웰 전위를 제어하는 구동 회로의 로우측의 전원선, Vddd은 메모리 셀 내의 트랜지스터의 웰 전위를 제어하는 구동 회로의 하이측의 전원선, Vbnst는 스텐바이시의 nMOS의 웰 전위이며 본 실시예에서는  $-0.5V$ , Vbpst는 스텐바이시의 pMOS의 웰 전위이며 본 실시예에서는  $1.5V$ , stby는 스텐바이시에 하이가 되는 스텐바이 신호이다. 스텐바이 상태가 아닌 경우에는, Vssd 및 Vddd에는 통상의 전원전위인  $0V$ 와  $1.0V$ 가 인가되어 있고, 실시예1로 동등한 동작을 한다. 스텐바이 신호(stby)가 하이가 되고, 스텐바이 상태가 되면 Vssd 및 Vddd에는, 각각  $-0.5V$ ,  $1.5V$ 가 인가되어, 메모리 셀 내의 nMOS 및 pMOS 트랜지스터의 웰 전위는 각각  $-0.5V$  및  $1.5V$ 로 제어되어, 각각의 트랜지스터의 Vth가 상승해 서브 스레숄드 리크전류가 저감된다.

<실시예6>

도 22에 본 발명을 사용한 SRAM 회로의 회로도를 나타낸다. 실시예1은, 일반적으로 횡장(橫長) 셀로 불리는 워드선 방향으로 긴 직사각형의 메모리 셀을 사용한 SRAM 회로에 알맞은 회로구성의 예(例)였다. 횡장 셀은, 워드선과 수직방향으로 긴 n웰과 p웰이 교대로 워드선 방향으로 반복해서 나란한 것에 의해 메모리 셀의 형상이 워드선 방향으로 긴 직사각형이 되는 것이다. 이것에 대하여, 본 실시예에서는, 일반적으로 종장(縱長) 셀로 불리는 메모리 셀을 사용했을 경우에 최적이 되는 회로구성에 관해서 예시한다. 종장 셀은, 비트선과 수직방향으로 긴 n웰과 p웰이 교대로 비트선방향으로 반복해서 나란한 것에 의해 메모리 셀의 형상이 비트선 방향으로 긴 직사각형이 되는 것이다. 도 22 중에서, WL[k]은 k행째의 워드선, VBN[k]은 k행째의 메모리 셀에서 공통인 nMOS 트랜지스터의 웰 노드, VBP[k]은 k행째의 메모리 셀에서 공통인 pMOS 트랜지스터의 웰 노드이다. 실시예1의 도 1이 나타내는 횡장 셀이 SRAM 회로도와 다른 점은, VBN[k] 및 VBP[k]이 WL[k]에 평행하게 연신하도록 배치되는 점이다.

도 23에 회로 각 부의 전위의 변화를 나타낸다. 워드선이 상승할 때에 동시에 nMOS 트랜지스터의 웰 노드전위인 VBN도 하이 전위가 되고, nMOS 트랜지스터의 V<sub>th</sub>가 저하해서 구동력이 증가한다. 이것에 의해, nMOS 트랜지스터의 전류가 증가하고, 기록 특성이 향상한다. 또한, 판독시에도 nMOS 트랜지스터의 전류가 증가하기 때문에 고속동작이 가능해진다. 또 pMOS 트랜지스터의 웰 전위인 VBP은 항상 하이 전위가 된다. 이것은 기록시에 전류가 증가해버리면 기록 특성을 악화시켜버리기 위해서다.

도 24에 메모리 셀의 레이아웃도를 나타낸다. 도면 중의 두꺼운 선으로 둘러싸여진 부분이 웰이 되어, 도 5와는 달리, n웰과 p웰이 교대로 비트선방향으로 반복해서 나란한 종장 메모리 셀이 된다. 이 셀 형상에 기인하고, 종장 셀의 SRAM 회로도는 도 22에 도시한 바와 같이 VBN[k] 및 VBP[k]이 WL[k]에 평행하게 연신하는 구성이 된다.

본 레이아웃 중을 A-A'로 절단했을 경우의 단면도를 도 25에 나타낸다. nMOS 트랜지스터 및 pMOS 트랜지스터의 웰 노드가 접속되어서 형성되는 것을 알 수 있다.

#### <실시예7>

도 26에 본 발명을 사용한 SRAM 회로의 회로도를 나타낸다. 도 26 중에서, V<sub>ssm</sub>은 메모리 셀 내의 구동 트랜지스터의 소스 전극을 접속한 노드, V<sub>cc</sub>은 V<sub>dd</sub>보다 높은 전위의 전원, stby 및 stbyb은 스텐바이시에 입력되는 스텐바이 신호이다. 회로도 중에서, 게이트 전극이 접속되는 부분이 선이 아니라 직사각형으로 표현되며, 도 아래쪽으로 High-Tox로 표시된 트랜지스터 기호가 있다. 이것은, 그 이외의 트랜지스터보다도 게이트 산화 막두께(Tox)가 두꺼운 트랜지스터에서, V<sub>dd</sub>보다 높은 전압을 게이트 전극등에 인가해도 트랜지스터가 파괴되지 않는, 두께막 트랜지스터를 나타내고 있다. 이 트랜지스터는 통상의 LSI에서는 LSI외부와의 입출력 회로로 사용되고 있다. V<sub>cc</sub>은 통상의 LSI로의 입출력 회로에 사용할 수 있는 전원을 나타내고 있으며 현재 1.8V과 2.5V, 3.3V의 전압이 사용되고 있다. 본 실시예에서는 2.5V로써 설명을 하지만, 그 이외의 전위이여도 같은 효과를 얻을 수 있다. stby 및 stbyb은 스텐바이 상태를 나타내는 신호로, stby는 스텐바이시에 하이, stbyb은 스텐바이시에 로우로 제어된다.

도 27에 회로 각부의 동작 상태마다의 전위상태를 나타낸다. 스텐바이 상태 이외에는, 실시예1과 동일하게 된다. 스텐바이 상태에는, VBN은 실시예1과 같은 0V가 되지만, VBP 및 V<sub>ssm</sub>의 전위가 다르다. V<sub>ssm</sub>의 전위는, 약 0.3V 정도로 제어되고, nMOS 트랜지스터가 백 바이어스가 인가된 것과 같은 상태가 되고, 서브 스레숄드 리크전류가 크게 저감된다. 구체적으로는, 1/10이하로 저감할 수 있다. 또한, nMOS 및 pMOS 트랜지스터의 게이트 전극으로부터 채널에 흐르는 게이트 리크 전류도, 전계가 완화되기 때문에 크게 저감된다. V<sub>ssm</sub>의 전위가 제어되었을 경우, pMOS 트랜지스터에 관해서는 소스 드레인간의 전압이 약2/3가 된 정도이기 때문에 리크 전류도 그것에 거의 비례해서 저감될 뿐으로 약2/3정도밖에 하강하지 않는다. 본 회로에서는, pMOS 트랜지스터의 웰 노드에 2.5V의 전위가 인가된다. 이것에 의해, pMOS 트랜지스터의 V<sub>th</sub>가 200mV정도 상승하여 서브 스레숄드 리크전류는 1/100이하로 저감할 수 있다. 이것에 의해, 스텐바이 상태에서의 리크 전류를 크게 저감하는 것이 가능해진다.

또한, 본 발명의 구성에서는, 웰 노드를 SRAM로 사용하는 전원의 전압보다 높은 전압으로 제어할 때에, LSI의 입출력 회로에 사용되는 전원이 웰 노드에 인가되는 구성을 취하고 있다. 따라서, 높은 전압을 발생하는 회로를 여분으로 가질 필요가 없고, 회로면적 및 소비 전력측면에서 유리하다.

한편, pMOS 트랜지스터의 웰 노드에 인가하는 높은 전압은 SRAM 회로에서 사용할 수 있는 전원전압보다 높은 전압이면, LSI의 입출력 회로에 사용된 전원의 전압과 다른 전압이라도 같은 효과를 얻을 수 있다. 따라서, 동일 LSI내에 전원을 생성하는 회로를 구비하여 높은 전압을 발생시키는 것도 가능하다. 또한, 외부로부터 SRAM에 인가되는 전원전압보다 높은 전압을 공급하고, 이것을 pMOS 트랜지스터의 웰 노드에 인가하는 것도 가능하다.

도 31에, 게이트 산화 막두께( $Tox$ )과 매립 산화 막두께( $T_{박스}$ ), 전원전압( $V_{dd}$ )과 pMOS 트랜지스터의 웰 전위( $V_{BP}$ )의 관계의 예를 나타낸다. 패턴1은, 본 실시예에서 상정하고 있는 막두께와 전압의 관계를 나타내고 있다. 패턴2는, pMOS 트랜지스터에 거는 것이 가능한 최대의 전압을 인가하고, 리크 전류를 저감하는 효과를 최대로 했을 경우의 예를 나타내고 있다.

패턴3은, 게이트 산화막의 두께가 얇아지고, 그에 따라 전원전압이 저하되는 관계를 나타내고 있다. 패턴4는, 매립 산화막의 두께를 두껍게 함으로써 웰 노드의 전위를 변화시켰을 때에  $V_{th}$ 가 변동하는 효과가 작아지지만, 그만큼 웰 노드에 인가하는 전압을 높이는 것으로써 동등한 성능을 달성하는 구성의 예를 나타내고 있다. 패턴5는, 매립 산화막의 막두께를 얇게 했을 경우의 예를 나타내고 있다. pMOS 트랜지스터의 웰노드에는 입출력 회로에서 사용할 수 있는 것과 같은 전압이 인가되어 있지만, 매립 산화막두께가 얕기 때문에  $V_{th}$ 가 변동하는 효과가 크고, 패턴2와 거의 동등한 성능을 얻을 수 있다고 생각된다. 패턴6은, 산화막의 막두께는 패턴5와 동일하게, 웰 노드에 더욱 높은 전압을 인가한 예를 나타내고 있다. 이 예로는, 더욱 높은 리크 전류저감 효과를 얻을 수 있다.

패턴7에서는, 매립 산화막의 두께를 더욱 얇게 한 예가 나타나 있다. 웰 노드의 전위는 그것 정도 크지 않지만 패턴2보다도 리크 전류를 저감하는 효과는 크다고 생각된다.

#### <실시예8>

도 28에 본 발명을 사용한 SRAM 메모리 셀 내의 트랜지스터의 전위의 상태를 나타낸다. 본 실시예에서는, 기록시에 0V로부터 상승하는 웰 전위가 0.5V이 된다. 이것에 의해,  $V_{BN}$  및  $V_{BP}$ 을 제어하는 것에 의해 소비되는 전력을 저감할 수 있다. 또한,  $V_{BN}$  및  $V_{BP}$ 의 전위를 제어하는데 걸리는 시간을 짧게 할 수 있고, 고속화의 효과도 있다.

#### <실시예9>

도 29에 본 발명을 사용한 SRAM 회로 각 부분의 전위의 변화를 나타낸다. 본 실시예에서는, 실시예1와는 달리, 제어되어야 할  $V_{BN}$  및  $V_{BP}$ 의 전위가 플 스윙하지 않고 0.6V정도까지밖에 상승하지 않고 있다. 이것에 의해, 실시예8와 같이  $V_{BN}$  및  $V_{BP}$ 을 제어함으로써 소비되는 소비 전력을 억제하는 효과가 있다.

본 실시예는, 실시예1과 같은 회로구성에서 실현하는 것이 가능하다. 한가지 다른 것은,  $V_{BN}$  및  $V_{BP}$ 을 구동하는 구동 회로의 구동력을 작게 하는 것이다. 실시예1에서는,  $V_{BN}$  및  $V_{BP}$ 의 전위를 급속히 변화시키기 위해서 구동력의 큰 구동 회로가 필요했지만, 본 실시예의 회로는 그 구동 회로의 구동력을 작게 함으로써 실현할 수 있다. 실제로는,  $V_{BN}$  및  $V_{BP}$ 을 구동하는 트랜지스터의 게이트 폭을 작게 하면 좋다. 이것에 의해, 실시예1와 비교해서 회로면적도 작게 하는 것이 가능해진다.

종래의 벌크 트랜지스터의 게이트 전극을 구동할 경우에는, 신호의 전위변화가 느리면 핫 커리어가 발생해서 LSI의 신뢰성이 열화하는 등의 문제가 있지만, 본 회로로 변화되는 것은 웰의 전위이기 때문에 핫 커리어 등 신뢰성의 문제도 발생하지 않는다.

#### <실시예10>

도 30에서, 본 발명을 사용한 SRAM 회로내의 메모리 셀의 웰 전위인  $V_{BN}$  및  $V_{BP}$ , 기록, 판독 및 스탠바이 상태에 있어서 얻을 수 있는 전위의 관계를 나타낸다. 패턴1은 실시예1의 예를 나타내고 있다.

패턴2에서는, 실시예1와는 달리 판독시에도  $V_{BN}$ 의 전위를 1.0V로 제어하고 있다.

이것에 의해, 판독시의 nMOS 트랜지스터의 전류가 증가해 고속인 판독 동작이 가능해진다.

패턴3에서는, 스탠바이 상태로  $V_{BP}$ 을 2.5V로 제어함으로써 pMOS 트랜지스터의  $V_{th}$ 를 상승시켜 리크 전류를 크게 저감하는 것이 가능해진다.

패턴4에서는, 스탠바이 상태에서 패턴3보다 더욱이  $V_{BN}$ 의 전위를 마이너스의 전위로 하고 있다. 이것에 의해 nMOS 트랜지스터의  $V_{th}$ 가 상승하고, 리크 전류를 더욱 저감하는 것이 가능해진다.

패턴5에서는, 기록시에 VBN의 전위를 2.5V까지 승압하고, 이것에 의해 nMOS 트랜지스터의 Vth를 크게 저하시킨다. 따라서, nMOS 트랜지스터의 전류가 패턴1등과 비교해서 더욱 커지고, 기록 특성이 더욱이 개선되는 동시에 동작속도가 고속화한다.

패턴6에서는, 판독시의 VBN의 전위를 2.5V까지 더 승압하고, 이것에 의해 nMOS 트랜지스터의 Vth를 크게 저하시킨다. 따라서, nMOS 트랜지스터의 전류가 패턴2와 비교해서 더욱 커지고, 판독 메모리 셀 전류가 크게 개선하고, 동작속도가 고속화한다.

이상의 각 실시예에 의하면, 트랜지스터 동작의 고속화와 리크 전류의 저감이 가능해진다. 또한, SRAM회로의 동작에 필요한 동작 마진이 개선해 동작 특성이 향상한다. 더욱이, 메모리 셀 면적의 증대를 억제할 수 있다.

### 발명의 효과

본 발명에 의하면, 트랜지스터 동작의 고속화와 리크 전류의 저감이 가능해지기 때문에, SRAM 회로의 동작 특성의 향상이 가능해진다.

### 도면의 간단한 설명

도 1은 본 발명이 적용된 SRAM 메모리 셀의 회로구성의 개략도이다.

도 2는 본 발명이 적용된 SRAM내의 웨爾 노드의 전압관계를 나타내는 도면이다.

도 3은 본 발명에서 사용되는 트랜지스터 구조의 단면의 개략도이다.

도 4는 본 발명에서 사용되는 트랜지스터의 등가 회로를 나타내는 도면이다.

도 5는 본 발명이 적용된 SRAM 메모리 셀의 레이아웃의 개략도이다.

도 6은 본 발명이 적용된 SRAM 메모리 셀의 단면도이다.

도 7은 본 발명이 적용된 SRAM 메모리 셀의 단면도이다.

도 8은 본 발명이 적용된 SRAM의 웨爾 노드를 제어하는 회로의 개략도이다.

도 9는 본 발명이 적용된 SRAM의 제어 회로의 개략도이다.

도 10은 본 발명이 적용된 SRAM의 워드선 드라이버의 개략도이다.

도 11은 본 발명이 적용된 SRAM의 워드선 드라이버의 개략도이다.

도 12는 본 발명이 적용된 SRAM내의 각 노드의 전위변화를 나타내는 도면이다.

도 13은 본 발명이 적용된 SRAM내의 웨爾 노드의 전압관계를 나타내는 도면이다.

도 14는 본 발명이 적용된 SRAM 메모리 셀의 회로구성의 개략도이다.

도 15는 본 발명이 적용된 SRAM내의 각 노드의 전위변화를 나타내는 도면이다.

도 16는 본 발명이 적용된 SRAM내의 각 노드의 전위변화를 나타내는 도면이다.

도 17은 본 발명이 적용된 SRAM 메모리 셀의 회로구성의 개략도이다.

도 18은 본 발명이 적용된 SRAM내의 각 노드의 전위변화를 나타내는 도면이다.

도 19는 본 발명이 적용된 SRAM 메모리 셀의 레이아웃의 개략도이다.

도 20은 본 발명이 적용된 SRAM내의 웰 노드의 전압관계를 나타내는 도면이다.

도 21은 본 발명이 적용된 SRAM의 웰 노드를 제어하는 회로의 개략도이다.

도 22는 본 발명이 적용된 SRAM 메모리 셀의 회로구성의 개략도이다.

도 23은 본 발명이 적용된 SRAM내의 각 노드의 전위변화를 나타내는 도면이다.

도 24는 본 발명이 적용된 SRAM 메모리 셀의 레이아웃의 개략도이다.

도 25는 본 발명이 적용된 SRAM 메모리 셀의 단면도이다.

도 26는 본 발명이 적용된 SRAM의 웰 노드를 제어하는 회로의 개략도이다.

도 27은 본 발명이 적용된 SRAM내의 각 노드의 전압관계를 나타내는 도면이다.

도 28은 본 발명이 적용된 SRAM 내의 웰 노드의 전압관계를 나타내는 도면이다.

도 29는 본 발명이 적용된 SRAM 내의 각 노드의 전위변화를 나타내는 도면이다.

도 30은 본 발명이 적용된 SRAM 내의 웰 노드의 전압관계를 나타내는 도면이다.

도 31은 막두께와 웰 노드로의 인가전압의 관계를 나타내는 도면이다.

도 32는 종래의 SRAM 메모리 셀의 회로구성의 개략도이다.

도 33은 본 발명이 적용된 SRAM을 탑재하는 시스템 LSI의 개략도이다.

(부호의 설명)

TR1,TR2,201,202 전송 트랜지스터

DR1,DR2,203,204 구동 트랜지스터

LD1,LD2 205,206 부하 트랜지스터

NT, NB, 207, 208 메모리 셀 내의 데이터 기억 노드

WL 워드선 Vdd 전원선

Vss 접지 전위 LT, BLB, BLT[n],BLB[n],BLT[n+1],BLB[n+1] 비트 선

VBN, VBN [n], VBN [n+1], VBN1, VBN2, VBN[4n] nMOS 웰 노드

VBN[4n+1], VBN[4n+2], VBN[k], VBN1[n], VBN2[n] nMOS 웰 노드

VBP, VBP[n], VBP[n+1], VBP1, VBP2 pMOS 웰 노드

VBP[4n] VBP[4n+1], VBP[4n+2], VBP[k], VBP1[n], VBP2[n] pMOS 웰 노드

1, 11 게이트 전극 2 드레인 전극

3 소스 전극 4, 17, Well 웰

5, 18 지지기판 6, 16 매립 산화막층

7, 13 소자분리층 12 콘택트 콘택트

19 디퓨전 확산층 14 게이트 절연막

15 SOI층 MC 메모리 셀

ys, ys[0]~ys[3] 컬럼 선택 신호 DRv1…웰 노드 드라이버

in…입력 신호 WDR…워드선 드라이버

xa, xb…어드레스 디코드 신호 CK…클록 신호

bwen…기록 신호 D…입력 데이터

Vssd…웰 노드 드라이버의 Vss선 Vddd…웰 노드 드라이버의 Vdd선

Vbnst, Vbpst 스탠바이용 웰 노드 전위선

stby, stbyb 스탠바이상 제어 신호

Vssm 메모리 셀 내 구동 트랜지스터 소스선

Vcc Vdd 보다 높은 전위의 전원선

SOC 시스템LSI의 칩 CPU CPU 코어

CACHE 캐시 메모리 RAM 워크 메모리

PERI 시스템LSI중의 CPU 코어 외의 논리회로.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

## 도면10

## 도면 11

도면12

도면13

도면14

도면15

도면16

도면17

## 도면18

도면19

도면20

## 도면21

## 도면22

도면23

도면24

도면25

## 도면26

기호  $\square$  및  $\square$  은 High-Tox을 나타낸다.

도면27

도면28

도면29

도면30

|          | 판독   |     | 기록   |      | 스탠바이<br>(STAND-BY) |      |

|----------|------|-----|------|------|--------------------|------|

|          | Vbn  | Vbn | Vbn  | Vbn  | Vbn                | Vbn  |

| PATTERN1 | 0V   | 0V  | 1.0V | 1.0V | 0V                 | 1.0V |

| PATTERN2 | 1.0V | 0V  | 1.0V | 1.0V | 0V                 | 1.0V |

| PATTERN3 | 0V   | 0V  | 1.0V | 1.0V | 0V                 | 2.5V |

| PATTERN4 | 0V   | 0V  | 1.0V | 1.0V | -1.0V              | 2.5V |

| PATTERN5 | 0V   | 0V  | 2.5V | 1.0V | 0V                 | 1.0V |

| PATTERN6 | 2.5V | 0V  | 2.5V | 1.0V | 0V                 | 1.0V |

도면31

|          | Tox   | Tbox  | Vdd  | VBP   |

|----------|-------|-------|------|-------|

| PATTERN1 | 2.0nm | 10nm  | 1.2V | 2.5V  |

| PATTERN2 | 2.0nm | 10nm  | 1.2V | 6.0V  |

| PATTERN3 | 1.2nm | 10nm  | 1.0V | 6.0V  |

| PATTERN4 | 1.2nm | 20nm  | 1.0V | 12.0V |

| PATTERN5 | 1.2nm | 5.0nm | 1.0V | 2.5V  |

| PATTERN6 | 1.2nm | 5.0nm | 1.0V | 4.0V  |

| PATTERN7 | 1.2nm | 2.4nm | 1.0V | 1.8V  |

## 도면32

### 도면33