DEUTSCHE DEMOKRATISCHE REPUBLIK

AMT FÜR ERFINDUNGS- UND PATENTWESEN

# PATENTSCHRIFT 126 878

## Wirtschaftspatent

Teilweise aufgehoben gemäß § 6 Absatz 1 des Änderungsgesetzes

zum Patentgesetz

Fachbibliothek

P

Int. Cl. 3

(11) 126 878 (45) 24.12.80 3(51) G 05 B 19/21

B 23 Q 15/00

(21) WP G 05 b / 193 905 (22) 16.07.76

(44)<sup>1</sup> 17.08.77

-

- (71) siehe (72)

- (72) Rose, Max, Dipl.-Ing.; Springer, Manfred, Dipl.-Ing., DD

- (73) siehe (72)

- (74) Hans Geßner, VEB Numerik „Karl Marx“ Karl-Marx-Stadt,

Betrieb des VEB Kombinates Automatisierungsanlagenbau,

9010 Karl-Marx-Stadt, Bornaer Straße 205, PSF 947

-

- (54) Schaltungsanordnung zur inkrementalen Vorgabe von Sollwerten

konstanter Größe in numerischen Steuerungen

-

17 Seiten

<sup>1)</sup> Ausgabedatum der Patentschrift für das gemäß § 5 Absatz 1 ÄndG zum PatG erteilte Patent

**Titel der Erfindung**

Schaltungsanordnung zur inkrementalen Vorgabe von Sollwerten konstanter Größe

**Anwendungsgebiet der Erfindung**

Die Erfindung bezieht sich auf eine Schaltungsanordnung zur inkrementalen Vorgabe von Sollwerten konstanter Größe in numerischen Steuerungen.

Obwohl die Erfindung zur Sollwertvorgabe für eine Vielzahl verschiedenartiger physikalischer Größen einsetzbar ist, kann sie in besonders vorteilhafter Weise zur Vorgabe von Wegsollwerten in numerischen Steuerungen für Mehrachsenwerkzeugmaschinen Verwendung finden.

**Charakteristik der bekannten technischen Lösungen**

Bekannt ist durch die Patentschrift DD-WP 114 470 eine Schaltungsanordnung zur inkrementalen Vorgabe von Soll-

werten in numerischen Steuerungen, in der von einem programmgesteuerten ersten Taktgenerator Impulse mit einer der gewünschten Sollwertvorgabegeschwindigkeit entsprechenden Frequenz erzeugt werden. Aus jedem dieser Impulse wird durch einen zweiten Taktgenerator eine Folge von Rechentaktimpulsen abgeleitet, die einer Sollwertrechenvorrichtung, wie z. B. einem Interpolationsrechner, zur schrittweisen Verrechnung der zu verknüpfenden Größen zugeführt werden. Um eine hohe Sollwertvorgabegeschwindigkeit zu erreichen und um gleichzeitig den Einsatz von billigen hochintegrierten Schaltkreisen niedriger Grenzfrequenz in numerischen Steuerungen zu ermöglichen, wurde vorgeschlagen, zwischen dem ersten programmsteuerbaren Taktgenerator und den zweiten Taktgenerator einen steuerbaren Frequenzteiler zu schalten.

Diese Anordnung wurde durch die Schaltung der Patentschrift DD-WP 118 734 weiter vereinfacht, ohne daß der Steuerungsablauf unzumutbar beeinflußt wurde. Diese Schaltungsanordnung enthält ebenfalls einen programmsteuerbaren Taktgenerator zum Erzeugen von zur programmierten Sollwertvorgabegeschwindigkeit frequenzproportionalen Impulsen und eine seriell arbeitende Sollwertrecheneinrichtung, wobei ein Ausgang des Taktgenerators direkt mit einem Rechentakteingang der Sollwertrecheneinrichtung und parallel dazu mit einem Impulseingang eines steuerbaren Frequenzteilzers verbunden ist, und wobei erste Ausgänge der Sollwertrecheneinrichtung auf erste Eingänge von ihnen jeweils zugeordneten UND-Gattern geführt sind, deren zweiten Eingängen ein Frequenzteiler vorgeschaltet ist.

Die Anordnung ist dort so getroffen, daß ein Speicher für den programmierten Wert der Sollwertvorgabegeschwindigkeit vorgesehen ist, der einen ersten Ausgang für niedrigwertige Ziffernstellen und einen zweiten Ausgang für hochwertige Ziffernstellen aufweist. Der erste Ausgang des Speichers ist mit dem ersten Steuereingang des Taktgenerators und der zweite Ausgang des Speichers mit einem ersten Eingang eines Entschlüsslers verbunden. Die Ausgänge des Entschlüsslers sind auf Steuereingänge des Frequenzteilers für diskrete Teilverhältnisse geführt. Der dem größten Teilerfaktor zugeordnete Ausgang des Entschlüsslers ist über einen Negator auf einen dominierenden zweiten Steuereingang des Taktgenerators geschaltet.

Der Nachteil dieser Lösung besteht darin, daß bei hohen programmierten Sollwertvorgabegeschwindigkeiten nur ein der Zahl der möglichen am Frequenzteiler einstellbaren Teilverhältnisse entsprechendes Frequenzspektrum der an den Ausgängen der UND-Gatter abnehmbaren Steuerimpulse erzeugbar ist, wodurch eine optimale Auslastung des jeweils gesteuerten Objektes, z. B. eine Werkzeugmaschine, nicht in jedem Fall gegeben ist. Zum anderen ist die Lösung noch recht aufwendig, wenn die Forderung besteht, alle Baugruppen des Systems in billiger hochintegrierter Schaltkreistechnik niedriger Grenzfrequenz zu realisieren sowie möglichst hohe Geschwindigkeiten bei hoher Genauigkeit der Sollwertvorgabe zu erreichen. Hierzu wäre der Taktgenerator in teurerer Paralleltechnik auszuführen, damit die maximal zulässige Rechentaktfrequenz für die Sollwertrecheneinrichtung erreicht werden kann.

#### Ziel der Erfindung

Das Ziel der Erfindung besteht darin, zur Vorgabe der Sollwerte den Einsatz von hochintegrierten Schaltkreisen niedriger Grenzfrequenz bei minimalem schaltungstechnischen

Aufwand und guter Genauigkeit der Sollwertvorgabe auch für hohe Sollwertvorgabegeschwindigkeiten zu ermöglichen.

#### Darlegung des Wesens der Erfindung

Aufgabe der Erfindung ist es, eine Schaltungsanordnung zur inkrementalen Vorgabe von Sollwerten konstanter Größe in numerischen Steuerungen, insbesondere für Mehrachsenwerkzeugmaschinen zu schaffen, unter Verwendung einer Sollwertrecheneinrichtung, eines steuerbaren Frequenzteilers, eines ersten und zweiten Taktgenerators und eines Speichers, wobei die programmierte Sollwertvorgabegeschwindigkeit in den Speicher eingeschrieben wird und durch die Anordnung eine Prüfung erfolgt, in welcher Größenordnung die programmierte Sollwertvorgabegeschwindigkeit liegt. Abhängig vom Ergebnis dieser Prüfung soll das entsprechende Teilverhältnis am Frequenzteiler aufgerufen werden, eine entsprechende Rechengröße der Sollwertrecheneinrichtung zugeführt sowie an den Speicher eine entsprechende Zahl von Schiebetakten ausgegeben werden, die gewährleisten, daß die so modifizierte programmierte Sollwertvorgabegeschwindigkeit vom ersten Taktgenerator verarbeitet werden kann. Erfindungsgemäß wird die Aufgabe dadurch gelöst, daß der Ausgang des Speichers über einen Zwischenspeicher mit dem Eingang einer Auswahlseinrichtung verbunden ist, deren erster Ausgang auf den Setzeingang eines Rückwärtszählers geführt ist. Der Impulseingang des Rückwärtszählers ist mit dem Takteingang verschaltet und der negierte Nullstandsausgang des Rückwärtszählers ist konjunktiv mit dem Takteingang verknüpft an den Eingang des Speichers geführt. Der Ausgang der Auswahlschaltung ist mit der Sollwertrecheneinrichtung verbunden. Dem ersten Taktgenerator ist eine Impulsglättungsschaltung nachgeschaltet und der Taktgenerator besteht aus einem seriell arbeitenden Haupttaktgenerator und einem ihm nachgeschalteten Hilfstaktgenerator.

Eine Ausgestaltung der Erfindung sieht vor, daß im Haupttaktgenerator der Ausgang eines zweiten Speichers für eine Konstante über ein erstes Tor an den ersten Eingang einer ersten differenzbildenden seriellen Rechenschleife geschaltet ist, deren Übertragungsausgang mit dem Steuereingang des ersten Tores und deren zweiter Eingang mit dem ersten Eingang des ersten Taktgenerators verbunden ist. Im Hilfstaktgenerator ist der Registerausgang einer zweiten differenzbildenden Rechenschleife mit dem ersten Eingang eines Differenzbildners verschaltet, dessen Ausgang auf den Steuereingang eines zweiten Frequenzteilers und parallel dazu auf den ersten Eingang einer Dividierschaltung geführt, deren Ausgang über den ersten Eingang eines zweiten Tores mit dem Eingang der zweiten Rechenschleife verbunden ist. Der Ausgang des zweiten Speichers ist mit dem zweiten Eingang der Dividierschaltung und parallel dazu mit dem zweiten Eingang des zweiten Tores verschaltet, dessen Steuereingang mit dem Übertragungsausgang der ersten Rechenschleife verbunden ist. Der Ausgang des zweiten Frequenzteilers ist an den Ausgang des ersten Taktgenerators angeschlossen.

Im Haupttaktgenerator wird ständig der Wert der programmierten Sollwertvorgabegeschwindigkeit von der im zweiten Speicher bereitgestellten Konstante subtrahiert, bis die Differenz kleiner als Null ist. Die Zwischenergebnisse dieser Rechnung werden im Hilfstaktgenerator mit jedem Rechenlauf im Differenzbildner mit dem in der zweiten differenzbildenden Rechenschleife, der mit jedem Übertragsimpuls am Übertragungsausgang der ersten differenzbildenden Rechenschleife die Konstante aus dem zweiten Speicher zugeführt wird, bereitgestellten Wert verglichen. In Abhängigkeit vom Vorzeichen und der Größe des Betrages des Vergleichsergebnisses wird der zweite Frequenzteiler so angesteuert, daß an dessen Ausgang pro Rechentaktzyklus

kein, ein oder mehrere Impulse der pro Rechenumlauf verfügbaren Rechentaktimpulse ausgegeben werden, und durch entsprechende Steuerung der Dividierschaltung gewährleistet, daß entweder kein oder ein entsprechender Bruchteil der im zweiten Speicher bereitgestellten Konstante in der zweiten differenzbildenden Rechenschleife verarbeitet wird, so daß eine ständige Ausregelung der im Differenzbildner ermittelten Differenz gegen den Wert Null erfolgt.

Auf diese Weise wird erreicht, daß die erreichbare Ausgangsimpulsfrequenz des seriell arbeitenden ersten Taktgenerators gleich der Grundtaktfrequenz ist, mit der der erste Taktgenerator betrieben wird.

#### Ausführungsbeispiel

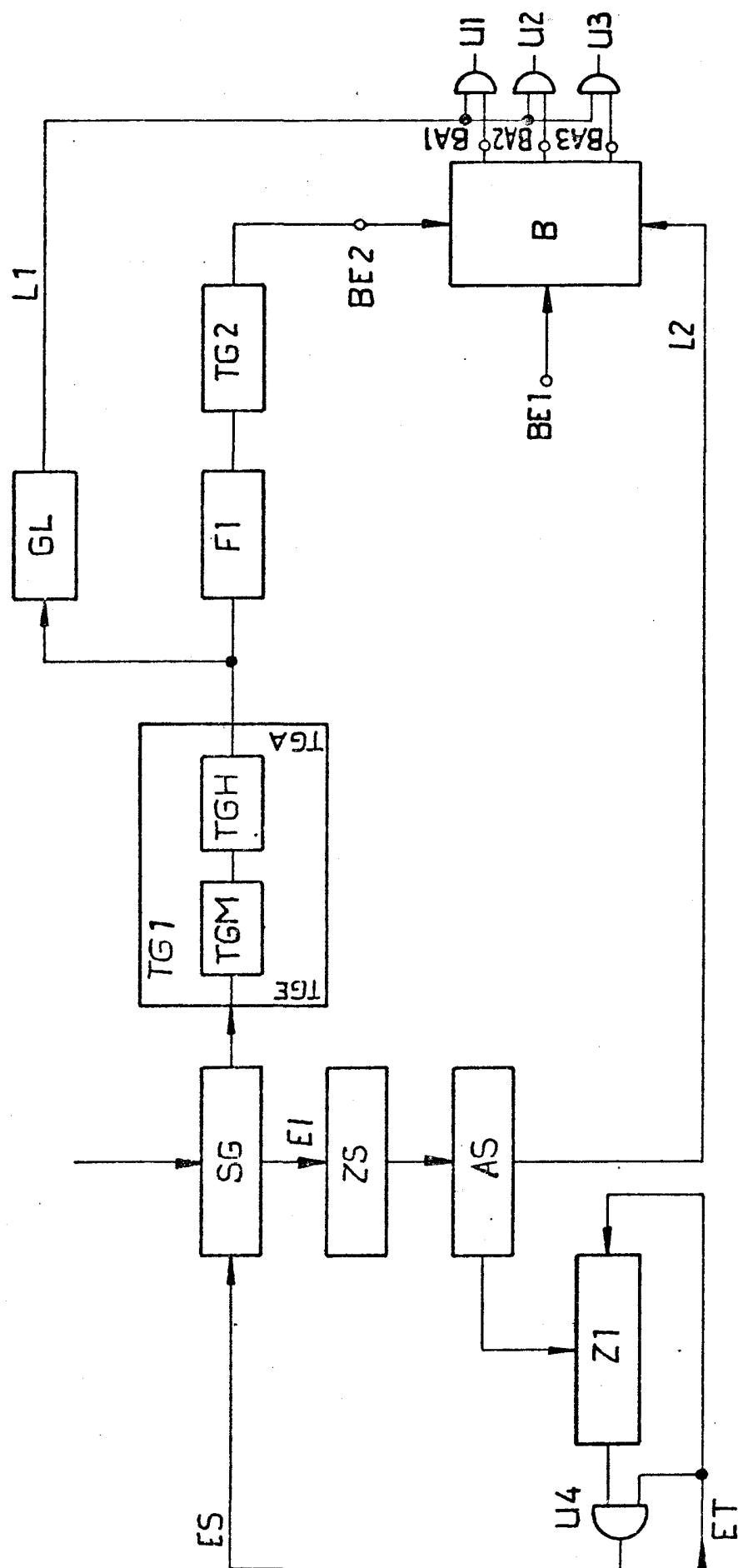

Die Zeichnung zeigt in

Fig. 1: die erfundungsgemäße Schaltungsanordnung im Blockschaltbild,

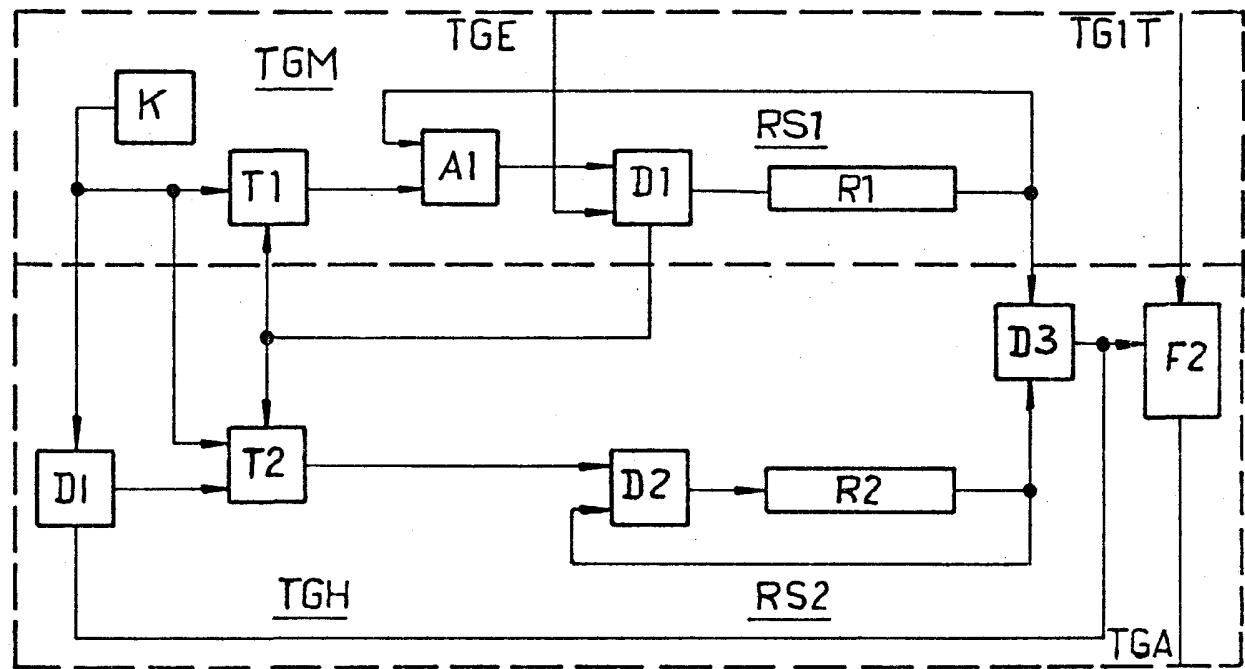

Fig. 2: ein detailliertes Blockschaltbild des Taktgenerators TG 1 aus Fig. 1.

Das Ausführungsbeispiel bezieht sich auf die Anwendung der Erfindung zur Steuerung einer dreiachsigen Werkzeugmaschine und soll anhand der Fig. 1 erläutert werden.

Ein bei der Steuerung von Werkzeugmaschinen für die Sollwertrecheneinrichtung eingesetzter 3D-Bahninterpolator B erhält über seinen Eingang BE 1 die geometrischen Daten der zu interpolierenden Bahn. Im Speicher SG wird mit der Eingabe der Bahndaten in den Interpolator B der programmierte Vorschubgeschwindigkeitssollwert bereitgestellt, wobei die Anwendung der direkten Vorschubprogrammierung vorgesehen ist. Der Vorschubgeschwindigkeitssollwert wird als binäre Zahl dargestellt. Der Speicher SG ist als Schieberegister ausgeführt. Nachdem der programmierte Vorschubgeschwindigkeitssollwert seriell in dem Speicher SG eingeschrieben wurde, er-

folgt eine parallele Übernahme der Ziffern aus den höchstwertigen Speicherstellen des Speichers SG in den Entschlüssler E über dessen Eingang EI. Abhängig vom Wert dieser Ziffern werden Schiebetaktimpulse erzeugt und über die Leitung L 2 der im Interpolator B zu verrechnende Subtrahend festgelegt.

Die Schiebetaktimpulse werden über Leitung ES dem Schiebeteakteingang des Speichers SG zugeführt. Nach dieser Modifizierung der binären Vorschubgeschwindigkeitszahl erfolgt die serielle oder parallele Übergabe der Ziffern aus den niedrigwertigen Speicherstellen des Speichers SG an den Steuereingang TGE des ersten Taktgenerators TG 1. Dessen Ausgangsimpulse gelangen auf den Impulseingang des Frequenzteilers F 1.

Dem Zwischenspeicher ZS ist eine Auswahlschaltung AS nachgeschaltet, in der der Wert des höchstwertigsten Bits dieser Ziffernfolge bzw. der Wert Null ermittelt wird. Die Auswahlschaltung AS bestimmt die Größe des Divisors, um den der Vorschubgeschwindigkeitssollwert über den Rückwärtszähler Z 1 modifiziert wird.

Mit dem Einschreiben eines Wertes, der  $> 0$  ist, wird über den negierten Nullstandsausgang des Zählers Z 1 das UND-Gatter U 4 geöffnet, so daß die vom Eingang EI zugeführten Grundtaktimpulse als Schiebetaktimpulse über den Ausgang ES an den Schiebeteakteingang des Speichers SG gelangen. Die Grundtaktimpulse werden auch an den Impulseingang des Rückwärtszählers Z 1 geleitet. Sobald der Rückwärtszähler Z 1 den Zählstand Null erreicht hat, wird das UND-Gatter U 4 geschlossen und es beginnt die bereits beschriebene Impulserzeugung durch den Taktgenerator TG 1 und somit der Betrieb des Interpolators. Die am Ausgang des Taktgenerators TG 1 bereitgestellten Impulse gelangen an den Eingang  $\overline{F_1}$  des Frequenzteilers F 1.

Zur Erhöhung der zeitlichen Gleichförmigkeit ist der erfundungsgemäßen Anordnung eine Impulsglättungsschaltung GL nachgeschaltet.

Durch den Aufbau des Taktgenerators TG 1 aus einem seriell arbeitenden Haupttaktgenerator TGM und einem ihm nachgeschalteten Hilftaktgenerator TGH nach Fig. 2 ist es möglich, am Ausgang des Taktgenerators TG 1 eine Impulsfolge mit einer der durch die beschriebene Stellenverschiebung modifizierte Vorschubgeschwindigkeitszahl proportionalen mittleren Frequenz abzugreifen, die maximal gleich der Grundtaktfrequenz ist, mit der der seriell arbeitende Taktgenerator TG 1 betrieben wird. Somit ist es trotz serieller Verarbeitung im Taktgenerator TG 1 möglich, den Interpolator B mit einer Rechentaktfrequenz anzusteuern, die bis in den Bereich der für MOS-FET-Schaltkreise zulässigen Grenzfrequenz geht.

Im folgenden soll nun eine mögliche Ausführungsform des Taktgenerators TG 1 näher erläutert werden.

Dessen Haupttaktgenerator TGM enthält eine differenzbildende serielle Rechenschleife RS 1, die aus dem Adder A 1, dem Differenzbildner D 1 und dem Differenzregister R 1 besteht. Ihr ist ein Speicher K zur Aufnahme eines Konstantwertes über ein Tor T 1 vorgeschaltet, das vom Übertragsausgang des Differenzbildners D 1 ansteuerbar ist. Alle Bausteine des Taktgenerators TG 1 werden über den Eingang TG 1T in nicht dargestellter Weise mit der Grundtaktfrequenz gesteuert.

Der Aufbau ist so getroffen, daß nach jeweils 32 Grundtaktimpulsen ein Rechenlauf in der Rechenschleife RS 1 abgeschlossen ist. Im Speicher K wird die Zahl  $4096 = 2^{12}$  in

binärer Form als Konstante bereitgestellt. Während die modifizierte Vorschubgeschwindigkeitszahl mit jedem Rechenumlauf in der Rechenschleife RS 1 subtrahiert wird, erfolgt auf jeden Übertragsimpuls am Übertragsausgang des Differenzbildners D 1, der einen Vorzeichenwechsel des im Differenzregister R 1 stehenden Wertes anzeigt, eine Addition der Konstante und eine Verrechnung des nun negativen Restwertes aus dem Differenzregister R 1 im Adder A 1. Die Addition der Konstante kann in einfacher Weise so erfolgen, daß zu dem Zeitpunkt innerhalb jedes Grundtaktzyklusses von 32 Grundtaktimpulsen ein L-Signal am Eingang des Tores T 1 bereitgestellt wird, in dem die Verrechnung der Ziffernstelle mit der Wertigkeit  $2^{12}$  vorgesehen ist. Auf diese Weise erscheint am Übertragsausgang des Differenzbildners D 1 eine der am Eingang TGE zugeführten Vorschubgeschwindigkeitszahl frequenzproportionale Impulsfolge. Deren Maximalfrequenz beträgt jedoch nur 1/32 der für den in MOS-FET-Technik aufgebauten Bahninterpolator B zulässigen Rechentaktfrequenz, so daß dieser bei erforderlichen sehr hohen Vorschubgeschwindigkeiten zu langsam arbeitet und nur mit einer niedrigen Rechenauflösung betrieben werden könnte. Zur Vermeidung dieses Nachteiles dient der dem Haupttaktgenerator TGM nachgeschaltete Hilfstaktgenerator TGH, an dessen Ausgang eine annähernd 32-fach größere Impulsfolgefrequenz zur Ansteuerung des Bahninterpolators B und des Frequenzteilers F 1 ausgegeben wird, als es die Frequenz der Übertragsimpulse am Übertragsausgang des Differenzbildners D 1 ist.

Der Hilfstaktgenerator TGH enthält ebenfalls eine differenzbildende serielle Rechenschleife RS 2, die aus dem Differenzbildner D 2 und dem Differenzregister R 2 besteht. Ihrem Eingang ist ein Tor T 2 vorgeschaltet, dessen Steuereingang mit dem Übertragsausgang des Differenzbildners D 1 verbunden ist. Der Ausgang des Differenzbildners R 2 ist auf einen Eingang eines Differenzbildners D 3 und dessen

Ausgang auf den Steuereingang einer Dividierschaltung DI geführt. Deren Ausgang ist an einen ersten Eingang des Tores T 2 geschaltet. Der zweite Eingang des Tores T 2 ist mit dem Ausgang des Speichers K verbunden. Auf den zweiten Eingang des Differenzbildners D 3 ist der Ausgang des Differenzregisters R 1 geführt. Der Ausgang des Differenzbildners D 3 ist weiterhin mit dem Steuereingang eines Frequenzteilers F 2 verbunden, dessen Impulseingang mit der Grundtaktfrequenz über den Eingang TG 1T angesteuert wird.

Gleichzeitig mit der Zuführung der Konstante aus dem Speicher K über das Tor T 1 an das Adder A 1 und der Verrechnung der entsprechenden Vorschubgeschwindigkeitszahl im Differenzbildner D 1 wird die Konstante über das Tor T 2 negiert auf den negativen Eingang des Differenzbildners D 2 geführt. Durch die zweifache Invertierung steht die Konstante dann als positiver Wert im Differenzregister R 2. Während des darauffolgenden Rechenumlaufes wird der Inhalt des Differenzregisters R 1 vom Inhalt des Differenzregisters R 2 im Differenzbildner D 3 subtrahiert. Das Ergebnis dieser Subtraktion ist infolge der bisher einmalig erfolgten Subtraktion der Vorschubgeschwindigkeitszahl von der konstanten Zahl 4096 größer als Null.

In Abhängigkeit vom Betrag der vom Differenzbildner D 3 ermittelten positiven Differenz wird die Dividierschaltung DI und der Frequenzteiler F 2 angesteuert. Ist der Betrag der Differenz 128, so wird der Divisor 32 und das Teilverhältnis 1 : 32 im Frequenzteiler F 2 aufgerufen. Somit gelangt von den 32 Grundtaktimpulsen des nachfolgenden Rechenumlaufes, die über den Eingang TG 1T auch dem Impulseingang des Frequenzteilers F 2 zugeführt werden, ein einziger Impuls an den Ausgang des Frequenzteilers F 2 und somit an den Ausgang des Taktgenerators TG 1. Außerdem wird in diesem folgenden Rechenlauf 1/32 der konstanten Zahl aus dem Speicher K vom Inhalt den

Differenzregister R 2 subtrahiert. Ist die Differenz  $< R 2 > - < R 1 >$  der Inhalte der Differenzregister R 1 und R 2 größer als 128, so wird in Abhängigkeit vom Betrag der Differenz im Frequenzteiler F 2 ein anderes Teilverhältnis und in der Dividierschaltung DI ein entsprechend kleinerer Divisor aufgerufen.

Ist die durch den Differenzbildner D 3 berechnete Differenz  $\leq$  Null, so erfolgt eine Blockierung des Frequenzteilers F 2 und der Dividierschaltung DI, wodurch keine Verrechnung in der Rechenschleife RS 2 stattfindet. Am Ausgang des Taktgenerators TG 1 wird in diesem Falle kein Impuls bereitgestellt. Auf diese Weise erfolgt eine dem positiven Differenzbetrag entsprechende Verrechnung eines Bruchteiles der im Speicher K bereitgestellten konstanten Zahl in der Rechenschleife RS 2 und in den einzelnen Rechenumläufen eine ständige Ausregelung der im Differenzbildner D 3 ermittelten Differenz gegen den Wert Null. Mit jedem Übertragsimpuls vom Übertragsausgang des Differenzbildners D 1 wird neben dem Tor T 1 auch das Tor T 2 erneut angesteuert und die Konstante aus dem Speicher K der Rechenschleife RS 2 zugeführt, wodurch sich der geschilderte Vorgang wiederholt. Wichtig ist hierbei nur, daß jedem Teilverhältnis des Frequenzteilers F 2 ein fester Divisor in der Dividierschaltung DI zugeordnet ist.

Zur Vereinfachung des Schaltungsaufbaues kann der Frequenzteiler F 2 nur für Teilverhältnisse und die Dividierschaltung DI nur für Divisoren ausgelegt sein, die Potenzen der Zahl 2 sind, wodurch die Division lediglich durch entsprechende Verzögerung der konstanten Zahl aus dem Speicher realisierbar wäre.

Beispielsweise könnte die folgende Zuordnung des Divisors in der Dividierschaltung DI und des Teilverhältnisses  $t_2$  am Frequenzteiler F 2 zur Differenz  $\Delta = < R 2 > - < R 1 >$  der Inhalte der Differenzregister R 1 und R 2 vorgenommen werden:

|      | $\Delta$ |          |             | $t_2$     | d     |

|------|----------|----------|-------------|-----------|-------|

| 0    | <        | $\Delta$ | $\leq 128$  | $1 : 2^5$ | $2^5$ |

| 128  | <        | $\Delta$ | $\leq 256$  | $1 : 2^4$ | $2^4$ |

| 256  | <        | $\Delta$ | $\leq 512$  | $1 : 2^3$ | $2^3$ |

| 512  | <        | $\Delta$ | $\leq 1024$ | $1 : 2^2$ | $2^2$ |

| 1024 | <        | $\Delta$ | $\leq 2048$ | $1 : 2^1$ | $2^1$ |

| 2048 | <        | $\Delta$ | $\leq 4096$ | $1 : 2^0$ | $2^0$ |

Die Ausgangsimpulsfolge des Taktgenerators TG 1 besitzt bereits eine recht gute zeitliche Gleichförmigkeit, die durch den Frequenzteiler F 1 insbesondere bei niedrigeren Vorschubgeschwindigkeitssollwerten infolge des hohen Teilerfaktors noch verbessert wird und somit von den den UND-Gattern U 1, U 2 und U 3 nachgeschalteten Lageregelkreisen zufriedenstellend verarbeitet werden kann

### Erfindungsanspruch

1. Schaltungsanordnung zur inkrementalen Vorgabe von Sollwerten konstanter Größe in numerischen Steuerungen, insbesondere für Mehrachsenwerkzeugmaschinen, unter Verwendung einer Sollwertrecheneinrichtung, eines steuerbaren Frequenzteilers, eines ersten und zweiten Taktgenerators und eines Speichers, gekennzeichnet dadurch, daß der Ausgang des Speichers (SG) über einen Zwischenspeicher (ZS) mit dem Eingang einer Auswahlseinrichtung (AS) verbunden ist, deren erster Ausgang auf den Setzeingang eines Rückwärtszählers (Z 1) geführt ist, daß der Impulseingang des Rückwärtszählers (Z 1) mit dem Takteingang (ET) verschaltet ist und daß der negierte Nullstandsausgang des Rückwärtszählers (Z 1) konjunktiv mit dem Takteingang (ET) verknüpft an den Eingang des Speichers (SG) geführt ist, daß der Ausgang der Auswahlschaltung (AS) mit der Sollwertrecheneinrichtung (B) verbunden ist, daß dem ersten Taktgenerator (TG 1) eine Impulsglättungsschaltung (GL) nachgeschaltet ist und daß der Taktgenerator (TG 1) aus einem seriell arbeitenden Haupttaktgenerator (TGM) und einem ihm nachgeschalteten Hilfstaktgenerator (TGH) besteht.

2. Schaltungsanordnung nach Punkt 1, gekennzeichnet dadurch, daß im Haupttaktgenerator (TGM) der Ausgang eines zweiten Speichers (K) für eine Konstante über ein erstes Tor (T 1) an den ersten Eingang einer ersten differenzbildenden seriellen Rechenschleife (RS 1) geschaltet ist, deren Übertragsausgang mit dem Steuereingang des ersten Tores (T 1) und deren zweiter Eingang mit dem ersten Eingang (TGE) des ersten Taktgenerators (TG 1) verbunden ist, und daß im Hilfstaktgenerator (TGH) der Registerausgang einer zweiten

differenzbildenden, seriellen Rechenschleife (RS 2) mit dem ersten Eingang eines Differenzbildners (DB) verbunden ist, dessen Ausgang auf den Steuereingang eines zweiten Frequenzteilchers (F 2) und parallel dazu auf den ersten Eingang einer Dividierschaltung (DI) geführt ist, deren Ausgang über den ersten Eingang eines zweiten Tores (T 2) mit dem Eingang der zweiten Rechenschleife (RS 2) verbunden ist, daß der Ausgang des zweiten Speichers (K) mit dem zweiten Eingang der Dividierschaltung (DI) und parallel dazu mit dem zweiten Eingang des zweiten Tores (T 2) verschaltet ist, dessen Steuereingang mit dem Übertragsausgang der ersten Rechenschleife (RS 1) verbunden ist, und daß der Ausgang des zweiten Frequenzteilchers (F 2) an den Ausgang (TGA) des ersten Taktgenerators (TG 1) angeschlossen ist.

Hierzu 2 Seiten Zeichnungen

Fig. 1

Fig. 2