## **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>6</sup> :                                                                            |           | (11) International Publication Number: WO 96/41326                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G09G 3/20                                                                                                                          | <b>A1</b> | (43) International Publication Date: 19 December 1996 (19.12.96)                                                                                                         |

| (21) International Application Number: PCT/US                                                                                      | 96/092    | (81) Designated States: AL, AM, AU, BB, BG, BR, CA, CN, CZ,<br>EE, FI, GE, HU, IS, JP, KG, KP, KR, LK, LR, LT, LV,                                                       |

| (22) International Filing Date: 5 June 1996 (0                                                                                     | 05.06.9   | MD, MG, MK, MN, MX, NO, NZ, PL, RO, SG, SI, SK, TR, TT, UA, US, UZ, VN, ARIPO patent (KE, LS, MW, SD, SZ, UG), Eurasian patent (AM, AZ, BY, KG, KZ, MD,                  |

| (30) Priority Data: 08/482,192 7 June 1995 (07.06.95)                                                                              | τ         | RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG). |

| (71) Applicant (for all designated States except US): EC INC. [US/US]; Suite 115, 385 Moffett Park Drive vale, CA 94089-1208 (US). |           |                                                                                                                                                                          |

| (72) Inventor; and (75) Inventor/Applicant (for US only): BLOOM, Da [US/US]; 140 Golden Oak Drive, Portola Val 94043 (US).         |           | м.                                                                                                                                                                       |

| (74) Agents: HAVERSTOCK, Thomas, B. et al.; Have Associates, Suite 420, 260 Sheridan Avenue, Palo 94306 (US).                      |           |                                                                                                                                                                          |

(54) Title: BINARY TIME MODULATION WITH DEAD PERIODS FOR MATRIX DISPLAY SYSTEMS

### (57) Abstract

A display system uses a weighted PWM scheme to deliver control during a frame time for developing a plurality of grayscale levels in each of a plurality of pixels. Of all the weighted subframes, a predetermined number of the shortest subframes utilize a like subframe duration. However, to provide additional levels of grayscale, differing durations of 'on' time are utilized in these like subframes. Thus, all but one of these like-time subframes has a dead zone time during which the pixels are never activated. A clear circuit turns 'off' the illuminated pixels during the dead zone time.

# FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM<br>AT<br>AU | Armenia<br>Austria<br>Australia | GB<br>GE | United Kingdom<br>Georgia    | MW<br>MX | Malawi<br>Mexico         |

|----------------|---------------------------------|----------|------------------------------|----------|--------------------------|

| BB             | Barbados                        | GN       | Guinea                       | NE       | Niger                    |

| BE             |                                 | GR       | Greece                       | NL       | Netherlands              |

| BF             | Belgium<br>Burkina Faso         | HU       | Hungary                      | NO       | Norway                   |

| BG             |                                 | IE       | Ireland                      | NZ       | New Zealand              |

| BJ             | Bulgaria                        | IT       | Italy                        | PL       | Poland                   |

| BR             | Benin                           | JP       | Japan                        | PT       | Portugal                 |

| BY             | Brazil                          | KE       | Kenya                        | RO       | Romania                  |

| CA             | Belarus                         | KG       | Kyrgystan                    | RU       | Russian Federation       |

| CF             | Canada                          | KP       | Democratic People's Republic | SD       | Sudan                    |

| CG             | Central African Republic        |          | of Korea                     | SE       | Sweden                   |

|                | Congo                           | KR       | Republic of Korea            | SG       | Singapore                |

| CH             | Switzerland                     | KZ       | Kazakhstan                   | SI       | Slovenia                 |

| CI             | Côte d'Ivoire                   | LI       | Liechtenstein                | SK       | Slovakia                 |

| CM             | Cameroon                        | LK       | Sri Lanka                    | SN       |                          |

| CN             | China                           | LR       | Liberia                      | SZ       | Senegal                  |

| CS             | Czechoslovakia                  | LT       | Lithuania                    | TD       | Swaziland                |

| CZ             | Czech Republic                  | LU       | Luxembourg                   | TG       | Chad                     |

| DE             | Germany                         | LV       | Latvia                       | TJ       | Togo                     |

| DK             | Denmark                         | MC       | Monaco                       | TT       | Tajikistan               |

| EE             | Estonia                         | MD       | Republic of Moldova          |          | Trinidad and Tobago      |

| ES             | Spain                           | MG       | Madagascar                   | UA       | Ukraine                  |

| FI             | Finland                         | ML       | Mali                         | UG<br>US | Uganda                   |

| FR             | France                          | MN       | Mongolia                     |          | United States of America |

| GA             | Gabon                           | MR       | Mauritania                   | UZ       | Uzbekistan               |

|                |                                 | -        |                              | VN       | Viet Nam                 |

## BINARY TIME MODULATION WITH DEAD PERIODS FOR MATRIX DISPLAY SYSTEMS .

## Field of the Invention

5

10

15

20

25

30

This invention relates to the field of pulse-width modulation for providing grayscale differentiation for displays. More particularly, the present invention is for a modified pulse-width modulation technique which provides very short 'on' times without requiring a commensurate increase in electrical bandwidth.

## Background of the Invention

When displaying an image on a digital display, a pixel is either 'on' or 'off'. To formulate a more variable image it is desirable to provide selectable grayscale. Such increased variability can be used to provide more information or more realism in an image. For example, consider a display where an 'on' pixel is white and an 'off' pixel is black. To achieve an in-between state, eg., gray, the pixel can be toggled equally between 'on' and 'off'. The eye of the average viewer automatically integrates this toggled pixel to perceive a gray image rather than black or white. To achieve a lighter or darker gray, the duty cycle for toggling the pixel can be adjusted to be on more or less of the time, respectively. It is well understood that such grayscale techniques can also apply to color systems to formulate varying intensities of color. Nevertheless, to avoid unnecessarily obscuring the invention in extraneous detail, the remainder of this disclosure will only discuss whites, blacks and varying levels of grays. It will be understood that colors are also contemplated within the teachings of the present invention.

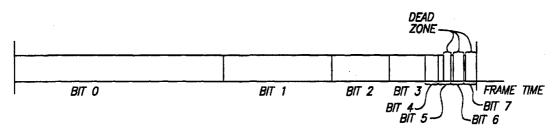

The technique described immediately above is conventionally as pulse-width modulation (PWM). It is well known to implement a PWM scheme as either unweighted or weighted. Figure 1 illustrates a conventional 3-bit unweighted scheme. According to the unweighted scheme a pixel cycle, commonly known as a frame, is divided into seven equal duration time slots, or subframes. The pixel can be activated during any number of the subframes from zero through seven. For typical frames, the intensity of the pixel is completely dependent upon the duration the pixel is 'on'. The same intensity will be achieved when activating only a single subframe regardless of which of the subframes is used. Similarly, the same intensity will be achieved where four subframes are activated whether the first four, last four or alternating subframes are activated. Thus, in the system

of Figure 1, there are eight intensity levels ranging from having the pixel 'off' in all the subframes to having the pixel 'on' in all the time slots.

5

10

15

20

25

30

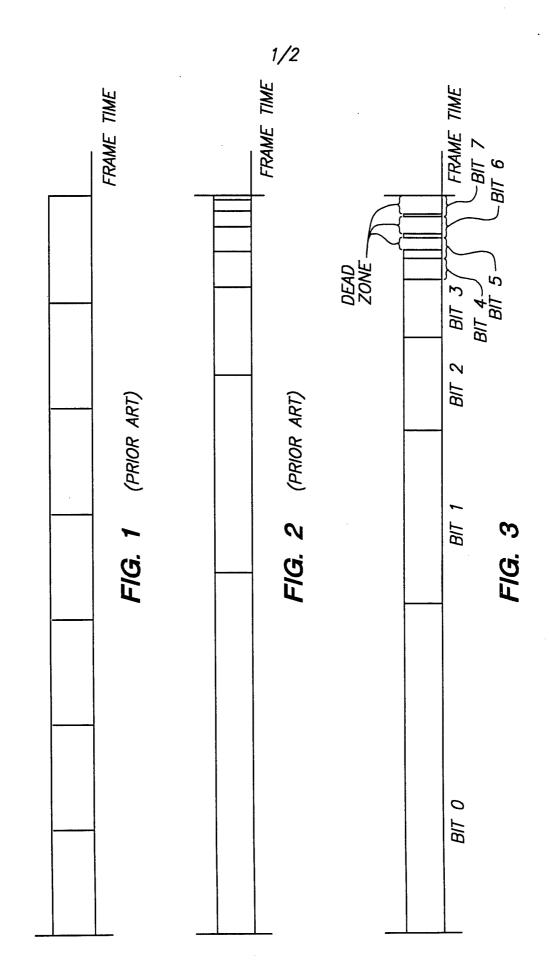

Figure 2 illustrates a conventional weighted 8-bit PWM scheme. In a weighted scheme, each subframe has a distinct duration. In a conventional weighted scheme such as shown in Figure 2, each subframe has twice the duration of the successive subframe. In this way, the intensity of the pixel can be selected using conventional binary counting. Thus, the scheme illustrated in Figure 2 can select among 256 (0 to 255) levels of grayscale from black to white. In the general weighted case, the frame-time is divided into N subframes, with the duration of each subframe selected by the weight of the bit. In an N-bit system, the frame-time is weighted by  $1/2^n$  where  $n=\{0,N\}$  and the sum of all intervals is  $1/2+1/4+..+1/2^N=(2^N-1)/2^N$ . The shortest duration subframe, corresponding to the least significant bit, is frame-time/ $(2^N-1)$ .

A digital display system includes a plurality of pixels arranged in an array of rows and columns. One conventional system includes 1024 rows of pixels, each having 1280 pixels arranged in columns. A row of 1280 registers is loaded with the display data. For a PWM system, shift registers are used to sequentially store the data for a row of pixels. Data can be fed into the shift registers serially or in parallel; for convenience, the serial case is considered. The time available for loading a row of data into the shift registers is  $\Lambda/(\# \text{ of rows})/(\# \text{ of columns})$ . Therefore, the required data bus bandwidth for the electronics supplying data to the shift registers is  $(\# \text{ of rows})(\# \text{ of columns})/\Lambda$ . This means that the bandwidth of the data bus doubles for every bit of grayscale that is added to a system. It is well understood that the cost of a system can increase significantly with increased bandwidth.

If the duration of the shortest subframe is  $\Lambda$ , then the duration available for turning on the pixel is  $\Lambda/(\#$  of rows of pixels), since rows are addressed sequentially. In addition, the operating frequency of a system that provides the control signals to such pixels must be (# of rows of pixels)/ $\Lambda$  (assuming the control timing for turning on the pixel is the same as for turning off the pixel). As the duration of the shortest subframe becomes smaller, the design of control circuitry with sufficient bandwidth becomes increasingly difficult.

It is well understood that the bandwidth cannot be reduced by simply lengthening the duration of all the subframes. Consider for example where a grayscale of 1/2 is desired. If the duration of the frame and appropriate subframe are sufficiently long, the displayed pixel(s) will appear to flicker rather than appear as an intermediate gray level. Thus, it is important that the display time for any of the subframes not be too long.

What is needed is a display system that provides grayscale using a weighted PWM scheme which does not flicker and without significantly increasing the bandwidth requirements of the associated control circuitry and data bus.

## Summary of the Invention

5

10

15

20

25

30

A display system uses a weighted PWM scheme to deliver control during a frame time for developing a plurality of grayscale levels in each of a plurality of pixels. Of all the weighted subframes, a predetermined number of the shortest subframes utilize a like subframe duration. However, to provide additional levels of grayscale, differing durations of 'on' time are utilized in these like subframes. Thus, all but one of these like-time subframes has a dead zone time during which the pixels are not activated. A separate control signal recognized as a clear circuit turns 'off' the illuminated pixels during the dead zone time.

In the preferred embodiment, the frame includes eight subframes. Each of the subframes is conditioned to activate the display for a unique duration. The first subframe turns its respective pixel 'on' for a predetermined length of time and each subsequent subframe for one-half the duration of its immediate predecessor. However, each of the last four subframes, subframes 5, 6, 7 and 8, have a same duration, one to the other. To maintain the condition that each successive subframe has one-half the duration of its immediate predecessor, the subframes 6, 7 and 8, each have a dead zone in which the pixels are never turned on. The dead zone in subframe 6 is 1/2 the subframe duration. The dead zone in subframe 7 is 3/4 the subframe duration and the dead zone in subframe 8 is 7/8 the subframe duration. A clear circuit is provided which provides the necessary counting capability to turn off the illuminated pixels at the appropriate times during the subframes 6, 7 and 8.

## Brief Description of the Drawings

5

10

15

20

25

30

Figure 1 shows a timing diagram for an unweighted PWM scheme in the prior art.

Figure 2 shows a timing diagram for a weighted PWM scheme in the prior art.

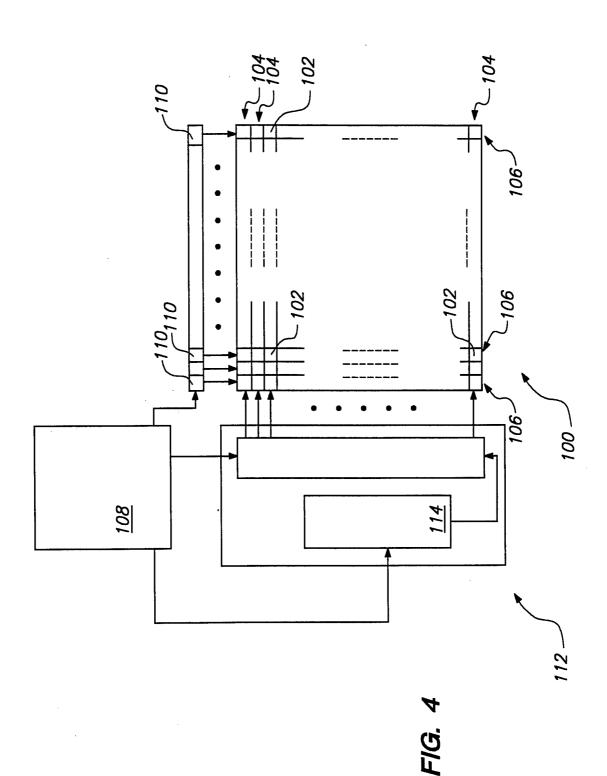

Figure 3 shows a timing diagram for a weighted PWM scheme according to the present invention.

Figure 4 shows a block diagram of system architecture for implementing the present invention.

## Detailed Description of the Preferred Embodiment

Figure 3 shows a timing diagram for the weighted PWM scheme according to the present invention. The invention is directed toward developing a grayscale display capability in a digital display. A single frame time is illustrated in Figure 3. In this preferred embodiment, there are eight subframes and thus eight bits of selectability for grayscale. This provides 256 unique gray levels from fully off to nearly fully on. As will be appreciated from the discussion below, because of certain features of this invention, a small portion of available light (about 6% in the preferred embodiment) will be lost. This is true even when all of the bits are 'on'.

The most significant bit is provided first according to the preferred embodiment. The subframe for the first bit, Bit 0, has a duration for a predetermined amount of time. A similar weighted PWM scheme according to the prior art would have a duration for controlling the pixel for 50% of the frame time for Bit 0. In the present invention, Bit 0 controls the pixel for slightly more than 47% of the frame time. Bit 1 controls the pixel for 1/2 the duration of Bit 0. Similarly, Bit 2 controls the pixel for 1/2 the duration of Bit 1, Bit 3 controls for 1/2 of Bit 2, Bit 4 controls for 1/2 of Bit 3, Bit 5 controls for 1/2 of Bit 4, Bit 6 controls for 1/2 of Bit 5, and Bit 7 controls for 1/2 of Bit 6.

According to the preferred embodiment, each of the bits falls within one of eight subframes. Bit 0 through Bit 4 each entirely fill their respective subframes. If two of these bits are utilized to achieve a particular grayscale, the 'off' signal at the end of the first such subframe is deactivated so that the pixel remains 'on'.

As shown in Figure 3, Bit 5 through Bit 7 each have the same subframe duration time as Bit 4. For Bit 5, the pixel receives a control signal to turn the pixel 'off' 1/2 the way through the subframe. For Bit 6, the pixel receives a control signal to turn the pixel

'off' 1/4 the way through the subframe. For Bit 7, the pixel receives a control signal to turn the pixel 'off' 1/8 the way through the subframe. The portion of each of the subframes for Bit 5 though Bit 7 is a dead zone during which time no pixel is 'on'. These dead zones do decrease the total amount of illumination available from each pixel by approximately 6%. However, because the time duration of bit 7 is maintained at the time duration of bit 4, the bandwidth of the control system need not operate at as high a frequency as would otherwise be necessary and does not need to be fed into the shift register as fast as would otherwise be necessary.

5

10

15

20

25

30

The following illustrates one example for achieving 8-bit grayscale with 5-bit timing. The technique can be generalized to N-bit grayscale timing with M-bit timing, where M<N. It is assumed that the display is digital and has 1024 rows with 1280 columns operating at a 75 Hz frame rate.

To achieve 8-bit grayscale, 8 subframes are required corresponding to bits 0 through 7. The timing corresponds to 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128 and 1/256 of a total frame-time as described in the prior art. In actuality according to the teachings of the present invention, the frame is divided into eight subframes which correspond to 1/2, 1/4, 1/8, 1/16, 1/32, 1/32, 1/32 and 1/32.

The three least significant bits, Bit 5 through Bit 7, are generated by subdividing the last three subframes into 1/2, 1/4 and 1/8 of the 1/32 subframes to yield 1/64, 1/128 and 1/256, respectively. This occurs by turning off a row of pixels after it has been on 1/2, 1/4 and 1/8 of the 1/32 subframes. It will be apparent that some of the intensity is lost even when all bits are on: approximately 6%.

The 1/32 subframes (Bit 4 through Bit 7) defines the speed required for addressing, the time it takes to write 1024 rows, since it corresponds to the shortest subframe. The time required in this example for the 1/32 subframe is

$$t(1/32 \text{ bit}) = (1/f)(32/34)(1/32)$$

For f=75 Hz,  $t=392~\mu s$ . The time allowed to write each row is then

$t_{ROW} = t/\rho$ ; where  $\rho =$  number of pixels per row.

For this example with 1024 pixels per row, the timing is 383 ns per pixel.

For all grayscale bits, the time to address 1024 rows is 392  $\mu s$

Figure 4 shows a block diagram of a display system according to the present invention. An array 100 of a plurality of discreet pixels is arranged in a plurality of rows 104 and columns 106. Each row contains a predetermined number of pixels. One commercially available display includes 1024 rows, each having 1280 pixels per row. Other sizes of displays are also available.

A control circuit 108 is coupled to load display data into a plurality of registers 110. There are the same number of registers 110 as pixels 102 in a row 104. In the preferred embodiment, the data is entered into a first register and shifted through the row of registers like a standard shift register. It is well known that other means for loading the registers can be used. The control circuit 108 is also coupled to a row select circuit 112. One function of the row select circuit is to condition the array 100 to transfer the display data from the registers 110 into a predetermined row 104 of pixels 102.

To display a particular grayscale image in a row, the data for Bit 0 for each pixel 102 in the selected row 104 is loaded into the registers 110. Once the data is loaded, the control circuit 108 generates a control signal to initiate the transfer of the data to the row 104 of pixels 102 that is selected by the row select circuit 112. The control circuit 108 also provides the row select circuit 112 information regarding which bit of the grayscale is being transmitted to the pixels 102 for display.

The row select circuit 112 incorporates a timer circuit 114 which counts down the desired duration of bit being displayed. Once the full duration has been displayed, the timer circuit 114 generates an off signal which is coupled to the appropriate row 104. Control logic is incorporated in the timer circuit 114 which inhibits the off signal in the event two consecutive bits are required for the generation of a grayscale. Of course, the inhibit function does not operate for those bits that include a dead zone.

The present invention has been described relative to a preferred embodiment.

Improvements or modifications that become apparent to persons of ordinary skill in the art only after reading this disclosure are deemed within the spirit and scope of the application.

5

10

15

20

#### CLAIMS

## What is claimed is:

4

5

6

7

8

7

| 1 | 1.      | A method of providing data bits to a display comprising an array of pixels arranged |

|---|---------|-------------------------------------------------------------------------------------|

| 2 | in a pl | urality of rows each having a like number of pixels for forming a grayscale image,  |

| 3 | the me  | ethod comprising the steps of:                                                      |

- a. providing a plurality of weighted data bits to each pixel within a frame-time;

- b. subdividing the frame-time into a plurality of subframes such that one of the weighted data bits is provided to each pixel during one of the subframes and further wherein each of the pixels is controlled by an appropriate one of the weighted data bits during an entire duration of a first portion of the subframes and during a partial duration of a second portion of the subframes.

- 2. A method of providing data bits to a display comprising an array of pixels arranged in a plurality of rows each having a like number of pixels for forming a grayscale image, the method comprising the steps of:

- a. in a frame time providing a set of weighted data bits to each pixel, one bit of the set during each of a plurality of subframes wherein the set provides sufficient information to develop a predetermined grayscale; and

- b. in at least a least significant bit, extending a duration of the subframe for a dead period.

- 1 3. The method according to claim 2 further comprising the step of compressing the frame time to equal an original frame duration.

- 1 4. An apparatus for forming a weighted grayscale display, comprising:

- a. an array of pixels arranged in a plurality of rows each having a like number of

pixels;

- b. means for providing a plurality of weighted data bits to each pixel within a frametime;

c. means for dividing the frame-time into a set of subframes which collectively

develop a predetermined grayscale according to the weighted data bits such that

one of the weighted data bits is provided to each pixel during one of the subframes

and further wherein each of the pixels is controlled by an appropriate one of the

weighted data bits during an entire duration of a first portion of the subframes and

during a partial duration of a second portion of the subframes.

- 5. The apparatus according to claim 4 wherein the second portion of the subframes each includes an active period and a dead period, the apparatus further including means for disabling the pixel during the dead period.

- 1 6. The apparatus according to claim 5 wherein eight subframes comprise the set of subframes.

- The apparatus according to claim 6 wherein the first portion of subframes includes 1 7. five subframes wherein a second subframe has half the duration of a first subframe, a third 2 subframe has half the duration of the second subframe, a fourth subframe has half the 3 duration of the third subframe and a fifth subframe has half the duration of a fourth 4 subframe and wherein the second portion of subframes includes three subframes wherein a 5 sixth subframe, a seventh subframe and an eighth subframe each have a duration equal to 6 7 the fifth subframe and wherein the sixth subframe has an active period half the duration of the fifth subframe, the seventh subframe has an active period one-quarter the duration of 8 the fifth subframe, the eighth subframe has an active period one-eighth the duration of the 9 10 fifth subframe.

- 1 8. The apparatus according to claim 7 wherein the frame-time is equal to an original frame duration.

- 1 9. An apparatus for forming a weighted grayscale display, comprising:

- a. an array of pixels arranged in a plurality of rows each having a like number of

pixels;

- b. a row select circuit for selecting a predetermined one of the rows;

5 c. a plurality of registers coupled to provide a weighted data bit to each pixel into the 6 predetermined one of the rows; 7 d. a control circuit coupled to the registers and including:

8

9

10

11

12

13

14 15

16

17

18

19

20

21

22

1

2

3

1

1 2

3

4

5

- (1) means for loading each of the registers with an appropriate weighted data bit;

- (2) means for providing a control signal for transferring the weighted data bits to the predetermined one of the rows;

- (3) means for transferring a predetermined number of the weighted data bits for developing a predetermined grayscale within a frame-time to each pixel; and

- (4) means for dividing the frame-time into a plurality of subframes such that one of the predetermined number of weighted data bits is provided to each pixel during one of the subframes and further wherein each of the pixels is controlled by an appropriate one of the weighted data bits during an entire duration of a first portion of the subframes and during a partial duration of a second portion of the subframes; and

- e. wherein the second portion of the subframes each includes an active period and a dead period, the apparatus further including means for disabling the pixel during the dead period.

- The apparatus according to claim 9 wherein the second portion of the subframes 10. each includes an active period and a dead period, the apparatus further including means for disabling the pixel during the dead period.

- 11. The apparatus according to claim 10 wherein eight subframes comprise the set of 2 subframes.

- 12. The apparatus according to claim 11 wherein the first portion of subframes includes five subframes wherein a second subframe has half the duration of a first subframe, a third subframe has half the duration of the second subframe, a fourth subframe has half the duration of the third subframe and a fifth subframe has half the duration of a fourth subframe and wherein the second portion of subframes includes three subframes wherein a sixth subframe, a seventh subframe and an eighth subframe each have a duration equal to

the fifth subframe and wherein the sixth subframe has an active period half the duration of 7

- the fifth subframe, the seventh subframe has an active period one-quarter the duration of 8

- the fifth subframe, the eighth subframe has an active period one-eighth the duration of the 9

- 10 fifth subframe.

4

5

6 7

8

- A method of providing a grayscale display having a plurality of pixels each having 1 13. an "on" state and an "off" state comprising the steps of: . 2 3

- a. providing a frame time each having a plurality of subframes times;

- b. providing a plurality of data bits, one per pixel, to control the state of each pixel during each subframe time; and

- c. controlling a time duration of each data bit to provide weighting of the data bits such that each pixel is controlled for the time duration by the data bit during a first portion of the subframes and during a partial duration of a second portion of the subframes.

#### INTERNATIONAL SEARCH REPORT

Inter anal Application No PC1/US 96/09253

A. CLASSIFICATION OF SUBJECT MATTER IPC 6 G09G3/20

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

$\begin{array}{ll} \mbox{Minimum documentation searched} & \mbox{(classification system followed by classification symbols)} \\ \mbox{IPC 6} & \mbox{G09G} \end{array}$

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

Further documents are listed in the continuation of box C.

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                         | Relevant to claim No. |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Х          | WO,A,92 12506 (RANKBRIMAR LTD.) 23 July<br>1992                                                                                                                            | 1-5,9,<br>10,13       |

| Υ          | see Abstract see page 2, line 10 - page 5, line 4; figures 5-9 see page 5, line 20 - line 25 see page 18, line 16 - page 22, line 2 see page 23, line 1 - page 26, line 15 | 6,11                  |

| X          | EP,A,0 654 777 (TEXAS INSTRUMENTS INC.) 24 May 1995 see Abstract see column 2, line 54 - column 4, line 29; figures 1,6 see column 5, line 42 - line 54                    | 1-5,13                |

|            | -/                                                                                                                                                                         |                       |

| · <del></del>                                                                                                                                      |                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:  *A* document defining the general state of the art which is not considered to be of particular relevance | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |

| "E" earlier document but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or          | "X" document of particular relevance; the claimed invention<br>cannot be considered novel or cannot be considered to<br>involve an inventive step when the document is taken alone                  |

| which is cited to establish the publication date of another citation or other special reason (as specified)                                        | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the                                                                              |

| "O" document referring to an oral disclosure, use, exhibition or<br>other means                                                                    | document is combined with one or more other such docu-<br>ments, such combination being obvious to a person skilled                                                                                 |

| "P" document published prior to the international filing date but<br>later than the priority date claimed                                          | in the art.  *&* document member of the same patent family                                                                                                                                          |

| Date of the actual completion of the international search                                                                                          | Date of mailing of the international search report                                                                                                                                                  |

| 19 September 1996                                                                                                                                  | 0 1. 10. 96                                                                                                                                                                                         |

| Name and mailing address of the ISA                                                                                                                | Authorized officer                                                                                                                                                                                  |

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+ 31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+ 31-70) 340-3016  | Corsi, F                                                                                                                                                                                            |

Form PCT/ISA/218 (second sheet) (July 1992)

1

Patent family members are listed in annex.

# INTERNATIONAL SEARCH REPORT

Inter onal Application No

PCT/US 96/09253

| (Continua | tion) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                   | PCT/US 96/09253       |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| tegory °  | Citation of document, with indication, where appropriate, of the relevant passages                                                          |                       |  |

|           |                                                                                                                                             | Relevant to claim No. |  |

|           | EP,A,O 488 326 (NEC CO.) 3 June 1992 see Abstract see page 3, line 42 - page 4, line 13; figures 5-7                                        | 1-5,7                 |  |

| 1         | PATENT ABSTRACTS OF JAPAN vol. 14, no. 525 (P-1132), 19 November 1990 & JP,A,02 219092 (FUJITSU GENERAL LTD.), 31 August 1990, see abstract | 6,11                  |  |

|           |                                                                                                                                             |                       |  |

|           |                                                                                                                                             |                       |  |

|           | ·                                                                                                                                           |                       |  |

|           |                                                                                                                                             |                       |  |

|           | į                                                                                                                                           |                       |  |

## INTERNATIONAL SEARCH REPORT

iformation on patent family members

Inter nal Application No

PCT/US 96/09253

| Patent document cited in search report | Publication<br>date | Patent family<br>member(s)       |                                            | Publication date                             |  |

|----------------------------------------|---------------------|----------------------------------|--------------------------------------------|----------------------------------------------|--|

| WO-A-9212506                           | 23-07-92            | GB-A-                            | 2251511                                    | 08-07-92                                     |  |

| EP-A-654777                            | 24-05-95            | CA-A-                            | 2136257                                    | 24-05-95                                     |  |

| EP-A-488326                            | 03-06-92            | JP-A-<br>DE-D-<br>DE-T-<br>US-A- | 4195087<br>69117675<br>69117675<br>5317334 | 15-07-92<br>11-04-96<br>08-08-96<br>31-05-94 |  |

Form PCT/ISA/210 (patent family annex) (July 1992)