**Patent Number:**

#### US005845150A

5,845,150

## United States Patent [19]

# Henion [45] Date of Patent: Dec. 1, 1998

[11]

|                               | AND REI<br>OUTPUT<br>SOURCE                  | LURALITY OF POWER SOURCES DUNDANCY CIRCUIT WHICH S SERVICE REQUEST SIGNAL IN A DOES NOT MEET ERMINED OUTPUT LEVEL |  |  |  |

|-------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| [75]                          | Inventor:                                    | Scott Gregory Henion, Stone Mountain, Ga.                                                                         |  |  |  |

| [73]                          | Assignee:                                    | Lanier Worldwide, Inc., Atlanta, Ga.                                                                              |  |  |  |

| [21]                          | Appl. No.                                    | 769,463                                                                                                           |  |  |  |

| [22]                          | Filed:                                       | Dec. 20, 1996                                                                                                     |  |  |  |

| Related U.S. Application Data |                                              |                                                                                                                   |  |  |  |

| [62]                          | Division of Ser. No. 324,903, Oct. 18, 1994. |                                                                                                                   |  |  |  |

MODULAR DIGITAL DICTATION SYSTEM

| [62] | Division of Ser. No. 324,90 | 3, Oct. 18, 1994.            |

|------|-----------------------------|------------------------------|

| [51] | Int. Cl. <sup>6</sup>       | <b>G06F 1/28</b> ; G06F 1/30 |

|      |                             | G06F 11/16; G06F 15/177      |

## [56] References Cited

## U.S. PATENT DOCUMENTS

| 3,648,248 | 3/1972  | Goldsberry 341/139    |

|-----------|---------|-----------------------|

| 3,936,805 | 2/1976  | Bringol et al 395/873 |

| 3,965,484 | 6/1976  | Matz et al 360/61     |

| 4,075,502 | 2/1978  | Walley, Jr 307/64     |

| 4,303,998 | 12/1981 | Plunkett, Jr          |

| 4,371,752 | 2/1983  | Matthews et al 379/89 |

| 4,430,726 | 2/1984  | Kasday 704/235        |

| 4,468,751 | 8/1984  | Plunkett, Jr          |

|           |         |                       |

| 4,651,020 | 3/1987  | Kenny et al 307/43        |

|-----------|---------|---------------------------|

| 4,817,127 | 3/1989  | Chamberlin et al 379/67   |

| 4,860,188 | 8/1989  | Bailey et al              |

| 4,999,787 | 3/1991  | McNally et al 395/283     |

| 5,146,439 | 9/1992  | Jachmann et al            |

| 5,163,085 | 11/1992 | Sweet et al 379/89        |

| 5,265,075 | 11/1993 | Bergeron et al 369/25     |

| 5,404,455 | 4/1995  | Daly et al 395/824        |

| 5,430,365 | 7/1995  | Taylor et al              |

| 5,440,223 | 8/1995  | Hayasaki                  |

| 5,457,782 | 10/1995 | Daly et al 704/200        |

| 5,488,531 | 1/1996  | Aldridge et al 361/18     |

| 5,513,062 | 4/1996  | Paul et al 361/90         |

| 5,519,808 | 5/1996  | Benton, Jr. et al 704/270 |

Primary Examiner—Thomas C. Lee Assistant Examiner—Ki S. Kim Attorney, Agent, or Firm—Jones & Askew

#### [57] ABSTRACT

A modular digital dictation system that can be easily modified to service a variable number of dictation stations and transcription stations. The modular digital dictation station comprises a central station for receiving digitized dictation signals from a network of dictation stations, storing the voice portion of the digitized dictation signals as digitized dictation segments, and routing the digitized dictation segments to a network of transcription stations. The central station includes a plurality of line interface and signal processing cards. The number of line interface and signal processing cards connected to the central station determines how many dictation stations and transcription stations the modular digital dictation station can service. The line interface cards may be removed from or connected to the central station during operations. A redundant power supply is connected to the central station to provide continuous power to the central station. The power supply includes multiple energy sources, each energy source capable of powering the central station.

## 3 Claims, 13 Drawing Sheets

FIG.3

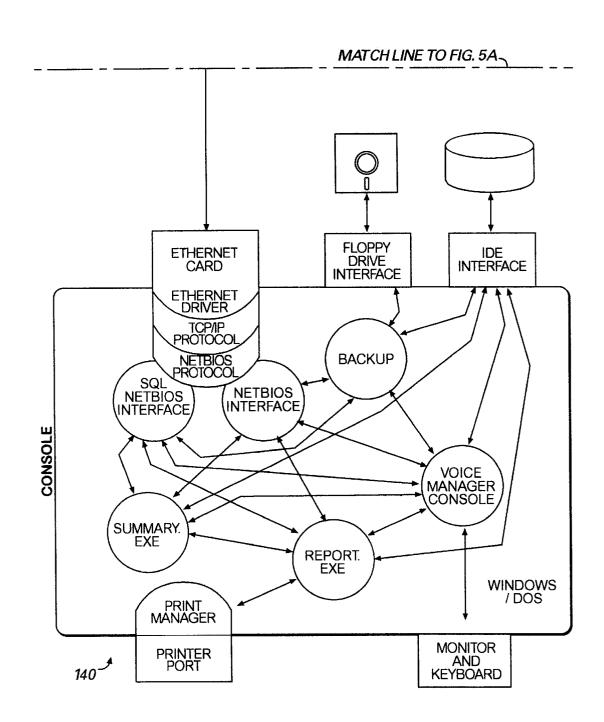

FIG.5B

**FIG.11**

**FIG.12**

MODULAR DIGITAL DICTATION SYSTEM WITH PLURALITY OF POWER SOURCES AND REDUNDANCY CIRCUIT WHICH OUTPUTS SERVICE REQUEST SIGNAL IN A SOURCE DOES NOT MEET PREDETERMINED OUTPUT LEVEL

This is a divisional application under 37 C.F.R. §1.60, of pending prior application Ser. No. 08/324,903, entitled "Modular Digital Dictation System," filed Oct. 18, 1994, on 10 behalf of inventors Alexander D. Raji, James G. Allen and Scott G. Henion, and assigned to Lanier Worldwide, Inc.

#### TECHNICAL FIELD

The present invention relates to digital dictation systems, and more particularly is a modular digital dictation system wherein component cards can be added or removed from a central station to service variable numbers of dictation and transcription stations.

#### BACKGROUND OF THE INVENTION

Centralized dictation systems have been features of many American businesses and medical facilities for many years. Central dictation systems evolved in response to two basic needs of users of dictation and transcription equipment. The first need was for a system that could efficiently handle high volume, in terms of individual pieces of dictation, dictation/ transcription loads where individual dictators may use the system only a relatively small portion of their working day. In other words, environments in which there were a large number of users, each of which required dictation equipment for a relatively small fraction of their working time is one that is ideally suited for a centralized system. This precludes the need for fixed locations for individual dictation recording units or the need to move from office to office to find an available dictation machine. Hospitals and other medical facilities are typical of such installations for central dictation equipment. A number of dictation stations which is substantially larger than the number of dictation recording media that are available can be connected and handled the traffic under all but the most unusual circumstances.

The transcription side corollary of this is that centralized dictation systems are ideally suited for circumstances in which there are pooled transcriptionists. Centralized systems provide relatively easy ways of switching output for transcription among various transcriptionists in a pool where there is little concern with matching a particular transcriptionist to the work of a particular dictator. Again, medical facilities, as well as insurance and military offices, are installations that typically employ such pools of transcriptionists.

A second need which central dictation systems meet, irrespective of whether there is transcription pooling or association of particular transcriptionists with particular 55 dictators, is the avoidance of handling of individual recording media. Even businesses whose personnel are arranged so that same transcriptionists typically transcribe the work of particular originators adopt central dictation systems so that individual recording media will not have to be physically transferred with files under circumstances in which they can be misplaced, damaged, or transcribed out of order. The retention of a fixed recording media at the central dictation site precludes physical transfer of recording media for transcription.

In typical tape based central dictation systems of the prior art, a dictation transcription machine having a long endless 2

loop of tape was provided. The tape was drawn by a recording station during dictation and deposited into a bin at which it awaited transcription via reproduction by a playback head on a transcription side, after which the tape was erased and deposited in a free tape bin. After this, it would return again to the dictation side for subsequent re-recording. Typical selection of a central recording unit by a dictator was accomplished through a key station selector mechanism or a multi-position switch, with audible ready tones being provided when an available central recording unit was selected.

On the transcribe side, selector switches or plug and cable patch panels were used to connect the outputs from transcription transducers from particular central recorders to transcription stations located at individual transcriptionists' desks

In the 1970s and 1980s central dictation systems using individual cassettes as the recording media were developed. These systems were, in some sense, a hybrid of the features 20 of previous fixed media central dictation units. Multiple cassette changers particularly designed for use in central dictation systems were provided. These could be selectively seized by various dictate stations in a manner essentially identical to that by which endless loop recorders were selected and seized. However, distribution of work for transcriptionists was accomplished by physical distribution of individual cassette recording media to transcriptionists having local transcription devices at their work stations. This allowed for more rapid selection of particular pieces of dictation for transcription from a given central dictation recorder at the expense of requiring physical handling of individual recording media, i.e., the cassettes. Additionally automated logging and assignment systems were developed to help control and supervise central systems employing cassette recorders.

Still more recently, digital central dictation systems have been developed. These are systems in which the recording media generally comprises a magnetic disk for storing digitized samples of recorded speech signals. On the dicta-40 tion side analog to digital converters are employed to digitize the speech. Also, since speech tends to be redundant and of limited bandwidth, various compression schemes are used to reduce the amount of disk space required to store the digitized dictation. Maintaining a doubly linked list file 45 structure for the individual pieces of dictation allows the transcription operation to move forward and backward through the samples during retrieval and reproduction (via digital to analog converters) on the transcription side. Additionally, the use of doubly linked lists allows material to be inserted within previously dictated material so that it is reproduced seemlessly when heard by the transcriber. Likewise, deletions of portions may be made without requiring the transcriber to wait for the passage of blank tape or long periods of silence.

While sophisticated central digital dictation systems represent the state of the art, there are some drawbacks to the basic architecture that has been employed in the prior art. In particular, most such systems have been designed so that a single media, at least from the perspective of system logic, is employed for recording of the digitized dictation. The number of channels that such a system can handle is normally fixed so that as the needs of a particular user of the equipment increase, a particular system may be out grown requiring discarding or resale of the system and the purchase of the next larger unit that will handle the user's increased requirements. The distance, in both system capacity and price, between adjacent units in any given suppliers line has

-,- --,--

tended to be relatively large, often increasing the number of available channels in the available storage space by a factor of two. The pricing of such size contiguous units tends to increase at approximately the same rate.

3

This has led to a situation in which the available technology has created a commercial environment in which a user that has out grown its dictation system is faced with trying to use a system with the inadequate capacity or purchase a significant excess of capacity. Common experience teaches that this leads to situations in which user  $^{10}$ dissatisfaction occurs during the period in which the user will struggle to get by with the existing system, and additional dissatisfaction at the practical requirement of purchasing an excess of capacity, much of which may not be needed for a considerable period of time, in order to alleviate that situation. It should be noted that prior art endless loop tape systems generally could be expanded gracefully in small increments by the addition of one or more central recording units. The only limitation normally encountered was exceeding the switching capacity of selection control equipment  $\ ^{20}$ interconnecting the various central recorders with the dictate and transcribe stations. In the design of current state of the art digital dictation systems, system capacity has tended to increase in large increments due to the employment of central controllers for multiplexing and buffering the various  $^{25}$ dictate and transcribe stations. System capacity, with respect to the number of channels that may be simultaneously employed, has been dictated by the speed and processing power of the central controller as well as available memory for buffering and storage media capacity, i.e., disk space. Thus, the basic architecture of prior art digital central dictation systems has precluded a system that may be gracefully expanded or contracted in relatively small increments. In order to accommodate a wide variety of system capacities within a product line, a manufacturer would need 35 to design, manufacture, and stock an excessive number of specific system designs leading to increased costs.

Thus, there is a need in the art for providing a central digital dictation system that may be gracefully expanded, in terms of channel and storage capacity, in relatively small units, without requiring substantial replacement of main components. The present invention is designed to address this need.

## SUMMARY OF THE INVENTION

The present invention was conceived to provide a modular, centralized digital dictation system that can easily be modified to service a variable number of dictation and transcription stations. Generally described, the present invention comprises a central station for receiving digitized dictation signals from a network of dictation stations, storing the voice portion of the digitized dictation signals as digitized dictation segments, and routing the digitized dictation segments to a network of transcription stations. The capacity of the central station to service dictation and transcription stations may easily be expanded or reduced, as desired by the user.

More specifically described, the central station includes an AT computer connected to a large memory storage area that stores all the files of voice data generated at the dictation stations. In the preferred embodiment, the AT computer is embodied in a plug-in card on a mainframe rack and many software modules to track and monitor files containing the digitized dictation.

The central station further includes line interface cards that serve as input/output gateways between the AT card in

the central station and the dictation and transcription stations. The central station also includes a plurality of signal processing cards. The signal processing cards process the digitized dictation signals, such as by compressing digitized voice for storage and expanding the digitized voice for transmission to the transcription stations. The signal processing cards also perform the handshaking necessary to pass digitized dictation signals between the line interface cards and the AT card. The line interface cards and signal processing cards are sometimes jointly referred to herein as component cards.

Both the line interface cards and the signal processing cards plug into a plurality of slots on a multiplexed bus in the central station. Alternatively, the line interface cards and signal processing cards can be remotely mounted in a rack and connected by cabling to connectors on the multiplexed bus in the central station.

A variable number of line interface and signal processing cards can operate in the central station. The addition of line interface and signal processing cards to the central station increases the number of digitized dictation stations and transcription stations that may be serviced. Therefore, a user can upgrade the capacity of a digital dictation system by simply installing more line interface cards and signal processing cards in the central station, rather than having to buy a new, more powerful system.

Furthermore, line interface cards can be installed while the modular digital dictation system of the present invention is operating. The line interface cards include extended power and ground pins that power up the circuitry on the card before the pins carrying signals into the line interface card are connected. The line interface card is thus powered up and ready to receive signals when the signals arrive at the line interface card. Therefore, the system need not be shut down to be upgraded with more line interface cards. Similarly, the system need not be shut down to replace faulty line interface cards.

Described in more detail, the digital dictation system comprises a network of dictation stations and transcription stations all connected to a central station. Digitized dictation segments are transmitted between the central station and each of the dictation stations and transcription stations. Line interface cards in the central station control the transfer of digitized dictation signals between the central station and the dictation and transcription stations. The line interface cards are the first stage of signal processing in the central station.

Inside the central station are two distinct data busses. The first bus connects each line interface card to a signal processing card for enabling the transfer of digitized dictation signals between the line processing cards and the signal processing cards. The first bus includes a time division multiplexed bus capable of carrying up to 128 voice and data channel pairs. Additionally, the first bus includes a communications control bus that facilitates control of the line interface and signal processing cards by the AT card.

In the preferred embodiment of the present invention, each individual line interface card and signal processing card can process up to eight channels of voice and data at one time. Each dictation station or transcription station utilizes one voice and data pair channel when operating. Therefore, one line interface card and one signal processing card can service up to eight dictation or transcription stations. The multiplexed bus (first bus) can carry up to 128 pairs of voice and data channels. The multiplexed bus can therefore service up to 128 dictation or transcription stations at one time.

For the central station to service more than eight voice/ data channel pairs at one time, more than one line interface card and signal processing card must be provided. Because the multiplexed bus can carry up to 128 channels of voice and data, up to sixteen of the line interface cards and sixteen signal processing cards may be connected to the central station in the preferred embodiment of the present invention.

The number of line interface cards and signal processing cards in the system can be increased or decreased to appropriately service the number of digital dictation stations and transcription stations in a network. By connecting additional line interface cards and signal processing cards to the multiplexed bus in the central station, the system can be upgraded to service an increased number of stations. Therefore, according to one aspect of the present invention, 15 a modular digital dictation system is provided.

The second bus connects the signal processing cards to a storage, processing and retrieval device that is controlled by the AT card. The second bus is a standard personal computer control and data communication bus as set forth in the ISA Bus standards promulgated by International Business Machines Corp. for series AT personal computers.

Digitized dictation segments transmitted from a dictation station through a signal processing card are stored in a large hard disk drive in the central station. Software opens a file related to an identification number for each dictation session, wherein the identification number is obtained from the dictation station. The software stores the dictation in eight (8) kilobyte segments. Each file is labeled with headers and certain identifiers and stored in the hard disk drive. The software thus forms the digitized dictation segments into files and tracks the processing of the files, including the opening, closing and deletion of the files.

The files containing digitized dictation consist of a sixteen (16) kilobyte header and eight (8) kilobyte blocks of digitized dictation. The header consists of record file information and an index that is used to determine the order in which the blocks of digitized dictation are played back. The number of eight (8) kilobyte blocks varies depending on the length of the dictation session.

The software that tracks and monitors the files includes a record manager. The record manager software includes a table that contains the job number, record identification number, and status for each file stored in the hard disk drive. 45 number. For example, in the preferred embodiment of the The table is built at system boot-up by reading the job record information of all files stored on the hard disk drive, and the table is maintained as files are created and completed.

When the dictation session first begins, a file manager software routine creates a file in the hard disk drive that will 50 contain the digitized dictation, and tables in the records manager are updated to reflect the existence of the new file. The signals arriving at the AT card include digitized information signals, such as a header, and a digitized dictation segment containing digitized voice. Typically, the header 55 identifies the dictator by a user identification number, and the header may also contain information regarding the subject and time of the dictation. For example, a doctor may type in his or her user identification number followed by a patient identification number.

The records manager may also be loaded with information corresponding to the patient, using the patient identification number. The information is looked up in memory tables accessible to the AT card. For example, one table might contain the patient history, including allergies, for each patient. The information obtained from the table(s) is added to the header of the corresponding file. When the file is

ultimately transcribed, the information added to the header is added to the originally dictated information. Thus, a more complete file is created.

After the header information is obtained, the digitized dictation segments arrive at the AT card. The digitized dictation segments are placed in the file that is labeled by the header containing the doctor and the patient identification number.

According to another aspect of the preferred embodiment of the present invention, a method for quickly tracking and retrieving a stored file based on a file identification number, such as a job or user identification number, is provided. The centralized station may create thousands of files to store the digitized dictation segments generated by the dictation stations. These files consume large blocks of memory to store the digitized voice. The records manager must be able to rapidly find a particular file via, for example, a user identification number so that the file can be retrieved for review by the dictator or a transcriptionist. Therefore, a fast search program for storing and rapidly retrieving files containing digitized voice is implemented herein.

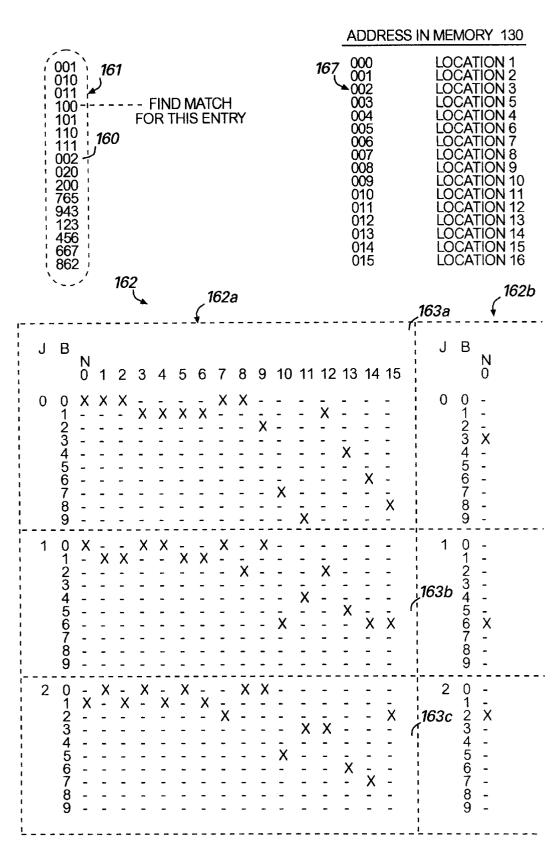

In the preferred embodiment of the fast search program, each file opened on the hard disk drive is assigned an identification number. Although the below discussion concerns a job identification number, it applies to a table constructed for fast access to user identification numbers or other identifiers for a large number of files. Each identification number is comprised of several digits. The identification number for the files are organized into a table forming a four-dimensional array of identification numbers.

Each digit from every identification number is loaded into a sub-array. For example, a first sub-array would contain the first digit of each identification number for a set number of jobs. The second sub-array would contain the second digit from each identification number for the set number of jobs, and so on. Thus, the first dimension in the array of identification numbers is the number of characters in the job number which equals the number of sub-arrays. For example, if the job identification number includes three characters, the number of sub-arrays is the first dimension and is equal to three.

The second dimension in the array of identification numbers is the possible values for a digit in the identification present invention, the identification number may be any number from 0-9 (because each identification number is encoded in ASCII), and so the second dimension would be ten. If each identification number was encoded in hexadecimal format, the second dimension would be sixteen.

Identification numbers are sequentially loaded in columns in the array as files are created. As is explained in detail below, the number of columns corresponds to the third dimension. The third dimension is limited by the width of the number of jobs that can be reviewed at one time. In the preferred embodiment, the third dimension is set to sixteen, but those skilled in the art will recognize that the third dimension could be up to thirty-two (32) bits wide in a computer that has a thirty-two bit mask. Typically, the third dimension corresponds to the number of bits used by the operating system in data operations.

The first, second and third dimensions are thus structured as follows. The first dimension is individual sub-arrays for each digit position in the job identification numbers. The second dimension is rows, with each row being one of the possible values of a digit in the identification number. The third dimension is the columns in the array, with each

column containing an identification number. The second and third dimensions form the traditional "X" and "Y" coordinates to locate a position within each sub-array.

The above three dimensions form a complete listing of a set number of identification numbers, with the number of identification numbers contained in the array being limited by the third dimension. Another three dimensional array, identical to the three dimensional array set forth above, must be created to hold more jobs than the third dimension. The fourth dimension of the array thus identifies a particular three dimensional array among a plurality of three dimensional arrays.

For example, referring to FIG. 11 the four dimensional array 162 of identification numbers is set forth. The first dimension includes the sub-arrays 163a, b and c, which are demarcated by the leftmost column containing "0", "1" and "2". The second dimension is marked by the numbers "0-9" preceding the rows of numbers within each sub-array **163***a*–*c*. The third dimension is marked by the numbers "0-15" above the columns in the arrays 162a. The fourth dimension is another array 162b containing more job identification numbers. Additional arrays 162c-n (not shown) are created each time more than sixteen new jobs are created. Each time a file containing digitized voice is created, the identification number for the file is stored in the array. The first digit, second digit and third digit of the identification number are stored in the first, second and third sub-arrays, respectively. For example, referring to FIG. 11, the identification number "001" is stored in column one and each digit is marked by an "x". A second identification number is stored in column two, and so on.

When a file is to be retrieved, an identification number for the file is known, but the location of the file in memory is not. To find a file in memory, a sixteen-bit mask is created. The mask is sixteen bits set to "1". The mask is sequentially ANDed with the row of digits in the first, second and third sub-arrays that correspond to the first, second and third digits desired in the identification number. By consecutively ANDing a mask with the appropriate rows of digits in the sub-arrays that correspond to the digits in the identification number, all the identification numbers that might correspond to the desired identification number are located in the sub-arrays. Each array 162a—n is searched for the file. Thus, the desired file is located in the array 162.

As each file is created a job record number for the file is sequentially added to a table of files received. Therefore, the table of files received is simply a sequential list of the addresses of the files in memory. Each identification number is also loaded in the array concurrently with the creation of the file. Therefore, the identification number for a file in the array and the address for the file in the table of file received are related by their position in the respective arrays. The identification number in the array is cross-referenced to the job record for the file in the table of files received. The job record is used to find the file in memory.

In other words, the table of files received is built in conjunction with the creation of the array of identification numbers. The position of the identification number in the array is used to calculate the location of the corresponding file in the table of files received, which stores the address of the file in memory.

The location of identification numbers in the array can be matched to job records in the table before the files are created. Alternatively, the system may calculate the address 65 in the host array for each identification number in real-time. The position in the array of the digits in the selected

8

identification number is used in a formula that calculates the corresponding position in the table of files received.

Those skilled in the art will recognize that the above method presents a significant increase in the speed of finding files. The mask is sixteen bits wide, meaning that sixteen files are simultaneously checked by the ANDing step to determine if they include the identification digit of interest. Furthermore, files not containing the digits of interest are not even searched. Therefore, the fast search program provides a rapid method for finding files while limiting the memory space consumed.

Another preferred feature of the fast search program is "wild carding". In situations where a file is needed but the user does not know all the digits in the identifier number, a wild card search may be performed. In this search, all the files containing the known identification number digits are located. These files are all retrieved for the user's perusal. Thus, the unknown digits in the identification number are inconsequential to the search and are "wild cards".

Another computer is also connected to the AT computer. The second computer is called a console in the present invention. The console computer can access information concerning the files containing digitized dictation, including the headers. The user can thus access and monitor the files via the console. The user can sort the above referenced files according to any of the above-referenced identification numbers.

Accordingly, it is an object of the present invention to provide a module digital dictation system in which the number of dictation stations and transcription stations being serviced may be varied.

It is a further object of this invention to provide a modular digital dictation system in which the number of dictation stations and transcription stations being serviced can be increased or decreased while the digital dictation system operates.

It is a further object of this invention to provide a modular digital dictation system that stores files containing digitized dictation signals in a standardized format.

It is a further object of the present invention to provide a fast search program for quickly retrieving a file from among a plurality of stored files.

It is a further object of this invention to provide a fast search program wherein less than all digits in the identifier may be used to retrieve a number of files, thereby allowing a user to access a file without all the file identifier information.

Other objects, features, and advantages of the present invention will become apparent upon review of the following detailed description of embodiments of the invention, when taken in conjunction with the drawings and appended claims.

## BRIEF DESCRIPTION OF DRAWINGS

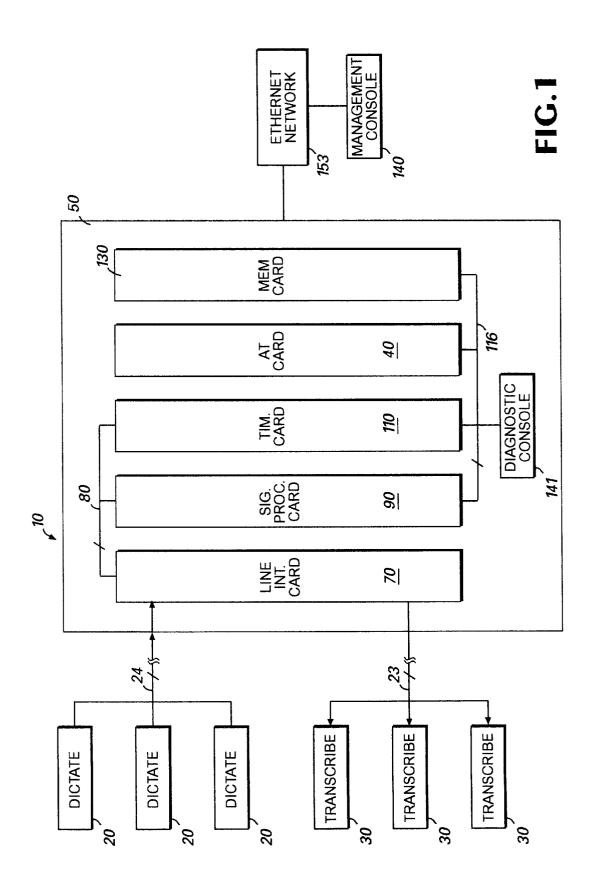

FIG. 1 is a block diagram of the preferred embodiment of the present invention.

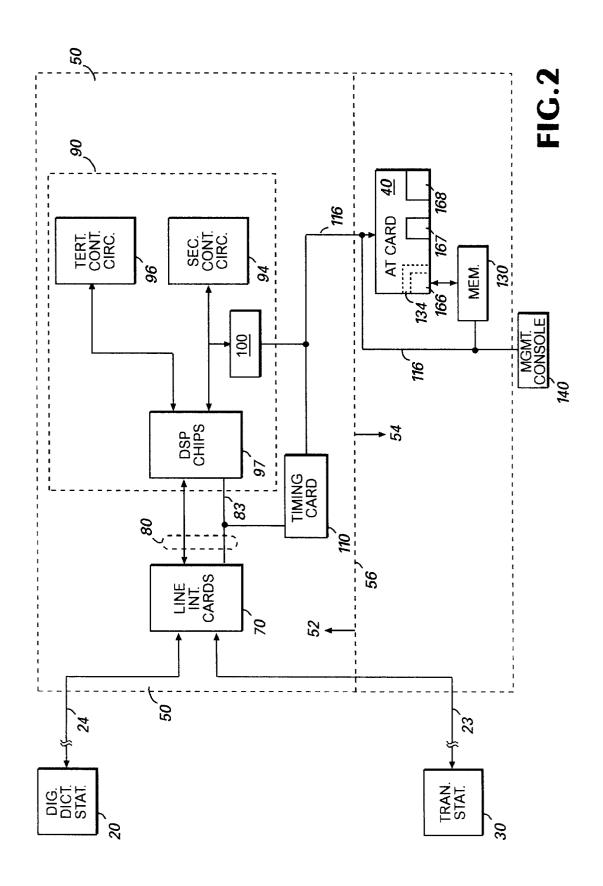

FIG. 2 is a block diagram showing the flow of digitized dictation signals in the present invention.

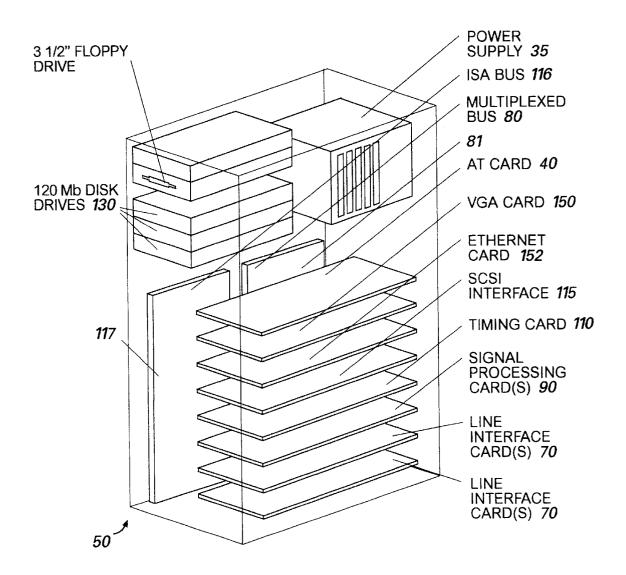

FIG. 3 is a front perspective view of the central station in the preferred embodiment of the present invention.

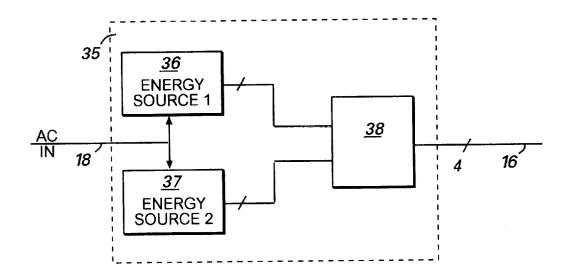

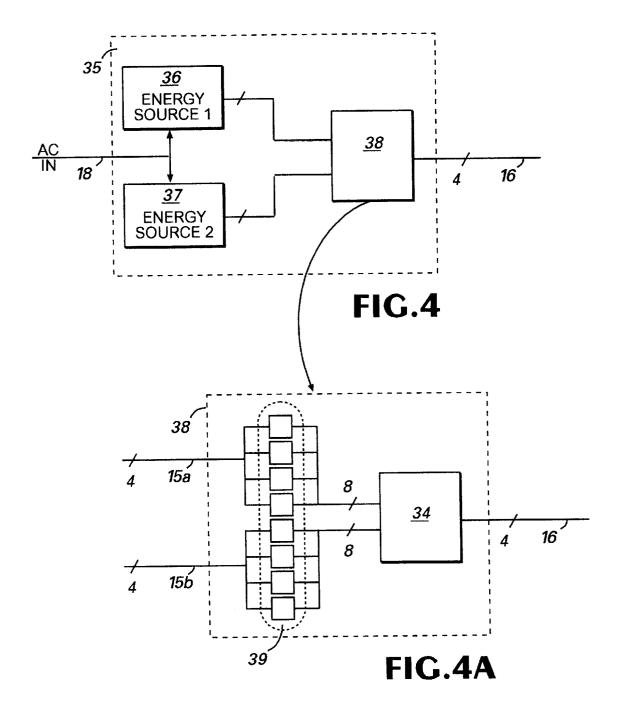

FIG. 4 is a block diagram of the power supply that provides power to the rest of the central station in the present invention

FIG. 4A shows a detailed block diagram of the power supply selector in the referred embodiment of the present invention.

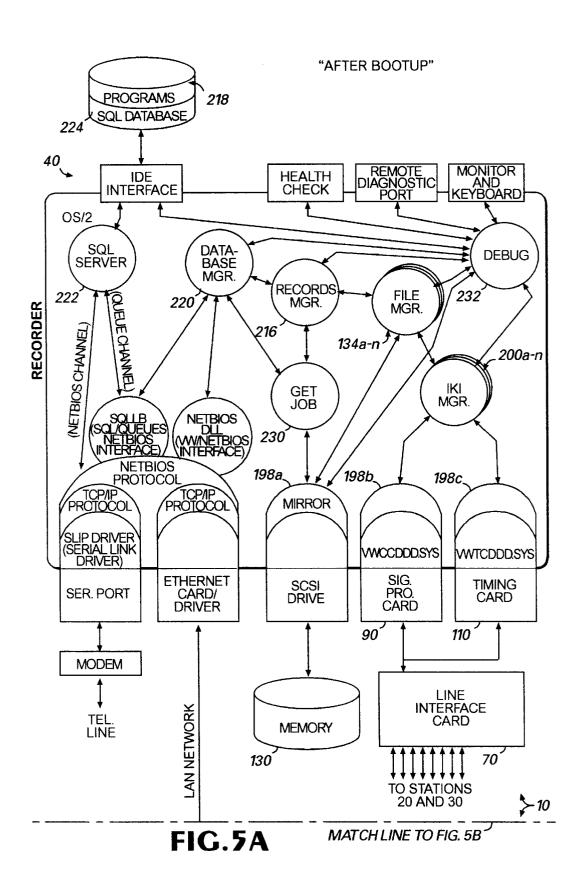

FIGS. 5A and 5B are block diagrams of the software and the communication paths among modules of the software within the preferred embodiment of the present invention.

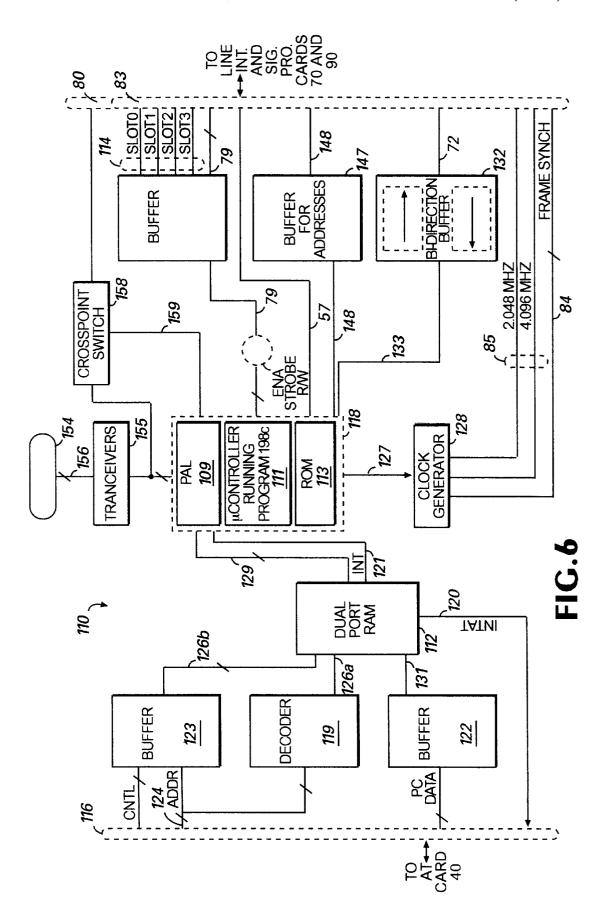

FIG. 6 is a block diagram of the timing card in the preferred embodiment of the present invention.

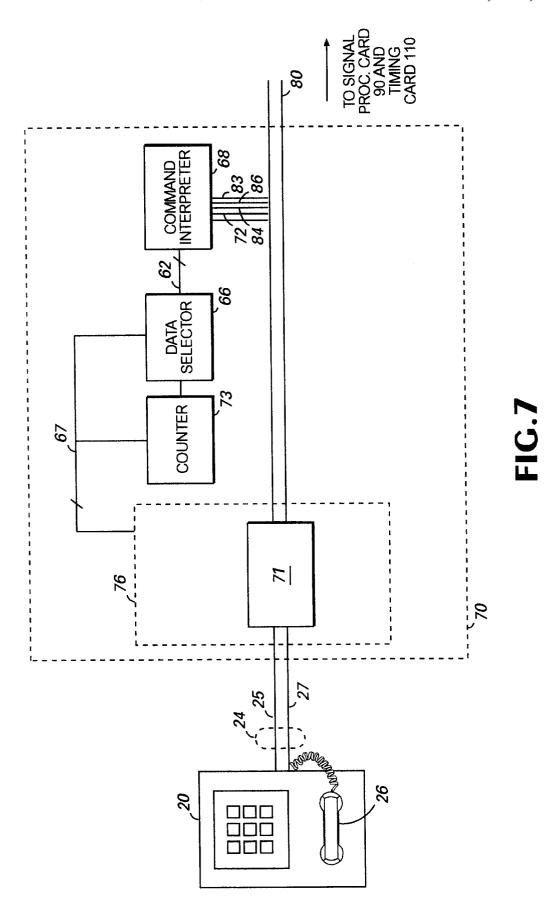

FIG. 7 is a block diagram of communication between a digital dictation station and a line interface card in the central station.

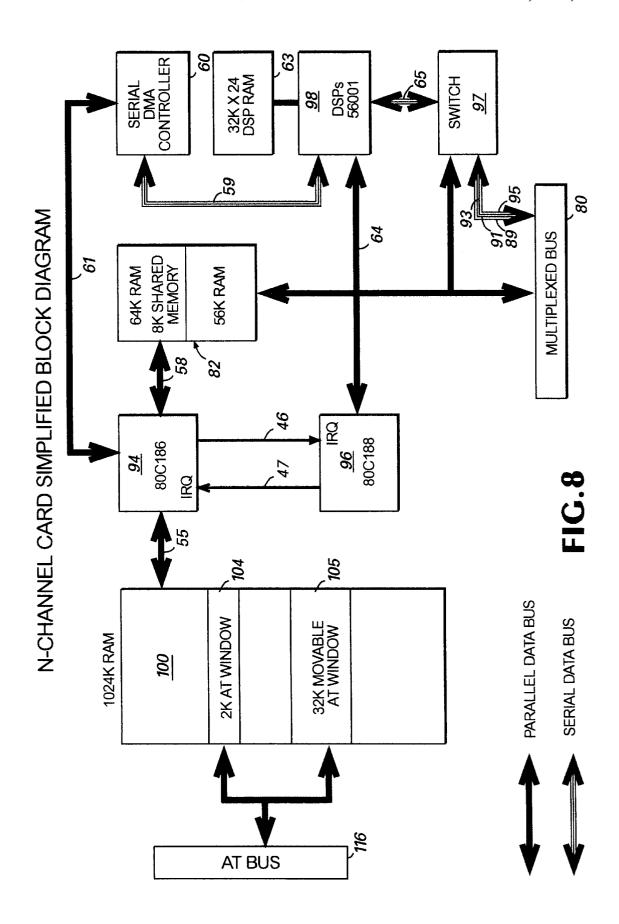

FIG. 8 is a block diagram of the signal processing cards in the preferred embodiment of the present invention.

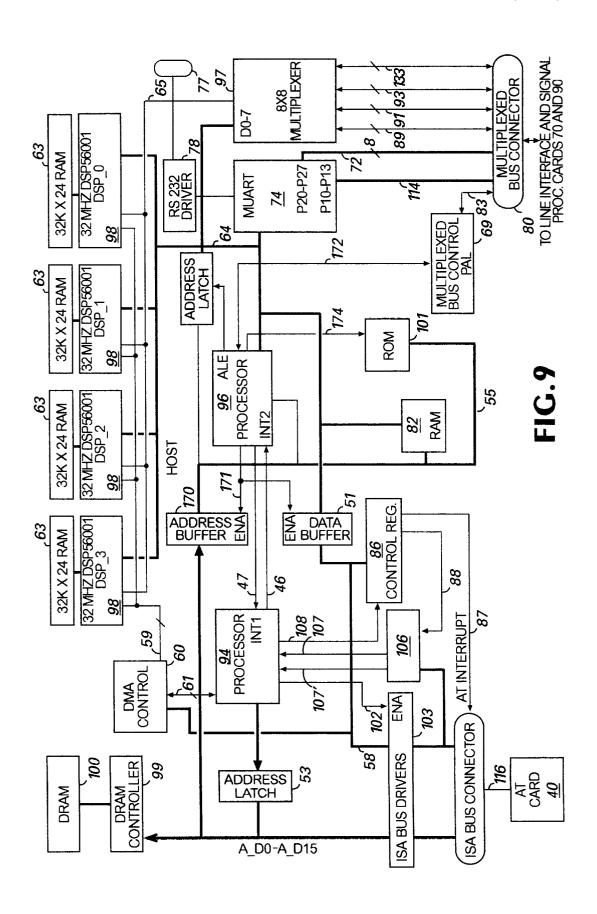

FIG. 9 is a detailed diagram of a signal processing card in the preferred embodiment of the present invention.

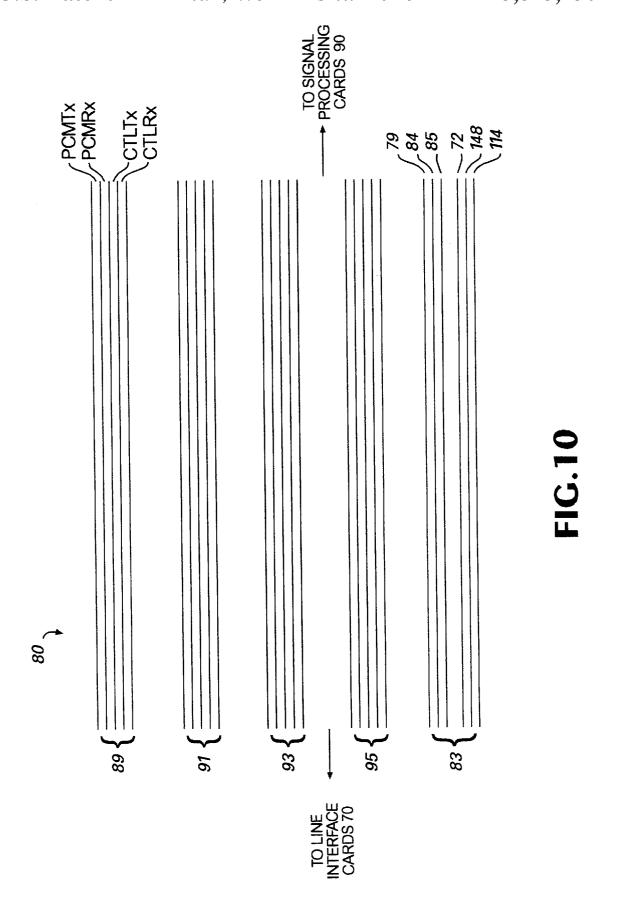

FIG. 10 is a diagram showing some signal lines on the multiplexed bus in the referred embodiment of the present 15 invention.

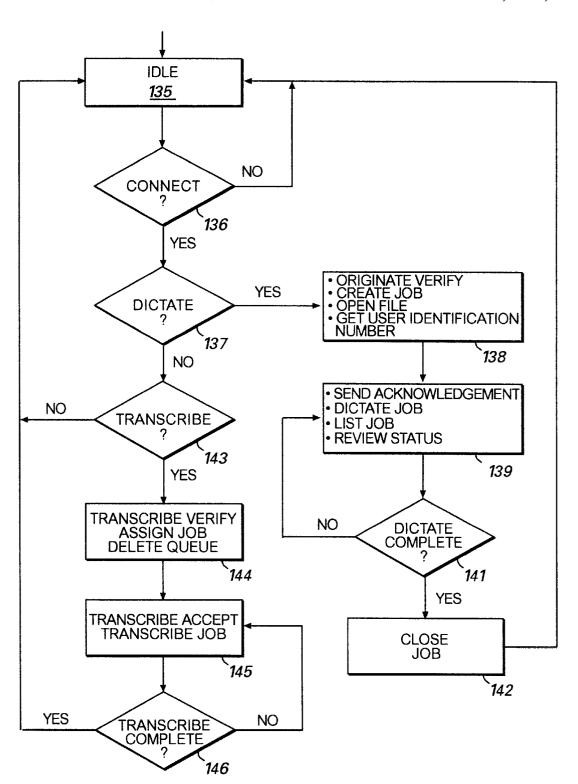

FIG. 11 is a diagram of an array of identification numbers in the fast search program in the preferred embodiment of the present invention.

FIG. 12 is a high level flow diagram of the file manager 20 program in the AT card of the present invention.

#### DETAILED DESCRIPTION OF DRAWINGS

This detailed description is divided under three subheadings. The three sub-headings are: I. SYSTEM OVERVIEW, II. CONTROL STRUCTURE, and III. FLOW OF DIGITIZED DICTATION SIGNALS. The SYSTEM OVERVIEW describes the structure and function of the digital dictation system in general terms. The text under the sub-heading entitled CONTROL STRUCTURE sets forth 30 the software and hardware operational controls of the modular digital dictation system. Finally, under the sub-heading FLOW OF DIGITIZED DICTATION SIGNALS, the flow of dictation signals through the hardware and software of the modular digital dictation system is detailed.

## I. SYSTEM OVERVIEW

Turning now to the drawings, in which like numerals represent like components throughout the several figures, FIG. 1 is a block diagram of the preferred embodiment of the present invention, a modular digital dictation system 10. The modular digital dictation system 10 comprises a plurality of digital dictation stations 20 and a plurality of transcription stations 30 connected to a central record and controller station 50.

10 of the present invention performs the following tasks. Analog audio voice is modulated into digitized dictation signals at dictation stations 20. The digitized dictation signals are passed to central station 50. The digitized dictation signals are organized into files by software running on 50 the AT card 40. The digitized dictation signals are processed and stored in files in memory 130. As desired, the files containing the digitized dictation signals are retrieved and passed to transcription stations by the central station 50. At the transcription stations 30, the digitized dictation signals 55 are formed into analog audio signals and transcribed.

The preferred modular digital dictation system 10 is representative of the type used in a central dictation system having transcribe stations 30 and dictation stations 20 connected to one or more centrally located stations or recorders via extensive conduit wiring 24 distributed throughout the physical plant of a business. During dictation operations, a dictation station 20 generates a sequence of digitized dictation signals, including a dictation segment containing the dictated work and a digitized identification signal containing 65 information corresponding to the dictation segment. The digitized identification signal typically includes descriptive

10

information, also referred to as header data, directed to the origination and the subject of the dictated work. In response to the digitized dictation signals carried by wiring 24, the central record and controller station 50 operates upon the dictation signals to store the dictation segment and header pending transcription at one of transcription stations 30. The transcription stations 30 are connected to the central station via wiring 23.

Referring now to FIG. 2, a block diagram showing the general flow of digitized dictation signals in the central station 50 is disclosed. Implementation of the preferred embodiment of the modular digital dictation system 10 includes many component cards, identified as line interface cards 70 and signal processing cards 90, but for simplicity only one of each is shown in FIG. 2.

As is shown in FIG. 2, the central station 50 can be logically divided into two sections, indicated by reference numerals 52 and 54. First, a timing card 110, line interface cards 70 and signal processing cards 90 may be considered as one distinct section 52 of the central station 50, shown above the dotted line 56. The components in section 52 are primarily hardware. Second, the AT card 40, memory 130 and management console 140 may be logically considered as a second section 54, shown below the dotted line 56. The primary functions performed in section 54 are software controlled. The distinction between the two sections, 52 and 54, is also based on the control structure in each section and the data and control busses utilized in each section. The distinction is simply a tool to help understand the operation of the modular digital dictation system 10.

Digitized dictation signals are communicated between line interface cards 70 and signal processing cards 90 via time division multiplexed bus 80 (FIG. 2). As will be more fully explained below, the multiplexed bus 80 carries many channels of digitized voice and data as well as control 35 signals. The signal processing cards 90 process and temporarily store the digitized dictation signals received on multiplexed bus 80 in dynamic random access memory (DRAM) 100.

After being processed in section 52, the digitized dictation 40 signals are transferred from the DRAM 100 in section 52 to the AT card 40 in section 54 via an ISA bus 116. The ISA bus 116 is a standard bus used in International Business Machines Corp. computers. Those skilled in the art will recognize that other busses, including but not limited to Referring to FIG. 1, the modular digital dictation system 45 standard personal computer busses, may be utilized. For example, an Extended ISA bus, known as an EISA bus, may be used to construct embodiments of the present invention.

> The AT card 40 is the motherboard for an IBM Corp. compatible computer, familiar to those skilled in the art. Other controllers can be used in place of AT card 40, as will be familiar to those skilled in the art.

> The operation of the software in the AT card 40 is described in detail below. Very generally described, the digitized dictation signals transferred to the AT card 40, are organized into files by a program running on the AT card 40 and stored in memory 130. Operation of the software on the AT card 40 is detailed below.

> When needed for transcription, or if a dictator wishes to review recorded dictation, the file containing digitized dictation segments is retrieved from memory 130 by AT card 40 (FIG. 1). For example, the file containing the dictation segments to be transcribed is passed along the same path that was used to bring it to the AT card 40. Specifically, the dictation segment is transferred from memory 130 to a signal processing card 90 via ISA bus 116, and then to a line interface card 70 on multiplexed bus 80 on the way to a transcription station 30.

In the preferred embodiment, dictation segments transmitted from the central station 50 are passed through another CODEC (not shown) at the transcription stations **30** (FIG. 2). The CODECs convert the digitized dictation segments from  $\mu$ -law pulse code modulation (PCM) format into audio signals. The transcriptionist can then transcribe the voice. The communication path between the transcription stations 30 and the central station 50 on wiring 23 is analogous to the communication along wiring 24 between the digital dictation station 20 and the central station 50.

One of the important features of the present invention is the modularity of the system. The provision of two distinct busses, 80 and 116, in the central station 50 allows for the modularity of the digital dictation system 10 (FIG. 2). The multiplexed bus 80 can carry up to 128 voice and data channel pairs in the preferred embodiment of the present invention. To vary the number of dictation stations 20 or transcription stations 30 that can be serviced by the modular dictation system 10, the number of line interface cards 70 and signal processing cards 90 that are connected to multi- 20 plexed bus 80 is varied. The addition of line interface cards 70 and signal processing cards 90 increases the number of dictation stations 20 and transcription stations 30 that are serviced by the central station 50. This modularity allows the preferred modular digital dictation system 10 to be expanded as desired by the user up to a maximum of 128 voice and data channels in increments of a few channels at a time, eight in the preferred embodiment.

The use of the standard AT bus 116 to receive and store files allows the files to be readily communicated to other 30 standard computers and networks. For example, a manager of the central station 50 might want to move files containing digitized dictation signals from a company's San Diego office to their Atlanta office, because there are more people in Atlanta available to do transcription. The manager could 35 access files from memory 130 via an ETHERNET network 153 (FIG. 1), and transfer the files to Atlanta via a modem or a wide area networking system (not shown). The interface between AT card 40 and other computers and/or networks for transferring files to and from memory 130 is well-known 40 to those skilled in the art. Thus, use of the AT ISA bus 116 allows for standardized treatment and communication of files that contain digitized dictation signals.

Turning now to FIG. 3, a front perspective view of the the present invention, the multiplexed bus 80 is formed on backplane 81 of the central station 50. An additional backplane 117, in parallel with backplane 81, carries the ISA bus 116. The functions of and electrical connections for the multiplexed and ISA busses 80 and 116, respectively, are 50 described in detail below.

Mounted onto the backplane 81 and backplane 117 are line interface cards 70, signal processing cards 90, a timing card 110 and the AT card 40. Additionally, a standard VGA card 150, for controlling a monitor in diagnostic console 141 55 (FIG. 1), and an ISA Ethernet card 152 are mounted in the central station 50, the functions of these cards being known to those skilled in the art. A management console 140 communicates with the system as an Ethernet node.

The VGA card 150, Ethernet card 152, timing card 110, 60 SCSI interface 115 and the AT card 40 are plugged into specific slots on backplane 117 in central station 50, and all these cards communicate to each other via the ISA bus 116 (FIG. 3). The line interface cards 70 and the signal processstation 50. The line interface cards 70 and the signal processing cards 90 communicate with each other via mul12

tiplexed bus 80. The signal processing cards 90 are also connected to the ISA bus 116.

Those skilled in the art will recognize that the line interface cards 70 and signal processing cards 90 may be connected to multiplexed bus 80 in a variety of manners. If enough 64 pin DIN connector slots are available on the backplane 81 in the central station 50, all the line interface cards 70 and signal processing cards 90 may be physically plugged into slots as shown in FIG. 2. However, if the 10 network has a large number of digital dictation stations 20 and transcription stations 30, many line interface cards 70 and signal processing cards 90 will be required. In this case, the number of slots on backplane 81 may be exceeded by the required number of line interface cards 70 and signal processing cards 90. Therefore, a ribbon cable or other connector familiar to those skilled in the art may be used to connect some of the line interface cards 70 and/or signal processing cards 90 to the multiplexed bus 80.

The line interface cards 70 can be connected to a running system ("hot plugged"). The line interface cards 70 have extended power and ground pins (not shown). Therefore, when these cards are plugged into a slot of a running system, the circuitry on the card is powered-up before receiving command and data signals. The electronic circuits on the line interface cards 70 are therefore relatively stable before signals begin arriving. This feature of the line interface cards 70 helps prevent lock-ups of the system due to randomly generated noise when a card is first connected to the present system. Those skilled in the art will recognize that being able to plug the line interface cards 70 into a running system allows upgrades and maintenance without turning off all or part of the central station 50.

It is imperative that embodiments of the present invention be operational as close to one-hundred percent of the time as possible. To that end, a redundant power supply is provided for the central station. Referring now to FIG. 4, a block diagram of the power supply 35 for the central station 50 in the present invention is set forth. It is important that the power supplied to the central station 50 never be turned off, especially in medical environments. Therefore, the power supply 35 is a redundant, uninterruptable power supply. The power supply 35 in the present invention is comprised of two redundant energy sources, 36 and 37. The energy sources, 36 and 37, are standard power supplies for computer systems, central station 50 is shown. In the preferred embodiment of 45 receiving AC power input on line 18 and outputting DC voltages on lines 16. Each energy source 36 and 37 has a full set of fuses and filters so that it can independently power the central station 50. The operation of the individual energy sources 36 and 37 is known to those skilled in the art. A redundancy circuit 38 ensures that one of the energy sources, 36 or 37, is always receiving AC power input and powering the central station 50.

> FIG. 4A is a block diagram of the power supply redundancy circuit 38 in the preferred embodiment of the present invention. The two energy sources, 36 and 37, each output the full complement of DC power required by the central station **50** on lines **15**a or b: +12V, -12V, +5V and -5V. Each output power signal is tested by testers 39, which are comparators or other voltage and current sensors that determine if the output from energy sources 36 and 37 on lines 15a and b are at the appropriate levels. Devices such as testers 39 are familiar to those skilled in the art.

The tested power signal plus a control signal are output from each tester 39 and enter a comparator 34. If any of the ing cards 90 are plugged into the remaining slots in central 65 output signals of the energy sources 36 or 37 are inadequate, as indicated by the control signals, the outputs from that energy source 36 or 37 are not used and a service request

issues in the form of a lit LED (not shown). If all the outputs from both energy sources 36 and 37 are adequate, the comparator 34 selects which energy source, 36 or 37, powers the central station 50 via power on lines 16. The comparator 34 may be a timer that switches between energy sources 36 and 37 or it may use one energy source exclusively until the power output from that energy source fails as determined by testers 39. Alternatively, the energy sources 36 and 37 can power share via a network of ORed diodes (not shown). In this embodiment, the energy source outputs are ORed and 10 between the hardware device (or a controller for the hardthe greater DC signal level is used. The redundant power supplies help prevent interruption of the system. II. CONTROL STRUCTURE

Briefly referring back to FIG. 2, files are opened in the AT card 40 to hold digitized dictation pending transcription. The 15 software in the AT card 40 controls the receipt of data from dictation stations 20, storage of the digitized dictation, and transmission of data to transcription stations 30. The lowerlevel processing of digitized dictation signals into or from the central station 50 is controlled by the timing card 110, line interface cards 70 and signal processing cards 90(section 52 in FIG. 2). Because the operation of the AT card 40 provides a higher level view of the operation of the central station 50, the control of data in the AT card 40 is set forth first. Then, operation of the components in section 52 is set forth. The detailed flow of data in the AT card 40, line interface cards 70, and signal processing cards 90 is set forth below in section III concerning the flow of data.

#### A) The AT Card

The AT card 40 is a controller for storing and retrieving 30 files containing digitized dictation. Using the descriptions herein, those skilled in the art will recognize that controllers other than the AT card 40 can perform the below described functions. The AT card 40: (1) allows the user to start-up the agement console 140, (2) receives and sends digitized dictation signals to and from the signal processing cards 90, (3) stores and retrieves files containing dictation segments in memory 130, (4) generates a header and inserts it with each digitized dictation segment in a file, and (5) communicates 40 with the signal processing cards 90, as set forth above.

In the preferred embodiment of the present invention, the AT card 40 (FIG. 1) is a controller or a personal computer, well known to those skilled in the art, that is dedicated to present invention. In the preferred embodiment, the AT card **40** is an IBM AT personal computer, specifically including a 80486 microprocessor running the OS/2 operating system. However, other microprocessors or operating systems well known to those skilled in the art may be used. The OS/2 operating system program is a multitasking system, broadly meaning that it can support many application programs running at the same time.

Referring now to FIGS. 5A & 5B, a block diagram of the software modules and interfaces used in the preferred AT card 40 within modular digital dictation system 10 is disclosed. As can be seen in FIGS. 5A & 5B the AT card 40 includes many software modules that interface with the hardware in modular digital dictation system 10, such as the line interface cards 70, signal processing cards 90, hard disk drive 218 and disk memory 130. The software modules are usually stored in hard disk drive 218. The many lines connecting the software modules represent direct transfer of data and commands between software modules.

The AT card 40 serves to accept data from digital dictation 65 stations 20 via the timing card 110, line interface cards 70 and signal processing cards 90. The detailed operation of the

14 timing card 110, line interface cards 70 and signal processing cards 90 is set forth below.

As fully described below, data is provided to the AT card 40 at a fixed location on the AT bus 116 (FIG. 2). Program 198a is a Dynamic Link Library (DLL) programs that, together with device drivers 198b and 198c, serve to interface the memory 130, signal processing cards 90 and timing cards 110, respectively, with the AT card 40. The DLL programs 198a, b, and c drive the signals that are passed ware device such as the SCSI interface 115) and the AT card 40. Those skilled in the art are familiar with programs such as the DLL programs 198a, b and c.

Digitized dictation is passed to and from the AT card 40 via the signal processing card 90 and program 198b. As described in detail below, the executable program 198b is executed by two processors in the signal processing card 90. One Interprocess Kernal I/O (IKI) manager program **200***a*–*n* is operating for each dictation or transcription station, 20 and 30 respectively, that is communicating with the central station 50. Each IKI manager program 200a-n recognizes when data is available from the signal processing card 90, as will be discussed in greater detail below, and passes the data to one of the file managers 134a-n.

There is one file manager program 134a-n running for each active dictation and transcription station, 20 and 30 respectively. The file managers 134a-n manage the communication of information with the signal processing cards 90. Specifically, the file managers 134a-n interface with the "mirror" program 198a to instruct the mirror program 198a when to create, update, and close files, and controls the flow of data between the signal processing cards 90 and the files in memory 130.

The file managers 134a-n are connected to the records modular digital dictation system 10 (FIG. 1) via the man- 35 manager 216. The records manager 216 contains tables that include job numbers, record identification numbers, length of files and status information. Each table is built at boot-up by reading the job record information of any files in memory 130. The information about each file that is created, opened or closed is passed to the records manager 216 by the file managers 134*a*–*n*. The tables are described in detail below.

Although the operation of the software in the AT card 40 in storing and retrieving files and the console 140 are detailed in Section III below, a brief overview of these two running the modular digital dictation system 10 of the 45 aspects of the system are now provided. The central station 50 includes memory 130 that comprises at least 120 Mbytes of space for storing files of digitized dictation signals and 120 Mbytes of space for redundant storage of the digitized dictation signals. The memory 130 is preferably a hard disk drive familiar to those skilled in the art. The AT card 40 communicates with the memory 130 via the SCSI interface 115 (including a controller card and drivers) familiar to those skilled in the art, to store and retrieve the digitized dictation signals that originate at the dictation stations 20, as will be described in Section III, below.

The database manager 220, server 222 and the other software routines on the AT card 40 interface the AT card 40 with the management console 140 to provide a database 224 of information concerning the files in memory 130 to console 140. The database manager 220 is a communication interface between the server 222 and the database manager 220, as is familiar to those skilled in the art. The database 224 is checked against the job record information found in the header in each file opened in memory 130.

Any additions, changes or deletions in the database 224 are performed by the database manager 220. For example, when a dictation session begins, job record information is

passed from file manager 134*a*–*n* through the records manager 216 to the database manager 220. The database manager 220 then accesses the database 224 and creates a new record in the job records table. The console 140 accesses the database 224 for reading and updates via the database manager 220 and server 222.

The management console **140** is a personal computer, including a floppy drive, hard drive, printer port, driver and card, a monitor and keyboard that allow operator interface with the AT card **40** in the modular digital dictation system 10 **10** for control and monitoring purposes. For example, the management console **140** is programmed to access the database **224**, archive information, and display information. Those skilled in the art are familiar with applications created under the "WINDOWS" operating system for accessing 15 and display information in a database. Therefore, the software modules in the management console **140** are not described in detail herein. The implementation of management console **140** is known to those skilled in the art.

B) Control of Data Into and From the Central Station

The apparatus controlling data flow into and from the central station 50 roughly corresponds to Section 52 in FIG.

2. Section 52 is controlled by timing card 110. Specifically, the timing card 110 facilitates communications between the AT card 40 and the line interface and signal processing cards, 70 and 90, on the multiplexed bus 80, provides control signals to the line interface cards 70 and signal processing cards 90, and provides clock and synchronization signals to the time division multiplexed bus 80.

1) Timing Card

Turning to FIG. 6, a block diagram of the timing card 110 in the preferred embodiment of the present invention is shown. The controller 118 is comprised of a Programmable Array Logic (PAL) chip 109, a microcontroller 111 and ROM 113. In the preferred embodiment, the microcontroller 35 111 is the 68HC11E1 eight bit microcontroller manufactured by Motorola Corp. The program 198c (FIG. 5A) run by the microcontroller 111 is stored in a read only memory device 113, which is a flash ROM P28F010 produced by Intel, Inc., but can be many different sizes and makes of ROM or other 40 memory device familiar to those skilled in the art. The PAL chip 109 is product number PALC16L8 manufactured by Cypress Semiconductor

Referring to FIGS. **5A**, **5B** and **6**, when the timing card **110** is first powered up, the microcontroller **111** begins 45 executing the program **198**c stored in ROM **113**. The program enables the microcontroller **111** to assume control over RAM **112** in a manner familiar to those skilled in the art. Once the timing card **110** is powered-up, it awaits a start-up message from the AT card **40** in RAM **112**.

Continuing with FIG. 6, all messages sent between the AT card 40 and the timing card 110 pass through the dual-port RAM 112, which may be written or read by either the AT card 40 or the microcontroller 111. The AT card 40 reads or writes RAM 112 via ISA bus 116.

The address that the RAM 112, and thus the timing card 110, occupies on the ISA bus 116 is preconfigured by switches (not shown) on the timing card 110, in a manner familiar to those skilled in the art. The dual port RAM 112 is 1K byte in the preferred embodiment, although it may be larger or smaller if desired. The timing card 110 occupies up to a 2 k byte area between 0C0000 and 0FF800 (in the hexadecimal numbering system) on the ISA bus 116. Address decoder 119 monitors the upper bits of the address on lines 124 to determine when the timing card 110 is being addressed by the AT card 40. The decoder output on line 126a is set to indicate when the timing card 110 is addressed.

The remaining control and address signals pass through buffer 123 to RAM 112 via bus 126b and on to controller 118 via bus 129.

16

Continuing with FIG. 6, an interrupt signal on line 121 generated by the contents of particular locations in dual-port 112 informs the microcontroller 111 that a message has been written by the AT card 40 to RAM 112 in the timing card 110. Messages pass from the ISA bus 116 through a buffer 122 onto bus 131 into RAM 112. Likewise, an interrupt signal on line 120 generated by the microcontroller 111 signals AT card 40 that the timing card 110 has written a message to the RAM 112 via bus 129. The AT card 40 reads messages from RAM 112 when the interrupt signal on line 120 is set. Messages from the microcontroller 111 pass through RAM 112 to buffer 122 via bus 131. Contention for the RAM 112 between the microcontroller 111 and the AT card 40 is controlled by microcontroller 111.

At start-up of the modular digital dictation system 10 (FIG. 1), the AT card 40 places an interrupt signal on line 121 and requests a list of cards that are in the slots on the multiplexed bus 80 by placing a message in dual port RAM 112. In response, the timing card 110 polls all the slots available for cards connected to the multiplexed bus 80 and reports back to the AT card 40 via RAM 112. An address decoder (not shown) on the backplane 81 for multiplexed bus 80 decodes the slot address 114 from the timing card 110 and provides the slot enable to each individual line interface card 70 and signal processing card 90 connected to bus 80 (FIGS. 2 and 3). The AT card 40 will utilize all this information to initialize the line interface cards 70 and the signal processing cards 90 for communications, as is set forth below.

Returning to FIG. 6, the timing card 110 outputs slot signals 0–3 on lines 114 of the communications bus 83. This is a 4-bit address driven by the microcontroller 111 that allows each card on the multiplexed bus 80 to identify the slot in which it resides. Typically, at start-up, reset, or when a line interface card 70 or signal processing card 90 is inserted into a running system, the card will identify its slot by reading the slot address on lines 114 during an access by the timing card 110 via the enable signal (ENA) on bus 79. Once the card has determined its address from the timing card 110 via lines 114, it can be uniquely addressed by the timing card 110 and accept commands from the timing card 110.

The timing card 110 uses a communications bus 83 to control and address each line interface card 70 and signal processing card 90. The communications bus 83 is considered herein to be a subcomponent of the multiplexed bus 80, and is formed on backplane 81 (FIG. 3).

Continuing with FIG. 6, the timing card 110 uses the communications bus 83 to determine what type of cards are connected to the multiplexed bus 80. As set forth above, each slot on the multiplexed bus 80 has a unique address, that address accesses a memory address in ROM on the card that rests in the slot. The timing card 110 accesses the first address in the ROM on each card connected to the multiplexed bus 80. The accessed ROM is the ROM in command interpreter 68 (FIG. 7) on line interface cards 70 and the ROM 101 on signal processing cards 90 (FIG. 9). As shown in the timing card 110 in FIG. 6, the microcontroller 111 and PAL 109 generate the address for accessing each card, and pass the addresses on lines 148 to buffer 147. The address lines 148 enter the cards on the multiplexed bus 80 as part of communications bus 83. The ROMs on each card are preprogrammed with a number at the first address in ROM indicating the type of card in the slot. For example, the first

address in ROM would be "10" if a signal processing card 90 was in the slot, and the first address would be "20" if a line interface card 70 was in the slot. The timing card 110 reports this information back to the AT card 40 via RAM 112.

Handshaking between the timing card and the line interface and signal processing cards, 70 and 90, occurs in a protocol known to those skilled in the art as "interlocked handshaking." Referring to FIG. 6, the communications bus 83 includes four handshaking/control signals on lines 79 from the timing card 110. The control signals on lines 79 are generated by the PAL 109 and the microcontroller 111 and are used for communications between the timing card 110 and the line interface and signal processing cards, 70 and 90. The four control signals that regulate message transfer are: /ENA, /STROBE, and R/W on bus 79 and /ACK on line 57. The addressed line interface card 70 or signal processing card 90 responds to the /ENA, /STROBE and R/W signals with an /ACK signal on line 57. Messages on data bus 72 are read by the addressed card before it sends the /ACK response on line 57. The data buffer 132 is a bidirectional buffer for messages passed between the timing card 110 and the line interface and signal processing cards, 70 and 90, respectively, on data bus 72.

The AT card 40 sends several other messages to the timing 25 card 110, including card enable and disable controls. Likewise, the timing card 110 sends messages to the AT card 40 when it detects errors emanating from a card, when a request for service of a card occurs, or when a new line interface card 70 is plugged into the central station 50. All 30 these messages are passed throughRAM 112.

2) Control of the Line Interface Cards

Referring now to FIGS. 6 and 7, a discussion of control of a line interface card 70 by the timing card 110 is set forth. Control signals and messages from the timing card 110 to the 35 line interface cards 70 are sent via the communications bus 83 that forms part of multiplexed bus 80 (FIG. 7).

Each line interface card 70 includes a command interpreter 68. The command interpreter 68 includes an address decoder (not shown), a latch (not shown) and a ROM data buffer (not shown). When the timing card 110 properly addresses a line interface card 70, control data enters the latch. Outgoing data on lines 72, read from the ROM buffer in command interpreter 68, identify the line interface card 70 for the timing card 110, as was discussed above.

The command interpreter **68** also includes a programmable array logic (PAL) chip that evaluates the address lines, the read/write (R/W) lines, the STROBE line, and the enable (ENA) line on command bus **83** to determine whether an access to the line interface card **70** is a write or a read. The 50 command interpreter **68** also generates the ACKNOWL-EDGE (ACK) signal that is placed on command bus **83**. Circuits that perform the above functions described in conjunction with the command interpreter **68** are familiar to those skilled in the art.

At system start-up, after reset of the central station 50 or after being plugged into a running system, each line interface card 70 is initialized by the timing card 110. The timing card 110 writes the number of the beginning time slot for each line interface card 70 on lines 72 and into the latch in the command interpreter 68. The number of the beginning time slot is sent from the command interpreter 68 to the data selector 66 over line 62.

The data selector 66 and counter 73 in each line interface card 70 are used to multiplex the digitized dictation signals received from the dictation stations 20 onto multiplexed bus 80. The data selector 66 and counter 73 also serve to

demultiplex digitized dictation signals from the multiplexed bus 80 to be sent to transcription stations 30. Each counter 73 is preloaded with a 5-bit number provided by timing card 110 via communications bus data lines 72. Each counter 73 is synchronized with the frame synchronization signal on line 84 and counts using one of the clocks from lines 85. The counter 73 outputs a block enable signal on lines 67 to enable the group 76 of transceivers 71 to receive and output data. The number preloaded into the counter 73 determines upon which of the time slots on multiplexed bus 80 the transceivers 71 in each line interface card 70 will transmit or receive, and the block enable signal enables the transceivers 71 at the appropriate time.

The different counters 73 on the line interface cards 70 are preloaded with different numbers. Each block of transceivers 76 is active for a preselected number of time slots, as determined by its block enable signal on lines 67 emanating from its counter 73. The system sequentially activates the blocks of transceivers on the line interface cards 70. Each block of transceivers 76 on each line interface card 70 always occupies the same time slots for which it is activated by its counter 73. Therefore, if some or all of the transceivers 71 in a block of transceiver 76 are not transmitting or receiving digitized dictation signals when the block enable signal for that line interface card 70 is active, the time slots dedicated to those transceivers 71 are not used.

Once each counter 73 on every line interface card 70 is programmed, other signals from the timing card 110 can enter the command interpreter 68 and data selector 66 to control the flow of data through transceivers 71. The flow of data through the line interface cards 70 is discussed below.

In the preferred embodiment, data entering the central station 50 passes through a line interface card 70 (FIG. 1). However, it is also desirable to be able to receive external digitized voice and data from a Digital Channel Selector (DCS) (not shown), familiar to those skilled in the art. Briefly, referring back to FIG. 6, a DCS can provide external digitized voice and data via connector 154 directly to timing card 110 (FIG. 6). A line interface card 70 (FIG. 1) is not required when a digital data source is connected to the AT card 40 via a DCS. The digitized voice and data on bus 156 (FIG. 6) enters transceivers 155 on the timing card 110, and is passed to a cross-point switch 158 which is embodied by the same chip as multiplexer 97 discussed in relation to FIG. 45 8. The cross-point switch 158 is controlled by microcontroller 111 via lines 159, which determines signal direction. DCS digitized voice and data signals entering timing card 110 are routed onto bus channels 89 and 91 and to a signal processing card 90. Those skilled in the art will recognize that any signal source that provides data in  $\mu$ -law format can provide data directly to the timing card 110, as set forth above, bypassing the line interface cards 70.

3) Control of Signal Processing Cards

Referring now to FIGS. 8 and 9, start-up of a signal processing card 90 is described. Turning first to FIG. 9, at system start-up, or after a system reset, the tertiary processor 96 in a signal processing card 90 accesses its operating program stored in ROM 101. The tertiary processor 96 begins operating on the code in ROM 101. Control lines 174 connect the tertiary processor 96 to the ROM 101. The tertiary processor 96 interrupts the secondary processor 94 via line 47, and transfers part of the code stored in the ROM 101 into DRAM 100 via lines 55. The tertiary processory 96 controls buffer 170 via an enable signal on line 171 to allow access to DRAM controller 99 and DRAM 100.

After the secondary processor 94 loads its portion of the operating program into DRAM 100, the secondary processor

94 continues execution of the code in DRAM 100 without interrupting the tertiary processor 96. The secondary processor reads and writes to DRAM 100 via address latch 53. Thus, both processors 94 and 96 are operational via their software, which was collectively referred to as program 198b in FIG. 4. The tertiary processor 96 also controls boot-up of the digital signal processors 96, in a manner known to those skilled in the art.

The address of each signal processing card 90 is set by the timing card 110 addressing ROM 101, as was discussed 10 above (FIG. 6). Once its processors 94 and 96 are operating, a signal processing card 90 can communicate with the timing card 110. The data portion of the communications bus 83 enters the signal processing cards 90 as the 8-bit communications bus data lines 72 (FIG. 9). A MUART 74 receives commands on bus 72 from the timing card 110.

The multiplexed bus control PAL 69 monitors and controls handshaking between the signal processing card 90 and the timing card 110. The control PAL 69 receives and reads the /ENA, R/W, and /STROBE signals from the communications bus 83 and generates the /ACK signal on line 57 (FIG. 6). The control PAL 69 is connected to the tertiary processor 96 via lines 172.

The signal processing cards 90 can also be accessed via an RS-232 driver 78 and associated serial port 77. The tertiary processor 96 controls the serial port 77 and the RS-232 driver 78 on the signal processing card 90 through the MUART 74. In a signal processing card 90, the four most significant bits of command bus 72 are Clear to Send, Data Set Ready, Request to Send and Data Terminal Ready, 30 signals familiar to those skilled in the art. Serial port 77 and RS-232 driver 78 allow the signal processing cards 90 to communicate with other systems.

As can be seen in FIG. 9, the transfer of digitized dictation signals into and out of the signal processing cards 90 entails 35 the use of three bus channels 89, 91 and 93. The three bus channels 89, 91 and 93 enter the signal processing card 90 from multiplexed bus 80. Each of the bus channels carries up to thirty-two (32) channels of digitized dictation signals.

Each signal processing card 90 can be assigned to any 40 time slots on any bus channel 89, 91 or 93. The AT card 40 controls the assignment of signal processing cards 90 to time slots using the timing card 110. The timing card 110 sends a message to tertiary processor 96 via communications bus 72 that determines the assigned bus channel, 89, 91 or 93, 45 and time slots. Since the signal processing cards 90 time slot and bus channel assignments are assigned with software, there are no fixed assignments and every signal processing card 90 can communicate on any time slot or bus channel cessing cards 90 are ready to communicate after being assigned time slots and bus channels.

In the preferred embodiment of the present invention, each signal processing card has access to all four bus channels 89, 91, 93 and 95. Those skilled in the art will 55 recognize that the number of channels in the system is variable by scaling the preferred embodiment up or down.

Continuing with FIGS. 1 and 9, the line interface cards 70 and signal processing cards 90 are prepared for operation at start-up of the modular digital dictation system 10. Furthermore, the timing card 110 periodically polls each address on the multiplexed bus 80 to determine if a new card is connected to the central station 50. If the timing card 110 detects a card at a previously empty address, the timing card 110 initiates communication with the card, and prepares the 65 card for communication of digital dictation signals. Therefore, line interface cards 70 may be added to the

20 central station 50 to expand the capacity of the modular digital dictation system 10 while the system is running.

Referring to FIG. 9, an intercom feature is provided via lines 133 in the preferred embodiment of the present invention. Control signals from timing card 110 on lines 133 allow digitized voice signals to pass from one signal processing card 90 to other signal processing cards 90. The voice signals are output on the voice output channels dedicated to the receiving signal processing cards 90. Therefore, the voice signals are passed through the line interface card(s) 70 and to transcription stations 30 assigned to receiving signal processing cards 90. Thus, voice signals can be broadcast to other stations, 20 or 30, from one dictation station 20. Control signals on lines 133 control transfer of the voice signals on to the appropriate bus for broadcast to the appropriate stations.

#### 4) Control of the Multiplexed Bus

Referring back to FIG. 6, the timing card 110 controls the multiplexed bus 80. The multiplexed bus 80 has two clocks, on lines 85, that are provided to bus 80 by a clock generator 128 on the timing card 110 in the preferred embodiment. The clock generator 128 receives a 8.192 MHz signal from a crystal oscillator (not shown) and divides the signal down in a manner familiar to those skilled in the art. The first clock is a 4.096 MHz signal that is used by Mitel compatible devices. The second clock is a 2.048 MHz clock signal that is used as the bit clock for data transfer in other standard systems.

Furthermore, three synchronization signals are supplied on lines 84. A frame synchronization signal indicates the start of a frame of data on muxbus 80. Having three synchronization signals, despite the fact that only one is used in a running system, permits the bus 80 to be compatible with a plurality of different systems, including the Signal Computing System Architecture, PCM expansion bus (PEB), and Multi-Vendor Integration Protocol (MVIP). In the preferred embodiment of the present invention, all the clocks and synchronization signals provided by the timing card 110 are synchronized, thereby reducing system noise.

When ready to initiate communications with the dictation stations 20 and transcription stations 30, the file manager 134a-n (FIG. 5A) in the AT card 40 sets up the modular digital dictation system 10 for communications by assigning each signal processing card 90 to a line interface card 70. The AT card 40 sets each line interface card 70 to operate on a particular time slot on multiplexed bus 80 by preloading counters 73 (FIG. 7). As was set forth above, the line interface cards 70 are dedicated to a certain bus channel, 89, 91, 93 or 95, as determined by their hard-wired connection that is physically supplied to the card 90. The signal pro- 50 to the multiplexed bus 80. The signal processing cards 90 are assignable to any time slots and bus channels. As was described above, each signal processing card 90 is assigned to a particular bus channel and certain time slots.