(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6867925号

(P6867925)

(45) 発行日 令和3年5月12日(2021.5.12)

(24) 登録日 令和3年4月13日(2021.4.13)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 3 4

請求項の数 1 (全 99 頁)

(21) 出願番号 特願2017-196615 (P2017-196615)

(22) 出願日 平成29年10月10日 (2017.10.10)

(65) 公開番号 特開2019-68985 (P2019-68985A)

(43) 公開日 令和1年5月9日 (2019.5.9)

審査請求日 令和2年3月16日 (2020.3.16)

(73) 特許権者 000144153

株式会社三共

東京都渋谷区渋谷三丁目29番14号

(72) 発明者 小倉 敏男

東京都渋谷区渋谷三丁目29番14号 株式会社三共内

審査官 阿部 知

(56) 参考文献 特許第6692330 (JP, B2)

(58) 調査した分野 (Int.Cl., DB名)

A 6 3 F 7/02

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技を行うことが可能な遊技機であって、

受信したコマンドに基づいて制御を行う制御手段と、

前記制御手段と電気的に接続可能な電子部品と、を備え、

前記制御手段は、

前記コマンドとして複数のテストコマンドの組み合わせにより、前記電子部品の状態

を検査する検査処理を実行可能であり、

前記検査処理として、データの書き込みと読み出しが可能な記憶領域に対する検査を実行可能

であり、

前記検査処理の実行中は、他の処理を実行せず、

前記複数のテストコマンドの組み合わせは、遊技の進行に伴い受信する遊技用コマンド

の個数よりも多い個数のコマンドの組み合わせである、

ことを特徴とする遊技機。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、パチンコ遊技機等の遊技を行うことが可能な遊技機に関する。

## 【背景技術】

## 【0002】

パチンコ遊技機等の遊技機において、受信コマンドにより配線の異常を検出して報知可能とする技術が提案されている（例えば特許文献1）。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007-296132号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上記特許文献1に記載の技術によると、受信コマンドのビット値により異常があるか否かを検出するので、例えばビット値のエラーにより、本来実行すべきではない状況で誤って配線の検査が実行されてしまい、遊技者に不利益を与えるおそれがある。 10

【0005】

この発明は、上記実状に鑑みてなされたものであり、適切な検査が可能な遊技機の提供を目的とする。

【課題を解決するための手段】

【0006】

(A) 上記目的を達成するために、本願の請求項に係る遊技機は、遊技を行うことが可能な遊技機であって、受信したコマンドに基づいて制御を行う制御手段と、前記制御手段と電気的に接続可能な電子部品と、を備え、前記制御手段は、前記コマンドとして複数のテストコマンドの組み合わせにより、前記電子部品の状態を検査する検査処理を実行可能であり、前記検査処理として、データの書込と読出が可能な記憶領域に対する検査を実行可能であり、前記検査処理の実行中は、他の処理を実行せず、前記複数のテストコマンドの組み合わせは、遊技の進行に伴い受信する遊技用コマンドの個数よりも多い個数のコマンドの組み合わせである、ことを特徴とする。 20

(1) 上記目的を達成するために、他の遊技機は、遊技を行うことが可能な遊技機（例えばパチンコ遊技機1など）であって、受信したコマンドに基づいて制御を行う制御手段（例えばCPU62AK101など）と、前記制御手段と電気的に接続可能な電子部品（例えば外部RAM62AK121など）とを備え、前記制御手段は、前記コマンドとして複数のテストコマンドの組み合わせにより、前記電子部品の状態を検査する検査処理（例えば外部RAMチェック処理、高負荷チェック処理など）を実行可能であり（例えば図48を参照）、前記検査処理の実行中は、他の処理を実行しない（例えば図47、図51～図54を参照）。 30

このような構成によれば、適切な検査が可能になる。

【0007】

(2) 上記(1)の遊技機において、前記複数のテストコマンドの組み合わせは、遊技の進行に伴い受信する遊技用コマンド（例えば図41を参照）とは異なるコマンドの組み合わせからなってもよい（例えば図48を参照）。

このような構成においては、適切な検査が可能になる。

【0008】

(3) 上記(1)または(2)の遊技機において、前記複数のテストコマンドの組み合わせは、遊技の進行に伴い受信する遊技用コマンドの個数（例えば2～3個）よりも多い個数（例えば12個）のコマンドの組み合わせからなってもよい。 40

このような構成においては、適切な検査が可能になる。

【0009】

(4) 上記(1)から(3)のいずれかの遊技機において、前記検査処理の実行中に、前記電子部品の状態に応じた検査時表示を行う表示手段（例えば画像表示装置5など）を備えてよい。

このような構成においては、適切な検査が可能になる。

【0010】

10

20

30

40

50

(5) 上記(4)の遊技機において、前記表示手段は、遊技の進行に伴う表示の設定と共通の設定により、前記検査時表示が可能であってもよい(例えば図44、図45、図47などを参照)。

このような構成においては、適切な検査が可能になる。

#### 【0011】

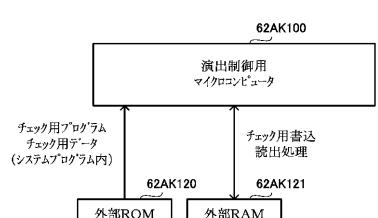

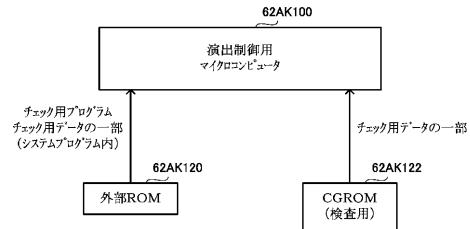

(6) 上記(1)から(5)のいずれかの遊技機において、前記制御手段と前記電子部品は、複数の記憶手段(例えば外部ROM62AK120、CGROM62AK122など)とともに基板(例えば演出制御基板12など)に搭載可能であり、前記制御手段は、前記基板に前記複数の記憶手段のうち1の記憶手段(例えば外部ROM62AK120など)が搭載されている場合に、前記検査処理を実行可能であってもよい。 10

このような構成においては、適切な検査が可能になる。

#### 【0012】

(7) 上記(1)から(6)のいずれかの遊技機において、前記制御手段は、前記複数のテストコマンドの組み合わせとして、当該テストコマンドを所定の順番で受信した場合に前記検査処理を実行可能であり、前記所定の順番は複数種類あり、前記検査処理として、前記複数のテストコマンドの組み合わせを受信した順番の種類に応じて異なる処理を実行可能であってもよい(例えば図48を参照)。

このような構成においては、適切な検査が可能になる。

#### 【図面の簡単な説明】

#### 【0013】

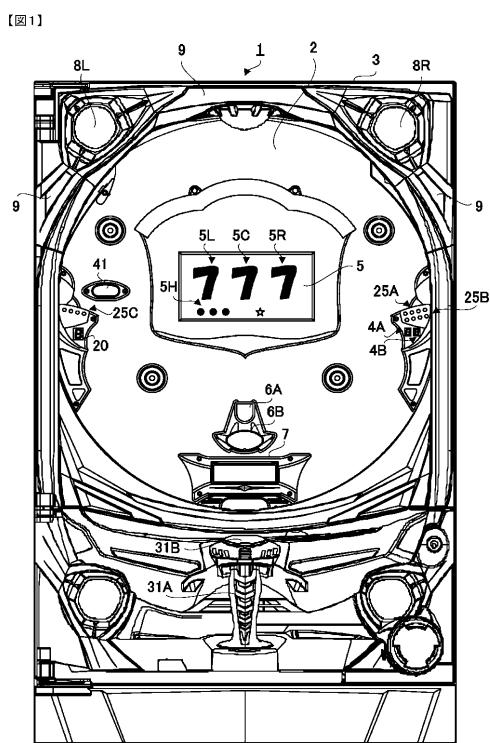

【図1】この実施の形態におけるパチンコ遊技機の正面図である。

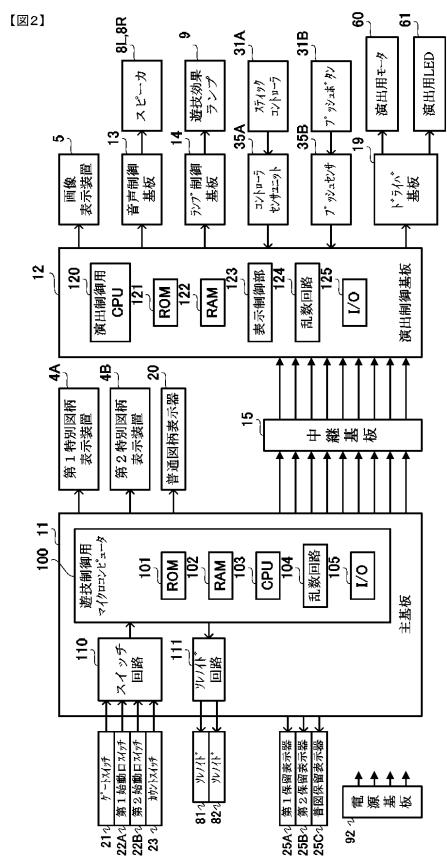

【図2】パチンコ遊技機に搭載された各種の制御基板などを示す構成図である。

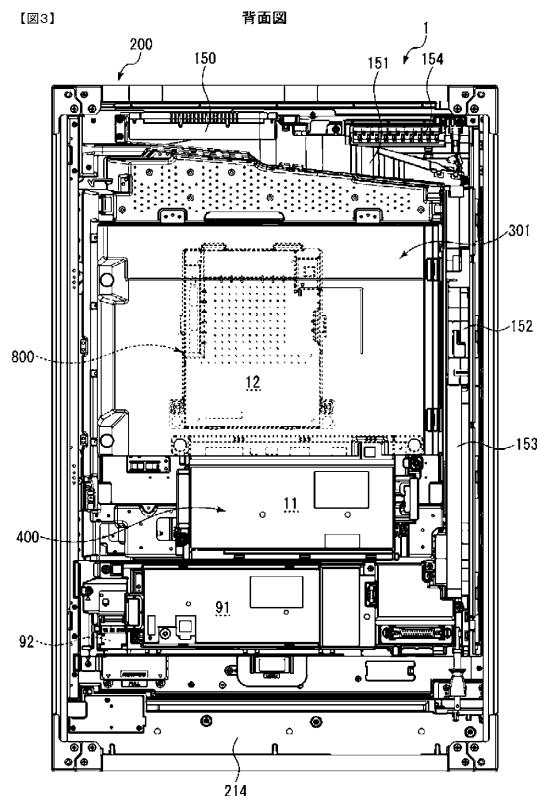

【図3】遊技機用枠の背面図である。

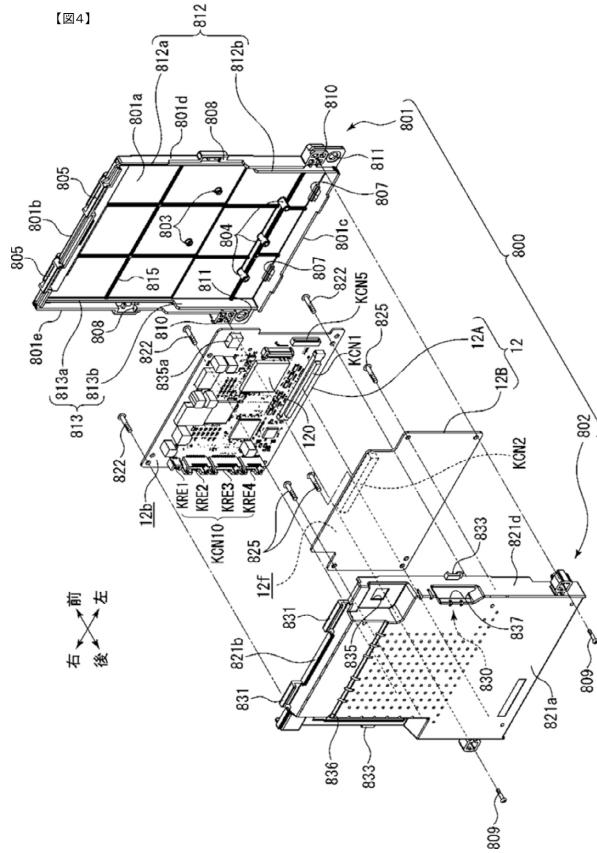

【図4】基板ケースを見た状態の分解斜視図である。

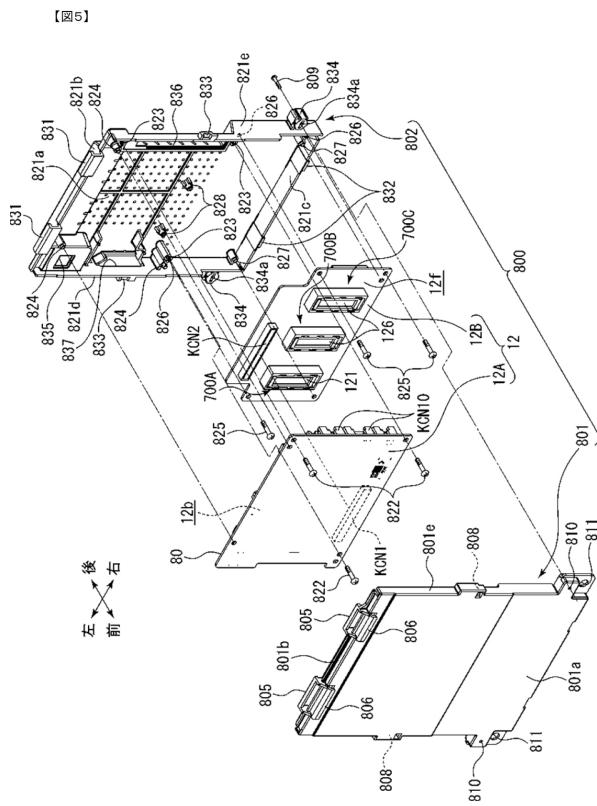

【図5】基板ケースを見た状態の分解斜視図である。

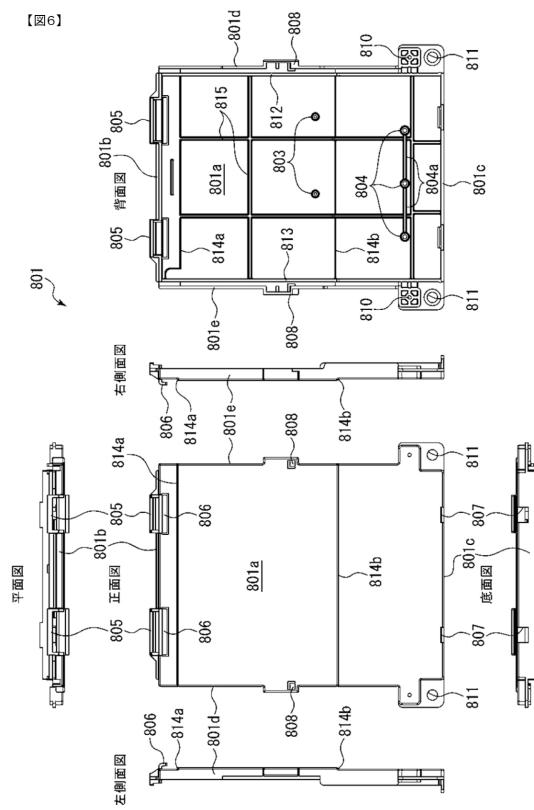

【図6】ベース部材を示す6面図である。

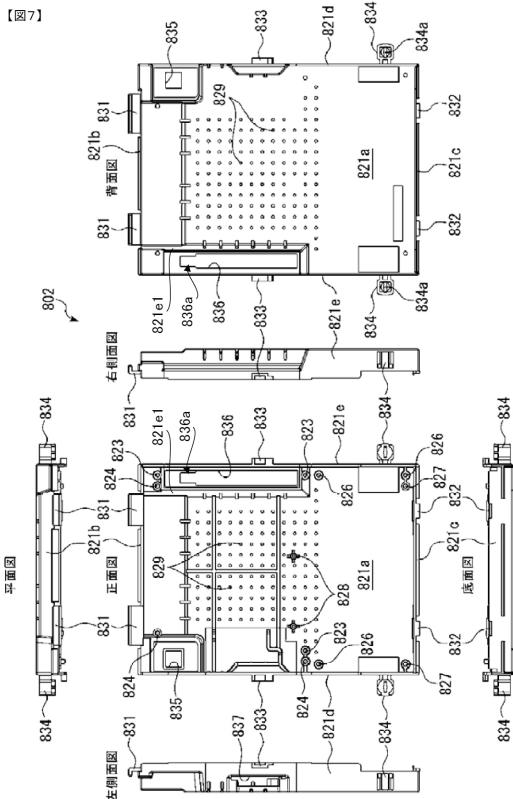

【図7】カバー部材を示す6面図である。

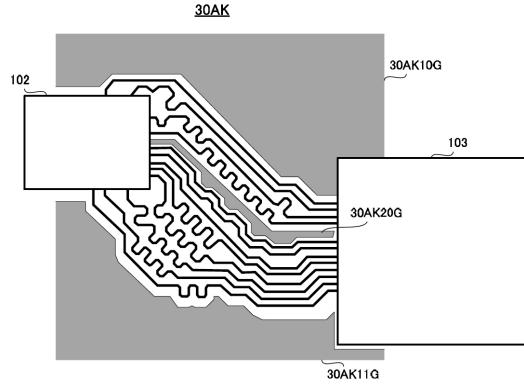

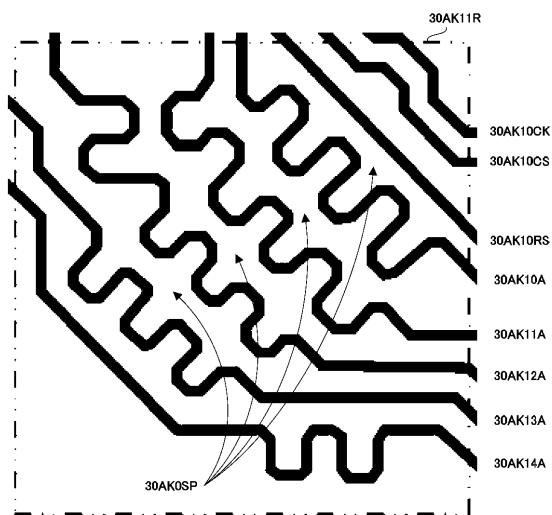

【図8】配線のパターンが形成された部分の構成例を示す図である。

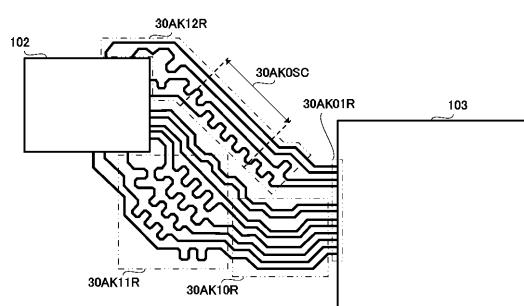

【図9】配線のパターンを説明するための領域や区間を示す図である。

【図10】図9に示された領域の拡大図である。 30

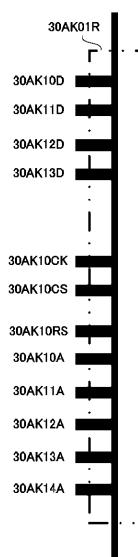

【図11】配線のパターンに対応する設定例を示す図である。

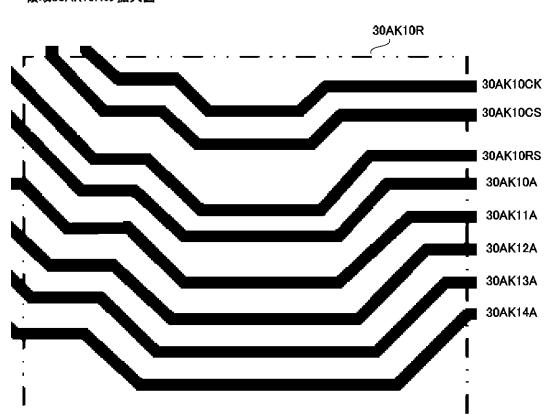

【図12】図9に示された領域の拡大図である。

【図13】図9に示された領域の拡大図である。

【図14】主基板の構成例を示す断面図である。

【図15】配線のパターンについて他の構成例を示す図である。

【図16】特徴部42AKに係る構成例を示す図である。

【図17】第2形状部が異なる方向に形成されている構成例を示す図である。

【図18】複数の信号配線が異なる配線幅に形成されている構成例を示す図である。

【図19】第2形状部が対応して形成されている構成例を示す図である。

【図20】回路部品が接続されるように実装された構成例を示す図である。 40

【図21】特徴部43AKに係る構成例を示す図である。

【図22】特徴部44AKに係る構成例を示す図である。

【図23】特徴部45AKに係る遊技機の基板ケース、基板、及びヒートシンクを後方からみた分解斜視図である。

【図24】特徴部45AKに係る遊技機の基板ケース、基板、及びヒートシンクを前方からみた分解斜視図である。

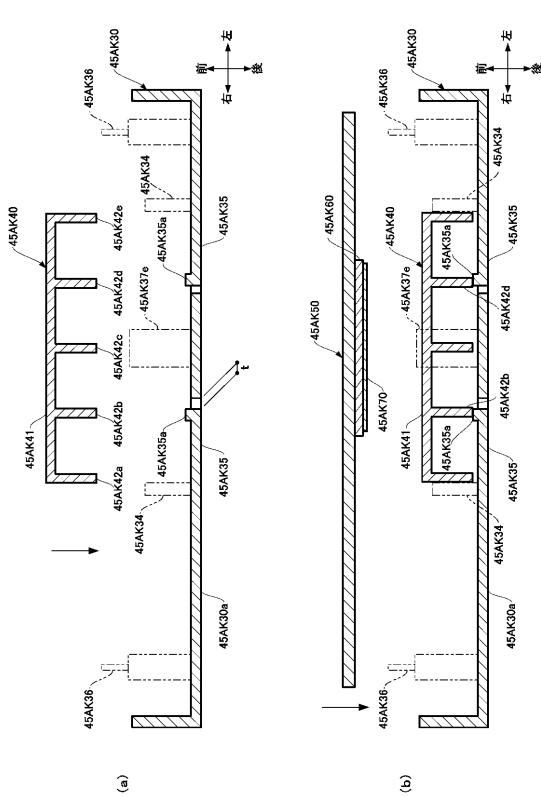

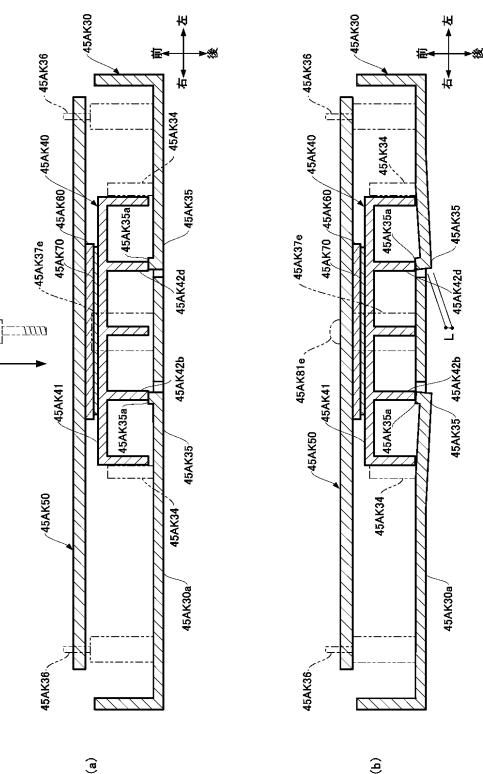

【図25】基板ケースにヒートシンク及び基板を取り付ける様子を取り付け順((a)～(b))で示した断面図である。

【図26】図25に続いて基板ケースにヒートシンク及び基板を取り付ける様子を取り付け順((a)～(b))で示した断面図である。 50

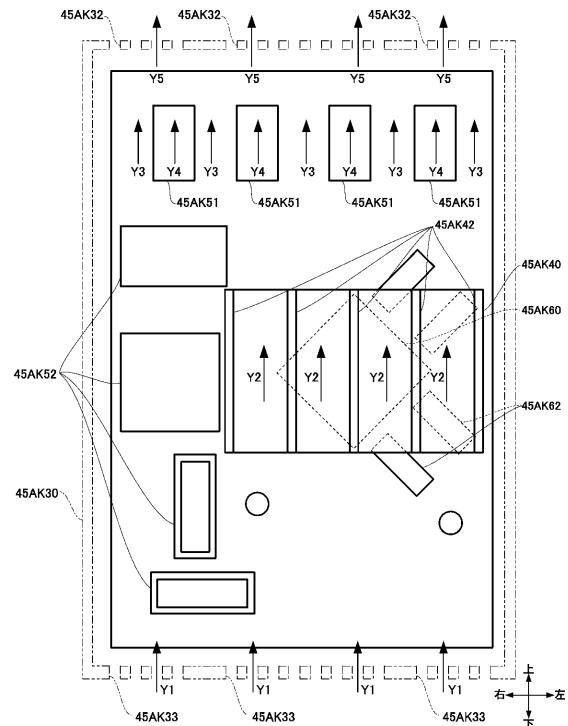

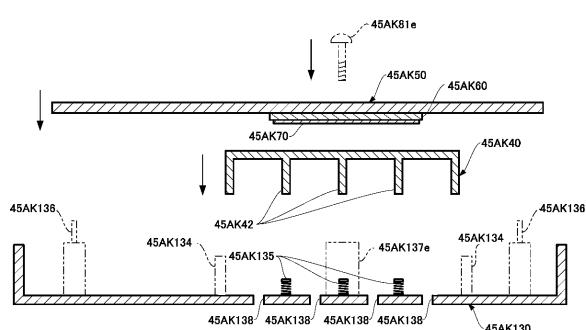

【図27】ヒートシンクと電子部品との関係を説明するための平面図である。

【図28】基板ケース内における空気の流れを説明するための説明図である。

【図29】他の実施形態1に係る遊技機の基板ケースにヒートシンク及び基板を取り付ける様子を示した断面図である。

【図30】他の実施形態2に係る遊技機の基板ケースにヒートシンク及び基板を取り付ける様子を示した断面図である。

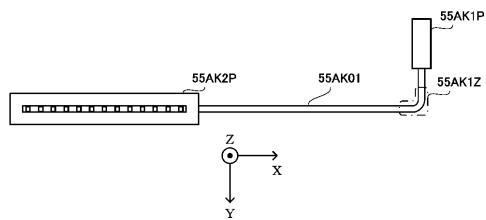

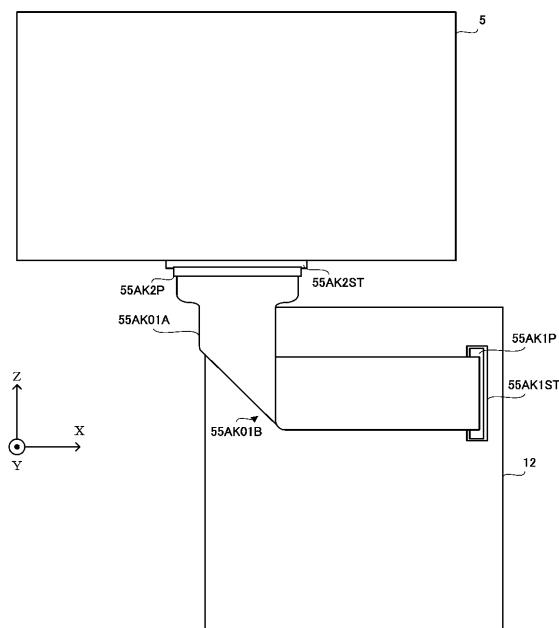

【図31】特徴部55AKに係る構成例を示す図である。

【図32】図31に示されるA-A断面図である。

【図33】演出制御基板と画像表示装置との接続例を示す図である。

【図34】図33の接続例における接続配線部材の上面図である。

10

【図35】演出制御基板と画像表示装置との他の接続例を示す図である。

【図36】図35の接続例における接続配線部材の上面図である。

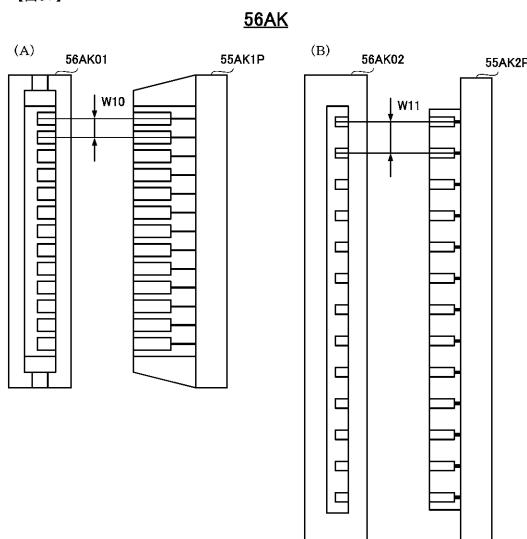

【図37】特徴部56AKに係る構成例を示す図である。

【図38】複数の電気部品について他の構成例を示す図である。

【図39】全体が直線形状または略直線形状を有する接続配線部材を用いた接続例を示す図である。

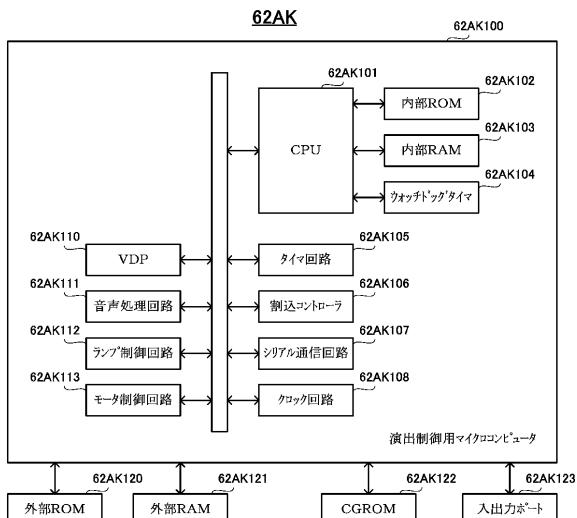

【図40】特徴部62AKに係る構成例を示す図である。

【図41】遊技用の演出制御コマンドの内容例を示す図である。

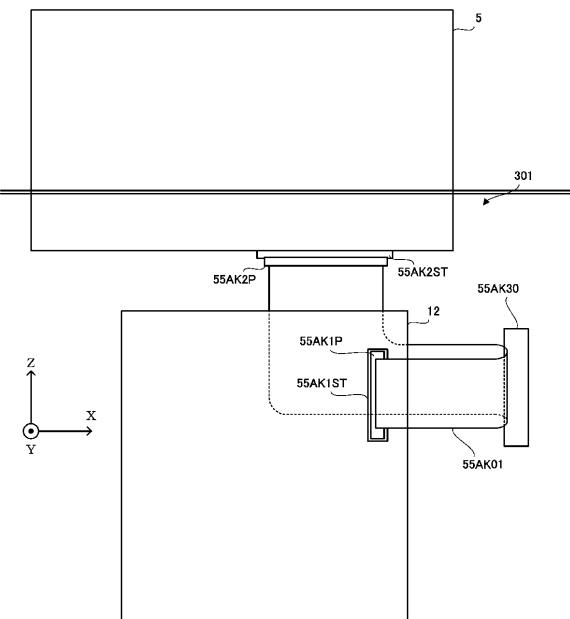

【図42】テストコマンドとなる演出制御コマンドの内容例を示す図である。

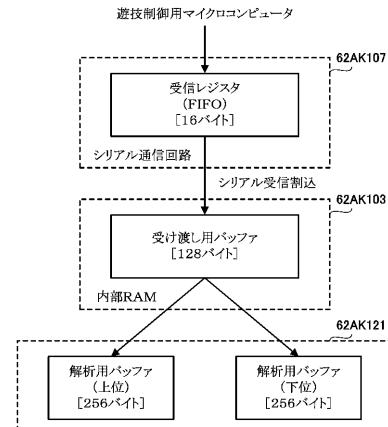

【図43】受信レジスタや受信バッファの構成例を示す図である。

20

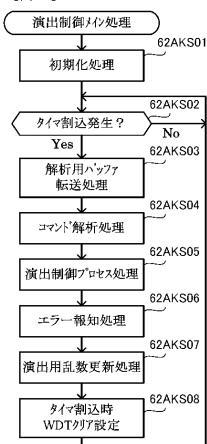

【図44】演出制御メイン処理の一例を示すフローチャートである。

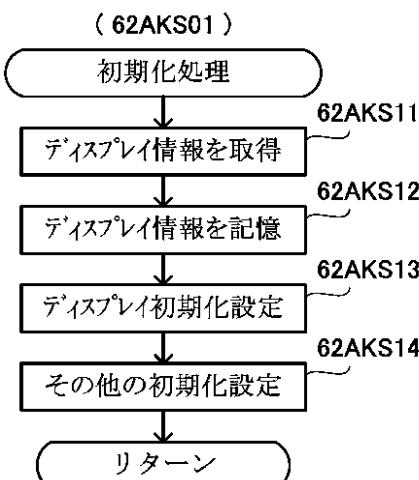

【図45】初期化処理の一例を示すフローチャートである。

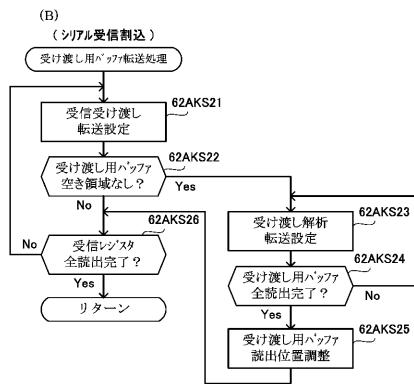

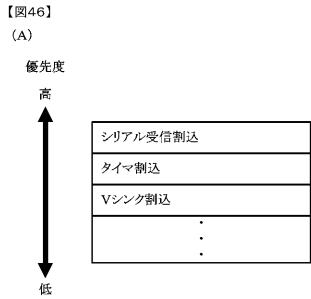

【図46】割込の優先度を示す図および受け渡し用バッファ転送処理の一例を示すフローチャートである。

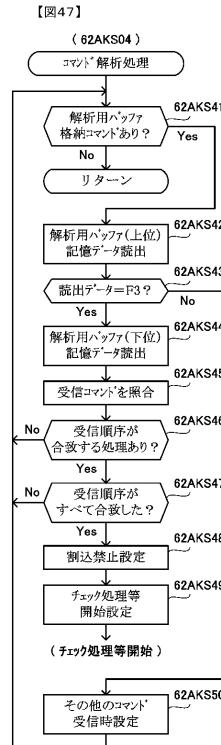

【図47】コマンド解析処理の一例を示すフローチャートである。

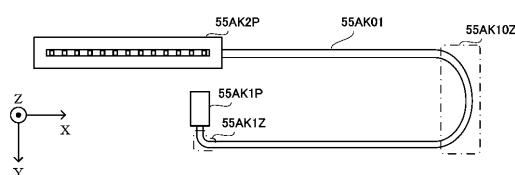

【図48】特徴部63Kに係る受信順序と実行する処理との設定例を示す図である。

【図49】チェック処理の実行に対応した画面表示の設定例を示す図である。

【図50】チェック用プログラムやチェック用データの使用例を示す図である。

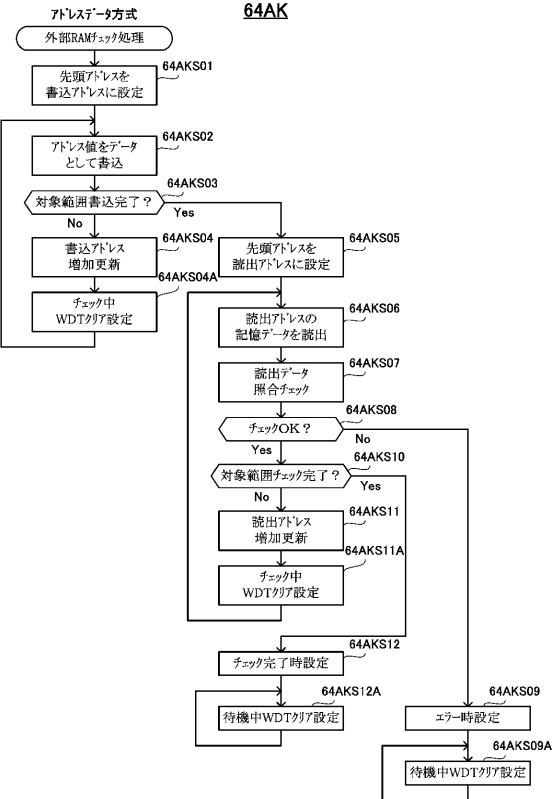

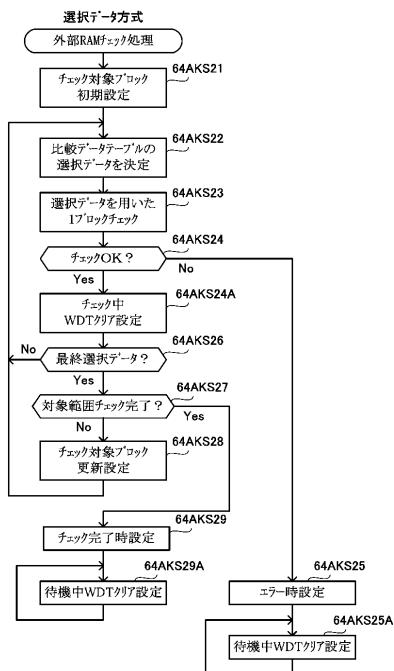

【図51】外部RAMチェック処理の一例を示すフローチャートである。

30

【図52】外部RAMチェック処理の他の一例を示すフローチャートである。

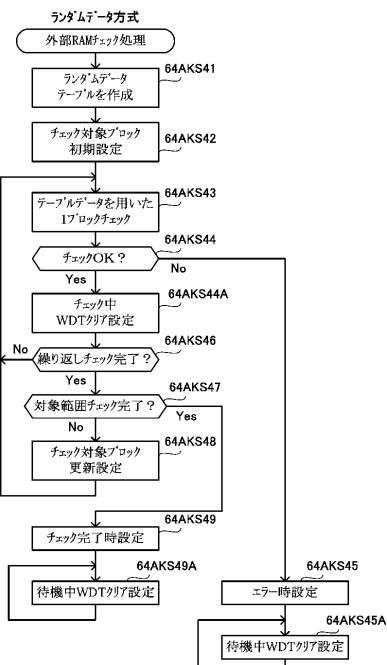

【図53】外部RAMチェック処理の他の一例を示すフローチャートである。

【図54】外部RAMチェック処理の他の一例を示すフローチャートである。

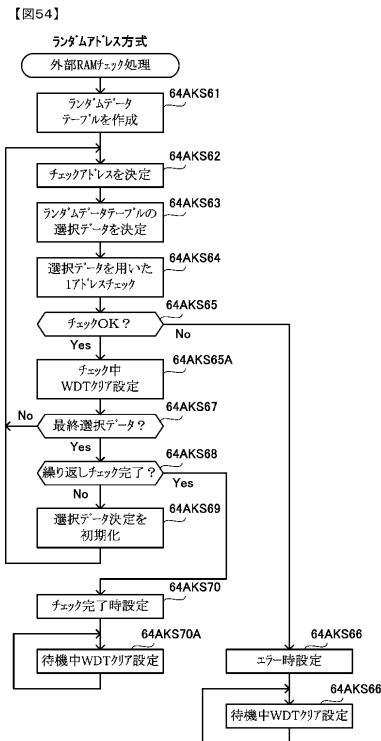

【図55】外部RAMチェック処理の実行例を示す図である。

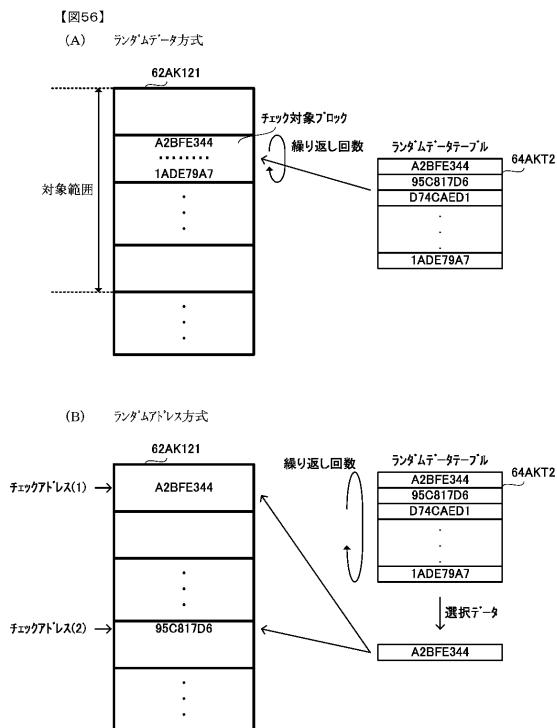

【図56】外部RAMチェック処理の実行例を示す図である。

**【発明を実施するための形態】**

**【0014】**

図1は、この実施の形態に係るパチンコ遊技機1の正面図である。パチンコ遊技機1は、遊技盤2と、遊技機用枠3とを備えている。その他、パチンコ遊技機1は、遊技機用枠3を回動可能に支持する外枠などを備えている。遊技盤2は、遊技盤面を構成するゲージ盤である。遊技機用枠3は、遊技盤2を固定する台枠である。遊技盤2には、ガイドレールなどによって囲まれた遊技領域が形成されている。発射装置から発射された遊技球(遊技媒体)は、発射通路を通過して、遊技領域に打ち込まれる。遊技機用枠3には、ガラス窓を有するガラス扉枠が回動可能に設けられている。

40

**【0015】**

遊技盤2の所定位置には、第1特別図柄表示装置4A、第2特別図柄表示装置4B、画像表示装置5、普通入賞球装置6A、普通可変入賞球装置6B、特別可変入賞球装置7、普通図柄表示器20、第1保留表示器25A、第2保留表示器25B、普図保留表示器25C、通過ゲート41などが設けられている。その他、遊技領域における遊技盤面には、風車や多数の障害釘、一般入賞口、アウト口などが設けられていればよい。遊技領域の周辺部には遊技効果ランプ9が設けられている。遊技機用枠3の左右上部位置にはスピーカ

50

8 L、8 Rが設けられている。

**【0016】**

遊技機用枠3の右下部位置には、打球操作ハンドル（操作ノブ）が設けられている。打球操作ハンドルは、遊技球を遊技領域に向けて発射するために遊技者等によって操作され、その操作量（回転量）に応じて遊技球の弾発力が調整される。遊技領域の下方における遊技機用枠3の所定位置には、遊技球を保持（貯留）する上皿（打球供給皿）と、上皿からの余剰球などを保持（貯留）する下皿が設けられている。下皿を形成する部材にはステイックコントローラ31Aが取り付けられ、上皿を形成する部材にはプッシュボタン31Bが設けられている。

**【0017】**

第1特別図柄表示装置4A、第2特別図柄表示装置4B、画像表示装置5の画面上などでは、特別図柄や飾り図柄の可変表示が行われる。これらの可変表示は、普通入賞球装置6Aに形成された第1始動入賞口を遊技球が通過（進入）したことによる第1始動入賞の発生に基づいて、あるいは、普通可変入賞球装置6Bに形成された第2始動入賞口を遊技球が通過（進入）したことによる第2始動入賞の発生に基づいて、実行可能となる。第1特別図柄表示装置4Aと第2特別図柄表示装置4Bはそれぞれ、例えば7セグメントやドットマトリクスのLED（発光ダイオード）などを用いて構成され、可変表示ゲームの一例となる特図ゲームにおいて、識別情報（特別識別情報）である特別図柄（特図）が、変動可能に表示（可変表示）される。画像表示装置5は、例えばLCD（液晶表示装置）などを用いて構成され、各種の演出画像を表示する表示領域を形成している。画像表示装置5の画面上では、特図ゲームにおける第1特別図柄表示装置4Aによる特別図柄（第1特図）の可変表示や第2特別図柄表示装置4Bによる特別図柄（第2特図）の可変表示のそれぞれに対応して、例えば3つといった複数の可変表示部となる飾り図柄表示エリアにて、識別情報（装飾識別情報）である飾り図柄が可変表示される。この飾り図柄の可変表示も、可変表示ゲームに含まれる。一例として、画像表示装置5の画面上には、「左」、「中」、「右」の飾り図柄表示エリア5L、5C、5Rが配置されている。

**【0018】**

画像表示装置5の画面上には、保留記憶表示エリア5Hが配置されている。保留記憶表示エリア5Hでは、特図ゲームに対応した可変表示の保留数（特図保留記憶数）を特定可能に表示する保留表示が行われる。保留表示は、可変表示に関する情報の保留記憶に対応して表示可能なものであればよい。保留記憶表示エリア5Hとともに、あるいは、保留記憶表示エリア5Hに代えて、第1保留表示器25Aと第2保留表示器25Bとを用いた保留表示が行われてもよい。

**【0019】**

図2は、各種基板や周辺装置などの構成例を示すブロック図である。パチンコ遊技機1には、例えば図2に示すような主基板11、演出制御基板12、音声制御基板13、ランプ制御基板14といった、各種制御基板が搭載されている。また、パチンコ遊技機1には、中継基板15、ドライバ基板19、電源基板92なども搭載されている。その他にも、例えば払出制御基板、情報端子基板、発射制御基板、インターフェース基板、タッチセンサ基板などといった、各種の基板が搭載されてもよい。各種制御基板は、導体パターンが形成されて電気部品が実装されるプリント配線板などの電子回路基板だけではなく、電子回路基板に電気部品が実装（搭載）されて特定の電気的機能を実現するように構成された電子回路実装基板を含む概念である。

**【0020】**

電源基板92は、外部電源（商用電源）である交流電源からの電力を、主基板11や演出制御基板12などの各種制御基板を含めた電気部品に供給可能となるように構成されている。電源基板92は、例えば交流（AC）を直流（DC）に変換するための整流回路、所定の直流電圧を特定の直流電圧（例えば直流12Vや直流5Vなど）に変換するための電源回路などを、備えている。電源基板92にて生成された電圧は、ドア中継基板を介して主基板11や演出制御基板12などに供給されてもよい。

10

20

30

40

50

**【0021】**

主基板11には、遊技制御用マイクロコンピュータ100、スイッチ回路110、ソレノイド回路111などが搭載されている。主基板11では、ゲートスイッチ21、始動口スイッチ（第1始動口スイッチ22Aおよび第2始動口スイッチ22B）、カウントスイッチ23といった、各種検出用のスイッチから取り込んだ信号が、スイッチ回路110を介して遊技制御用マイクロコンピュータ100に伝送される。ゲートスイッチ21は、通過ゲート41を通過した遊技球（ゲート通過球）を検出する。ゲートスイッチ21によるゲート通過球の検出に基づいて、普通図柄表示器20による普通図柄の可変表示が実行可能となる。第1始動口スイッチ22Aは、第1始動入賞口を通過（進入）した遊技球を検出する。第2始動口スイッチ22Bは、第2始動入賞口を通過（進入）した遊技球を検出する。カウントスイッチ23は、大入賞口を通過（進入）した遊技球を検出する。第1始動入賞口や第2始動入賞口、大入賞口といった、各種の入賞口を通過した遊技球が検出された場合には、それぞれの入賞口に対応して予め個数が定められた賞球としての遊技球が払い出される。10

**【0022】**

主基板11では、遊技制御用マイクロコンピュータ100からのソレノイド駆動信号が、ソレノイド回路111を介して普通電動役物用のソレノイド81や大入賞口扉用のソレノイド82に伝送される。普通電動役物用のソレノイド81は、普通可変入賞球装置6Bに形成された第2始動入賞口を遊技球が通過しにくい状態（または通過しない状態）と通過しやすい状態（または通過する状態）とに変化可能にする。大入賞口扉用のソレノイド82は、特別可変入賞球装置7に形成された大入賞口を遊技球が通過不可能な状態と通過可能な状態とに変化可能にする。主基板11からは、第1特別図柄表示装置4A、第2特別図柄表示装置4B、普通図柄表示器20などの表示制御を行うための指令信号が伝送される。20

**【0023】**

主基板11に搭載された遊技制御用マイクロコンピュータ100は、例えば1チップのマイクロコンピュータであり、遊技制御用のプログラムや固定データ等を記憶するROM101と、遊技制御用のワークエリアを提供するRAM102と、遊技制御用のプログラムを実行して制御動作を行うCPU103と、CPU103とは独立して乱数値を示す数値データの更新を行う乱数回路104と、I/O(Input/Output port)105とを備えて構成される。一例として、遊技制御用マイクロコンピュータ100では、CPU103がROM101から読み出したプログラムを実行することにより、パチンコ遊技機1における遊技の進行を制御するための処理が実行される。主基板11に搭載された遊技制御用マイクロコンピュータ100では、例えば乱数回路104やRAM102の所定領域に設けられた遊技用ランダムカウンタなどにより、遊技の進行を制御するために用いられる各種の乱数値を示す数値データが更新可能にカウント（生成）される。遊技の進行を制御するために用いられる乱数は、遊技用乱数ともいう。30

**【0024】**

演出制御基板12は、中継基板15を介して主基板11から伝送された制御信号（演出制御コマンド）の受信に基づいて、画像表示装置5、スピーカ8L、8R、遊技効果ランプ9、演出用モータ60および演出用LED61といった演出用の電気部品による演出動作を制御可能とする。演出制御基板12には、演出制御用CPU120やROM121、RAM122、表示制御部123、乱数回路124、I/O125などが搭載されている。40

**【0025】**

演出制御基板12に搭載された演出制御用CPU120は、ROM121から読み出した演出制御用のプログラムや固定データ等を用いて、演出用の電気部品による演出動作を制御するための処理を実行する。演出制御基板12に搭載された表示制御部123は、演出制御用CPU120からの表示制御指令などに基づき、画像表示装置5における表示動作の制御内容を決定する。例えば、表示制御部123は、画像表示装置5の表示画面内に50

表示させる演出画像の切換タイミングを決定することなどにより、飾り図柄の可変表示や各種の演出表示を実行させるための制御を行う。

#### 【0026】

演出制御基板12には、コントローラセンサユニット35Aと、プッシュセンサ35Bとが接続されている。コントローラセンサユニット35Aは、傾倒方向センサと、トリガセンサとを含んでいる。傾倒方向センサは、ステイックコントローラ31Aの操作桿に対する傾倒操作が行われたときに、複数のセンサを用いて操作桿の傾倒方向を検出可能にする。トリガセンサは、ステイックコントローラ31Aの操作桿に設けられたトリガボタンに対する押引操作の有無を検出可能にする。すなわち、コントローラセンサユニット35Aにより、ステイックコントローラ31Aの操作桿に対する傾倒動作やトリガボタンに対する押引動作といった、ステイックコントローラ31Aを用いた遊技者の動作を検出することができる。プッシュセンサ35Bにより、プッシュボタン31Bに対する押下動作といった、プッシュボタン31Bを用いた遊技者の動作を検出することができる。演出制御基板12では、例えば乱数回路124やRAM122の所定領域に設けられた演出用ランダムカウンタなどにより、演出の実行を制御するために用いられる各種の乱数値を示す数値データが更新可能にカウント(生成)される。演出の実行を制御するために用いられる乱数は、演出用乱数ともいう。

#### 【0027】

演出制御基板12は、第1基板12Aと、該第1基板12Aに対し基板対基板接続される第2基板12Bとを有する。第1基板12Aには、演出制御用CPU120や表示制御部123のグラフィックスプロセッサなどが搭載され、第2基板12Bには、ROM121や画像データメモリといった機種に固有なデータなどが記憶された電気部品が搭載されている。表示制御部123のグラフィックスプロセッサは、演出制御用CPU120の機能を統合したマイクロプロセッサであってもよいし、演出制御用CPU120とは別個のチップとして構成されたマイクロプロセッサであってもよい。

#### 【0028】

音声制御基板13は、演出制御基板12とは別個に設けられた音声出力制御用の制御基板であり、演出制御基板12からの指令や制御データなどに基づいて、スピーカ8L、8Rから音声を出力させるための音声信号処理を実行する処理回路などが搭載されている。なお、演出制御基板12に搭載された表示制御部123を構成するグラフィックスコントローラなどが音声信号処理を実行可能であれば、音声制御基板13に帯域フィルタや增幅回路などを搭載すればよい。あるいは、音声制御基板13を省略して、演出制御基板12の基板上に帯域フィルタや增幅回路などを搭載してもよい。ランプ制御基板14は、演出制御基板12とは別個に設けられたランプ出力制御用の制御基板であり、演出制御基板12からの指令や制御データなどに基づいて、遊技効果ランプ9などにおける点灯や消灯を行うランプドライバ回路などが搭載されている。ドライバ基板19は、演出制御基板12とは別個に設けられた電気部品駆動用の制御基板であり、演出制御基板12からの指令や制御データなどに基づいて、演出用モータ60に含まれる各種モータの回動制御や演出用LED61に含まれる各種LEDの点灯制御などを行うためのドライバ回路などが搭載されている。ドライバ基板19からの出力信号は、演出用モータ60に含まれる各モータと、演出用LED61に含まれる各LEDとに向けて伝送される。

#### 【0029】

パチンコ遊技機1においては、遊技媒体としての遊技球を用いた所定の遊技が行われ、その遊技結果に基づいて所定の遊技価値が付与可能となる。遊技球を用いた遊技の一例として、パチンコ遊技機1における遊技機用枠3の右下部位置に設けられた打球操作ハンドルが遊技者によって所定操作(例えば回転操作)されたことにに基づいて、所定の打球発射装置が備える発射モータなどにより、遊技媒体としての遊技球が遊技領域に向けて発射される。遊技領域を流下した遊技球が、各種の入賞口を通過(進入)した場合に、賞球としての遊技球が払い出される。特別図柄や飾り図柄の可変表示結果が「大当たり」となった場合には、大入賞口が開放されて遊技球が通過(進入)しやすい状態となることで、遊技者

10

20

30

40

50

にとって有利な有利状態としての大当たり遊技状態となる。

#### 【0030】

有利状態は大当たり遊技状態に限定されず、時短状態や確変状態といった特別遊技状態が含まれてもよい。その他、大当たり遊技状態にて実行可能なラウンド遊技の上限回数が第2ラウンド数（例えば「7」）よりも多い第1ラウンド数（例えば「15」）となること、時短状態にて実行可能な可変表示の上限回数が第2回数（例えば「50」）よりも多い第1回数（例えば「100」）となること、確変状態における大当たり確率が第2確率（例えば $1/50$ ）よりも高い第1確率（例えば $1/20$ ）となること、通常状態に制御されることなく大当たり遊技状態に繰り返し制御される回数である連チャン回数が第2連チャン数（例えば「5」）よりも多い第1連チャン数（例えば「10」）となることの一部または全部といった、遊技者にとってより有利な遊技状況となることが含まれていてもよい。10

#### 【0031】

主基板11では、電源基板92からの電力供給が開始されると、遊技制御用マイクロコンピュータ100のCPU103が起動し、CPU103によって遊技制御メイン処理の実行が開始される。遊技制御メイン処理において、CPU103は、割込み禁止に設定した後、必要な初期設定を行う。初期設定が終了すると、割込み許可とした後、ループ処理に入る。以後、所定時間（例えば2ミリ秒）ごとにCTCから割込み要求信号がCPU103へ送出され、CPU103は定期的に遊技制御用タイマ割込み処理を実行する。

#### 【0032】

遊技制御用タイマ割込み処理は、スイッチ処理、メイン側エラー処理、情報出力処理、遊技用乱数更新処理、特別図柄プロセス処理、普通図柄プロセス処理、コマンド制御処理などを含んでいる。スイッチ処理では、各種スイッチから入力される検出信号の状態を判定する。メイン側エラー処理では、パチンコ遊技機1の異常診断を行い、必要ならば警告を発生可能とする。情報出力処理では、ホール管理コンピュータに供給される所定のデータを出力する。遊技用乱数更新処理では、遊技用乱数の少なくとも一部をソフトウェアにより更新する。特別図柄プロセス処理では、特別図柄の表示制御や大入賞口の開閉動作設定などを、所定の手順で行うために、各種の処理が選択されて実行される。普通図柄プロセス処理では、普通図柄の表示制御や普通可変入賞球装置6Bにおける可動翼片の傾動動作設定などを、所定の手順で行うために、各種の処理が選択されて実行される。20

#### 【0033】

特別図柄プロセス処理では、まず、始動入賞判定処理が実行される。始動入賞判定処理を実行した後には、特図プロセスフラグの値に応じて選択した処理が実行される。このとき選択可能な処理は、特別図柄通常処理、変動パターン設定処理、特別図柄変動処理、特別図柄停止処理、大当たり開放前処理、大当たり開放中処理、大当たり開放後処理、大当たり終了処理などを含んでいればよい。30

#### 【0034】

始動入賞判定処理では、第1始動入賞や第2始動入賞が発生したか否かを判定し、発生した場合には特図保留記憶数を更新するための設定などが行われる。特別図柄通常処理では、特図ゲームの実行を開始するか否かの判定が行われる。また、特別図柄通常処理では、特別図柄や飾り図柄の可変表示結果を「大当たり」とするか否かの判定が行われる。さらに、特別図柄通常処理では、可変表示結果に対応して、特図ゲームにおける確定特別図柄の設定などが行われる。変動パターン設定処理では、可変表示結果などに基づいて、変動パターンの決定などが行われる。特別図柄変動処理では、特別図柄を変動させるための設定や、変動開始からの経過時間を計測するための設定などが行われる。特別図柄停止処理では、特別図柄の変動を停止させ、可変表示結果となる確定特別図柄を停止表示（導出）させるための設定などが行われる。40

#### 【0035】

大当たり開放前処理では、可変表示結果が「大当たり」に対応して、大当たり遊技状態において大入賞口を開放状態とするための設定などが行われる。大当たり開放中処理では、大入賞口を開放状態から閉鎖状態に戻すか否かの判定などが行われる。大当たり開放後処理では、50

大入賞口を閉鎖状態に戻した後、ラウンドの実行回数が上限値に達したか否かを判定し、達していないければ次回のラウンドを実行可能とし、達していれば大当たり遊技状態を終了させるための設定などが行われる。大当たり終了処理では、大当たり遊技状態の終了を報知するエンディング演出の実行期間に対応した待ち時間が経過するまで待機した後、確変制御や時短制御を開始するための設定などが行われる。

#### 【0036】

演出制御基板12では、電源基板92からの電力供給が開始されると、演出制御用CPU120が演出制御メイン処理の実行を開始する。演出制御メイン処理では、所定の初期化が行われた後、タイマ割込みが発生する毎に、コマンド解析処理、演出制御プロセス処理、演出用乱数更新処理が実行される。10 コマンド解析処理では、主基板11から伝送された演出制御コマンドを解析し、解析結果に応じたフラグがセットされる。演出制御プロセス処理では、演出用の電気部品を所定の手順に従って制御するために、各種の処理が選択されて実行される。演出用乱数更新処理では、演出用乱数を生成するためのカウント値などをソフトウェアにより更新する。

#### 【0037】

演出制御プロセス処理では、まず、保留表示更新処理が実行される。保留表示更新処理を実行した後には、演出プロセスフラグの値に応じて選択した処理が実行される。このとき選択可能な処理は、可変表示開始待ち処理、可変表示開始設定処理、可変表示中演出処理、可変表示停止処理、大当たり表示処理、大当たり中演出処理、エンディング演出処理などを含んでいればよい。20

#### 【0038】

保留表示更新処理では、保留記憶表示エリア5Hの表示を、特図保留記憶数に応じて更新するための設定などが行われる。可変表示開始待ち処理では、特別図柄や飾り図柄の可変表示を開始するか否かの判定などが行われる。可変表示開始設定処理では、飾り図柄の可変表示を開始するための設定などが行われる。可変表示中演出処理では、飾り図柄の可変表示に対応して、演出用の電気部品を演出制御パターンに従って制御するための設定などが行われる。可変表示停止処理では、飾り図柄の可変表示を停止して可変表示結果となる確定飾り図柄を導出する制御などが行われる。

#### 【0039】

大当たり表示処理では、可変表示結果が「大当たり」に対応して、大当たりの発生を報知する演出（ファンファーレ演出）を実行するための制御などが行われる。大当たり中演出処理では、大当たり遊技状態に対応して、演出用の電気部品を演出制御パターンに従って制御するための設定などが行われる。エンディング演出処理では、大当たり遊技状態の終了に対応して、エンディング演出の実行を制御するための設定などが行われる。30

#### 【0040】

図3は、パチンコ遊技機1が備える遊技機用枠3の背面図である。遊技機用枠3の背面に上部には、球タンク150、ターミナル基板154が設けられている。また、補給通路151、払出装置152、賞球通路153も設けられている。遊技盤2の背面には、遊技制御基板用の基板ケース400、演出制御基板用の基板ケース800、カバー体301が設けられている。基板ケース400は、主基板11を収納する。基板ケース800は、演出制御基板12を収納する。カバー体301は、透明な合成樹脂などを用いて構成され、基板ケース800と基板ケース400の上部とを覆っている。遊技制御基板用の基板ケース400の下方位置には、払出制御基板91と、電源基板92とが、前後に重畳するように設けられている。40

#### 【0041】

図4～図7を参照して、演出制御基板用の基板ケース800の構造を説明する。図4は、基板ケース800を左後部の斜め上方から見た状態を示す分解斜視図である。図5は、基板ケース800を右前部の斜め上方から見た状態を示す分解斜視図である。図6は、ベース部材801を示す6面図である。図7は、カバー部材802を示す6面図である。基板ケース800は、ベース部材801と、カバー部材802とから構成され、演出制御基50

板12を前後から挟持するように組み付けられる。ベース部材801は演出制御基板12の前面側を覆い、カバー部材802は演出制御基板12の背面側を覆う。

#### 【0042】

ベース部材801は、透明な熱可塑性合成樹脂からなり、縦長略長方形状に形成されるベース板801aと、上下及び左右側辺に背面側に向けて立設される側壁801b～801eとから構成され、背面側に向けて開口する箱状に形成されている。ベース板801aには、ボス803、804、係止バー805、係止フック806、係止孔807、被係止部808、ワンウェイネジ809のネジ穴810、取付孔811、基板支持用リブ812、813、段部814a、814b、リブ815が設けられている。

#### 【0043】

カバー部材802は、透明な熱可塑性合成樹脂からなり、縦長略長方形状に形成されるベース板821aと、上下及び左右側辺に背面側に向けて立設される側壁821b～821eとから構成され、背面側に向けて開口する箱状に形成されている。ベース板821aには、ネジ822が螺入されるネジ穴823、位置決め凸部824、ネジ825が螺入されるネジ穴826、位置決め凸部827、係止フック831、係止片832、係止部833、ワンウェイネジ809の取付孔834aが形成された取付片834、音量調整用スイッチ835aを外部に臨ませるスイッチ用開口835、コネクタ用開口836、837が設けられている。

#### 【0044】

コネクタ用開口836は、ベース板821aの上部右側にて、第1基板12Aに搭載された各種基板側コネクタKCN10を外部に臨ませるために、縦長形状となるように形成されている。各種基板側コネクタKCN10は、レセプタクルKRE1～KRE4を含んでいればよい。レセプタクルKRE1は、主基板配線用のコネクタポートである。レセプタクルKRE2は、電源基板配線用のコネクタポートである。レセプタクルKRE3は、ドライバ基板配線用のコネクタポートである。レセプタクルKRE4は、音声制御基板配線用のコネクタポートである。なお、レセプタクルの配置や接続される配線は、パチンコ遊技機1の仕様に応じて任意に変更されたものであってもよい。

#### 【0045】

主基板配線用のレセプタクルKRE1は、主基板11との間で電気的に接続される信号配線（主基板配線）を着脱自在に接続可能な配線接続装置の構成を有している。電源基板配線用のレセプタクルKRE2は、電源基板92との間で電気的に接続される信号配線（電源基板配線）を着脱自在に接続可能な配線接続装置の構成を有している。ドライバ基板配線用のレセプタクルKRE3は、ドライバ基板19との間で電気的に接続される信号配線（ドライバ基板配線）を着脱自在に接続可能な配線接続装置の構成を有している。音声制御基板配線用のレセプタクルKRE4は、音声制御基板13との間で電気的に接続される信号配線（音声制御基板配線）を着脱自在に接続可能な配線接続装置の構成を有している。

#### 【0046】

（特徴部30AKに関する説明）

図8は、本実施形態の特徴部30AKに関し、主基板11における一方の基板面（表面）にて、CPU103とRAM102とを接続する配線のパターンが形成された部分の構成例を示している。主基板11では、例えばRAM102とCPU103といった、複数の電気部品を複数の信号配線により接続するために、複数の信号配線を構成する配線のパターンが形成されている。CPU103は、パチンコ遊技機1における遊技の制御について、所定の処理を実行可能に構成された電気部品であり、RAM102はCPU103による処理の実行に関する情報を記憶可能に構成された電気部品である。

#### 【0047】

複数の信号配線を構成する配線のパターンに対し、それらの周囲あるいは信号配線間ににおける領域にて、1または複数のグランド導体が配置されている。グランド導体は、基準グランドや特性インピーダンス調整用グランドとして機能し、グランド電圧に維持される

10

20

30

40

50

。図8に示す構成例では、複数のグランド導体として、複数の信号配線の周囲における領域にグランド導体30AK10Gおよびグランド導体30AK11Gが配置され、複数の信号配線間における領域にグランド導体30AK20Gが配置されている。このように、複数の信号配線を構成する配線のパターンが設けられていない空白領域となる空域部分には、1または複数のグランド導体が設けられていてもよい。これにより、複数の信号配線から放射される電磁波ノイズや信号配線間での電磁波ノイズによる電磁妨害を、防止あるいは抑制できる。

#### 【0048】

なお、複数の信号配線の周囲および信号配線間における双方の領域に複数のグランド導体が配置されるものに限定されず、複数の信号配線の周囲または信号配線間における一方の領域にのみグランド導体が配置されるものであってもよい。あるいは、このようなグランド導体が配置されないものであってもよい。

10

#### 【0049】

図9は、図8に示した複数の信号配線を構成する配線のパターンについて、より詳細に説明するための領域や区間を示している。図9に示す領域30AK01Rは、複数の信号配線がCPU103に接続される側の端部における領域である。図9に示す領域30AK10Rは、複数の信号配線がいずれも直線形状または略直線形状で互いに平行または略平行な第1形状となる領域であり、図9に示す領域30AK11Rと領域30AK12Rは、少なくとも一部の信号配線が直線形状および略直線形状とは異なる形状で他の信号配線と平行および略平行ではない第2形状となる領域である。図9に示す区間30AK0SCでは、複数の信号配線のうち一部の信号配線が最短または略最短の距離で接続する短距離パターンと短距離パターンに含まれない信号配線が短距離パターンよりも長い距離で接続する長距離パターンとが配置されている。

20

#### 【0050】

図10は、図9に示された領域30AK01Rの拡大図である。図10に示す領域30AK01Rにおいて、複数の信号配線を構成する配線のパターンは、パターン30AK10D～30AK13Dと、パターン30AK10CKと、パターン30AK10CSと、パターン30AK10RSと、パターン30AK10A～30AK14Aとを含んでいる。

#### 【0051】

30

図11は、図10に示された配線のパターンに対応して、信号種類、信号同期の有無、蛇行形状の有無についての設定例を示している。図11に示す信号種類は、各配線のパターンが構成する信号配線で伝送される電気信号の内容（用途）を示している。図11に示す信号同期は、他の信号配線で伝送される電気信号に対する同期の有無を示している。図11に示す蛇行形状は、RAM102とCPU103との間を接続する各配線のパターンについて、直線形状および略直線形状とは異なる蛇行形状となる部分が設けられているか否かを示している。蛇行形状は、ミアンダ形状やジグザグ形状、あるいは折返し形状とも称され、所定区間における信号配線の延設方向に対し、信号配線が繰り返し折り曲げられることにより、例えば延設方向に直交あるいは略直交する方向に折返し往復する形状であればよい。

40

#### 【0052】

図11に示す設定例において、配線のパターン30AK10D～30AK13Dは、いずれもデータ信号を伝送するための信号配線を構成する。各信号配線で伝送されるデータ信号は、例えばクロック信号および他の信号配線で伝送されるデータ信号といった、他の信号配線で伝送される信号と同期して伝送される。配線のパターン30AK10CKは、クロック信号を伝送するための信号配線を構成する。クロック信号は、例えばデータ信号やアドレス信号、チップセレクト信号といった、他の信号配線で伝送される信号と同期して伝送される。配線のパターン30AK10CSは、チップセレクト信号を伝送するための信号配線を構成する。チップセレクト信号は、例えばクロック信号といった、他の信号配線で伝送される信号と同期して伝送される。配線のパターン30AK10RSは、リセ

50

ット信号を伝送するための信号配線を構成する。リセット信号は、他の信号配線で伝送される信号とは同期しない非同期で伝送される。配線のパターン 30 A K 10 A ~ 30 A K 14 A は、いずれもアドレス信号を伝送するための信号配線を構成する。各信号配線で伝送されるアドレス信号は、例えばクロック信号および他の信号配線で伝送されるアドレス信号といった、他の信号配線で伝送される信号と同期して伝送される。

#### 【0053】

他の信号配線で伝送される信号と同期して伝送されるデータ信号、クロック信号、チップセレクト信号、アドレス信号のうちデータ信号を伝送するための信号配線を構成する配線のパターン 30 A K 10 D ~ 30 A K 13 D には、蛇行形状がない配線のパターン 30 A K 10 D が含まれている。配線のパターン 30 A K 10 D が構成する信号配線で伝送されるデータ信号とは異なるデータ信号、クロック信号、チップセレクト信号、アドレス信号を伝送するための信号配線を構成する配線のパターンは、少なくとも一部分が直線形状および略直線形状とは異なる形状としての蛇行形状となっている。10

#### 【0054】

配線のパターン 30 A K 10 D が構成するデータ信号を伝送するための信号配線は、他のデータ信号、クロック信号、チップセレクト信号、アドレス信号を伝送するための信号配線に比べて、RAM 102 と CPU 103 における接続端子間の距離が長くなっている。そこで、配線のパターン 30 A K 10 D が構成する信号配線で伝送されるデータ信号とは異なるデータ信号、クロック信号、チップセレクト信号、アドレス信号を伝送するための信号配線を構成する配線のパターンは、少なくとも一部分が蛇行形状となることにより、各信号配線の配線長が同一または略同一となる。その一方で、配線のパターン 30 A K 10 D には蛇行形状を設ける必要がない。20

#### 【0055】

このように、同期信号を伝送するための信号配線のうち複数の電気部品における接続端子間の距離が他の接続端子間の距離と比べて長くなる信号配線は、例えば蛇行形状となる配線部分といった、直線形状および略直線形状とは異なる形状となる配線部分を含まないように、配線のパターンが形成されていればよい。逆にいうと、直線形状または略直線形状などの形状となる一方で蛇行形状のような直線形状および略直線形状とは異なる形状を含まない配線のパターンが構成する信号配線は、蛇行形状のような直線形状および略直線形状とは異なる形状を含む配線のパターンが構成する信号配線と比較して、複数の電気部品における接続端子間の距離が長い。あるいは、同期信号を伝送するための信号配線のうち複数の電気部品における接続端子間の距離が他の接続端子間の距離と比べて長くなる信号配線は、例えば蛇行形状となる配線部分といった、他の信号配線と平行および略平行な形状とは異なる形状となる配線部分を含まないように、配線のパターンが形成されていればよい。逆にいうと、他の信号配線と平行または略平行な形状となる一方で蛇行形状のような平行および略平行な形状とは異なる形状を含まない配線のパターンが構成する信号配線は、蛇行形状のような他の信号配線と平行および略平行な形状とは異なる形状を含む配線のパターンが構成する信号配線と比較して、複数の電気部品における接続端子間の距離が長い。これにより、各信号配線の配線長を同一または略同一とし、複数の信号配線で伝送される信号の遅延時間差（スキー）が発生することを、防止あるいは抑制できる。複数の信号配線で伝送される信号の遅延時間差を減少させることにより、複数の信号配線で伝送される信号の信頼性を向上させることができる。3040

#### 【0056】

配線のパターン 30 A K 10 R S には、蛇行形状が設けられていない。配線のパターン 30 A K 10 R S は、非同期信号であるリセット信号を伝送するための信号配線を構成する。リセット信号などの非同期信号を伝送する場合には、他の信号配線で伝送される信号との遅延時間差を考慮する必要がない。そこで、リセット信号を伝送するための信号配線を構成する配線のパターン 30 A K 10 R S のように、非同期信号が伝送される信号配線を構成する配線のパターンには蛇行形状を設けない。配線のパターンに蛇行形状を設けないようにすれば、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化50

を図ることができる。

#### 【0057】

蛇行形状を設けない配線のパターンとして、グランド電圧に維持されるダミー配線を構成する配線のパターンが配置されてもよい。例えば配線のパターン30AK10RSが構成する信号配線では、リセット信号が伝送されることに代えて、グランド電圧に維持されてもよい。配線のパターン30AK10RSは、データ信号を伝送するための信号配線を構成する配線のパターン30AK10D～30AK13D、クロック信号を伝送するための信号配線を構成する配線のパターン30AK10CK、チップセレクト信号を伝送するための信号配線を構成する配線のパターン30AK10CSで構成される一群のパターンと、アドレス信号を伝送するための信号配線を構成する配線のパターン30AK10A～30AK14Aで構成される一群のパターンとの間に配置されている。配線のパターン30AK10RSのような他の信号配線間に配置される信号配線をグランド電圧に維持されるダミー配線とすることにより、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。10 蛇行形状を設けない配線のパターンとしては、グランド電圧に維持されるダミー配線とともに、電源電圧に維持される配線のパターンが配置されてもよい。例えば配線のパターン30AK10RSが構成する信号配線では、リセット信号が伝送されることに代えて、電源電圧に維持されてもよい。なお、電源電圧に維持される配線のパターンは、他の信号配線を構成する配線のパターンと近接して配置すると、それぞれの信号配線どうしの電磁結合などにより、電磁波ノイズが発生するおそれがある。そこで、電源電圧に維持される配線のパターンを配置する場合には、グランド電圧に維持される配線のパターンを配置する場合と比較して、信号配線からの距離が長くなるように、各配線のパターンが形成されてもよい。20 これにより、信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。

#### 【0058】

図12は、図9に示された領域30AK10Rの拡大図である。領域30AK10Rには、配線のパターン30AK10CK、30AK10CS、30AK10RS、30AK10A～14Aが形成されている。これらの配線のパターンは、領域30AK10Rにおいて、複数の信号配線がいずれも直線形状または略直線形状で互いに平行または略平行な形状となるように形成されている。このように、領域30AK10Rでは、複数の信号配線を構成する配線のパターンがいずれも直線形状または略直線形状となるように形成され、複数の信号配線が互いに平行または略平行な形状となるように配線のパターンが形成されている。30

#### 【0059】

図13は、図9に示された領域30AK11Rの拡大図である。領域30AK11Rには、領域30AK10Rと同じく、配線のパターン30AK10CK、30AK10CS、30AK10RS、30AK10A～14Aが形成されている。これらの配線のパターンは、領域30AK11Rにおいて、少なくとも1の信号配線が直線形状または略直線形状となるように形成されている一方で、他の信号配線が直線形状および略直線形状とは異なる形状となるように形成されている。図13に示す領域30AK11Rにおいて、例えばクロック信号を伝送するための信号配線を構成する配線のパターン30AK10CK、チップセレクト信号を伝送するための信号配線を構成する配線のパターン30AK10CSは、複数の折り曲げ部を含むものの、いずれも直線形状または略直線形状となるように形成されている。また、図13に示す領域30AK11Rにおいて、リセット信号を伝送するための信号配線を構成する配線のパターン30AK10RSは、折り曲げ部を含まない直線形状または略直線形状となるように形成されている。これに対し、図13に示す領域30AK11Rにおいて、アドレス信号を伝送するための信号配線を構成する配線のパターン30AK10A～30AK14Aは、複数の折り曲げ部により蛇行形状が形成され、直線形状および略直線形状とは異なる形状となるように形成されている。40

#### 【0060】

蛇行形状が形成される部分では、例えば複数の折り曲げ部を介することにより、信号配線が本来の延設方向に対して直交する方向へと屈曲されなければよい。各折り曲げ部では、信号配線が直角よりも大きい角度（鈍角）をなすように折り曲げられることにより、信号配線の延設方向が変更された配線のパターンが形成されなければよい。この場合に、各折り曲げ部における折り曲げ量は、直角よりも小さい角度となるように、信号配線が折り曲げられる。蛇行形状が形成される部分では、第1延設方向と、この第1延設方向に対して直交または略直交する第2延設方向とに、信号配線を延設可能とし、第1延設方向の信号配線を構成する配線のパターンと、第2延設方向の信号配線を構成する配線のパターンとの間には、複数の折り曲げ部が設けられていればよい。このように、信号配線の折り曲げ量が所定角度よりも小さい角度となる複数の折り曲げ部を介して信号配線の延設方向が変更される。折り曲げ量を小さくすることにより、折り曲げ部における配線のパターン幅が大きく変化してしまうことを抑制し、伝送路の特性インピーダンスが急変することを防止して、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。

。

#### 【0061】

各信号配線では、折り曲げ部の位置が他の信号配線における折り曲げ部の位置から所定長より長い距離となるように、複数の折り曲げ部が配置されなければよい。所定長は、例えば2mm～5mmの範囲に含まれる一定長といった、基板設計上の観点から予め定められた長さであればよい。信号配線の折り曲げ部では、特性インピーダンスの変化などにより、電磁波ノイズが発生しやすくなる。複数の信号配線に含まれる1の信号配線を構成する配線のパターンが形成する折り曲げ部は、複数の信号配線に含まれる他の信号配線を構成する配線のパターンが形成する折り曲げ部と接近して配置されると、各信号配線で伝送される信号が電磁波ノイズの影響を受けやすくなるおそれがある。そこで、複数の信号配線に含まれる1の信号配線を構成する配線のパターンが形成する折り曲げ部と、複数の信号配線に含まれる他の信号配線を構成する配線のパターンが形成する折り曲げ部とが、所定長より長い距離となるように間隔をあけて配置することにより、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。

。

#### 【0062】

また、領域30AK11Rでは、少なくとも1の信号配線が平行および略平行とは異なる形状となるように形成されている。図13に示す領域30AK11Rにおいて、例えばクロック信号を伝送するための信号配線を構成する配線のパターン30AK10CKと、チップセレクト信号を伝送するための信号配線を構成する配線のパターン30AK10CSは、いずれも複数の折り曲げ部を介しながら、全体として互いの信号配線が平行または略平行な形状となるように形成されている。これに対し、図13に示す領域30AK11Rにおいて、アドレス信号を伝送するための信号配線を構成する配線のパターン30AK10A～30AK14Aは、複数の折り曲げ部により蛇行形状が形成されているので、全体として互いの信号配線が平行または略平行とは異なる形状となるように形成されている。

。

#### 【0063】

図13に示す領域30AK11Rでは、複数の信号配線のうち少なくとも1の信号配線が、平行および略平行な形状とは異なる蛇行形状などの形状となっている。この領域30AK11Rにおいて、信号配線を構成する配線のパターンに近接するスペース領域30AK0SPには、少なくとも信号配線と同一の基板上で導体が設けられていない。スペース領域30AK0SPは、例えばアドレス信号を伝送するための信号配線を構成する配線のパターン30AK10A～30AK14Aのうち領域30AK11Rにて蛇行形状が設けられた配線のパターン30AK10A～30AK13Aに近接している。スペース領域30AK0SPには導体が設けられていないことにより、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。蛇行形状となる配線のパターンに近接する領域に導体が設けられている場合には、信号配線から電磁波が放射される可能性があり、信号配線と導体との電磁結合などにより、電磁波ノイズが発生するおそれがある。そこ

。

で、例えばスペース領域 30AK0SP のように、蛇行形状が設けられた配線のパターンに近接する領域には導体が設けられないことで、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。

#### 【0064】

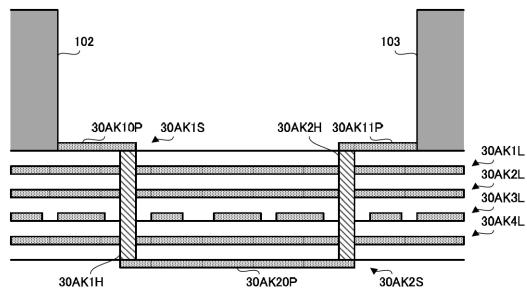

図14は、多層配線基板として形成された主基板11の構成例を示す断面図である。図14に示す主基板11は、合成樹脂を重ねて形成された多層構造を有し、各層の表面または内層には様々な配線のパターンを形成可能とされている。このような多層構造を有する主基板11に形成された配線のパターンを介して、例えばRAM102とCPU103といった、複数の電子部品が電気的に接続される。図14に示す主基板11の多層構造は、表面層30AK1Sと、グランド層30AK1Lと、電源層30AK2Lと、配線層30AK3Lと、電源層30AK4Lと、裏面層30AK2Sとを含んでいる。

10

#### 【0065】

主基板11における一方の基板面となる表面には、表面層30AK1Sが設けられ、信号配線を構成する配線のパターン30AK10Pおよびパターン30AK11Pが形成されている。主基板11における他方の基板面となる裏面には、裏面層30AK2Sが設けられ、信号配線を構成する配線のパターン30AK20Pが形成されている。主基板11の表面層30AK1Sに形成された配線のパターン30AK10Pは、主基板11の表面層30AK1Sおよび裏面層30AK2Sを貫通するスルーホール30AK1Hを介して、裏面層30AK2Sに形成された配線のパターン30AK20Pと電気的に接続されている。主基板11の表面層30AK1Sに形成された配線のパターン30AK11Pは、主基板11の表面層30AK1Sおよび裏面層30AK2Sを貫通するスルーホール30AK2Hを介して、裏面層30AK2Sに形成された配線のパターン30AK20Pと電気的に接続されている。このように、主基板11には、一方の基板面となる表面に設けられた表面層30AK1Sにおいて信号配線を構成する配線のパターン30AK10Pおよびパターン30AK11Pと、他方の基板面となる裏面に設けられた裏面層30AK2Sにおいて信号配線を構成する配線のパターン30AK20Pとを、電気的に接続可能なスルーホール30AK1Hおよびスルーホール30AK2Hが設けられている。

20

#### 【0066】

図14に示すRAM102とCPU103を接続する複数の信号配線に含まれる各信号配線の配線長は、表面層30AK1Sに形成された配線のパターン30AK10Pおよびパターン30AK11Pと、裏面層30AK2Sに形成された配線のパターン30AK20Pとが構成する信号配線の配線長だけでなく、スルーホール30AK1Hおよびスルーホール30AK2Hの長さを含めて、同一または略同一となる。図14に示す多層構造を有する主基板11において、スルーホール30AK1Hおよびスルーホール30AK2Hの長さを含めて、各信号配線の配線長を同一または略同一とし、複数の信号配線で伝送される信号の遅延時間差が発生することを、防止あるいは抑制できる。主基板11のような多層配線基板において複数の信号配線で伝送される信号の遅延時間差を減少させることにより、複数の信号配線で伝送される信号の信頼性を向上させることができる。

30

#### 【0067】

図14に示す多層構造を有する主基板11において、表面層30AK1Sに隣接する導体層として、グランド層30AK1Lが設けられている。グランド層30AK1Lには、1または複数のグランド導体が配置され、グランド導体はグランド電圧に維持される。表面層30AK1Sにおいて信号配線を構成する配線のパターン30AK10Pおよびパターン30AK11Pは、少なくともいずれか一方のパターンにおいて、蛇行形状といった、直線形状および略直線形状とは異なる形状で複数の信号配線が平行および略平行な形状とは異なる形状となる領域を含むように形成されていればよい。このような表面層30AK1Sに隣接する導体層としてのグランド層30AK1Lでは、信号の伝送が行われない。配線のパターン30AK10Pおよびパターン30AK11Pが形成された表面層30AK1Sに隣接する導体層で信号の伝送が行われないので、配線のパターン30AK10Pおよびパターン30AK11Pが構成する複数の信号配線で伝送される信号が電磁波ノ

40

50

イズの影響を受けにくくなり、他の信号配線に電磁波ノイズの影響が及ぶことも、防止あるいは抑制できる。

**【0068】**

図14に示す多層構造を有する主基板11の裏面層30AK2Sにおいて信号配線を構成する配線のパターン30AK20Pが、蛇行形状といった、直線形状および略直線形状とは異なる形状で複数の信号配線が平行および略平行な形状とは異なる形状となる領域を含むように形成されてもよい。このような裏面層30AK2Sに隣接する導体層としての電源層30AK4Lでは、信号の伝送が行われない。電源層30AK4Lには、1または複数の電源導体が配置され、電源導体は電源電圧に維持される。配線のパターン30AK20Pが形成された裏面層30AK2Sに隣接する導体層で信号の伝送が行われないので、配線のパターン30AK20Pが構成する複数の信号配線で伝送される信号が電磁波ノイズの影響を受けにくくなり、他の信号配線に電磁波ノイズの影響が及ぶことも、防止あるいは抑制できる。主基板11のような多層配線基板において複数の信号配線が設けられる層に隣接する導体層では信号の伝送が行われないことににより、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。

10

**【0069】**

図14に示す多層構造を有する主基板11の配線層30AK3Lにおいて信号配線を構成する配線のパターンが、蛇行形状といった、直線形状および略直線形状とは異なる形状で複数の信号配線が平行および略平行な形状とは異なる形状となる領域を含むように形成されてもよい。このような配線層30AK3Lに隣接する導体層としての電源層30AK2Lや電源層30AK4Lでは、信号の伝送が行われない。主基板11のような多層配線基板において複数の信号配線が設けられる配線層30AK3Lに隣接する導体層では信号の伝送が行われないことにより、複数の信号配線での電磁波ノイズによる電磁妨害の防止あるいは抑制が図られる。ただし、多層配線基板に設けられた内層の導体層である配線層30AK3Lにおいて信号配線を構成する配線のパターンが蛇行形状などの形状となる領域を含むように形成された場合には、信号配線の断線などによる障害が発生した場合に、配線層30AK3Lにおける信号配線の状態を基板の外部から確認することが困難になるおそれがある。これに対し、主基板11の表面層30AK1Sや裏面層30AK2Sといった、主基板11が備える一方の基板面や他方の基板面において信号配線を構成する配線のパターンが蛇行形状などの形状となる領域を含むように形成された場合には、信号配線の断線などによる障害が発生した場合に、表面層30AK1Sや裏面層30AK2Sにおける信号配線の状態を基板の外部から確認しやすい適切な基板構成が可能になる。

20

**【0070】**

主基板11の表面層30AK1Sおよび裏面層30AK2Sを貫通するスルーホールは、図14に示すスルーホール30AK1Hおよびスルーホール30AK2Hに限定されず、より多くのスルーホールが設けられ、複数の信号配線における各信号配線の配線長を同一または略同一にするために用いられてもよい。複数の信号配線を構成する配線のパターンのうちには、スルーホール30AK1Hおよびスルーホール30AK2Hのようなスルーホールを介することなく、例えば主基板11の表面層30AK1Sのみに信号配線が配置されるように形成されたパターンが含まれてもよい。配線のパターン30AK10Dが構成するデータ信号を伝送するための信号配線といった、複数の電気部品における接続端子間の距離が他の接続端子間の距離と比べて長くなる信号配線は、スルーホール30AK1Hおよびスルーホール30AK2Hのようなスルーホールを介することなく、主基板11の表面層30AK1Sのみに信号配線が配置されてもよい。逆にいうと、表面層30AK1Sなど1の導体層にてスルーホールを介することなく形成された配線のパターンが構成する信号配線は、表面層30AK1Sおよび裏面層30AK2Sなど複数の導体層にてスルーホールを介して電気的に接続可能となるように形成された配線のパターンが構成する信号配線と比較して、複数の電気部品における接続端子間の距離が長い。

30

40

**【0071】**

複数の信号配線が隣接して設けられる場合には、図13に示したスペース領域30AK

50

0 S P のように、小さな空白領域が形成される。この空白領域にスルーホールを設け、例えばグランド層 3 0 A K 1 L といった他の導体層と電気的に接続されるように、銅などの導電材料が埋設されたスルーホール電極を有する構成とすることも考えられる。空白領域にスルーホール電極のような導体が設けられる構成では、例えば空白領域における電界分布を安定させるために、多数のスルーホール電極が配置される場合もある。この場合には、主基板 1 1 の表面層 3 0 A K 1 S のみでなく、裏面層 3 0 A K 2 S にも、例えばバンプといった、スルーホール電極に対応する構造物が配置され、基板上における配線パターンの設計が制約されるという不都合が生じるおそれがある。また、多層配線基板に設けられた内層の導体層であるグランド層 3 0 A K 1 L や電源層 3 0 A K 2 L 、 3 0 A K 4 L などでは、スルーホール電極が設けられる場合に、そのスルーホール電極の周囲では導体層のパターンを除去することになり、グランド層 3 0 A K 1 L や電源層 3 0 A K 2 L 、 3 0 A K 4 L など内層の導体層におけるパターンが分断され、導体層におけるパターンの設計が困難になるという不都合が生じるおそれがある。さらに、スルーホール電極に代えて、例えばダミーパッドのような導体が空白領域に設けられ、他の導体層とは接続されないような構成では、この導体が外部からの電磁波ノイズによる影響を受けたり、この導体が複数の信号配線に電磁波ノイズの影響を及ぼしたりして、電磁妨害などの悪影響を与える不都合が生じるおそれがある。これに対し、信号配線を構成する配線のパターンに近接するスペース領域 3 0 A K 0 S P には、導体が設けられないことにより、これらの不都合が生じることを、防止あるいは抑制できる。

## 【 0 0 7 2 】

その他、図 13 に示したスペース領域 3 0 A K 0 S P のように、複数の信号配線が隣接して設けられる場合に形成される空白領域には、例えば基板固定用のネジ穴といった、基板の構成材料とは異なる材料が用いられる構造物が設けられないようにしてよい。基板固定用のネジ穴が設けられた場合には、ネジ止めにより基板を固定した場合に、ネジの構成材料が外部からの電磁波ノイズによる影響を受け、他の信号配線にも電磁妨害などの悪影響を与える不都合が生じるおそれがある。また、基板に含まれる絶縁層とは誘電率が異なる合成樹脂や誘電材料を用いた構造物、あるいは基板に含まれる導体層とは電気伝導率が異なる合成樹脂や金属材料を用いた構造物が、複数の信号配線に近接した空白領域に設けられた場合には、これらの構造物が外部からの電磁波ノイズによる影響を受けたり、これらの構造物が複数の信号配線に電磁波ノイズの影響を及ぼしたりして、電磁妨害などの悪影響を与える不都合が生じるおそれがある。これに対し、信号配線を構成する配線のパターンに近接するスペース領域 3 0 A K 0 S P などの空白領域には、基板の構成材料とは異なる材料を用いた構造物が設けられないことにより、これらの不都合が生じることを、防止あるいは抑制できる。

## 【 0 0 7 3 】

図 9 に示す区間 3 0 A K 0 S C では、データ信号を伝送するための複数の信号配線を形成する配線のパターン 3 0 A K 1 0 D ~ 3 0 A K 1 3 D のうち 1 のパターン 3 0 A K 1 3 D が、蛇行形状といった、直線形状および略直線形状とは異なる形状で他の信号配線と平行および略平行な形状とは異なる形状となる信号配線の部分を含むように形成されている。これに対し、少なくともパターン 3 0 A K 1 0 D およびパターン 3 0 A K 1 1 D は、区間 3 0 A K 0 S C にて、蛇行形状を含むことなく、直線形状または略直線形状で互いの信号配線が平行または略平行な形状となるように形成されている。したがって、パターン 3 0 A K 1 0 D およびパターン 3 0 A K 1 1 D は、信号配線が区間 3 0 A K 0 S C を最短または略最短で接続するパターンとなる。これに対し、パターン 3 0 A K 1 2 D およびパターン 3 0 A K 1 3 D は、信号配線が区間 3 0 A K 0 S C をパターン 3 0 A K 1 0 D およびパターン 3 0 A K 1 1 D よりも長い距離で接続するパターンとなる。

## 【 0 0 7 4 】

区間 3 0 A K 0 S C にて、パターン 3 0 A K 1 3 D が構成する信号配線が蛇行形状などの直線形状および略直線形状とは異なる形状となっている部分では、他のパターン 3 0 A K 1 0 D ~ パターン 3 0 A K 1 2 D が構成する信号配線は直線形状または略直線形状とな

るようによく形成されている。このように、複数の信号配線を構成する配線のパターンのうち1の配線のパターンにより構成される信号配線が蛇行形状などの直線形状および略直線形状とは異なる形状となっている部分では、他の配線のパターンにより構成される信号配線が直線形状または略直線形状となるように形成されてもよい。1の配線のパターンにより構成される信号配線が蛇行形状などの直線形状および略直線形状とは異なる形状となる部分は、他の配線のパターンにより構成される信号配線が直線形状または略直線形状となる部分と重複しないように形成されてもよい。蛇行形状などの直線形状および略直線形状とは異なる形状となる部分が、複数の信号配線について重複しないように配線のパターンが形成されることにより、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

10

#### 【0075】

図15は、複数の信号配線が蛇行形状となる部分が重複しない配線のパターンについて、他の形成例を示している。図15に示す領域30AK20Rでも、複数の信号配線を構成する配線のパターンのうち1の配線パターンにより構成される信号配線が蛇行形状となっている部分では、他の配線のパターンにより構成される信号配線が直線形状または略直線形状となるように形成されている。そして、第1配線のパターンにより構成される第1信号配線が蛇行形状となる部分である第1蛇行部が終了すると、第1配線のパターンとは異なる第2配線のパターンにより構成される第2信号配線が蛇行形状となる部分である第2蛇行部が開始されるように、複数の信号配線を構成する配線のパターンが形成されている。第1蛇行部では、第1信号配線以外の信号配線を構成する配線のパターンとして、第2信号配線を構成する第2配線のパターンを含めた配線のパターンは、各パターンにより構成される信号配線が平行または略平行な形状となるように形成されればよい。第2蛇行部では、第2信号配線以外の信号配線を構成する配線のパターンとして、第1信号配線を構成する第1配線のパターンを含めた配線のパターンは、各パターンにより構成される信号配線が平行または略平行な形状となるように形成されればよい。第1蛇行部が終了してから第2蛇行部が開始されるので、第1蛇行部は第2蛇行部と重複しないように配置されている。これにより、多数の信号配線について蛇行形状などの直線形状および略直線形状とは異なる形状となる部分を設けた場合でも、配線のパターンを配置する基板面積の増大が可及的に抑制されて、基板の小型化を図ることができる。

20

#### 【0076】

30

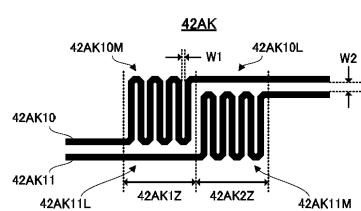

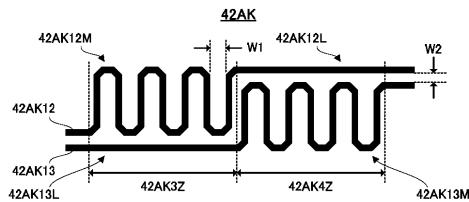

(特徴部42AKに関する説明)

図16は、本実施形態の特徴部42AKに関し、配線のパターンにより構成される複数の信号配線が形成された部分の構成例を示している。図16に示す配線のパターンは、例えば主基板11にて、RAM102とCPU103といった、複数の電気部品を接続する複数の信号配線を構成するものであればよい。図16に示す構成例では、複数の信号配線を構成する配線のパターンとして、2つの信号配線を構成する配線のパターンが示されている。図16(A)は配線間隔W1が配線間隔W2よりも狭いW1 < W2の場合を示し、図16(B)は配線間隔W1が配線間隔W2よりも広いW1 > W2の場合を示している。配線間隔W1は、同一の信号配線が蛇行形状となる部分における配線のパターンによる配線間隔である。配線間隔W2は、平行または略平行に隣接して互いに異なる信号配線を構成する配線のパターンどうしによる配線間隔である。

40

#### 【0077】

図16(A)に示す2つの信号配線を構成する配線のパターンは、配線の第1パターン42AK10と、配線の第2パターン42AK11とを含んでいる。配線の第1パターン42AK10および配線の第2パターン42AK11は、それらの配線のパターンにより構成される信号配線の形状に応じて、配線部42AK1Zと、配線部42AK2Zとが含まれるように、各信号配線を形成している。

#### 【0078】

配線部42AK1Zでは、配線の第1パターン42AK10により構成される信号配線が第2形状部42AK10Mを形成し、配線の第2パターン42AK11により構成され

50

る信号配線が第1形状部42AK11Lを形成している。配線部42AK2Zでは、配線の第1パターン42AK10により構成される信号配線が第1形状部42AK10Lを形成し、配線の第2パターン42AK11により構成される信号配線が第2形状部42AK11Mを形成している。第1形状部42AK10L、42AK11Lは、信号配線が直線形状または略直線形状の第1形状となるように形成されている。第2形状部42AK10M、42AK11Mは、信号配線が蛇行形状といった、直線形状および略直線形状とは異なる第2形状となるように形成されている。なお、第2形状部42AK10M、42AK11Mは、蛇行形状に限定されず、直線形状および略直線形状とは異なる任意の形状となるように形成されればよい。

## 【0079】

10

このように、配線の第1パターン42AK10および配線の第2パターン42AK11により構成される複数の信号配線は、配線部42AK1Zにて、配線の第2パターン42AK11により構成される信号配線が、直線形状または略直線形状の第1形状となる第1形状部42AK11Lに対応して、配線の第1パターン42AK10により構成される信号配線が、第1形状部42AK11Lとは異なる蛇行形状などの第2形状となる第2形状部42AK10Mを含んでいる。すなわち、配線部42AK1Zでは、配線の第2パターン42AK11により構成される信号配線における第1形状部42AK11Lに対応して、配線の第1パターン42AK10により構成される信号配線が第2形状部42AK11Mを含んでいる。

## 【0080】

20

また、配線の第1パターン42AK10および配線の第2パターン42AK11により構成される複数の信号配線は、配線部42AK2Zにて、配線の第1パターン42AK10により構成される信号配線が、直線形状または略直線形状の第1形状となる第1形状部42AK10Lに対応して、配線の第2パターン42AK11により構成される信号配線が、第1形状部42AK10Lとは異なる蛇行形状などの第2形状となる第2形状部42AK11Mを含んでいる。すなわち、配線部42AK2Zでは、配線の第1パターン42AK10により構成される信号配線における第1形状部42AK10Lに対応して、配線の第2パターン42AK11により構成される信号配線が第2形状部42AK11Mを含んでいる。

## 【0081】

30

図16(A)に示す信号配線が蛇行形状などの第2形状となる第2形状部42AK10Mおよび第2形状部42AK11Mは、第2形状部42AK10Mが配線部42AK1Zに含まれ、第2形状部42AK11Mが配線部42AK2Zに含まれるように形成されている。これにより、第2形状部42AK10Mおよび第2形状部42AK11Mは、それぞれの配置が互いに重複しない。加えて、各信号配線の配線長は同一または略同一となるように形成されている。このような第2形状部42AK10Mと第2形状部42AK11Mとが含まれるように、配線の第1パターン42AK10および配線の第2パターン42AK11により構成される信号配線が形成されているので、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

## 【0082】

40

図16(B)に示す2つの信号配線を構成する配線のパターンは、配線の第3パターン42AK12と、配線の第4パターン42AK13とを含んでいる。配線の第3パターン42AK12および配線の第4パターン42AK13は、それらの配線のパターンにより構成される信号配線の形状に応じて、配線部42AK3Zと、配線部42AK4Zとが含まれるように、各信号配線を形成している。

## 【0083】

配線の第3パターン42AK12および配線の第4パターン42AK13により構成される信号配線は、配線部42AK3Zにて、配線の第4パターン42AK13により構成される信号配線が、直線形状または略直線形状の第1形状となる第1形状部42AK13Lに対応して、配線の第3パターン42AK12により構成される信号配線が、第1形状

50

部42AK13Lとは異なる蛇行形状などの第2形状となる第2形状部42AK12Mを含んでいる。すなわち、配線部42AK3Zでは、配線の第4パターン42AK13により構成される信号配線における第1形状部42AK13Lに対応して、配線の第3パターン42AK12により構成される信号配線が第2形状部42AK12Mを含んでいる。

#### 【0084】

また、配線の第3パターン42AK12および配線の第4パターン42AK13により構成される信号配線は、配線部42AK4Zにて、配線の第3パターン42AK12により構成される信号配線が、直線形状または略直線形状の第1形状となる第1形状部42AK12Lに対応して、配線の第4パターン42AK13により構成される信号配線が、第1形状部42AK12Lとは異なる蛇行形状などの第2形状となる第2形状部42AK13Mを含んでいる。すなわち、配線部42AK4Zでは、配線の第3パターン42AK12により構成される信号配線における第1形状部42AK12Lに対応して、配線の第4パターン42AK13により構成される信号配線が第2形状部42AK13Mを含んでいる。10

#### 【0085】

図16(B)に示す信号配線が蛇行形状などの第2形状となる第2形状部42AK12Mおよび第2形状部42AK13Mは、第2形状部42AK12Mが配線部42AK3Zに含まれ、第2形状部42AK13Mが配線部42AK4Zに含まれるように形成されている。これにより、第2形状部42AK12Mおよび第2形状部42AK13Mは、それぞれの配置が互いに重複しない。加えて、各信号配線の配線長は同一または略同一となるように形成されている。このような第2形状部42AK12Mと第2形状部42AK13Lとが含まれるように、配線の第3パターン42AK12および配線の第4パターン42AK13により構成される信号配線が形成されているので、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。20

#### 【0086】

図16(A)に示す構成例では、配線間隔W1よりも配線間隔W2の方が広くなるように、各信号配線が形成されている。例えば第2形状部42AK10Mや第2形状部42AK11Mでは、折り曲げ部により折り返された同一の信号配線が配線間隔W1で往復する蛇行形状を形成しているのに対し、配線の第1パターン42AK10により構成される信号配線と配線の第2パターン42AK11により構成される信号配線とが互いに平行または略平行であるときに隣接する信号配線どうしの配線間隔W2は、配線間隔W1よりも広くなるように、各信号配線が形成されている。このように、同一の信号配線における配線間隔W1よりも隣接する信号配線どうしの配線間隔W2の方が広くなるので、1の信号配線にて発生した短絡などによる悪影響が、他の信号配線にて伝送される信号に及ぶことを、防止あるいは抑制できる。30

#### 【0087】

図16(B)に示す構成例では、配線間隔W1よりも配線間隔W2の方が狭くなるように、各信号配線が形成されている。例えば第2形状部42AK12Mや第2形状部42AK13Mでは、折り曲げ部により折り返された同一の信号配線が配線間隔W1で往復する蛇行形状を形成しているのに対し、配線の第3パターン42AK12により構成される信号配線と配線の第4パターン42AK13により構成される信号配線とが互いに平行または略平行であるときに隣接する信号配線どうしの配線間隔W2は、配線間隔W1よりも狭くなるように、各信号配線が形成されている。このように、同一の信号配線における配線間隔W1よりも隣接する信号配線どうしの配線間隔W2の方が狭くなるので、1の信号配線の内部における短絡よりも、1の信号配線と他の信号配線との間ににおける短絡の方が、発生しやすくなる。1の信号配線と他の信号配線との間で発生した短絡は、各信号配線に設けられたテストポイントを用いて容易に検出することができる。例えば各信号配線に設けられたテストポイントにテストプローブを接触させて信号配線の電気特性検査を行うことにより、1の信号配線と他の信号配線との間で発生した短絡を検出することができる。40

#### 【0088】

50

図16(A)に示すように、一方では、配線の第2パターン42AK11により構成される信号配線が第1形状部42AK11Lを形成している配線部42AK1Zに対応して、配線の第1パターン42AK10により構成される信号配線が第2形状部42AK10Mを形成している。他方では、配線の第1パターン42AK10により構成される信号配線が第1形状部42AK10Lを形成している配線部42AK1Zに対応して、配線の第2パターン42AK11により構成される信号配線が第2形状部42AK11Mを形成している。図16(B)に示すように、一方では、配線の第4パターン42AK13により構成される信号配線が第1形状部42AK13Lを形成している配線部42AK3Zに対応して、配線の第3パターン42AK12により構成される信号配線が第2形状部42AK12Mを形成している。他方では、配線の第3パターン42AK12により構成される信号配線が第1形状部42AK12Lを形成している配線部42AK4Zに対応して、配線の第4パターン42AK13により構成される信号配線が第2形状部42AK13Mを形成している。各配線のパターンにより構成される各信号配線の対応関係は、例えば主基板11などの基板面に垂直な方向からみて、上下関係、左右関係、あるいは所定距離未満の範囲内といった、予め定めた任意の位置範囲内にある信号配線であれば成立し、そのような位置範囲内にない信号配線であれば不成立となる関係であればよい。

#### 【0089】

図16(A)や図16(B)に示す例では、1の配線のパターンにより構成される信号配線における第1形状部に対応して他の配線のパターンにより構成される信号配線が第2形状を形成している配線部と、他の配線のパターンにより構成される信号配線における第1形状部に対応して1の配線のパターンにより構成される信号配線が第2形状を形成している配線部とにおいて、配線間隔W1が共通であり配線間隔W2も共通となるように、各信号配線が形成されている。より具体的には、図16(A)に示す配線の第2パターン42AK11により構成される信号配線における第1形状部42AK11Lに対応して、配線の第1パターン42AK10により構成される信号配線が第2形状部42AK10Mを形成している配線部42AK1Zと、配線の第1パターン42AK10により構成される信号配線における第1形状部42AK10Lに対応して、配線の第2パターン42AK11により構成される信号配線が第2形状部42AK11Mを形成している配線部42AK2Zとにおいて、配線間隔W1が共通(一定)であり配線間隔W2も共通(一定)となるように、各信号配線が形成されている。これにより、基板面における配線のパターン設計が容易になる。また、複数の信号配線における形状の相違が抑制されるので、各信号配線における特性インピーダンスのばらつきを抑制して、複数の信号配線における信号品質の均質化が図られる。

#### 【0090】

なお、1の配線のパターンにより構成される信号配線における第1形状部に対応して他の配線のパターンにより構成される信号配線が第2形状を形成している配線部と、他の配線のパターンにより構成される信号配線における第1形状部に対応して1の配線のパターンにより構成される信号配線が第2形状を形成している配線部とでは、配線間隔W1と配線間隔W2の一方または双方が相違するよう、各信号配線が形成されてもよい。例えば図16(A)に示す配線部42AK1Zと配線部42AK2Zとにおいて、配線間隔W2は共通とする一方で、配線間隔W1は配線部42AK1Zよりも配線部42AK2Zの方が広くなるように、各信号配線が形成されてもよい。こうした場合には、基板面における配線のパターン設計を柔軟に行うことができる。

#### 【0091】

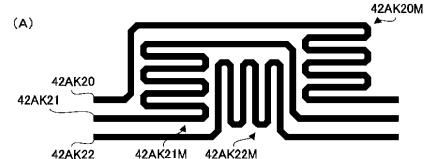

図17は、配線のパターンにより構成される複数の信号配線における第2形状部が異なる方向に形成されている構成例を示している。図17(A)に示す構成例では、複数の信号配線を構成する配線のパターンとして、3つの信号配線を構成する配線のパターンが示されている。図17(B)に示す構成例では、複数の信号配線を構成する配線のパターンとして、4つの信号配線を構成する配線のパターンが示されている。

#### 【0092】

10

20

30

40

50

図17(A)に示す3つの信号配線を構成する配線のパターンは、配線の第1パターン42AK20、配線の第2パターン42AK21、配線の第3パターン42AK22を含んでいる。配線の第1パターン42AK20により構成される信号配線は、第2形状部42AK20Mを形成する部分を含んでいる。配線の第2パターン42AK21により構成される信号配線は、第2形状部42AK21Mを形成する部分を含んでいる。配線の第3パターン42AK22により構成される信号配線は、第2形状部42AK22Mを形成する部分を含んでいる。第2形状部42AK20Mおよび第2形状部42AK21Mは、例えば左右方向といった、第1方向に折返し往復する蛇行形状を有している。これに対し、第2形状部42AK22Mは、例えば上下方向といった、第1方向とは異なる第2方向に折返し往復する蛇行形状を有している。なお、それぞれの第2形状部は、蛇行形状に限定されず、直線形状および略直線形状とは異なる任意の形状となるように形成されればよい。

10

#### 【0093】

このように、配線の第1パターン42AK20により構成される信号配線における第2形状部42AK20Mは、配線の第2パターン42AK21により構成される信号配線における第2形状部42AK21Mと共に(平行)な第1方向に形成されている。これに対し、配線の第3パターン42AK22により構成される信号配線における第2形状部42AK22Mは、配線の第1パターンにより構成される第2形状部42AK20Mや配線の第2パターンにより構成される第2形状部42AK21Mが形成される第1方向とは異なる第2方向に形成されている。複数の信号配線において異なる方向に第2形状部が形成されるようにしたことにより、基板面における配線のパターン設計を容易かつ柔軟に行うことができる。また、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

20

#### 【0094】

図17(B)に示す4つの信号配線を構成する配線のパターンは、配線の第4パターン42AK23、配線の第5パターン42AK24、配線の第6パターン42AK25、配線の第7パターン42AK26を含んでいる。配線の第4パターン42AK23により構成される信号配線は、2つの第2形状部42AK23M1、42AK23M2を形成する部分を含んでいる。配線の第5パターン42AK24により構成される信号配線は、1つの第2形状部42AK24Mを形成する部分を含んでいる。配線の第6パターン42AK25により構成される信号配線は、1つの第2形状部42AK25Mを形成する部分を含んでいる。配線の第7パターン42AK26により構成される信号配線は、2つの第2形状部42AK26M1、42AK26M2を形成する部分を含んでいる。図17(B)に示す複数の第2形状部のうち、第2形状部42AK23M1、42AK25M、42AK26M2は、例えば上下方向といった、第1方向に折返し往復する蛇行形状を有している。これに対し、第2形状部42AK23M2、42AK24M、42AK26M1は、例えば左右方向といった、第1方向とは異なる第2方向に折返し往復する蛇行形状を有している。

30

#### 【0095】

図17(B)に示すように、配線のパターンにより構成される複数の信号配線には、1つの第2形状部を形成する部分を含む信号配線と、複数の第2形状部を形成する部分を含む信号配線とがあつてもよい。あるいは、配線のパターンにより構成される複数の信号配線は、各信号配線が1つの第2形状部を形成する部分のみを含んでいてもよい。あるいは、配線のパターンにより構成される複数の信号配線は、各信号配線が複数の第2形状部を形成する部分を含んでいてもよい。図17(B)に示す配線の第4パターン42AK23により構成される信号配線における第2形状部42AK23M1は、配線の第6パターン42AK25により構成される信号配線における第2形状部42AK25Mや配線の第7パターン42AK26により構成される信号配線における第2形状部42AK26M2と共に(平行)な第1方向に形成されている。また、配線の第4パターン42AK23により構成される信号配線における第2形状部42AK23M2は、配線の第5パターン42

40

50

A K 2 4 により構成される信号配線における第2形状部 4 2 A K 2 4 M や配線の第7パターン 4 2 A K 2 6 により構成される信号配線における第2形状部 4 2 A K 2 6 M 1 と共に通(平行)な第2方向に形成されている。これに対し、第2形状部 4 2 A K 2 3 M 2 、 4 2 A K 2 4 M 、 4 2 A K 2 6 M 1 は、第2形状部 4 2 A K 2 3 M 1 、 4 2 A K 2 5 M 、 4 2 A K 2 6 M 2 が形成される第1方向とは異なる第2方向に形成されている。

#### 【 0 0 9 6 】

配線の第4パターン 4 2 A K 2 3 により構成される信号配線は、第1方向に形成される第2形状部 4 2 A K 2 3 M 1 と、第2方向に形成される第2形状部 4 2 A K 2 3 M 2 とを含んでいる。配線の第7パターン 4 2 A K 2 6 により構成される信号配線は、第2方向に形成される第2形状部 4 2 A K 2 6 M 1 と、第1方向に形成される第2形状部 4 2 A K 2 6 M 2 とを含んでいる。このように、同一の配線のパターンにより構成される1の信号配線であっても、異なる方向に形成される複数の第2形状部を含んでいてもよい。また、1の配線のパターンにより構成される信号配線は、他の配線のパターンにより構成される信号配線における第2形状部と、共通(平行)な方向に形成されている第2形状部および異なる方向に形成されている第2形状部を含んでもよい。1または複数の信号配線において異なる方向に第2形状部が形成されるようにしたことにより、基板面における配線のパターン設計を容易かつ柔軟に行うことができる。また、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

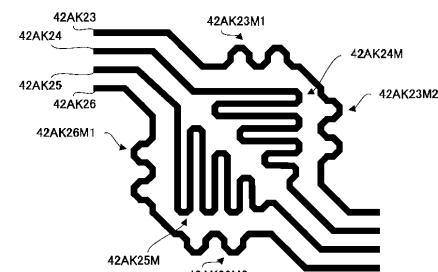

#### 【 0 0 9 7 】

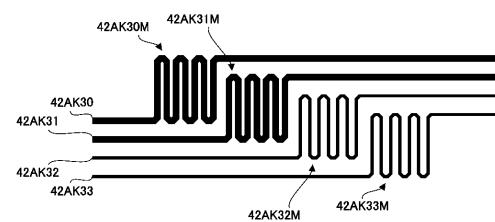

図18は、配線のパターンにより構成される複数の信号配線が異なる配線幅に形成されている構成例を示している。図18に示す構成例では、複数の信号配線を構成する配線のパターンとして、4つの信号配線を構成する配線のパターンが示されている。図18(A)は信号配線の全体で配線幅が異なる場合を示し、図18(B)は信号配線の一部で配線幅が異なる場合を示している。

#### 【 0 0 9 8 】

図18(A)に示す4つの信号配線を構成する配線のパターンは、配線の第1パターン 4 2 A K 3 0 、配線の第2パターン 4 2 A K 3 1 、配線の第3パターン 4 2 A K 3 2 、配線の第4パターン 4 2 A K 3 3 を含んでいる。配線の第1パターン 4 2 A K 3 0 により構成される信号配線は、第2形状部 4 2 A K 3 0 M を形成する部分を含んでいる。配線の第2パターン 4 2 A K 3 1 により構成される信号配線は、第2形状部 4 2 A K 3 1 M を形成する部分を含んでいる。配線の第3パターン 4 2 A K 3 2 により構成される信号配線は、第2形状部 4 2 A K 3 2 M を形成する部分を含んでいる。配線の第4パターン 4 2 A K 3 3 により構成される信号配線は、第2形状部 4 2 A K 3 3 M を形成する部分を含んでいる。

#### 【 0 0 9 9 】

配線の第1パターン 4 2 A K 3 0 により構成される信号配線は、配線の第2パターン 4 2 A K 3 1 により構成される信号配線と、配線幅が同一または略同一となるように形成されている。配線の第3パターン 4 2 A K 3 2 により構成される信号配線は、配線の第4パターン 4 2 A K 3 3 により構成される信号配線と、配線幅が同一または略同一となるように形成されている。これに対し、配線の第1パターン 4 2 A K 3 0 により構成される信号配線および配線の第2パターン 4 2 A K 3 1 により構成される信号配線は、配線の第3パターン 4 2 A K 3 2 により構成される信号配線および配線の第4パターン 4 2 A K 3 3 により構成される信号配線と比較して、信号配線の全体において配線幅が広くなるように形成されている。このように、配線の第1パターン 4 2 A K 3 0 と配線の第2パターン 4 2 A K 3 1 は配線幅が広い信号配線を構成し、配線の第3パターン 4 2 A K 3 2 と配線の第4パターン 4 2 A K 3 3 は配線幅が狭い信号配線を構成している。

#### 【 0 1 0 0 】

配線の第1パターン 4 2 A K 3 0 により構成される信号配線と、配線の第2パターン 4 2 A K 3 1 により構成される信号配線とでは、例えば第1種類の差動信号といった、共通する種類の電気信号が伝送されてもよい。また、配線の第3パターン 4 2 A K 3 2 により

10

20

30

40

50

構成される信号配線と、配線の第4パターン42AK33により構成される信号配線とでは、例えば第1種類とは異なる第2種類の差動信号といった、共通する種類の電気信号が伝送されてもよい。その一方で、配線の第1パターン42AK30により構成される信号配線や配線の第2パターン42AK31により構成される信号配線と、配線の第3パターン42AK32により構成される信号配線や配線の第4パターン42AK33により構成される信号配線とでは、互いに相違する種類の電気信号が伝送されてもよい。このように、配線のパターンにより構成される複数の信号配線は、伝送される電気信号の種類に応じて異なる配線幅となるように形成されていてもよい。あるいは、配線のパターンにより構成される複数の信号配線は、伝送される電気信号の種類が共通する場合に、同一または略同一の配線幅となるように形成されていてもよい。なお、配線のパターンにより構成される複数の信号配線は、伝送される電気信号の種類が共通する場合であっても、異なる配線幅となるように形成された信号配線を含んでいてもよい。あるいは、配線のパターンにより構成される複数の信号配線は、伝送される電気信号の種類が異なる場合であっても、同一または略同一の配線幅となるように形成された信号配線を含んでいてもよい。複数の信号配線が異なる配線幅に形成されるようにしたことにより、各信号配線における特性インピーダンスを容易に調整して、電気信号の種類などに応じた適切な伝送が可能になる。

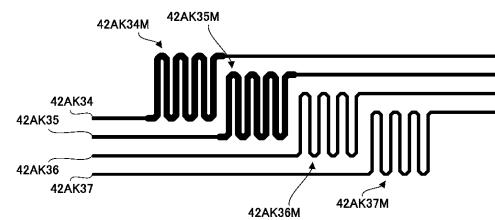

#### 【0101】

図18(B)に示す4つの信号配線を構成する配線のパターンは、配線の第5パターン42AK34、配線の第6パターン42AK35、配線の第7パターン42AK36、配線の第8パターン42AK37を含んでいる。配線の第5パターン42AK34により構成される信号配線は、第2形状部42AK34Mを形成する部分を含んでいる。配線の第6パターン42AK35により構成される信号配線は、第2形状部42AK35Mを形成する部分を含んでいる。配線の第7パターン42AK36により構成される信号配線は、第2形状部42AK36Mを形成する部分を含んでいる。配線の第8パターン42AK37により構成される信号配線は、第2形状部42AK37Mを形成する部分を含んでいる。

#### 【0102】

配線の第5パターン42AK34により構成される信号配線と、配線の第6パターン42AK35により構成される信号配線は、一部の配線幅が他の部分における配線幅とは異なるように構成されている。例えば配線の第5パターン42AK34により構成される信号配線における第2形状部42AK34Mは、同一の信号配線における他の部分と比較して、配線幅が広くなるように形成されている。配線の第6パターン42AK35により構成される信号配線における第2形状部42AK35Mは、同一の信号配線における他の部分と比較して、配線幅が広くなるように形成されている。このように、配線の第5パターン42AK34は、第2形状部42AK34Mにて配線幅が広い信号配線を構成し、第2形状部42AK34M以外の部分では配線幅が狭い信号配線を構成している。配線の第6パターン42AK35は、第2形状部42AK35Mにて配線幅が広い信号配線を構成し、第2形状部42AK35M以外の部分では配線幅が狭い信号配線を構成している。なお、第2形状部にて配線幅が広い信号配線を構成するものに限定されず、直線形状または略直線形状となる第1形状部にて配線幅が広い信号配線を構成するものであってもよい。

#### 【0103】

配線の第5パターン42AK34により構成される信号配線は、第2形状部42AK34Mの配線幅が他の部分よりも広くなることにより、同一の信号配線において配線幅が異なるように形成されている。配線の第6パターン42AK35により構成される信号配線は、第2形状部42AK35Mの配線幅が他の部分よりも広くなることにより、同一の信号配線において配線幅が異なるように形成されている。これに対し、配線の第7パターン42AK36により構成される信号配線や配線の第8パターン42AK37により構成される信号配線は、同一の信号配線において配線幅が同一または略同一となるように形成されている。1または複数の信号配線において一部が異なる配線幅に形成されるようにしたことにより、各信号配線における特性インピーダンスを容易に調整して、電気信号の種類

10

20

30

40

50

などに応じた適切な伝送が可能になる。

#### 【0104】

図19は、配線のパターンにより構成される複数の信号配線における第2形状部が対応して形成されている構成例を示している。図19に示す構成例では、複数の信号配線を構成する配線のパターンとして、2つの信号配線を構成する配線のパターンが示されている。図19(A)は2つの信号配線が略平行に蛇行する場合を示し、図19(B)は2つの信号配線が離れる方向に蛇行する場合を示している。

#### 【0105】

図19(A)に示す2つの信号配線を構成する配線のパターンは、配線の第1パターン42AK40と、配線の第2パターン42AK41とを含んでいる。配線の第1パターン42AK40と、配線の第2パターン42AK41は、例えば上下方向といった、共通(平行)な方向に折返し往復する蛇行形状を有している。この蛇行形状において、配線の第1パターン42AK40により構成される信号配線が延設方向DR1に対して配線の第2パターン42AK41により構成される信号配線に近づく方向へと屈曲されて突出する場合に、配線の第2パターン42AK41により構成される信号配線は、延設方向DR1に対して、配線の第1パターン42AK40により構成される信号配線から離れる方向へと屈曲されて突出する。その後に、配線の第1パターン42AK40により構成される信号配線が延設方向DR1に対して配線の第2パターン42AK41により構成される信号配線から離れる方向へと屈曲されて復帰する場合に、配線の第2パターン42AK41により構成される信号配線は、延設方向DR1に対して、配線の第1パターン42AK40により構成される信号配線に近づく方向へと屈曲されて復帰する。また、この蛇行形状において、配線の第1パターン42AK40により構成される信号配線が延設方向DR1に対して配線の第2パターン42AK41により構成される信号配線から離れる方向へと屈曲されて突出する場合に、配線の第2パターン42AK41により構成される信号配線は、延設方向DR1に対して、配線の第1パターン42AK40により構成される信号配線に近づく方向へと屈曲されて突出する。その後に、配線の第1パターン42AK40により構成される信号配線が延設方向DR1に対して配線の第2パターン42AK41により構成される信号配線に近づく方向へと屈曲されて復帰する場合に、配線の第2パターン42AK41により構成される信号配線は、延設方向DR1に対して、配線の第1パターン42AK40と、配線の第2パターン42AK41は、略同一の配線間隔を維持しつつ略平行に折返し往復する蛇行形状の信号配線を形成している。なお、蛇行形状に限定されず、直線形状および略直線形状とは異なる任意の形状となるように形成されればよい。

#### 【0106】

このように、配線の第1パターン42AK40により構成される信号配線は、配線の第2パターン42AK41により構成される信号配線と平行または略平行に形成され、直線形状および略直線形状とは異なる形状となるように形成されている。複数の信号配線において平行または略平行でありながら、直線形状および略直線形状とは異なる形状となる第2形状部が形成されるようにしたことにより、基板面における配線のパターン設計を容易かつ柔軟に行うことができる。また、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

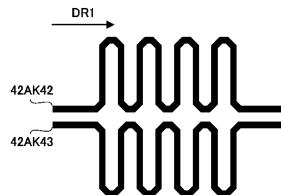

#### 【0107】

図19(B)に示す2つの信号配線を構成する配線のパターンは、配線の第3パターン42AK42と、配線の第4パターン42AK43とを含んでいる。配線の第3パターン42AK42と、配線の第4パターン42AK43は、例えば上下方向といった、共通(平行)な方向に折返し往復する蛇行形状を有している。この蛇行形状において、配線の第3パターン42により構成される信号配線が延設方向DR1に対して配線の第4パターン42AK43により構成される信号配線から離れる方向へと屈曲されて突出する場合に、配線の第4パターン42AK43により構成される信号配線は、延設方向DR1に対して

10

20

30

40

50

、配線の第3パターン42AK42により構成される信号配線から離れる方向へと屈曲されて突出する。これらの突出による突起から、配線の第3パターン42AK42により構成される信号配線が延設方向D R 1に対して配線の第4パターン42AK43により構成される信号配線に近づく方向へと屈曲されて復帰する場合に、配線の第4パターン42AK43により構成される信号配線は、延設方向D R 1に対して、配線の第3パターン42AK42により構成される信号配線に近づく方向へと屈曲されて復帰する。こうして、配線の第3パターン42AK42と、配線の第4パターン42AK43は、配線間隔を変化させつつ互いに離れる方向に突出してから近づく方向に復帰するという、折返し往復する蛇行形状の信号配線を形成している。

## 【0108】

10

このように、配線の第3パターン42AK42により構成される信号配線は、配線の第4パターン42AK43により構成される信号配線と共に（平行）な方向に形成され、直線形状および略直線形状とは異なる形状となるように形成されている。複数の信号配線が離れる方向に屈曲されて突出し近づく方向に屈曲されて復帰するなど、直線形状および略直線形状とは異なる形状となる第2形状部が形成されるようにしたことにより、基板面における配線のパターン設計を容易かつ柔軟に行うことができる。また、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

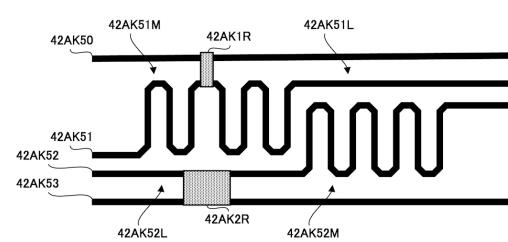

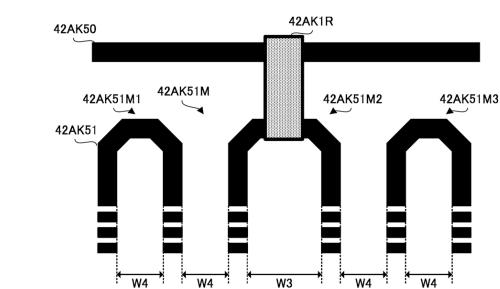

## 【0109】

20

図20は、配線のパターンにより構成される複数の信号配線に回路部品が接続されるように実装された構成例を示している。図20（A）に示す構成例では、複数の信号配線を構成する配線のパターンとして、4つの信号配線を構成する配線のパターンが示されている。これら4つの信号配線を構成する配線のパターンは、配線の第1パターン42AK50、配線の第2パターン42AK51、配線の第3パターン42AK52、配線の第4パターン42AK53を含んでいる。配線の第2パターン42AK51により構成される信号配線は、第1形状部42AK51Lを形成する部分と、第2形状部42AK51Mを形成する部分とを含んでいる。配線の第3パターン42AK52により構成される信号配線は、第1形状部42AK52Lを形成する部分と、第2形状部42AK52Mを形成する部分とを含んでいる。

## 【0110】

30

図20（A）に示す配線の第2パターン42AK51により構成される信号配線における第2形状部42AK51Mには、配線の第1パターン42AK50により構成される信号配線と接続された回路部品42AK1Rが、配線の第2パターン42AK51により構成される信号配線と接続されるように実装される。回路部品42AK1Rは、例えば抵抗素子といった回路素子であればよい。回路部品42AK1Rは、抵抗素子とともに、あるいは抵抗素子に代えて、例えばコンデンサやコイルといった受動素子を、一部または全部に含んでいてもよい。回路部品42AK1Rは、抵抗素子、コンデンサ、コイルといった受動素子に代えて、あるいは受動素子とともに、ダイオード、バイポーラトランジスタやMOSトランジスタなどのトランジスタ、サイリスタといった能動素子を、一部または全部に含んでいてもよい。回路部品42AK1Rは、例えばfiltration回路、ノイズ防止回路、その他のICチップといった、機能回路を構成するものであってもよい。回路部品42AK1Rは、配線の第1パターン42AK50により構成される信号配線が特定の電源電圧に維持される場合に、配線の第2パターン42AK51により構成される信号配線に対して特定の電源電圧を供給可能にするプルアップ抵抗として機能してもよい。あるいは、回路部品42AK1Rは、配線の第1パターン42AK50により構成される信号配線がグランド電圧に維持される場合に、配線の第2パターン42AK51により構成される信号配線に対してグランド電圧を供給可能にするプルダウン抵抗として機能してもよい。あるいは、回路部品42AK1Rは、極性切替部により抵抗素子をプルアップ抵抗とプルダウン抵抗とに切替可能とした機能回路であってもよい。

## 【0111】

図20（B）は、回路部品42AK1Rの接続部分を示す拡大図である。図20（B）

40

50

に示す第2形状部42AK51Mにおいて、配線の第2パターン42AK51により構成される信号配線が折り曲げ部を介して折り返される3つの折返し部が示されている。これら3つの折返し部は、第1折返し部42AK51M1、第2折返し部42AK51M2、第3折返し部42AK51M3を含んでいる。回路部品42AK1Rは、第2折返し部42AK51M2にて、配線の第2パターン42AK51により構成される信号配線と、配線の第1パターン42AK50により構成される信号配線とに、接続されるように実装されている。図20(B)に示す第2折返し部42AK51M2では、折り曲げ部を介して折り返された同一の信号配線が配線間隔W3で往復する形状を形成している。これに対し、第1折返し部42AK51M1や第3折返し部42AK51M3では、折り曲げ部を介して折り返された同一の信号配線が配線間隔W4で往復する形状を形成している。また、第1折返し部42AK51M1と第2折返し部42AK51M2との間隔や、第2折返し部42AK51M2と第3折返し部42AK51M3との間隔も、配線間隔W4となるよう形成されている。配線間隔W3は、配線間隔W4よりも広くなるように、信号配線が形成されている。このように、回路部品42AK1Rが実装される第2折返し部42AK51M2における配線間隔W3は、第2形状部42AK51Mにて回路部品42AK1Rが実装されない部分における配線間隔W4よりも広くなるものに限定されず、配線間隔W3が配線間隔W4と同一または略同一のものでもよいし、配線間隔W3が配線間隔W4よりも狭くなるように形成されていてもよい。また、回路部品42AK1Rは、第2折返し部42AK51M2にて配線の第2パターン42AK52により構成される信号配線と接続されるように実装されるものに限定されず、第1折返し部42AK51M1または第3折返し部42AK51M3にて、配線の第2パターン42AK52により構成される信号配線と接続されるように実装されるものであってもよい。

#### 【0112】

なお、回路部品42AK1Rが実装される第2折返し部42AK51M2における配線間隔W3は、第2形状部42AK51Mにて回路部品42AK1Rが実装されない部分における配線間隔W4よりも広くなるものに限定されず、配線間隔W3が配線間隔W4と同一または略同一のものでもよいし、配線間隔W3が配線間隔W4よりも狭くなるように形成されていてもよい。また、回路部品42AK1Rは、第2折返し部42AK51M2にて配線の第2パターン42AK52により構成される信号配線と接続されるように実装されるものに限定されず、第1折返し部42AK51M1または第3折返し部42AK51M3にて、配線の第2パターン42AK52により構成される信号配線と接続されるように実装されるものであってもよい。

#### 【0113】

このように、図20(A)などに示す配線の第2パターン42AK51により構成される信号配線における第2形状部42AK51Mにて、配線の第1パターン42AK50により構成される信号配線と接続されるように実装された回路部品42AK1Rを備えている。第2形状部に回路部品が実装されることにより、信号配線における伝送特性などを適切に調整することができる。また、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。

#### 【0114】

図20(A)に示す配線の第3パターン42AK52により構成される信号配線における第1形状部42AK52Lには、配線の第4パターン42AK53により構成される信号配線と接続された回路部品42AK2Rが、配線の第3パターン42AK52により構成される信号配線と接続されるように実装される。回路部品42AK2Rは、例えば抵抗素子といった回路素子であればよい。回路部品42AK2Rは、抵抗素子とともに、あるいは抵抗素子に代えて、例えばコンデンサやコイルといった受動素子を、一部または全部に含んでいてもよい。回路部品42AK2Rは、抵抗素子、コンデンサ、コイルといった受動素子に代えて、あるいは受動素子とともに、ダイオード、バイポーラトランジスタやMOSトランジスタなどのトランジスタ、サイリスタといった能動素子を、一部または全部に含んでいてもよい。回路部品42AK2Rは、例えばフィルタ回路、ノイズ防止回路、その他のICチップといった、機能回路を構成するものであってもよい。回路部品42AK2Rは、配線の第4パターン42AK53により構成される信号配線が特定の電源電圧に維持される場合に、配線の第3パターン42AK52により構成される信号配線に対して特定の電源電圧を供給可能にするプルアップ抵抗として機能してもよい。あるいは、回路部品42AK2Rは、配線の第4パターン42AK53により構成される信号配線が

10

20

30

40

50

グランド電圧に維持される場合に、配線の第3パターン42AK52により構成される信号配線に対してグランド電圧を供給可能にするプルダウン抵抗として機能してもよい。あるいは、回路部品42AK2Rは、極性切替部により抵抗素子をプルアップ抵抗とプルダウン抵抗とに切替可能とした機能回路であってもよい。

#### 【0115】

このように、図20(A)に示す配線の第3パターン42AK52により構成される信号配線における第2形状部42AK52Mとは異なる第1形状部42AK52Lにて、配線の第4パターン42AK53により構成される信号配線と接続されるように実装された回路部品42AK2Rを備えている。第2形状部とは異なる部分に回路部品が実装されることにより、信号配線における伝送特性などを適切に調整することができる。また、配線のパターンを配置する基板面積の増大が抑制されて、基板の小型化を図ることができる。10

#### 【0116】

回路部品42AK1Rや回路部品42AK2Rが実装される部分における配線幅は、回路部品42AK1Rや回路部品42AK2Rが実装されない部分とは異なる配線幅となるように、各信号配線が形成されてもよい。例えば回路部品42AK1Rや回路部品42AK2Rが実装される部分における配線幅は、回路部品42AK1Rや回路部品42AK2Rが実装されない部分の配線幅よりも広くなるように、各信号配線が形成されてもよい。このように、配線のパターンにより構成される複数の信号配線は、回路部品が実装される部分に対応して、実装されない部分とは異なる配線幅となるように形成されてもよい。回路部品が実装される部分に対応して異なる配線幅に形成されるようにしたことにより、各信号配線における特性インピーダンスを容易に調整して、信号配線による適切な伝送が可能になる。20

#### 【0117】

図16(A)や図16(B)に示すような第1形状部42AK10L、42AK11L、42AK12L、42AK13Lおよび第2形状部42AK10M、42AK11M、42AK12M、42AK13Mを有する信号配線が形成されている場合に、配線のパターンにより構成される複数の信号配線は、例えば図17に示すように、第2形状部が異なる方向に形成されてもよく、例えば図18に示すように信号配線の全体または一部で異なる配線幅に形成されてもよく、例えば図19に示すように第2形状部が略平行または離れる方向に対応して形成されてもよく、例えば図20に示すように第2形状部または第2形状部とは異なる部分に接続される回路部品が実装されてもよく、これらの一部または全部を組み合わせて形成されてもよい。30

#### 【0118】

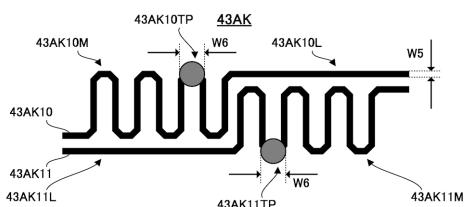

##### (特徴部43AKに関する説明)

図21は、本実施形態の特徴部43AKに関し、配線のパターンにより構成される複数の信号配線における第2形状部に接続確認用の特定導体部となるテストポイントが設けられている構成例を示している。図21に示す構成例では、複数の信号配線を構成する配線のパターンとして、2つの信号配線を構成する配線のパターンが示されている。これら2つの信号配線を構成する配線のパターンは、配線の第1パターン43AK10と、配線の第2パターン43AK11とを含んでいる。配線の第1パターン43AK10により構成される信号配線は、第1形状部43AK10Lを形成する部分と、第2形状部43AK10Mを形成する部分とを含んでいる。配線の第2パターン43AK11により構成される信号配線は、第1形状部43AK11Lを形成する部分と、第2形状部43AK11Mを形成する部分とを含んでいる。第1形状部43AK10L、43AK11Lは、信号配線が直線形状または略直線形状の第1形状となるように形成されている。第2形状部43AK10M、43AK11Mは、信号配線が蛇行形状といった、直線形状および略直線形状とは異なる第2形状となるように形成されている。なお、第2形状部43AK10M、43AK11Mは、蛇行形状に限定されず、直線形状および略直線形状とは異なる任意の形状となるように形成されればよい。40

#### 【0119】

50

配線の第1パターン43AK10および配線の第2パターン43AK11により構成される複数の信号配線は、少なくとも一部が、例えば図16(A)に示した配線の第1パターン42AK10および配線の第2パターン42AK11と同様に、あるいは図16(B)に示した配線の第3パターン42AK12および配線の第4パターン42AK13と同様に、形成されればよい。例えば、配線の第2パターン43AK11により構成される信号配線が、直線形状または略直線形状の第1形状となる第1形状部43AK11Lに対応して、配線の第1パターン43AK10により構成される信号配線が、第1形状部43AK11Lとは異なる蛇行形状などの第2形状部43AK10Mを含んでいればよい。また、配線の第1パターン43AK10により構成される信号配線が、直線形状または略直線形状となる第1形状部43AK10Lに対応して、配線の第2パターン43AK11により構成される信号配線が、第1形状部43AK10Lとは異なる蛇行形状などの第2形状部43AK10Mを含んでいればよい。10

#### 【0120】

配線の第1パターン43AK10により構成される信号配線における第2形状部43AK10Mには、接続確認用の特定導体部として、テストポイント43AK10TPが設けられている。配線の第2パターン43AK11により構成される信号配線における第2形状部43AK11Mには、接続確認用の特定導体部として、テストポイント43AK11TPが設けられている。テストポイント43AK10TP、43AK11TPは、例えばはんだ、または銅箔といった、金属材料を用いて形成されればよい。テストポイント43AK10TP、43AK11TPは、例えば円形に形成された場合の直径W6が、配線の第1パターン43AK10により構成される信号配線や配線の第2パターン43AK11により構成される信号配線における配線幅W5よりも、大きく(広く)なるように形成されている。なお、テストポイント43AK10TP、43AK11TPは、円形に形成されるものに限定されず、例えば方形状や短冊状といった、任意の形状に形成されたものであればよい。テストポイント43AK10TP、43AK11TPがどのような形状であっても、その平均的な形状が、信号配線における配線幅よりも大きく(広く)なるように形成されたものであればよい。テストポイント43AK10TP、43AK11TPが設けられることにより、複数の信号配線における特性インピーダンスのばらつきが抑制できるようにしてもよい。これにより、複数の信号配線における信号品質の均質化が図られる。30

#### 【0121】

例えばテストポイント43AK10TPとテストポイント43AK11TPとにテストプローブを接触させることにより、配線の第1パターン43AK10により構成される信号配線と配線の第2パターン43AK11により構成される信号配線との間において、短絡の発生の有無を検査することができる。なお、テストポイント43AK10TP、43AK11TPの他にも、接続確認用の特定導体部となるテストポイントが設けられてもよい。一例として、配線の第1パターン43AK10により構成される信号配線には、テストポイント43AK10TPの他にもテストポイントが設けられてもよい。このテストポイントと、第2形状部43AK10Mに設けられたテストポイント43AK10TPとともに、テストプローブを接触させることにより、配線の第1パターン43AK10により構成される信号配線において、断線の発生の有無を検査することができる。短絡や断線について、発生の有無を検査できるとともに、あるいは、それらの検査に代えて、例えばオシロスコープを用いて信号波形の確認や検査を行うことができるよう構成されてもよい。40

#### 【0122】

このように、図21に示す信号配線が蛇行形状などの第2形状となる第2形状部43AK10Mにはテストポイント43AK10TPが設けられ、第2形状部43AK11Mにはテストポイント43AK11TPが設けられている。信号配線における第2形状部にテストポイントを設けることにより、配線のパターンを適切に配置するとともに、各種の構造物を適切に配置して、基板面積の増大が抑制され、基板の小型化を図ることができる。また、テストポイント43AK10TP、43AK11TPは金属材料を用いて形成され50

、信号配線の配線幅よりも広くなるように形成されている。このような信号配線の配線幅より大きく（広く）なるようにテストポイントが形成されることにより、テストプローブを容易に接触させて、信号配線の電気特性検査を行うことができる。また、配線のパターンを適切に配置するとともに、各種の構造物を適切に配置して、基板面積の増大が抑制され、基板の小型化を図ることができる。

#### 【0123】

図21に示すようなテストポイント43AK10TP、43AK11TPが設けられた場合に、配線のパターンにより構成される複数の信号配線は、例えば図17に示すように、第2形状部が異なる方向に形成されてもよく、例えば図18に示すように信号配線の全体または一部で異なる配線幅に形成されてもよく、例えば図19に示すように第2形状部が略平行または離れる方向に対応して形成されてもよく、例えば図20に示すように第2形状部または第2形状部とは異なる部分に接続される回路部品が実装されてもよく、これら的一部または全部を組み合わせて形成されてもよい。

10

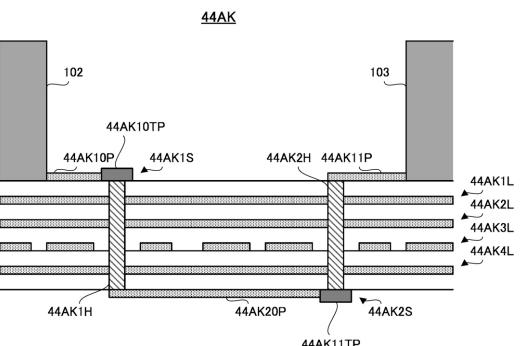

#### 【0124】

（特徴部44AKに関する説明）

図22は、本実施形態の特徴部44AKに関し、多層配線基板として構成された主基板11において、一面に第2形状を含む信号配線が設けられ、他面に接続確認用の特定導体部となるテストポイントが設けられている場合の構成例を示している。図22に示す特徴部44AKの少なくとも一部は、図14に示した構成例と同様に形成されていればよい。例えば特徴部44AKについても、合成樹脂を重ねて形成された多層構造を有していればよい。図22に示す主基板11の多層構造は、表面層44AK1Sと、グランド層44AK1Lと、電源層44AK2Lと、配線層44AK3Lと、電源層44AK4Lと、裏面層44AK2Sとを含んでいる。

20

#### 【0125】

主基板11における一方の基板面となる表面には、表面層44AK1Sが設けられ、信号配線を構成する配線のパターン44AK10Pおよびパターン44AK11Pが形成されている。主基板11における他方の基板面となる裏面には、裏面層44AK2Sが設けられ、信号配線を構成する配線のパターン44AK20Pが形成されている。主基板11の表面層44AK1Sに形成された配線のパターン44AK10Pは、主基板11の表面層44AK1Sおよび裏面層44AK2Sを貫通するスルーホール44AK1Hを介して、裏面層44AK2Sに形成された配線のパターン44AK20Pと電気的に接続されている。主基板11の表面層44AK1Sに形成された配線のパターン44AK11Pは、主基板11の表面層44AK1Sおよび裏面層44AK2Sを貫通するスルーホール44AK2Hを介して、裏面層44AK2Sに形成された配線のパターン44AK20Pと電気的に接続されている。このように、主基板11には、一方の基板面となる表面に設けられた表面層44AK1Sにおいて信号配線を構成する配線のパターン44AK10Pおよびパターン44AK11Pと、他方の基板面となる裏面に設けられた裏面層44AK2Sにおいて信号配線を構成する配線のパターン44AK20Pとを、電気的に接続可能なスルーホール44AK1Hおよびスルーホール44AK2Hが設けられている。

30

#### 【0126】

表面層44AK1Sに形成された配線のパターン44AK10Pは、例えば図21に示した配線の第1パターン43AK10および配線の第2パターン43AK11と同様に、第1形状部や第2形状部を形成する部分を含むように、複数の信号配線が形成されていればよい。図21に示す配線の第1パターン43AK10および配線の第2パターン43AK11により構成される信号配線は、配線の第2パターン43AK11により構成される信号配線が、直線形状または略直線形状の第1形状となる第1形状部43AK11Lに対応して、配線の第1パターン43AK10により構成される信号配線が、第1形状部43AK11Lとは異なる蛇行形状などの第2形状部43AK10Mを含んでいればよい。また、配線の第1パターン43AK10により構成される信号配線が、直線形状または略直線形状となる第1形状部43AK10Lに対応して、配線の第2パターン43AK11に

40

50

より構成される信号配線が、第1形状部 43AK10L とは異なる蛇行形状などの第2形状部 43AK10M を含んでいればよい。

#### 【0127】

そして、図21に示した第2形状部 43AK10M に設けられたテストポイント 43AK10TP および第2形状部 43AK11M に設けられたテストポイント 43AK11TP に対応して、図22に示すテストポイント 44AK10TP が、配線のパターン 44AK10P により構成される信号配線に設けられていればよい。テストポイント 44AK10TP は、スルーホール 44AK1H を介して、例えば裏面層 44AK2S に形成された配線のパターン 44AK20P といった、異なる導体層と接続されていればよい。なお、テストポイント 44AK10TP は、裏面層 44AK2S に形成された配線のパターン 44AK20P に限定されず、例えば配線層 44AK3L に形成された配線のパターン 44AK20P といった、テストポイント 44AK10TP が設けられる表面層 44AK1S とは異なる任意の導体層と接続されたものであればよい。テストポイントが設けられる層とは異なる導体層とテストポイントがスルーホールを介して接続されることにより、信号配線や導体層の電気特性検査を容易に行うことができる。また、配線のパターンを適切に配置するとともに、各種の構造物を適切に配置して、基板面積の増大が抑制され、基板の小型化を図ることができる。10

#### 【0128】

表面層 44AK1S に形成された配線のパターン 44AK11P についても、第1形状部や第2形状部を形成する部分を含むように、複数の信号配線が形成されていればよい。20

このように、配線のパターン 44AK11P により構成される複数の信号配線は、主基板 11 の表面層 44AK1S といった、基板の一面にて、直線形状および略直線形状とは異なる第2形状部を含むように形成されている。これに対し、裏面層 44AK2S には、テストポイント 44AK11TP が設けられている。テストポイント 44AK11TP は、例えば配線のパターン 44AK20P により構成される信号配線に設けられ、スルーホール 44AK2H を介して、表面層 44AK1S に形成された配線のパターン 44AK11P といった、異なる導体層と接続されていればよい。テストポイント 44AK10TP、44AK11P が設けられることにより、複数の信号配線における特性インピーダンスのばらつきが抑制できるようにもよい。これにより、複数の信号配線における信号品質の均質化が図られる。基板の一面に第2形状部を含む信号配線が設けられ、基板の他面にテストポイントが設けられることにより、信号配線や導体層の電気特性検査を容易に行うことができる。また、配線のパターンを適切に配置するとともに、各種の構造物を適切に配置して、基板面積の増大が抑制され、基板の小型化を図ることができる。30

#### 【0129】

例えばテストポイント 44AK10TP にテストプローブを接触させることにより、配線のパターン 44AK10P により構成される複数の信号配線において、短絡の発生の有無を検査することができればよい。また、例えばテストポイント 44AK10TP とテストポイント 44AK11TP とにテストプローブを接触させることにより、裏面層 44AK2S に形成された配線のパターン 44AK20P により構成される信号配線や、スルーホール 44AK1H において、断線の発生の有無を検査することができればよい。その他、配線のパターン 44AK10P により構成される複数の信号配線における断線の発生の有無、配線のパターン 44AK11P により構成される複数の信号配線における短絡や断線の発生の有無、配線のパターン 44AK20P により構成される複数の信号配線における短絡の発生の有無、スルーホール 44AK1H における短絡や断線の発生の有無を、検査可能にするテストポイントが設けられていてもよい。40

#### 【0130】

接続確認用の特定導体部となるテストポイントは、テストプローブを接触させるために専用の電極パッドが設けられたものに限定されず、例えば信号配線における特性インピーダンスの調整用に回路部品などを接続可能に設けられ電極パッドといった、任意の電極パ50

ッドを用いて構成されたものであればよい。このようなテストポイントなどの特定導体部は、多層配線基板に設けられたスルーホールにより、多層配線基板に含まれる複数の層のうち複数の信号配線およびテストポイントが設けられる層とは異なる導体層と、電気的に接続されることにより、多層配線基板における電気特性検査を適切に行うことができる。例えば裏面側の基板面といった、配線のパターンが形成された一方の基板面とは異なる他方の基板面に、テストポイントなどの特定導体部が設けられることにより、多層配線基板における電気特性検査を適切に行うことができる。また、配線のパターンを適切に配置するとともに、各種の構造物を適切に配置して、基板面積の増大が抑制され、基板の小型化を図ることができる。

## 【0131】

10

図22に示すようなテストポイント44AK10TP、44AK11TPが設けられた場合に、配線のパターンにより構成される複数の信号配線は、例えば図17に示すように、第2形状部が異なる方向に形成されてもよく、例えば図18に示すように信号配線の全体または一部で異なる配線幅に形成されてもよく、例えば図19に示すように第2形状部が略平行または離れる方向に対応して形成されてもよく、例えば図20に示すように第2形状部または第2形状部とは異なる部分に接続される回路部品が実装されてもよく、これらの一部または全部を組み合わせて形成されてもよい。

## 【0132】

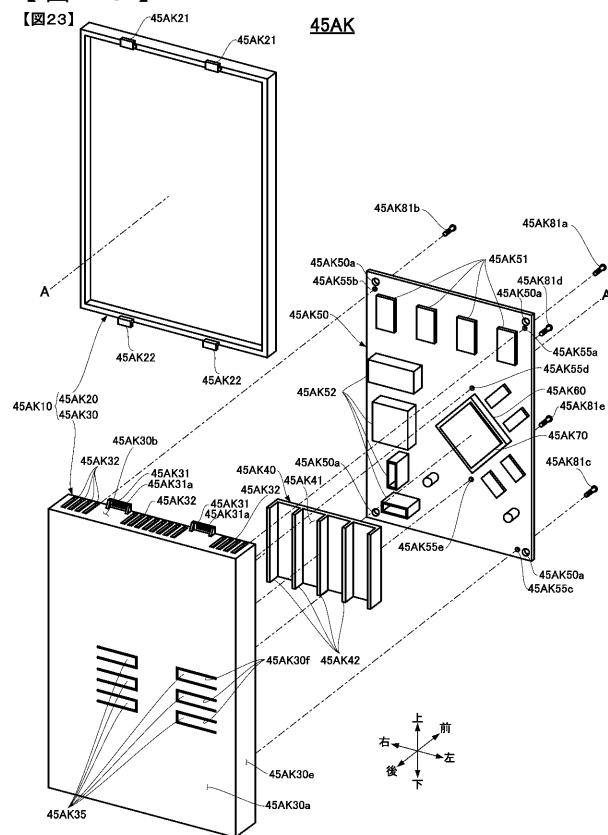

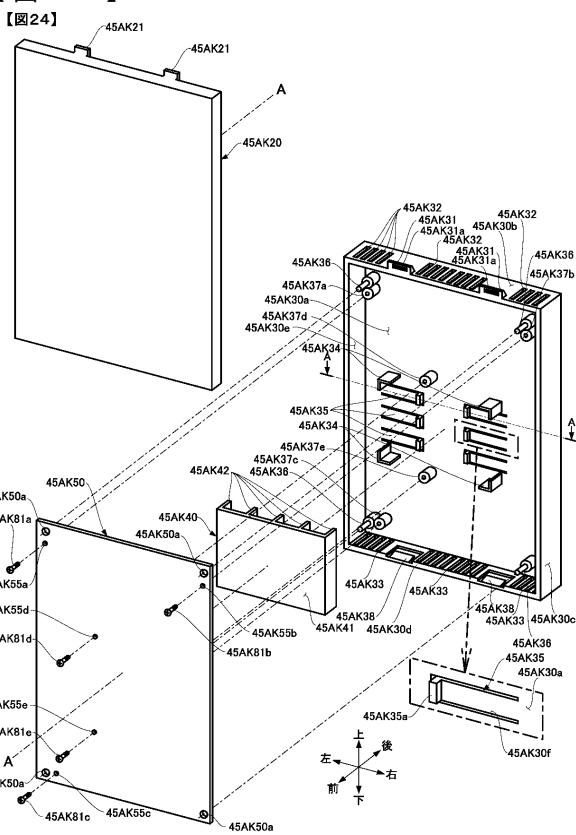

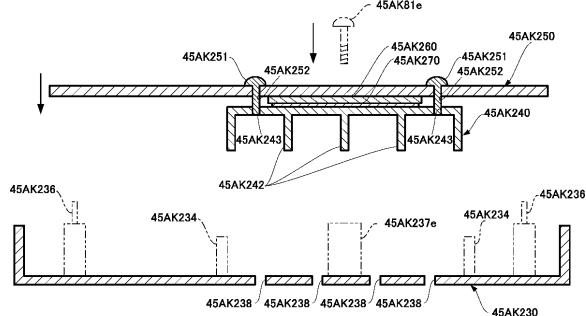

## (特徴部45AKに関する説明)

20

以下、図面を参照しつつ、特徴部45AKに係る遊技機の基板ケース45AK10と、この基板ケース45AK10に収容されている基板45AK50及びヒートシンク45AK40について詳細に説明する。図23は、本発明の実施形態に係る遊技機の基板ケース45AK10、基板45AK50、及びヒートシンク45AK40を後方からみた分解斜視図である。図24は、本発明の実施形態に係る遊技機の基板ケース45AK10、基板45AK50、及びヒートシンク45AK40を前方からみた分解斜視図である。以下の説明において、理解を容易にするために、図23等に示した前後方向を規定し、基板ケース45AK10等を前方から見たときの上下左右方向を、基板ケース45AK10等の上下左右方向として説明する。

## 【0133】

基板ケース45AK10は、前方を構成する前ケース45AK20と、後方を構成する後ケース45AK30とが組み合わされて構成されている。基板ケース45AK10の内部には、CPU、ROM、コネクタ等の電子部品を搭載した基板45AK50、及びヒートシンク45AK40を収容するための収容空間が形成されている。

30

## 【0134】

前ケース45AK20は、例えば、熱可塑性を有する合成樹脂からなり、平面視して略長方形状に形成されている。前ケース45AK20は、後方が開放された箱状をなしている。前ケース45AK20の上縁には、上方に突出した2つの突出部45AK21が形成されている。また、前ケース45AK20の下縁には、下方に突出した2つの突出部45AK22が形成されている。

## 【0135】

40

後ケース45AK30も前ケース45AK20と同様に、例えば、熱可塑性を有する合成樹脂からなり、平面視して略長方形状に形成されている。後ケース45AK30は、後面を形成するベース板45AK30aと、ベース板45AK30aから前方に立設した上壁45AK30b、右壁45AK30c、下壁45AK30d、及び左壁45AK30eと、を有している。これにより、後ケース45AK30は、前方が開放された箱状をなしており、その収容部は前ケース45AK20のものよりも深い。後ケース45AK30の上壁45AK30bには、前ケース45AK20に形成された突出部45AK21が挿通される挿通孔45AK31aを有する係止部45AK31が2つ形成されている。また、後ケース45AK30の下壁45AK30dには、前ケース45AK20に形成された突出部45AK22が引掛けられる係止部45AK38(図24)が2つ形成されている。

50

**【 0 1 3 6 】**

前ケース 4 5 A K 2 0 と後ケース 4 5 A K 3 0 とを組み合わせる場合には、まず、前ケース 4 5 A K 2 0 の突出部 4 5 A K 2 1 を、後ケース 4 5 A K 3 0 の挿通孔 4 5 A K 3 1 a に挿入する。そして、前ケース 4 5 A K 2 0 の下部を後ケース 4 5 A K 3 0 に押し付けて、前ケース 4 5 A K 2 0 の突出部 4 5 A K 2 2 を後ケース 4 5 A K 3 0 の係止部 4 5 A K 3 8 に引掛ける。これにより、前ケース 4 5 A K 2 0 と後ケース 4 5 A K 3 0 とが組み合わされ、内部に基板 4 5 A K 5 0 等の収容空間が形成される。

**【 0 1 3 7 】**

また、後ケース 4 5 A K 3 0 には、上壁 4 5 A K 3 0 b に複数の空気孔 4 5 A K 3 2 が形成され、下壁 4 5 A K 3 0 d に複数の空気孔 4 5 A K 3 3 (図 2 4) が形成されている。

10 これにより、基板ケース 4 5 A K 1 0 には、上下方向に沿った空気の通り道が確保されている。また、後ケース 4 5 A K 3 0 のベース板 4 5 A K 3 0 a には、基板 4 5 A K 5 0 の位置決めをするための 4 つの挿入凸部 4 5 A K 3 6 と、基板 4 5 A K 5 0 をねじ止めするためのねじ穴 4 5 A K 3 7 a ~ 4 5 A K 3 7 e と、ヒートシンク 4 5 A K 4 0 の四隅を抑えて位置決めするための 4 つの位置決め部 4 5 A K 3 4 と、4 つの位置決め部 4 5 A K 3 4 に位置決めされたヒートシンク 4 5 A K 4 0 に当接して支持する 6 つの支持部 4 5 A K 3 5 と、が形成されている。

**【 0 1 3 8 】**

挿入凸部 4 5 A K 3 6 は、ベース板 4 5 A K 3 0 a の四隅に形成されている。挿入凸部 4 5 A K 3 6 のそれぞれは、基板 4 5 A K 5 0 に形成された挿入孔 4 5 A K 5 0 a に挿入される円柱状の凸部である。

20

**【 0 1 3 9 】**

4 つの位置決め部 4 5 A K 3 4 のそれぞれは、アングル状をなしており、直交した面でヒートシンク 4 5 A K 4 0 の角部に当接することが可能なように配置されている。

**【 0 1 4 0 】**

支持部 4 5 A K 3 5 は、図 2 4 の拡大図に示すように、ベース板 4 5 A K 3 0 a の切欠き 4 5 A K 3 0 f 内に配置されており、ベース板 4 5 A K 3 0 a よりも前方に突出した突出部 4 5 A K 3 5 a を有している。支持部 4 5 A K 3 5 は、一端のみがベース板 4 5 A K 3 0 a に支持された片持ちの状態にある。そのため、支持部 4 5 A K 3 5 は、突出部 4 5 A K 3 5 a に後方への応力が作用すると弾性変形して後方へと変位する。一方、突出部 4 5 A K 3 5 a に後方への応力が作用しなくなると、支持部 4 5 A K 3 5 は前方へと戻り元の状態に復帰する。

30

**【 0 1 4 1 】**

ヒートシンク 4 5 A K 4 0 は、例えば、伝熱性に優れたアルミニウムを加工してなる。ヒートシンク 4 5 A K 4 0 は、矩形状のベース板 4 5 A K 4 1 と、ベース板 4 5 A K 4 1 に立設した矩形状の 5 つのフィン 4 5 A K 4 2 とを備えている。フィン 4 5 A K 4 2 のそれぞれは上下方向に延び、左右方向に平行に配列されている。

**【 0 1 4 2 】**

基板 4 5 A K 5 0 は、例えば、C P U、R O M、コネクタ等の各種電子部品が搭載されたプリント基板である。基板 4 5 A K 5 0 には、後ケース 4 5 A K 3 0 に形成された挿入凸部 4 5 A K 3 6 に対応する位置に設けられた 4 つの挿入孔 4 5 A K 5 0 a と、基板 4 5 A K 5 0 を固定するためのねじ 4 5 A K 8 1 a ~ 4 5 A K 8 1 e が挿通されるねじ挿通孔 4 5 A K 5 5 a ~ 4 5 A K 5 5 e とが形成されている。

40

**【 0 1 4 3 】**

さらに基板 4 5 A K 5 0 には、発熱性の電子部品 4 5 A K 6 0 と、非発熱性の電子部品 4 5 A K 5 1 及び電子部品 4 5 A K 5 2 と、が設けられている。電子部品 4 5 A K 6 0 、電子部品 4 5 A K 5 1 、及び電子部品 4 5 A K 5 2 は、矩形状をなしている。特に、電子部品 4 5 A K 6 0 は、略正方形状をなしている。また、非発熱性の電子部品のうち、電子部品 4 5 A K 5 2 は、電子部品 4 5 A K 5 1 よりも高さが高い(厚みがある)。すなわち、図 2 3 においては、電子部品 4 5 A K 5 2 は、電子部品 4 5 A K 5 1 よりも後方に大き

50

く突出している。ここで、発熱性の電子部品とは、電子部品の誤動作を防止するために放熱対策が必要なほどの熱を発生させる電子部品のことをいう。一方、非発熱性の電子部品とは、放熱対策を行わなくてもよい程度しか熱を発生させない、あるいは全く熱を発生させない電子部品のことをいう。

#### 【0144】

非発熱性の電子部品のうち、高さの低い電子部品45AK51は、発熱性の電子部品45AK60よりも上方に配置されている。非発熱性の電子部品のうち、高さの高い電子部品45AK52は、発熱性の電子部品45AK60の右方に配置されている。また、非発熱性の電子部品45AK51及び電子部品45AK52の向きは、平面視した場合に各辺が矩形状の基板45AK50の辺と平行となるように配置されている。一方、発熱性の電子部品45AK60は、平面視した場合に各辺が矩形状の基板45AK50の辺と平行とならないように配置されている。発熱性の電子部品45AK60には、該電子部品45AK60とヒートシンク45AK40との間に介在して、発せられて熱をヒートシンク45AK40に伝える熱伝導シート45AK70が貼付されている。熱伝導シート45AK70は、電子部品45AK60のおおよそ全体を覆う。

#### 【0145】

熱伝導シート45AK70は、両面が粘着するタイプの公知の熱伝導シート、シリコーン、非シリコーン、あるいはセラミックを主原料とした柔軟な熱伝導シートから採用することができる。熱伝導シート45AK70は、電子部品45AK60とヒートシンク45AK40との間に介在して、両者を接着する。

#### 【0146】

(ヒートシンク45AK40及び基板45AK50の取り付けについて)

次に、基板ケース45AK10に、ヒートシンク45AK40及び基板45AK50を取り付けるための手順について説明する。図25は、基板ケース45AK10にヒートシンク45AK40及び基板45AK50を取り付ける様子を取り付け順((a)~(b))で示した断面図である。また、図26は、図25に続いて基板ケース45AK10にヒートシンク45AK40及び基板45AK50を取り付ける様子を取り付け順((a)~(b))で示した断面図である。なお、図25及び図26に示す図は、図24中の断面線A-Aで切断した断面図である。

#### 【0147】

図25(a)に示すように、まず、後ケース45AK30をテーブル等に載置し、ヒートシンク45AK40を後ケース45AK30に設置する。ヒートシンク45AK40は、フィン45AK42が上下方向に沿うように、図25(b)に示すように、ベース板45AK30aに形成された位置決め部45AK34に四隅を合わせて載置する。これにより、後ケース45AK30に対するヒートシンク45AK40の位置決めをすることができる。このとき、ヒートシンク45AK40のフィン45AK42b及びフィン45AK42dは、支持部45AK35の突出部45AK35aに当接した状態にある。

#### 【0148】

続いて、図25(b)に示すように、電子部品45AK60に熱伝導シート45AK70を貼付した基板45AK50を、後ケース45AK30に設置する。その際、図24に示す基板45AK50に形成された挿入孔45AK50aに、後ケース45AK30に形成された挿入凸部45AK36を挿入して、図26(a)に示すように、基板45AK50を後ケース45AK30に載置する。このように、挿入孔45AK50aに挿入凸部45AK36が挿入されることにより、後ケース45AK30に対する基板45AK50の位置決めがされる。

#### 【0149】

続いて、図26(a)に示すように、ねじ45AK81a~45AK81e(図26(a)では、ねじ45AK81eのみを図示)を基板45AK50に挿通し、対応するねじ孔45AK37a~45AK37eに締め付ける。これにより、支持部45AK35に支持されていたヒートシンク45AK40及び基板45AK50は、後ケース45AK30

10

20

30

40

50

に向けて押し付けられる。これにより、図26(b)に示すように、支持部45AK35は弾性変形し、その先端は距離Lだけ後方に変位する。このように弾性変形した支持部45AK35は、当接するヒートシンク45AK40を前方に押圧する。一方、ねじ45AK81a~45AK81eは、ヒートシンク45AK40を介して前方に押圧されている基板45AK50を押さえ込む。これにより、ヒートシンク45AK40と熱伝導シート45AK70とが密着するとともに、電子部品45AK60と熱伝導シート45AK70とが密着する。このような構成により、電子部品45AK60から発せられた熱は、熱伝導シート45AK70を介してヒートシンク45AK40に伝わり、ヒートシンク45AK40から放熱される。

## 【0150】

10

## (特徴部45AKの効果等について)

特徴部45AKに係る遊技機の効果について、図面を参照しながら説明する。図27は、ヒートシンク45AK40と電子部品45AK60との関係を説明するための平面図である。また、図28は、基板ケース45AK10内における空気の流れを説明するための説明図である。なお、図27は、ヒートシンク45AK40をフィン45AK42側からみた図であるため、電子部品45AK60はかくれ線である破線で図示している。また、ヒートシンク45AK40と電子部品45AK60との間には、熱伝導シート45AK70が介在して熱を伝導させているが、便宜上、熱伝導シート45AK70の図示を省略して、電子部品45AK60の全面からヒートシンク45AK40に熱が伝導するものとする。なお、二点鎖線で示した電子部品45AK61は、電子部品45AK60と比較するために示した比較例である。

20

## 【0151】

図27に示すように、平面視した場合に、矩形状の電子部品45AK60は、その辺45AK60a~45AK60dが、矩形状のヒートシンクの辺45AK40a~45AK40dと平行とならないように配置されている。すなわち、各辺をヒートシンクの辺45AK40a~45AK40dと平行となるように配置した電子部品45AK61を、中心点Oを中心に所定角度だけ回転させることで、電子部品45AK60の配置とすることができます。所定角度は例えば略45°である。なお、電子部品45AK60が略正方形状であるため、電子部品45AK60の対角線は上下左右方向を向く。電子部品45AK60をこのような配置とすることで、電子部品45AK60の頂点45AK60fをフィン45AK42bよりも右側(図中左側)に、電子部品45AK60の頂点45AK60eをフィン45AK42dよりも左側(図中右側)に配置することができる。一方、ヒートシンク45AK40と向きが一致するように配置された比較例の電子部品45AK61においては、いずれの部位も、フィン45AK42bよりも右側(図中左側)に、あるいはフィン45AK42dよりも左側(図中右側)に位置していない。これにより、電子部品45AK60は、フィン45AK42b及びフィン45AK42dに多くの熱を伝えることができ、放熱する際にフィン45AK42bとフィン45AK42dとを有効利用することができる。これにより、電子部品45AK60から発生した熱の放熱効果を高めることができる。なお、上記では、ヒートシンク45AK40に対する電子部品45AK60の配置態様について記載したが、これは当然に、電子部品45AK60に対するヒートシンク45AK40の配置態様として記載したとしても技術的に同等である。

30

## 【0152】

40

また、電子部品45AK60から発せられた熱は、ヒートシンク45AK40に伝わって放熱されるものだけでなく、その一部は電子部品45AK60から直接上方に放熱される。このように電子部品45AK60から直接上方に放熱される量は、電子部品45AK60の左右方向の長さが長いほどより大きくなる。ここで、図27に示すように、電子部品45AK60の左右方向の幅W1は、比較例である電子部品45AK61の左右方向の幅W2よりも大きい。そのため、電子部品45AK60の配置とした方が、電子部品45AK60から発せられた熱をより多く直接上方に向けて放熱させることができる。これにより、電子部品45AK60から発生した熱の放熱効果を高めることができる。

50

### 【 0 1 5 3 】

また、図28に示すように、後ケース45AK30の下部には空気が流入するための空気孔45AK33が形成され、後ケース45AK30の上部には空気を排出するための空気孔45AK32が形成されている。これにより、基板ケース45AK10内には、上下方向に沿った空気の通り道が確保されている。空気孔45AK33から流入した空気(矢印Y1)は上方へと移動する。上方へと移動した空気は、やがて、ヒートシンク45AK40に形成されたフィン45AK42の間に通り抜ける(矢印Y2)。このときに、ヒートシンク45AK40の熱が奪われ、空気が暖められる。暖められた空気は、ヒートシンク45AK40の上方に配置された高さの低い電子部品45AK51の間に通り(矢印Y3)、あるいは、高さの低い電子部品45AK51の後方を通り(矢印Y4)、上方へと移動する。やがて上方へと移動した空気は、後ケース45AK30の上部に形成された空気孔45AK32から排出される(矢印Y5)。このように、ヒートシンク45AK40の上方に、高さの低い電子部品45AK51を配置することで、電子部品45AK51間だけでなく、電子部品45AK51の後方に空気を通すことができる。一方、高さの高い電子部品45AK52は、ヒートシンク45AK40の上方及び下方には配置せずに、右方(図中左側)に配置している。これにより、下方から上方へと移動する空気の流れを阻害することなく、電子部品45AK60から発生した熱の放熱効果を高めることができる。

。

### 【 0 1 5 4 】

また、電子部品45AK51の長手方向を、上下方向に一致させていることにより、電子部品45AK51間を大きくとることができます。これにより、上方に移動する空気の流れを阻害することなく、電子部品45AK60から発生した熱の放熱効果を高めることができます。

20

### 【 0 1 5 5 】

また、ヒートシンク45AK40を、左右方向に平行に配列されたフィン45AK42が上下方向を向くように配置している。これにより、下方から上方に向けて移動する空気を、上下方向に沿ったフィン45AK42の間に通すことができる。これにより、上方方向に移動する空気の流れを阻害することなく、電子部品45AK60から発生した熱の放熱効果を高めることができます。

。

### 【 0 1 5 6 】

また、電子部品45AK60とヒートシンク45AK40との間に介在した熱伝導シート45AK70を、両面が粘着する柔軟な熱伝導シートとしている。そのため、熱伝導シート45AK70を、電子部品45AK60とヒートシンク45AK40とに隙間なく密着させることができます。これにより、電子部品45AK60から発生した熱を、熱伝導シート45AK70を介してヒートシンク45AK40にスムーズに伝えることができる。

30

### 【 0 1 5 7 】

また、後ケース45AK30には、発熱性の電子部品45AK60にヒートシンク45AK40を押圧する支持部45AK35が設けられている。これにより、ヒートシンク45AK40及び電子部品45AK60は熱伝導シート45AK70を押圧し、熱伝導シート45AK70に隙間なく密着する。これにより、電子部品45AK60から発生した熱を、熱伝導シート45AK70を介してヒートシンク45AK40にスムーズに伝えることができる。

40

### 【 0 1 5 8 】

また、図23、図24に示すように、基板45AK50は複数のねじ45AK81a～45AK81eによって後ケース45AK30に取り付けられる。複数のねじ45AK81a～45AK81eのうち、ねじ45AK81d及びねじ45AK81eは、電子部品45AK60の近傍のねじ挿通孔45AK55d及びねじ挿通孔45AK55eに挿通され、後ケース45AK30に締め付けられる。このように、電子部品45AK60の近傍で、ねじ45AK81d及びねじ45AK81eを後ケース45AK30に締めつけることで、電子部品45AK60に接着されたヒートシンク45AK40を後ケース45AK

50

30に向けて確実に押さえつけることができる。これにより、ヒートシンク45AK40と電子部品45AK60との接着を確実なものとすることができる。

#### 【0159】

また、支持部45AK35は、ベース板45AK30aの切欠き45AK30f内に配置されており、支持部45AK35と切欠き45AK30fとの間には、若干の隙間t(図25(a))が設けられている。この隙間tから、ヒートシンク45AK40に伝わった熱を基板ケース45AK10の外部へ逃がすことができる。これにより、電子部品45AK60から発生した熱を効率的に放熱することができる。

#### 【0160】

また、基板45AK50が後ケース45AK30に設置されていない場合、支持部45AK35は、突出部45AK35aを除き後ケース45AK30のベース板45AK30aと面一にある。一方、後ケース45AK30に基板45AK50が設置されると、支持部45AK35は、後方に撓んでベース板45AK30aとの間でずれが生じる。このように、支持部45AK35とベース板45AK30aとの間に生じるずれにより、隙間tから熱を逃がしやすくすることができる。これにより、電子部品45AK60から発生した熱を効率的に放熱することができる。

#### 【0161】

(他の実施形態1について)

図29は、他の実施形態1に係る遊技機の基板ケースにヒートシンク及び基板を取り付ける様子を示した断面図である。なお、他の形態に関する以下の説明では、上記の形態と異なる点を中心に説明する。なお、上記形態と同一の部材については、同一の符号を付すものとし、その説明は省略する。図29に示すように、後ケース45AK130には、図24に示す支持部45AK35の代わりに、ヒートシンク45AK40のフィン45AK42と当接し支持するばね45AK135が設けられている。ばね45AK135は、圧縮コイルばねであるが、その他、ばね座金等の板ばねを採用することができる。また、後ケース45AK130には、ヒートシンク45AK40の熱を外部に放出するための複数の空気孔45AK138が形成されている。なお、ヒートシンク45AK40及び基板45AK50の後ケース45AK130の取り付けかたについては、上記の形態と同様である。すなわち、ヒートシンク45AK40を位置決め部45AK134に合わせて載置する。このとき、ばね45AK135上にはフィン45AK42が載せられる。続いて、熱伝導シート45AK70が電子部品45AK60に貼付された基板45AK50を、挿入凸部45AK136に差し込むことで位置合わせをして、ヒートシンク45AK40上に載置する。続いて、ねじ45AK81eを基板45AK50に挿通して、ねじ孔45AK37eに締結する。これにより、ばね45AK135は、フィン45AK42に押圧されて縮むとともに、フィン45AK42を基板45AK50に向けて押圧する。これにより、熱伝導シート45AK70を、ヒートシンク45AK40及び電子部品45AK60に密着させることができる。

#### 【0162】

(他の実施形態2について)

また、図30は、他の実施形態2に係る遊技機の基板ケースにヒートシンク及び基板を取り付ける様子を示した断面図である。図30に示すように、後ケース45AK230には、上記実施形態とは異なり、支持部45AK35(図24)やばね45AK135(図29)のようなフィン45AK242を支持する部材は設けられていない。なお、後ケース45AK230には、ヒートシンク45AK240の熱を外部に放出するための複数の空気孔45AK238が形成されている。

#### 【0163】

基板45AK250には、ねじ45AK251を通すためのねじ挿通孔45AK252が形成されている。また、ヒートシンク45AK240には、ねじ45AK251を締めつけるためのねじ孔45AK243が形成されている。ねじ45AK251を、基板45AK250に形成されたねじ挿通孔45AK252に挿通し、ヒートシンク45AK24

10

20

30

40

50

0に形成されたねじ孔45AK243に締め付けることにより、ヒートシンク45AK240と基板45AK250とを一体化することができる。この時、ねじ45AK251を十分に締め付けることにより、ヒートシンク45AK240が基板45AK250側に引き寄せられる。これにより、熱伝導シート45AK270を、ヒートシンク45AK240及び電子部品45AK260に密着させることができる。

#### 【0164】

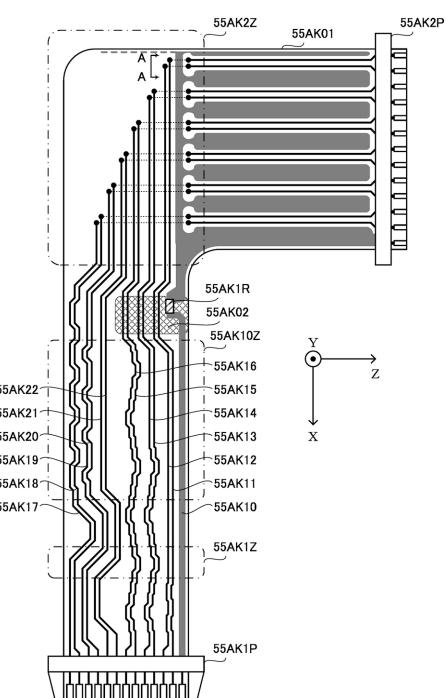

(特徴部55AKに関する説明)

図31は、本実施形態の特徴部55AKに関し、接続配線部材55AK01の構成例を示している。接続配線部材55AK01は、例えば演出制御基板12および画像表示装置5といった、複数の電気部品を電気的に接続可能な接続部材である。接続配線部材55AK01は、例えばフレキシブル配線基板あるいはフレキシブルフラットケーブルといった、一部または全部が可撓性を有する材料を用いて構成されればよい。接続配線部材55AK01では、複数の電気部品を複数の信号配線により接続するために、複数の信号配線を構成する配線のパターンが形成されている。接続配線部材55AK01において、複数の信号配線を構成する配線のパターンは、配線のパターン55AK10～55AK22を含んでいる。

#### 【0165】

配線のパターン55AK10～55AK22により構成される信号配線は、一端がコネクタプラグ55AK1Pに接続され、他端がコネクタプラグ55AK2Pに接続される。コネクタプラグ55AK1Pは、例えば演出制御基板12といった、一方の電気部品を複数の信号配線と電気的に接続可能とする配線接続部品である。コネクタプラグ55AK2Pは、例えば画像表示装置5といった、他方の電気部品を複数の信号配線と電気的に接続可能とする配線接続部品である。

#### 【0166】

配線のパターン55AK10は、例えばグランド電圧といった、基準電圧に維持される信号配線を形成する。配線のパターン55AK10は、線状の信号配線を形成してもよいし、一部または全部に面状の信号配線を形成してもよい。配線のパターン55AK11～55AK22は、2つの信号配線を組み合わせて一対の信号配線を構成してもよい。例えば配線のパターン55AK11により構成される信号配線は、配線のパターン55AK12により構成される信号配線と組み合わせて、一対の信号配線を構成している。

#### 【0167】

図31の構成例において、配線のパターン55AK21、55AK22には、蛇行形状が設けられていない。配線のパターン55AK11～55AK20には、少なくとも一部に蛇行形状が設けられている。例えば、配線のパターン55AK11～55AK20により構成される複数の信号配線は、図31に示す領域55AK10Zにて、一部または全部の信号配線が、直線形状または略直線形状の第1形状とは異なる蛇行形状などの第2形状となる。これに対し、配線のパターン55AK21、55AK22それぞれにより構成される信号配線は、図31に示す領域55AK10Zにて、直線形状または略直線形状の第1形状となる。配線のパターン55AK11～55AK20により構成される複数の信号配線のうち、配線のパターン55AK11、55AK12それぞれにより構成される信号配線は、図31に示す領域55AK10Zにて、直線形状または略直線形状の第1形状となる。その一方で、配線のパターン55AK11、55AK12それぞれにより構成される信号配線は、図31に示す領域55AK10Z以外の領域（領域55AK10Zよりもコネクタプラグ55AK1Pに近い領域）にて、例えば蛇行形状など、第1形状とは異なる第2形状となる。

#### 【0168】

図31に示す配線のパターン55AK10～55AK22により構成される複数の信号配線は、少なくとも一部の信号配線の配線長が、同一または略同一となる。例えば配線のパターン55AK11～55AK22により構成される複数の信号配線は、配線長が同一または略同一となる。このうち、配線のパターン55AK11～55AK20により構成

10

20

30

40

50

される複数の信号配線は、少なくとも一部分が蛇行形状となることにより、配線のパターン 55AK21、55AK22により構成される信号配線と、配線長が同一または略同一となればよい。配線のパターン 55AK21、55AK22により構成される信号配線は、配線のパターン 55AK10～55AK20により構成される信号配線に比べて、接続配線部材 55AK01の信号配線面上で、コネクタプラグ 55AK1Pとコネクタプラグ 55AK2Pにおける接続端子間の距離が長くなっていてもよい。接続配線部材 55AK01において、複数の信号配線が平行または略平行な第1形状となる平行配線部と、複数の信号配線のうち少なくとも1の信号配線が、他の信号配線と平行でない第2形状となる特定配線部とを含むように、配線のパターンが形成されてもよい。これにより、配線のパターンを配置する接続部材における面積の増大が抑制されて、構成の小型化を図ることができる。少なくとも一部の信号配線の配線長が、同一または略同一となるように配線のパターンが形成されることにより、複数の信号配線で伝送される信号の遅延時間差を減少させて、複数の信号配線で伝送される信号の信頼性を向上させることができる。10

#### 【0169】

接続配線部材 55AK01は、領域 55AK2Zにて曲折することにより、全体がL字形状または略L字形状を有するように形成されている。このように、接続配線部材 55AK01には、曲折部となる領域 55AK2Zが設けられている。接続配線部材 55AK01におけるコネクタプラグ 55AK1Pから領域 55AK2Zまでの区間では、配線のパターン 55AK11～55AK22により構成される複数の信号配線が、例えば図31に示すX軸に沿う方向といった、第1方向に延設されるように形成されている。接続配線部材 55AK01における領域 55AK2Zからコネクタプラグ 55AK2Pまでの区間では、配線のパターン 55AK11～55AK22により構成される複数の信号配線が、例えば図31に示すZ軸に沿う方向といった、第1方向とは異なる第2方向に延設されるように形成されている。接続配線部材 55AK01における領域 55AK2Zでは、配線のパターン 55AK11～55AK22により構成される複数の信号配線について、延設方向が第1方向から第2方向へと変更される。第1方向と第2方向は、互いに交差する方向であればよい。領域 55AK2Zは、所定角度を有する角形状であってもよいし、所定曲率を有する円弧形状であってもよい。なお、配線のパターン 55AK10により構成される信号配線は、一部または全部に面上の信号配線を含む場合に、線状の信号配線とは異なり延設方向を特定できないことがある。ただし、信号配線の全体としては、他の配線のパターン 55AK11～55AK22と同様に、コネクタプラグ 55AK1Pから領域 55AK2Zを介してコネクタプラグ 55AK2Pへと向かう方向に延設されるように形成されていればよい。20

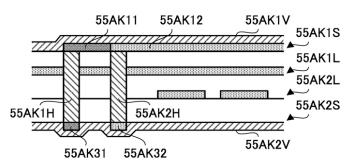

#### 【0170】

図32は、図31に示されるA-A断面図である。接続配線部材 55AK01は、例えばポリイミド樹脂などの合成樹脂を重ねて形成された多層構造を有し、各層の表面または内層には様々な配線のパターンを形成可能とされている。このような多層構造を有する接続配線部材 55AK01に形成された配線のパターンを介して、例えば演出制御基板12と画像表示装置5といった、複数の電気部品が電気的に接続される。図32に示す接続配線部材 55AK01の多層構造は、表面層 55AK1Sと、電源層 55AK1Lと、配線層 55AK2Lと、裏面層 55AK2Sとを含んでいる。表面層 55AK1Sは、カバー層 55AK1Vによって覆われて保護されている。裏面層 55AK2Sは、カバー層 55AK2Vによって覆われて保護されている。30

#### 【0171】

接続配線部材 55AK01における一面となる表面には、表面層 55AK1Sが設けられ、信号配線を構成する配線のパターン 55AK10～55AK22が形成されている。接続配線部材 55AK01における他面となる裏面には、裏面層 55AK2Sが設けられる。裏面層 55AK2Sには、配線のパターン 55AK10～55AK22により構成される複数の信号配線に対応して、複数の信号配線を構成する配線のパターン 55AK40～55AK52が形成されていればよい。このように、複数の信号配線を構成する配線の4050

パターンは、接続配線部材 55AK01 の両面に形成されればよい。

【0172】

接続配線部材 55AK01 の表面層 55AK1S に形成された配線のパターン 55AK11 は、接続配線部材 55AK01 の表面層 55AK1S および裏面層 55AK2S を貫通するスルーホール 55AK1H などの貫通部を介して、裏面層 55AK2S に形成された配線のパターン 55AK31 と電気的に接続されている。接続配線部材 55AK01 の表面層 55AK1S に形成された配線のパターン 55AK12 は、接続配線部材 55AK01 の表面層 55AK1S および裏面層 55AK2S を貫通するスルーホール 55AK2H などの貫通部を介して、裏面層 55AK2S に形成された配線のパターン 55AK32 と電気的に接続されている。その他、接続配線部材 55AK01 の表面層 55AK1S に形成された配線のパターン 55AK10、55AK13～55AK22 は、スルーホールなどの貫通部を介して、裏面層 55AK2S に形成された配線のパターン 55AK40、55AK43～55AK52 と電気的に接続されればよい。配線のパターン 55AK10～55AK22 により構成される複数の信号配線のうちには、接続配線部材 55AK01 の表面層 55AK1S にのみ形成され、裏面層 55AK2S に形成された信号配線とは電気的に接続されない信号配線が含まれてもよい。接続配線部材 55AK01 の領域 55AK2Z には、スルーホール 55AK1H、55AK2H のように、一面となる表面に設けられた表面層 55AK1S において信号配線を構成する配線のパターンと、他面となる裏面に設けられた裏面層 55AK2S において信号配線を構成する配線のパターンとを、電気的に接続可能な貫通部が設けられている。10

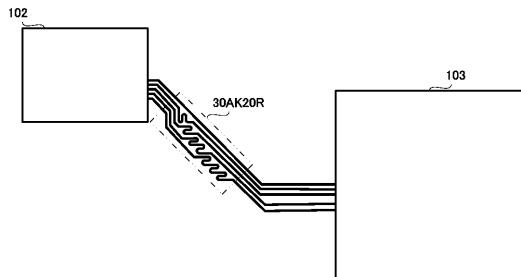

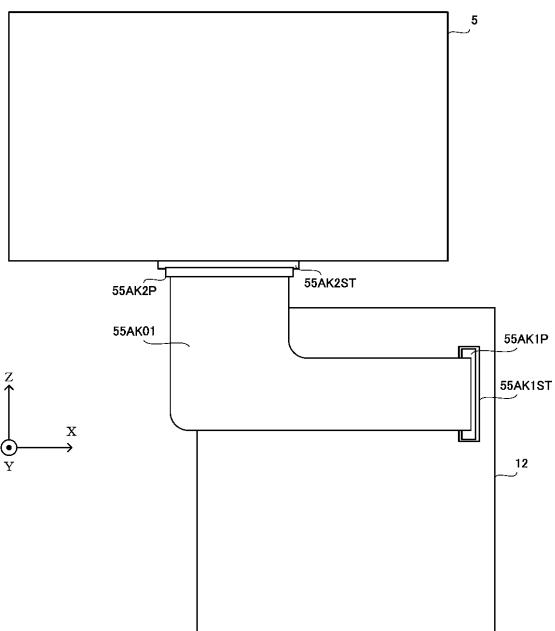

【0173】

図 33 は、接続配線部材 55AK01 を用いた演出制御基板 12 と画像表示装置 5 の接続例を示している。接続配線部材 55AK01 が備えるコネクタプラグ 55AK1P は、演出制御基板 12 に設けられたコネクタポート 55AK1ST に差し込まれる。接続配線部材 55AK01 が備えるコネクタプラグ 55AK2P は、画像表示装置 5 に設けられたコネクタポート 55AK2ST に差し込まれる。演出制御基板 12 に設けられたコネクタポート 55AK1ST や画像表示装置 5 に設けられたコネクタポート 55AK2ST は、上記実施の形態で示されたレセプタクル KRE1～KRE4 と同様の電気部品であり、他の電気部品との間で電気的に接続される信号配線を着脱自在に接続可能な配線接続装置の構成を有すればよい。例えば、一方の電気部品であるコネクタポート 55AK1ST は、演出制御基板 12 に設けられて、接続配線部材 55AK01 のコネクタプラグ 55AK1P を着脱可能に構成され、他方の電気部品であるコネクタポート 55AK2ST は、画像表示装置 5 に設けられて、接続配線部材 55AK01 のコネクタプラグ 55AK2P を着脱可能に構成される。コネクタポート 55AK1ST にコネクタプラグ 55AK1P を装着し、コネクタポート 55AK2ST にコネクタプラグ 55AK2P を装着することにより、接続配線部材 55AK01 に形成された配線のパターン 55AK10～55AK22 が構成する複数の信号配線は、一方の電気部品であるコネクタポート 55AK1ST と他方の電気部品であるコネクタポート 55AK2ST との間を電気的に接続可能となる。30

【0174】

図 34 は、図 33 のような接続例における接続配線部材 55AK01 の上面図である。接続配線部材 55AK01 では、少なくとも領域 55AK1Z が可撓性を有している。これにより、コネクタポート 55AK1ST にコネクタプラグ 55AK1P を装着し、コネクタポート 55AK2ST にコネクタプラグ 55AK2P を装着した場合には、領域 55AK1Z にて接続配線部材 55AK01 が湾曲するように折り曲げられ、コネクタプラグ 55AK1P とコネクタプラグ 55AK2P の方向を、コネクタポート 55AK1ST とコネクタポート 55AK2ST の方向にあわせて、調整することができる。図 33 および図 34 に示す例では、演出制御基板 12 に設けられたコネクタポート 55AK1ST に対し、接続配線部材 55AK01 のコネクタプラグ 55AK1P を Y 軸正方向から Y 軸負方向に向けて差し込むことにより装着する。また、画像表示装置 5 に設けられたコネクタボ40

50

ー<sup>ト</sup>5 5 A K 2 S Tに対し、接続配線部材5 5 A K 0 1のコネクタプラグ5 5 A K 2 PをZ軸負方向からZ軸正方向に向けて差し込むことにより装着する。例えば、まずは、コネクタプラグ5 5 A K 2 Pをコネクタポート5 5 A K 2 S Tに差し込んで装着し、その後、コネクタプラグ5 5 A K 1 Pをコネクタポート5 5 A K 1 S Tに差し込んで装着する。このような順番で装着すれば、接続配線部材5 5 A K 0 1の領域5 5 A K 1 Zが有する可撓性により、接続配線部材5 5 A K 0 1を容易に装着することができる。

#### 【0175】

図35は、他の接続例を示している。図35に示す接続例でも、接続配線部材5 5 A K 0 1が備えるコネクタプラグ5 5 A K 1 Pは演出制御基板1 2に設けられたコネクタポート5 5 A K 1 S Tに差し込まれ、接続配線部材5 5 A K 0 1が備えるコネクタプラグ5 5 A K 2 Pは画像表示装置5に設けられたコネクタポート5 5 A K 2 S Tに差し込まれる。<sup>10</sup>演出制御基板1 2のコネクタポート5 5 A K 1 S Tは、カバーボディ3 0 1からみてY軸正方向側となるカバーボディ3 0 1の背面側に配置され、画像表示装置5のコネクタポート5 5 A K 2 S Tは、カバーボディ3 0 1からみてY軸負方向側となるカバーボディ3 0 1の前面側に配置されている。接続配線部材5 5 A K 0 1は、カバーボディ3 0 1に形成された開口部5 5 A K 3 0を介して、コネクタプラグ5 5 A K 1 Pが演出制御基板1 2のコネクタポート5 5 A K 1 S Tに装着され、コネクタプラグ5 5 A K 2 Pが画像表示装置5のコネクタポート5 5 A K 2 S Tに装着される。

#### 【0176】

図36は、図35のような接続例における接続配線部材5 5 A K 0 1の上面図である。<sup>20</sup>接続配線部材5 5 A K 0 1では、領域5 5 A K 1 Zの他に、領域5 5 A K 1 0 Zも可撓性を有していてもよい。図35に示す接続例において、コネクタポート5 5 A K 1 S Tにコネクタプラグ5 5 A K 1 Pを装着し、コネクタポート5 5 A K 2 S Tにコネクタプラグ5 5 A K 2 Pを装着した場合には、領域5 5 A K 1 Zに加え、領域5 5 A K 1 0 Zにて接続配線部材5 5 A K 0 1が湾曲するように折り曲げられ、コネクタプラグ5 5 A K 1 Pとコネクタプラグ5 5 A K 2 Pの方向を、コネクタポート5 5 A K 1 S Tとコネクタポート5 5 A K 2 S Tの方向にあわせて、調整することができる。図35および図36に示す例でも、図33および図34に示された例と同様に、まずは、コネクタプラグ5 5 A K 2 Pをコネクタポート5 5 A K 2 S Tに差し込んで装着する。続いて、接続配線部材5 5 A K 0 1をコネクタプラグ5 5 A K 1 Pからカバーボディ3 0 1の開口部5 5 A K 3 0に通すこと<sup>30</sup>で、カバーボディ3 0 1の前面側から背面側へと接続配線部材5 5 A K 0 1を引き出す。その後、コネクタプラグ5 5 A K 1 Pをコネクタポート5 5 A K 1 S Tに差し込んで装着する。このような順番で装着すれば、接続配線部材5 5 A K 0 1の領域5 5 A K 1 0 Zが有する可撓性により、カバーボディ3 0 1の開口部5 5 A K 3 0にて折り返すようにクセ付けられ、接続配線部材5 5 A K 0 1を容易に装着することができる。

#### 【0177】

図33～図36に示された接続例では、接続配線部材5 5 A K 0 1の領域5 5 A K 1 Zや領域5 5 A K 1 0 Zが有する可撓性により、接続配線部材5 5 A K 0 1の装着時に湾曲するように折り曲げられる。このように、接続配線部材5 5 A K 0 1は、例えば基体が柔軟なシート状に形成され、領域5 5 A K 1 Zや領域5 5 A K 1 0 Zが可撓性を有している。<sup>40</sup>こうした接続配線部材5 5 A K 0 1に対し、補強部材5 5 A K 0 2が取り付けられている。補強部材5 5 A K 0 2は、例えばアクリル系樹脂材料などの合成樹脂材料、石英ガラスなどの石英系材料、セラミック系材料その他の材料を選択的に用いて、可撓性を有しないように構成されればよい。この補強部材5 5 A K 0 2が取り付けられた位置では、例えば配線のパターン5 5 A K 1 0により構成される信号配線と接続される回路部品5 5 A K 1 Rが実装されている。回路部品5 5 A K 1 Rは、上記実施の形態における回路部品4 2 A K 1 Rと同様に、回路素子あるいは機能回路を構成するものであればよい。例えば、回路部品5 5 A K 1 Rは、配線のパターン5 5 A K 1 0により構成される信号配線が基準電圧となるグランド電圧あるいは所定の電源電圧に維持される場合に、信号配線でのノイズ発生を防止するノイズ除去回路として構成されてもよい。回路部品5 5 A K 1 Rは、<sup>50</sup>

可撓性を有しない補強部材 55AK02 が取り付けられた位置にて実装されているので、可撓性を有する位置にて実装された場合と比較して、接続配線部材 55AK01 からの脱落や信号配線の断線が発生しにくくなる。

#### 【0178】

複数の信号配線を構成する配線のパターンは、接続配線部材 55AK01 の両面に形成され、接続配線部材 55AK01 の領域 55AK2Z には、貫通部としてのスルーホールが設けられている。これにより、接続配線部材 55AK01 の一面となる表面に設けられた信号配線と、接続配線部材 55AK01 の他面となる裏面に設けられた信号配線とが、電気的に接続可能となる。図 33～図 36 に示された接続例では、接続配線部材 55AK01 の領域 55AK1Z や領域 55AK10Z が有する可撓性により、接続配線部材 55AK01 の装着時に湾曲するように折り曲げられる。その一方で、接続配線部材 55AK01 の領域 55AK2Z は、接続配線部材 55AK01 の装着時に折り曲げられない。このように、複数の電気部品を複数の信号配線により接続した場合に、接続配線部材 55AK01 にて形状が変化する領域 55AK1Z や領域 55AK10Z には、貫通部としてのスルーホールが設けられていない。形状が変化する位置に貫通部が設けられていないので、形状が変化する位置に設けられた場合と比較して、接続配線部材 55AK01 の強度低下や信号配線の断線が発生しにくくなる。なお、スルーホールなどの貫通部が設けられる位置では、接続配線部材 55AK01 の基体として、例えばリジッド配線板といった、補強部材 55AK02 と同様の部材として、あるいは補強部材 55AK02 とは異なる材料により形成された部材として、可撓性を有しない部材が用いられてもよい。また、貫通部は、接続配線部材 55AK01 の一面となる表面層 55AK1S および他面となる裏面層 55AK2S を貫通するスルーホールに限定されず、例えば接続配線部材 55AK01 の一面あるいは他面と、接続配線部材 55AK01 の内層として構成された導体層とを貫通するビアなどであってもよい。10

#### 【0179】

(特徴部 56AK に関する説明)

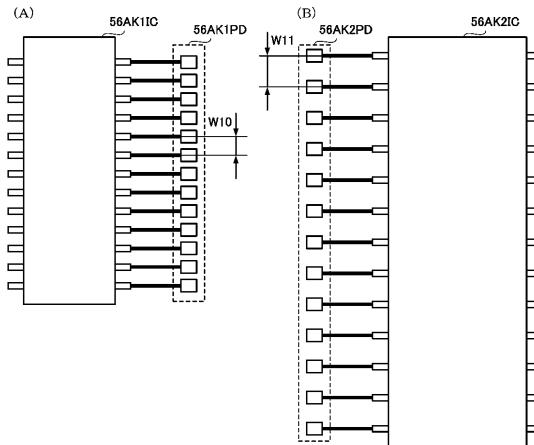

図 37 は、本実施形態の特徴部 56AK に関し、コネクタプラグやコネクタポートの構成例を示している。図 37 (A) は、接続配線部材 55AK01 のコネクタプラグ 55AK1P を差し込んで装着可能なコネクタポート 56AK01 の構成例を示している。図 37 (B) は、接続配線部材 55AK01 のコネクタプラグ 55AK2P を差し込んで装着可能なコネクタポート 56AK02 の構成例を示している。コネクタポート 56AK01 は、例えば図 33 や図 35 に示された演出制御基板 12 が備えるコネクタポート 55AK1ST として用いられるものであればよい。コネクタポート 56AK02 は、例えば図 33 や図 35 に示された画像表示装置 5 が備えるコネクタポート 55AK2ST として用いられるものであればよい。30

#### 【0180】

コネクタポート 56AK01 では、複数の信号配線と接続される複数の端子が、第 1 ピッチ W10 で設けられている。コネクタポート 56AK02 では、複数の信号配線と接続される複数の端子が、第 1 ピッチ W10 とは異なる第 2 ピッチ W11 で設けられている。例えばコネクタポート 56AK01 では、第 1 ピッチ W10 が 1mm 以上 3mm 未満となるように、複数の端子が並んで配置されていればよい。コネクタポート 56AK02 では、第 2 ピッチ W11 が 3mm 以上 5mm 未満となるように、複数の端子が並んで配置されていればよい。第 1 ピッチ W10 は第 2 ピッチ W11 よりも短くなるように設定されてもよいし、第 1 ピッチ W10 は第 2 ピッチ W11 よりも長くなるように設定されてもよい。このように、コネクタポート 56AK01 は、複数の導体としての端子が第 1 ピッチ W10 で設けられた第 1 部品となり、コネクタポート 56AK02 は、複数の導体としての端子が第 2 ピッチ W11 で設けられた第 2 部品となる。また、コネクタポート 56AK01 は、接続配線部材 55AK01 の一端に設けられたコネクタプラグ 55AK1P が差し込まれて装着されることにより、接続配線部材 55AK01 に形成された配線のパターン 55AK10～55AK22 などで構成される複数の信号配線を着脱自在に接続可能とする4050