(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6211971号

(P6211971)

(45) 発行日 平成29年10月11日(2017.10.11)

(24) 登録日 平成29年9月22日(2017.9.22)

(51) Int.Cl.

F 1

G O 1 R 31/28 (2006.01)

G O 1 R 31/28

V

H O 1 L 21/822 (2006.01)

H O 1 L 27/04

T

H O 1 L 27/04 (2006.01)

請求項の数 12 (全 17 頁)

(21) 出願番号

特願2014-63880 (P2014-63880)

(22) 出願日

平成26年3月26日(2014.3.26)

(65) 公開番号

特開2015-184265 (P2015-184265A)

(43) 公開日

平成27年10月22日(2015.10.22)

審査請求日

平成28年12月8日(2016.12.8)

(73) 特許権者 303046277

旭化成エレクトロニクス株式会社

東京都千代田区神田神保町一丁目105番地

(74) 代理人 100066980

弁理士 森 哲也

(74) 代理人 100103850

弁理士 田中 秀▲てつ▼

(72) 発明者 深瀬 智史

神奈川県厚木市岡田3050番地 旭化成

エレクトロニクス株式会社内

審査官 繢山 浩二

最終頁に続く

(54) 【発明の名称】半導体テスト回路及びICチップ

## (57) 【特許請求の範囲】

## 【請求項1】

デジタル回路の故障検知を行うテストモードを有する半導体テスト回路において、

スキャンイネーブル信号に基づいて、通常動作とスキャンデータ信号が入力されるシフ

トレジスタを構成するスキャン動作とを選択する選択回路を有する複数のフリップフロップ(12a～12c)と、

前記スキャンデータ信号が入力されて前記複数のフリップフロップへ出力する組み合わ

せ回路(11)と、

前記スキャンデータ信号が入力されて前記スキャンイネーブル信号を出力するカウンタ

(13)と、

を備える半導体テスト回路。

## 【請求項2】

前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期し

て取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが

配されない区間に配されるカウンタ制御信号と、を有し、

前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が

制御される請求項1に記載の半導体テスト回路。

## 【請求項3】

前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期し

て取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが

10

20

配されない区間に配されるカウンタ制御信号と、を有し、

前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が立ち上がる又は立ち下がる請求項 1 又は 2 に記載の半導体テスト回路。

#### 【請求項 4】

前記カウンタは、前記スキャンデータ信号と前記スキャンクロック信号が入力され、状態遷移するカウンタである請求項 2 又は 3 に記載の半導体テスト回路。

#### 【請求項 5】

前記カウンタは、少なくとも 4 つの状態を遷移し、

前記データ信号と前記スキャンクロック信号により、第 1 の状態と第 2 の状態の遷移を繰り返し、また、第 3 の状態と第 4 の状態の遷移を繰り返し、

10

前記カウンタ制御信号により、前記第 1 の状態又は前記第 2 の状態から、前記第 3 の状態又は第 4 の状態への遷移、または、前記第 3 の状態又は前記第 4 の状態から、前記第 1 の状態又は第 2 の状態への遷移を行い、

前記第 1 の状態又は前記第 2 の状態に対応するカウント値が通常動作に対応する前記イネーブル信号であり、前記第 3 の状態又は前記第 4 の状態に対応するカウント値がスキャン動作に対応する前記イネーブル信号である請求項 4 に記載の半導体テスト回路。

#### 【請求項 6】

前記カウンタは、前記スキャンクロック信号により、第 1 の状態又は第 2 の状態から第 1 の状態へリセットする遷移を行い、及び、第 3 の状態又は第 4 の状態から第 3 の状態へリセットする遷移を行う請求項 5 に記載の半導体テスト回路。

20

#### 【請求項 7】

前記カウンタは、`2 bit` バイナリカウンタであり、

前記スキャンイネーブル信号は、前記カウンタのカウント値の M S B 又は L S B である請求項 1 ~ 6 のいずれか一項に記載の半導体テスト回路。

#### 【請求項 8】

複数のフリップフロップと組み合わせ回路とを有するデジタルブロックを、スキャンクロックと、スキャンデータ信号と、スキャンイネーブル信号と、によりスキャンテストを行う I C チップであって、

スキャンクロックが入力される第 1 の P A D ( S C A N C L K ) と、

スキャンデータ信号が入力される第 2 の P A D ( S C A N I N ) と、

30

前記第 2 の P A D に接続され、前記スキャンデータ信号から前記スキャンイネーブル信号を出力するカウンタと、

を備える I C チップ。

#### 【請求項 9】

前記カウンタのクロックラインに、前記第 2 の P A D が接続され、

前記カウンタの第 1 のリセットラインに、前記第 1 の P A D が論理素子を介して接続される請求項 8 に記載の I C チップ。

#### 【請求項 10】

前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるパルス信号と、を有する請求項 8 又は 9 に記載の I C チップ。

40

#### 【請求項 11】

前記データ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力された後、次にスキャンクロックが配されるまでの間に、前記パルス信号が配される請求項 10 に記載の I C チップ。

#### 【請求項 12】

前記次のスキャンクロックが配された後、別のデータ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力されるまでの間に、前記パルス信号が配される請求項 11 に記載の I C チップ。

#### 【発明の詳細な説明】

50

## 【技術分野】

## 【0001】

本発明は、半導体テスト回路及びICチップに関し、より詳細には、スキャンデータが入力されるSCANINとスキャンイネーブル信号が入力されるSCANENBを、同一ピンとした半導体テスト回路及びICチップに関する。

## 【背景技術】

## 【0002】

LSI (Large Scale Integration; 大規模集積回路) のデジタルブロックは、一般に組み合わせ回路とFlip Flop (FF) による順序回路から構成されている。

10

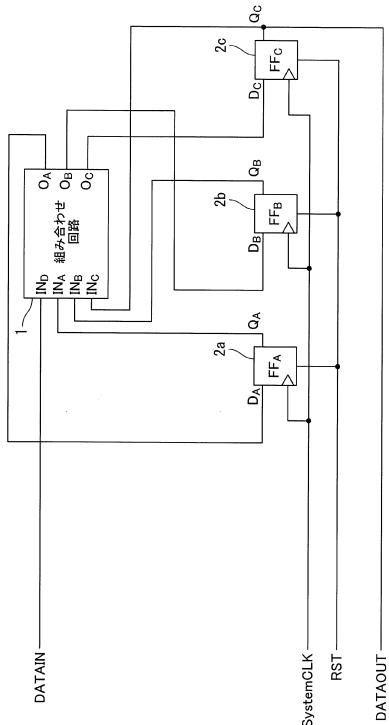

図1は、一般的なLSI回路の例を示す回路構成図である。入力ピンDATAINと、出力ピンDATAOUTと、FFのリセット用ピンRSTと、FFのCLK用ピンSystemCLKをピンとして有している。FF<sub>A</sub>2a、FF<sub>B</sub>2b、FF<sub>C</sub>2cは、SystemCLKで動作するFFである。それぞれのFFの入力D<sub>A</sub>、D<sub>B</sub>、D<sub>C</sub>は、組み合わせ回路1の出力O<sub>A</sub>、O<sub>B</sub>、O<sub>C</sub>と接続し、FFの出力Q<sub>A</sub>、Q<sub>B</sub>、Q<sub>C</sub>とDATAINピンは組み合わせ回路の入力IN<sub>A</sub>、IN<sub>B</sub>、IN<sub>C</sub>、IN<sub>D</sub>に接続されるように構成された回路である。

## 【0003】

一般に、LSIのテストは、回路中の全FFをMUX付きのFFに置き換え、そのMUXのセレクタ信号により全FFをシフトレジスタ回路にする「SCAN動作」を出来るようにしている。これをSCAN化という。

20

SCAN化された回路は、SCAN動作により、回路中の任意のノードに任意の値を設定できる制御 (control)、回路中の任意のノードの値を出力できる (observe) 観測が自由となる。つまり、回路中の組み合わせ回路等に自由な値を設定し、その出力をモニタすることによって、故障検出率の高いテストを行うことができる。

## 【0004】

このSCANテストを行うためには、例えば、以下の外部入力ピンを必要とする。

SCANIN: SCANデータの入力ピン

SCANENB: SCANバスと通常バスを切り替える入力ピン

SCANCLK: SCAN回路のCLK

30

SCANOUT: SCAN回路の出力ピン

SCANRST: SCAN回路のリセットピン

TESTMODE: SCANテストの許可ピン

## 【0005】

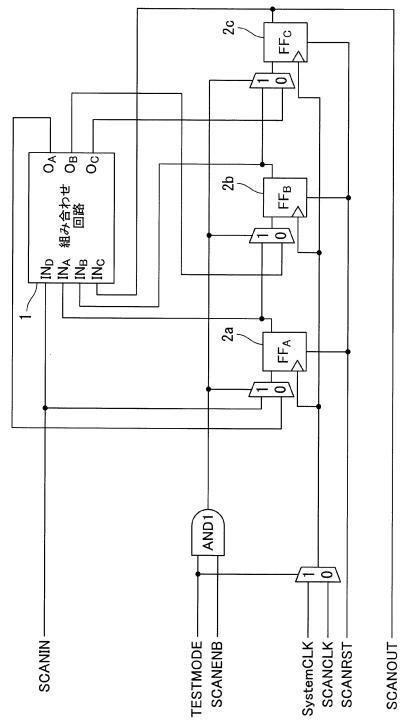

図2は、図1に示したSCAN化した回路構成図で、SCANテストを可能にした回路構成図である。入力ピンSCANINと、出力ピンSCANOUTと、FFのリセット用ピンSCANRSTと、FFの通常CLK用ピンSystemCLKと、FFのSCANテストCLK用ピンSCANCLKと、SCANバスと通常バスの切り替えピンSCANENBと、SCANテストの許可ピンTESTMODEをピンとして有している。組み合わせ回路1は、図1と同様である。

40

## 【0006】

全FFは、図1からMUX付のFFに変わり、そのセレクタ信号はSCANENBとTESTMODEのAND出力となる。このAND1はTESTMODEが0のとき、つまり、SCANテストモードではないときに、FFの入力が誤選択されないように保護するためである。以下、TESTMODEが1のときを考えると、FFのセレクタは、SCANENBが0のときは、図1と同様のバスとなり、SCANENBが1のときは、全FFがSCANINからSCANOUTまでのシフトレジスタとして動作する。

## 【0007】

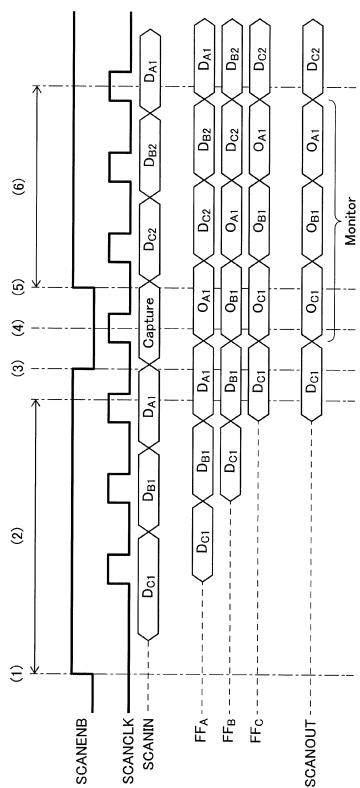

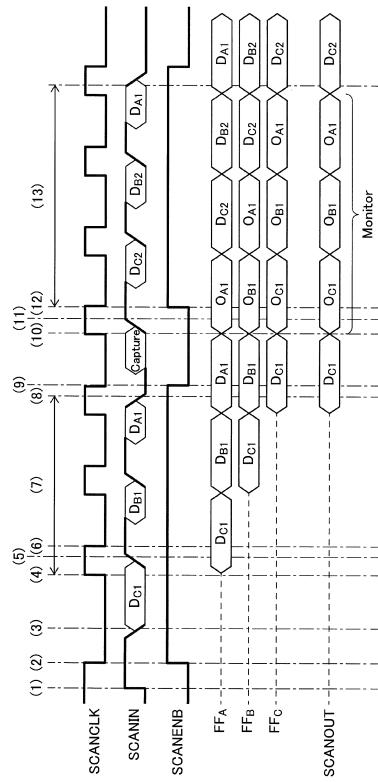

図3は、図2に示した回路における一般的なSCANテスト動作について説明するためのタイミングチャートを示す図である。前提としてTESTMODEは1とする。

50

- (1) ; SCANENBを1にして全FFをSCAN動作可能にする。

- (2) ; 全FFに所望の値をSCAN動作によりセットする(図3ではFF<sub>A</sub>、；FF<sub>B</sub>、FF<sub>B</sub>にそれぞれD<sub>A1</sub>、D<sub>B1</sub>、D<sub>C1</sub>をセットしている)。

- (3) ; SCANENBを0にして通常バスに戻す。

- (4) ; SCANCLKからCLK入力し、通常バスの出力(=組み合わせ回路の出力)を各FFに取り込む(図3ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ組み合わせ回路出力のO<sub>A1</sub>、O<sub>B1</sub>、O<sub>C1</sub>が取り込まれる)。

- (5) ; SCANENBを1にして全FFをSCAN動作可能にする。

- (6) ; SCANCLKを入力して全FFの値(O<sub>A1</sub>、O<sub>B1</sub>、O<sub>C1</sub>)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値D<sub>A2</sub>、D<sub>B2</sub>、D<sub>C2</sub>をセットする)。 10

- (7) ; 上記(3)～(6)を繰り返す。

以上が一般的なスキャン化した回路のテスト動作である。

#### 【0008】

例えは、特許文献1では、ピン数の少ないLSIでもSCANテストを可能にするために、SCANINとSCANENBを共通化する方法を提案している。

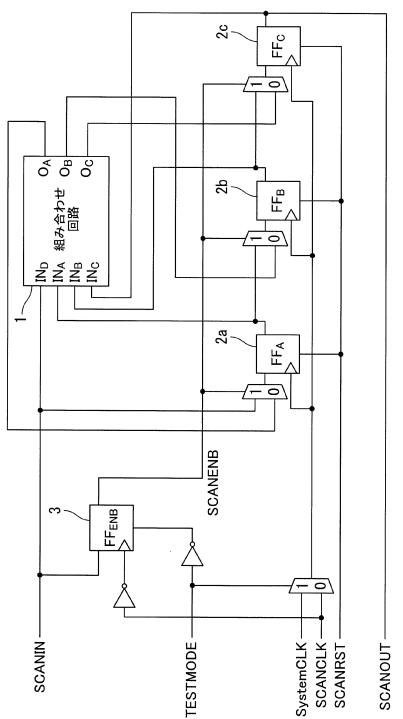

図4は、特許文献1に記載されているSCANテストを可能にした回路構成図である。以下のような特徴を有している。

SCAN回路はSCANCLKの正転信号をCLKとする。

SCANINをデータ、SCANCLKの反転信号をCLK入力としたFFであるFF<sub>ENB3</sub>の出力をSCANENBとする。 20

#### 【0009】

図5は、図4に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。前提としてTEST MODEは1とする。

- (1) ; SCANCLKが1のときにSCANINを1にする。

- (2) ; SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFF<sub>ENB</sub>に1を取り込むことでSCAN動作を可能にする。

- (3) ; SCANCLKが0のときにSCANINを所望の値にする。

- (4) ; SCANCLKの立ち上がりEdgeでSCANINからSCAN化されたFF<sub>A</sub>に所望の値を取り込む(図5ではFF<sub>A</sub>にD<sub>C1</sub>をセットしている)。 30

- (5) ; SCANCLKが1のときにSCANINを1にする。

#### 【0010】

(6) ; SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFF<sub>ENB</sub>に1を取り込むことで引き続きSCAN動作を可能にする。

(7) ; 上記(3)～(6)を繰り返し全FFに所望の値をセットする(図5ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれD<sub>A1</sub>、D<sub>B1</sub>、D<sub>C1</sub>をセットしている)。

(8) ; SCANCLKが1のときにSCANINを0にする。

(9) ; SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFF<sub>ENB</sub>に0を取り込むことで通常バスに戻す。

(10) SCANCLKの立ち上がりEdgeで、通常バスの出力(=組み合わせ回路の出力)を各FFに取り込む(図5ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ組み合わせ回路出力のO<sub>A1</sub>、O<sub>B1</sub>、O<sub>C1</sub>が取り込まれる)。 40

#### 【0011】

(11) ; SCANCLKが1のときにSCANINを1にする。

(12) ; SCANCLKの立ち下がりEdgeでSCANINからSCANENB用FFであるFF<sub>ENB</sub>に1を取り込むことでSCAN動作を可能にする。

(13) ; SCANCLKを入力して全FFの値(O<sub>A1</sub>、O<sub>B1</sub>、O<sub>C1</sub>)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値D<sub>A2</sub>、D<sub>B2</sub>、D<sub>C2</sub>をセットする。SCANENBは1のままになるようにしておく)。

(14) ; 上記(8)～(12)を繰り返す。 50

**【先行技術文献】****【特許文献】****【0012】**

【特許文献1】米国特許第7380185号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0013】**

上述した特許文献1により、SCANINとSCANENBを共用してSCANテストが可能になる。しかし、通常のSCANテストでは、SCAN回路は、SCANCLKの立ち上がりと立下りEdgeで動作するFFが混在してもよいが、上述した従来の手法では、SCANENBは、SCANCLKの立下りEdgeで生成するため、SCAN回路は、必ずSCANCLKの立ち上がりEdgeで動作する必要があり、設計の自由度がない。また、立ち上がりEdge(SCAN用)と立下りEdge(SCANENB用)のFFが混在しているため、それぞれのFFのセットアップタイムとホールドタイムを確保する必要があり、SCANCLK周波数を挙げることができず、テスト時間の短縮ができない。

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、設計の自由度が高く、また、テスト時間が短い半導体テスト回路及びICチップを提供することにある。

**【課題を解決するための手段】****【0014】**

本発明は、このような目的を達成するためになされたもので、請求項1に記載の発明は、デジタル回路の故障検知を行うテストモードを有する半導体テスト回路において、スキャンイネーブル信号に基づいて、通常動作とスキャンデータ信号が入力されるシフトレジスタを構成するスキャン動作とを選択する選択回路を有する複数のフリップフロップ(12a～12c)と、前記スキャンデータ信号が入力されて前記複数のフリップフロップへ出力する組み合わせ回路(11)と、前記スキャンデータ信号が入力されて前記スキャンイネーブル信号を出力するカウンタ(13)と、を備えることを特徴とする。

**【0015】**

また、請求項2に記載の発明は、請求項1に記載の発明において、前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が制御されることを特徴とする。

また、請求項3に記載の発明は、請求項1又は2に記載の発明において、前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、前記カウンタにおいて、前記カウンタ制御信号により、前記スキャンイネーブル信号が立ち上がる又は立ち下がることを特徴とする。

**【0016】**

また、請求項4に記載の発明は、請求項2又は3に記載の発明において、前記カウンタは、前記スキャンデータ信号と前記スキャンクロック信号が入力され、状態遷移するカウンタであることを特徴とする。

また、請求項5に記載の発明は、請求項4に記載の発明において、前記カウンタは、少なくとも4つの状態を遷移し、前記データ信号と前記スキャンクロック信号により、第1の状態と第2の状態の遷移を繰り返し、また、第3の状態と第4の状態の遷移を繰り返し、前記カウンタ制御信号により、前記第1の状態又は前記第2の状態から、前記第3の状態又は第4の状態への遷移、または、前記第3の状態又は前記第4の状態から、前記第1の状態又は第2の状態への遷移を行い、前記第1の状態又は前記第2の状態に対応するカウント値が通常動作に対応する前記イネーブル信号であり、前記第3の状態又は前記第4

10

20

30

40

50

の状態に対応するカウント値がスキャン動作に対応する前記イネーブル信号であることを特徴とする。

#### 【0017】

また、請求項6に記載の発明は、請求項5に記載の発明において、前記カウンタは、前記スキャンクロック信号により、第1の状態又は第2の状態から第1の状態へリセットする遷移を行い、及び、第3の状態又は第4の状態から第3の状態へリセットする遷移を行うことを特徴とする。

また、請求項7に記載の発明は、請求項1～6のいずれか一項に記載の発明において、前記カウンタは、2bitバイナリカウンタであり、前記スキャンイネーブル信号は、前記カウンタのカウント値のMSB又はLSBであることを特徴とする。 10

#### 【0018】

また、請求項8に記載の発明は、複数のフリップフロップと組み合わせ回路とを有するデジタルブロックを、スキャンクロックと、スキャンデータ信号と、スキャンイネーブル信号と、によりスキャンテストを行うICチップであって、スキャンクロックが入力される第1のPAD(SCANCLK)と、スキャンデータ信号が入力される第2のPAD(SCANIN)と、前記第2のPADに接続され、前記スキャンデータ信号から前記スキャンイネーブル信号を出力するカウンタと、を備えることを特徴とする。

#### 【0019】

また、請求項9に記載の発明は、請求項8に記載の発明において、前記カウンタのクロックラインに、前記第2のPADが接続され、前記カウンタの第1のリセットラインに、前記第1のPADが論理素子を介して接続されることを特徴とする。 20

また、請求項10に記載の発明は、請求項8又は9に記載の発明において、前記スキャンデータ信号は、前記複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、前記複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるパルス信号と、を有することを特徴とする。

#### 【0020】

また、請求項11に記載の発明は、請求項10に記載の発明において、前記データ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力された後、次にスキャンクロックが配されるまでの間に、前記パルス信号が配されることを特徴とする。 30

また、請求項12に記載の発明は、請求項11に記載の発明において、前記次のスキャンクロックが配された後、別のデータ信号を前記複数のフリップフロップに、前記スキャンクロックに同期して設定するために順次データが入力されるまでの間に、前記パルス信号が配されることを特徴とする。

#### 【発明の効果】

#### 【0021】

本発明によれば、ピン数を削減したうえで、設計の自由度が高く、また、テスト時間が短い半導体テスト回路及びICチップを実現することができる。

#### 【図面の簡単な説明】

#### 【0022】

【図1】一般的なLSI回路の例を示す回路構成図である。 40

【図2】図1に示したSCAN化した回路構成図である。

【図3】図2に示した回路における一般的なSCANテスト動作について説明するためのタイミングチャートを示す図である。

【図4】特許文献1に記載されているSCANテストを可能にした回路構成図である。

【図5】図4に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

【図6】本発明に係るシフトレジスタ回路の回路構成図である。

【図7】図6に示したシフトレジスタ回路の動作を説明するためのタイミングチャートを示す図である。 50

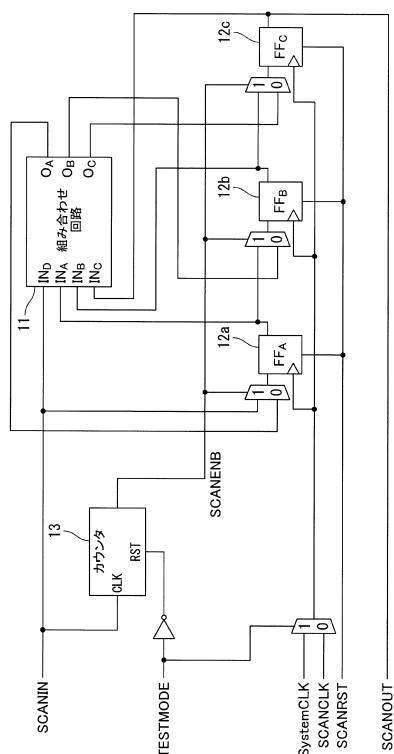

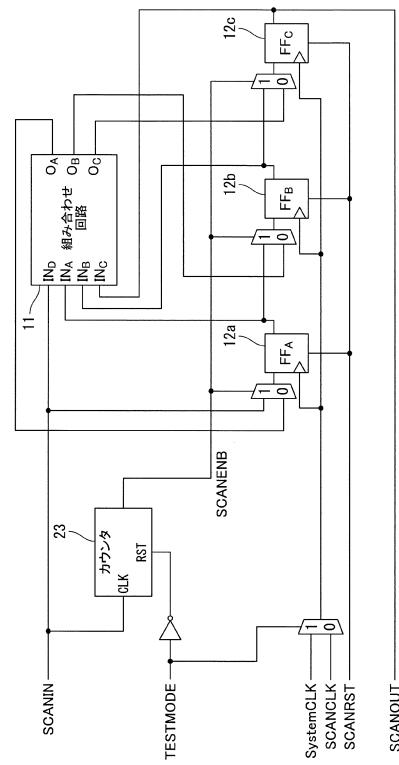

【図8】本発明に係る半導体テスト回路の実施例1を説明するための回路構成図である。

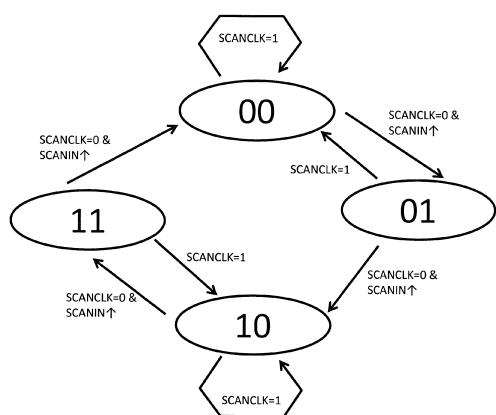

【図9】図8に示したカウンタの状態遷移図である。

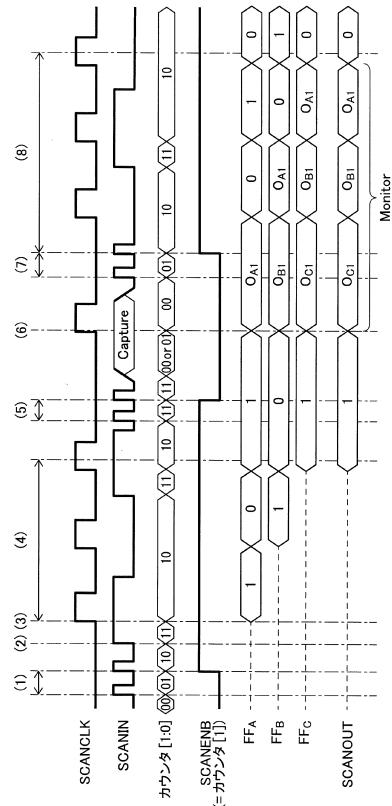

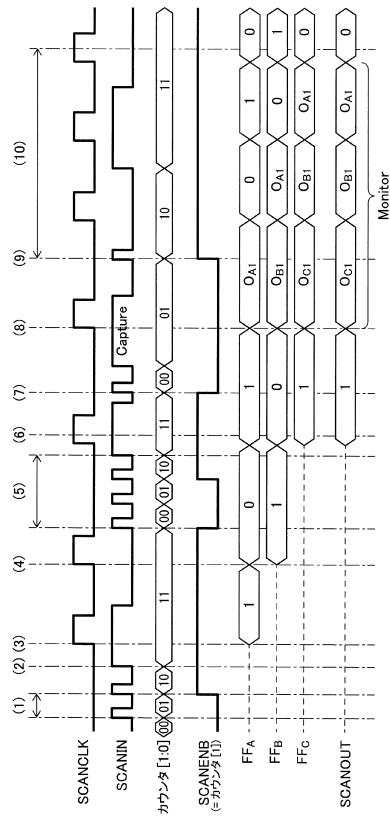

【図10】図8に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

【図11】本発明に係る半導体テスト回路の実施例2を説明するための回路構成図である。

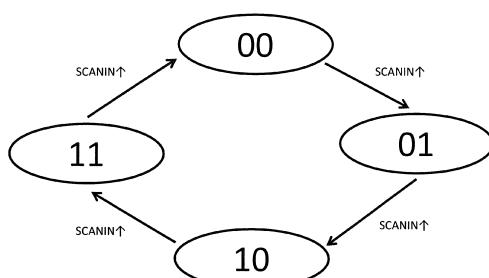

【図12】図11に示したカウンタの状態遷移図である。

【図13】図11に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

【図14】本発明に係る半導体テスト回路の実施例3を説明するための回路構成図である

10

【図15】図14に示したカウンタの状態遷移図である。

【図16】図14に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

【発明を実施するための形態】

【0023】

以下、図面を参照して本発明の実施の形態について説明する。

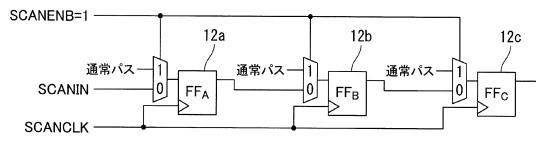

図6は、本発明に係るシフトレジスタ回路の回路構成図で、図7は、図6に示したシフトレジスタ回路の動作を説明するためのタイミングチャートを示す図である。図中符号12a, 12b, 12cは第1乃至第3のフリップフロップ(FF<sub>A</sub>, FF<sub>B</sub>, FF<sub>C</sub>)を示している。

20

本実施形態の半導体テスト回路は、SCANINをCLKとするカウンタを用いて、そのカウンタ値をSCANE NBとすることにより、SCANINとSCANE NBを同一ピンで制御できるため、ピン数の削減ができる特徴とする。また、カウンタを用いることで、設計の自由度が高く、また、テスト時間が短いテストが可能となる。

【0024】

【実施形態】

本実施形態は、SCANINとSCANE NBを共用するために、SCANE NBをSCAN CLKではなくSCANINをCLKとしたカウンタの値とすることを特徴とする。

30

以下に、基本原理について説明する。

SCAN動作は、SCAN CLKのEdgeでSCANINを取り込みシフトレジスタ動作する。図6及び図7に示すように、SCAN CLKのEdge以外では、SCANINは、どのように変化してもFFに取り込む値は変わらない。よって、SCAN CLKのEdgeの前にSCANINにパルスを発生させ、そのSCANINをCLKとするカウンタを用意し、そのカウンタ値をもってSCANE NBを生成する。

【実施例1】

【0025】

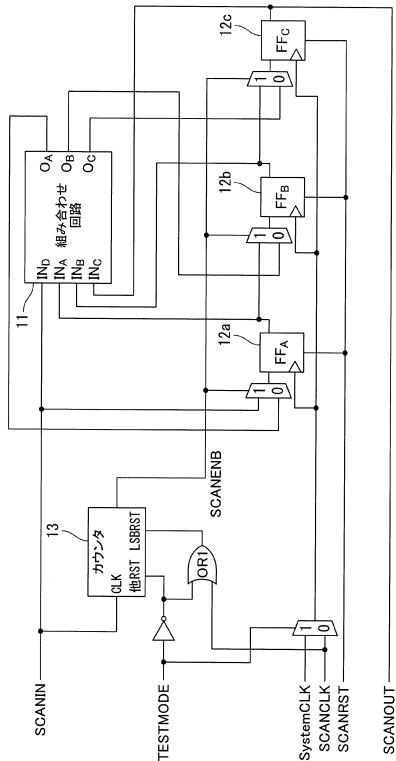

図8は、本発明に係る半導体テスト回路の実施例1を説明するための回路構成図で、SCANINとSCANE NBとを共通化したSCANテストを可能にした回路構成図である。図中符号11は組み合わせ回路、13はカウンタを示している。なお、図6と同じ機能を有する構成要素には同一に符号を付してある。

40

本発明の半導体テスト回路は、デジタル回路の故障検知を行うテストモードを有する半導体テスト回路である。

複数のフリップフロップ12a～12cは、スキャンイネーブル信号に基づいて、通常動作とスキャンデータ信号が入力されるシフトレジスタを構成するスキャン動作とを選択する選択回路を有する。

【0026】

組み合わせ回路11は、スキャンデータ信号が入力されて複数のフリップフロップへ出力する。カウンタ13は、スキャンデータ信号が入力されてスキャンイネーブル信号を出

50

力する。

また、スキャンデータ信号は、複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、カウンタにおいて、カウンタ制御信号により、スキャンイネーブル信号が制御される。

#### 【0027】

また、スキャンデータ信号は、複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるカウンタ制御信号と、を有し、カウンタにおいて、カウンタ制御信号により、スキャンイネーブル信号が立ち上がる又は立ち下がる。

10

また、カウンタ13は、スキャンデータ信号とスキャンロック信号が入力され、状態遷移するカウンタである。

また、カウンタ13は、少なくとも4つの状態を遷移し、データ信号とスキャンクロック信号により、第1の状態と第2の状態の遷移を繰り返し、また、第3の状態と第4の状態の遷移を繰り返し、カウンタ制御信号により、第1の状態又は第2の状態から、第3の状態又は第4の状態への遷移、または、第3の状態又は第4の状態から、第1の状態又は第2の状態への遷移を行い、第1の状態又は第2の状態に対応するカウント値が通常動作に対応するイネーブル信号であり、第3の状態又は第4の状態に対応するカウント値がスキャン動作に対応するイネーブル信号である。

#### 【0028】

20

また、カウンタ13は、スキャンロック信号により、第1の状態又は第2の状態から第1の状態へリセットする遷移を行い、及び、第3の状態又は第4の状態から第3の状態へリセットする遷移を行う。

また、カウンタ13は、2bitバイナリカウンタであり、スキャンイネーブル信号は、カウンタのカウント値のMSB(最上位ビット)である。なお、LSB(最下位ビット)をスキャンイネーブル信号とする構成であってもよい。

SCAN回路が、SCANCLKの立ち上がりEdgeで動作するときの新回路の例を図8に示している。SCANENBを、SCANINをCLKとしたカウンタの出力とするように構成する。

#### 【0029】

30

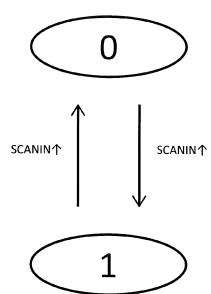

図9は、図8に示したカウンタの状態遷移図である。SCANCLKが0のとき、SCANINの立ち上がりEdgeで2進数表記で00 01 10 11 00 ...と動作する2bitバイナリカウンタであり、そのMSBをSCANENBとして構成する。つまり、カウンタが2進数表記で00, 01の時は、SCANENBが0に、カウンタが2進数表記で10, 11のときは、SCANENBが1となる。また、SCANCLKが1のときは、カウンタのLSBが0になるようにリセットさせる。

図10は、図8に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

#### 【0030】

(1) ; SCANCLKが0のときにSCANINから2発パルスを入れることでカウンタを2進数表記で00 01 10とし、SCANENBを1にして全FFをSCAN動作可能にする。

40

(2) ; SCANCLKが0のときにSCANINを所望の0または1にする(図9では1にセットしている。この際カウンタは2進数表記で11となる)。

(3) ; SCANCLKを入れてFF<sub>A</sub>に所望の値を取り込む(図9では1をとりこむ。このときカウンタはSCANCLKが1のためLSBがリセットされ必ず2進数表記で10になる)。

#### 【0031】

(4) ; (2), (3)を繰り返し全FFに所望の値をセットする(図9ではFF<sub>A</sub>, FF<sub>B</sub>, FF<sub>B</sub>にそれぞれ1, 0, 1をセットしている)。

50

(5) ; SCANCLKが0のときにSCANINから2発パルスを入れることでカウンタを2進数表記で10 11 00とし、SCANE NBを0(=通常バス)にする。

(6) ; SCANCLKからCLK入力し、通常バスの出力(=組み合わせ回路の出力)を各FFに取り込む(図10ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ組み合わせ回路出力のQ<sub>A1</sub>、Q<sub>B1</sub>、Q<sub>C1</sub>が取り込まれる。このときカウンタはSCANCLKが1のためLSBがリセットされ必ず2進数表記で00になる)。

#### 【0032】

(7) ; SCANCLKが0のときにSCANINから2発パルスを入れることでカウンタを2進数表記で00 01 10とし、SCANE NBを1にして全FFをSCAN動作可能にする。

10

(8) ; SCANCLKを入力して全FFの値(Q<sub>A1</sub>、Q<sub>B1</sub>、Q<sub>C1</sub>)をSCAN OUTから出力しモニタする(この際同時に全FFに次の所望の値をセットする。図10では0、1、0をそれぞれセットしている)。

(9) ; 上記(5)～(8)を繰り返す。

#### 【0033】

本実施例1におけるカウンタは、2bitのバイナリカウンタとしたが、カウンタは、2bit以上であればbit数は問わない。また、本実施例1は、バイナリカウンタとしたがカウンタの種類は問わない。また、本実施例1は、カウンタの動作は、SCANINのEdgeは立ち上がりとしたがEdgeの向きは問わない。また、SCANE NBが0又は1となるカウンタ値もSCAN動作と通常バスが切り替えることができるよう自由に決めてよい。カウンタのリセット信号は、本実施例1では、SCANテストを行う際に1とするTEST MODE信号の反転信号をリセットとしたが、通常動作時にSCANE NBが1にならないようにすれば構成は問わない。

20

更に、本実施例1は、カウンタのLSBのリセット信号にSCANCLKの1を入力しているが、これはSCANCLKが1となるとカウンタが2進数表記で00又は10となり、カウンタの値を把握しやすくするためのものであり、取り除いても構わない。その場合の構成例を以下の実施例2に示す。

#### 【実施例2】

#### 【0034】

図11は、本発明に係る半導体テスト回路の実施例2を説明するための回路構成図で、SCANINとSCANE NBとを共通化したSCANテストを可能にした回路構成図である。なお、図8と同じ機能を有する構成要素には同一に符号を付してある。

30

SCAN回路がSCANCLKの立ち上がりEdgeで動作するときの新回路の例を図11に示してある。SCANE NBを、SCANINをCLKとしたカウンタ13の出力とするように構成する。カウンタ13は、SCANテストを行うTEST MODE = 1以外はリセットされる。

#### 【0035】

図12は、図11に示したカウンタの状態遷移図である。SCANCLKが0のとき、SCANINの立ち上がりEdgeで2進数表記で00 01 10 11 00 ...と動作する2bitバイナリカウンタであり、そのMSBをSCANE NBとして構成する。つまり、カウンタが2進数表記で00, 01の時は、SCANE NBが0に、カウンタが2進数表記で10, 11のときは、SCANE NBが1となる。

40

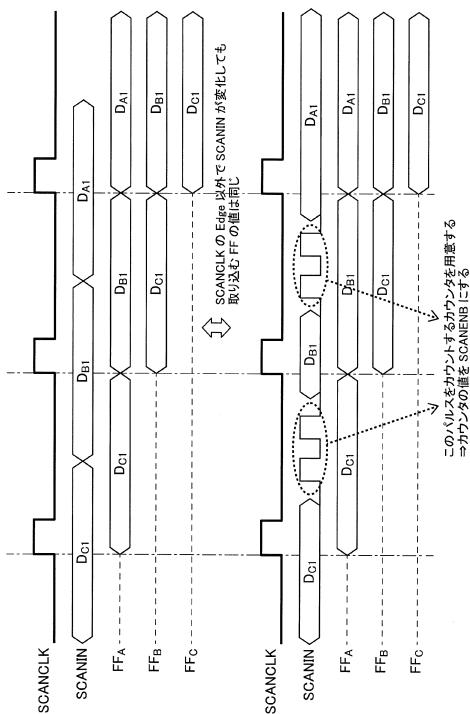

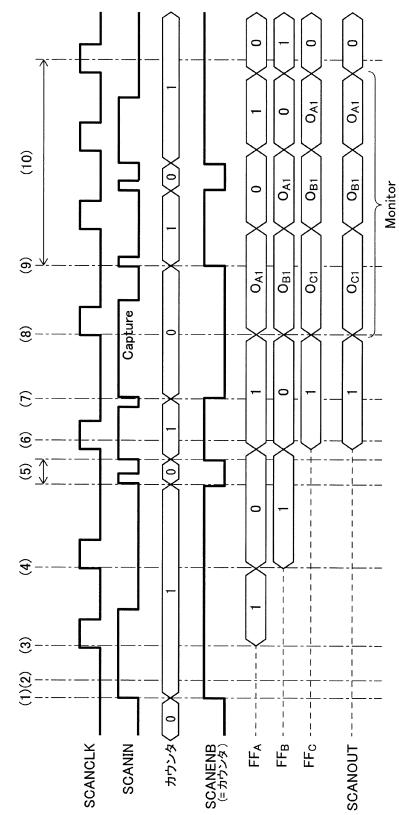

図13は、図11に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。

#### 【0036】

(1) ; SCANINからパルスを入れることでカウンタを2進数表記で10とし、SCANE NBを1にして全FFをSCAN動作可能にする(図13ではSCANINからパルス2発を入れることでカウンタを2進数表記で00 01 10とし、SCANE NBを1にして全FFをSCAN動作可能にしている)。

(2) ; SCANE NBが1かつSCANINを所望の0または1にする(図13では1

50

にセットしている。この際カウンタは2進数表記で10 11となる)。

(3) ; SCANE NBが1のままでSCAN CLKを入れてFF<sub>A</sub>に所望の値を取り込む(図13では1をとりこむ。このときカウンタは2進数表記で11のまま)。

#### 【0037】

(4) ; SCANE NBが1のままでSCAN CLKを入れてFF<sub>A</sub>、FF<sub>B</sub>、に所望の値を取り込む(図13ではFF<sub>A</sub>、FF<sub>B</sub>にそれぞれ0、1をセットしている。このときカウンタは2進数表記で11のまま)。

(5) ; SCANE NBが1かつSCAN INを所望の0または1にする。(図13では次にSCAN INを1にしてFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ1、0、1を取り込ませるが、その際カウンタが1周して00になりSCANE NBが0になってしまうため、その前にSCAN INにパルスを3発いれ、カウンタを2進数表記で11 00 01 10とし、SCANE NBを1にして全FFをSCAN動作可能にしている。その後SCAN INを1にしている。この際カウンタは2進数表記で10 11となる)。

(6) ; SCANE NBが1のままでSCAN CLKを入れて全FFに所望の値をセットする(図13ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ1、0、1をセットしている。この際カウンタは2進数表記で11のまま)。

#### 【0038】

(7) ; SCAN INからパルスを入れることでカウンタを2進数表記で00とし、SCAN ENBを0(=通常バス)にする(図13ではSCAN INから1発パルスを入れることでカウンタを2進数表記で11 00とし、SCANE NBを0(=通常バス)にする)。

(8) ; SCANE NBが0のままでSCAN CLKから1 CLK入力し、通常バスの出力(=組み合わせ回路の出力)を各FFに取り込む(図13ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ組み合わせ回路出力のQ<sub>A 1</sub>、Q<sub>B 1</sub>、Q<sub>C 1</sub>が取り込まれる。このときカウンタはSCAN INを1にしたため2進数表記で01になっている)。

#### 【0039】

(9) ; SCAN INからパルスを入れることでカウンタを2進数表記で10とし、SCAN ENBを1にして全FFをSCAN動作可能にする(図13ではSCAN INからパルス1発を入れることでカウンタを2進数表記で01 10とし、SCANE NBを1にして全FFをSCAN動作可能にしている)。

(10) ; SCANE NBが1でSCAN CLKを入力して全FFの値(Q<sub>A 1</sub>、Q<sub>B 1</sub>、Q<sub>C 1</sub>)をSCAN OUTから出力しモニタする(この際同時に全FFに次の所望の値をセットする。図13では0、1、0をそれぞれセットしている)。

(11) ; 上記(8)～(10)を繰り返す。

#### 【0040】

本実施例2におけるカウンタは、2bitのカウンタとしたが、カウンタは、1bit以上であればbit数は問わない。また、カウンタの種類は問わない。また、本実施例2は、カウンタの動作は、SCAN INのEdgeは立ち上がりとしたがEdgeの向きは問わない。また、SCANE NBが0又は1となるカウンタ値もSCAN動作と通常バスが切り替えることができるよう自由に決めてよい。カウンタのリセット信号は、本実施例2では、SCANテストを行う際に1とするTEST MODE信号の反転信号をリセットとしたが、通常動作時にSCANE NBが1にならないようにすれば構成は問わない。

#### 【実施例3】

#### 【0041】

実施例3は、上述した実施例2において1bitカウンタでカウンタを構成した例を示す。

図14は、本発明に係る半導体テスト回路の実施例3を説明するための回路構成図で、SCAN INとSCANE NBとを共通化したSCANテストを可能にした回路構成図である。なお、図11と同じ機能を有する構成要素には同一に符号を付してある。

SCAN回路がSCAN CLKの立ち上がりEdgeで動作するときの新回路の例を図

10

20

30

40

50

14に示してある。SCANENBを、SCANINをCLKとしたカウンタ23の出力とするように構成する。カウンタ23は、SCANテストを行うTESTMODE=1以外はリセットされる。

#### 【0042】

図15は、図14に示したカウンタの状態遷移図である。SCANCLKが0のとき、SCANINの立ち上がりEdgeで2進数表記で0 1 ...と動作する1bitカウンタであり、その値をSCANENBとして構成する。つまり、カウンタが2進数表記で0の時は、SCANENBが0に、カウンタが2進数表記で1のときは、SCANENBが1となる。

図16は、図14に示したSCANテスト動作を説明するためのタイミングチャートを示す図である。 10

#### 【0043】

(1) ; SCANINから立ち上がりEdgeを1回いれることでカウンタを2進数表記で1とし、SCANENBを1にして全FFをSCAN動作可能にする(図16ではSCANINから立ち上がりEdgeを1回いれることでカウンタを2進数表記で0 1とし、SCANENBを1にして全FFをSCAN動作可能にしている)。

(2) ; SCANENBが1かつSCANINを所望の0または1にする(図16では1にセットしている。この際カウンタは2進数表記で1のまま)。

(3) ; SCANENBが1のままでSCANCLKを入れてFF<sub>A</sub>に所望の値を取り込む(図16では1をとりこむ。このときカウンタは2進数表記で1のまま)。 20

#### 【0044】

(4) ; SCANENBが1のままでSCANCLKを入れてFF<sub>A</sub>、FF<sub>B</sub>、に所望の値を取り込む(図13ではFF<sub>A</sub>、FF<sub>B</sub>にそれぞれ0、1をセットしている。このときカウンタは2進数表記で1のまま)。

(5) ; SCANENBが1かつSCANINを所望の0または1にする。(図16では次にSCANINを1にしてFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ1、0、1を取り込ませるが、その際カウンタが1周して0になりSCANENBが0になってしまふため、その前にSCANINにパルスを1発いれ、カウンタを2進数表記で1 0とする。その後SCANINを1にしている。この際カウンタは2進数表記で0 1となり、SCANENBを1にして全FFをSCAN動作可能にする)。 30

(6) ; SCANENBが1のままでSCANCLKを入れて全FFに所望の値をセットする(図13ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ1、0、1をセットしている。この際カウンタは2進数表記で1のまま)。

#### 【0045】

(7) ; SCANINから立ち上がりEdgeを1回いれることでカウンタを2進数表記で0とし、SCANENBを0(=通常バス)にする(図16ではSCANINから立ち上がりEdgeを1回いれることでカウンタを2進数表記で1 0とし、SCANENBを0(=通常バス)にする)。

(8) ; SCANENBが0のままでSCANCLKから1CLK入力し、通常バスの出力(=組み合わせ回路の出力)を各FFに取り込む(図16ではFF<sub>A</sub>、FF<sub>B</sub>、FF<sub>B</sub>にそれぞれ組み合わせ回路出力のQ<sub>A1</sub>、Q<sub>B1</sub>、Q<sub>C1</sub>が取り込まれる。このときカウンタはSCANINを1にしたため2進数表記で0のまま)。 40

#### 【0046】

(9) ; SCANINから立ち上がりEdgeを1回いれることでカウンタを2進数表記で1とし、SCANENBを1にして全FFをSCAN動作可能にする(図16ではSCANINから立ち上がりEdgeを1回いれることでカウンタを2進数表記で0 1とし、SCANENBを1にして全FFをSCAN動作可能にしている)。

(10) ; SCANENBが1でSCANCLKを入力して全FFの値(Q<sub>A1</sub>、Q<sub>B1</sub>、Q<sub>C1</sub>)をSCANOUTから出力しモニタする(この際同時に全FFに次の所望の値をセットする。図16では0、1、0をそれぞれセットしている)。 50

( 11 ) ; 上記 ( 8 ) ~ ( 10 ) を繰り返す。

#### 【 0 0 4 7 】

このような上記構成例 1 ~ 3 により、SCANINとSCANENBを共通化することでピン数の削減ができる。また、従来技術とは異なり、SCANENB用FFは、SCANCLKで動作しないため、SCAN回路は、一般的SCAN回路と同様にSCANCLKの立ち上がりと立下りEdgeで動作するFFが混在してもよく、設計に自由度が増す。例えば、SCAN回路を全てSCANCLKの立ち上がりEdgeのみで動作させる場合、従来技術とは異なり、SCANCLKの立下りEdgeをSCANENB用のFFに使用しないため、このFF用のセットアップタイムが不要となり、SCANCLKのHiの幅を短くできるため、テスト時間の削減ができる。

同様に、SCAN回路を全てSCANCLKの立ち下がりEdgeのみで動作させる場合、従来技術とは異なり、SCANCLKの立ち上がりEdgeをSCANENB用に使用しないため、FFのセットアップタイムが不要となり、SCANCLKのLowの幅を短くできるため、テスト時間の削減ができる。

#### 【 0 0 4 8 】

次に、本発明の半導体テスト回路を組み入れたICチップについて説明する。

本発明のICチップは、複数のフリップフロップと組み合わせ回路とを有するデジタルブロックを、スキャンクロックと、スキャンデータ信号と、スキャンイネーブル信号と、によりスキャンテストを行うICチップである。

スキャンクロックが入力される第1のPAD(SCANCLK)と、スキャンデータ信号が入力される第2のPAD(SCANIN)と、第2のPADに接続され、スキャンデータ信号からスキャンイネーブル信号を出力するカウンタと、を備えている。

また、カウンタのクロックラインに、第2のPADが接続され、カウンタの第1のリセットラインに、第1のPADが論理素子を介して接続されている。

また、スキャンデータ信号は、複数のフリップフロップがスキャンクロックに同期して取り込むデータ信号と、複数のフリップフロップに入力されるスキャンクロックが配されない区間に配されるパルス信号と、を有している。

#### 【 0 0 4 9 】

また、データ信号を複数のフリップフロップに、スキャンクロックに同期して設定するために順次データが入力された後、次にスキャンクロックが配されるまでの間に、パルス信号が配される。

また、次のスキャンクロックが配された後、別のデータ信号を複数のフリップフロップに、スキャンクロックに同期して設定するために順次データが入力されるまでの間に、パルス信号が配される。

このような構成により、設計の自由度が高く、また、テスト時間が短い半導体テスト回路を組み入れたICチップを実現することができる。

#### 【 符号の説明 】

#### 【 0 0 5 0 】

1 組み合わせ回路

2 a , 2 b , 2 c , 1 2 a , 1 2 b , 1 2 c 第1乃至第3のフリップフロップ(FF<sub>A</sub>、FF<sub>B</sub>、FF<sub>C</sub>)

3 フリップフロップ(FF<sub>ENB</sub>)

1 1 組み合わせ回路

1 3 , 2 3 カウンタ

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2013-036960(JP,A)

特開2008-021359(JP,A)

特開2004-347537(JP,A)

特開2003-121499(JP,A)

米国特許出願公開第2013/0305106(US,A1)

特開平09-089993(JP,A)

特開平07-287052(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 01 R      31 / 28

H 01 L      21 / 822

H 01 L      27 / 04