(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 28 588 T2 2006.02.09

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 966 763 B1

(21) Deutsches Aktenzeichen: 698 28 588.3

(86) PCT-Aktenzeichen: PCT/US98/02384

(96) Europäisches Aktenzeichen: 98 904 992.9

(87) PCT-Veröffentlichungs-Nr.: WO 98/035390

(86) PCT-Anmeldetag: 06.02.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 13.08.1998

(97) Erstveröffentlichung durch das EPA: 29.12.1999

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 12.01.2005

(47) Veröffentlichungstag im Patentblatt: 09.02.2006

(51) Int Cl.<sup>8</sup>: H01L 29/78 (2006.01)

H01L 29/739 (2006.01)

H01L 29/24 (2006.01)

(30) Unionspriorität:

797535 07.02.1997 US

795135 07.02.1997 US

(74) Vertreter:

Witte, Weller, Gahlert, Otten & Steil, 70178

Stuttgart

(73) Patentinhaber:

Cooper jun., James Albert, West Lafayette, Ind.,

US; Tan, Jian, West Lafayette, Ind., US

(84) Benannte Vertragsstaaten:

AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LI,

LU, MC, NL, PT, SE

(72) Erfinder:

gleich Anmelder

(54) Bezeichnung: STRUKTUR ZUR ERHÖHUNG DER MAXIMALEN SPANNUNG VON SILIZIUMKARBID-LEISTUNGSTRANSISTOREN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingereicht, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung betrifft Halbleiter-Leistungsvorrichtungen mit isoliertem Gate und insbesondere UMOS- und IGBT-Feldeffektransistoren, die aus Siliziumkarbid gebildet sind.

**Hintergrund der Erfindung**

**[0002]** Die vorliegende Erfindung betrifft Halbleiter-Leistungsvorrichtungen und insbesondere Leistungs-MOSFETs (Halbleiter-Feldeffektransistoren aus Metalloxid), die aus Siliziumkarbid gebildet sind. Ein Leistungs-MOSFET ist eine kleine, zuverlässige, elektronisch steuerbare Schaltvorrichtung, die zunehmend Anwendung bei Hochspannungs-/Hochleistungsvorrichtungen und integrierten Schaltungen findet. Leistungs-MOSFETs haben eine Vielzahl von Anwendungen in zahlreichen Gebieten einschließlich Kommunikation, Kundenanwendungen, Datenverarbeitung, Militär-, Industrie-, Automobil- und verwandten Märkten. Insbesondere weisen Leistungs-MOSFETs von Natur aus höhere Schaltgeschwindigkeiten als bipolare Transistoren auf und sind dementsprechend besonders bei Hochfrequenzanwendungen nützlich. Obwohl Silizium für viele Halbleiteranwendungen das Material der Wahl war, verhindern seine fundamentale elektronische Struktur und seine Eigenschaften seine Verwendung über gewisse Parameter hinaus. Somit hat sich das Interesse an Leistungs-MOSFET-Vorrichtungen von Silizium zu anderen Materialien gedreht, einschließlich Siliziumkarbid. Siliziumkarbid weist eine Anzahl intrinsischer Vorteile für Leistungs-MOSFET-Anwendungen auf. Siliziumkarbid weist eine hohe Feldsättigungsgeschwindigkeit auf, die dreimal so groß ist wie die von Galliumarsenid (GaAs). Siliziumkarbid weist ein hohes inneres Durchschlag- bzw. Zusammenbruchfeld, welches zehnmal größer als das von Galliumarsenid ist, und eine Wärmeleitfähigkeit auf, die zehnmal größer als die von Galliumarsenid ist.

**[0003]** SiC ist unter Verbindungshalbleitern einzigartig, weil sein natürliches Oxid  $\text{SiO}$  ist, welches das gleiche Oxid wie von Silizium ist. Dies bedeutet, dass die verwendeten Arbeitspferd-Leistungsvorrichtungen aus Silizium, d.h. die Leistungs-MOSFET, die, bipolare Transistoren mit isoliertem Gate („insulated gate bipolar transistor“, IGBT) und MOS-gesteuerten Thyristoren (MCT) alle aus SiC hergestellt werden können.

**[0004]** Aufgrund technologischer Unterschiede können Leistungsvorrichtungen aus SiC jedoch sehr verschieden zu Siliziumvorrichtungen sein, und eine direkte Übersetzung von Siliziumkonzepten zu SiC hin ist nicht immer möglich. SiC weist ein Durchschlagfeld auf, welches achtmal so groß wie das von Silizi-

um ist, und SiC-Leistungsvorrichtungen können spezifische Ein-Widerstände aufweisen, die 100- bis 200-mal geringer als von ähnlichen Vorrichtungen aus Silizium sind. Nichtsdestotrotz muss man sich um mehrere praktische Probleme kümmern, bevor solche Vorrichtungen realisiert werden können. Bipolare Vorrichtungen aus SiC (z.B. der IGBT und der MCT) leiden unter kurzen Minoritätsträger-Lebensdauern, die üblicherweise im Bereich von 40 bis 400 Nanosekunden (ns) liegen. Im Ergebnis liegen die schon berichteten höchsten Stromverstärkungen bei bipolaren SiC-Transistoren im Bereich von 10 bis 12. Da das elektrische Spitzenzfeld achtmal (8X) größer als bei Silizium sein kann, können SiC-Schaltvorrichtungen mit einem Driftbereich hergestellt werden, der 8X mal dünner als bei vergleichbaren Siliziumvorrichtungen ist. Falls der Driftbereich 8X mal dünner ist, kann die Dotierung des Driftbereichs ungefähr zwölfmal (12X) höher sein. Der Widerstand des Driftbereichs ist proportional zu der Dicke und umgekehrt proportional zu der Dotierung, so dass der spezifische Ein-Widerstand einer SiC-Vorrichtung 100-200 mal kleiner sein kann als bei einer vergleichbaren Siliziumvorrichtung mit gleichen Nennspannung. Dies bedeutet, dass die SiC-Vorrichtung 100-200 mal kleiner als die vergleichbare Siliziumvorrichtung sein kann. Falls die SiC-Vorrichtung die gleiche Fläche wie die vergleichbare Siliziumvorrichtung aufweist, wird alternativ ihr spezifischer Ein-Widerstand 100-200 mal kleiner sein.

**[0005]** Obwohl es wesentliche Vorteile gegenüber Silizium bietet, ist SiC als Halbleitermaterial noch relativ unentwickelt. Einzelne Kristallwafer aus SiC waren lediglich seit 1991 käuflich erhältlich, und man muss sich um eine Anzahl technischer Probleme kümmern, bevor SiC Silizium bei Leistungsvorrichtungsanwendungen verdrängen kann. Die Hauptprobleme bei SiC-Materialien stehen im Zusammenhang mit dem Kristallwachstum. Aufgrund des sehr hohen Schmelzpunkts, können Einkristallkörper nicht aus einer Schmelze wie bei dem Czochralski-Verfahren gezogen werden, welches für Silizium verwendet wird. Anstatt dessen wächst der Einkristallkörper durch einen Hochtemperatur-Sublimationsprozess an einem Kristallkeim. Gegenwärtig sind die durch den Sublimationsprozess gewachsenen Einkristalle ungefähr 2 Inch im Durchmesser, was viel kleiner als die in der Siliziumindustrie üblichen 6 bis 8 Inch ist. Zusätzlich weist das Material eine relativ große Anzahl von Defekten auf. Diese Defekte schließen Mikroleitungen („micropipes“) mit ein; d.h. Mikron-große Löcher, die vollständig durch den Wafer laufen. Glücklicherweise scheint das Micropipe-Problem bei den jüngsten Wafern mit Micropipe-Dichten, die so klein wie  $27 \text{ cm}^{-2}$  sind, unter Kontrolle zu sein und sollte bei der aktuellen Verbesserungsrate von Micropipes eventuell vollständig eliminiert sein.

**[0006]** SiC kristallisiert im hexagonalen Gitter mit

abwechselnden Ebenen aus Silizium- und Kohlenstoffatomen. Die Si-C-Ebenenpaare können in drei Orientierungen auftreten, welche mit A, B und C bezeichnet werden. Die besondere Stapelsequenz von SiC-Ebenenpaaren identifiziert den Polytyp des Kristalls. SiC tritt in einer Vielzahl von Polytypen auf, die üblichsten sind jedoch 3C, 4H und 6H. Gegenwärtig ist der 6H-Polytyp der am gründlichsten charakterisierte, jedoch ist der 4H-Polytyp für Leistungsvorrichtungen aufgrund seiner hohen Elektronenmobilität attraktiver.

**[0007]** Obwohl es ein viel höheres Durchschlagfeld als Silizium aufweist, hat SiC eine niedrigere Loch- und Elektronenmobilität und kürzere Minoritätsträger-Lebensdauern. Die kürzeren Lebensdauern ermöglichen es bipolaren Vorrichtungen aus SiC, viel schneller als vergleichbare Siliziumvorrichtungen zu schalten, jedoch begrenzen sie die Stromverstärkung von bipolaren SiC-Transistoren auf sehr geringe Werte, die üblicherweise kleiner als 20 sind. Zum Hochgeschwindigkeitsschalten mit einem geringen Durchlassspannungsabfall wird die beste SiC-Vorrichtung ein Leistungs-MOSFET sein. Der typische Power-MOSFET aus Silizium ist eine DMOS- (oder doppelt diffundierte MOS)-Struktur. Die kurze Kanallänge wird durch Diffundieren der p-leitenden Basis schicht und der n<sup>+</sup>-Quelle durch das gleiche Oxidfenster erreicht, wodurch jegliche Abhängigkeit von einer Photomaskenausrichtung beseitigt wird. Die p-leitende Basis muss eine ausreichende Anzahl von Dotierungsatomen pro Einheitsfläche (Dicke mal Konzentration) aufweisen, um Durchgriffe durch das elektrische Drain-Feld im sperrenden Zustand zu verhindern. Unglücklicherweise ist das DMOS-Konzept schwer auf SiC zu übertragen, da es nicht für thermisch diffuse Dotierungsatome aus SiC durchführbar ist. Man könnte künstlich eine ähnliche Struktur unter Verwendung einer Ionenimplantation konstruieren, jedoch wäre die Kanallänge dann durch eine Maskenausrichtung definiert und es wäre schwierig, die p-leitende Unreinheit in ausreichender Tiefe zu implantieren, um einen Durchgriff zu verhindern. Aus diesen Gründen ist eine vertikale UMOSFET-Struktur – d.h. eine Kombination von epitaxialen SiC-Schichten und einem Graben – bei SiC die praktischste.

**[0008]** Das theoretische Potential von SiC-MOSFETs wurde jedoch nicht erreicht, da die Maximalspannung bei MOSFETs aus Siliziumkarbid anstatt dessen durch das Durchschlagfeld des Siliziumdioxid(SiO<sub>2</sub>)-Isolators begrenzt ist. Obwohl dieses Oxid eigentlich nicht versagt, bis Felder von ungefähr 10<sup>7</sup> Volt pro Zentimeter (V/cm) erreicht sind, verschlechtert sich die kurzzeitige Zuverlässigkeit des Oxsids, von einem praktischen Standpunkt aus, ernstlich bei Feldern von ungefähr 2–3 × 10<sup>6</sup> V/cm. Eine solche Feldbegrenzung ist schon leicht geringer als das Durchschlagfeld von Siliziumkarbid. Problematischer ist es aufgrund des 2,5:1-Verhältnisses der elektrischen Feldstärke zu den Feldern im Isolator.

schen Konstanten von Siliziumdioxid und Siliziumkarbid jedoch, dass das Gaußsche Gesetz fordert, dass das Maximalfeld bei Siliziumkarbid-Leistungstransistoren praktisch auf eine Sperrspannung begrenzt ist, die viel geringer als die ist, zu der Siliziumkarbid theoretisch fähig ist.

**[0009]** Dementsprechend besteht ein Bedürfnis nach Leistungstransistoren, insbesondere Leistungs-MOSFETs, aus Siliziumkarbid, die fähig sind, größeren Nutzen aus den favorisierten intrinsischen Eigenschaften von Siliziumkarbid zu ziehen, und es ist eine Aufgabe der Erfindung solche Transistoren bereitzustellen.

**[0010]** US 5,488,236 A offenbart einen Gate-gesteuerten bipolaren Transistor einschließlich eines vergraben Kollektorbereichs.

#### Zusammenfassung der Erfindung

**[0011]** Dementsprechend besteht die vorliegende Erfindung aus einem UMOS-Leistungstransistor, wie in Anspruch 1 definiert.

**[0012]** Die Erfindung besteht auch aus einem bipolaren Leistungstransistor mit isoliertem Gate (IGBT), wie in Anspruch 10 definiert.

#### Kurze Beschreibung der Zeichnung

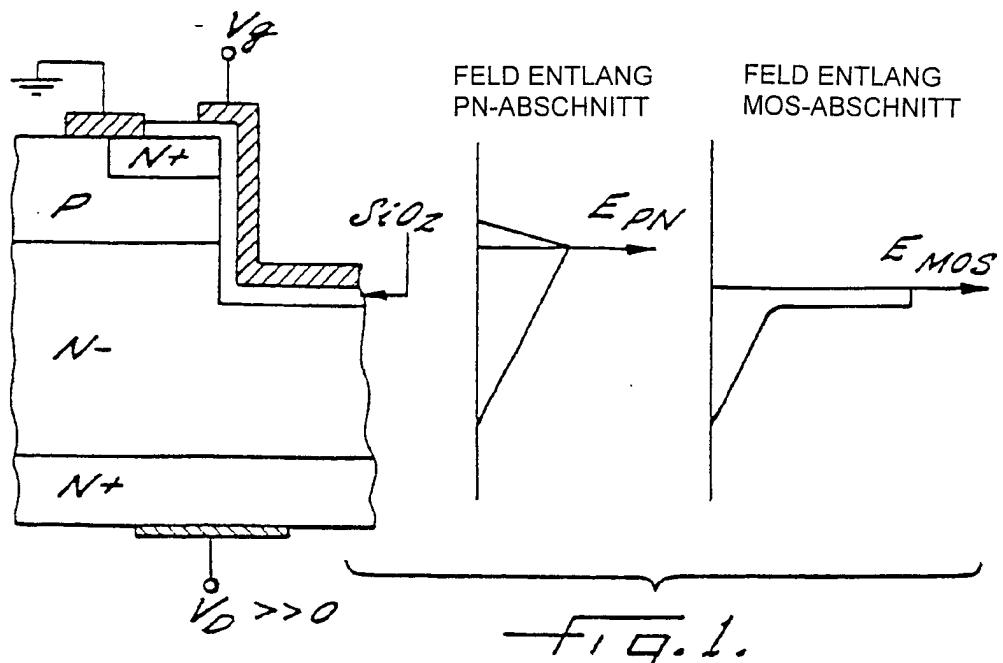

**[0013]** [Fig. 1](#) stellt ein schematisches Diagramm eines Querschnitts eines UMOS gemäß dem Stand der Technik dar, welchem formlose Diagramme des Felds entlang der p-n- und MOS-Abschnitte solcher Vorrichtungen gemäß dem Stand der Technik beige fügt sind.

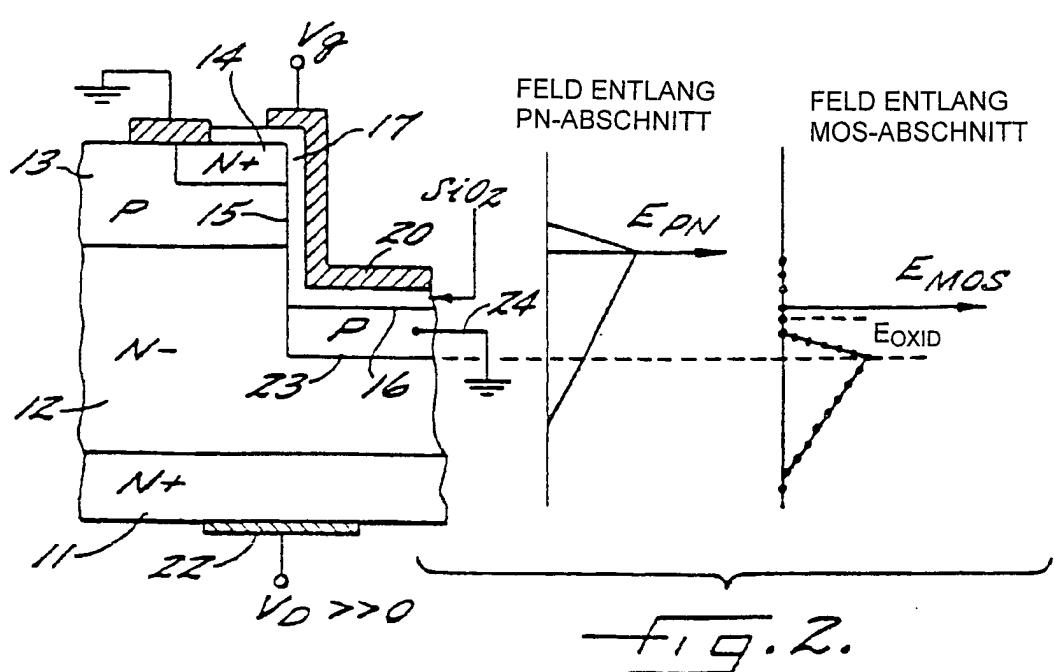

**[0014]** [Fig. 2](#) stellt eine ähnliche schematische Querschnittsansicht eines UMOS dar, die hilfreich zum Verstehen der vorliegenden Erfindung ist und der wiederum formlose Diagramme des resultierenden Felds entlang der p-n- und MOS-Abschnitte der Vorrichtung beige fügt sind.

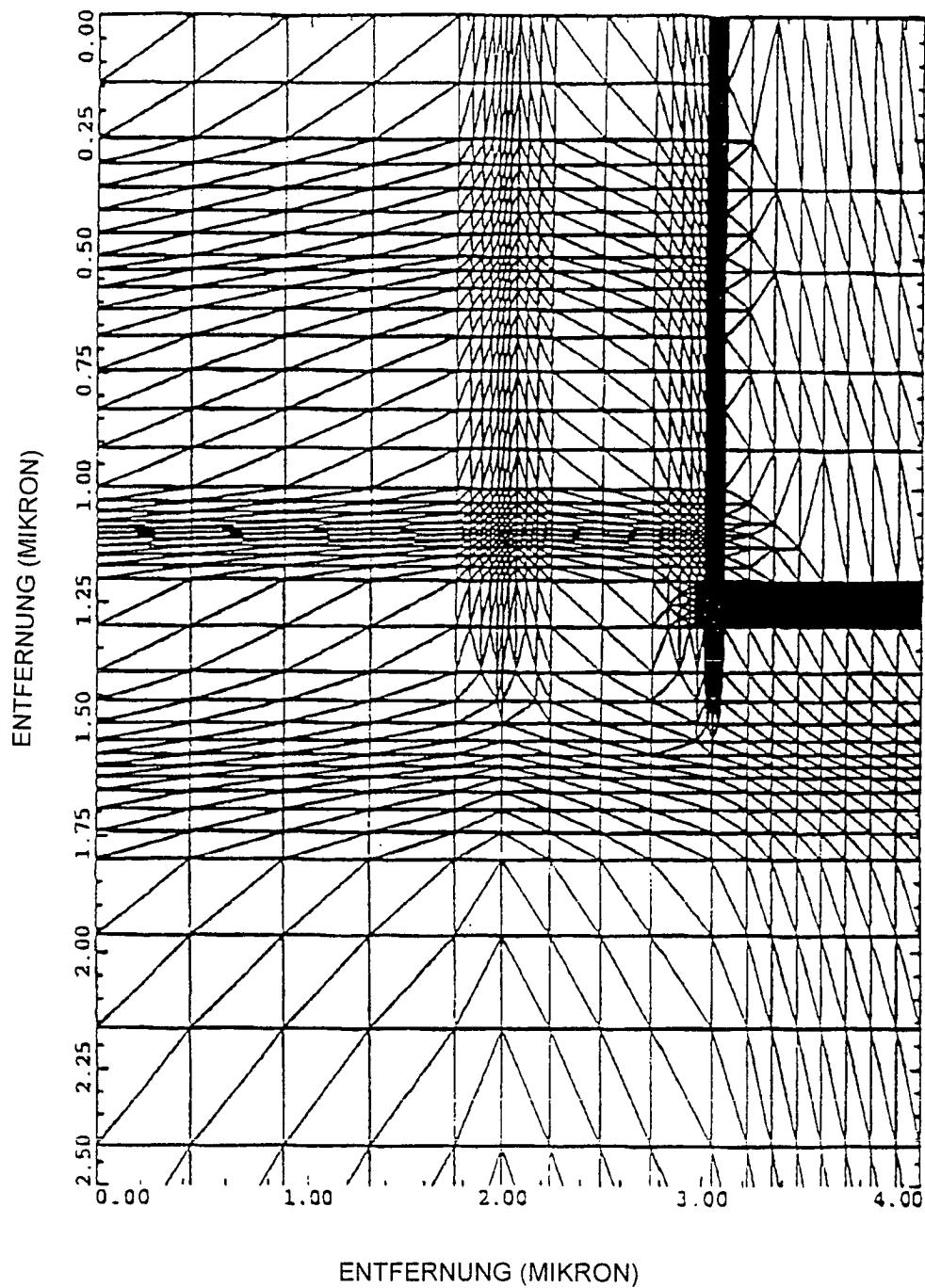

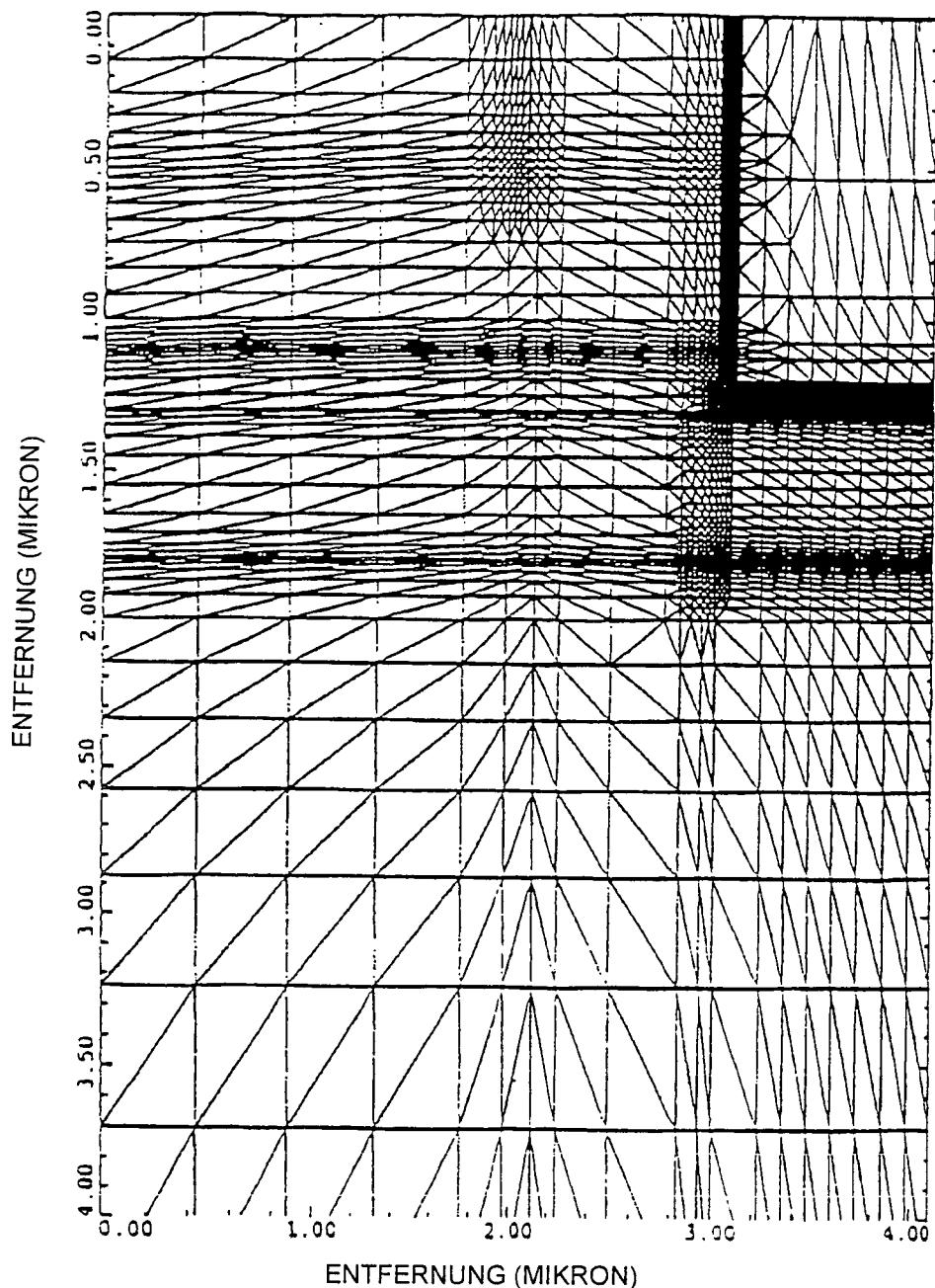

**[0015]** [Fig. 3](#) stellt ein Benutzer-definiertes Gitter eines herkömmlichen UMOS gemäß dem Stand der Technik unter Verwendung einer Simulationssoftware für Vorrichtungen dar.

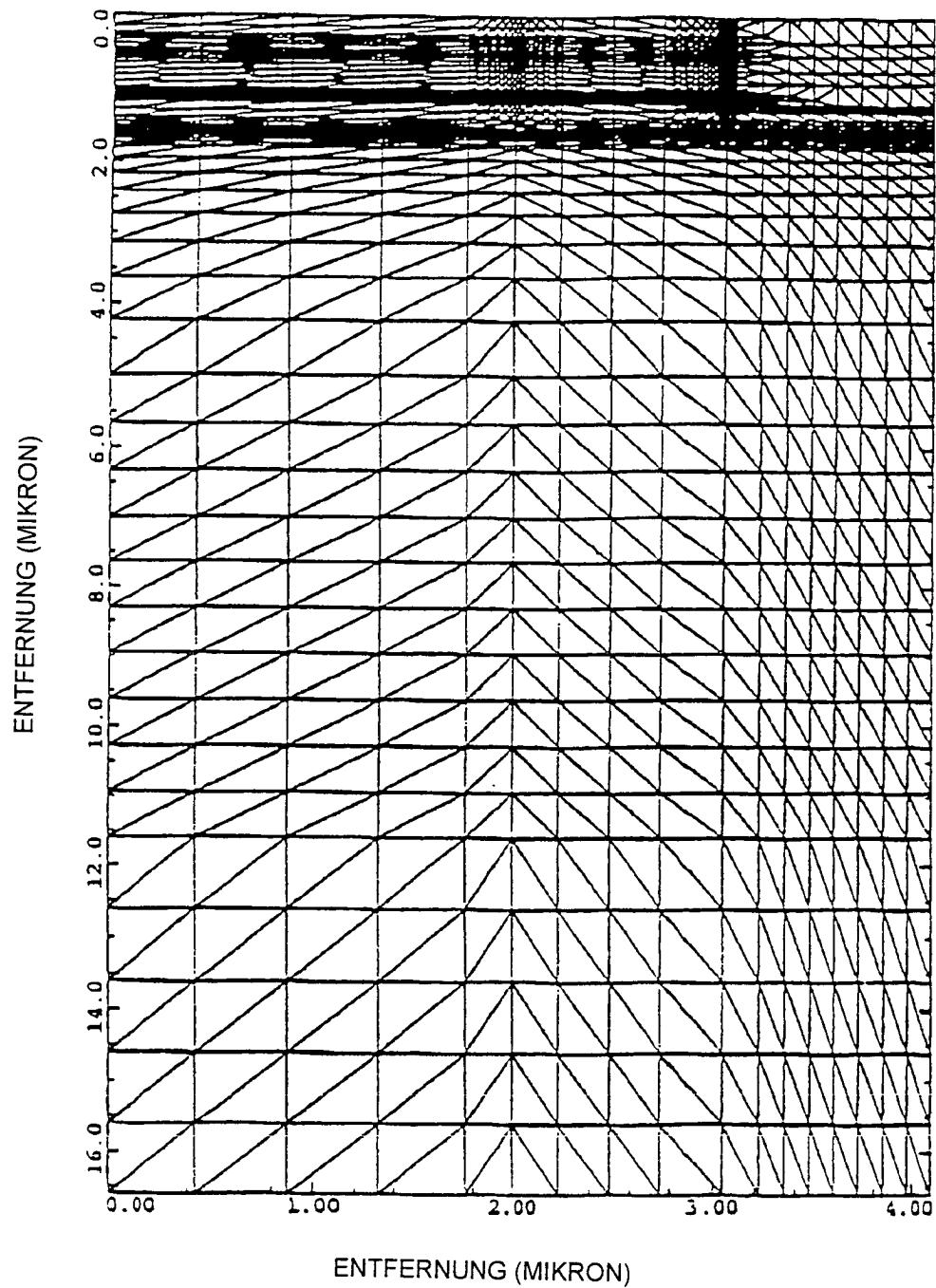

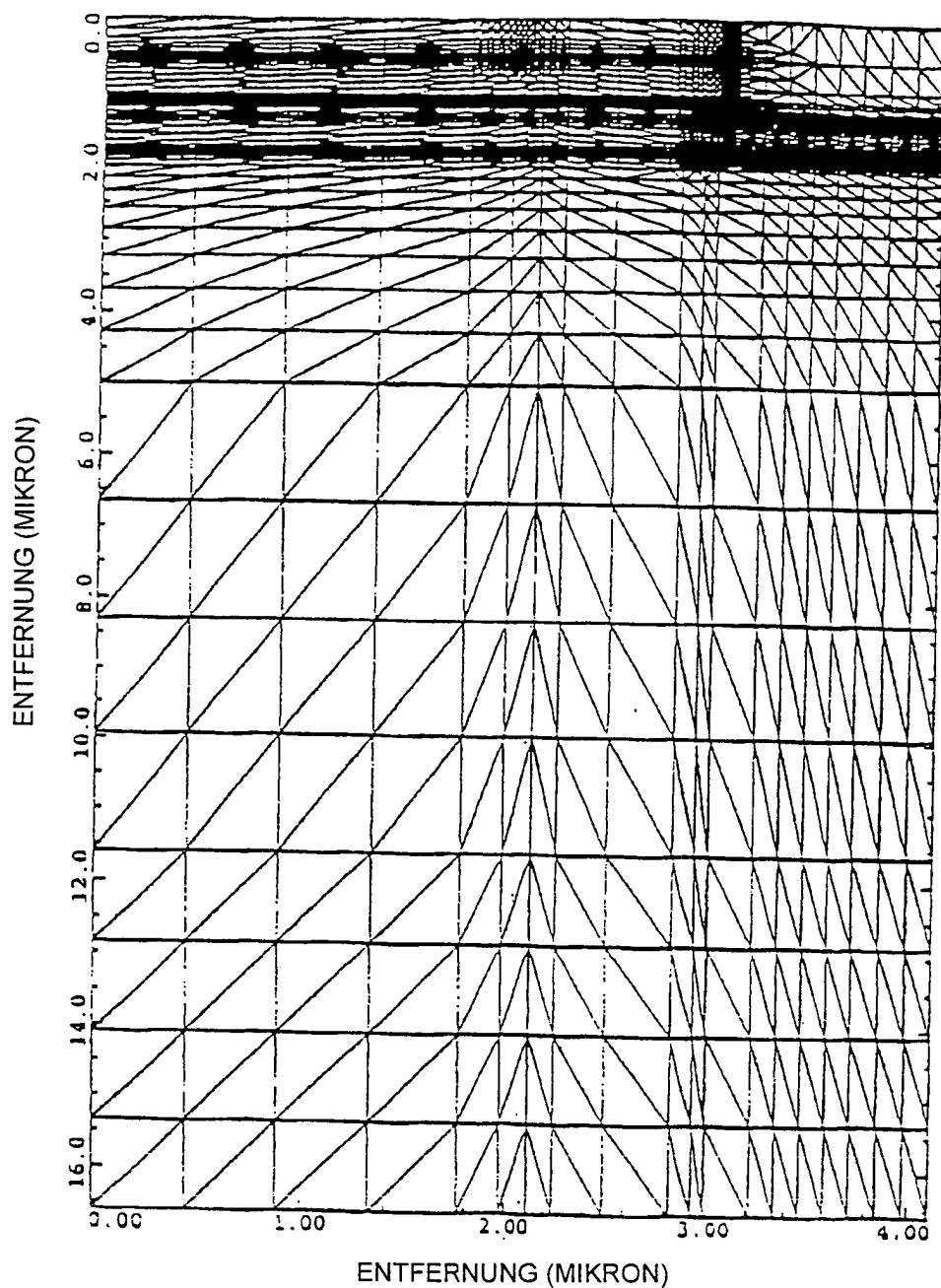

**[0016]** [Fig. 4](#) stellt ein Gitter ähnlich zu [Fig. 3](#) dar, welches jedoch in die vertikale Richtung erweitert ist.

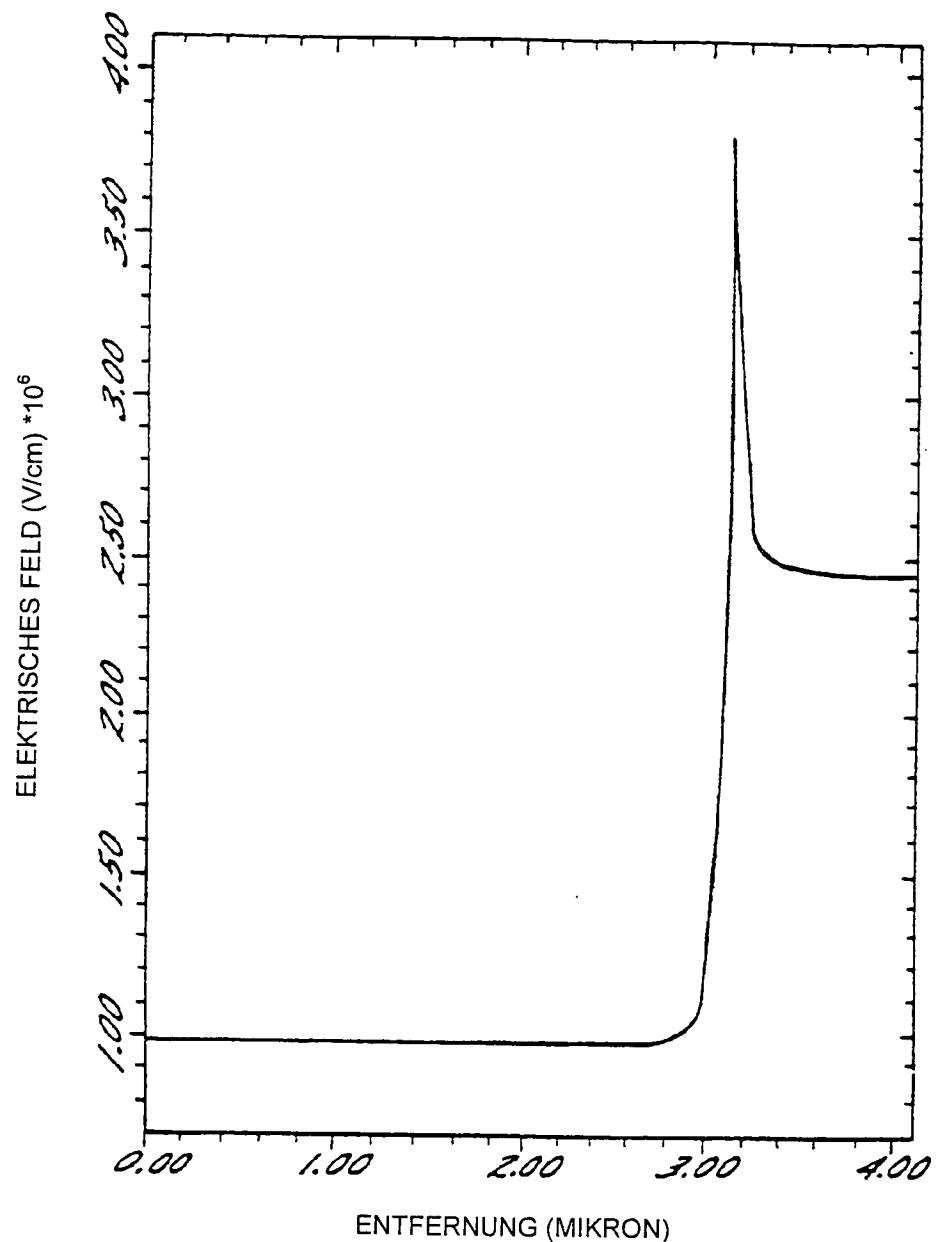

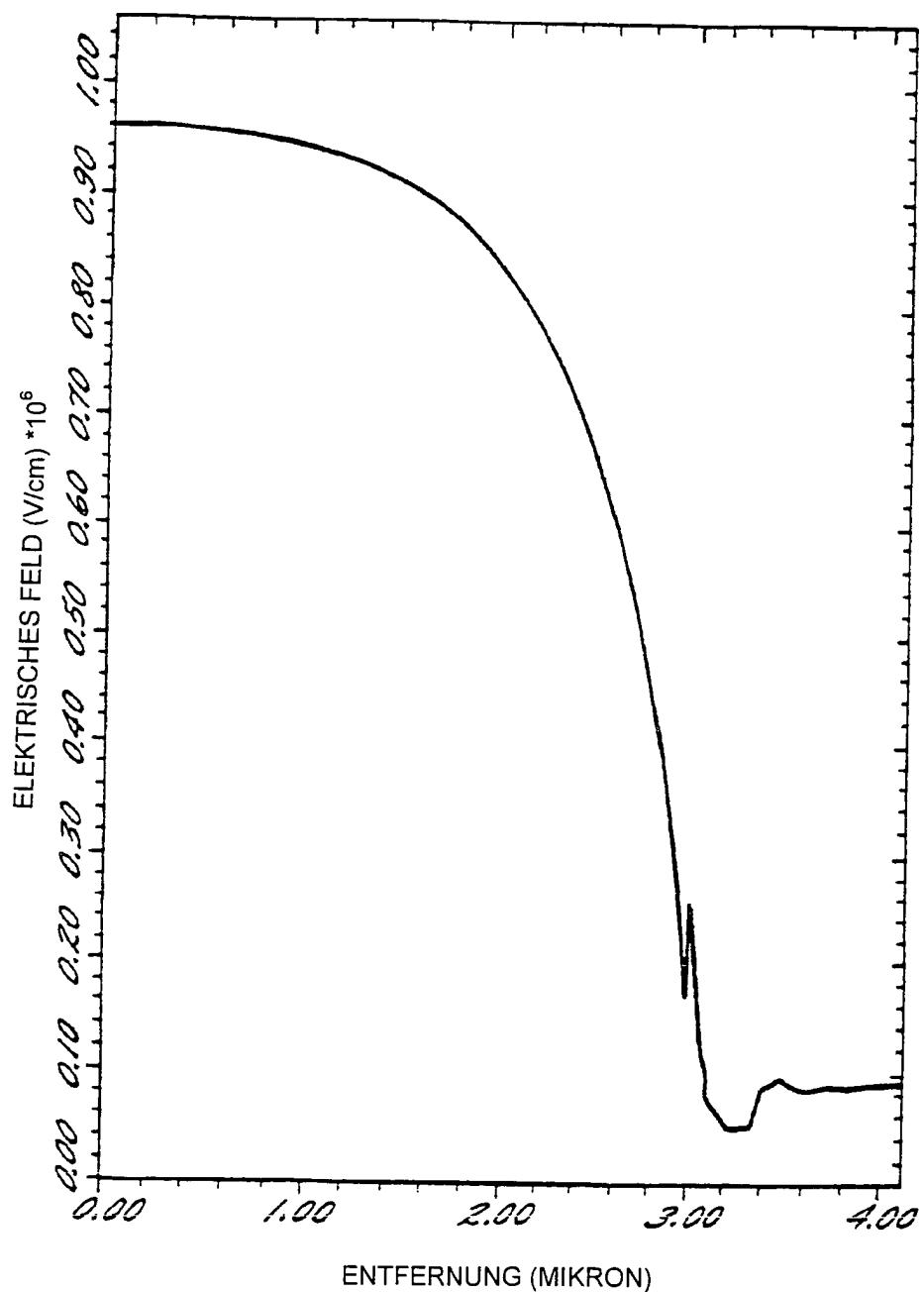

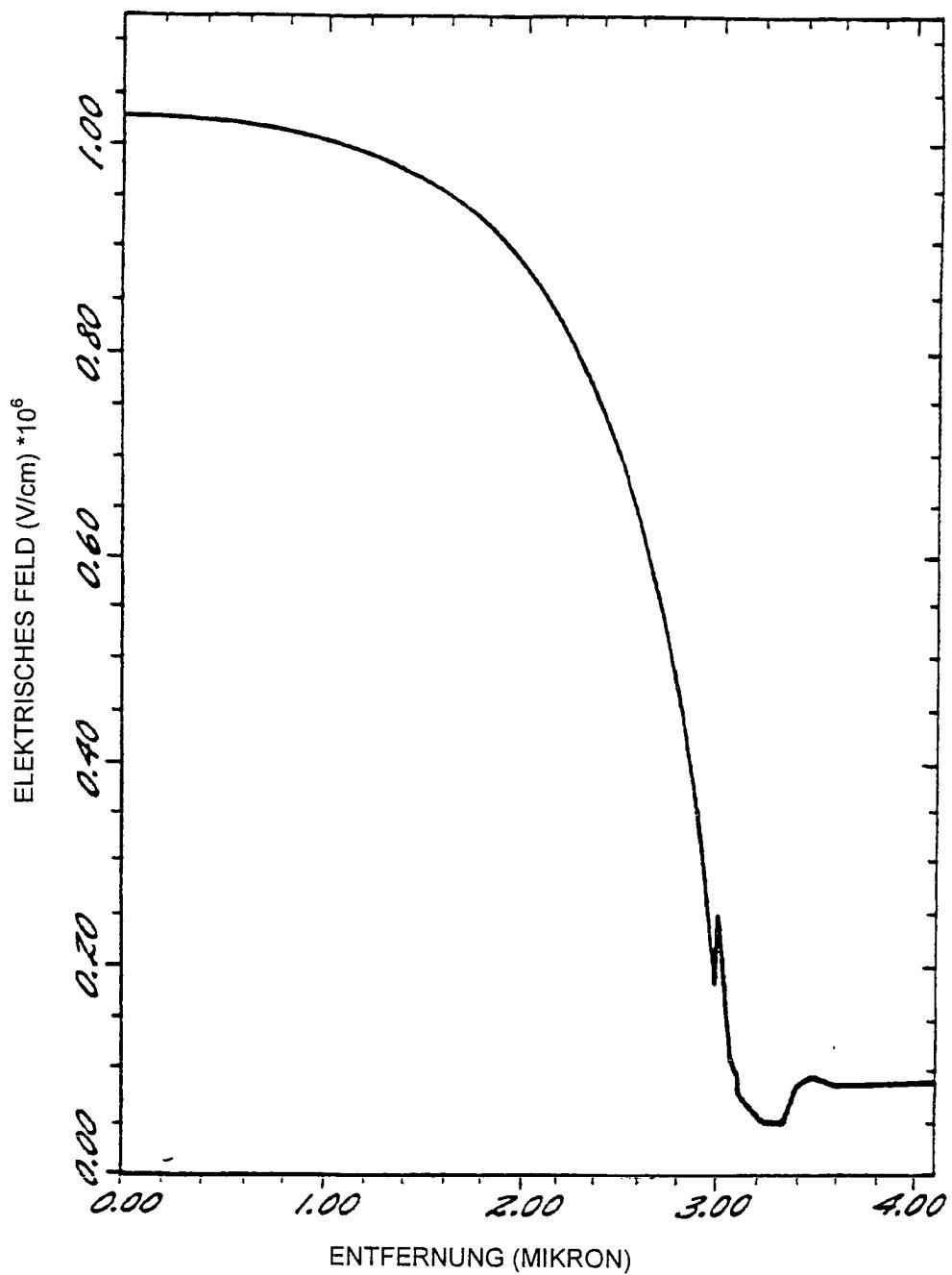

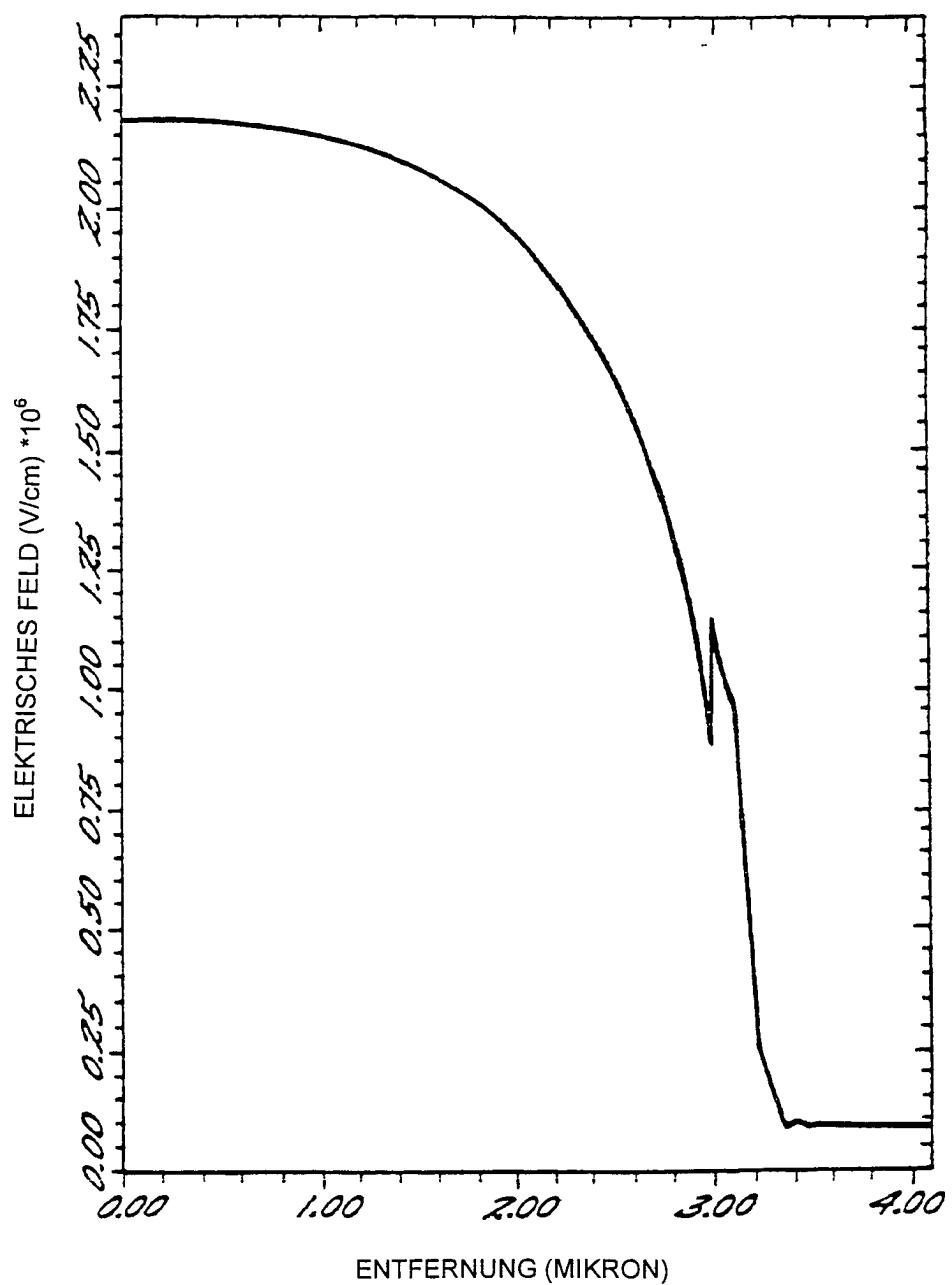

**[0017]** [Fig. 5](#) und [Fig. 6](#) stellen Diagramme der elektrischen Feldstärke bei verschiedenen Stellen innerhalb eines herkömmlichen UMOS gemäß dem Stand der Technik dar, welche auf den Gittern der [Fig. 3](#) und [Fig. 4](#) basieren.

**[0018]** [Fig. 7](#) und [Fig. 8](#) stellen Benutzer-definierte

Gitter für den UMOS gemäß der vorliegenden Erfindung basierend auf einem Vertikalquerschnitt von 4 Mikron- bzw. 16 Mikron dar.

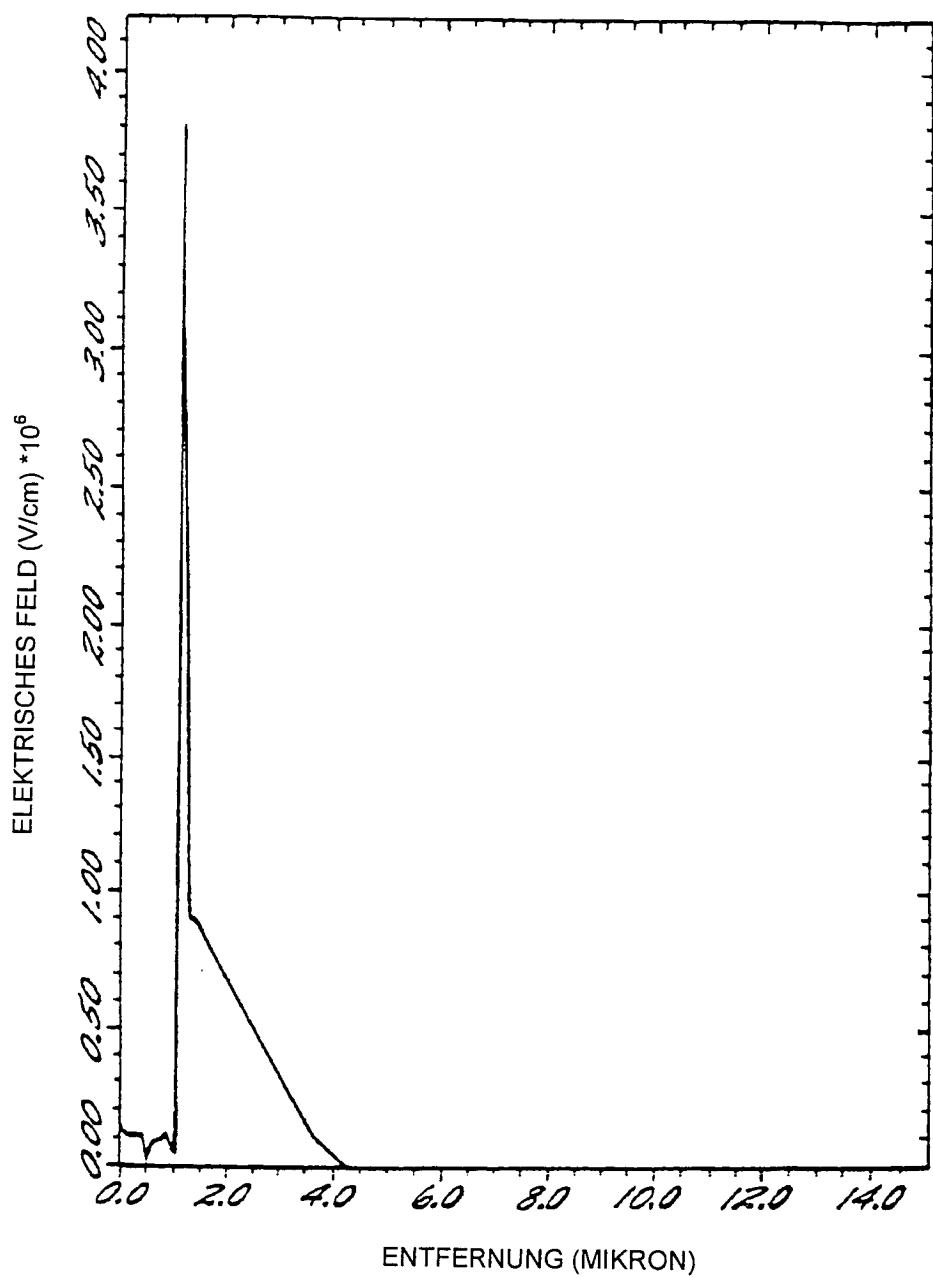

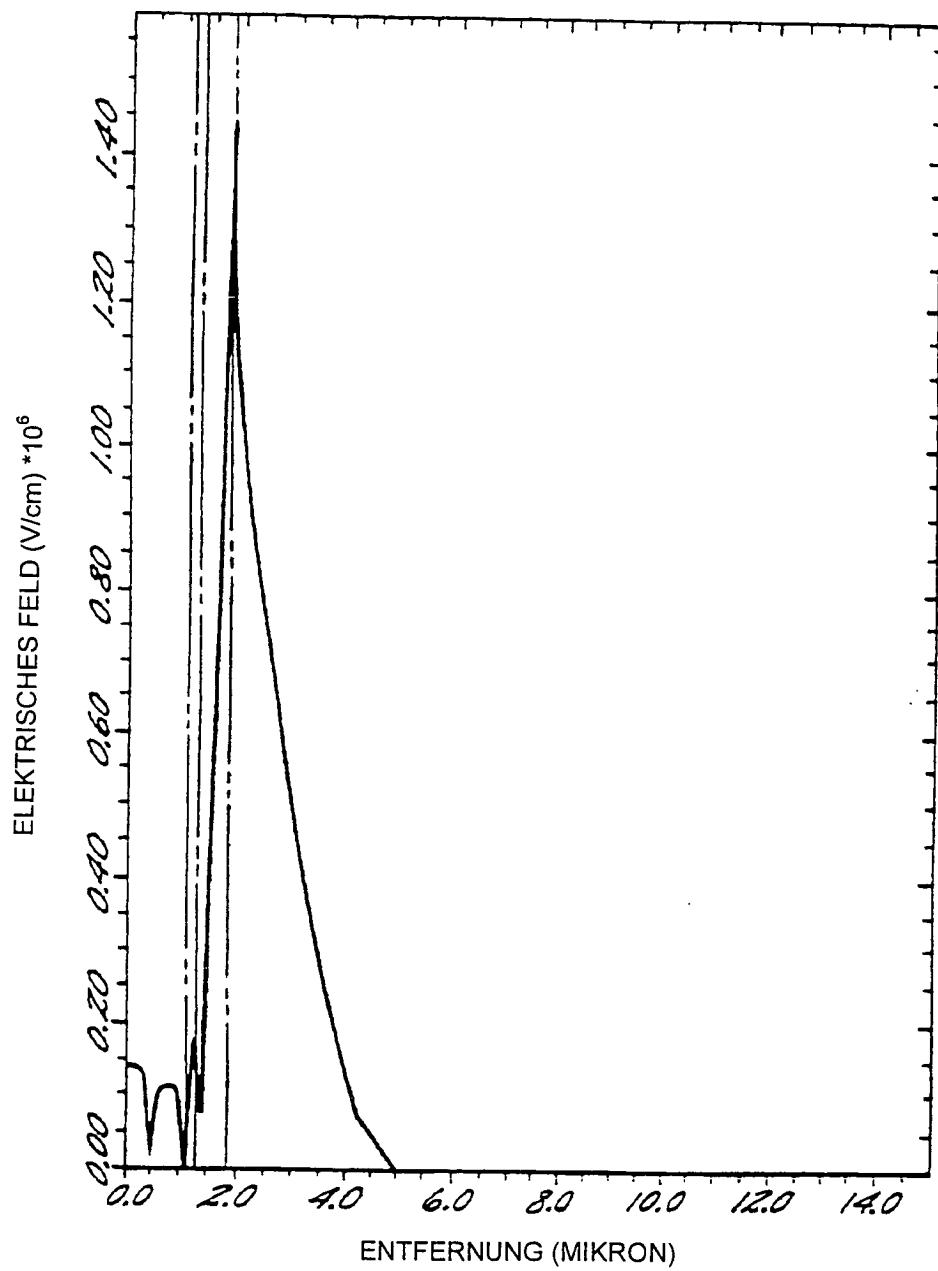

[0019] [Fig. 9](#) und [Fig. 10](#) stellen Diagramme der elektrischen Feldstärke bei verschiedenen Stellen innerhalb des UMOS der vorliegenden Erfindung dar, wie in [Fig. 7](#) und [Fig. 8](#) definiert.

[0020] [Fig. 11](#) und [Fig. 12](#) drücken den gleichen Informationstyp wie [Fig. 9](#) und [Fig. 10](#) aus, jedoch bei einer höheren, angelegten Spannung.

[0021] [Fig. 13](#) stellt ein Diagramm unter den gleichen Bedingungen wie bei [Fig. 11](#) und [Fig. 12](#) dar, jedoch entlang eines anderen Teils der Vorrichtung.

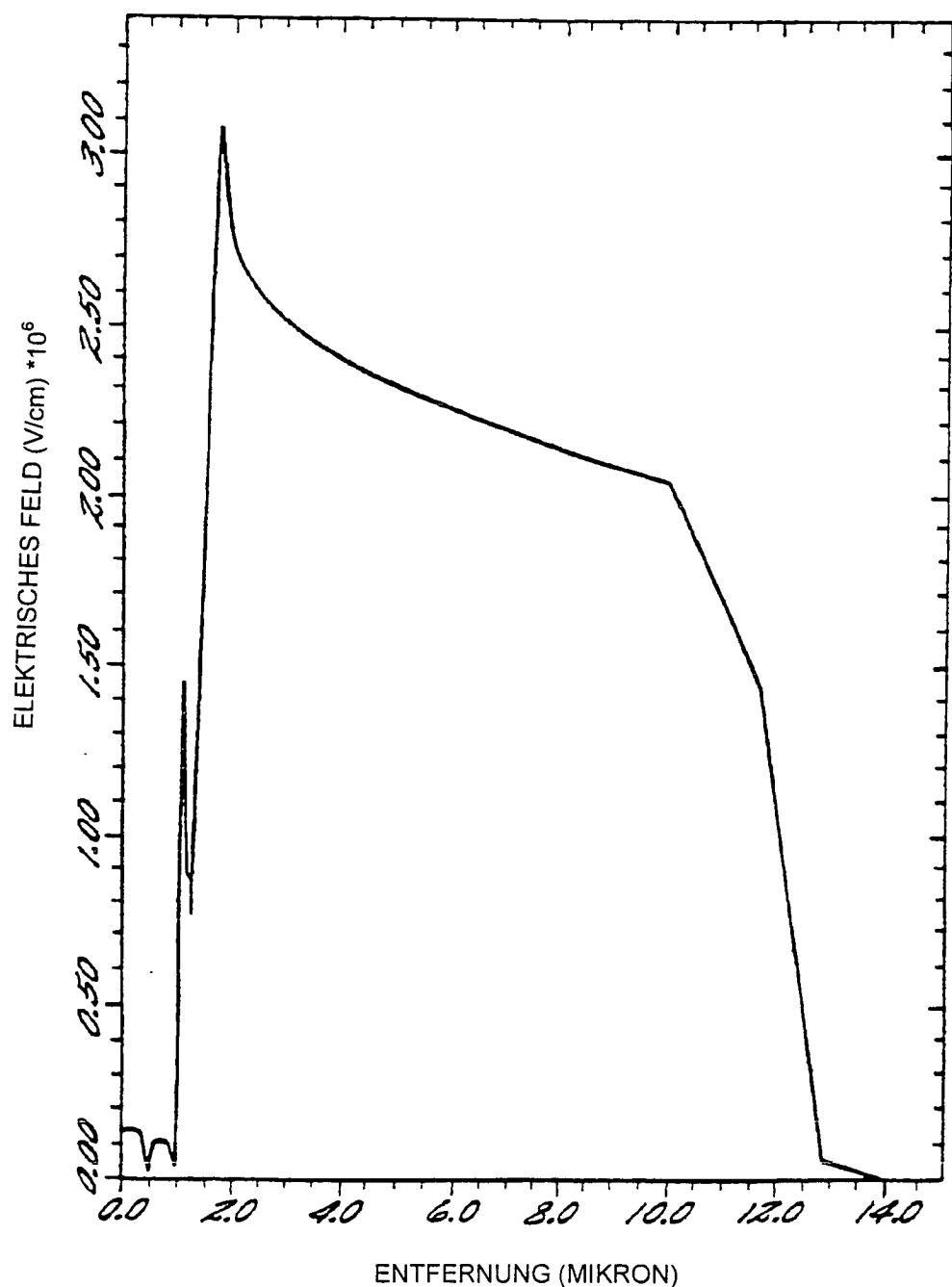

[0022] [Fig. 14](#) und [Fig. 15](#) stellen Diagramme ähnlich zu den [Fig. 9](#) bis [Fig. 12](#) dar, jedoch bei einem niedrigeren Dotierungsniveau als die in den vorherigen Figuren modellierten Vorrichtungen.

[0023] [Fig. 16](#) – [Fig. 18](#) stellen ähnliche Diagramme für die niedrigeren Dotierungsniveaus der [Fig. 14](#) und [Fig. 15](#) dar, jedoch unter viel höheren, angelegten Drain-Spannungen.

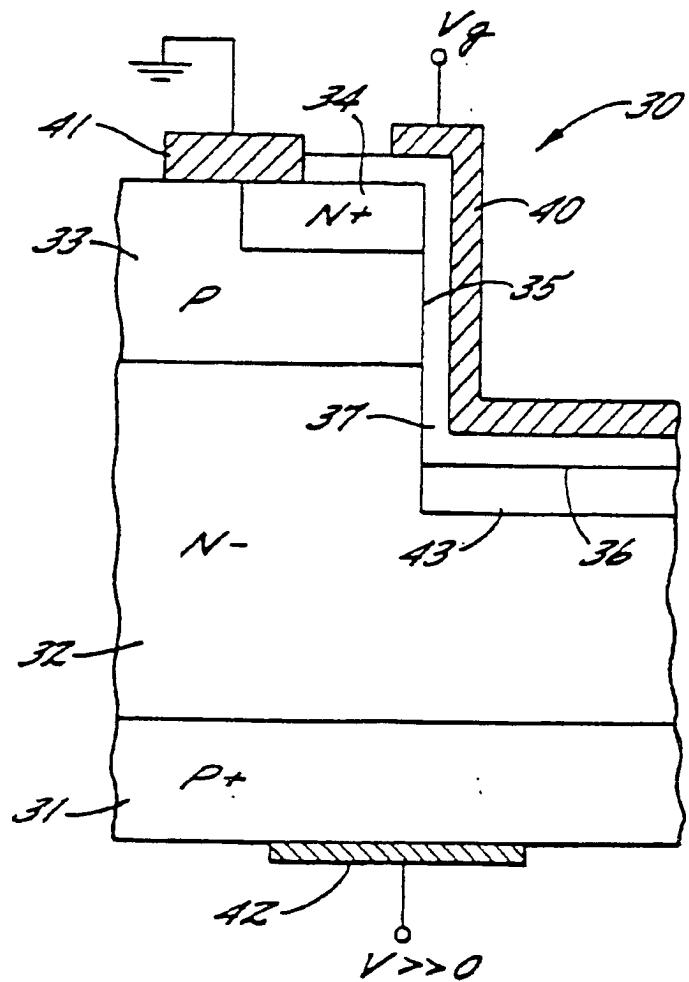

[0024] [Fig. 19](#) stellt einen IGBT gemäß der vorliegenden Erfindung dar.

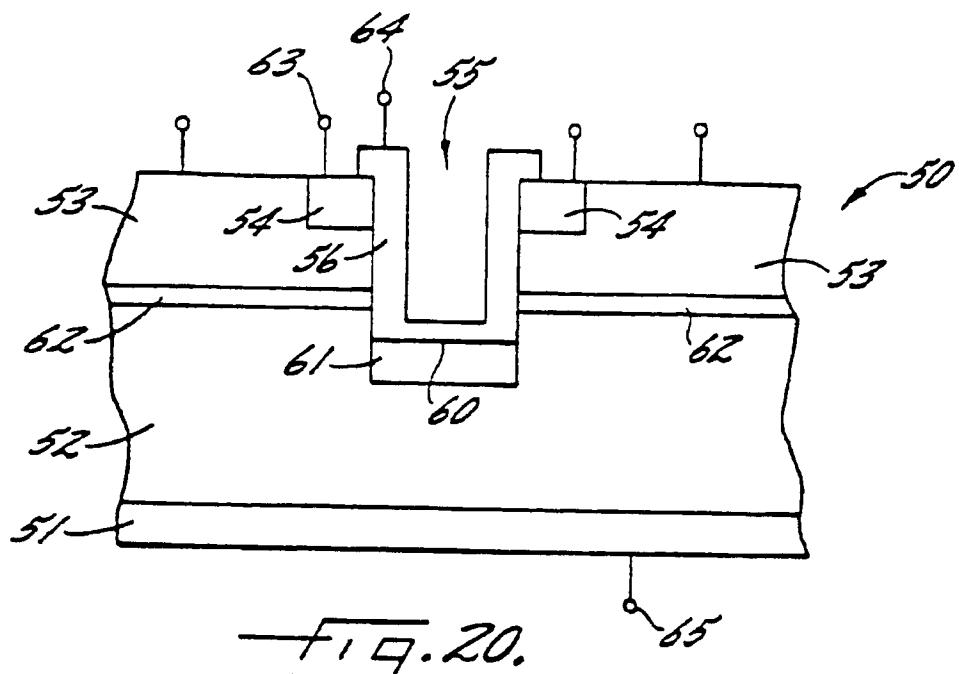

[0025] [Fig. 20](#) stellt eine Querschnittsansicht eines UMOS gemäß der vorliegenden Erfindung dar.

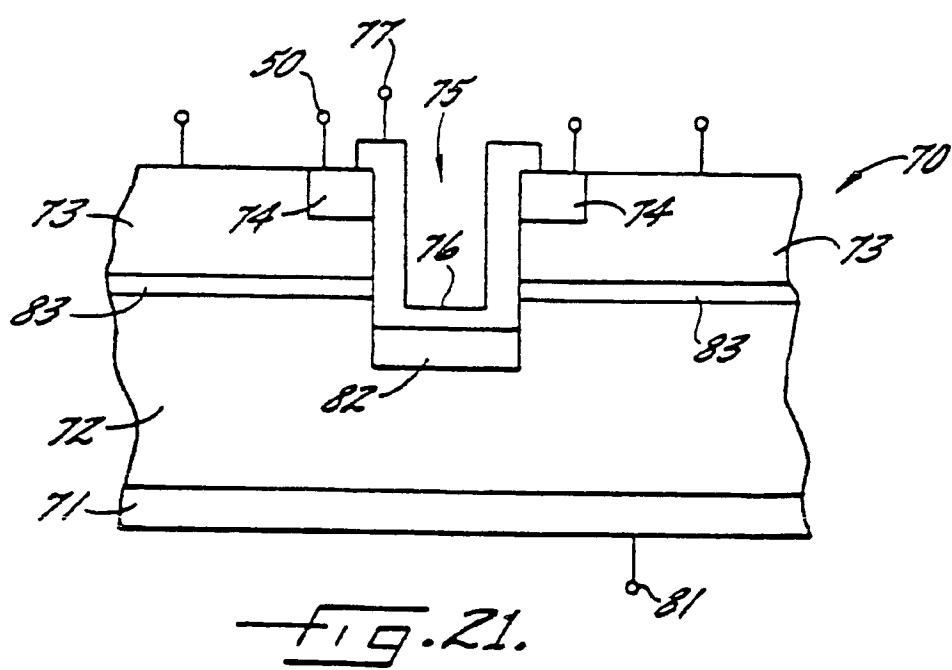

[0026] [Fig. 21](#) stellt eine Querschnittsansicht eines IGBT gemäß der vorliegenden Erfindung dar.

Detaillierte Beschreibung der bevorzugten Ausführungsform

[0027] Im weitesten Sinne stellen die bevorzugten Ausführungsformen der Erfindung einen Feldeffekt- oder bipolaren Transistor mit isoliertem Gate dar, bei dem das Gate-Material ein Oxid ist und bei dem der Halbleiter mit hinsichtlich des Oxids gegengesetzter Leitfähigkeit gegenüber liegend angeordnet ist, um das Oxid gegen hohe elektrische Felder zu schützen. Ein für das Verständnis der Erfindung hilfreiches Beispiel ist ein Siliziumkarbid-UMOS-Leistungstransistor, der in [Fig. 2](#) allgemein mit 10 bezeichnet ist. Zu Vergleichszwecken ist in [Fig. 1](#) eine Vorrichtung gemäß dem Stand der Technik veranschaulicht.

[0028] Der UMOS 10 ist aus einem n-leitenden Ein-kristall-Siliziumkarbid-Substrat 11, einer n-leitenden Siliziumkarbid-Epitaxialschicht 12 auf dem n-leitenden Substrat 11 und einer epitaxialen, p-leitenden Schicht 13 auf der n-leitenden Epitaxialschicht 12 gebildet. In der p-leitenden Epitaxialschicht 13 ist eine n-leitende Mulde 14 ausgebildet. Ein Gate-Graben, der durch eine Grabenwand 15 und einen flachen

Grabenboden 16 definiert ist, erstreckt sich durch die n-leitende Mulde 14 und die p-leitende Epitaxialschicht 13 und endet in der n-leitenden Epitaxialschicht 12. Das Gate-Oxid 17 bedeckt die Wand 15 und den Boden 16 des Grabens. Ohmsche Kontakte definieren die Source, das Gate bzw. die Drain. Insbesondere befindet sich der Gate-Kontakt 20 auf der Oxidschicht 17, der Source-Kontakt 21 befindet sich auf der p-leitenden Epitaxialschicht 13 und überlappt mit der n-leitenden Mulde 14, und der Drain-Kontakt 22 ist so zu dem n-leitenden Substrat 11 gebildet, dass die drei Kontakte die Source, das Gate und die Drain des UMOS 10 definieren.

[0029] Es gibt viele Metalle und Verbundmetallsysteme, die für diese Kontakte geeignet sind, und da diese im Allgemeinen im Stand der Technik wohl bekannt sind, müssen sie hier nicht detailliert beschrieben werden, außer dass bemerkt wird, dass bspw. Nickel oder Nickel-Titankombinationen geeignete ohmsche Kontakte zu einem n-leitenden Siliziumkarbid sind, während Aluminium oder Aluminium-Titan-kombinationen nützliche ohmsche Kontakte zu einem p-leitenden Siliziumkarbid sind. Vor kurzem hat Kobaltsilizid ( $CoSi_2$ ) Ansätze als ohmsches Kontaktmaterial zu einem p-leitenden Siliziumkarbid gezeigt.

[0030] Wie bereits im Abschnitt zum Hintergrund erwähnt, sind innerhalb der letzten Dekade Siliziumkarbid-Substrate und Substrate, die geeignete Epitaxialschichten umfassen, kommerziell erhältlich geworden. Deshalb wird ihre Bildung und ihr Wachstum hier nicht detailliert erläutert werden, außer dass bemerkt wird, dass ein exemplarisches Substrat und Epitaxialwachstumstechniken in den U.S.-Patenten 4,912,063; 4,912,064; Re. 34,861; und 5,011,549 aufgeführt sind. Ähnlich kann die Oxidschicht 17 ein gedampftes Oxid oder ein thermisches Oxid sein, und einige vorteilhafte Verfahren zum Bilden von hochqualitativen Siliziumdioxidschichten auf einem Siliziumkarbid werden in dem U.S.-Patent 5,459,107 aufgeführt. Geeignete ohmsche Kontaktstrukturen werden z.B. in den U.S.-Patenten 5,323,022 und 5,409,859 aufgeführt.

[0031] Wie [Fig. 2](#) zeigt, ist bei dem Beispiel das n-leitende Substrat 11 etwas stärker als die n-leitende Epitaxialschicht 12 mit geeigneten Dotierungskonzentrationen dotiert, die z.B.  $2 \times 10^{19} \text{ cm}^{-3}$  für das Substrat 11 und  $2 \times 10^{16} \text{ cm}^{-3}$  für die n-leitende Epitaxialschicht 12 betragen. Es versteht sich, dass die Verwendung einer n<sup>-</sup>-Epischicht auf einem n<sup>+</sup>-Substrat in besonderen Situationen gewisse Vorteile für einen Stromfluss bietet. Bei anderen Ausführungsformen stellt die einzelne n-leitende Schicht oder das Substrat eine geeignete Drain-Struktur bereit. Auf ähnliche Weise ist, vergleichend gesprochen, die n-leitende Mulde 14 stärker als entweder die p-leitende Epitaxialschicht 13 oder die n-leitende Epitaxialschicht 12 dotiert. Ein beispielhaftes Dotierungsni-

veau für die n-leitende Mulde **14** beträgt auch  $2 \times 10^{19} \text{ cm}^{-3}$  und für die p-leitende Schicht **13** beträgt es  $5 \times 10^{17} \text{ cm}^{-3}$ . Das Beispiel weist des Weiteren einen geerdeten p-leitenden Schutzbereich **23** zwischen der Oxid-Schicht **17** und der n-leitenden Epitaxialschicht **12** auf, die bei der in [Fig. 2](#) veranschaulichten Ausführungsform unter dem Bodenteil der Grabenoxid-schicht **17** liegt. Der p-leitende Schutzbereich **23** ist durch den ohmschen Kontakt geerdet, der schematisch bei **24** in [Fig. 2](#) gezeigt ist. Dieser ohmsche Kontakt ist typischerweise an der horizontalen Oberfläche **16** bei einer Stelle gebildet, die nicht durch das Gate-Metall und das Gate-Oxid bedeckt ist, z.B. bei einem Punkt auf einer Ebene hinter der Ansicht der [Fig. 2](#). Der p-leitende Bereich **23** ist nach dem Boden **16** des Gate-Grabens zum Schützen des Oxsids **17** in dem Graben gegenüber Verschlechterungs- oder Durchschlagseffekten einer großen positiven Spannung ausgerichtet, die an den Drain-Kontakt **22** angelegt ist.

**[0032]** Unabhängig von einer spezifischen Polarität ausgedrückt, ist der entgegengesetzt leitende Schutzbereich (**23** in [Fig. 2](#)) angrenzend an das isolierte Gate (Siliziumdioxid **20** in [Fig. 2](#)) angeordnet und schützt das Gate-Isolatormaterial **20** gegen die Verschlechterungs- bzw. Durchschlagseffekte einer großen Spannung, die an die Drain angelegt ist. Die Ergebnisse dieser Struktur sind formlos durch Vergleich der Feldstärkendiagramme der [Fig. 1](#) mit denen der [Fig. 2](#) veranschaulicht und sind noch formloser durch die Information veranschaulicht, die in [Fig. 3](#)-[Fig. 18](#) präsentiert wird. Sowohl in [Fig. 1](#) als auch in [Fig. 2](#) ist die Feldstärke entlang des p-n-Abschnitts grundsätzlich die gleiche. Die Wirkung eines Hinzufügens der p-Schicht **23** der vorliegenden Erfindung wird jedoch durch die Differenz zwischen dem Feld entlang des MOS-Abschnitts, der in [Fig. 1](#) gezeigt ist, gegenüber dem in [Fig. 2](#) gezeigten veranschaulicht. Wie [Fig. 2](#) veranschaulicht, hält die Erfindung die Spitzenfeldstärke des Oxsids derart, dass eine hohe, an die Drain angelegte Spannung (wie durch  $V_d \gg 0$  in [Fig. 2](#) gezeigt) die Oxsidschicht **17** im UMOS **10** der [Fig. 2](#) nicht auf die gleiche Weise beeinflusst, wie eine ähnlich hohe Drain-Spannung die Oxsidschicht bei dem Beispiel gemäß dem Stand der Technik der [Fig. 1](#) beeinflusst.

**[0033]** Indem die Oxsidschicht **17** im Wesentlichen gegen das Feld geschützt wird, das durch die Hochspannung erzeugt wird, ermöglicht die p-leitende Schicht **23**, dass sich die Leistung der Siliziumkarbidvorrichtung näher an ihr theoretisches Potential annähert.

**[0034]** Um eine formlose Angabe der Leistung der Vorrichtung zu erhalten, wird die in [Fig. 2](#) veranschaulichte Konstruktion unter Verwendung des MEDICI™-Simulationsprogramms für Vorrichtungen analysiert. MEDICI™, welches eines von vielen kom-

merziell erhältlichen Simulationsprogrammen für Vorrichtungen darstellt, wurde verwendet, um E-Feld-wert von jedem Punkt innerhalb der verschiedenen SiC-UMOS-Vorrichtungen mit den verschiedenen Vorspannungen aufzufinden. Daraus konnte die Maximalvorspannung für jeden UMOS mit dem maximalen E-Feld in der Oxsidschicht als kleiner oder gleich  $3 \times 10^6 \text{ V/cm}$  bestimmt werden. Für analytische Zwecke wurde dies als die maximale Vorspannung für die Vorrichtung definiert. Das MEDICI™-Programm kann von TMA, 595 Lawrence Expressway, Sunnydale, CA 94087 (URL: <http://www.tmai.com>) erhalten werden. MEDICI™ sagt die elektrischen Eigenschaften von beliebigen zweidimensionalen Strukturen unter Benutzer-spezifizierten Betriebsbedingungen voraus. Die Analyse von MOSFETs ist eine der typischen Vorrichtungsanwendungen, für die das MEDICI™-Simulationsprogramm nützlich ist. Die MEDICI™-Ergebnisse sind in [Fig. 3](#)-[Fig. 18](#) veranschaulicht. [Fig. 3](#)-[Fig. 6](#) beschreiben einen herkömmlichen UMOS gemäß dem Stand der Technik, während [Fig. 7](#)-[Fig. 18](#) einen UMOS gemäß der vorliegenden Erfindung beschreiben. [Fig. 3](#) stellt ein Benutzerdefiniertes Gitter bzw. Netz für eine herkömmliche UMOS-Leistungsvorrichtung dar, wie z.B. die in [Fig. 1](#) veranschaulichte. Unter Verwendung des MEDICI™-Programms wurden Anzahl und Ort der Gitterpunkte ausgewählt, die gewünschte Vorrichtung in einem zweidimensionalen Muster zu definieren. Üblicherweise, und wie in [Fig. 3](#) veranschaulicht, werden sehr viele Gitterpunkte ausgewählt und solchen Teilen der Vorrichtung zugewiesen, die die größten Effekte oder Reaktionen auf eine Spannung, einen Strom und ein elektrisches Feld zeigen werden. In [Fig. 3](#) bspw. werden dem Oxd eine große Anzahl von Gitterpunkten zugewiesen und erscheint in Form der dunklen L-förmigen breiten Linien. Wie die aufge-listeten Maße zeigen, veranschaulicht [Fig. 3](#) einen Teil des herkömmlichen UMOS im Querschnitt, der ungefähr 4 Mikron breit und 2 Mikron hoch ist. [Fig. 4](#) basiert auf den identischen Daten wie [Fig. 3](#), außer dass [Fig. 4](#) entlang einer vertikalen Entfernung von ungefähr 16 Mikron ausgedrückt ist.

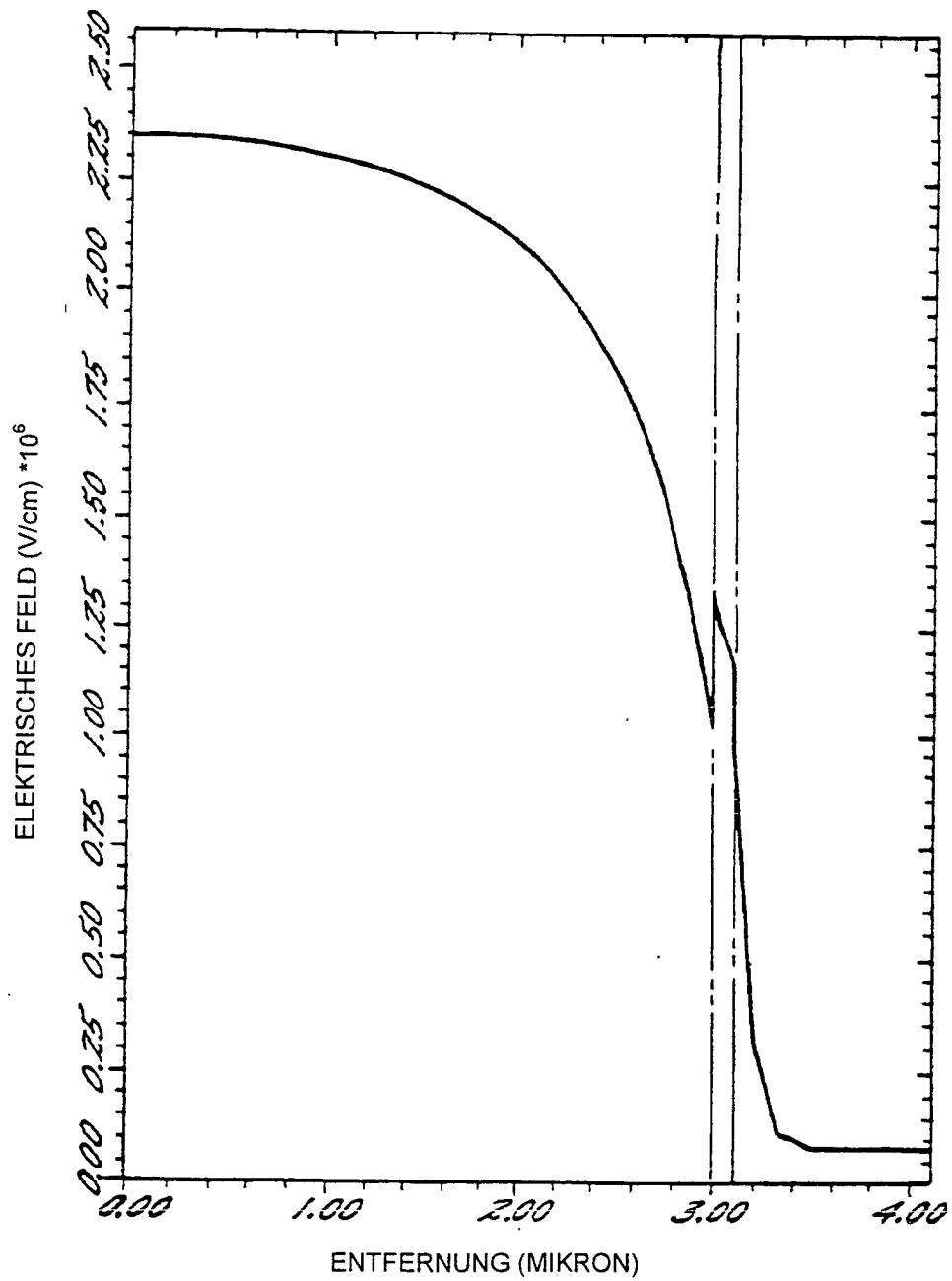

**[0035]** [Fig. 5](#) zeigt das Verhalten eines herkömmlichen SiC-UMOS wie er durch das MEDICI™-Programm modelliert ist. Das Diagramm der [Fig. 5](#) ist entlang der Linie  $y = 1,2033$  Mikron gezeigt; d.h. entlang einer horizontalen Linie zwischen der linken und rechten Grenze der [Fig. 3](#). Wie [Fig. 3](#) veranschaulicht, verläuft eine solche horizontale Linie durch den Oxidteil am Boden des UMOS-Grabens. Insbesondere modelliert [Fig. 5](#) das Verhalten des herkömmlichen UMOS bei einer Drain-Spannung von 150 Volt. Unter solchen Bedingungen beträgt die Spitze des elektrischen Felds ungefähr  $3,82 \times 10^6 \text{ V/cm}$  und erscheint entlang der horizontalen Linie bei einer x-Koordinate von ungefähr 3,08 Mikron. Zurückkehrend zu [Fig. 3](#) entspricht dies der Ecke des Oxsids, was im Allgemeinen die erwartete Position für die höchste

Feldstärke ist. Wie oben erwähnt, kann eine solch hohe Feldstärke das Oxid dazu veranlassen, entweder sofort durchzuschlagen oder sich derart schnell zu verschlechtern, dass die Vorrichtung unter solchen Bedingungen allgemein nutzlos wird. Wie ebenfalls zuvor erwähnt, sollte die elektrische Feldspitze bei dem Oxid wünschenswerterweise unterhalb von ungefähr  $2,5-3 \times 10^6$  V/cm sein, und vorzugsweise sogar geringer, um eine Oxidverschlechterung zu verhindern.

[0036] [Fig. 6](#) veranschaulicht die gleiche Information wie [Fig. 5](#), jedoch durch Messen des Felds entlang einer vertikalen Linie, die durch eine x-Koordinate von 3,0967 Mikron definiert ist, wiederum bei einer angelegten Drain-Spannung von 150 Volt. Wie [Fig. 6](#) zeigt, beträgt der Spitzenwert des elektrischen Felds wieder ungefähr  $3,82 \times 10^6$  V/cm und erscheint bei der Ecke des Oxids; d.h. bei einer Koordinate, die durch  $x = 3,1$  Mikron und  $y = 1,25$  Mikron definiert ist.

[0037] [Fig. 7](#) stellt ein Benutzer-definiertes MEDICI™-Gitter für den UMOS mit der implantierten p-Schicht (z.B. bei 23 in [Fig. 2](#) veranschaulicht) mit einer Tiefe von ungefähr 0,5 Mikron dar. Auf eine zur [Fig. 3](#) ähnliche Weise wird die größte Anzahl von Punkten im Gitter innerhalb des Oxideils ausgewählt, die wiederum als die großen L-förmigen durchgezogenen Linien in [Fig. 7](#) erscheinen. [Fig. 7](#) umfasst jedoch auch eine große Anzahl von Gitterpunkten, die der implantierten p-Schicht gerade unter dem Oxid entsprechen. Wie bei [Fig. 3](#) bedeckt das Querschnittsgitter der [Fig. 7](#) ungefähr vertikal 4 Mikron und horizontal 4 Mikron.

[0038] [Fig. 8](#) entspricht der gleichen Struktur wie [Fig. 7](#), ist jedoch graphisch dargestellt, um eine Tiefe von 16 Mikron zu zeigen.

[0039] [Fig. 9](#) zeigt das durch das MEDICI™-Programm vorhergesagte Verhalten für den UMOS bei einer angelegten Drain-Spannung von 150 Volt und Dotierungskonzentrationen von  $2,0 \times 10^{16} \text{ cm}^{-3}$  (2E16) in der n-Schicht (z.B. 12 in [Fig. 7](#)), von  $2 \times 10^{19} \text{ cm}^{-3}$  im Substrat 11 und  $5 \times 10^{17} \text{ cm}^{-3}$  sowohl in der p-leitenden Epischicht 13 als auch in dem geerdeten p-leitenden Bereich 23. [Fig. 9](#) ist entlang einer horizontalen Linie gezeigt, die wiederum durch  $y = 1,2023$  Mikron definiert ist; d.h. durch die gleiche horizontale Linie wie bei [Fig. 5](#). Somit ermöglichen [Fig. 5](#) und [Fig. 9](#) eine Basis zum Vergleichen der zwei Vorrichtungen bei einem strukturell äquivalenten Punkt. Wie [Fig. 9](#) zeigt, tritt eine Spitze im elektrischen Feld dennoch bei der Ecke des Oxids ( $x = 3$  Mikron,  $y = 20,12$  Mikron) auf, jedoch zeigt sie auch, dass das elektrische Feld bei dem Punkt stark verringert wurde; d.h. auf ungefähr  $0,278 \times 10^6$  V/cm; d.h. auf mehr als eine Größenordnung kleiner als das elektrische Feld bei der Oxidecke ohne die implantierte p-Schicht (im Vergleich zu dem Feld von  $3,82 \times$

$10^6$  V/cm bei dem gleichen Punkt in [Fig. 5](#) und [Fig. 6](#)).

[0040] [Fig. 10](#) stellt graphisch die gleiche Information wie [Fig. 9](#) dar, jedoch wieder entlang der vertikalen Linie bei  $x = 3,0967$ . Somit entspricht [Fig. 10](#) in ihrer Geometrie der [Fig. 6](#). [Fig. 10](#) zeigt zwei Spitzen. Die größte der beiden Spitzen fällt auf die Koordinaten  $x = 3,1$  und  $y = 1,75$ , was, Bezug nehmend auf [Fig. 7](#), an den p-n-Übergang angrenzt.

[0041] [Fig. 10](#) zeigt auch, dass die Oxidspitze bei der Ecke des Oxids abfällt ( $x = 3,1$  und  $y = 1,2$ ) und wieder stark verringert gegenüber der Vorrichtung gemäß dem Stand der Technik ist; d.h. ungefähr  $0,18 \times 10^6$  V/cm.

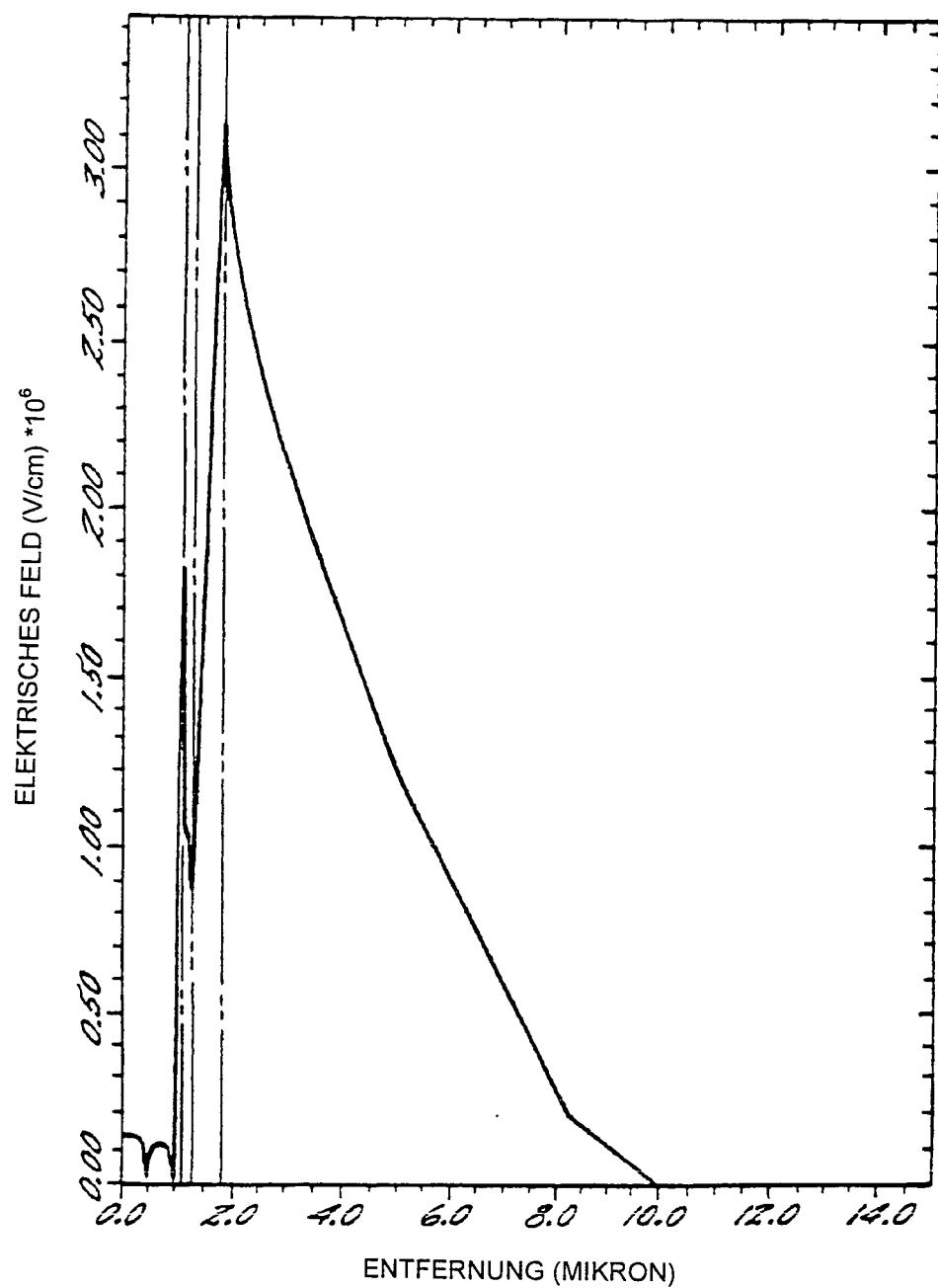

[0042] In [Fig. 11](#) ist das elektrische Feld entlang der gleichen horizontalen Linie ( $y = 1,2033$  Mikron) wie in den anderen ähnlichen Figuren, aber bei einer angelegten Drain-Spannung von 950 Volt, bei der Struktur der Erfindung aufgetragen. [Fig. 11](#) repräsentiert auch das gleiche Dotierungsniveau (2E16) in der n-Schicht wie in [Fig. 9](#) und [Fig. 10](#). Wiederum befindet sich die elektrische Feldspitze bei der Ecke des Oxids ( $x = 3, y = 1,2$  Mikron), ist jedoch relativ gering; d.h. ungefähr  $1,32 \times 10^6$  V/cm. Anders ausgedrückt, selbst bei einer angelegten Drain-Spannung von 950 Volt, verringert die Struktur der vorliegenden Erfindung das elektrische Feld bei der Spitze des Oxids auf einen Bruchteil des elektrischen Felds bei herkömmlichen Strukturen bei der gleichen Stelle und einer viel geringeren Spannung.

[0043] [Fig. 12](#) entspricht [Fig. 11](#) darin, dass sie eine angelegte Drain-Spannung von 950 Volt repräsentiert, aber wie bei den anderen Diagrammen ist sie entlang der vertikalen Linie  $x = 3,0967$  Mikron gezeigt. [Fig. 12](#) umfasst ebenfalls zwei Spitzen. Wieder repräsentiert die höhere der zwei Spitzen (bei Koordinaten  $x = 3,1$  und  $y = 1,9$  Mikron) das Feld bei dem p-n-Übergang und nähert sich dem Durchschlagfeld von Siliziumkarbid bei diesem Dotierungsniveau bei einer Stärke von ungefähr  $3,12 \times 10^6$  V/cm. Die andere Spitze tritt wieder bei der Ecke des Oxids auf ( $x = 3,1$  Mikron,  $y = 1,2$  Mikron) und beträgt ungefähr  $1,82 \times 10^6$  V/cm, was gut innerhalb der gewünschten Feldstärkenparameter liegt. [Fig. 13](#) ist entlang einer etwas anderen vertikalen Linie ( $x = 1,0536$  Mikron) als die vorherigen Diagramme gezeigt, repräsentiert jedoch auch 950 V, die an die Drain angelegt sind, und ein n-Dotierungsniveau von 2E16. Diese besondere x-Koordinate repräsentiert eine vertikale Scheibe der Struktur der Erfindung, die etwas aus dem Oxid entfernt wurde, und demonstriert somit die Feldstärke durch die p- und n-Teile des Transistors und insbesondere das Feld bei dem p-n-Übergang ( $x = 1,0536$ ,  $y = \text{ungefähr } 1,1$  Mikron).

[0044] [Fig. 13](#) zeigt, dass die Spitzenfeldstärke in

dem Siliziumkarbid nahe dem p-n-Übergang in der Größenordnung von ungefähr  $2,33 \times 10^6$  V/cm sein soll, was wiederum innerhalb der gewünschten Grenzen liegt. Wie zuvor erwähnt, wurden [Fig. 5](#) bis [Fig. 13](#) alle bei Dotierungskonzentrationen von  $2\text{E}16$  cm $^{-3}$  in der n-Schicht berechnet. Aufgrund des Dotierungseffekts auf die Durchschlagsspannung wurde wieder das MEDICI™-Programm verwendet, um das Verhalten der Struktur der Erfindung bei einem verringerten Dotierungsniveau von  $2,5 \times 10^{15}$  cm $^{-3}$  ( $2,5\text{E}15$ ) in der n-Schicht zu simulieren. Das Gitter ist das gleiche wie das ursprünglich bei [Fig. 7](#) und [Fig. 8](#) definierte, und somit entsprechen die Koordinaten der [Fig. 14](#)-[Fig. 18](#) denen der [Fig. 9](#)-[Fig. 13](#).

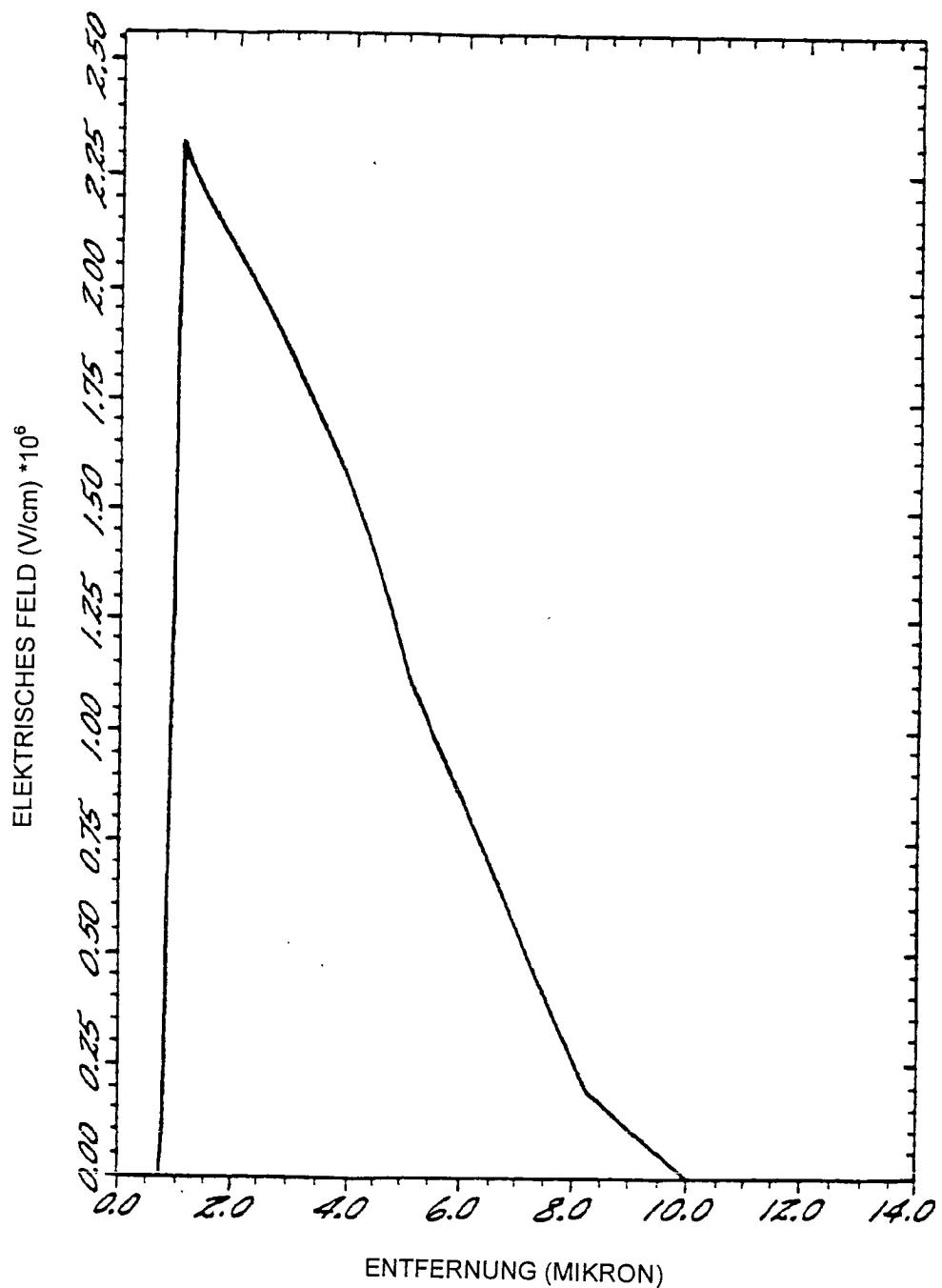

**[0045]** [Fig. 14](#) stellt ein weiteres Diagramm des elektrischen Felds entlang der vertikalen Linie bei einer Koordinate  $x = 3,0967$  Mikron dar, wobei eine Drain-Spannung von 950 Volt bei dem niedrigen Dotierungsniveau von  $2,5\text{E}15$  cm $^{-3}$  angelegt ist. [Fig. 14](#) umfasst zwei Spitzen, die wieder eine Feldstärke bei dem Oxid bzw. bei dem p-n-Übergang repräsentieren. Die Feldstärke bei dem p-n-Übergang ( $x = 3,1$  und  $y = 1,95$  Mikron) beträgt ungefähr  $1,69 \times 10^6$  V/cm, was gut innerhalb der gewünschten Grenzen liegt. Ähnlich beträgt das maximale Feld im Oxid ( $x = 3,1$  und  $y = 1,25$  Mikron) ungefähr  $0,19 \times 10^6$  V/cm, was gut unterhalb des Maximalfelds der entsprechenden Vorrichtung gemäß dem Stand der Technik liegt.

**[0046]** [Fig. 15](#) entspricht [Fig. 14](#), wobei jedoch die Daten entlang der horizontalen Linie  $y = 1,2033$  Mikron aufgetragen sind. Die entlang dieser Linie gezeigte Spitzenfeldstärke erscheint wieder bei der Ecke des Oxids ( $x = 3$  und  $y = 1,2$  Mikron) mit einem Wert von ungefähr  $0,25 \times 10^6$  V/cm, was wiederum gut unter dem Maximalfeld der Vorrichtung gemäß dem Stand der Technik liegt.

**[0047]** [Fig. 16](#) und [Fig. 17](#) repräsentieren Diagramme für die gleichen Dotierungsniveaus wie bei [Fig. 14](#) und [Fig. 15](#), jedoch bei einer angelegten Drain-Spannung von 2300 Volt. Das Spitzenfeld fällt weiter auf die Ecke des Oxids ( $x = 3$  und  $y = 1,2$  Mikron), und die Feldstärke bei diesem Punkt beträgt  $1,15 \times 10^6$  V/cm; d.h. sie beträgt nur noch einen Bruchteil der Feldstärke, die herkömmlichen Vorrichtungen bei viel geringeren Spannungen widerfährt.

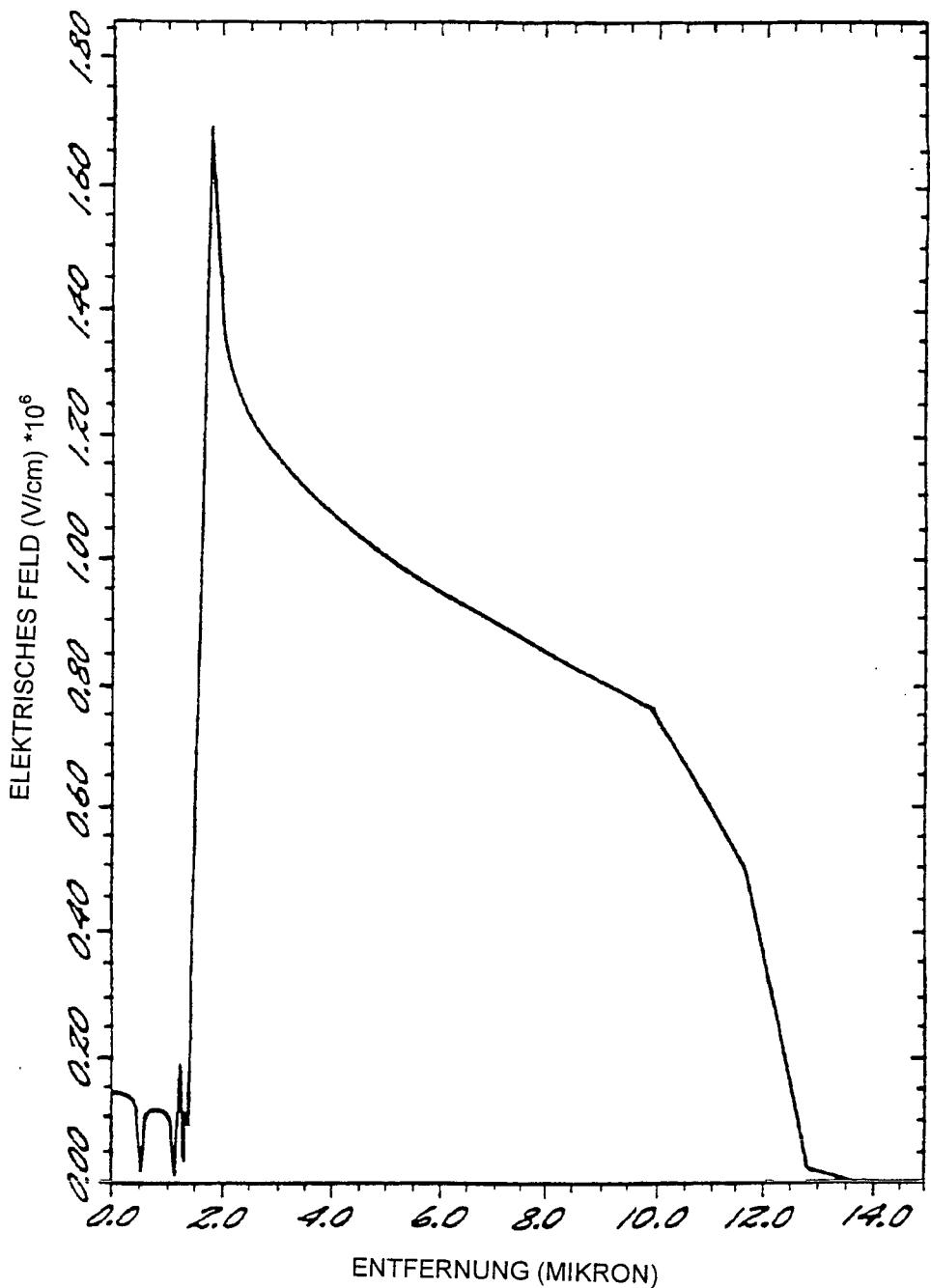

**[0048]** [Fig. 17](#) entspricht [Fig. 16](#), ist jedoch entlang der vertikalen Linie  $x = 3,0967$  Mikron gezeigt. Wie bei den anderen Diagrammen, die entlang einer vertikalen Linie gezeigt sind, zeigt [Fig. 17](#) zwei Spitzen, von denen die höhere den p-n-Übergang ( $x = 3,1$  und  $y = 1,8$  Mikron) repräsentiert. Bei dem p-n-Übergang erreicht das elektrische Feld ungefähr  $3,1 \times 10^6$  V/cm; d.h. ist näher an der Durchschlagsspannung des Siliziumkarbids bei diesem Dotierungsniveau. Die Spitzenfeldstärke bei dem Oxid bleibt jedoch viel

geringer, in der Größenordnung von ungefähr  $1,47 \times 10^6$  V/cm; d.h. sie ist ein Bruchteil der Feldstärke, die problematisch werden würde.

**[0049]** Schließlich entspricht [Fig. 18](#) [Fig. 13](#) (d.h. einer vertikalen Linie bei  $x = 1,0536$  Mikron), abgesehen von dem niedrigeren Dotierungsniveau ( $2,5\text{E}15$  cm $^{-1}$ ) und der höheren Drain-Spannung (2300 Volt). [Fig. 18](#) zeigt, dass entlang dieser vertikalen Linie, das Feld durch die p- und n-Teile der Vorrichtung stark ist und näher an einem Durchschlag bei all diesen Punkten ist (d.h. immer über ungefähr  $2,10 \times 10^6$  V/cm).

**[0050]** Kurz zusammengefasst, [Fig. 4](#) bis [Fig. 18](#) zeigen, dass der UMOS einen höheren Widerstand gegen eine Oxiddegradation oder einen Oxiddurchschlag bei Spannungen bietet, die sowohl um ein Vielfaches oder um Größenordnungen größer sind, als die bei denen herkömmliche UMOS-Vorrichtungen aus Siliziumkarbid einen Durchschlag erfahren würden. Als Provisio kann die relativ enge Nähe der p-leitenden Epitaxialschicht des Transistors zu dem implantierten p-leitenden Schutzbereich einen Pinch-Effekt hervorrufen, der den Einstrom der Vorrichtung verringert. Dementsprechend wird der geerdete p-leitende Bereich ausreichend von der p-leitenden Epitaxialschicht beabstandet, um jegliche Pinch-Effekte zu minimieren.

**[0051]** Ein Verfahren zum Herstellen eines Siliziumkarbid-Leistungsverstärkers mit isoliertem Gate umfasst: Ätzen einer ersten gegenüber liegenden Siliziumkarbidstruktur einer ersten Leitfähigkeit, um einen Graben mit einer ersten gegenüber liegenden Wand einer ersten Leitfähigkeit zu definieren, Bilden einer Schicht einer entgegengesetzten Leitfähigkeit an dem Boden des Grabens und Ausrichten durch die Grabenwände, Bilden einer geeigneten Oxidationschicht an den Grabenwänden und dem Grabenboden, und dann Hinzufügen jeweiliger ohmscher Kontakte, um die Source, das Gate und die Drain (oder einen Emitter in einem IGBT) zu bilden.

**[0052]** Dementsprechend kann beim Erzeugen der zuvor beschriebenen Beispiele mit der n-leitenden Source und Drain das Verfahren des Weiteren aufweisen: Züchten einer p-leitenden Epischicht, entweder auf einer n-leitenden Epischicht oder einem n-leitenden Substrat, gefolgt von dem Schritt eines Formens einer n-leitenden Mulde in der p-leitenden Epischicht. Dies schafft eine n-p-n-SiC-Struktur, die geätzt werden kann, um eine n-p-n-Wand zu erzeugen. Eine Epitaxie von SiC wird normalerweise durch eine chemische Bedampfung („chemical vapor deposition, CVD“) erreicht. Sowohl 4H- als auch 6H-SiC-Wafer mit kundenspezifischen Epischichten sind kommerziell erhältlich. Diese Schichten können stickstoffsdotiert (n-leitend) oder aluminiumdotiert (p-leitend) bei Dotierungsniveaus von  $10^{14}$  cm $^{-3}$  bis  $10^{20}$  cm $^{-3}$  sein.

**[0053]** Wahlweises Bereichsdotieren wird durch Ionenimplantation erreicht. Dies ist notwendig, da thermale Diffusionskoeffizienten in SiC zu klein für eine Diffusion von Unreinheiten sind, um praktikabel zu sein. SiC kann mit mehr als  $10^{19} \text{ cm}^{-3}$  mit Stickstoff (n-leitend) und sowohl mit Bor als auch Aluminium (p-leitend) implantiert sein. Bei bevorzugten Ausführungsformen wird die Implantation mit dem Wafer bei einer erhöhten Temperatur durchgeführt, und die Implantate werden bei 1200 bis 1500°C in Argon aktiviert. (Man bemerke, dass ein Siliziumwafer bei 1500°C schmelzen würde). Eine solche Hochtemperaturimplantation ist im U.S.-Patent 5,087,576 beschrieben. Anisotropes Ätzen erfolgt durch RIE. Jedes mit Fluorid behandelte Gas kann verwendet werden, einschließlich  $\text{NF}_3$  und  $\text{SF}_6$ . Geeignete Techniken zum Ätzen von Siliziumkarbid werden bspw. im U.S.-Patent 4,865,685 und 4,981,551 beschrieben. Ein frühes von Forschern beschriebenes Problem war eine Mikromaskierung, die durch eine Kontamination mit Aluminiumpartikeln während RIE von SiC verursacht wurde. Dieses Problem kann durch Hinzufügen einer Graphitabdeckplatte über der Aluminiumkathode in der RIE-Kammer eliminiert werden. Hoch anisotope Profile können bei 6H-SiC bis zu einer Tiefe von einigen zehn Mikron dementsprechend erhalten werden. Die Oberflächenmorphologie der geätzten Oberflächen ist gut.

**[0054]** Hinsichtlich einer thermalen Oxidation stellen MOS-Oxide kritische Elemente bei den meisten Halbleitervorrichtungen, insbesondere Leistungsvorrichtungen dar. Die wichtigsten Gütefaktoren sind die Grenzflächenzustandsdichte („interface state density“) DIT, die feste Ladungsdichte QF und das Durchschlagsfeld EBOX. Die Schwierigkeit besteht im Erhalten einer genauen Messung der Grenzflächenzustandsdichte DIT auf SiC. Aufgrund des breiten Bandabstands von SiC befinden sich tiefer liegende Grenzflächenzustände bei der  $\text{SiO}_2/\text{SiC}$ -Grenzfläche nicht im thermischen Gleichgewicht mit dem Halbleiter bei Raumtemperatur, und die Besetzung der Grenzfläche kann Änderungen der DC-Vorspannung nicht folgen. Um die Grenzflächenzustandsdichte unter Verwendung von CV-Techniken korrekt zu messen, ist es notwendig, die Probe zu erhitzen, damit die Zustände in einem quasi-stabilen Zustand bleiben können, wenn die Gate-Spannung geändert wird. Dies wurde von keinem SiC-Forscher erkannt und mehrere falsche Berichte existieren in der Literatur.

**[0055]** Ein besserer Ansatz scheint eine modifizierte Stark-Schwach-Kapazitätstechnik („hi-lo capacitance technique“) und eine AC-Konduktanztechnik bei erhöhten Temperaturen zu sein, um die  $\text{SiO}_2/\text{SiC}$ -Grenzfläche zu charakterisieren. Dicke Oxide werden für Feld- und Zwischendielektrika und als Passivierungsschichten für einen Feldabschluss bei Hochspannungsvorrichtungen verwendet. Es ist auf-

grund der langen Zeiten und damit einhergehenden Temperaturen nicht praktisch, dicke Oxide mittels einer herkömmlichen thermischen Oxidation wachsen zu lassen. Des Weiteren kann eine Dopantumverteilung (Segregation) in ein wachsendes thermisches Oxid ein Problem darstellen. Verschiedene andere Techniken werden, abhängig von den Umständen, bevorzugt: (i) Ablagerung von dickem  $\text{SiO}_2$  durch entweder LPCVD oder PECVD, (ii) Ablagerung einer amorphen Siliziumschicht, die später durch thermische Oxidation zu  $\text{SiO}_2$  gewandelt wird oder (iii) Anwendung von Aufschleuderglas („spin-on-glass, SOG“).

**[0056]** Ohmsche Kontakte werden zu n-leitenden und p-leitenden Schichten mittels geglühtem Nickel bzw. geglühtem Aluminium gebildet. Diese Prozeduren sind völlige Routine, und spezifische Kontaktwiderstandsfähigkeiten im Bereich von  $10^{-6} \text{ Ohm/cm}^2$  können durch stark dotiertes n-leitendes SiC erhalten werden. Ohmsche Kontakte zu p-leitendem Material sind schwieriger, und Kontaktwiderstandsfähigkeiten reichen von  $10^{-6} \text{ Ohm/cm}^2$  für leicht dotiertes Material bis  $10^{-1} \text{ Ohm/cm}^2$  für stark dotiertes Material.

**[0057]** Schottky-Kontakte sind einfach herzustellen und ein Fermi-Niveau-Pinning wird nicht beobachtet. Folglich sind Barrierenhöhen eine Funktion des Metalls, und ein weiter Bereich von Barrierenhöhen ist erreichbar. Typische, für Schottky-Kontakte auf SiC verwendete Metalle sind Au, Pt und Ti.

**[0058]** Metall- und Polysilizium-Ablagerungsprozeduren sind ähnlich zu Silizium, und im Allgemeinen trifft man auf keine unüblichen Probleme. Bevorzugte Techniken umfassen Boot-bedampftes („boat-evaporated“) Aluminium, Molybdän oder LPCVD-Polysilizium als Gate-Materialien für SiC-MOSFETs.

**[0059]** Bei einer anderen Ausführungsform weist die Erfindung einen bipolaren Transistor mit isoliertem Gate (IGBT) auf. Für einen Fachmann auf dem Gebiet solcher Vorrichtungen weist ein IGBT die hohe Eingangsimpedanz und Hochgeschwindigkeitseigenschaften eines MOSFET der Leitfähigkeiteigenschaft – geringe Sättigungsspannung – eines bipolaren Transistors auf. Bei seiner typischsten Anwendung wird der IGBT durch Anlegen einer positiven Spannung zwischen der Source und dem Emitter eingeschaltet und wird, wie bei einem MOSFET, ausgeschaltet, indem das Gate-Signal genullt oder leicht negativ gemacht wird. Ein IGBT hat einen viel geringeren Ein-Widerstand als ein entsprechender MOSFET. Verglichen zu einem MOSFET ist ein IGBT im Allgemeinen kleiner bei dem gleichen Nennstrom, obwohl die bipolare Wirkung bei einem IGBT die Vorrichtung derart verlangsamt, dass sie eine viel niedrigere Frequenz als ein entsprechender MOSFET aufweist. IGBTs werden detailliert bei Dorf, The Electrical Engineering Handbook (1993), CRC Press, auf

Seiten 699-700 diskutiert; und verwandte Vorrichtungen, wie z.B. der feldgesteuerte Thyristor werden bei Sze, Physics of Semiconductor Devices, 2. Ausgabe, 1981 auf Seiten 238-240 diskutiert. Dementsprechend werden die Struktur und die Funktion des IGBT hier nicht detailliert erläutert werden, außer um diese Ausführungsform der vorliegenden Erfindung zu veranschaulichen.

**[0060]** Bei dieser Ausführungsform weist die Erfindung einen bipolaren Leistungstransistor mit isoliertem Gate auf, der aus Siliziumkarbid mit Siliziumdioxid als Gate-Isolator gebildet ist. Der Transistor umfasst eine Source des ersten Leitfähigkeitsstyps und einen Schutzbereich unter dem Gate-Oxid, das den entgegengesetzten Leitfähigkeitsstyp relativ zur Source aufweist, um das Gate-Oxid gegen die Verschlechterungs- oder Durchschlagseffekte einer großen Spannung zu schützen, die über dem Transistor angelegt ist.

**[0061]** Ein IGBT gemäß der vorliegenden Erfindung ist in [Fig. 19](#) veranschaulicht und allgemein mit **30** bezeichnet. Der IGBT **30** weist ein p-leitendes Siliziumkarbid-Substrat **31**, eine n-leitende Siliziumkarbid-Epitaxialschicht **32** auf dem p-leitenden Substrat **31**, eine p-leitende Siliziumkarbid-Epitaxialschicht **33** auf der n-leitenden Epitaxialschicht **32** und eine n-leitende Mulde **34** in der p-leitenden Epitaxialschicht **33** auf. Ein Gate-Graben, der durch seine Wand **35** und seinen Boden **36** veranschaulicht ist, erstreckt sich durch die n-leitende Mulde **34** und die p-leitende Epitaxialschicht **33** und endet in dem n-leitenden Substrat **32**. Ein Gate-Oxid **37** befindet sich an der Wand **35** und dem Boden **36** des Grabens. Ohmsche Kontakte **40**, **41** bzw. **42** zu dem Gate-Oxid **37**, n-leitende Mulde **34** und dem p-leitenden Substrat **31** definieren das Gate, die Source und den Emitter.

**[0062]** Wie bei den anderen Ausführungsformen umfasst der IGBT **30** einen p-leitenden Siliziumkarbidbereich **43** zwischen dem Gate-Oxid **37** und der n-leitenden Epitaxialschicht **32** und ist entlang des Bodens **36** des Gate-Grabens zum Schützen des Oxids **37** im Graben gegen die Verschlechterungs- oder Durchschlagseffekte einer großen positiven Spannung ausgerichtet, die über dem Transistor **30** angelegt ist. Der p-leitende Bereich ist geerdet und wird durch Implantation gebildet, wie zuvor erläutert. Auf ähnliche Weise und wie bei den MOSFET-Beispielen ist der p-leitende Bereich **43** ausreichend von der p-leitenden Epitaxialschicht **33** beabstandet, um jegliche Strom-Pinch-Effekte zwischen dem p-leitenden Bereich **43** und der p-leitenden Epitaxialschicht **33** zu minimieren.

**[0063]** Wie bei den Beispielen werden die ohmschen Kontakte zu den n-leitenden Bereichen aus der Gruppe ausgewählt, die aus Nickel und Nickellegerungen besteht, während die ohmschen Kontakte

zu dem p-leitenden Material vorzugsweise aus der Gruppe ausgewählt werden, die aus Aluminium, Aluminiumlegierungen und Kobalsilizid besteht. Wie bei den Beispielen, wird Stickstoff typischerweise zum Dotieren des n-leitenden Materials bevorzugt, während das p-leitende Material typischerweise mit entweder Aluminium oder Bor dotiert ist. Wie bei den früheren Ausführungsformen weist das Siliziumkarbid in dem Transistor **30** einen Polype auf, der aus der Gruppe bestehend aus 4H und 6H ausgewählt ist.

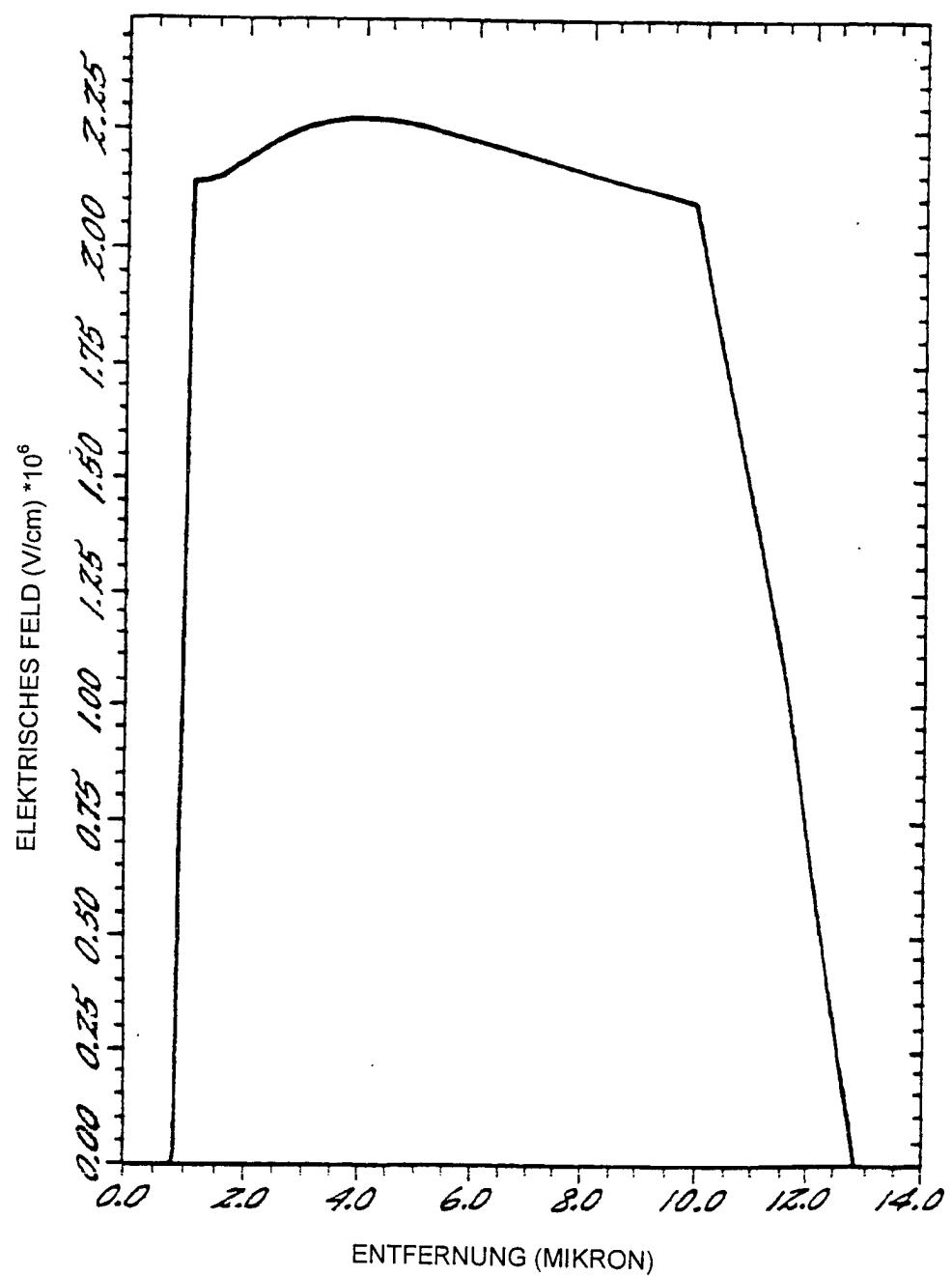

#### Verringerung des Ein-Widerstands

**[0064]** [Fig. 20](#) veranschaulicht eine Ausführungsform gemäß der Erfindung. In dieser Hinsicht zeigt die hier verwendete MEDICI™-Simulation ebenfalls, dass der durch die zusätzliche p-leitende Schicht an dem Boden des Grabens gebotene Schutz steigt, wenn die Entfernung („d“ in [Fig. 20](#)) entlang der Grabenwand zwischen der p-leitenden Schicht des Transistors und der p-leitenden Schutzschicht abnimmt. Alternativ ausgedrückt, die Schutzwirkung ist besser für das Oxid, wenn diese zwei p-leitenden Teile der Vorrichtung enger zueinander angeordnet sind. Wie zuvor als Maßnahme erwähnt, führt jedoch eine Verringerung dieses Abstands zwischen den p-leitenden Bereichen zur Unterstützung einer Abschnürung zwischen ihnen, was eventuell den gesamten Strom bei einer Durchlassspannung blockieren kann. Basisberechnungen zeigen, dass für typischerweise nützliche Dotierungskonzentrationen in den p- und n-leitenden Teilen des UMOS (z.B.  $p = 2 \times 10^{17} \text{ cm}^{-3}$ ,  $n = 2,5 \times 10^{15} \text{ cm}^{-3}$ ) eine Abschnürung auftreten wird, wenn die Entfernung zwischen den zwei p-leitenden Teilen geringer als ungefähr 1,5 Mikron ist.

**[0065]** Jedoch stellt ein Erhalten eines 1,5 Mikron breiten Spalts einige Probleme dar. Von einem Verarbeitungsstandpunkt aus erfordert es ein physikalisches Definieren eines solchen Abstands erstens, dass der Graben bis zu einer Tiefe von ungefähr 3 Mikron geätzt werden muss. Dementsprechend werden theoretisch, falls Aluminium auf eine übliche Weise als reaktive Ionenätz(RIE-)Maske verwendet wird, zumindest ungefähr 6750 A Aluminium benötigt. Tatsächlich wären jedoch aufgrund der Dickeänderung der Aluminiumablagerung und einer Ätzratenvariation während RIE 8000 A Aluminium üblicherweise für eine sichere Maske notwendig. Die Aluminiummaske müsste dann unter Verwendung einer Abhebetechnik entfernt werden, um gerade Seitenwände im Graben zu behalten. Ein Abheben einer 8000 A-Aluminiumschicht ist jedoch technisch schwierig und wird am besten vermieden, falls überhaupt möglich.

**[0066]** Falls die zwei p-leitenden Schichten 1,5 Mikron oder mehr voneinander beabstandet sind, um die Verarbeitungsprobleme zu minimieren, wird alternativ die größere Entfernung dementsprechend die Schutzwirkung minimieren, für die die zusätzliche

p-leitende Schicht in der Struktur beinhaltet ist. Dementsprechend besteht ein Bedürfnis, die Geometrie der hier offenbarten Strukturen zuzuschneiden, um die Möglichkeit eines Abschnürens des Stroms zu minimieren und um technische Schwierigkeiten beim Maskieren und Ätzen von tiefen Gräben für den bloßen Zweck eines Errichtens einer minimalen Entfernung zwischen den p-leitenden Schichten zu vermeiden.

**[0067]** Dementsprechend sieht die vorliegende Erfindung bei der in [Fig. 20](#) veranschaulichten Ausführungsform eine Struktur mit isoliertem Gate vor, die die Möglichkeit einer Stromabschnürung minimiert, während gleichzeitig die ganzen Fähigkeiten von UMOS- und IGBT-Strukturen, insbesondere bei Siliziumkarbid, genutzt werden. Bei dieser Ausführungsform weist die Erfindung einen UMOS-Feldeffekttransistor auf, einschließlich eines Grabens und eines Grabenoxids an den Wänden und dem Boden des Grabens. Ein Schutzbereich befindet sich unter dem Bodenteil des Grabenoxids des Transistors, um das Grabenoxid gegen die Verschlechterungs- oder Durchschlagseffekte einer großen Spannung zu schützen, die über der Vorrichtung angelegt ist. Eine Stromvergrößerungsschicht bzw. Stromanreicherungsschicht befindet sich zwischen dem Schutzbereich und dem Kanal der Struktur mit isoliertem Gate, und die Stromvergrößerungsschicht ist vorzugsweise stärker dotiert als der Rest des n-leitenden Drain-Bereichs des Transistors.

**[0068]** [Fig. 20](#) veranschaulicht die vorliegende Erfindung in Form eines senkrechten Metalloxid-Halbleiter-p-Kanal-Vergrößerung-Feldeffekttransistors, der allgemein mit **50** bezeichnet ist. Die Struktur ist konstruiert, um insbesondere die Eigenschaften von Siliziumkarbid zu nutzen.

**[0069]** [Fig. 20](#) veranschaulicht, dass der UMOS **50** der Erfindung ein n-leitendes Siliziumkarbidsubstrat **51** mit einer n-leitenden Siliziumkarbid-Epitaxialschicht **52** auf dem n-leitenden Substrat umfasst. Wie [Fig. 20](#) mit den n<sup>+</sup>- und n<sup>-</sup>-Bezeichnungen veranschaulicht, ist bei bevorzugten Ausführungsformen das Substrat **51**, das den Drain-Kontakt trifft, stärker dotiert als die Epitaxialschicht **52**, um den Stromfluss zu der Drain zu steigern. Es versteht sich, dass unter einigen Umständen, ein einzelnes Substrat den Platz des Substrats **51** und der Epischicht **52** einnehmen kann. Die n<sup>+</sup>/n<sup>-</sup>-Struktur bietet jedoch gewisse Stromflussvorteile und wird somit allgemein bevorzugt.

**[0070]** Eine p-leitende Epitaxialschicht **53** bildet den Kanalbereich des UMOS **50**, und eine n-leitende Mulde **54** bildet die Source. [Fig. 20](#) veranschaulicht auch den Graben **55** und das Gate-Oxid **56**, das die Wände **57** und den Boden **60** des Grabens **55** bedeckt. Wie bei den vorherigen Ausführungsformen umfasst die Erfindung den geerdeten p-leitenden Bereich **61**

zwischen dem Oxid **56** und der n-leitenden Epitaxialschicht **52** und ist nach dem Boden **60** des Gate-Grabens **55** zum Schützen des Oxids **56** in dem Graben **55** gegen die Verschlechterungs- oder Durchschlagseffekte einer großen positiven Spannung ausgerichtet, die an die Drain angelegt ist.

**[0071]** Der UMOS dieser Ausführungsform weist jedoch des Weiteren die n-leitende Stromvergrößerungsschicht **62**, vorzugsweise eine n<sup>+</sup>-leitende Schicht zwischen dem geerdeten p-leitenden Bereich **61** und dem p-leitenden Kanalbereich **53** der UMOS-Struktur **50** auf. Die n-leitende Stromvergrößerungsschicht **62** ist stärker dotiert als der Rest der n-leitenden Epitaxialschicht **52**. [Fig. 20](#) veranschaulicht auch die Source-Kontakte **63**, den Gate-Kontakt **64** und den Drain-Kontakt **65**.

**[0072]** Durch Anordnen der n-leitenden Stromvergrößerungsschicht **62** unterhalb der p-leitenden Kanalschicht **53**, vermeidet die Struktur eine Stromabschnürung selbst bei viel geringeren Entfernungen (d) zwischen dem p-leitenden Kanalbereich **53** und dem geerdeten p-leitenden Bereich **61**. Die gleichen Berechnungen, die eine Abschürfung demonstrieren, die bei Entfernungen (d) von 1,5 Mikron oder geringer in einer Struktur wie z.B. in [Fig. 1](#) auftreten, zeigt bspw., dass eine Abschnürung unter Verwendung der Erfindung für Entfernungen (d) von kleiner als 0,18 Mikron vermieden werden kann. Dementsprechend kann, falls die Entfernung d etwas verringert werden kann, die Verarbeitung der Struktur dementsprechend einfacher gemacht werden, während gleichzeitig die Schutzwirkung der p-leitenden Schicht **61** gestärkt wird.

**[0073]** Zusätzlich hilft die Stromvergrößerungsschicht **62** auch, den Drain-Widerstand bei einer Durchlassspannung zu verringern. Bei Abwesenheit der zusätzlichen n-leitenden Schicht **62** erzeugt der von dem Boden der Grabenecke sich zu der Drain ausbreitende Strom einen großen Ausbreitungswiderstand um die Grabenecke. Durch Hinzufügen der n-leitenden Schicht **62** kann der Strom zuerst seitlich in die n-leitende Schicht fließen und dann hinab zur Drain fließen, womit der Ausbreitungswiderstand bei einer Durchlassspannung minimiert oder eliminiert wird.

**[0074]** Wieder wurde das MEDICI™-Simulationsprogramm verwendet, um das Verhalten der Struktur der vorliegenden Erfindung zu überprüfen. Die Simulation zeigte, dass bei einer Konzentration von ungefähr  $2 \times 10^{17} \text{ cm}^{-3}$  in der n-leitenden Stromvergrößerungsschicht **62** und bei einer Entfernung d von 0,18 Mikron zwischen den zwei p-leitenden Teilen **53** und **61** keine Abschnürung auftritt und sich ein Durchlassstrom um einen Faktor von ungefähr 10 erhöht. Es versteht sich, dass die Dotierungskonzentration und die Dicke der n-leitenden Schicht **62** vorsichtig ent-

worfen werden sollten, so dass die n-leitende Schicht **62** die Schutzwirkung der geerdeten p-leitenden Schicht **61** effektiv stärken kann, während gleichzeitig die maximale Benutzung des n-Bereichs **52** ermöglicht wird, um einen Sperrspannungsabfall zu blockieren.

**[0075]** Zusammengefasst gesagt, die Hinzufügung der n-leitenden Schicht **62** dient zumindest zwei Zwecken. Erstens verhindert sie eine Abschnürung selbst für ein sehr kleines  $d$ , wodurch wiederum die Schutzwirkung der geerdeten p-leitenden Schicht **61** bei Sperrspannung gestärkt wird. Zweitens verringert die n-leitende Schicht **62** den Ein-Widerstand bei Durchlassspannung. Wie zuvor bemerkt, scheint eine vorläufige zweidimensionale MEDICI™-Simulation diese beiden Vorteile zu verifizieren.

**[0076]** Von einem Verarbeitungsstandpunkt aus ist die Hinzufügung der n-leitenden Schicht **62** relativ einfach, da sie lediglich ein Wachsen einer weiteren Epitaxialschicht erfordert, während die identische Maskenkonstruktion und identische Vorgänge verwendet werden, die verwendet werden, um den in [Fig. 2](#) veranschaulichten UMOS herzustellen.

**[0077]** Als zusätzliches Detail weist bei einer bevorzugten Ausführungsform das n-leitende Substrat **51** üblicherweise eine Trägerkonzentration von ungefähr  $2 \times 10^{19} \text{ cm}^{-3}$  auf. Die n-leitende Epitaxialschicht **52** weist allgemein eine Trägerkonzentration von zwischen ungefähr  $2,5 \times 10^{15} \text{ cm}^{-3}$  und  $2 \times 10^{16} \text{ cm}^{-3}$  auf. Die n-leitende Stromvergrößerungs-Epitaxialschicht **62** weist vorzugsweise eine Trägerkonzentration von  $2 \times 10^{17} \text{ cm}^{-3}$  auf. Die p-leitende Epitaxialschicht **53** und der geerdete p-leitende Bereich **61** haben typischerweise Trägerkonzentrationen zwischen  $2 \times 10^{17} \text{ cm}^{-3}$  und  $5 \times 10^{17} \text{ cm}^{-3}$ . Wie unter Bezug auf die früheren Ausführungsformen erläutert, stellt, wenn der Halbleiter aus Siliziumkarbid ist, der geerdete p-leitende Bereich **61** üblicherweise einen implantierten Bereich dar, der mit Aluminium oder Bor dotiert ist. Zusätzlich ist bei den Siliziumkarbid-Ausführungsformen der bevorzugte n-leitende Dopant Stickstoff, und der bevorzugte Dopant für die p-leitende Epitaxialschicht **53** ist auch Aluminium. Wenn die Struktur aus Silizium gebildet wird, ist der bevorzugte p-leitende Dopant Bor, und die bevorzugten n-leitenden Dopanten sind Phosphor (III), Arsen und Antimon.

**[0078]** Bei den Siliziumkarbid-Ausführungsformen sind die ohmschen Kontakte **63** und **65** zu der n-leitenden Mulde **54** und dem n-leitenden Substrat **51** allgemein aus der Gruppe ausgewählt, die aus Nickel und Nickellegierungen besteht, während der p-leitende Bereich **61** durch einen ohmschen Kontakt (nicht gezeigt) geerdet ist, der aus der Gruppe ausgewählt ist, die aus Aluminium und Aluminiumlegierungen und Kobaltsilizid ( $\text{CoSi}_2$ ) besteht.

**[0079]** Bei einem anderen Aspekt kann die vorliegende Ausführungsform durch die Struktur des Grabens **55** beschrieben werden. Diese Struktur weist die Grabenwand **57** und den geerdeten p-leitenden Bereich **61** auf, der den Grabenboden **60** bildet. Die Grabenwand **57** und der Grabenboden **60** sind durch das Gate-Oxid **56** des UMOS **50** bedeckt. Die Grabenwand **57** unterhalb des Oxids **56** weist wiederum die n<sup>+</sup>-Mulde **54** für die Source, die p-leitende Epitaxialschicht **53** für den unterhalb der n<sup>+</sup>-leitenden Mulde **54** angeordneten Kanal, die n-leitende Stromvergrößerungsschicht **62** unterhalb der p-leitenden Epitaxialschicht **53** und den n-leitenden Drain-Bereich **52** (zusammen mit dem Substrat **51**) unterhalb der n-leitenden Stromvergrößerungsschicht **62** auf. Wie bei den anderen Ausführungsformen ist der n-leitende Drain-Bereich **52** weniger stark dotiert als die n-leitende Stromvergrößerungsschicht **62**.

**[0080]** Bei einer weiteren Ausführungsform weist die Erfindung einen bipolaren Transistor mit isoliertem Gate (IGBT) auf, der in Siliziumkarbid mit Siliziumdioxid als Gate-Isolator gebildet ist. Der Transistor weist eine Source eines ersten Leitfähigkeitsstyps, einen dem Gate-Oxid gegenüber liegenden Schutzbereich, der relativ zur Source einen entgegengesetzten Leitfähigkeitsstyp aufweist, um das Gate-Oxid gegenüber den Verschlechterungs- oder Durchschlags-Effekten einer großen über dem Transistor angelegten Spannung zu schützen, und eine Stromvergrößerungsschicht des ersten Leitfähigkeitsstyps auf, die zwischen dem Schutzbereich und dem Source-Bereich des Transistors angeordnet ist.

**[0081]** [Fig. 21](#) veranschaulicht eine besonders bevorzugte IGBT-Ausführungsform, die allgemein mit **70** bezeichnet ist. Der IGBT **70** weist ein p-leitendes Siliziumkarbid-Substrat **71**, eine n-leitende Siliziumkarbid-Epitaxialschicht **72** auf dem p-leitenden Substrat **71**, eine p-leitende Siliziumkarbid-Epitaxialschicht **73** auf der n-leitenden Epitaxialschicht **72**, eine n-leitende Mulde **74** in der p-leitenden Epitaxialschicht **73** und einen Gate-Graben auf, der allgemein mit **75** bezeichnet ist und sich durch die n-leitende Mulde **74**, die p-leitende Epitaxialschicht **73** erstreckt und in der n-leitenden Epitaxialschicht **72** endet. Ein Gate-Oxid **76** befindet sich an den Wänden und dem Boden des Grabens **75**, und ohmsche Kontakte **77**, **80** bzw. **81** sind zu dem Gate-Oxid **76**, zu der n-leitenden Mulde **74** und dem p-leitenden Substrat **71** zum Definieren des Gates, der Source bzw. des Emitters vorgesehen.

**[0082]** Ein p-leitender Siliziumkarbid-Schutzbereich **82** befindet sich zwischen dem Oxid **76** und der n-leitenden Epitaxialschicht **72** und ist nach dem Boden des Gate-Grabens **75** ausgerichtet, um das Oxid **76** in dem Graben **75** gegen die Verschlechterungs- oder Durchschlagseffekte einer großen positiven Spannung zu schützen, die über dem IGBT **70** ange-

legt ist. Eine n-leitende Stromvergrößerungsschicht **83** ist zwischen dem Schutzbereich **82** und der Source **74** angeordnet.

**[0083]** Wie bei früheren Beispielen ist der p-leitende Schutzbereich **82** mit einem ohmschen Kontakt geerdet, der aus der Gruppe ausgewählt ist, die aus Aluminium, Aluminiumlegierungen und Kobaltsilizid besteht, und der vorzugsweise durch Ionenimplantation gebildet ist. Die ohmschen Kontakte zu der n-leitenden Mulde **74** werden vorzugsweise aus der Gruppe bestehend aus Nickel und Nickellegierungen ausgewählt. Die n-leitende Mulde **74**, die n-leitende Epitaxialschicht **72** und die n-leitende Stromvergrößerungsschicht **83** werden alle vorzugsweise mit Stickstoff dotiert, und der bevorzugte Dopant für die p-leitende Epitaxialschicht **73** ist aus der Gruppe bestehend aus Aluminium und Bor ausgewählt. Wie bei den anderen Beispielen, weist das Siliziumkarbid vorzugsweise einen Polytype auf, der aus der Gruppe bestehend aus 4H und 6H ausgewählt ist.

### Patentansprüche

1. UMOS-Leistungstransistor, der eine erhöhte Maximalspannung zeigt und der ein Metalloxidhalbleiter-Feldeffekttransistor (**50**) vom Anreicherungstyp ist, der einen Graben und ein Grabenoxid (**56**) an den Wänden und dem Boden des Grabens, eine Source (**54**) und eine Drain (**52**) eines ersten Leitfähigkeitsstyps, einen Kanalbereich (**53**) des entgegengesetzten Leitfähigkeitsstyps, einen Bereich (**61**) unterhalb des Grabenoxids, der den zu der Source (**54**) und der Drain (**52**) entgegengesetzten Leitfähigkeitsstyp aufweist, um das Grabenoxid gegen Degradations- oder Durchschlageffekte einer großen Spannung zu schützen, die an die Drain angelegt ist, und der ausreichend von dem Kanalbereich (**53**) beabstandet ist, um jegliche Stromeinschnürungseffekte zwischen dem Bereich (**61**) und dem Kanalbereich zu minimieren, und eine Stromanreicherungsschicht (**62**) des ersten Leitfähigkeitsstyps aufweist, die stärker dotiert ist als der Drainbereich (**52**), wobei der Transistor in SiC gebildet ist, wobei der Bereich (**61**) elektrisch mit einem Erdungsanschluss verbunden ist, der an dem Transistor gebildet ist, und wobei sich die Stromanreicherungsschicht (**62**) seitlich unter dem Kanalbereich (**53**) und über dem Drainbereich (**52**) erstreckt.

2. Transistor nach Anspruch 1, wobei die Source (**54**) und die Drain (**52**) p-leitend und der Bereich (**61**) unterhalb des Grabenoxids (**56**) n-leitend ist.

3. Transistor nach Anspruch 1, der ein n-leitendes Siliziumkarbidsubstrat (**51**), eine p-leitende Siliziumkarbid-Epitaxialschicht (**53**) auf dem n-leitenden Substrat, eine n-leitende Mulde (**54**) in der p-leitenden Epitaxialschicht, wobei der Graben ein Gategraben ist, der sich durch die n-leitende Mulde und die p-leitende Epitaxialschicht erstreckt und in dem n-lei-

tenden Substrat endet, und wobei das Grabenoxid (**56**) ein Gateoxid (**17, 56**) an den Wänden und dem Boden des Grabens ist, und jeweilige ohmsche Kontakte (**64, 63, 65**) aufweist, und zwar zu dem Gateoxid zum Definieren eines Gates, zu der n-leitenden Mulde zum Definieren einer Source, und zu dem Substrat zum Definieren einer Drain, und wobei der Bereich (**61**) unterhalb des Grabens ein p-leitender Siliziumkarbidbereich zwischen dem Oxid (**56**) und dem n-leitenden Substrat (**51**) ist und nach dem Holden des Gategrabens ausgerichtet ist.

4. Transistor nach Anspruch 3, wobei das n-leitende Substrat (**51**) eine Trägerkonzentration von ungefähr  $2 \times 10^{16} \text{ cm}^{-3}$  aufweist, und wobei die p-leitende Epitaxialschicht eine Trägerkonzentration von ungefähr  $5 \times 10^{17} \text{ cm}^{-3}$  aufweist.

5. Transistor nach Anspruch 3 oder 4, der eine n-leitende Epitaxialschicht (**52**) umfasst, die in Berührung mit dem n-leitenden Substrat (**51**) steht und zwischen dem n-leitenden Substrat und der p-leitenden Epitaxialschicht (**53**) angeordnet ist.

6. Transistor nach Anspruch 5, wobei das n-leitende Substrat (**51**) stärker dotiert ist als die n-leitende Epitaxialschicht (**52**).

7. Transistor nach Anspruch 5, wobei das n-leitende Substrat (**51**) eine Trägerkonzentration von ungefähr  $2 \times 10^{19} \text{ cm}^{-3}$  aufweist und die n-leitende Epitaxialschicht (**52**) eine Trägerkonzentration von zwischen ungefähr  $2,5 \times 10^{15} \text{ cm}^{-3}$  und  $2 \times 10^{16} \text{ cm}^{-3}$  aufweist.

8. Transistor nach einem der vorhergehenden Ansprüche 5, 6 oder 7, wobei die n-leitende Epitaxialschicht (**52**) mit Stickstoff dotiert ist.

9. Transistor nach einem der vorhergehenden Ansprüche 5 bis 8, wobei die p-leitende Epitaxialschicht (**53**) eine Trägerkonzentration von ungefähr  $5 \times 10^{17} \text{ cm}^{-3}$  aufweist, und wobei der p-leitende Bereich (**61**) eine Trägerkonzentration von ungefähr  $5 \times 10^{17} \text{ cm}^{-3}$  aufweist.

10. Bipolarleistungstransistor (IGBT) mit isoliertem Gate, der eine erhöhte Maximalspannung zeigt und der einen Transistor darstellt, der ein p-leitendes Substrat (**71**), eine n-leitende Epitaxialschicht (**72**) auf dem p-leitenden Substrat (**71**), eine p-leitende Epitaxialschicht (**73**) über der n-leitenden Epitaxialschicht, eine n-leitende Mulde (**74**) in der p-leitenden Epitaxialschicht (**73**), einen Gategraben, der sich durch die n-leitende Mulde (**74**) und die p-leitende Epitaxialschicht (**73**) erstreckt und in der n-leitenden Epitaxialschicht endet, ein Gate-isolierendes Material (**76**) an den Wänden und dem Boden des Grabens, jeweilige ohmsche Kontakte (**50, 77, 81**) zu dem Gate-isolierenden Material zum Definieren eines

Gates, zu der n-leitenden Mulde zum Definieren einer Source, und zu dem Substrat zum Definieren eines Emitters, einen p-leitenden Bereich (82) zwischen dem isolierenden Material und der n-leitenden Epitaxialschicht (72), wobei der p-leitende Bereich nach dem Boden des Gategrabs ausgerichtet ist, um das isolierende Material in dem Graben gegen die Degradations- oder Durchschlagseffekte einer großen positiven Spannung zu schützen, die über dem Transistor angelegt ist, und der ausreichend von der p-leitenden Epitaxialschicht (73) beabstandet ist, um jegliche Stromeinschnürungseffekte zwischen dem p-leitenden Bereich und der p-leitenden Epitaxialschicht zu minimieren, und eine n-leitende Stromanreicherungsschicht (83) aufweist, die stärker dotiert ist als die n-leitende Epitaxialschicht (72), wobei der p-leitende Bereich (82), das Substrat (71), die Epitaxialschichten (72, 73) und die n-leitende Mulde (74) aus Siliziumkarbid sind, wobei der p-leitende Bereich (82) elektrisch mit einem Erdungsanschluss verbunden ist, der an dem Transistor gebildet ist, und wobei sich die Stromanreicherungsschicht (83) seitlich unter der p-leitenden Epitaxialschicht (73) und über der n-leitenden Epitaxialschicht (72) erstreckt, und wobei sich der Gategraben durch die Stromanreicherungsschicht erstreckt.

11. Transistor nach einem der vorhergehenden Ansprüche 3 bis 10, wobei die ohmschen Kontakte zu der n-leitenden Mulde (54, 74) und das n-leitende Substrat (51) aus der Gruppe ausgewählt sind, die aus Nickel und Nickellegierungen besteht.

12. Transistor nach einem der vorhergehenden Ansprüche 3 bis 11, wobei das Dotierungsmaterial für die p-leitende Epitaxialschicht (53, 73) aus der Gruppe ausgewählt ist, die aus Aluminium und Bor besteht.

13. Transistor nach einem der vorhergehenden Ansprüche 3 bis 12, wobei sowohl die n-leitende Mulde (54, 74) als auch das n-leitende Substrat mit Stickstoff dotiert sind.

14. Transistor nach einem der vorhergehenden Ansprüche, wobei der p-leitende Bereich (61, 82) durch einen ohmschen Kontakt geerdet ist, der aus der Gruppe ausgewählt ist, die aus Aluminium, Aluminiumlegierungen und einer Kobalt-Siliziumverbindung besteht.

15. Transistor nach einem der vorhergehenden Ansprüche, wobei das Dotierungsmaterial für den p-leitenden Bereich (61) ausgewählt aus der Gruppe ist, die aus Aluminium und Bor besteht.

16. Transistor nach einem der vorhergehenden Ansprüche, wobei der p-leitende Bereich (61, 82) ein implantierter Bereich ist.

17. Transistor nach einem der vorhergehenden Ansprüche, wobei das Siliziumkarbid einen Polype aufweist, der aus der Gruppe ausgewählt ist, die aus 4H und 6H besteht.

18. Transistor nach Anspruch 10, wobei die n-leitende Stromanreicherungsschicht (83) zwischen dem p-leitenden Bereich (82) und dem Sourcebereich (54) des Transistors angeordnet ist.

19. Transistor nach einem der vorhergehenden Ansprüche, wobei das Oxid oder das isolierende Material (56, 76) Siliziumdioxid aufweist.

Es folgen 19 Blatt Zeichnungen

## Anhängende Zeichnungen

(STAND DER TECHNIK)

Fig. 4.

—fig. 5.

Fig. 6.

FIG. 7.

—Fig. 8.

— 15.9.

Fig. 10.

—Fig. 11.

Fig. 12.

Fig. 13.

—Fig. 14.

Fig. 15.

—fig. 16.

FIG. 17.

Fig. 18.

Fig. 19.