**【特許請求の範囲】****【請求項 1】**

極性が交互に変化する入力信号エッジのシーケンスからパルスを生成する方法であって、

前記入力信号エッジの正の遷移を区別する第一のステップと、

前記第一のステップで区別された正の遷移を増幅するステップと、

前記入力信号エッジの負の遷移を区別する第三のステップと、

前記第三のステップで区別された負の遷移を増幅するステップと、

前記区別され増幅された第二のステップの遷移と、前記区別され増幅された第四のステップの遷移で、キャパシタンスを交互に充電するステップと、

前記キャパシタンスが第1の極性に帯電したときに、オンに切り替えられた第1のFETで負荷を正の電源電圧に駆動する第六のステップと、

前記キャパシタンスが第2の極性に帯電したときに、オンに切り替えられた第2のFETで前記負荷を負の電源電圧に駆動する第七のステップと、

前記第1のFETと前記第2のFETのうち1つはNタイプのFETであり、もう1つはPタイプのFETである第八のステップとを有する方法。

**【請求項 2】**

前記第1のFETと前記第2のFETは直列であり、前記FETの極性は、マイク・ビフォア・ブレイク動作を生成するように選択されることを特徴とする請求項1に記載の方法。

**【請求項 3】**

前記第1のFETと前記第2のFETは直列であり、前記FETの極性は、ブレイク・ビフォア・マイク動作を生成するように選択されることを特徴とする請求項1に記載の方法。

**【請求項 4】**

前記負荷は積分器の入力に結合された抵抗器であり、

前記第1のFETと前記第2のFETの切り替えが形成する電流パルスを積分するステップをさらに有することを特徴とする請求項1に記載の方法。

**【請求項 5】**

極性が交互に変わる入力信号エッジのシーケンスを受信するための入力を有するインパルスドライバであって、入力信号エッジを正の過渡インパルスと負の過渡インパルスとに区別し、前記正の過渡インパルスと前記負の過渡インパルスとを別々に増幅し、前記増幅を前記インパルスドライバの共通出力に提供するインパルスドライバと、

前記インパルスドライバの共通出力と、ACアースの間に結合されるキャパシタンスと、

互いに直列で相補的なFETスイッチの対であって、前記相補的な対は供給電圧に対しても並列であり、前記相補的なFETスイッチの対のゲートは各々、前記インパルスドライバの共通出力に接続される相補的なFETスイッチの対と、

出力パルスを供給するよう結合されたパルス出力である、前記直列で相補的なFETスイッチの対の接合部とを備えるパルス生成装置。

**【請求項 6】**

前記相補的なFETスイッチの対の順序が前記供給電圧と並列の時にマイク・ビフォア・ブレイク動作を生成することを特徴とする請求項5に記載の装置。

**【請求項 7】**

前記相補的なFETスイッチの対の順序が前記供給電圧と並列の時にブレイク・ビフォア・マイク動作を生成することを特徴とする請求項5に記載の装置。

**【請求項 8】**

入力を有する積分器をさらに備え、

前記パルス出力と前記積分器の入力との間に結合された積分器入力抵抗器をさらに備える請求項5に記載の装置。

10

20

30

40

50

**【請求項 9】**

前記出力パルスのピークピーク電圧は、前記極性が交互に変化する入力信号エッジのピークピーク電圧より大きいことを特徴とする請求項 5 に記載の装置。

**【請求項 10】**

極性が交互に変化する入力信号エッジのシーケンスからパルスを生成する方法であって

、

前記入力信号エッジの遷移を区別する第一のステップと、

前記第一のステップで区別された遷移を増幅する第二のステップと、

前記第二のステップで増幅された遷移に応答して、応答する増幅された遷移の極性によ

10

って極性が決定される電流を生成する第三のステップと、

前記第三のステップの電流をノードに結合する第四のステップと、

前記第四のステップのノードにおいて前記電圧を正の値と負の値にクランプする第五の

ステップと、

前記第四のステップのノードが第 1 の極性にクランプされると、負荷をオンに切り替え

られた第 1 の FET で正の電源電圧に駆動する第六のステップと、

前記第四のステップのノードが第 2 の極性にクランプされると、前記負荷をオンに切り

替えられた第 2 の FET で負の電源電圧に駆動する第七のステップと、

前記第 1 の FET と前記第 2 の FET のうち 1 つは N タイプの FET であり、もう 1 つ

は P タイプの FET である第八のステップとを有する方法。

**【請求項 11】**

前記第 1 の FET と前記第 2 の FET は直列であり、前記 FET の極性は、マイク・ビ

フォア・ブレイク動作を生成するように選択されることを特徴とする請求項 10 に記載の

方法。

**【請求項 12】**

前記第 1 の FET と前記第 2 の FET は直列であり、前記 FET の極性は、ブレイク・

ビフォア・マイク動作を生成するように選択されることを特徴とする請求項 10 に記載の

方法。

**【請求項 13】**

前記負荷は積分器の入力に結合された抵抗器であり、

前記第 1 の FET と前記第 2 の FET の切り替えが形成する電流パルスを積分するステ

ップをさらに有する請求項 10 に記載の方法。

**【請求項 14】**

前記負荷を駆動する電圧に応答して、前記負荷に結合され前記負荷を介する電流の大部分を供給する、対応する極性の選択された電流を生成するステップをさらに有する請求項 10 に記載の方法。

**【請求項 15】**

極性が交互に変わる入力信号エッジのシーケンスを受信するための入力を有するインパルスドライバであって、前記入力信号エッジを正の過渡インパルスと負の過渡インパルスに区別し、各過渡を別々に増幅し、前記増幅を前記インパルスドライバの共通出力に提供するインパルスドライバと、

入力を有し、前記入力における正の電圧と負の電圧を選択された量に制限する電圧クラ

ンプ回路と、

前記インパルスドライバの共通出力に結合された入力を有し、選択された量と極性の電流を前記電圧クランプ回路の入力に供給する電圧制御式電流源と、

互いに直列で相補的な FET スイッチの対であって、前記相補的な対は供給電圧と並列

であり、前記相補的な FET スイッチの対のゲートは各々、前記電圧クランプ回路の入力

に接続される相補的な FET スイッチの対と、

出力パルスを供給するよう結合されたパルス出力である、前記直列な FET スイッチ

の対の接合部と、

を備えるパルス生成装置。

10

20

30

40

50

**【請求項 16】**

前記相補的な F E T スイッチの対の順序が前記供給電圧と並列の時にマイク・ビフォア・ブレイク動作を生成することを特徴とする請求項 15 に記載の装置。

**【請求項 17】**

前記相補的な F E T スイッチの対の順序が前記供給電圧と並列の時にブレイク・ビフォア・マイク動作を生成することを特徴とする請求項 15 に記載の装置。

**【請求項 18】**

入力を有する積分器をさらに備え、

前記パルス出力と前記積分器の入力の間に結合された積分器入力抵抗器をさらに備える請求項 15 に記載の装置。 10

**【請求項 19】**

前記出力パルスのピークピーク電圧は、前記極性が交互に変化する入力信号エッジのピークピーク電圧より大きいことを特徴とする請求項 15 に記載の装置。

**【請求項 20】**

前記パルス出力に結合された負荷をさらに備え、

電圧制御式電流源であって、前記パルス出力に結合された入力を有し、選択された大きさと極性で前記負荷に結合される電流を生成し、前記負荷に対する電流の大部分を供給する電圧制御式電流源をさらに備える請求項 15 に記載の装置。

**【発明の詳細な説明】****【背景技術】****【0001】**

多くのタイプの電子回路では、精密に定義された幅を有するパルスの使用が一般的である。このようなパルスはデジタル論理で作成できる。このようなパルスを時間的な幅以外にも定義する必要がしばしば生じる。たとえば、パルスの振幅に対しても応答する積分器にパルスを供給するときなどである。このような状況の一般的な例は、精密な幅と電圧のパルスが積分器入力抵抗器を駆動する場合である。このような精密な電流パルスは精密な長さを有するだけでなく、精密な振幅も有しなければならない。これは、積分器に印加される電荷の合計量が（理想的な形状のパルスについて）パルスの長さと振幅との積であるためである。精密な電流パルスは D A C (デジタルアナログコンバータ)などの用途においてしばしば積分器と共に使用される。D A C は研究室の品質のデジタルマルチメータにある精密 A D C (アナログデジタルコンバータ)に使用することができる。 30

**【発明の開示】****【発明が解決しようとする課題】****【0002】**

現在の 2 つの傾向により、精密なパルスの電流源の設計が困難になった。第 1 の傾向は、より多くの回路を単一の I C (集積回路) 上に載せるという傾向である。これはいくつかの点では多くの利点を有するが、使用可能な半導体プロセスの混合を限定し、さらに、電力損失を最小に抑えることが重要になる。第 2 の傾向は第 1 の傾向に応答するもので、この業界が 5 V または 5 V 未満で動作する低電圧高速論理シリーズを開発したことである。高速で位置が精密なパルスエッジをこれらの低電圧論理シリーズで生成することは可能であるが、電流パルスに変換すると、電圧が低いため信号ノイズ比が低減され、望ましくない。設計者は非常にしばしばはるかに高い電圧を使用することを好むが、新しい論理シリーズと関連する低い電圧を使用して精度を低減させるか、または高い電圧を伴う古いプロセス（おそらく入手が難しい）を使用するかの選択を強いられる。第 3 のオプションは、最新の低電圧高速論理シリーズを使用してパルスエッジを生成し、ついでこのパルスエッジを切り替え機構に印加して、レベルを、安定した基準電圧から得られる適切に高い電圧にシフトさせることである。非常に高い精度が求められるシステムで後者の方法を使用すると多くの課題が生じ、この課題をどう処理するか自体が重大な問題になってしまう。 40

**【課題を解決するための手段】****【0003】**

精密な振幅と長さの電流パルスのための入力エッジの低電圧源を入力バッファに印加して、低インピーダンス源を提供する。この低インピーダンス源の出力は正のエッジ区別器 (edge differentiator) に A C 結合され、また負のエッジ区別器にも A C 結合される。各区別器は通常はオフである対応するスイッチを短時間の間オンに駆動する。このスイッチの対は相対する極性の第 1 の電源の間に直列に配置され、スイッチの対の接合部はインパルスドライバとしての機能を果たし、第 1 の電源の電圧より小さい、対称的で相対する基準電圧にクランプすることができる。クランプされたインパルスドライバは、結合抵抗器を介して負の第 1 の電源電圧の一定のパーセンテージを印加することによって正のインパルスドライバ電圧に応答する双安定スイッチドライバにも結合できる。双安定スイッチドライバは、結合抵抗器を介して正の第 1 の電源電圧の一定のパーセンテージを印加することによって負のインパルスドライバ電圧に応答する。双安定スイッチドライバは極性が交互に変わる入力エッジが入力バッファに印加されるたびに状態を変える。インパルスドライバはまた、相補的な M O S F E T スイッチの対のゲートにも結合する。この M O S F E T スイッチは相対する極性の精密な基準電圧の間に直列に配置され、共通接合部は電流決定抵抗に接続し、他の端はたとえば積分器などの使用回路に接続することができる。M O S F E T スイッチの出力は、これらの M O S F E T から引き出された負荷電流の量を低減しオン抵抗において温度変動から生じるエラーを低減する、補助の双安定出力ドライバが補助することができる。精密な基準電圧は対称的な相対する基準と同じであってもよい。

10

20

#### 【発明を実施するための最良の形態】

##### 【0 0 0 4】

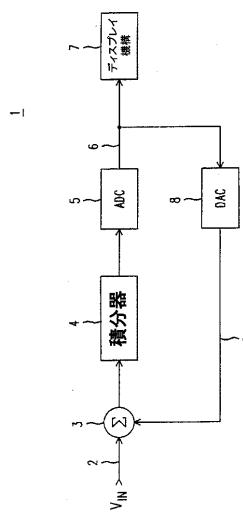

次に図 1 を参照すると、アーキテクチャとして知られる電圧測定技術の簡単な構成図 1 が示されている。本明細書の主題はアーキテクチャで使用できるので、まずこのアーキテクチャを簡単に説明する。アーキテクチャ自体は、中程度の性能から最高性能の範囲に渡る、デジタルマルチメータの中で使用できる（たとえばアジレント 3458A などのマルチメータ）。

##### 【0 0 0 5】

測定される電圧  $V_{IN}$  2 を加算接合部 3 の + 入力に印加する。加算接合部 3 の出力は積分器 4 に結合する。測定が終了するまでの経過で、平均の値が -  $V_{IN}$  に等しいフィードバックバランス電圧 (9) が生成される。この電圧は加算接合部 3 のほかの入力に印加され、この状態が適切な期間の間続いた場合、加算接合部の出力がゼロになり、積分器の出力は変化を効果的に終了する。積分器の出力は A D C に印加され、 $V_{IN}$  のデジタル表現である（ここでもバランスに達したと仮定する）。デジタル表現は出力ディスプレイ機構に供給され（または他の所定の使用に供給される）、また D A C にも供給される。D A C はフィードバックバランス電圧 9 を発行する。これはアーキテクチャの非常に簡単な概略であり、入力増幅器や減衰器など、実際のフルスケールの実装に重要な多くの点を無視している。しかし、ここではこの説明で充分である。

30

##### 【0 0 0 6】

図 1 における発明者らの関心事は、D A C 8 の中で起こる事象である。D A C 8 は、おそらくたとえば 4 枠から 8 枠の 10 進数字を表す多くのビットのデジタル値の集合を受信する。次にたとえば - 7 V . . . + 7 V などの所定の範囲内のアナログ電圧に戻す必要がある。しばしば行われるように、A D C 6 からのバイナリ表現を使用して、おそらく 3 ボルトから 5 ボルトの低電圧エッジによって精密に幅が定義されるパルスを作成したと仮定する。これらのパルス幅変調入力信号は小さすぎ、加算接合部に供給された入力をキャンセルする 7 ボルトまでの平均値を生成することができない。より小さな振幅パルス幅変調信号（たとえば 3 から 5 V）を直接使用する場合、 $V_{IN}$  の振幅をスケールダウンしなければならず、動作の間の信号ノイズ比を上昇させる。したがって、次に進むために、低電圧パルス幅変調信号を垂直に（電圧において）「伸ばす」必要がある。この方法が図 2 と図 3 に示されている。

40

##### 【0 0 0 7】

50

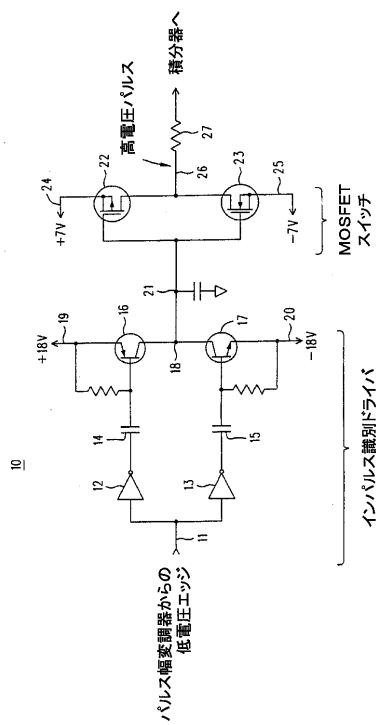

次に図2を参照すると、低電圧パルス幅変調信号11のエッジから精密なパルスを生成するための基本回路の簡単な概略図10が示されている。低電圧エッジ11は2つの部分を有するインパルス区別ドライバ回路(differentiating impulse driver)に印加される。この2つの部分の各々は、低電圧エッジ11の極性の各遷移のためである。バッファ12、キャパシタ14、トランジスタ16は負の遷移に応答し、バッファ13、キャパシタ15、トランジスタ17は正の遷移に応答する。遷移と遷移の間は、トランジスタ16と17は通常はオフである。低電圧エッジにおける正の遷移を考える。どちらのキャパシタもこれを区別するが、非常に短時間だけオンになることによってトランジスタ17だけが遷移に応答し、負の電源20から導出された負のインパルスを生成する。時定数は、オン時間が、パルス幅期間の最大値または合計値の2%から5%の範囲になるように選択する。同様に負の遷移はトランジスタ16を短時間だけオンし、正の電源19から導出される正のインパルスを生成する。

10

## 【0008】

トランジスタ16と17について示された構成の利点は、これらがほとんどオフであることである。これは、消費電力が低減され、熱による挙動の変化が低減されるため望ましい。さらに、これらのオン時間は時定数だけの関数であり、パルス幅の関数ではないことを理解されたい。オン時間が入力パルス幅の関数である場合、望ましくない非線形動作につながる可能性がある。

## 【0009】

トランジスタ17がオンになると、短い負のスパイクまたは電圧インパルスがノード18に現われ、キャパシタ21に印加され電荷を与える。この負の電圧によりMOSFETスイッチ22がオンになり、MOSFETスイッチ23がオフになる。このようにして、低電圧エッジ11の正の遷移により、正の電源電圧24が、抵抗器27に印加される出力線26上の出力パルスの源となる(これにより積分器の電流パルスとなる。積分器は図示しない)。出力26における正の電圧は、低電圧エッジ11における次の負の遷移によりトランジスタ16から正のインパルスが生成され、これによってキャパシタ21が以前の負の値から放電されて新しい正の値に帯電するまで残る。これによってMOSFETスイッチ23はオンになり、MOSFETスイッチ22はオフになる。この結果、パルス出力線26は電源電圧25の値にプルされる。キャパシタ21は別の部分であってもよく、または、MOSFET22と23のゲートキャパシタンスであってもよく、またはこれらの組み合わせであってもよい。

20

30

## 【0010】

極性が交互に変わる低電圧エッジ11の安定したシーケンスが印加されるとき、2つのMOSFETスイッチ22と23は本当の3状態では動作しないことに注意されたい。遷移の間に起こりうることを除いては、1つは常にオンでありもう1つは常にオフである。しかしこの観察は、インパルス区別ドライバが駆動するMOSFETスイッチが、メイク・ビフォア・ブレイク(make-before-break)で動作するか、ブレイク・ビフォア・メイク(break-before-make)で動作するかという問題には対処しない。どちらも得ることができるが、図示されているのはメイク・ビフォア・ブレイクで動作している。ブレイク・ビフォア・メイクを得るためにには、2つのMOSFETスイッチを入れ替えるだけでよい(これらは相対する極性のチャネルを有するので相補的な対であることに注意されたい)。メイク・ビフォア・ブレイク構成の利点は、MOSFET22と23に対してより低いオンレジスタンスを提供するということである。

40

## 【0011】

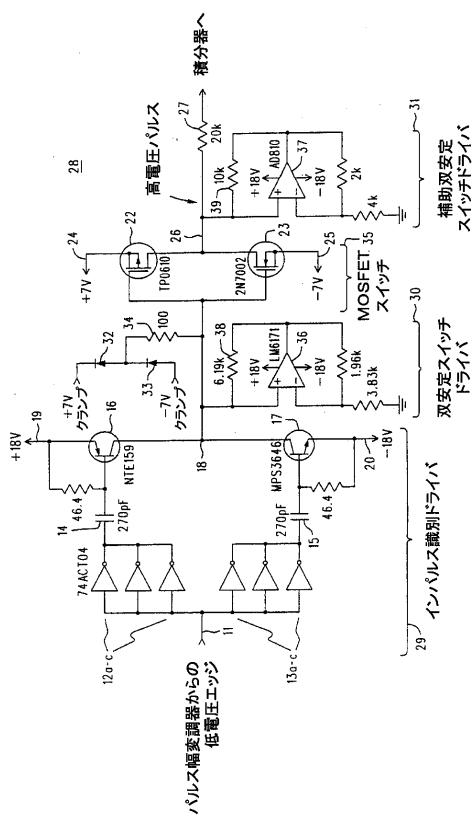

次に図3を参照する。図3は図2に示した基本技術の、より洗練された応用の、より詳細な概念図28である。部品がよく対応する場所では同じ参照番号を使用し、その他の場所では新しい参照番号を追加した。回路28の基本動作は同じであるので、追加のコンポーネントが提供する追加の機能のみを論じる。

## 【0012】

インパルス区別ドライバ29の入力バッファは、いくつかの部分を並列に動作させるこ

50

とにより(12aから12cと13aから13c)非常にロバストになっていることに注意されたい。これは、速度が適切に高速であることと、駆動されるインピーダンスが適切に低いことに調和するものである。たとえば、一実施形態ではパルス幅の範囲は300nsから1700nsであり、小さなナノ秒の上昇時間と500KHzの反復レートを伴う。

#### 【0013】

次に注目すべき点は双安定スイッチドライバ30が追加されたことである。まずこれはアースと、インパルスドライバ29の2つのトランジスタ16と17の接合ノード18の間に接続されている。キャパシタ21はなくなるが、不可避的なストレイ(stray)とデバイスキャパシタンス(トランジスタ22と23について)は残っている。実際、キャパシタンスをここで電圧貯蔵機構として作用させるより、ノード18からアースへのキャパシタンスができるだけ小さくするほうが好ましい。しかし、インパルスドライバ29からの過渡インパルスによってMOSFETスイッチ22と23から安定したパルス出力を得るために、「ストア&ホールド(store-and-hold)」機能を行うためになにかが必要である。このなにかが双安定スイッチドライバ30である。これは増幅器36周囲に構築された能動ネットワークである。さらに、ノード18における電圧スイングは抵抗器34(ダイオード保存電流制限)を介してダイオード32により+7Vクランプ電圧にクランプされ、ダイオード33によって-7Vクランプ電圧にクランプされている。

#### 【0014】

双安定スイッチドライバ30は、+7Vクランプ電圧より高い正の電圧または-7Vクランプ電圧より小さい負の電圧でノード18を駆動している。双安定スイッチドライバは、インパルスドライバ29からの対応する極性のインパルスによって1つの状態または他の状態からトリガされるかまたは切り替えられる。ついで抵抗器38を介してノード18を駆動し(すなわちクランプダイオード32と33のうち1つ)、ついで、低電圧エッジ11に次の遷移が起きるまでMOSFETスイッチ35の安定した駆動を維持する。

#### 【0015】

双安定スイッチドライバ30は電圧駆動式電流源と見ることもできる。ドライバ30はインパルスドライバが提供する短いが強力な過渡電圧に「従い」、一度摂動すると、関連するクランプ電圧よりも高い電源電圧を有する。しかしクランプ作用の方が強いので、次に、クランプ電圧が過渡インパルス駆動にとって代わる。しかし、電圧応答性の電流源挙動は残り、今度はこれ自体の出力のクランプに応答するようになる。作用はラッチに似ている。

#### 【0016】

ここで100 抵抗器34の理由が明らかになる。100 は、インパルスドライバからの大きな過渡電圧がダイオード32と33を壊したり関連する電流源を故障させたりするのを防ぐ程度に充分に大きく、しかもクランプ作用と干渉しない程度に充分に小さい。

#### 【0017】

クランプ作用は次のような理由でエラーの低減のために重要である。MOSFETスイッチ35への駆動がクランプされない場合、遷移と遷移の間に低下または他の不定な挙動を示す可能性が非常に高くなる。低下の量はその低下が放置される期間の関数、すなわち、パルス長さの関数である。遷移は所定の低下(または他のドリフト)が起きた後に起き、MOSFETを切り替える閾値に達するまでに必要な電圧の偏位は低下の量にしたがって場合ごとに異なるため、好ましくない。スルーレートは有限なので、出力パルスについてエッジの配置に対して、パルス幅に依存したタイミングエラーになる。クランプにより、閾値に対するスルーレート/または偏位の効果がすべてのパルスについて一定にすることができ、本質的に効果を相殺するため、問題が解決する。

#### 【0018】

図3に追加された別の要素は、補助的な双安定出力ドライバ31である。これはもう1つの双方向電圧駆動式電流源であり、増幅器37の周囲に構築され、抵抗器39を介してノード(この場合ライン26)に結合する。すなわち、MOSFET22がオンの時、本

質的にMOSFET 22と並列な追加の源である補助的な双方向出力ドライバ31が正の電圧（およびその電流）を供給する。代わりにMOSFET 23がオンの時、同様な負の電圧（およびその電流）が供給される。MOSFETスイッチのうち1つがオンの時（既知の±7Vを生成する）、関連する出力電圧は、抵抗器27を介して特定の電流を供給するかまたはシンクする（抵抗器27の他端は積分器が提供するバーチャルアースである）。IT供給がほとんどその電流になり、MOSFETスイッチ自体から供給される分はほとんどないように、補助的な双安定出力ドライバ31のコンポーネント値を選択する。補助的な双方向安定出力ドライバ31を有する理由は次の通りである。

## 【0019】

MOSFET 22と23は各々、約10のオン抵抗を有する。この値が一定であれば悪くはないが、残念なことにこの値は温度の関数として変化し、検出可能な性能の違いを生成してしまう。補助的な双安定出力ドライバ31から追加の駆動を提供することにより（積分器負荷抵抗器27を流れるほとんどの電流は実際、補助的な双方向出力ドライバの作用、すなわちソースとシンクによるものである）、これらの温度による変動を抑制できる。すなわち、ほとんど電流が流れなくなるため、温度可変オン抵抗全体の電圧低下は非常に小さくなる。

## 【0020】

図3に示す回路28は精密な動作ができる。入力エッジに対する出力パルスのエッジの配置にエラーがあっても、適切に注意すれば、2/10 ppmのオーダにできる。集積出力にこの種類の精度を持たせようすると、種々の基準電圧と供給電圧に適切な注意を払い、また全般にコンポーネントの選択にも適切に注意しなければならない。多くの受動コンポーネント値と能動素子の選択の組み合わせがあるが、本開示全体の観点から、図3には、2/10 ppm性能仕様に適合する実施形態の実際のコンポーネント値とデバイスの指定子を含めた。

## 【0021】

最後に、一部の用途では図示されたパルス生成回路がたとえばアースと36ボルトの供給の間でアンバランスな構成で動作するほうが望ましい場合があることを指摘したい。これは種々の他の電圧に適切にシフトさせることで容易に達成できる。また、これを試してみれば、はるかに高い電圧のパルスを生成できることが明らかであろう。

## 【0022】

本発明を本発明に従う特定の実施形態にて説明してきたが、本発明はこの種の本発明に従う実施形態により限定されるものとして解釈してはならず、特許請求の範囲に従って解釈しなければならない。念のため、以下に、本発明の実施態様を例示列挙する。

## 【0023】

## (実施形態1)

- 極性が交互に変化する入力信号エッジのシーケンスからパルスを生成する方法であって、

- (a) 前記入力信号エッジの正の遷移を区別するステップ(15)と、

- (b) 前記ステップ(a)で区別された正の遷移を増幅するステップ(17)と、

- (c) 前記入力信号エッジの負の遷移を区別するステップ(14)と、

- (d) 前記ステップ(c)で区別された負の遷移を増幅するステップ(16)と、

- (e) 前記区別され増幅されたステップ(b)の遷移と、前記区別され増幅されたステップ(d)の遷移で、キャパシタンス(21)を交互に充電するステップと、

- (f) 前記キャパシタンスが第1の極性に帯電したときに、オンに切り替えられた第1のFET(22)で負荷(27)を正の電源電圧(24)に駆動するステップと、

- (g) 前記キャパシタンスが第2の極性に帯電したときに、オンに切り替えられた第2のFET(23)で前記負荷(27)を負の電源電圧(25)に駆動するステップと、

- (h) 前記第1のFETと前記第2のFETのうち1つはNタイプのFETであり、もう1つはPタイプのFETであるステップとを有する方法。

## 【0024】

10

20

30

40

50

## (実施形態 2 )

前記第 1 の F E T と前記第 2 の F E T は直列であり、前記 F E T の極性は、マイク・ビフォア・ブレイク動作を生成するように選択されることを特徴とする実施形態 1 に記載の方法。

## 【 0 0 2 5 】

## (実施形態 3 )

前記第 1 の F E T と前記第 2 の F E T は直列であり、前記 F E T の極性は、ブレイク・ビフォア・マイク動作を生成するように選択されることを特徴とする実施形態 1 に記載の方法。

## 【 0 0 2 6 】

## (実施形態 4 )

前記負荷は積分器の入力に結合された抵抗器 ( 2 7 ) であり、

前記第 1 の F E T と前記第 2 の F E T の切り替えが形成する電流パルスを積分するステップをさらに有することを特徴とする実施形態 1 に記載の方法。

## 【 0 0 2 7 】

## (実施形態 5 )

極性が交互に変わる入力信号エッジのシーケンスを受信するための入力 ( 1 1 ) を有するインパルスドライバ ( 2 9 ) であって、入力信号エッジを正の過渡インパルス ( 1 5 ) と負の過渡インパルス ( 1 4 ) とに区別し、前記正の過渡インパルスと前記負の過渡インパルスとを別々に増幅し ( 1 7 、 1 6 ) 、前記増幅を前記インパルスドライバの共通出力 ( 1 8 ) に提供するインパルスドライバ ( 2 9 ) と、

前記インパルスドライバの共通出力と、 A C アースの間に結合されるキャパシタンス ( 2 1 ) と、

互いに直列で相補的な F E T スイッチの対 ( 3 5 ) であって、前記相補的な対は供給電圧に対して並列であり、前記相補的な F E T スイッチの対のゲートは各々、前記インパルスドライバの共通出力に接続される相補的な F E T スイッチの対 ( 3 5 ) と、

出力パルスを供給するよう結合されたパルス出力である、前記直列で相補的な F E T スイッチの対の接合部 ( 2 6 ) とを備えるパルス生成装置。

## 【 0 0 2 8 】

## (実施形態 6 )

前記相補的な F E T スイッチの対の順序が前記供給電圧と並列の時にマイク・ビフォア・ブレイク動作を生成することを特徴とする実施形態 5 に記載の装置。

## 【 0 0 2 9 】

## (実施形態 7 )

前記相補的な F E T スイッチの対の順序が前記供給電圧と並列の時にブレイク・ビフォア・マイク動作を生成することを特徴とする実施形態 5 に記載の装置。

## 【 0 0 3 0 】

## (実施形態 8 )

入力を有する積分器をさらに備え、

前記パルス出力と前記積分器の入力との間に結合された積分器入力抵抗器 ( 2 7 ) をさらに備える実施形態 5 に記載の装置。

## 【 0 0 3 1 】

## (実施形態 9 )

前記出力パルスのピークピーク電圧は、前記極性が交互に変化する入力信号エッジのピークピーク電圧より大きいことを特徴とする実施形態 5 に記載の装置。

## 【 0 0 3 2 】

## (実施形態 1 0 )

極性が交互に変化する入力信号エッジのシーケンスからパルスを生成する方法であって、

( a ) 前記入力信号エッジ ( 1 1 ) の遷移を区別するステップ ( 1 4 、 1 5 ) と、

10

20

30

40

50

( b ) 前記ステップ( a )で区別された遷移を増幅するステップ( 16、17 )と、

( c ) 前記ステップ( b )で増幅された遷移に応答して、応答する増幅された遷移の極性によって極性が決定される電流を生成するステップと、

( d ) 前記ステップ( c )の電流をノード( 18 )に結合するステップと、

( e ) 前記ステップ( d )のノードにおいて前記電圧を正の値と負の値にクランプするステップ( 32、33 )と、

( f ) 前記ステップ( d )のノードが第1の極性にクランプされると、負荷( 27 )をオンに切り替えられた第1のFET( 22 )で正の電源電圧に駆動するステップと、

( g ) 前記ステップ( d )のノードが第2の極性にクランプされると、前記負荷をオンに切り替えられた第2のFET( 23 )で負の電源電圧に駆動するステップと、

( h ) 前記第1のFETと前記第2のFETのうち1つはNタイプのFETであり、もう1つはPタイプのFETであるステップとを有する方法。

#### 【 0033 】

( 実施形態 11 )

前記第1のFETと前記第2のFETは直列であり、前記FETの極性は、マイク・ビフォア・ブレイク動作を生成するように選択されることを特徴とする実施形態10に記載の方法。

#### 【 0034 】

( 実施形態 12 )

前記第1のFETと前記第2のFETは直列であり、前記FETの極性は、ブレイク・ビフォア・マイク動作を生成するように選択されることを特徴とする実施形態10に記載の方法。

#### 【 0035 】

( 実施形態 13 )

前記負荷は積分器の入力に結合された抵抗器( 27 )であり、

前記第1のFETと前記第2のFETの切り替えが形成する電流パルスを積分するステップをさらに有する実施形態10に記載の方法。

#### 【 0036 】

( 実施形態 14 )

前記負荷を駆動する電圧に応答して、前記負荷に結合され前記負荷を介する電流の大部分を供給する、対応する極性の選択された電流を生成するステップ( 31 )をさらに有する実施形態10に記載の方法。

#### 【 0037 】

( 実施形態 15 )

極性が交互に変わる入力信号エッジのシーケンスを受信するための入力( 11 )を有するインパルスドライバ( 29 )であって、前記入力信号エッジを正の過渡インパルスと負の過渡インパルスに区別し( 14、15 )、各過渡を別々に増幅し( 16、17 )、前記増幅を前記インパルスドライバの共通出力( 18 )に提供するインパルスドライバ( 29 )と、

入力を有し、前記入力における正の電圧と負の電圧を選択された量に制限する電圧クランプ回路( 32、33、34 )と、

前記インパルスドライバの共通出力に結合された入力を有し、選択された量と極性の電流を前記電圧クランプ回路の入力に供給する電圧制御式電流源( 30 )と、

互いに直列で相補的なFETスイッチの対( 35 )であって、前記相補的な対は供給電圧と並列であり、前記相補的なFETスイッチの対のゲートは各々、前記電圧クランプ回路の入力に接続される相補的なFETスイッチの対( 35 )と、

出力パルスを供給するように結合されたパルス出力である、前記直列なFETスイッチの対の接合部( 26 )と、

を備えるパルス生成装置。

#### 【 0038 】

10

20

30

40

50

## (実施形態 16)

前記相補的な F E T スイッチの対の順序が前記供給電圧と並列の時にマイク・ビフォア・ブレイク動作を生成することを特徴とする実施形態 15 に記載の装置。

## 【0039】

## (実施形態 17)

前記相補的な F E T スイッチの対の順序が前記供給電圧と並列の時にブレイク・ビフォア・マイク動作を生成することを特徴とする実施形態 15 に記載の装置。

## 【0040】

## (実施形態 18)

入力を有する積分器をさらに備え、

前記パルス出力と前記積分器の入力の間に結合された積分器入力抵抗器(27)をさらに備える実施形態 15 に記載の装置。

## 【0041】

## (実施形態 19)

前記出力パルスのピークピーク電圧は、前記極性が交互に変化する入力信号エッジのピークピーク電圧より大きいことを特徴とする実施形態 15 に記載の装置。

## 【0042】

## (実施形態 20)

前記パルス出力に結合された負荷をさらに備え、

電圧制御式電流源(31)であって、前記パルス出力に結合された入力を有し、選択された大きさと極性で前記負荷に結合される電流を生成し、前記負荷に対する電流の大部分を供給する電圧制御式電流源(31)をさらに備える実施形態 15 に記載の装置。

## 【図面の簡単な説明】

## 【0043】

【図 1】本発明を行う機会を提供する電圧測定アーキテクチャの簡単な構成図である。

【図 2】電流パルスがパルス幅変調信号の低電圧エッジから生成される、図 1 の D A C 機構の一部の簡単な概略図である。

【図 3】図 1 の D A C 機構の一部を概略で示し、さらに精度と線形性を改善した部分的な概略図である。

## 【符号の説明】

## 【0044】

1 アナログディジタル測定アーキテクチャ

2 電圧

3 加算接合部

4 積分器

6 アナログディジタルコンバータ

8 ディジタルアナログコンバータ

9 フィードバックバランス電圧

11 低電圧エッジ

12、13 バッファ

14、15、21 キャパシタ

16、17 トランジスタ

18 ノード

19 正の電源

20 負の電源

22、23、35 M O S F E T スイッチ

24 正の電源電圧

25 電源電圧

26 出力線

27、34、38、39 抵抗器

10

20

30

40

50

## 2 8 回路

2 9 インパルス区別ドライバ

3 0 双安定スイッチドライバ

3 1 補助的な双安定出力ドライバ

3 2 、 3 3 ダイオード

3 6 、 3 7 増幅器

【図 1】

基本的な $\Delta\Sigma$ アナログ-デジタル変換アーキテクチャ

【図 2】

【図3】

---

フロントページの続き

(72)発明者 ステファン・ビー・ベンズク

アメリカ合衆国コロラド州 ラブランド ウィンブルトン・ドライブ 2043

F ターム(参考) 5J055 AX07 BX16 CX29 DX22 DX56 DX72 DX83 EX02 EX06 EY01

EY10 EY12 EY17 EY21 EZ01 EZ02 EZ07 EZ16 EZ24 EZ37

FX05 FX12 FX18 FX37 GX01 GX02

5J056 AA11 BB16 CC07 CC08 CC10 CC12 CC21 DD02 DD13 DD36

DD40 DD51 DD55 EE05 EE06 EE08 FF08 GG09

5J064 AA01 BA03 BC03 BC06 BC07 BC08 BC10 BD01

【要約の続き】