(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 101 42 400 B4 2009.09.03**

(12)

## Patentschrift

(21) Aktenzeichen: **101 42 400.0**

(22) Anmelddetag: **30.08.2001**

(43) Offenlegungstag: **27.03.2003**

(45) Veröffentlichungstag

der Patenterteilung: **03.09.2009**

(51) Int Cl.<sup>8</sup>: **H01L 21/304 (2006.01)**

**B24B 37/04 (2006.01)**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(73) Patentinhaber:

**Siltronic AG, 81737 München, DE**

(74) Vertreter:

**Rimböck, K., Dr., 81737 München**

(72) Erfinder:

**Pietsch, Georg J. Dipl.-Phys., 84489 Burghausen, DE; Kerstan, Michael, 84489 Burghausen, DE; Huber, Anton, Dipl.-Ing., 84489 Burghausen, DE**

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

|    |            |    |

|----|------------|----|

| DE | 198 33 257 | C1 |

| DE | 198 23 904 | A1 |

| DE | 196 26 396 | A1 |

| US | 60 66 565  | A  |

| EP | 10 49 145  | A1 |

| EP | 08 13 931  | A1 |

| EP | 07 55 751  | A1 |

| US | 67 26 525  | B1 |

| WO | 01/21 356  | A1 |

(54) Bezeichnung: **Halbleiterscheibe mit verbesselter lokaler Ebenheit und Verfahren zu deren Herstellung**

(57) Hauptanspruch: Verfahren zur Herstellung von Halbleiterscheiben, das folgende Teilschritte enthält:

a) Auftrennen eines Halbleiterstabs in eine Vielzahl von Halbleiterscheiben,

b) Verrunden der Kanten der Halbleiterscheiben

c) simultanes Schleifen beider Seiten der Halbleiterscheiben, das als „double-disk grinding“ ausgeführt wird, unter Verwendung keramisch gebundener Schleifräder mit einer Schleifmittelkörnung gemäß JIS/US mesh #2000 oder feiner und

d) Politur der Halbleiterscheiben,

wobei Schritt c) der einzige spanende mechanische Bearbeitungsschritt ist, mit dem die Flächen der Halbleiterscheiben bearbeitet werden.

(A)

## Beschreibung

**[0001]** Gegenstand der Erfindung ist eine Halbleiterscheibe mit verbesserter lokaler Ebenheit (Nanotopologie) sowie ein Verfahren zur Herstellung einer solchen Halbleiterscheibe.

**[0002]** Die Elektronik, Mikroelektronik und Mikro-Elektromechanik beruht ganz wesentlich auf der mechanischen und chemischen Formgebung, Bearbeitung und Strukturierung des Werkstoffs Silicium sowie einiger anderer Halbleitermaterialien wie Germanium oder Galliumarsenid in immer feinerem, aufwendigerem und reproduzierbarerem Maße. Technologietreiber ist insbesondere die Silicium-Mikroelektronik, die bei immer höheren Bauteil-Integrationsdichten inzwischen nach auf nahezu atomarer Skala chemisch und strukturell wohl-definierten Strukturen verlangt. Besonders anspruchsvolle Bauteile, etwa Mikroprozessoren, bestehen typischerweise aus mehrlagig strukturierten Bauteilebenen, die miteinander verdrahtet und durch isolierende Zwischenlagen voneinander getrennt sind. Als zentraler Schritt bei der Herstellung derartiger Mehrlagen-Bauteile kommt inzwischen nahezu ausschließlich ein chemo-mechanisches Polierverfahren (CMP) zum Einsatz, das die Zwischenlagen planarisiert. Eine hohe Ebenheit dieser Zwischenlagen ist Voraussetzung für die meist photolithographische Strukturierung der nächsten Bauteilebene. Die Lithographie hat aufgrund der erforderlichen lateralen Strukturauflösung von zur Zeit 0,18 µm oder 0,13 µm und Belichtungs-wellenlängen von unter 200 nm eine außerordentlich geringe Belichtungs-Schärfentiefe und funktioniert daher nur auf außerordentlich ebenen Belichtungsflächen. Damit das CMP-Verfahren die Isolierschicht nicht durchbricht und die darunter liegenden Bauteile angreift oder geschaffene Strukturen räumlich ungleichmäßig ausdünnnt, muss bereits die Startfläche, also die Oberfläche der Silicium-Substratunterlage, von möglichst perfekter Ebenheit sein.

**[0003]** Bis vor wenigen Jahren waren die erforderlichen Ebenheiten für die Substratscheiben, „Wafer“ genannt, nur global für die gesamte Scheibe oder für die von einzelnen Bauelementen beanspruchte Fläche definiert und spezifiziert. Zum Beispiel gibt die Kenngröße TTV („total thickness variation“) die Abweichung der Scheibendicke über die gesamte Scheibenfläche an. Auf die Ausdehnung einzelner Bauelementgruppen („sites“; Belichtungsplätze; z. B. ein Mikroprozessor mit einer Fläche von beispielsweise 25 mm × 25 mm) bezieht sich dagegen die Kenngröße SFQR („site focal-plane least-square deviation range (peak to valley)“). Neben diesen langreichweitigen Kenngrößen gab und gibt es Vorgaben für die kurzreichweite (atomare) Rauigkeit auf der Längenskala der einzelnen Bauelemente, da sich die Restrauhigkeit der Startfläche direkt auf die Funktion der einzelnen Bauteile auswirkt, die auf dieser Star-

toberfläche und aus ihr heraus strukturiert werden. Mit dem Einzug des CMP-Verfahrens zum Planarisieren der Bauteilzwischenlagen in Mehrschicht-Bauelementen auf breiter Front ist zusätzlich zu diesen traditionellen besonders kurz- und langreichweitigen Bereichen der Festlegung die Spezifikation maximaler Restunebenheiten im Millimeter-Bereich und etwas darüber hinzugekommen. Strukturen in diesem Ausdehnungsbereich bezeichnet man als Nanotopologie.

**[0004]** Genauer wird der Begriff „Nanotopologie“ oder „Nanotopographie“ von SEMI (Semiconductor Equipment and Materials International) sinngemäß definiert als Planaritätsabweichung der gesamten Scheibenvorderseite im Bereich räumlicher Wellenlängen von etwa 0,2 bis 20 mm (laterale Korrelationslänge) und innerhalb der „Qualitätszone“ (FQA, „fixed quality area“; Oberflächenbereich, für den die in der Produktspezifikation geforderten Wafer-Eigenschaften erfüllt sein müssen). Insbesondere unterscheiden sich der Nanotopologie zuzuordnende Merkmale eines Wafers also von anderen Merkmalen mit Höhenvariationen vergleichbarer Größenordnung durch ihre charakteristische laterale Ausdehnung. (Korrelationslängen bzw. Ortsfrequenzen). Beispielsweise führen bereits Nanotopologiemerkmale von nur 20 nm Höhe (peak to valley) zu einer Änderung der Dicken von auf die Halbleiterscheiben aufgebrachten Filmstrukturen, die die Bauteilfunktion nachhaltig beeinflusst und die bei der Herstellung als ungleichmäßige Färbung des Films („discoloration“) in Erscheinung tritt.

**[0005]** Eine gute Nanotopologie ist von besonderer Bedeutung für ein erfolgreiches CMP-Verfahren, mit dem beispielsweise derartige Schichten geebnet werden. Die Steifigkeit der Poliertücher, die beim CMP zum Einsatz kommen, und andere Prozessparameter des CMP bewirken eine bevorzugte Glättung gerade im Nanotopologie-Bereich. Dadurch werden Bauteilstrukturen auf einer Halbleiterscheibe, die mit schlechter Nanotopologie in den CMP-Prozess eingeht, inhomogen ausgedünnt. Infolgedessen wird die Bauteilcharakteristik verschlechtert bis hin zum Kurzschluss bei gar durchbrochenen Zwischenlagen (Dielektrika).

**[0006]** Die Nanotopologie wird gemessen, indem die gesamte Scheibenoberfläche mit unterschiedlich großen Messfeldern vollständig und mit Überlapp abgerastert wird. Keine einzige der in diesen Messfeldern jeweils gefundenen Höhenvariationen der Oberfläche (peak to valley) darf den geforderten Maximalwert für die gesamte Scheibe überschreiten. Die Messfeldgrößen sind spezifikationsabhängig und zum Beispiel auf 2 mm × 2 mm, (5 mm × 5 mm) und 10 mm × 10 mm erklärt. Für diese Messfelder sind z. B. bei 0,13 µm minimaler lateraler Strukturgröße der Bauelemente maximale Höhenabweichungen < 20

nm, (< 30 nm) und < 50 nm zugelassen. Für anspruchsvolle höchstintegrierte mikroelektronische Bauteile, die fast ausschließlich unter Einsatz des CMP-Prozesses hergestellt werden, gelten besonders strenge Anforderungen an die Nanotopologie. Diese sind aufgrund der Eigenarten des CMP-Prozesses verglichen mit den globalen, „site“-bezogenen und mikroskopischen Rest-Unebenheitswerten wesentlich strenger und mit konventionellen Bearbeitungssequenzen zur Herstellung der Halbleiterscheiben nicht oder nur mit unwirtschaftlicher Ausbeute zu erreichen.

**[0007]** Die Herausforderung besteht somit darin, eine Halbleiterscheibe bereitzustellen, deren Nanotopologie so gut ist, dass sie den Anforderungen an die Ausgangsebene genügt, die die Herstellung besonders anspruchsvoller mikroelektronischer Bauelemente, insbesondere in Mehrlagen-Technik und mit einem CMP-Schritt, für 0,13 µm laterale Bauteil-Strukturgröße und darunter und für Scheibendurchmesser von 200 mm und darüber stellt.

**[0008]** Halbleiterscheiben, insbesondere Siliciumscheiben, werden gemäß dem Stand der Technik, ausgehend von einem defektarmen monolithischen Einkristall, durch eine Bearbeitungssequenz hergestellt, die mehrere Prozessgruppen umfasst (vgl. beispielsweise DE19823904A1 oder DE19833257C1):

- a) Trennen („Aufsägen“) des Einkristalls in Scheiben,

- b) mechanische Bearbeitung,

- c) chemische Bearbeitung,

- d) chemo-mechanische Bearbeitung.

**[0009]** Daneben kann eine Vielzahl weiterer Schritte wie Reinigungs-, Sortier-, Mess-, und Verpackungsschritte durchgeführt werden, die jedoch keinen Einfluss auf die Ebenheit der Scheibenoberfläche haben und daher im Folgenden nicht weiter betrachtet werden.

**[0010]** Das Trennen a) erfolgt nach dem Stand der Technik in der Regel mittels einer Innenlochsäge („internal-diameter saw“, ID), einer Drahtsäge („multi-wire saw“, MWS), durch Trenn-Planarisierungsschleifen („grind-slicing“, GS), mittels Bandsäge (Einfach-schnitt) oder Gattersäge (Mehrachschnitt).

**[0011]** Die mechanische Bearbeitung b) umfasst das Verrunden der Scheibenkante und die Planarisierung der Scheibenfläche mittels mechanisch abrasiver, materialabtragender Schritte. Das Kantenverrunden („edge/notch rounding“, ENR) geschieht durch Schleifen oder Polieren mit runden, bandförmigen o. ä. Werkzeugen. Die Planarisierung der Scheibenfläche geschieht im „batch“, d. h. für mehrere Scheiben gleichzeitig, durch sog. Läppen mit freiem Korn (vgl. beispielsweise EP813931A1) unter Einsatz einer Läppssuspension („slurry“) oder als Einzel-

scheiben-Prozess durch Schleifen mit gebundenem Korn. Beim Schleifen wird eine Seite der Halbleiterscheibe auf einem Scheibenträger („chuck“) durch Vakuum fixiert und die andere Seite mit einer mit Schleifkorn belegten Schleifscheibe bearbeitet. Die Bearbeitung der beiden Seiten der Halbleiterscheibe erfolgt sequentiell. In der Regel werden Batch-Doppelseitenschleifverfahren mit Läppkinematik angewendet, bei denen sich gebundenes oder auf Beschichtungen (Tuch) aufgebrachtes und dort quasi-fest „eingenistetes“ Abrasiv auf zwei großen gegenüberstehenden Arbeitsscheiben befindet, zwischen denen die Halbleiterscheiben wie beim Läppen halb-frei in Führungskäfigen beweglich beidseitig geschliffen werden. Dieses Verfahren ist beispielsweise in DE19626396A1 beschrieben Daneben ist das sog. „Flachhonen“ bekannt, bei dem die Arbeitsscheiben mit hartstoffbelegten Pellets bestückt sind. EP755751A1 beschreibt ein Schleifverfahren, bei dem beide Seiten einer Halbleiterscheibe simultan durch zwei Schleifwalzen bearbeitet werden, deren Rotationsachsen parallel zu den Flächen der Halbleiterscheibe angeordnet sind.

**[0012]** Die chemische Bearbeitung c) besteht aus einem oder mehreren Reinigungs- und Ätzschritten. Beim Ätzen erfolgt – im Batch oder per Einzelscheibe – ein beidseitiger Materialabtrag, der das Ziel einer „Tiefenreinigung“, eines Abtrags der kristallin geschädigten Oberflächenzonen und einer Reduktion der mechanischen Oberflächenverspannung nach der mechanischen Bearbeitung hat. Es sind zahlreiche Linienabläufe bekannt, die auf das Ätzen verzichten, da der Ätzabtrag zusätzlichen Materialverbrauch und eine Steigerung des Gesamtbearbeitungsaufwands der Halbleiterscheibenherstellung bedeutet und außerdem meist mit einer Verschlechterung der zuvor während der mechanischen Bearbeitung erzielten Scheibengeometrie (Ebenheit, Formtreue) einhergeht.

**[0013]** Die chemo-mechanische Bearbeitung d) besteht aus mehreren Polierschritten. Nach dem Stand der Technik kommt ein ggf. mehrstufiges Vor- und ein in der Regel mehrstufiges Fein-Polierverfahren zum Einsatz. Vorpolutur („Abtrags-“, „Geometriepolitur“; engl.: „pre-“, „stock-removal-“, „primary polishing“) und Feinpolitur („Schleiferfrei-Politur“; engl.: „haze-free polishing“, „secondary polishing“) können hierbei in Form mehrerer Werkstück-Aufspannungen auf unterschiedlichen Maschinen mit dazwischenliegenden Reinigungs-, Sortier-, Mess- und sonstigen Schritten durchgeführt werden, oder in integrierten Bearbeitungswerkzeugen, in denen die Halbleiterscheiben auf die verschiedenen Polierteller mit unterschiedlichen Poliertüchern, deren Eigenschaften jeweils für Vor- und Feinpolitur optimiert sind, direkt umgesetzt werden.

**[0014]** Der Polierschritt ist in der Regel eine che-

mo-mechanische Politur, bei der mit kolloid-dispersem, chemisch modifiziertem Kieselsol („slurry“) teils mechanisch abrasiv, jedoch überwiegend durch chemischen Angriff, durch Relativbewegung der Halbleiterscheiben zu einem Poliertuch ein Materialabtrag bewirkt wird, der die Scheiben kristalldefektarm oder -frei fertig-planarisiert (Geometrie) und die Oberfläche mikroskopisch glättet (Rauigkeit).

**[0015]** Es kommen für Vor- und Feinpolitur Einseiten-Polierverfahren und für das Vorpölieren außerdem noch Doppelseiten-Polierverfahren zum Einsatz. Beim Einseitenpolieren sind die Halbleiterscheiben rückseitig mit einer Trägerplatte verklebt (Kittpolitur), werden von Vakuum gehalten oder haften durch Reibung an einem rückseitigen sog. „backing pad“ (hauptsächlich beim Feinpolieren). Es gibt Einzelscheiben- und Batch-Polierverfahren beim Einseitenpolieren. Die Fein-Politur wird nur auf der späteren Vorderseite der Halbleiterscheibe angewendet. Je nach gewünschtem Finish der späteren Scheibenrückseite wird bei der Vorpölitur nur die Vorderseite bearbeitet, so dass die Rückseite die durch die Vorprozesse vorgegebene Rauigkeit behält, oder es werden beide Seiten mit sequentieller Einseitenpolitur oder mit simultaner Doppelseitenpolitur bearbeitet. Das Doppelseitenpolieren kommt nur für den Vorpölierprozess zum Einsatz. Es ist nach dem Stand der Technik ein Batch-Prozess, bei dem die Halbleiterscheiben halb-frei beweglich, in dünne Führungskäfige eingelegt, simultan beidseitig zwischen zwei Tellern mit Poliertüchern in einer Läppkinematik poliert werden.

**[0016]** Ferner wird i. d. R. vor der Vorpölitur die Scheibenkante feinbearbeitet (poliert). Jedoch sind auch andere Abläufe bekannt, insbesondere auch solche, die ein integriertes Vorverrunden („chamfering“) und Feinverrunden (Kantenpolitur) in einem Schritt vorsehen.

**[0017]** Es ist bekannt, dass eine besonders gute Geometrie der bearbeiteten Scheiben durch den Einsatz eines simultanen Doppelseiten-Schleifverfahrens („double disk grinding“, DDG) im Rahmen der mechanischen Bearbeitung b) erreicht werden kann. Dieses Verfahren ist in WO01/21356A1 beschrieben. Allen bisher veröffentlichten, einen simultanen Doppelseiten-Schleifschnitt beinhaltenden Bearbeitungsabläufen ist jedoch gemein, dass sie mehrere mechanische (spanende) Bearbeitungsschritte beinhalten.

**[0018]** Grundsätzlich wurden bisher nur Bearbeitungsabläufe mit DDG-Schritt für möglich und umsetzbar gehalten, bei denen DDG entweder nur als grober Vorschleifschnitt oder aber in einem zweistufigen Verfahren als Vor- und Feinschleifschnitt zum Einsatz kommt. In der EP 1 049 145 A1 ist ein Bearbeitungsablauf offenbart, der einen DDG-Vorschleif-

schnitt („Schruppen“), gefolgt von einem oder mehreren (sequentiellen) Einseiten-Feinschleifschritten („Schlichten“) enthält. Dagegen wird in der US 6,066,565 der Einsatz des DDG-Verfahrens in einem zweistufigen Prozess mit Doppelseiten-Vorschleifen und Doppelseiten-Feinschleifen beschrieben. Dafür sind zwei Maschinen und mehrere Aufspannungen des Werkstücks nötig.

**[0019]** Die genannten Bearbeitungsabläufe nach dem Stand der Technik sind dadurch charakterisiert, dass die generellen Vorteile einer DDG-Bearbeitung durch die Nachteile einer beim Einsatz von DDG stets für notwendig gehaltenen mechanischen Bearbeitung in mehreren Schritten erkauft werden. Die mehrstufigen mechanischen Teilbearbeitungsabläufe nach dem Stand der Technik, die einen oder mehrere DDG-Schritte enthalten, weisen für die auf ihnen beruhenden Gesamt-Bearbeitungsabläufe folgende erhebliche Nachteile auf:

Der Materialverbrauch steigt mit der Zahl der Bearbeitungsschritte. Bei Doppel- bzw. Mehrstufenbearbeitung wird insgesamt mehr Material vom Werkstück abgetragen als bei einer Ein-Schritt-Bearbeitung, da Ein- und Ausschleifvorgänge sowie das „Warmschleifen“ bis zur Einstellung des thermischen Gleichgewichts mehrfach anfallen. Außerdem müssen Abtragszugaben, um die für die Qualitätsziele jeden Einzelschritts erforderlichen Mindestmaterialabträge mit Sicherheit auch bei schwankenden Eingangsqualitäten der Werkstücke zu erreichen, mehrfach auf den Materialeinsatz beaufschlagt werden.

**[0020]** Ebenso wie der Materialabtrag steigt auch die Ausfallquote mit der Zahl der Bearbeitungsschritte an, da jede Einzelschritt-Ausbeute unter 100% liegt.

**[0021]** Hinzu kommt, dass lange Prozessketten mit vielen Bearbeitungsschritten sich durch geringe Flexibilität, schlechte Verfügbarkeit des Gesamtbearbeitungsablaufs und hohe Durchlaufzeiten auszeichnen. Generell sinkt die Gesamtverfügbarkeit der Bearbeitungskette mit zunehmender Zahl der Einzelschritte. Um Ausfälle in der Produktion zu vermeiden, müssen daher Pufferlager und Reservemaschinen vorgehalten werden.

**[0022]** In der Summe steigen daher die Herstellkosten für Halbleiterscheiben mit der Zahl der Bearbeitungsschritte an. Dies gilt auch für die mehrstufigen mechanischen Bearbeitungsabläufe gemäß dem Stand der Technik, die einen ansonsten vorteilhaften DDG-Schritt enthalten.

**[0023]** Die der Erfindung zu Grunde liegende Aufgabe bestand daher darin, ein Verfahren für die Herstellung von Halbleiterscheiben bereitzustellen, das den steigenden Qualitätsanforderungen für die nachfolgende Bauteilherstellung, insbesondere bezüglich

der Nanotopologie, genügt und das gleichzeitig möglichst kostengünstig, materialsparend, schnell und flexibel ist.

**[0024]** Die Aufgabe wird gelöst durch ein Verfahren zur Herstellung von Halbleiterscheiben, das folgende Teilschritte enthält:

- a) Auftrennen eines Halbleiterstabs in eine Vielzahl von Halbleiterscheiben,

- b) Verrunden der Kanten der Halbleiterscheiben,

- c) simultanes Schleifen beider Seiten der Halbleiterscheiben, das als „double-disk grinding“ ausgeführt wird, unter Verwendung keramisch gebundener Schleifräder mit einer Schleifmittelkörnung gemäß JIS/US mesh #2000 oder feiner und

- d) Politur der Halbleiterscheiben, wobei Schritt c) der einzige spanende mechanische Bearbeitungsschritt ist, mit dem die Flächen der Halbleiterscheiben bearbeitet werden.

**[0025]** Beim erfindungsgemäßen Verfahren zur Herstellung einer Halbleiterscheibe erfolgt die formgebende mechanische Bearbeitung der Flächen der Halbleiterscheibe einzig durch ein „Ein-Schritt Simultanes Doppelseitenschleifen“. („One-stop simultaneous double-disk grinding“, „single-pass simultaneous double-disk grinding“, 1S-DDG. Die Begriffe „double-disk grinding“ und „double-side grinding“ werden synonym im Sinne des beschriebenen Simultanschleifprozesses verwendet.) Darunter versteht man ein Verfahren, das auf einer simultanen Doppelseiten-Schleifmaschine durchgeführt wird und das dadurch gekennzeichnet ist, dass es nur einen einzigen Bearbeitungsvorgang mit nur einer Werkstückaufspannung umfasst. Das bedeutet, dass die allgemein erforderliche Vor- und Fein-Bearbeitung („Schruppen“ und „Schlichten“) in einem einzigen, integrierten Bearbeitungsschritt stattfindet.

**[0026]** Trotzdem bestehen keine Einschränkungen bezüglich akzeptabler Start-Oberflächen. Es können Oberflächen mit allen realistischen Rauigkeiten und Strukturen der Vorprozesse bearbeitet werden, insbesondere Oberflächen, die durch das Aufsägen mittels MWS (uni- und bidirektional), ID, GS oder Gattersäge erhalten wurden. Es können aber auch bereits geschliffene oder sogar bereits polierte Oberflächen bearbeitet werden. Insbesondere entfällt beim 1S-DDG das bei den Verfahren nach dem Stand der Technik stets für notwendig gehaltene Aufrauen der Oberfläche im Schrupschritt, um eine „Angriffsrauhigkeit“ insbesondere auf glatten Oberflächen guter vorhergehender Trennprozesse („Fein-Trennen“) für den nachfolgenden Schlichtschritt herzustellen, d. h. eine Rauigkeit herzustellen, an der das feine Korn des Feinschleifschritts angreifen kann.

**[0027]** Das 1S-DDG-Verfahren toleriert in hohem Maße Qualitätsschwankungen der Eingangsscheiben bezüglich Rauigkeit, Dicke oder Geometrie,

ohne Zusatzabträge erforderlich zu machen. Generell werden durch den 1S-DDG-Schritt die oben angeführten Nachteile der mehrstufigen mechanischen Bearbeitungsverfahren nach dem Stand der Technik vermieden, so dass sehr materialsparend gearbeitet werden kann.

**[0028]** Gleichzeitig erlaubt der Doppelseiten-Schleifprozess aufgrund der kollinearen Anordnung der beiden Spindel-Achsen das Erreichen einer hohen Enddicken-Maßhaltigkeit der Halbleiterscheiben nach der Doppelseitenpolitur.

**[0029]** Erfindungsgemäß findet keine weitere Vor- oder Nachbearbeitung durch Läppen, Einseiten-schleifen („single-side grinding“, SSG), sequentielles Einseitenschleifen beider Scheibenseiten ( $2 \times$  SSG) oder einen anderen durch überwiegend mechanischen, spanenden Materialabtrag formgebenden Bearbeitungsschritt, wie er nach dem Stand der Technik notwendig ist, statt. Nicht ausgeschlossen ist damit ein vor oder nach dem Schleifschritt durchgeführtes Kantenverrunden oder eine Kantenpolitur, da durch diese Verfahren nicht die Flächen der Halbleiterscheibe bearbeitet werden, sondern deren Kante.

**[0030]** Die Halbleiterscheibe kann nach dem erfindungsgemäßen Verfahren mit einer besonders geringen Zahl von Einzelbearbeitungsschritten hergestellt werden. Aus der geringen Zahl an Einzelbearbeitungsschritten resultieren erhebliche Vorteile hinsichtlich Flexibilität der Herstellung (schnelle Reaktion auf verschiedenste Kundenspezifikationen), Logistik (weniger Material in der Linie; schnellere Disposition) usw. Ferner wird die Halbleiterscheibe in besonders materialsparender Weise hergestellt. Die Präparation des einkristallinen Halbleiterstabs verursacht einen erheblichen Anteil an den Gesamtherstellkosten einer Halbleiterscheibe. Ein verringelter Materialverlust während der Folgebearbeitung des Einkristallstabs in den zahlreichen Schritten bis zur fertigen Halbleiterscheibe zieht daher eine erhebliche Kostenersparnis nach sich.

**[0031]** Nach dem Stand der Technik wurde der Schritt des Doppelseiten-Schleifens (double-disk grinding, DDG) stets nur zur Verwendung für Bearbeitungssequenzen in Betracht gezogen, die eine weitere mechanische Vor- oder Nachbearbeitung der Halbleiterscheibe durch Läppen, Einseiten- oder sequentielles Einseiten-Schleifen zwingend vorsahen. Eine Verwendung von DDG als zentralen mechanischen Planarisierungsschritt allein wurde bislang nicht in Betracht gezogen. Überraschenderweise zeigte sich jedoch, dass beim Ein-Schritt Simultanen Doppelseitenschleifen, 1S-DDG, die geforderten Eigenschaften erzielt werden können. Das erfindungsgemäße Verfahren ermöglicht somit die Herstellung von Halbleiterscheiben in hoher Ausbeute und ohne Qualitätsverluste. Darüber hinaus liefert das erfin-

dungsgemäße Verfahren Vorteile, die die Prozesssequenzen gemäß dem Stand der Technik nicht aufweisen bzw. gerade durch die Kombination mehrerer Schritte verlieren.

**[0032]** Besonders vorteilhaft am erfindungsgemäßen Verfahren ist, dass die Halbleiterscheiben durch das 1S-DDG-Verfahren im Kreuzschliff bearbeitet werden. Das bedeutet, dass beim Schleifen sich schneidende Schleifriefen der individuellen Abrasiv-Körper entstehen – im Gegensatz zum Strahlenschliff, z. B. bei SSG-Verfahren, bei dem nur parallele Schleifriefen entstehen. Der Kreuzschliff und seine Eigenschaften bestimmen die Eingangsmorphologie der Halbleiterscheiben für die nachfolgende chemische Bearbeitung durch Ätzen oder die chemo-mechanische Politur. Durch den Kreuzschliff werden mehrere positive Eigenschaften bewirkt: Der Materialabtrag mit Kreuzschliffkinematik ist schneller und damit kostengünstiger als mit Strahlenschliff, z. B. bei der Bearbeitung nach dem Stand der Technik mittels SSG, 2 × SSG oder einer Kombination aus DDG und SSG oder 2 × SSG.

**[0033]** Kreuzschliff ist kristallographisch isotroper als Strahlenschliff. Aufgrund der gerichteten Eigenschaften eines Einkristalls (kristallographische Anisotropie) gibt es leichter und schwerer zu spanende ausgezeichnete Richtungen. In den leicht zu spanenden kristallographischen Richtungen erfolgt beim Kreuzschliff kein höherer Materialabtrag als in den schwerer zu spanenden kristallographischen Richtungen, da in jedem Oberflächenpunkt der bearbeiteten Scheibe sich stets Schleifspuren mit unterschiedlichen Richtungen kreuzen, so dass sich alle kristallorientierungsabhängigen Individualschnittgeschwindigkeiten herausmitteln.

**[0034]** Beim Strahlenschliff, der keine kreuzenden Bahnen aufweist, ist der kristallographische Spanwinkel vom Ort auf der Halbleiterscheibe abhängig. Verschiedene Orte werden also unterschiedlich stark abgetragen. Dies ist nur durch die Steifigkeit der Schleifscheibe begrenzt, die ein übermäßig inhomogenes Ausdünnen der Halbleiterscheibe verhindert. Beim Strahlenschliff entsteht ein sehr langreichweites Muster, dessen Vorzugsrichtungen die Kristallsymmetrie widerspiegeln. Bei einer zur Kristallebene <100> parallelen Siliciumoberfläche (Si<100>) entsteht beispielsweise ein Kreuz, bei Si<111> ein Sechsach-Stern. Derartig langwellige Geometriestörungen sind in den Folgebearbeitungsschritten nicht oder nur mit erheblichem Materialabtrag zu entfernen. Es verbleibt ein qualitativ, insbesondere mit der Messmethode des sog. „Magic Mirror“, und quantitativ, z. B. mittels Interferometrie oder Lasertriangulation, auffälliges, unerwünschtes „Schleifkreuz“ an der fertig bearbeiteten Halbleiterscheibe.

**[0035]** Bei Kombinationsbearbeitungen aus DDG

und SSG oder 2 × SSG nach dem Stand der Technik bestimmt der zweite SSG-Schritt die Oberflächenmorphologie des Wafers. Der vorteilhafte Kreuzschliff des DDG steht daher bei Bearbeitungssequenzen nach dem Stand der Technik den selektiv angreifenden chemischen oder chemo-mechanischen Folgebearbeitungsprozessen nicht mehr zur Verfügung. Diese entwickeln das Schleifkreuz durch präferentiellen Angriff an den durch die mechanische Bearbeitung geschwächten Kristallgitterbereichen gerade erst heraus.

**[0036]** Bevorzugt wird im Rahmen der Erfindung ein simultanes Doppelseiten-Schleifverfahren unter Verwendung einer Werkstückaufnahme eingesetzt, die die Halbleiterscheibe praktisch zwangsführungsfrei hält und bewegt („frei schwimmend“, „free-floating process“, FFP). Die generellen Vorteile einer FFP-Bearbeitung, die aus dem Fortfall einschränkender Zwangsbedingungen durch im Allgemeinen selbst fehlerbehaftete kraft- oder formschlüssige Werkstückaufnahmen resultieren, sind beispielsweise aus dem (Doppelseiten-)Läppen und Doppelseitenpolieren (DSP) bekannt und werden bezüglich der für das DSP charakteristischen Eigenschaften exemplarisch für einen typischen Anwendungsfall von J. Haisma et al. (Appl. Opt. 33 (34) (1994) 7945) beschrieben.

**[0037]** Weiterhin ist im Rahmen der Erfindung die Verwendung von Schleifräder mit einer harten, keramischen Bindung vorgesehen. Diese führen aufgrund ihrer Steifigkeit zu einer besonders hohen Enddicken-Maßhaltigkeit der Halbleiterscheiben. Außerdem verhindert die Verwendung keramisch gebundener Schleifscheiben beim 1S-DDG eine Oberflächenkontamination in Form von Kunststoffabrieb sowie eine Oberflächen- oder Volumenkontamination z. B. durch Metalle. Das Fehlen von Kunststoffabrieb, wie er beispielsweise bei Verwendung kunstharzgebundener Schleifscheiben auftritt, macht einen nachfolgenden „Tiefenreinigungsschritt“, z. B. durch materialabtragendes Ätzen, verzichtbar.

**[0038]** Voraussetzung für ein Weglassen des Ätzschritts ist ein ausreichend glattes Finish nach dem Schleifen, da das Ätzen auch eine Reduktion der Oberflächenverspannung bewirkt, die auf die Kristallschädigung durch die mechanische Bearbeitung zurückzuführen ist. Ist die Kristallverspannung und die Dichte der Defekte zu hoch, pflanzen sich diese Defekte aufgrund der mechanischen Belastung beim Polieren, insbesondere beim „free-floating“-DSP mit den frei beweglichen Halbleiterscheiben, fort und überdauern bis zum Endprodukt.

**[0039]** Für das erfindungsgemäße Verfahren wird daher ein besonders feines Schleifkorn verwendet, das eine geringe Rauigkeit der Scheibenoberfläche nach dem 1S-DDG-Prozess gewährleistet. Der Fein-

heit des Korns ist aber eine Grenze dadurch gesetzt, dass eine Direktbearbeitung der Eingangsoberfläche der Halbleiterscheibe (also z. B. nach dem Auftrennen des Einkristallstabs mittels MWS) durch 1S-DDG noch möglich ist, was umso leichter gegeben ist, je größer das verwendete Schleifkorn ist. Diese konträren Anforderungen werden durch spezielle keramisch gebundene Schleifscheiben erfüllt, deren Verwendung daher im Rahmen des erfindungsgemäßen Verfahrens vorgesehen ist. Es werden Schleifscheiben mit einer Schleifmittelpörnung gemäß US mesh oder JIS mesh #2000 (und entsprechender FEPA Normen; etwa 4–6 µm mittlere Korngröße) oder feiner verwendet. Besonders bevorzugt ist es, Bindungshärte und -porosität, Schleifkorndichte und -verteilungskurve und einige andere Materialparameter sowie Prozessparameter beim 1S-DDG wie Spindelvorschub und -strategie sowie den Abtrag dem bearbeiteten Material anzupassen.

**[0040]** Erfindungsgemäß hergestellte Halbleiterscheiben weisen nach dem Teilearbeitungsschritt des 1S-DDG eine geringe Oberflächenrauhigkeit und eine geringe Dichte und Tiefe der verbleibenden Kristallgitterdefekte („damage“) auf. Beispielsweise werden in einer bevorzugten Ausführung des erfindungsgemäßen Verfahrens Rauhigkeiten von um 400 Å RMS mit einem keramisch gebundenen Schleifrad mit #2000 Schleifkornsiebung (4–6 µm Korngröße) erzielt und um 100 Å RMS mit 1,5 µm Korngröße. Ferner wurden mit einem Schleifrad-Prototypen bereits Rauhigkeiten um 50 Å RMS in einem erfindungsgemäß einzigen 1S-DDG-Bearbeitungsvorgang erreicht. Dies ist zu vergleichen mit nicht wesentlich unter 500 Å RMS erzielbarer Rauhigkeit beim Einseitenschleifen (Strahlenschliff), betrieben mit einem feinst möglichen, noch wirtschaftlichen Abtragsraten liefernden, ebenfalls selbtschärfenden (nicht zusetzenden) Kunstharz-gebundenen Schleifrad, das dem Stand der Technik entspricht. (Messwerte aus Profilometer mit 1 µm Diamant-Stylus im < 80 µm Hochpass.) Die Rauhigkeit ist insbesondere so gering, dass bereits ein materialsparender Folge-Polierabtrag das gewünschte End-Finish liefern kann. Zudem erfolgt keine Defektfortpflanzung aufgrund der mechanischen Belastung beim Polieren, so dass die verbleibenden Kristalldefekte nicht bis zum Endprodukt überdauern. Prinzipiell ermöglicht das erfindungsgemäße 1S-DDG-Verfahren eine endproduktnahe Feinbearbeitung. Durch das Nichtvorhandensein einer Scheibenauflage („chuck“) treten bei den geschliffenen Halbleiterscheiben keine Schädigungen durch Auflagekontakt und somit keine Kratzer usw. auf, die materialintensiv entfernt bzw. „repariert“ werden müssten.

**[0041]** Die Halbleiterscheiben haben nach dem Teilearbeitungsschritt des 1S-DDG eine außerordentlich geringe Dickenstreuung um den Prozess-Zielwert herum. Eine Halbleiterscheibe weist unmittelbar

nach einem simultanen Doppelseitenschleifen der Halbleiterscheibe in einem Schritt eine Abweichung von der angestrebten mittleren Zieldicke („thickness“,  $\langle THK \rangle$ ) von  $\Delta THK \leq 0,75 \mu\text{m}$  ( $\Delta THK$  = Standardabweichung der mittleren Waferdicke  $\langle THK \rangle$  im Prüflös) sowie eine totale Dickenvarianz („total thickness variation“, TTV) von  $TTV \leq 1 \mu\text{m}$  auf.

**[0042]** Darüber hinaus sind die Halbleiterscheiben nach dem Teilearbeitungsschritt des 1S-DDG außerordentlich rotationsymmetrisch, d. h. die den verbleibenden TTV-Wert liefernde Dickenverteilung innerhalb einer Halbleiterscheibe ist durch ein radialsymmetrisches (ein-parametriges) Querschnittsprofil nahezu vollständig bestimmt. Unmittelbar nach einem simultanen Doppelseitenschleifen der Halbleiterscheibe in einem Schritt eine Rotationsasymmetrie  $\Delta ROT \leq 0,5 \mu\text{m}$  auf.

**[0043]** Definitionsgemäß muss die auf eine verbleibende Winkelabhängigkeit der Dickenverteilung entfallende Rotationsasymmetrie  $\Delta ROT$  stets kleiner oder gleich der gesamten Dickenverteilung TTV sein. Bei Schleifverfahren nach dem nächsten Stand der Technik resultiert tatsächlich ein wesentlicher Beitrag zur Gesamtdickenvarianz

$$TTV = \max_{\varphi,r} \{THK(\varphi_1, r_1) - THK(\varphi_2, r_2)\}$$

aus einer Rotationsasymmetrie  $\Delta ROT$ , beispielsweise einer Keiligkeit der Halbleiterscheibe, z. B. infolge eines taumelnden Chucks (Höhenschlag) beim Einseitenschleifen.

**[0044]**  $\Delta ROT$  kann ähnlich dem TTV als

$$\Delta ROT = \max_r [\max_{\varphi} \{THK_r(\varphi_1) - THK_r(\varphi_2)\}]$$

definiert sein, wobei  $\max_{\varphi,r}$  das bei Variation von Winkel  $\varphi$  und Radius  $r$  erhaltene Maximum der Höhendifferenz  $THK(\varphi_1, r_1) - THK(\varphi_2, r_2)$ ,  $\max_{\varphi}$  das bei Variation von  $\varphi$  bei festem  $r$  und  $\max_r$  das bei Variation von  $r$  bei festem  $\varphi$  jeweils erhaltene Maximum bezeichnet und  $THK_r(\varphi)$  die lokale Dicke THK in Abhängigkeit von  $\varphi$  bei festem  $r$  angibt.

**[0045]** Aufgrund ihrer guten Zieldicken-Maßhaltigkeit sind die erfindungsgemäßen Halbleiterscheiben besonders für die direkte Weiterbearbeitung durch Polieren geeignet. Das Vorpolieren ist weit überwiegend ein Mehrscheiben-Prozess, bei dem gleichzeitig in einem Bearbeitungslauf eine Vielzahl von Scheiben parallel auf einem Polierteller bearbeitet werden. Eine sehr gleichmäßige Eingangsdicke der in einen solchen Mehrscheiben-Polierprozess gelgenden Halbleiterscheiben ist Grundvoraussetzung für ein leistungsfähiges Polierverfahren, das geprägt ist durch gleichmäßigen Materialabtrag und gleiche, gute Geometrie und Nanotopologie für alle Scheiben im Polierlos. Dies ist nur bei identischer individueller

Polierkinematik für alle Scheiben in einer Polierfahrt gegeben. Insbesondere beim Doppelseitenpolieren, bei dem die Scheiben lose in dünnen Führungskäfigen liegen und zwischen zwei Poliertellern quasi frei schwimmend poliert werden, führt eine etwaige Eingangsdickenstreuung zu einer ungleichen Auflast-Verteilung auf die einzelnen Scheiben. Dies führt zu erhöhtem Bruchrisiko, da die dicksten Scheiben am Beginn des Polierprozesses einen großen Teil der Polierteller-Last aufnehmen. Weiterhin führt eine große Streuung der Eingangsdicken zu von Scheibe zu Scheibe unterschiedlicher Kinematik, d. h. zu individueller Eigenbewegung: dicke Scheiben rotieren schnell, dünne langsam. Dies wiederum führt bei den einzelnen Scheiben zu unterschiedlichen Geometrien nach der Doppelseitenpolitur.

**[0046]** Außerdem wird durch die Schwankung der Eingangsdicke der Mindestmaterialabtrag beim Mehrscheiben-Polieren erhöht, der erforderlich ist, um eine weitgehend homogene Ausgangsdicke bei akzeptabler Geometrie und anderen Scheibeneigenschaften zu erzielen.

**[0047]** Materialabtrag durch Polieren ist sehr kostenintensiv. Möglichst kurze Polierprozesse sind daher bevorzugt. Daher ist eine sehr homogene Eingangsdicke erforderlich, wie sie das 1S-DDG-Verfahren liefert. In einem kombinierten Verfahren aus z. B. DDG-Grobschliff und SSG- oder 2 × SSG-Feinschliff wird der inhärente Vorteil der DDG-Methode, identische Scheibenausgangsdicken zu liefern, durch die Nachbearbeitung mit dem SSG bzw. 2 × SSG wieder zunichto gemacht, da das SSG von Haus aus nur vergleichsweise schlechtere Enddickenstabilitäten zu liefern imstande ist. Dies röhrt von der Kollinearität der Schleifspindel-Achsen beim DDG gegenüber dem Achsversatz zwischen Scheibenhalter („chuck“) und Schleifspindel beim SSG her. Die Kollinearität beim DDG macht das Verfahren gegen Schwankungen der momentanen Schnittfreudigkeit der Schleifräder immun, ist inhärent steif und verwindungsresistent. Der Achsversatz führt, wenn die Schnittfreudigkeit der Schleifräder natürlicherweise schwankt, zum Verkippen der Achsen zueinander bzw. zu elastischen Verwindungen in der Maschine, die den Gegendruck der durch die Schleifspindel-Zustellung sich aufbauenden Drücke kompensieren.

**[0048]** Ferner ist eine genaue Messung der momentanen Werkstückdicke während des Prozesses („in-process gauge“) nur beim DDG möglich, da hier beide Seiten der Scheiben während der Bearbeitung frei zugänglich sind. Beim SSG ist eine Scheibenseite auf einem Chuck gehalten, der eine genaue Messung der momentanen Dicke verhindert, da der an manchen Stellen verbleibende Zwischenraum zwischen Chuck-Oberseite und Werkstückunterseite, der sich aus der mangelnden Planlage der i. d. R. welligen Halbleiterscheiben auf dem Chuck ergibt,

unbekannt ist und ferner verbleibende Höhenschläge und Unebenheiten des Chucks selbst die Dickenmessung verfälschen. Die Messung der aktuellen Scheibendicke wird zusätzlich dadurch erschwert, dass in einem 2 × SSG-Prozess typischerweise ein weicher (Soft-)Chuck und ein harter (Hard-)Chuck im Wechsel zum Einsatz kommen und eine Dickenmessung auf einem Soft-Chuck generell nicht genau möglich ist.

**[0049]** Die Halbleiterscheiben besitzen nach dem Teilarbeitungsschritt des 1S-DDG eine hohe Ziel-Formtreue. Das heißt, dass die tatsächliche Form der Halbleiterscheiben nach dem 1S-DDG nur geringfügig von der gewünschten Form abweicht, wie sie die Eingangsform für den Folgebearbeitungsschritt des Polierens oder optional des Ätzens bildet. Darüber hinaus sind die nach 1S-DDG ggf. noch verbleibenden Rest-Formabweichungen stets von einer Art, die besonders unkritisch für die Folgeprozesse sind.

**[0050]** So reagiert beispielsweise die Doppelseiten-Politur (DSP) kritischer auf eine verbleibende Rotationsasymmetrie  $\Delta\text{ROT}$  der Scheibendicke THK als auf deren aus beliebig verteilten lokalen Dicken THK = THK( $\varphi, r$ ) erhaltenen Gesamtdickenvariation TTV (bei jeweils vergleichbaren Werten für  $\Delta\text{ROT}$  und TTV), da die DSP selbst rotationssymmetrische Scheibengeometrien erzeugt und vergleichbare Rotationsasymmetrien (beispielsweise Keiligkeit) erst durch Polier-Mehrabtrag wirkungsvoll entfernt werden können. Allgemein weicht sogar die optimale Eingangsform für die Folgebearbeitung oft von der einer idealen ebenen Scheibe ab, insbesondere dann, wenn durch gezielte Formabweichungen Prozesseigenarten der Folgeprozesse im Voraus gerade kompensiert werden können. Als Beispiel ist hier wieder die DSP zu nennen, die unter bestimmten Umständen und abweichend vom angestrebten (und erzielbaren) Ideal einer planparallelen Oberfläche zu rotationssymmetrischen, aber konkav gekrümmten Oberflächen neigt („Bikonvexlinse“) und daher von einer – ebenfalls erforderlich rotationssymmetrischen – gezielt konkav gekrümmten Oberfläche nach 1S-DDG („Bikonkavlinse“) profitiert.

**[0051]** Da durch die Verkürzung der Gesamtprozesskette durch den Einsatz von 1S-DDG die geschliffene Scheibe näher am Finish der fertig bearbeiteten Scheibe ist, ist der Punkt einer guten Geometrie bereits nach der mechanischen Formbearbeitung von großer Bedeutung. Da die Folgeprozesse der erfundungsgemäßen Prozesskette keine wesentlichen Veränderungen der Scheibengeometrie mehr mit sich bringen, insbesondere bei kurzen Prozessketten mit wesentlich reduziertem Materialabtrag beim Polieren, ist eine besonders ebene Scheibe nach dem mechanischen Bearbeitungsschritt, wie sie das 1S-DDG-Verfahren liefert, im Allgemeinen von Vor-

teil.

**[0052]** Im Folgenden werden die einzelnen Schritte des erfindungsgemäßen Verfahrens beschrieben:

**[0053]** Schritt a) ist ein Trennschritt, bei dem eine scheibenförmige Einheit von einem gezogenen und maßhaltig gemachten Einkristall getrennt wird. Dieser Trennschritt wird nach dem Stand der Technik durchgeführt und kann ein sequentieller Trennprozess (eine Scheibe nach der anderen) oder ein simultaner Trennprozess (alle Scheiben eines Schnittloses gleichzeitig) sein. Sequentielle Trennprozesse werden beispielsweise mit Innenlochsägen (ID) oder Bandsägen durchgeführt. Möglich ist auch das gleichzeitige Sägen der Scheibe und Schleifen der Stabendfläche, d. h. der Oberfläche der entstehenden Halbleiterscheibe („grind-slicing“, GS). Bevorzugt im Rahmen der erfindungsgemäßen Prozesssequenz ist jedoch ein simultaner Trennprozess mittels einer Drahtsäge („multi-wire slicing“, MWS), wahlweise unter Verwendung einer Schneidsuspension (Slurry-Trennläppen, S-MWS), oder eines Drahtes mit gebundenem Schneidkorn (z. B. Diamantdraht-Trennschleifen, D-MWS). Vorteile des MWS-Verfahrens sind geringe Kosten, hoher Durchsatz und Verwendbarkeit auch bei größeren Stabdurchmessern. Die MWS-typischen Nachteile wie beispielsweise Sägewellen werden beim erfindungsgemäßen Verfahren durch den nachfolgenden Doppelseiten-Schleifschritt besonders vorteilhaft eliminiert.

**[0054]** In Schritt b) erfolgt eine Profilierung der Scheibenkante (Kanten-/Notch-Verrundung, „chamfering“). Dieser Schritt kann beliebig aus den Verfahren nach dem Stand der Technik ausgewählt werden. Möglich ist ein Schleifen mit einem Profilschleifkörper, ein Schleifen mit Konturbewegung der Halbleiterscheibe an einem Schleifkörper oder ein Walzen-, Band- oder Tuch-Schliff. Insbesondere kann auch ein Kanten-Feinverrunden bzw. ein integriertes Verfahren mit Kanten-Vorverrunden und Kanten-Politur zum Einsatz kommen. Im Fall einer konventionellen Grobverrundung ist im weiteren Bearbeitungsablauf gegebenenfalls an geeigneter Stelle ein Kanten-/Notch-Polierschritt vorzusehen.

**[0055]** Das Kantenverrunden kann alternativ auch nach dem 1S-DDG durchgeführt werden. Nachteile dieser Alternative sind die erschwerte Werkstückhandhabung beim 1S-DDG aufgrund des noch nicht maßhaltigen Scheibendurchmessers und der scharfen Scheibenkante sowie eine Gefährdung des durch 1S-DDG erreichten Oberflächen-Finishs der Halbleiterscheibe durch das neuere Aufspannen beim nachfolgenden Kantenverrunden. Dem steht der Vorteil gegenüber, dass beim Kantenverrunden integrierte Vor- und Feinver rundungsprozesse (Schleifen und Politur) eingesetzt werden können, wie sie beispiels-

weise in JP 08090401 A beschrieben sind.

**[0056]** Schritt c) ist der oben ausführlich beschriebene 1S-DDG-Prozess.

**[0057]** Schritt d) ist ein Polierprozess nach dem Stand der Technik. Dieser besteht in der Regel aus einer Vor- und einer Endpolitur, die daher im Folgenden getrennt betrachtet werden. Die Vorpolitur kann ein Mehr- oder Einzelscheibenpolierprozess sowie ein Einseiten- oder Doppelseitenpolierprozess sein. Der Doppelseitenpolierprozess kann ein sequentieller Einseitenpolierprozess (erst Rück-, dann Vorderseite) oder ein simultaner Doppelseitenpolierprozess (DSP) sein. Alle Kombinationen aus Ein- und Mehrscheiben-, Einseiten- und Doppelseitenpolierprozess sind möglich. Für DSP ist bislang jedoch nur ein Mehrscheiben-DSP Stand der Technik. Die Endpolitur wird in der Regel als Einseitenpolitur ausgeführt.

**[0058]** Folgende erfindungsgemäßen Bearbeitungsabläufe mit unterschiedlichen Polierprozessen in Schritt d) sind bevorzugt: Die Politur kann aus der Sequenz Doppelseiten-Vorpolitur – Einseiten-Endpolitur der Scheibenvorderseite bestehen. Daneben sind Bearbeitungsabläufe möglich, bei denen beide Seiten der Halbleiterscheibe sequentiell einseitenpoliert werden und im Anschluss daran die Vorderseite der Halbleiterscheibe die Endpolitur erfährt. Die Vor- und End-Einseitenpolitur können getrennt voneinander oder gekoppelt erfolgen. Dabei kann beispielsweise die Rück- und Vorderseiten-Vorpolitur in einer Maschine bzw. in einem Prozess durchgeführt werden. Alternativ kann eine Kombination von Vorderseiten-Vorpolitur und Vorderseiten-Endpolitur in einer Maschine bzw. in einem Prozess erfolgen. Möglich ist auch ein Bearbeitungsablauf, bei dem nur die Vorderseite der Halbleiterscheibe vor- und anschließend endpoliert wird. Vor- und End-Einseitenpolitur können wiederum isoliert (z. B. auf getrennten Maschinen) oder integriert erfolgen (z. B. auf einer Maschine mit verschiedenen Poliertellern, zwischen denen die Halbleiterscheibe ohne Prozessunterbrechung und Be- bzw. Entladevorgänge direkt umgesetzt wird, ggf. mit einem dazwischen durchgeführten Reinigungsschritt).

**[0059]** Optional kann zwischen dem Doppelseiten-Schleifen c) und der Politur d) ein Ätz- oder (Tiefen-)Reinigungsschritt eingefügt werden, bei dem simultan doppelseitig oder sequentiell einseitig oder aber auch nur einseitig (z. B. Spin-Etch-Verfahren) chemisch Material von der Scheibenoberfläche abgetragen wird. Auf diese Weise werden, falls erforderlich, Kristallgitterschäden und Oberflächenverspannungen reduziert sowie Kontaminationen entfernt. Bevorzugt ist jedoch eine Bearbeitungssequenz ohne Ätzschritt. Dies spart Material, Zeit und Kosten und vereinfacht den Prozessablauf. Ferner wird die durch ein Ätzen stets stattfindende Ver-

schlechterung der bei der mechanischen Bearbeitung erzielten Scheibengeometrie vermieden.

**[0060]** Daneben kann eine Vielzahl weiterer Schritte wie Reinigungs-, Sortier-, Mess-, und Verpackungsschritte durchgeführt werden, die jedoch keinen Einfluss auf die Ebenheit der Scheibenoberfläche haben. Weiterhin kann die Scheibenoberfläche nach der Endpolitur beispielsweise epitaktisch beschichtet werden.

**[0061]** Die erfindungsgemäß fertig bearbeitete Halbleiterscheibe, z. B. nach einer Feinpolitur, weist eine ausgezeichnete lokale Ebenheit (Nanotopologie) auf. Die Erfindung bezieht sich daher auch auf eine Halbleiterscheibe mit einer maximalen Unebenheit der Scheibenvorderseite von weniger als 20 nm in einem beliebigen Messfeld von 2 mm × 2 mm Größe und von weniger als 50 nm in einem beliebigen Messfeld von 10 mm × 10 mm Größe.

**[0062]** Sie ist dadurch besonders geeignet für die nachfolgende Weiterverarbeitung mit hoher Ausbeute zu besonders anspruchsvollen Bauelementen, bei deren Herstellung der CMP-Prozess zur Anwendung kommt. Dieser CMP-Prozess reagiert besonders kritisch auf Rest-Unebenheiten im genannten kurzreichweiten Bereich.

**[0063]** Das erfindungsgemäße Verfahren führt insbesondere auch dann zu einer guten Nanotopologie, wenn in Schritt a) beim Auftrennen des Halbleiterstabs mit einer Drahtsäge („multi-wire slicing“, MWS) der Sägedraht reißt und deshalb durch einen neuen Draht ersetzt werden muss. Dies führt nach dem Auftrennen zu einer markanten Stufe im Dickenprofil der Scheiben. Derartige „Drahtriss-Scheiben“ sind nach dem Stand der Technik nicht für hochwertige Verwendungen weiterverwendbar und in der Regel Ausschluss – mit entsprechend dramatischen Folgen für die Gesamt-Herstellungskosten, da ein Drahtriss immer jeweils alle Scheiben eines Sägeloses, d. h. etwa 200 bis 300 Scheiben gleichzeitig, betrifft. Das erfindungsgemäße Verfahren ist in der Lage, auch derartige Scheiben noch zu hochwertigen Endprodukten weiterzuverarbeiten.

**[0064]** Eine weitere besonders vorteilhafte Eigenschaft der erfindungsgemäß hergestellten Halbleiterscheiben ist ihre hohe Ebenheit bis zum äußersten Rand. Insbesondere weisen sie gute Geometriewerte auch für den derzeit bei der Bewertung der Scheibenoberfläche ausgenommenen Randbereich auf (Randausschluss, „edge exclusion“, EE). Der Randausschluss beträgt derzeit typischerweise 3 mm. Bei den erfindungsgemäß hergestellten Halbleiterscheiben verschlechtert sich die Qualität mit Vergrößerung des spezifizierten Oberflächenbereichs – beispielsweise auf Randausschlüsse von 2 mm (erwarteter Standard), 1 mm (zukünftig) und 0,5 mm – nur gering-

fügig.

**[0065]** Die erfindungsgemäß hergestellten Scheiben weisen insbesondere keinen „Randabfall“ auf, d. h. sie zeigen keine konvexe Form bzw. Dickenverjüngung zum Scheibenrand hin. Ein derartiger Randabfall tritt beim SSG bzw. 2 × SSG aufgrund der dort benötigten großen Schleifscheibendurchmesser auf. Die Durchmesser der beim SSG eingesetzten Schleifscheiben liegen typischerweise über den Durchmessern der bearbeiteten Halbleiterscheiben. Dies ist nötig, um dem Ideal eines möglichst geradlinig diametral über die Scheibe verlaufenden Schnittpfads nahe zu kommen. Dadurch wird der Instabilität durch die ungleichmäßige Krafteinleitung beim Schleifen aufgrund des Versatzes von Chuck- und Schleifspindel-Achse entgegengewirkt. Die beim SSG somit notwendigerweise große Schleifscheibe schleift demzufolge fast senkrecht über den Scheibenrand in die Scheibenfläche hinein. Ein senkrechter schneller Schleifangriff der Scheibenfläche hat an der strukturell schwächeren Kante mikroskopische Kantenausbrüche zur Folge. Außerdem führt das SSG über die Schleifkinematik des sog. Strahlenschliffs (parallele, nicht-kreuzende Schleifriefen) zu einer Kristallgitterschwächung am Scheibenrand, die in der Folgebearbeitung, z. B. durch chemisches Ätzen oder chemo-mechanisches Polieren, einen erhöhten Materialabtrag an der Scheibenkante nach sich zieht.

**[0066]** Beim SSG wird der nicht-kreuzende, radiale Strahlenschliff üblicherweise durch konkaves Verspannen des Werkstücks auf dem leicht balligen Chuck und entsprechendes leichtes Neigen der Chuck- oder Spindelachse gegeneinander erzwungen. Prinzipiell ist beim SSG auch ein Kreuzschliff möglich. Dieser ist jedoch nachteilig, da aufgrund des Chuck-/Spindel-Achsversatzes und der daraus resultierenden inhärenten Neigung zu Instabilität ein noch ungleichmäßigerer Eingriff mit Vibration, „stick-and-slip“ usw. erfolgen würde als beim Betrieb mit bewusst vorgespannter Ausrichtung der Achsen.

**[0067]** Beim DDG können jedoch vorteilhaft kleinere Schleifscheiben mit Durchmessern im Bereich des halben Durchmessers der bearbeiteten Halbleiterscheiben eingesetzt werden. Dies ist möglich, da sich die Achsen beider Schleifrad-Spindeln genau in Flucht befinden (Kollinearität) und sich alle Kräfte, anders als beim SSG, beim DDG genau kompensieren. Dies führt dazu, dass die Schleifkörper fast parallel zur Scheibenkante und somit sehr „sanft“ unter kleinen Schliffwinkeln in die Scheibenfläche hineinschleifen. Dadurch sind Rand-Mikrausbrüche unwahrscheinlicher. Zudem führt der Kreuzschliff des DDG zu keinen kristallographisch präferentiellen Kristallgitterschäden mit inhomogenem Folgeschritt-Materialabtrag im Randbereich.

**[0068]** Die Vorteile des erfindungsgemäßen Verfahrens werden im Folgenden anhand von Figuren und Beispielen detailliert dargelegt.

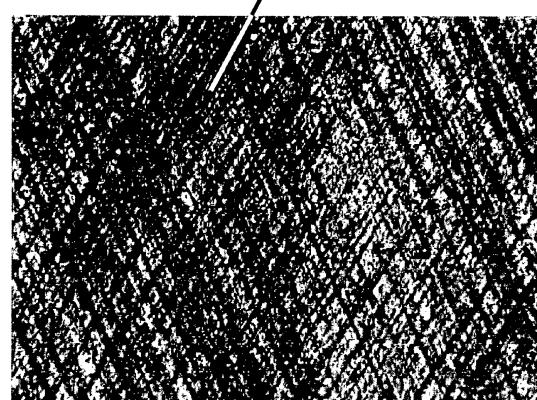

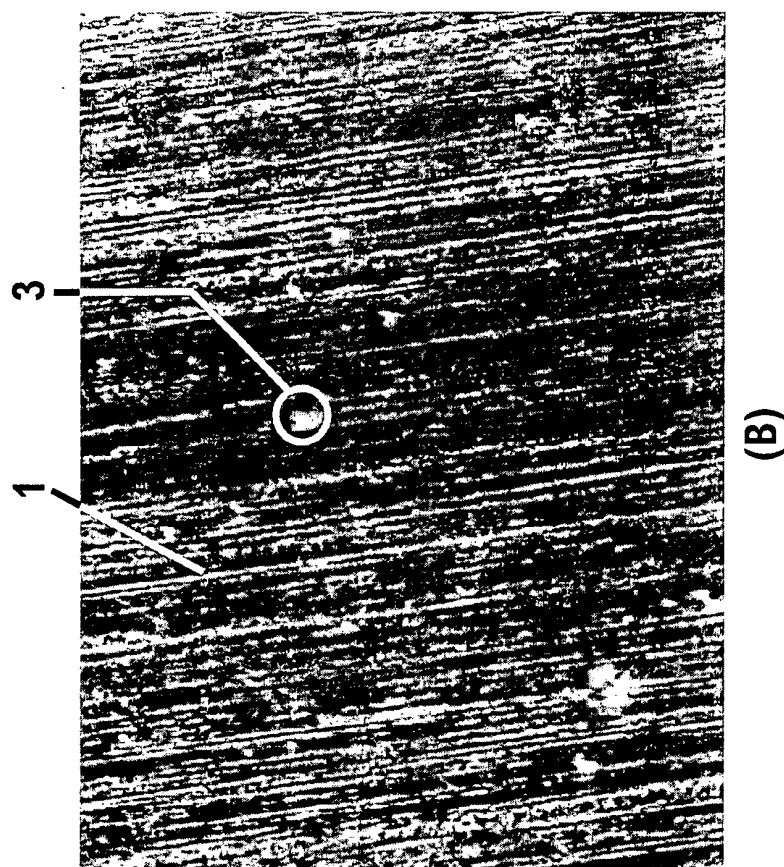

**[0069]** [Fig. 1](#) ist eine Mikroskopie der Scheibenflächen jeweils einer erfindungsgemäß hergestellten, doppelseitengeschliffenen Siliciumscheibe ([Fig. 1\(A\)](#)) und einer nach dem Stand der Technik hergestellten Siliciumscheibe ([Fig. 1\(B\)](#)), jeweils nach erfolgter mechanischer Bearbeitung.

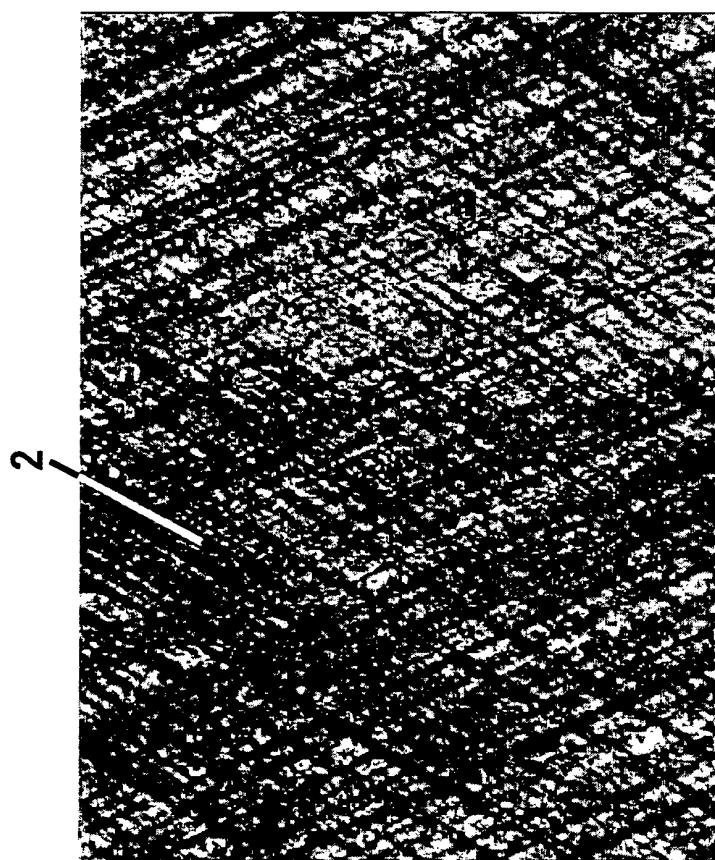

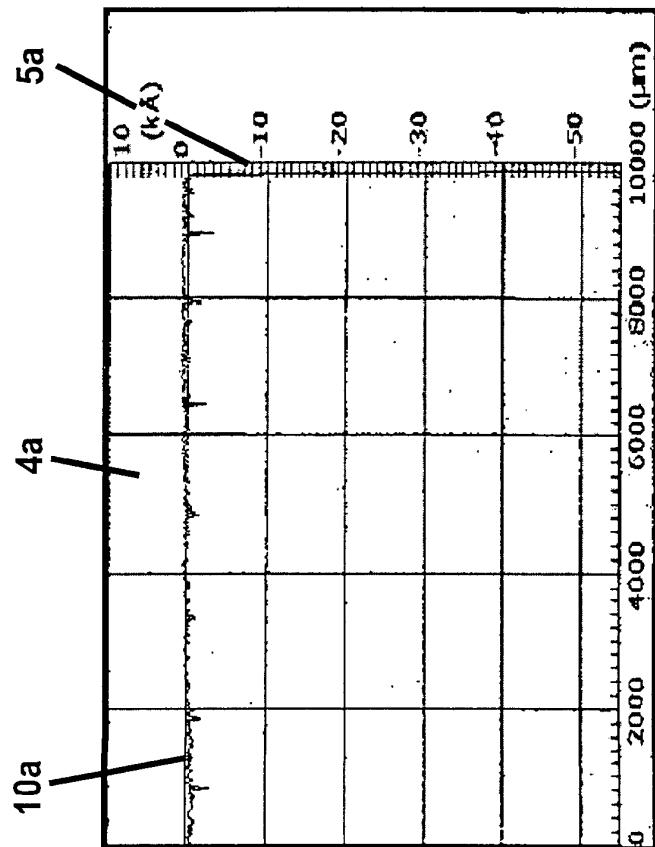

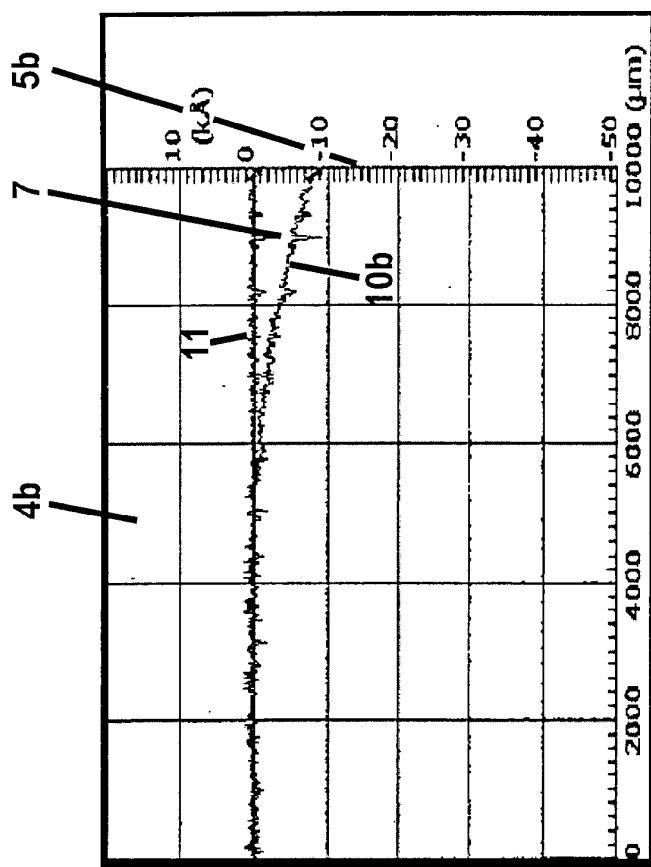

**[0070]** [Fig. 2](#) zeigt die Oberflächenprofile im Randbereich einer erfindungsgemäß hergestellten, doppelseitengeschliffenen Siliciumscheibe ([Fig. 2\(A\)](#)) und einer nach dem Stand der Technik hergestellten Siliciumscheibe ([Fig. 2\(B\)](#)), jeweils nach erfolgter mechanischer Bearbeitung.

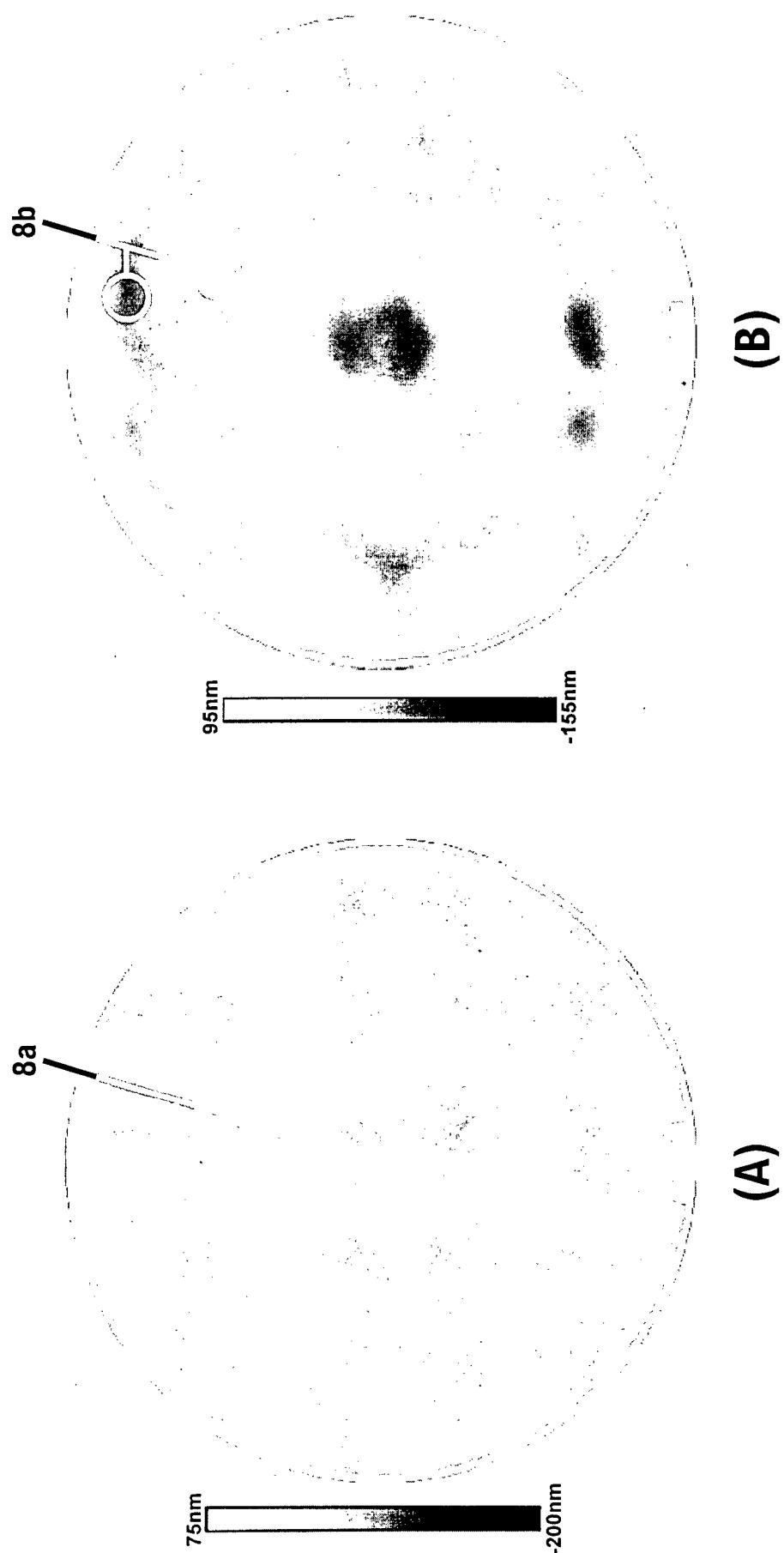

**[0071]** [Fig. 3](#) zeigt die Nanotopologie einer erfindungsgemäß hergestellten Siliciumscheibe nach erfolgter Politur ([Fig. 3\(A\)](#)) im Vergleich zu einer nach dem Stand der Technik hergestellten Siliciumscheibe, ebenfalls nach erfolgter Politur ([Fig. 3\(B\)](#)).

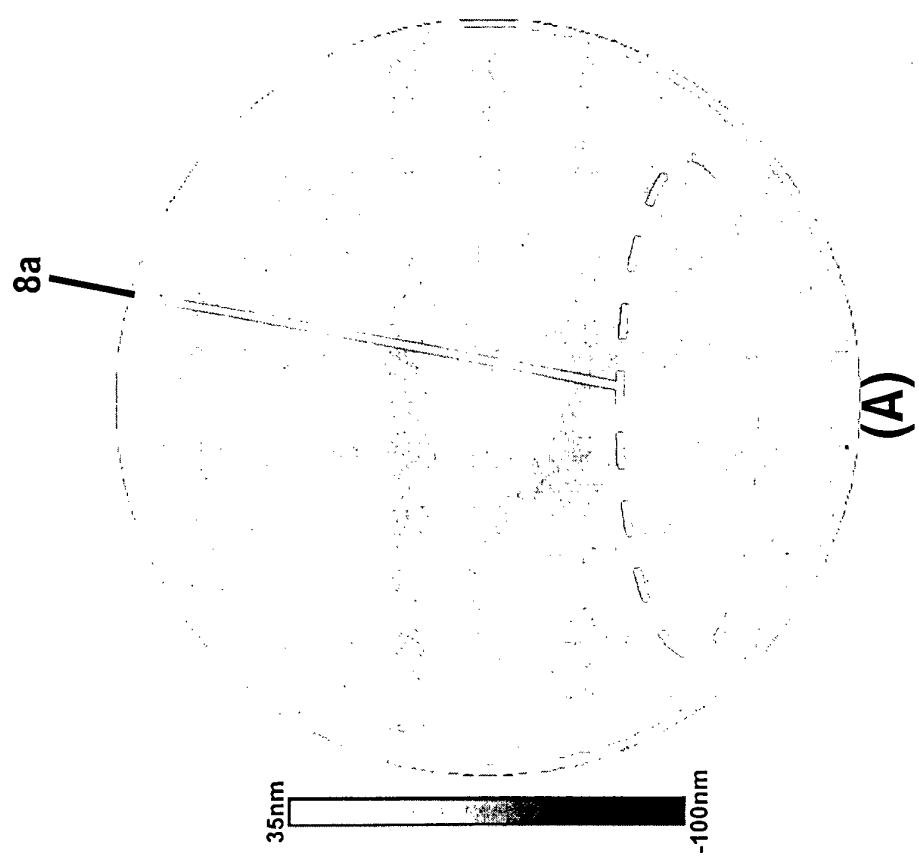

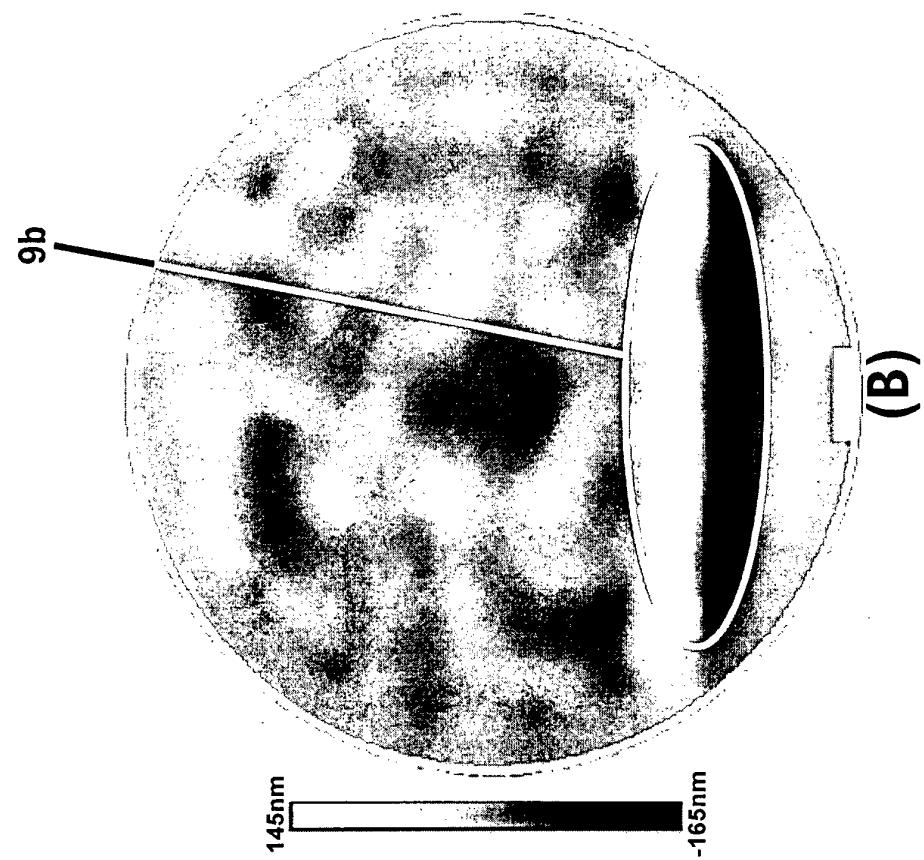

**[0072]** [Fig. 4](#) zeigt einen Vergleich wie [Fig. 3](#), jedoch stammen die Siliciumscheiben aus einem Stabstück, bei dessen Trennen mittels einer Drahtsäge (MWS) der Sägedraht gerissen war.

Beispiel 1:

**[0073]** Eine Siliciumscheibe wurde erfindungsgemäß durch Abtrennen von einem maßhaltig gemachten Einkristall von nominell 300 mm Durchmesser mittels einer Drahtsäge, Kantenverrunden, 1S-DDG unter Verwendung von Schleifräder mit keramisch gebundenem Schleifkorn der Größe #2000 (ca. 4–6 µm), Ätzen mit einem geeigneten Gemisch aus Flusssäure und Salpetersäure in einer Ätzanlage mit laminarer Strömungsbewegung der Ätzmischung über die Scheibenoberfläche, Doppelseiten-Vorpolitur und Einseiten-Endpolitur erfindungsgemäß hergestellt.

**[0074]** [Fig. 1\(A\)](#) zeigt eine vergrößerte Ansicht (Mikroskopie) der Oberfläche der Siliciumscheibe nach dem Teil-Bearbeitungsschritt 1S-DDG. Die einander kreuzenden Schleifspuren **2** von der 1S-DDG-Bearbeitung sind deutlich sichtbar. Abrieb und Kontamination der Oberfläche, die zusammen mit der geringen Rauigkeit und Schädigungstiefe ein nachfolgendes Ätzen oder eine nachfolgende Tiefen-Reinigung überflüssig machen, sind nicht vorhanden. Die Oberfläche ist sauber und homogen.

**[0075]** Eine quantitative Darstellung des Randbereichs der Siliciumscheibe nach dem Teil-Bearbeitungsschritt 1S-DDG in Form eines mit einer Tastsonde aufgenommenen Profilogramms enthält [Fig. 2\(A\)](#). Klar erkennbar ist die gute Ebenheit **10a** bis zum

Scheibenrand mit dem abrupten Übergang zwischen Scheibenfläche **4a** und der zuvor gezielt verrundeten Scheibenkante **5a**. Die beim Kantenverrunden erzeugte Fase ist aufgrund der empfindlichen Höhen Skala (Einheiten: 10 kÅ = 1 µm) an der nahezu senkrechten Linie nach unten zu erkennen.

**[0076]** Die Vorderseite der fertig bearbeiteten, polierten Siliciumscheibe ist in [Fig. 3\(A\)](#) dargestellt. Die Grauwertdarstellung der lokalen Höhenabweichungen (−200 nm bis +75 nm) wurde aus einem interferometrischen Untersuchungsverfahren erhalten. Die Oberfläche ist nahezu perfekt eben (**8a**). Insbesondere sind in beliebigen Messbereichen von 2 mm × 2 mm und 10 mm × 10 mm auf der gesamten Oberfläche alle lokalen Höhenabweichungen kleiner als 20 nm bzw. kleiner als 50 nm. Die Grauwerte geben Absoluthöhen der Oberfläche an, wobei die Nullhöhe einer Regressionsfläche entspricht.

Vergleichsbeispiel 1:

**[0077]** Eine Siliciumscheibe wurde analog zu Beispiel 1 hergestellt, wobei lediglich beim mechanischen Bearbeitungsschritt das 1S-DDG-Verfahren durch ein sequentielles zweimaliges Einseitenschleifen ( $2 \times$  SSG) ersetzt wurde. Das  $2 \times$  SSG-Verfahren besteht aus einem ersten soft-chuck-Schleifschritt, gefolgt – nach Ent-Chucken, Drehen und Zwischenreinigung der Siliciumscheibe – von einem zweiten hard-chuck-Schleifschritt. Es wurde ein kunstharzbundenes Schleifrad mit Schleifkorn der Größe 15 µm (etwa #1200) verwendet. Außerdem erfolgte zwischen der mechanischen Bearbeitung und der Politur ein saurer laminar-flow-Ätzschritt mit 20 µm Gesamtmaterialabtrag.

**[0078]** [Fig. 1\(B\)](#) zeigt die vergrößerte Ansicht (Mikroskopie) der Oberfläche der Siliciumscheibe nach der mechanischen Bearbeitung. Deutlich sind die annähernd parallelen, sich nicht schneidenden einzelnen Schleifspuren **1** zu erkennen. Der Abrieb **3** der Kunstharz-Bindung des Schleifrads erfordert eine nachfolgende materialabtragende Tiefenreinigung bzw. einen Ätzschritt. Während dieser zusätzlichen Schritte verbleiben durch Maskierung an Orten mit Abrieb Materialerhöhungen stehen, die die Rauigkeit verschlechtern und einen vergleichsweise höheren Materialabtrag erforderlich machen.

**[0079]** Ein Profilogramm **10b** des Randbereichs der Scheibenoberfläche nach der mechanischen Bearbeitung ist in [Fig. 2\(B\)](#) dargestellt. Durch das eingesetzte Schleifverfahren tritt ein vorzeitiger Abfall **7** der Scheibenfläche **4b** zum zuvor gezielt verrundeten Randbereich **5b** hin auf. Beim derzeit üblichen Randausschluss von 3 mm (in dieser Darstellung etwa bei  $x = 7000$  µm) trägt der unerwünschte Randabfall **7** mit einer Abweichung von etwa 3 kÅ = 0,3 µm noch nicht maßgeblich zur Gesamt-Ebenheit der Siliciumschei-

be bei. Bei zukünftigen, reduzierten Randausschlusszonen von 2 mm (hier etwa bei  $x = 8000 \mu\text{m}$ , Abweichung  $\Delta y$  dort etwa  $4 \text{ k}\text{\AA} = 0,4 \mu\text{m}$ ), 1 mm ( $x \sim 9000 \mu\text{m}$ ,  $\Delta y \sim 6 \text{ k}\text{\AA} = 0,6 \mu\text{m}$ ) oder 0,5 mm ( $x \sim 9500 \mu\text{m}$ ;  $\Delta y \sim 8 \text{ k}\text{\AA} = 0,8 \mu\text{m}$ ) und zu erwartenden abermals erhöhten Ebenheitsanforderungen an die Gesamtoberfläche der Scheibe wird sich dieser Randabfall 7 deutlich qualitäts- und ausbeutereduzierend bemerkbar machen. Gezeigt sind das ungefilterte Profilogramm 10b und eine hochpassgefilterte Rauigkeitskurve 11.

**[0080]** Fig. 3(B) zeigt die Nanotopologie der fertig bearbeiteten Siliciumscheibe. Die Grauwertdarstellung von  $-155 \text{ nm}$  bis  $+95 \text{ nm}$  stammt wiederum aus einem interferometrischen Untersuchungsverfahren. Deutlich sind ausgeprägte kurzreichweitige lokale Höhenabweichungen (8b) sichtbar, die innerhalb gewählter Messfelder von  $2 \text{ mm} \times 2 \text{ mm}$  bzw.  $10 \text{ mm} \times 10 \text{ mm}$  Größe häufig über  $20 \text{ nm}$  bzw.  $50 \text{ nm}$  liegen. Eine derartige Halbleiterscheibe, hergestellt nach dem Stand der Technik, ist für die Weiterverarbeitung zu anspruchsvollen, höchstintegrierten mikroelektronischen Mehrlagen-Bauelementen und insbesondere dem dabei zum Einsatz kommenden chemo-mechanischen Polierprozess (CMP) ungeeignet.

#### Beispiel 2:

**[0081]** Eine Siliciumscheibe wurde analog zu Beispiel 1 erfindungsgemäß hergestellt. Der Unterschied zu Beispiel 1 besteht ausschließlich darin, dass beim Auftrennen des Silicium-Einkristalls durch MWS der Sägedraht gerissen ist und der Trennvorgang nach Einlegen eines neuen Drahts fortgesetzt wurde. Durch die Prozessunterbrechung kommt es aufgrund thermischer Drift und einiger anderer Gründe stets zu einer deutlich ausgeprägten Stufe im Dickenprofil der so abgetrennten Scheiben. Die Weiterbearbeitung entfernte diese Stufe jedoch nahezu vollständig, wie das in Fig. 4(A) dargestellte Interferogramm zeigt. Die Oberfläche des Endprodukts ist nahezu perfekt eben (8a).

#### Vergleichsbeispiel 2:

**[0082]** Eine Siliciumscheibe aus dem Sägelos des Beispiels 2, bei dem der Drahtriss aufgetreten war, wurde analog zu Vergleichsbeispiel 1 nach dem Stand der Technik weiterverarbeitet. Fig. 4(3) zeigt das Interferogramm der fertig bearbeiteten Siliciumscheibe. Selbst in der im Vergleich zu Fig. 4(A) deutlich größeren Höhenskala ( $-165 \text{ nm}$  bis  $+145 \text{ nm}$  gegenüber  $-100 \text{ nm}$  bis  $+35 \text{ nm}$  in Fig. 4(A)) ist die beim Drahtriss entstandene Stufe noch deutlich als gravierende lokale Höhenabweichung an der fertig bearbeiteten Scheibe, d. h. nach der Politur, sichtbar. Eine derartige Scheibe, hergestellt nach dem Stand der Technik, und damit das gesamte Säge-Los, bei dem der Drahtriss auftrat, ist für die Weiterverarbeitung zu

anspruchsvollen, höchstintegrierten mikroelektronischen Mehrlagen-Bauelementen ungeeignet, insbesondere, wenn dabei ein chemo-mechanischer Planarisierprozess (CMP) zum Einsatz kommt.

#### Patentansprüche

1. Verfahren zur Herstellung von Halbleiterscheiben, das folgende Teilschritte enthält:

- Auftrennen eines Halbleiterstabs in eine Vielzahl von Halbleiterscheiben,

- Verrunden der Kanten der Halbleiterscheiben

- simultanes Schleifen beider Seiten der Halbleiterscheiben, das als „double-disk grinding“ ausgeführt wird, unter Verwendung keramisch gebundener Schleifräder mit einer Schleifmittelkörnung gemäß JIS/US mesh #2000 oder feiner und

- Politur der Halbleiterscheiben, wobei Schritt c) der einzige spanende mechanische Bearbeitungsschritt ist, mit dem die Flächen der Halbleiterscheiben bearbeitet werden.

2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, dass beim Schleifen gemäß Schritt c) eine Werkstückaufnahme eingesetzt wird, die die Halbleiterscheiben zwangsführungs frei hält und bewegt.

3. Verfahren nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass die momentane Dicke der Halbleiterscheiben während des Schleifens gemäß Schritt c) gemessen wird.

4. Verfahren nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, dass vor der Politur der Halbleiterscheiben deren Oberfläche einseitig oder beidseitig mit einem Ätzmedium behandelt wird.

5. Halbleiterscheibe mit einer maximalen Unebenheit der Scheibenvorderseite von weniger als  $20 \text{ nm}$  in einem beliebigen Messfeld von  $2 \text{ mm} \times 2 \text{ mm}$  Größe und von weniger als  $50 \text{ nm}$  in einem beliebigen Messfeld von  $10 \text{ mm} \times 10 \text{ mm}$  Größe.

6. Halbleiterscheibe nach Anspruch 5, dadurch gekennzeichnet, dass die maximalen Unebenheitswerte bis zu einem Randausschluss von  $0,5 \text{ mm}$  erfüllt sind.

7. Halbleiterscheibe nach Anspruch 5 oder 6, dadurch gekennzeichnet, dass sie einen Durchmesser von  $300 \text{ mm}$  aufweist.

Es folgen 4 Blatt Zeichnungen

Anhängende Zeichnungen

(B)

(A)

Fig. 1

(A)

(B)

Fig. 2

Fig. 3

Fig. 4