(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5494147号

(P5494147)

(45) 発行日 平成26年5月14日(2014.5.14)

(24) 登録日 平成26年3月14日(2014.3.14)

(51) Int.Cl.

H02M 7/48 (2007.01)

H02M 7/483 (2007.01)

F 1

H02M 7/48

H02M 7/483

Z

請求項の数 10 (全 13 頁)

(21) 出願番号 特願2010-87471 (P2010-87471)

(22) 出願日 平成22年4月6日 (2010.4.6)

(65) 公開番号 特開2011-223666 (P2011-223666A)

(43) 公開日 平成23年11月4日 (2011.11.4)

審査請求日 平成25年4月1日 (2013.4.1)

(73) 特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74) 代理人 100150441

弁理士 松本 洋一

(72) 発明者 滝沢 脍毅

神奈川県川崎市川崎区田辺新田1番1号

富士電機ホールディングス株式会社内

(72) 発明者 谷津 誠

神奈川県川崎市川崎区田辺新田1番1号

富士電機ホールディングス株式会社内

審査官 松永 謙一

最終頁に続く

(54) 【発明の名称】パワー半導体モジュール及びそれを用いた電力変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、カソードが前記第1のIGBTのエミッタに接続されたダイオードと、エミッタが前記第1のIGBTのエミッタに接続された逆耐圧を有する第2のIGBTとを、一つのパッケージ内に収納し、前記第1のIGBTのコレクタと、前記第2のIGBTのコレクタと、前記第1のIGBTのエミッタと前記第2のIGBTのエミッタとの接続点と、前記ダイオードのアノードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

## 【請求項 2】

前記第1のIGBTのコレクタを直流電源の正極に接続する端子Pとし、前記第2のIGBTのコレクタを直流電源の中点に接続する端子Mとし、前記第1のIGBTのエミッタと前記第2のIGBTのエミッタとの接続点を出力端子Uとし、前記ダイオードのアノードを直流電源の負極に接続する端子Nとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項1に記載のパワー半導体モジュール。

## 【請求項 3】

電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、アノードが前記第1のIGBTのコレクタに接続されたダイオードと、コレクタが前記第1のIGBTのコレクタに接続された逆耐圧を有する第2のIGBTとを、一つのパッケージ内に収納し、前記第1のIGBTのエミッタと、前記第2のIGBT

10

20

Tのエミッタと、前記第1のIGBTのコレクタと前記第2のIGBTのコレクタとの接続点と、前記ダイオードのカソードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

**【請求項4】**

前記第1のIGBTのエミッタを直流電源の負極に接続する端子Nとし、前記第2のIGBTのエミッタを直流電源の中点に接続する端子Mとし、前記第1のIGBTのコレクタと前記第2のIGBTのコレクタとの接続点を出力端子Uとし、前記ダイオードのカソードを直流電源の正極に接続する端子Pとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項3に記載のパワー半導体モジュール。

**【請求項5】**

電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、カソードが前記第1のIGBTのエミッタに接続された第1のダイオードと、一端が前記第1のIGBTのエミッタに接続された第2のダイオードと第2のIGBTとの直列回路とを、一つのパッケージ内に収納し、前記第1のIGBTのコレクタと、前記直列回路の他端と、前記第1のIGBTのエミッタと前記直列回路一端との接続点と、前記第1のダイオードのアノードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

**【請求項6】**

前記第1のIGBTのコレクタを直流電源の正極に接続する端子Pとし、前記直列回路の他端を直流電源の中点に接続する端子Mとし、前記第1のIGBTのエミッタと前記直列回路の一端との接続点を出力端子Uとし、前記第1のダイオードのアノードを直流電源の負極に接続する端子Nとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項5に記載のパワー半導体モジュール。

**【請求項7】**

電圧形の3以上の多レベルの変換回路に適用するパワー半導体モジュールにおいて、第1のIGBTと、アノードが前記第1のIGBTのコレクタに接続された第1のダイオードと、一端が前記第1のIGBTのコレクタに接続された第2のダイオードと第2のIGBTとの直列回路とを、一つのパッケージ内に収納し、前記第1のIGBTのエミッタと、前記直列回路の他端と、前記第1のIGBTのコレクタと前記直列回路との接続点と、前記第1のダイオードのカソードとを、各々外部端子としたことを特徴とするパワー半導体モジュール。

**【請求項8】**

前記第1のIGBTのエミッタを直流電源の負極に接続する端子Nとし、前記直列回路の他端を直流電源の中点に接続する端子Mとし、前記第1のIGBTのコレクタと前記直列回路の一端との接続点を出力端子Uとし、前記第1のダイオードのカソードを直流電源の正極に接続する端子Pとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置したことを特徴とする請求項7に記載のパワー半導体モジュール。

**【請求項9】**

請求項2に記載したパワー半導体モジュールの端子配列と、請求項4に記載したパワー半導体モジュールの端子配列とが平行になるように前記二つのパワー半導体モジュールを隣接配置したことを特徴とする電力変換装置。

**【請求項10】**

請求項6に記載したパワー半導体モジュールの端子配列と、請求項8に記載したパワー半導体モジュールの端子配列とが平行になるように前記二つのパワー半導体モジュールを隣接配置したことを特徴とする電力変換装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、3レベル以上の多レベル（マルチレベルとも言う）の電力変換装置に適用するパワー半導体モジュールとそれを適用した電力変換装置に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

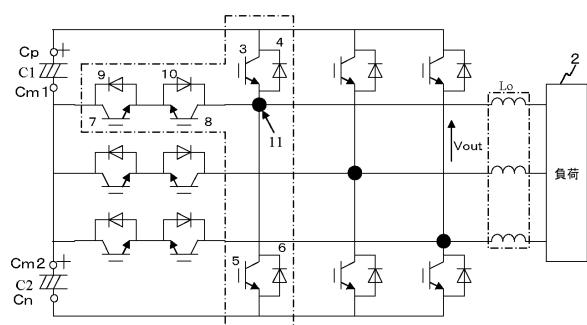

図11に、直流から交流に変換する電力変換回路である3レベルインバータの回路例を示す。C1、C2が直列に接続された直流電源（大容量コンデンサでも代用）で、正側電位をCp、負側電位をCn、中点電位をCm（Cm1、Cm2）としている。一般に本直流電源を交流電源システムより構成する場合は、整流器と大容量の電解コンデンサなどを適用して構成することが可能である。

## 【0003】

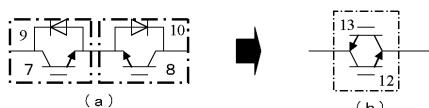

3、4が正側電位Cpに接続されている上アームのIGBTとダイオードで、5、6が負側電位Cnに接続されている下アームのIGBTとダイオードで、上アームと下アームは直列接続されて1相分の相アームを構成する。3個の相アームで三相回路を構成する。また、7、8、9、10は直流電源の中点電位Cm（Cm1、Cm2）と交流出力端子11との間に接続された双方向性のスイッチを構成する素子で、7、8がIGBT、9、10がダイオードである。図11に示す双方向スイッチは、ダイオードを逆並列接続したIGBTを逆直列に接続した構成で、各相に適用される。本図ではIGBT7とIGBT8はエミッタを共通にして逆直列接続しているが、コレクタ共通の構成、あるいは図13（b）に示すように逆耐圧を有するIGBT12、13を逆並列接続した構成でも実現できる。

10

## 【0004】

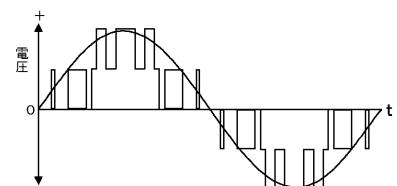

Loがフィルタ用のリアクトル、2が本システムの負荷である。本回路構成することで、出力端子11には、直流電源の正側電位Cp、負側電位Cn、及び中点電位Cmを出力することが可能となる。即ち、本回路は3つのレベルの電圧波形を出力する3レベルインバータの回路となる。図12に出力電圧（Vout）の波形例を示す。2レベルのインバータに対してより低次の高調波成分が少ない（正弦波形に近い）ことが特長であり、出力のフィルタリアクトルLoの小型化が可能となる。

20

## 【0005】

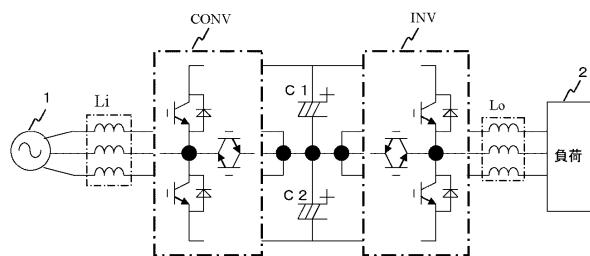

また、図14に交流を直流に変換するPWMコンバータ（CONV）と直流を交流に変換するPWMインバータ（INV）からなるダブルコンバータタイプの電力変換装置を示す。3相交流電源1を入力として、入力フィルタリアクトルLi、3相の3レベルPWMコンバータCONV、直列に接続された大容量のコンデンサC1、C2、3相の3レベルPWMインバータINV、出力フィルタLoにより安定した交流電圧を生成し、負荷2に交流電力を供給する構成である。

30

## 【0006】

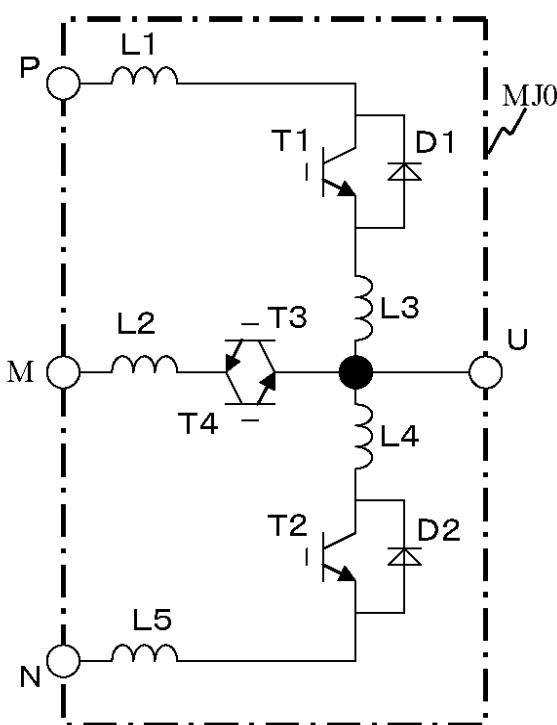

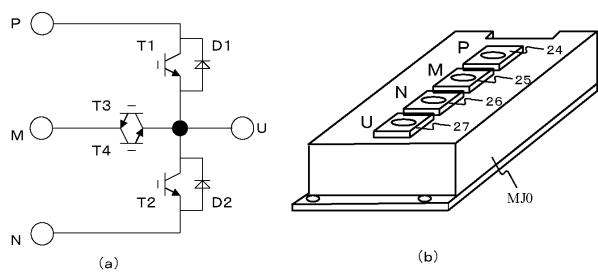

本3レベル変換器（コンバータ又はインバータ）を専用のIGBTモジュールで構成する場合の例が、特許文献1に示されている。図15（b）にそのモジュールの外形構造図を、図15（a）に内部回路例を示す。24、25、26、27がそれぞれ電位Cpに接続される端子P、電位Cmに接続される端子M、電位Cnに接続される端子N、交流出力の端子Uである。本モジュールを3台使用することで3相のインバータを構成することが可能であり、さらに大容量化を図る場合は、本モジュールを並列接続することで実現可能である。

40

## 【先行技術文献】

## 【特許文献】

## 【0007】

## 【特許文献1】特開2008-193779号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

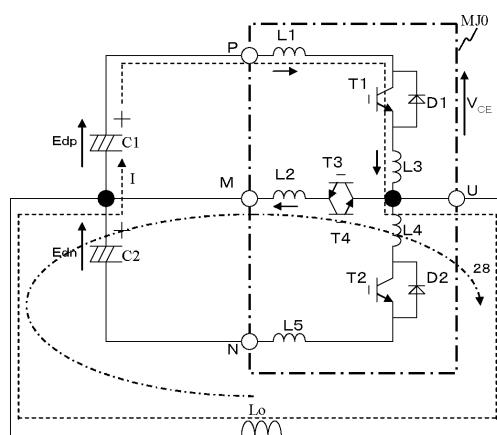

## 【0008】

図16に、図15のモジュールの内部配線インダクタンス（L1～L5）に着目して描いた等価回路を示す。各インダクタンスは主にモジュール出力端子と半導体チップ間、及び半導体チップ間の配線によるものである。各配線は通常数cm程度あるため、各インダクタンス値は10nH程度となる。

50

## 【0009】

図17は、課題を説明するための回路図である。図17において、IGBTT1がオン状態の場合、点線で示す経路（コンデンサC1 インダクタンスL1 IGBTT1 インダクタンスL3 リアクトルLoを通る経路）で電流Iが流れる。次に、IGBTT1がターンオフすると、事前にオンさせておいたIGBTT4が導通し、リアクトルLoの電流は、リアクトルLo インダクタンスL2 IGBTT4 リアクトルLoを通る電流経路28に転流される。その際過渡的に、インダクタンスL1、L2、L3にはIGBTの電流変化率（di/dt）に応じて、図中の矢印の向きに電圧が発生する。

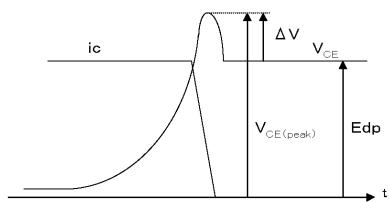

## 【0010】

その結果、外部配線の配線インダクタンスを無視すると、IGBTT1のコレクタ-エミッタ間には最大で式(1)で示される電圧が印加されることになる。図18にIGBTT1がターンオフする時のコレクタ電流(iC)とコレクタ・エミッタ間電圧(VCE)波形例を示す。

## 【0011】

$$V_{CE(\text{peak})} = E_{dp} + (L_1 + L_2 + L_3) \cdot di/dt \quad \dots \text{式(1)}$$

$$\text{サージ電圧 } V = (L_1 + L_2 + L_3) \cdot di/dt \quad \dots \text{式(2)}$$

E<sub>dp</sub>：直流電源1の直流電圧

di/dt：IGBTターンオフ時のIGBTの電流変化率

L<sub>1</sub> + L<sub>2</sub> + L<sub>3</sub>：各配線のインダクタンス値

一例として100AクラスのIGBTの場合、そのdi/dtは最大で2000A/μs程度となるため、L<sub>1</sub> + L<sub>2</sub> + L<sub>3</sub> = 30nHとすると、式(1)によるサージ分(L<sub>1</sub> + L<sub>2</sub> + L<sub>3</sub>) · di/dtは60Vとなる。

## 【0012】

よって、L<sub>1</sub>、L<sub>2</sub>、L<sub>3</sub>、L<sub>4</sub>、L<sub>5</sub>の存在によって、IGBTターンオフ時のIGBTに印加されるピーク電圧値は、直流電圧E<sub>dp</sub>に対して上記式(2)のサージ電圧分高くなるため、IGBTチップ及び並列に接続されているチップは電圧耐量が高いものが必要となる。通常、電圧耐量が高いチップは、概ね電圧耐量比例でチップ面積が広くなるため、モジュールの大型化及びコストアップとなる。

特に、モジュールの大電流化（大容量化）を図った場合、モジュールは体積的に大きくなるため、必然的にモジュール内の配線長は長くなり、その結果配線インダクタンス値も大きくなる。また、スイッチング時のdi/dtも電流値にほぼ比例して大きくなるため、上記式(2)によるサージ電圧Vは、モジュールの電流定格の増加に対して指数的に増加する。そのため、1モジュールにて大容量化を図るのには限界が生じる。一方モジュールの並列接続による大容量化は通常的に行われるが、1モジュールで構成する場合と比較してコストアップとなることや、並列接続間の電流のアンバランスを考慮しなければならないため、設計上ディレーティングしなければならないといった課題がある。

## 【課題を解決するための手段】

## 【0013】

上述の課題を解決するために、第1の発明においては、電圧形の3以上の多レベルの変換回路に適用するIGBTなどのパワー半導体モジュールにおいて、第1のIGBTと、カソードが前記第1のIGBTのエミッタに接続されたダイオードと、エミッタが前記第1のIGBTのエミッタに接続された逆耐圧を有する第2のIGBTとを、一つのパッケージ内に収納し、前記第1のIGBTのコレクタと、前記第2のIGBTのコレクタと、前記第1のIGBTのエミッタと前記第2のIGBTのエミッタとの接続点と、前記ダイオードのアノードとを、各々外部端子とする。

## 【0014】

第2の発明においては、第1の発明における、前記第1のIGBTのコレクタを直流電源の正極に接続する端子Pとし、前記第2のIGBTのコレクタを直流電源の中点に接続する端子Mとし、前記第1のIGBTのエミッタと前記第2のIGBTのエミッタとの接続点

10

20

30

40

50

を出力端子Uとし、前記ダイオードのアノードを直流電源の負極に接続する端子Nとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置する。

#### 【0015】

第3の発明においては、電圧形の3以上の多レベルの変換回路に適用するIGBTなどのパワー半導体モジュールにおいて、第1のIGBTと、アノードが前記第1のIGBTのコレクタに接続されたダイオードと、コレクタが前記第1のIGBTのコレクタに接続された逆耐圧を有する第2のIGBTとを、一つのパッケージ内に収納し、前記第1のIGBTのエミッタと、前記第2のIGBTのエミッタと、前記第1のIGBTのコレクタと前記第2のIGBTのコレクタとの接続点と、前記ダイオードのカソードとを、各々外部端子とする。

10

#### 【0016】

第4の発明においては、第3の発明における、前記第1のIGBTのエミッタを直流電源の負極に接続する端子Nとし、前記第2のIGBTのエミッタを直流電源の中点に接続する端子Mとし、前記第1のIGBTのコレクタと前記第2のIGBTのコレクタとの接続点を出力端子Uとし、前記ダイオードのカソードを直流電源の正極に接続する端子Pとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置する。

#### 【0017】

第5の発明においては、電圧形の3以上の多レベルの変換回路に適用するIGBTなどのパワー半導体モジュールにおいて、第1のIGBTと、カソードが前記第1のIGBTのエミッタに接続された第1のダイオードと、一端が前記第1のIGBTのエミッタに接続された第2のダイオードと第2のIGBTとの直列回路とを、一つのパッケージ内に収納し、前記第1のIGBTのコレクタと、前記直列回路の他端と、前記第1のIGBTのエミッタと前記直列回路一端との接続点と、前記第1のダイオードのアノードとを、各々外部端子とする。

20

#### 【0018】

第6の発明においては、第5の発明における、前記第1のIGBTのコレクタを直流電源の正極に接続する端子Pとし、前記直列回路の他端を直流電源の中点に接続する端子Mとし、前記第1のIGBTのエミッタと前記直列回路の一端との接続点を出力端子Uとし、前記第1のダイオードのアノードを直流電源の負極に接続する端子Nとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置する。

30

#### 【0019】

第7の発明においては、電圧形の3以上の多レベルの変換回路に適用するIGBTなどのパワー半導体モジュールにおいて、第1のIGBTと、アノードが前記第1のIGBTのコレクタに接続された第1のダイオードと、一端が前記第1のIGBTのコレクタに接続された第2のダイオードと第2のIGBTとの直列回路とを、一つのパッケージ内に収納し、前記第1のIGBTのエミッタと、前記直列回路の他端と、前記第1のIGBTのコレクタと前記直列回路との接続点と、前記第1のダイオードのカソードとを、各々外部端子とする。

#### 【0020】

第8の発明においては、第7の発明における、前記第1のIGBTのエミッタを直流電源の負極に接続する端子Nとし、前記直列回路の他端を直流電源の中点に接続する端子Mとし、前記第1のIGBTのコレクタと前記直列回路の一端との接続点を出力端子Uとし、前記第1のダイオードのカソードを直流電源の正極に接続する端子Pとし、端子配列順序を、端子P、端子M、端子N、端子Uの順に直線状に配置する。

40

#### 【0021】

第9の発明においては、電圧形の3以上の多レベルの電力変換回路における、第2の発明である請求項2に記載したパワー半導体モジュールの端子配列と、第4の発明である請求項4に記載したパワー半導体モジュールの端子配列とが平行になるように前記二つのパワー半導体モジュールを隣接配置する。

#### 【0022】

50

第10の発明においては、電圧形の3以上の多レベルの電力変換回路における、第6の発明である請求項6に記載したパワー半導体モジュールの端子配列と、第8の発明である請求項8に記載したパワー半導体モジュールの端子配列とが平行になるように前記二つのパワー半導体モジュールを隣接配置する。

**【発明の効果】**

**【0023】**

本発明では、3レベル以上の多レベルの変換回路に使用するパワー半導体モジュールにおいて、転流動作に着目した回路にてモジュール内のチップを構成することで、外部配線を介さずに転流することが可能である。その結果、従来形の同一体積のモジュールと比較して、モジュール内部の配線インダクタンス値はほぼ変わらずに、電流定格を約2倍とすることが可能となり、大容量化してもコストアップを抑制することが可能となる。10

**【0024】**

また、本発明のモジュールを交流から直流、又は直流から交流に変換する電力変換装置に適用することにより、スイッチング時のサージ電圧の低減が可能となる。さらに、多並列接続して適用する場合、設計時の電流のディレーティングを小さくすることが可能となる。その結果、小型で安価な電力用半導体モジュールと、変換装置での配線数の低減、装置の小型化、低コスト化が可能となる。

**【図面の簡単な説明】**

**【0025】**

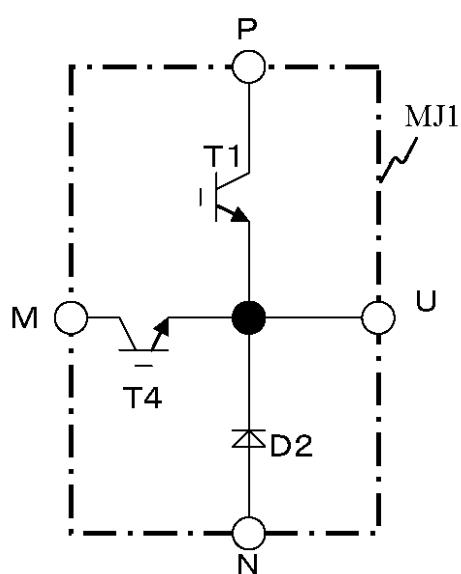

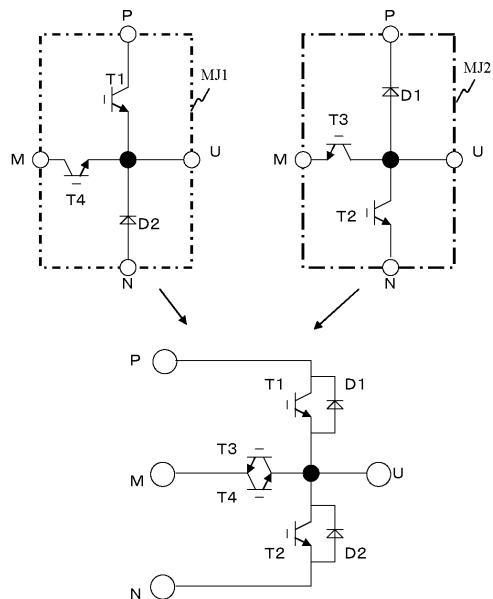

【図1】本発明の第1の実施例を示す回路構成図である。20

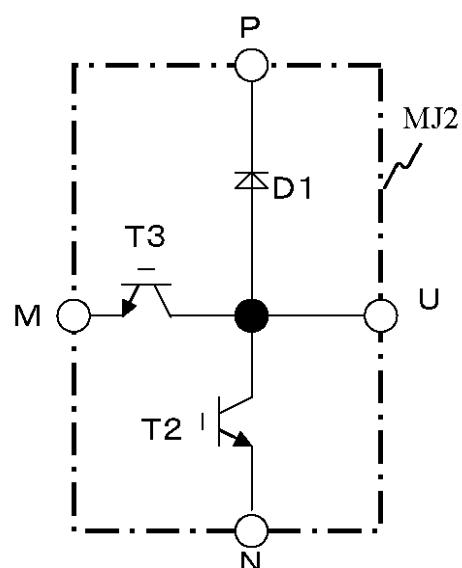

【図2】本発明の第2の実施例を示す回路構成図である。

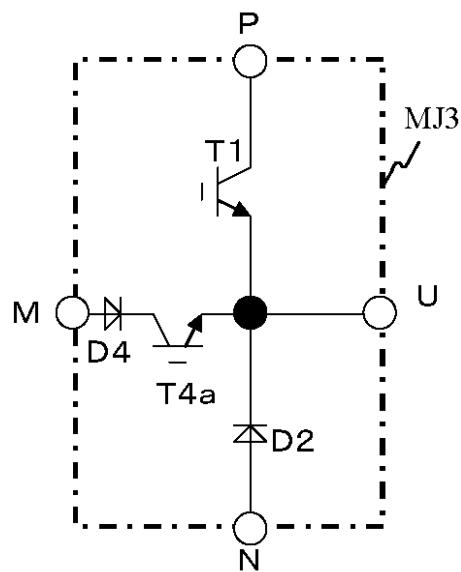

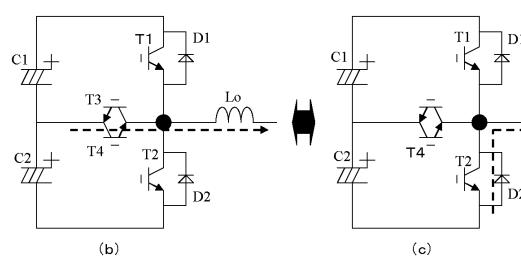

【図3】本発明の第3の実施例を示す回路構成図である。

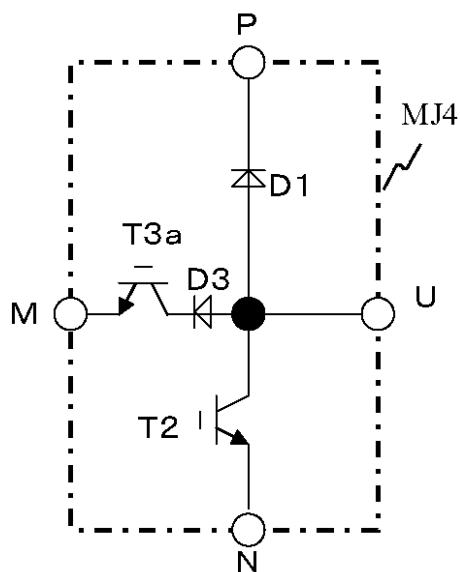

【図4】本発明の第4の実施例を示す回路構成図である。

【図5】3レベル変換回路1相分の回路構成図である。

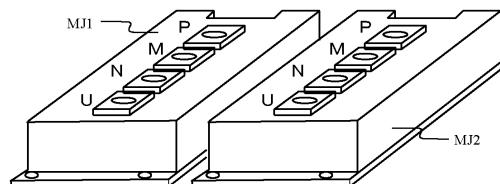

【図6】3レベル変換回路用モジュールの例である。

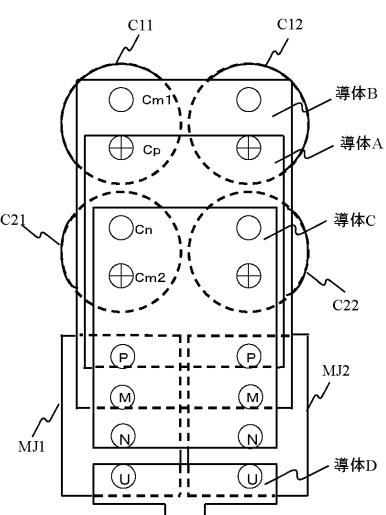

【図7】モジュールとコンデンサとの配線構造例(1相分)である。

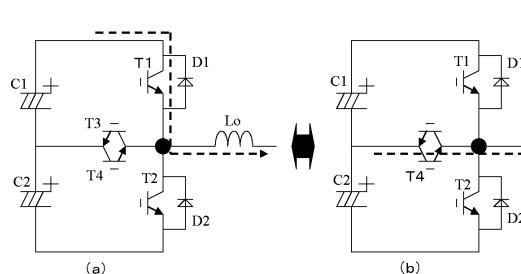

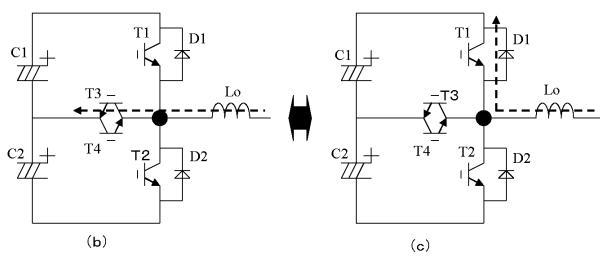

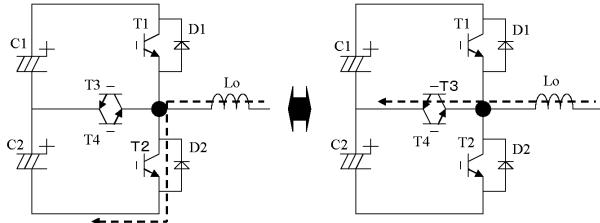

【図8】インバータ運転中の電流の第1の転流動作を示す動作説明図である。

【図9】インバータ運転中の電流の第1の転流動作を示す動作説明図である。

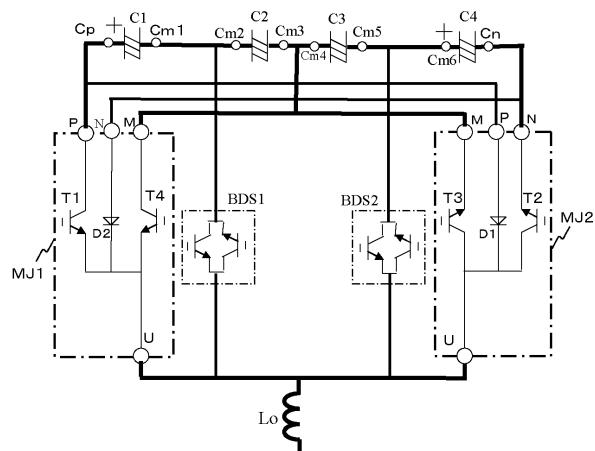

【図10】5レベルインバタ回路への適用例を示す回路図である。

【図11】3レベルインバタ主回路構成図を示す。30

【図12】3レベルインバタ出力電圧波形例を示す。

【図13】双方向スイッチの構成例である。

【図14】ダブルコンバータ(コンバータ+インバタ)の主回路構成図である。

【図15】従来の3レベル変換回路用モジュール例である。

【図16】従来の3レベル変換回路用モジュールの内部等価回路図である。

【図17】従来の課題を説明するための回路図である。

【図18】IGBTターンオフ時の電流、電圧波形例である。

**【発明を実施するための形態】**

**【0026】**

本発明の要点は、1相分の上下アームIGBT直列回路の直列接続点と、直流電源の中点との間に双方向スイッチを接続した3レベル以上の変換回路を構成するパワー半導体モジュールとして、上下アームの一方のIGBTと、他方のダイオードと、双方向スイッチを構成する一方の素子とを内蔵したパワー半導体モジュールを2種類組合せて3レベル以上の変換回路の1相分を構成するようにした点である。40

**【実施例1】**

**【0027】**

図1、図2に、本発明の第1の実施例を示す。図1、図2は、各々第1、第2の発明及びに第3、第4の発明に相当し、直流電源の電位Cmに接続される半導体素子は逆耐圧を有するIGBTで、かつモジュールの形状は図6に示す外観構造である。図5、図7は、本モジュールを3レベルインバタ(直流から交流への変換器)に適用する場合の実施例50

である。

図1のモジュールM J 1は、コレクタが直流電源の正極に接続されるIGBT T T 1と、アノードが直流電源の負極に接続されるダイオードD2と、双方向スイッチ用逆阻止型IGBT T T 4を内蔵し、端子PにIGBT T T 1のコレクタが、端子Mに逆阻止型IGBT T T 4のコレクタが、端子Uに逆阻止型IGBT T T 1のエミッタとIGBT T T 1のエミッタとダイオードD2との接続点が、各々接続された構成である。

#### 【0028】

図2のモジュールM J 2は、エミッタが直流電源の負極に接続されるIGBT T T 2と、カソードが直流電源の正極に接続されるダイオードD1と、双方向スイッチ用逆阻止型IGBT T T 3を内蔵し、端子NにIGBT T T 2のエミッタが、端子Mに逆阻止型IGBT T T 3のエミッタが、端子UにIGBT T T 2のコレクタと逆阻止型IGBT T T 3のコレクタとダイオードD1のアノードとの接続点が、各々接続された構成である。

10

#### 【0029】

図5に、上記モジュールM J 1とM J 2を用いて、3レベルインバータの1相分の回路を構成した回路図を示す。各モジュールの端子P同士、端子N同士、及び端子U同士を、各々接続することにより、3レベルインバータの1相分の回路を構成している。

#### 【0030】

図6に、上記モジュールM J 1とM J 2の外観図を示す。また、図7にモジュールM J 1とM J 2と直流電源としてのコンデンサ直列回路に導体で配線した構造図例を示す。コンデンサC 1 1とC 1 2、及びコンデンサC 2 1とC 2 2は、各々並列接続され、さらに直列接続されて、直流電源を構成している。

20

#### 【0031】

各モジュールの端子列が平行となるように隣接して配置し、各モジュールの端子Pと並列接続されたコンデンサC 1 1、C 1 2の正側電位C pとは導体Aで、各モジュールの端子Mと並列接続されたコンデンサC 1 1、C 1 2の中点電位C m 1とコンデンサC 2 1、C 2 1の中点電位C m 2は導体Bで、各モジュールの端子Nと並列接続されたコンデンサC 2 1、C 2 2の負側電位C nは導体Cで、各々接続される。

また、各モジュールの端子Uは導体Dで接続され、交流端子となる。

#### 【0032】

上述のように、モジュールM J 1、M J 2を端子列が平行となるように隣接配置することで、各モジュールの端子P、M、N、U同士を近接させることが可能となる。この結果、図7に示すようにコンデンサとモジュール間の配線長を短く、かつ低配線インダクタンス化することを目的に、平行平板構造とすることが容易に実現できる。

30

この構成を3個用いることにより、3相3レベルインバータや3相3レベルコンバータを構成できる。

#### 【0033】

図8に、インバータ運転中の電流の転流動作モード1の例を示す。直流電源から負荷側(リアクトルL o側)へ電流を流している時の動作である。図8(a)の状態からIGBT T T 1がターンオフした場合、図8(b)に示すようにIGBT T T 4側に電流は転流する。また図8(b)の状態からIGBT T T 1がターンオンした場合は、図8(a)に示すようにIGBT T T 1側に電流は転流する。

40

#### 【0034】

一方、図8(b)の状態からIGBT T T 4がターンオフした場合は、図8(c)に示すようにダイオードD 2側に電流は転流する。また(c)の状態からIGBT T T 4がターンオンした場合は、図8(b)に示すようにIGBT T T 4側に電流は転流する。

#### 【0035】

図9に、インバータ運転中の電流の転流動作モード2の例を示す。負荷側(リアクトルL o側)から直流電源へ電流を流している時の動作である。図9(a)の状態からIGBT T T 2がターンオフした場合、図9(b)に示すようにIGBT T T 3側に電流は転流する。また図9(b)の状態からIGBT T T 2がターンオンした場合は、図9(a)に示すよ

50

うに IGBT T2 側に電流は転流する。

**【0036】**

一方、図 9 (b) の状態から IGBT T3 がターンオフした場合は、図 9 (c) に示すようにダイオード D1 側に電流は転流する。また図 9 (c) の状態から IGBT T3 がターンオンした場合は、図 9 (b) に示すように IGBT T3 側に電流は転流する。

**【0037】**

以上のように、図 8 に示す出力電流の極性では、IGBT T1、T4、又はダイオード D2 が導通するため、図 1 のモジュール MJ1 であれば、外部配線を介さずに転流することが可能である。また、図 9 に示す出力電流の極性では、IGBT T2、T3 又はダイオード D1 が導通するため、図 2 のモジュール MJ2 であれば、外部配線を介さずに転流することが可能である。10

**【実施例 2】**

**【0038】**

図 3、図 4 に、本発明の第 2 の実施例を示す。第 1 の実施例との違いは、直流電源の中点電位 Cm (Cm1、Cm2) に接続される双方向スイッチ用の素子として逆耐圧を有しない IGBT とダイオードとの直列回路を用いている点である。

**【0039】**

図 3 に示すモジュール MJ3 は、実施例 1 におけるモジュール 1 の逆耐圧を有する IGBT T4 の代わりに、ダイオード D4 と IGBT T4a との直列回路を、また図 4 に示すモジュール MJ4 は、モジュール 2 の逆耐圧を有する IGBT T3 の代わりに、ダイオード D3 と IGBT T3a との直列回路を、各々用いた構成である。ここで、ダイオード D4 と IGBT T4a との直列接続順序、及びダイオード D3 と IGBT T3a との直列接続順序は、逆でも良い。また、主回路構成及び動作は、第 1 の実施例と同様である。20

**【0040】**

尚、上記実施例には直流から交流を作り出すインバータ回路への適用例を示したが、交流から直流を作り出すコンバータ (PWM 整流器) 回路への適用も同様である。

**【実施例 3】**

**【0041】**

図 10 に、本発明の第 3 の実施例を示す。5 レベル電力変換回路への適用例である。直流電源としてのコンデンサ C1 ~ C4 を直列接続し、最も高い電位が Cp、最も低い電位が Cn で、5 つの電位をつくり、各電位をスイッチ回路で、リアクトル Lo を介して負荷側に供給する 5 レベルインバータの 1 相分の構成である。図 7 に示した 3 レベルインバータの構成を 5 レベル化したもので、3 レベルインバータ回路と同様に、本発明のパワー半導体モジュールを適用することができる。コンデンサの直列接続数とスイッチ回路を変更することにより、レベルを自由に変更することができる。30

図 10 の構成では、図 1 に示したパワー半導体モジュール MJ1 と、図 2 に示したパワー半導体モジュール MJ2 を用いて、最も高い電位 Cp、最も低い電位 Cn、及び中間の電位 (Cm3、Cm4) をリアクトル Lo に出力し、第 2 番目に高い電位 (Cm5、Cm6) は双方向スイッチ BDS2 で、第 4 番目に高い電位 (Cm1、Cm2) は双方向スイッチ BDS1 で、各々リアクトル Lo に出力する構成である。モジュール MJ1 と MJ2 を隣接して配置することにより、3 レベル変換回路と同様の効果が得られる。40

また、3 レベルインバータやコンバータと同様に、モジュール MJ1 と MJ2 の代わりに、モジュール MJ3 と MJ4 を、各々用いることができる。

**【0042】**

尚、分割された直流電源と、直流電源間に接続された二つの半導体スイッチの直列回路を用い、半導体スイッチの直列接続点と直流電源の分割点との間に双方向スイッチを接続する構成であれば、コンバータ、インバータのいずれでも実現可能である。

**【産業上の利用可能性】**

**【0043】**

本発明は、3 レベル以上の変換回路に適用できるパワー半導体モジュールとそれを適用50

した変換回路の提案であり、無停電電源装置、電動機駆動装置、系統連系装置などへの適用が可能である。

【符号の説明】

【0044】

|                                         |                 |    |

|-----------------------------------------|-----------------|----|

| 1 . . . 交流電源                            | 2 . . . 負荷      |    |

| 3、5、7、8、T1、T2、T3a、T4a . . . IGBT        |                 |    |

| 12、13、T3、T4 . . . 逆阻止型IGBT              |                 |    |

| BDS1、BDS2 . . . 双方向スイッチ                 |                 |    |

| 4、6、9、10、D1、D2、D3、D4 . . . ダイオード        |                 |    |

| C1、C2、C3、C4、C11、C12、C21、C22 . . . コンデンサ |                 | 10 |

| Lo、Li . . . リアクトル                       | 11 . . . 交流端子   |    |

| CONV . . . コンバータ(PWM整流器)                | INV . . . インバータ |    |

| MJ0、MJ1、MJ2、MJ3、MJ4 . . . 半導体モジュール      |                 |    |

| 導体A~D . . . 導体                          |                 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 12】

【図 11】

【図 13】

【図14】

【図16】

【図15】

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開2009-022062(JP,A)

国際公開第01/031771(WO,A1)

特開2011-223664(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 7/48

H02M 7/483