(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5707634号

(P5707634)

(45) 発行日 平成27年4月30日(2015.4.30)

(24) 登録日 平成27年3月13日(2015.3.13)

|                             |                    |

|-----------------------------|--------------------|

| (51) Int.Cl.                | F 1                |

| G 05 F   3/24   (2006.01)   | G 05 F   3/24   Z  |

| H 01 L   21/822   (2006.01) | H 01 L   27/04   F |

| H 01 L   27/04   (2006.01)  | H 03 F   3/347     |

| H 03 F   3/347   (2006.01)  |                    |

請求項の数 8 (全 10 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2011-130765 (P2011-130765) |

| (22) 出願日  | 平成23年6月12日 (2011.6.12)       |

| (65) 公開番号 | 特開2013-3615 (P2013-3615A)    |

| (43) 公開日  | 平成25年1月7日 (2013.1.7)         |

| 審査請求日     | 平成25年11月13日 (2013.11.13)     |

特許権者において、実施許諾の用意がある。

早期審査対象出願

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 710010157<br>菅原 光俊<br>神奈川県横浜市泉区領家四丁目17番地2 |

| (72) 発明者  | 菅原 光俊<br>神奈川県横浜市泉区領家四丁目17番地2              |

| 審査官       | 榎木澤 昌司                                    |

最終頁に続く

(54) 【発明の名称】 トンネル電流回路

## (57) 【特許請求の範囲】

## 【請求項 1】

ソースを共通接続したトランジスタ対と、

かかるトランジスタ対のドレインの少なくとも一方に負荷が接続され、

かかるトランジスタ対の第一のゲートに第一の信号が接続され、第二のゲートに第二の信号もしくはバイアス電圧が接続された差動増幅器において、

一端が上記共通ソースに接続され、他端が正又は負の電源に接続されたトンネル電流素子を有することを特徴とする差動増幅用トンネル電流回路。

## 【請求項 2】

実質的な定電流源にソースを共通接続したトランジスタ対と、

かかるトランジスタ対のドレインの少なくとも一方に負荷が接続され、

かかるトランジスタ対の第一のゲートに第一の信号が接続され、第二のゲートには第二の信号もしくはバイアス電圧が接続された差動増幅器において、

前記トランジスタ対のバックゲートを共通接続し、かつ、前記ゲートの少なくとも一方のゲート電位と概略等しい電位に接続することにより、かかるゲート・バックゲート間トンネル電流を抑えたことを特徴とする差動増幅用トンネル電流回路。

## 【請求項 3】

請求項 2 の「概略等しい電位」は、上記少なくとも一方のゲート電位をボルテージ・フォロア回路を介して発生させた電位であることを特徴とする差動増幅用トンネル電流回路。

## 【請求項 4】

10

20

順方向バイアスされたMOSトランジスタのゲート電位をボルテージ・フォロア回路を介し前記トランジスタのバックゲートに印加することにより、かかるトランジスタのゲート・バックゲート間トンネル電流を抑えたことを特徴とするトンネル電流回路。

## 【請求項 5】

順方向バイアスされた第一のMOSトランジスタのソース電位に、順方向バイアスされた第二のMOSトランジスタのゲート・ソース間電圧を加算した電圧を前記第一のトランジスタのバックゲートに印加することにより、かかる第一のトランジスタのゲート・バックゲート間トンネル電流を抑えたことを特徴とするトンネル電流回路。

## 【請求項 6】

少なくとも 2 個の M O S トランジスタ対からなるカレントミラー回路において、かかるトランジスタ対の共通ゲート接続端にソースが接続された第三のトランジスタを有し、かかる第三のトランジスタのゲートは前記 M O S トランジスタ対の一方のドレインに接続され、かかる第三のトランジスタのドレインは、前記トランジスタ対の共通接続されたゲート・トンネル電流を流すに足りる電位に接続されたことを特徴とするトンネル電流回路。

## 【請求項 7】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、前記差電圧が印加される第一のトンネル電流素子と、第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段を有し、上記「差電圧に比例する電圧」を発生させることを特徴とするバンドギャップリファレンス用トンネル電流回路。

## 【請求項 8】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、前記差電圧が印加される第一のトンネル電流素子と、第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流して上記「差電圧に比例する電圧」を発生させる手段と、

上記もしくは別の半導体接合に生ずる順方向電圧を、少なくとも第 3 と第 4 のトンネル電流素子の直列接続により分圧する分圧回路と、かかる分圧回路の出力電圧をバッファするアンプを有し、かかるアンプの出力を上記「半導体接合に生ずる順方向電圧に比例する電圧」とすることを特徴とするバンドギャップリファレンス用トンネル電流回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明はトンネル電流を利用したアナログ電子回路に関し、特に低消費電流バンドギャップリファレンス回路を構成する際にも有用なトンネル電流を利用したアナログ電子回路に関する。

## 【背景技術】

## 【0 0 0 2】

10

20

30

40

50

従来からバンドギャップリファレンスと称される基準電圧発生回路が知られている。これは例えばシリコン半導体PN接合(以下「接合」という)に生ずる電圧が常温で約0.7V、約-2mV/という負の温度係数を持つことと、接合に流れる電流密度を変えた対を作るとその電位差が絶対温度に比例する正の温度係数になるので、それを所定の抵抗比で増幅して前記接合の電圧と加算して温度係数を相殺する回路である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許公開2002-304224「電圧発生回路および電圧発生方法」

発明者 菅原光俊

10

【特許文献2】特願2010-235993「基準電圧発生回路」発明者 菅原光俊

【発明の概要】

【発明が解決しようとする課題】

【0004】

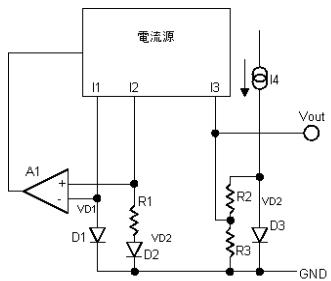

図4は特許文献1に記載した本願発明者の発明になる従来のCMOS型バンドギャップリファレンス回路であり、CMOSプロセスでも作れ、かつシリコンのバンドギャップ電圧約1.3Vよりも低電圧の温度係数がほぼゼロの基準電圧も発生できるバンドギャップリファレンス回路である。

【0005】

以下、簡単に原理と動作説明をする。

20

電流源I1により接合D1に生ずる電圧VD1の関係は

$$I_1 = I_s \times e \times p (q \times VD_1 \div (k \times T))$$

で与えられる。ここで $I_s$ はプロセスと接合の大きさで決まる飽和電流、 $q$ は電子の電荷、 $k$ はボルツマン係数、 $T$ は絶対温度である。同様に電流源I2により接合D2に生ずる電圧VD2は

$$I_2 = m \times I_s \times e \times p (q \times VD_2 \div (k \times T))$$

で与えられる。ここで $I_s$ は集積回路上ではほぼ等しく、 $m$ は電流密度比である。この二式から

$$VD_1 - VD_2 = (k \times T \div q) \times 1n (m \times I_1 \div I_2)$$

となり、絶対温度Tに比例する電圧が得られる。例えば、接合D2の面積をD1の10倍とし、 $I_1 = I_2$ とすれば、常温 $T = 300^{\circ}\text{K}$ で、 $V_1 - V_2 = 60\text{mV}$ となる。

30

【0006】

これを差動アンプA1で、その入力電圧差がゼロに近づくように負帰還をかけることにより、抵抗R1の両端が $VD_1 - VD_2$ に限りなく等しくなる。従ってオームの法則により

$$I_2 = (VD_1 - VD_2) \div R_1$$

となる。

一方、バイアス電流源I4によって接合D3に生ずる電圧VD3を、抵抗R2とR3で分圧し、そこに $I_2$ のn倍の電流I3を流入させると、テブナンの定理により、出力電圧

$$V_{out} = VD_3 \times R_3 \div (R_2 + R_3) + I_3 \times (R_2 // R_3)$$

が得られる。ここで//は抵抗の並列を示し、 $R_2 // R_3 = R_2 \times R_3 \div (R_2 + R_3)$ である。

40

$$V_{out} = VD_3 \times R_3 \div (R_2 + R_3) + R_2 \times R_3 \div (R_2 + R_3) \div R_1 \times n \times k \times T \times 1n (m) \div q$$

となる。

第一項目は接合の温度特性に比例する負の温度特性を持ち、第二項目は絶対温度に比例する正の温度係数を持つので、 $R_1, R_2, R_3, m$ を適正に選ぶことにより負、ゼロ、正の任意の温度係数を持つ電圧が得られる。

工業的にはゼロが頻繁に使われ、正や負の温度係数を補正する等の目的で用いることもある。

【0007】

50

例えば、接合D2の面積をD1の10倍とし、 $I_1 = I_2 = I_3$ ， $R_2 = R_3 = 10 \times R_1$ とすれば、 $m = 10$ ， $n = 1$ となり、常温 $T = 300^\circ K$ のとき、第一項目は接合の電圧の半分で約350mVで-1mV/となり、第二項は約300mVで+1mV/となる。合わせて約650mVで温度係数が相殺されてほぼゼロにできる。

#### 【0008】

このとき、消費電力は主に抵抗 $R_1$ と電流源の電流比によって決まり、例えば $R_1 = 6 k$ 時、 $R_1$ の両端の電位差が60mVなので、 $I_2 = 10 \mu A$ となり $I_1 + I_2 + I_3 + I_4 = 40 \mu A$ となる。電源電圧が1Vの場合40 $\mu W$ の電力を消費する。なお $R_2 = R_3 = 60 k$ である。例えば消費電力を1/10の4 $\mu W$ にする場合は、 $R_1 = 60 k$ とすれば良いが、 $R_2 = R_3 = 600 k$ となり、集積回路上に作るとき、相当に広い面積が必要となる。さらに1/10000の400 $pW$ にすることを考えると、 $R_2 = R_3 = 6 G$ が必要となり、もはや工業的にリズナブルな面積では作れないという欠点がある。

この回路に限らず、ほぼ全てのバンドギャップリファレンス回路が類似の方式なので、低消費電力化に際して同様な課題を持っている。

#### 【発明の効果】

#### 【0009】

本発明を適用すれば、高抵抗を使わずに、小さな面積でnWクラス以下の消費電力のバンドギャップリファレンス回路を提供することができる。

また本発明を適用すれば、高抵抗を使わずに、小さな面積でnWクラス以下の消費電力のシリコンのバンドギャップ電圧約1.3Vよりも低電圧の温度係数がほぼゼロの基準電圧も発生できる基準電圧発生回路を提供することができる。

さらに本発明のバンドギャップリファレンス回路内部の各回路は、高抵抗を使わずに、小さな面積でnWクラス以下の消費電力の回路として汎用的に利用できる。

#### 【課題を解決するための手段】

#### 【0010】

本発明では、抵抗の代わりに、トンネル電流を用いる。トンネル電流は絶縁物の電極間距離を10nm程度以下にすると顕著に流れ始める電流であり、原理は量子力学で説明される。トンネル電流を積極的に用いた素子として、本発明では「トンネル電流素子」と称し、これを用いた回路を「トンネル電流回路」と称する。

トンネル電流素子の第一の例として、90nm以降の集積回路プロセスで見え始めたMOS型トランジスタのゲートとバック・ゲート間に流れる「ゲート・トンネル・リーコ電流」を積極的に使うことを提唱する。トンネル電流素子として使う場合には、かかるMOS型トランジスタのドレインとソースは、実質的に動作しておらず、無くてもさしつかえない。薄いゲート絶縁膜の上側全部をトンネル素子の電極としてゲート電極と同時に形成し、かつソースやドレインのイオン注入する穴を設けぬことにより、ドレインやソースの無いトンネル素子ができる。あるいはゲート電極を一周するような電極を、ソースやドレインと一緒に形成することもできる。また、単に極めて薄い絶縁膜をはさんで導体もしくは半導体の電極が対向した素子であれば良く、このような構造をMOSトランジスタと無関係に作ることもできる。

本発明では、かかるトンネル電流がpA乃至nA程度と小さいことを利用する。

#### 【0011】

本発明のトンネル電流素子を使った基準電圧発生回路は、半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して、出力電圧とする基準電圧発生回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくはそれを直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二の複数のトンネル素子に流す手段によって、

10

20

30

40

50

上記差電圧に比例する電圧を発生させることを特徴とする。

【0012】

本発明では、上記トンネル電流素子を高精度で利用するため、それ以外の素子に生ずる不要なトンネル電流を抑制する、あるいは補償する手段も提供する。

【発明を実施するための形態】

【実施例1】

【0013】

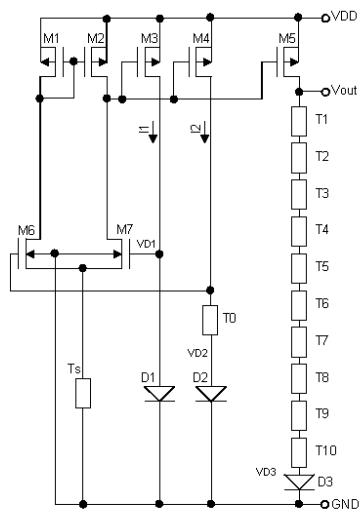

図1は、本発明の第一の実施例である。

PチャネルトランジスタM3のドレン電流をI1とするとき、接合D1に生ずる電圧VD1との関係は

$$I_1 = I_s \times e \times p (q \times VD_1 \div (k \times T))$$

で与えられる。ここで $I_s$ はプロセスと接合の大きさで決まる飽和電流、 $q$ は電子の電荷、 $k$ はボルツマン係数、 $T$ は絶対温度である。同様にPチャネルトランジスタM4のドレン電流をI2とするとき、接合D1の10倍の面積を持つ接合D2に生ずる電圧VD2との関係は

$$I_2 = 10 \times I_s \times e \times p (q \times VD_2 \div (k \times T))$$

で与えられる。この二式から

$$VD_1 - VD_2 = (k \times T \div q) \times \ln (10 \times I_1 \div I_2)$$

となり、絶対温度Tに比例する電圧が得られる。 $I_1 = I_2$ とすれば、常温 $T = 300^\circ K$ で、 $V_1 - V_2 = 60 mV$ となる。

これを、Nチャネルトランジスタ差動対M6及びM7と、Pチャネルトランジスタの能動負荷M1及びM2、等価的に電流源として動作するトンネル電流素子T<sub>s</sub>からなる差動アンプで、その差動入力電圧差がゼロに近づくように負帰還をかけることにより、トンネル電流素子T<sub>0</sub>の両端がVD1 - VD2に限りなく等しくなる。

ここまで、トンネル電流素子T<sub>s</sub>を除き、従来例と同様である。

【0014】

ここでトンネル電流素子の一例として、Pチャネルトランジスタのゲート対バックゲートを用いる。かかるトランジスタのソースとドレンは例えばバックゲートに接続しておく。こうすると既存のBSIM4等のトランジスタ・モデルを使って回路シミュレーションをすることができる。例えばゲート面積が $30 \mu m \times 30 \mu m$ の場合、プロセスにも依るが、 $60 mV$ 印加すると約 $10 pA$ 程度の電流が流れる。本実施例ではまず、トンネル電流素子T<sub>0</sub>と同じ形状のトンネル電流素子T<sub>1</sub> ~ T<sub>10</sub>を直列にし、PチャネルトランジスタM4とM5の電流を等しく設定することにより、トンネル電流素子T<sub>0</sub> ~ T<sub>10</sub>に等しい電流が流れ、それぞれのトンネル電流素子の両端の電圧は互いに等しくなる。つまりトンネル電流素子T<sub>1</sub> ~ T<sub>10</sub>の直列接続の両端には、トンネル電流素子T<sub>0</sub>の10倍の電圧が生ずる。この電圧は、従来例と同様に、約 $600 mV$ で絶対温度に比例し常温 $+2 mV / ^\circ C$ の温度特性を持つ電圧である。この電圧と、約 $-2 mV / ^\circ C$ の温度特性を持つ接合D3に生ずる順方向電圧VD3(ほぼ $0.7 V$ )とを加算し、基準電圧V<sub>out</sub>として出力する。約 $1.3 V$ で温度特性ゼロの基準電圧となる。実際にはVD3の電圧や温度係数はプロセスや電流密度で多少変わるので、それに合わせてトンネル電流素子の個数や大きさを調整し、ゼロを含む所望の温度特性の電圧が得られる値に設計する。

【0015】

消費電流は各電流が $10 pA$ 程度なので、全体で数 $10 pA$ 程度に抑えられる。消費電力も数 $10 \sim 100 pW$ 程度が実現できる。特徴的なのは、トンネル電流素子の面積を小さくすると、比例して電流が小さくなることである。従って例えば各トンネル電流素子の面積を $10 \mu m \times 10 \mu m$ とすると消費電力を $1/9$ にできる。従来例のように抵抗を使った場合、抵抗の面積と消費電流が反比例するのとは好対照である。上記のサイズや電流値等は説明のための一例であり、要求やプロセスに合わせて適宜変更できる。

【0016】

なお、トンネル電流素子以外のトランジスタのゲート・トンネル・リーク電流が気になる

10

20

30

40

50

場合、それらのトランジスタを、ゲート膜厚が厚くてトンネル電流がほとんど流れない入出力用の耐圧の高いトランジスタで作るのが簡単である。

また直列接続されるトンネル電流素子の個数は上記の例に限らず、接合D1とD2の面積比に合わせて適宜選ぶことが出来る。またPチャネルトランジスタM3とM4の比を調整して、トンネル電流素子T1～T10の直列接続の両端に生ずる電圧を調整することもできる。例えばPチャネルトランジスタM5のサイズを2倍にし、トンネル電流素子の面積も2倍にすることで、負荷の駆動能力を上げることもできる。

#### 【0017】

90nm以降の集積回路プロセスのMOSトランジスタを実測すると、トンネル電流素子の電圧Vと電流Iの関係は、 $I = V^n$ のn乗であり、nは概略2であることがわかる。任意の大きさの二つのトンネル電流素子の場合、

$$I_1 = a \cdot V_1^n$$

$$I_2 = b \cdot V_2^n$$

$I_1$ と $I_2$ が比例関係にある場合、つまり $I_2 = m \cdot I_1$ のとき、

$$b \cdot V_2^n = m \cdot a \cdot V_1^n$$

$$V_2 = (m \cdot a / b)^{1/n} \cdot V_1$$

となり、 $V_1$ と $V_2$ も比例関係にあることがわかる。

#### 【0018】

本実施例の別な形態として、トンネル電流素子T0の電極面積をT1の約4倍とする。

上記の関係を利用して、従来の抵抗比で作っていた回路を置き換えて、低消費電力化する。前項のn=2、m=1、a=4、b=1に相当し、T2の両端の電圧はT0のちょうど2倍に設定可能である。同様にT2～T5の電極面積もT1の面積と同じにすれば、T1～T5の両端の電圧はT0の10倍となるので、T6～T10を省略できる（図示せず）。これによりこの部分の面積を削減できる利点がある。この数値例に限定すること無く、端数を含む任意の電極面積比と任意の個数にすることが出来、所望の特性に調整出来る。

#### 【実施例2】

#### 【0019】

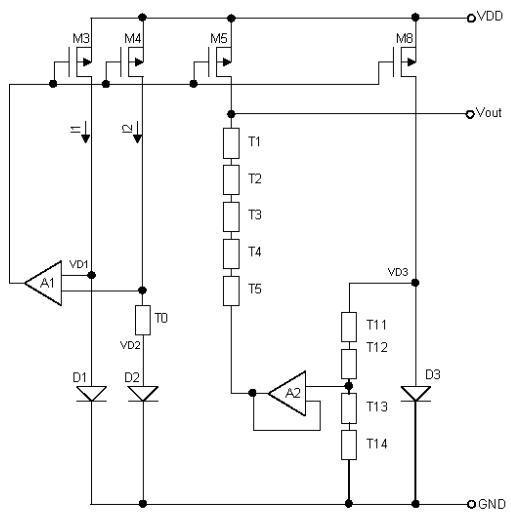

図2は、本発明の第二の実施例である。図1と同じ機能のものには同じ記号を付し、説明を省略する。PチャネルトランジスタM5のドレイン電流により、トンネル電流素子T1～T5の直列接続の両端に、トンネル電流素子T0に生ずる電圧の5倍の電圧を生ずる。

図1と同じ接合の面積比の場合、この電圧は300mVで-1mVとなる。

一方、新たに追加したPチャネルトランジスタM8によって接合D3に順方向電圧VD3を発生させ、トンネル電流素子T11～T14により2分圧し、差動アンプA2によるボルテージフォロア回路により、VD3の半分の電圧を発生させている。この電圧は約350mVで、約-1mVの温度特性である。この電圧と前記トンネル電流素子T1～T5の直列接続の両端に生じた電圧の和が出力端子Voutに生ずる。その電圧は約650mVで、温度係数は相殺されほぼゼロになる。

#### 【0020】

分圧比を1/3や2/3等任意に選ぶことも可能であり、その場合は接合の面積比と直列接続するトンネル電流素子の個数やサイズの比を適宜選択して、所望の出力電圧や温度係数を実現可能である。

#### 【0021】

本実施例では、従来より桁違いに省電力で、かつ電源電圧がわずか1Vでも動作し、バンドギャップリファレンスの半分の電圧が得られる。トランジスタM3、M4、M5、およびM8の比を1:1:1:1とすると、わずか40pWの消費電力である。

#### 【実施例3】

#### 【0022】

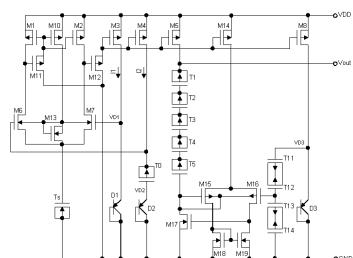

図3は、本発明の第二の実施例をトランジスタ・レベルで記載した実施例である。図2と同じ機能のものには同じ記号を付し、説明を省略する。ここではすべてゲートのトンネル電流が無視できないトランジスタを使う例を示す。PNPトランジスタQ1、Q2および

10

20

30

40

50

Q 3 はそれぞれベースとコレクタが接続されており、等価接合として動作することが知られている。特に CMOS プロセスでは追加コスト無しで、基板をコレクタとし、N ウェルをベースとし、P チャネルトランジスタのソースやドレインのための拡散層をエミッタとする PNP トランジスタを作れるので、これを利用した例である。

【 0 0 2 3 】

PNP トランジスタ Q 3 に発生させた順方向電圧 VD 3 を、トンネル電流素子 T 11 ~ T 14 により 2 分圧している。ここで T 11 と T 12 を逆方向にしてつなぐことにより、両者間のバックゲートを同一の N ウェルとすることで接続でき、バックゲートの引き出し電極と両者をつなぐ配線を省略できる。ドレインも共通にすることができる。T 13、T 14 も同様である。これらにより、さらに小型にできる。

10

なお 0018 項で述べた式を使い、トンネル電流素子のサイズや個数を適宜選ぶことにより、任意の分圧が可能である。

【 0 0 2 4 】

差動アンプ A 2 は、P チャネルトランジスタ M 15 と M 16 からなる差動対と、N チャネルトランジスタ M 18 と M 19 からなる能動負荷と、N チャネルトランジスタ M 17 からなるソース接地回路から構成されている。

差動アンプ A 2 は、ボルテージフォロアとして動作するので、トランジスタ M 15 と M 16 のゲートとトランジスタ M 17 のドレインはほぼ同電位となっており、トランジスタ M 15 と M 16 のバックゲートはそこに接続されている。このため、トランジスタ M 15 と M 16 は、どちらもゲートとバックゲート間がほぼ 0 V となり、これらの間の電流は全く流れない。つまりこれらのトランジスタのゲート・トンネル電流をゼロにすることができます。

20

【 0 0 2 5 】

P チャネルトランジスタ M 15 のドレイン電流は、N チャネルトランジスタ M 18 のドレイン電流となる他、N チャネルトランジスタ M 18 と M 19 のゲート・トンネル電流としても供給される。これを補償するために、N チャネルトランジスタ M 17 のゲート・トンネル電流を後者とほぼ等しくなるように設定する。具体的には、N チャネルトランジスタ M 17 のゲート面積を、N チャネルトランジスタ M 18 と M 19 の和とほぼ等しくし、かつ、これらすべての電流密度を等しくする。これによりこれら三つのトランジスタのゲート・バックゲート間電圧は等しくなり、ゲート・バックゲート間トンネル電流をそろえ、P チャネルトランジスタ M 15 と M 16 のバランス時のドレイン電流を等しく流し出すことができる。

30

【 0 0 2 6 】

差動アンプ A 1 の主要部は、N チャネルトランジスタ M 6 と M 7 からなる差動対と、P チャネルトランジスタ M 1 と M 2 からなる能動負荷と、概略定電流源とみなされるトンネル電流素子 T s で構成される。

トンネル電流素子 T s は、N チャネルトランジスタのゲートとバックゲート間を用いると、サブストレート部に作ることができ、P チャネルトランジスタで作るより小型にできる。

40

【 0 0 2 7 】

定電流源として動作する P チャネルトランジスタ M 10 と、ダイオードとして動作する N チャネルトランジスタ M 13 によって、N チャネルトランジスタ M 6 と M 7 からなる差動対の共通ソース電圧より VGS 高い電圧を作り出している。この電圧は概略 N チャネルトランジスタ M 6 と M 7 の両ゲート電圧と等しいので、この電圧でこれらの共通バックゲートをバイアスする。これによりこれらのトランジスタのベースとバックゲート間電圧はほぼ 0 V となり、ゲート・トンネル電流は流れない。なお N チャネルトランジスタのバックゲートをサブストレートと異なる電位にバイアスするためには、ディープ N ウェルという工程を用いるのが一般的だが、これに限定されない。

【 0 0 2 8 】

P チャネルトランジスタ M 1 、 M 2 と M 10 からなる回路のゲート・トンネル電流による

50

バランス劣化を補償するため、PチャネルトランジスタM11を挿入している。PチャネルトランジスタM11のソース電流は、PチャネルトランジスタM1、M2とM10のゲート・トンネル電流のみのため、小さな値である。よってPチャネルトランジスタM11をできるだけ小さくすることができ、ゲート・トンネル電流を抑えることができる。

【0029】

PチャネルトランジスタM12は、後段の電流源PチャネルトランジスタM3、M4、M5、M14とM8のゲート・トンネル電流の影響を補償するために挿入したものである。このPチャネルトランジスタM12と上記PチャネルトランジスタM11のゲート・トンネル電流を概略等しくするように電流値やゲート寸法を設計することにより、さらにバランスを高めることができる。

10

【0030】

本実施例では、上記の幾つもの発明を適用することにより、回路内の不要なゲート・トンネル電流による影響を相殺したり、抑えたりすることにより、ゲート・トンネル電流が無視できないトランジスタを使っても、精度を劣化させずにバンドギャップリファレンス回路が構成できることを示した。

必要に応じ、起動回路を付したり、アンプA1やA2に発振対策をすることがある。

【産業上の利用可能性】

【0031】

本発明では、従来より4桁小さい1nA以下でバンドギャップリファレンス回路を、従来並みの大きさで構成することができる。と同時に、差動アンプ、カレントミラーや能動負荷、分圧等で、トンネル電流を応用したり、不要なトンネル電流の影響を補償することを広く応用することにより、他のアナログ回路も低電力化することができる。

20

これにより電池で動かすポータブル機器の稼働時間を飛躍的に伸ばすことができる。電池のみならず、磁界や電界や光発電や接触電位等による微弱な電源を利用することも可能となり、電池無でんやお生体内に埋め込む機器等へも応用できる。

【0032】

なお、本発明は実施例として例示したものに限定することなく、一部を切り出して実施したり、任意に組み合わせて実施することも可能である。

【図面の簡単な説明】

30

【0033】

【図1】第一の実施例で、消費電力の少ない約1.3Vで温度係数ゼロの基準電圧発生回路

【図2】第二の実施例で、消費電力の少ない約650mVで温度係数ゼロの基準電圧発生回路

【図3】第三の実施例で、図2の基準電圧発生回路をトランジスタ・レベルで記載したもの

【図4】従来例で、特許文献1に記載された回路図

【符号の説明】

【0034】

T1～T14、Ts

トンネル電流素子

D1～D3

半導体接合

M1～M19

トランジスタ

I0～I4

電流源

R1～R3

抵抗

A1、A2

差動アンプ

VDD

電源

GND

接地

Vout

出力端子

40

【 図 1 】

图 1

【 図 2 】

图2

【図3】

図3

【図4】

4

---

フロントページの続き

(56)参考文献 特開平07-079154(JP,A)

特開2002-064150(JP,A)

特開2004-147175(JP,A)

米国特許出願公開第2003/0107431(US,A1)

特開2005-204297(JP,A)

特開2008-178083(JP,A)

特開2004-085526(JP,A)

特開2002-304224(JP,A)

特開2012-088978(JP,A)

(58)調査した分野(Int.Cl., DB名)

G05F 3/24-3/30

H01L 21/822

H01L 27/04

H03F 3/34-3/347

H03F 3/45