(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 08 310 T2 2006.07.27

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 308 958 B1

(21) Deutsches Aktenzeichen: 602 08 310.9

(96) Europäisches Aktenzeichen: 02 257 425.5

(96) Europäischer Anmeldetag: 25.10.2002

(97) Erstveröffentlichung durch das EPA: 07.05.2003

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 28.12.2005

(47) Veröffentlichungstag im Patentblatt: 27.07.2006

(51) Int Cl.<sup>8</sup>: G11C 8/12 (2006.01)

H01L 21/822 (2006.01)

H01L 25/065 (2006.01)

(30) Unionspriorität:

**984934** 31.10.2001 US

(84) Benannte Vertragsstaaten:

**DE, GB**

(73) Patentinhaber:

**Hewlett-Packard Development Co., L.P., Houston,

Tex., US**

(72) Erfinder:

**Tran, Lung T., Saratoga, US; Anthony, Thomas C.,

Sunnyvale, US**

(74) Vertreter:

**Schoppe, Zimmermann, Stöckeler & Zinkler, 82049

Pullach**

(54) Bezeichnung: Dreidimensionaler grosser Speicher mit wahlfreiem Zugriff

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung**

**[0001]** Diese Erfindung bezieht sich allgemein auf Speichervorrichtungen. Insbesondere bezieht sich die Erfindung auf dreidimensionale Großspeicher-Direktzugriffsspeichervorrichtungen.

**[0002]** Die folgenden Patentanmeldungen enthalten einen verwandten Gegenstand und sind hierin durch Bezugnahme aufgenommen:

**[0003]** Europäische Patentanmeldungen 02256632.7, 02256631.9, 02255452.1 und U.S.-Patentanmeldung mit der Serien-Nr. 09/924,500 mit dem Titel „ONE-TIME PROGRAMMABLE UNIT MEMORY CELL BASED ON VERTICALLY ORIENTED FUSE AND DIODE AND ONE-TIME PROGRAMMABLE MEMORY USING THE SAME“ (Einmalig programmierbare Einheitsspeicherzelle basierend auf vertikal ausgerichteter Sicherung und Diode und einmalig programmierbarer Speicher unter Verwendung derselben) (Anwaltssaktenzeichen 10019168-1).

**[0004]** Es besteht ein ständig ansteigender Bedarf nach einer dichten und großen Speicherkapazität in Vorrichtungen, wie z. B. Computern, Kommunikationsausrüstungen, Verbraucherelektronik, usw. Dies hat zu großen Verbesserungen bei der Speicherung und der Leistung von Datenspeichervorrichtungen, wie z. B. Festplattenlaufwerken, Festkörperspeichern, usw., geführt. In Festplattenlaufwerken haben kleine Formfaktoren in Verbindung mit einer starken Verbesserung einer Flächendichte die Entwicklung von Plattenlaufwerken mit hoher Kapazität erlaubt.

**[0005]** In integrierten Schaltungen hat die Entwicklung von Mehrchipmodulen (MCM) und Hybrid-Herstellungstechniken zu einer starken Größenreduzierung geführt und in einigen Fällen eine Leistung des letztendlichen Produkts verbessert. Eine häufig verwendete MCM-Konfiguration für die dynamischen Direktzugriffsspeicher (DRAM) sind die einreihigen Speichermodule (SIMMs; SIMM = single-in-line memory module). Gegenwärtig sind viele Speicherspeicherungsvorrichtungen auf eine einzelne Schicht eingeschränkt. Dies ist allgemein aufgrund zweier Faktoren so. Erstens benötigt ein aktiver Schaltungsaufbau Silizium als das Basismaterial zur Unterstützung der Funktionsweise des Speichers, wie z. B. zum Lesen und Schreiben. Zum Lesen und Schreiben sind Adressdecodierer, Lese-/Schreib-Steueroberlogik, Leseverstärker, Ausgangspuffer, Multiplexer und anderes in einem Speicherchip enthalten. Dies wird allgemein als Mehraufwand bzw. Overhead bezeichnet und verbraucht üblicherweise 20–30 des physischen Speichers. Vorzugsweise wird dieser Mehraufwand gering gehalten, so dass mehr Raum für einen Speicher verfügbar ist. Der zweite Faktor, der die Speicherspeicherungsvorrichtung auf eine Einzelarrayschicht einschränkt, sind die Leistungsdiissipierungs-

beschränkungen.

**[0006]** In jüngster Zeit wurden Mehrarrayspeicher vorgeschlagen, die auf einem Komplementärmetalloxid-Halbleiter (CMOS) hergestellt sind. Ein derartiger Ansatz jedoch erfordert eines oder mehrere Durchgangslöcher für jede Speicherschicht, so dass jede Speicherschicht einzeln mit dem aktiven Schaltungsaufbau verbunden sein kann. Dieser Ansatz könnte für einige Schichten einen sehr dichten und effizienten Speicherentwurf ergeben. Mit zunehmender Anzahl von Schichten jedoch nimmt die Anzahl von Durchgangslöchern bis zu dem Punkt zu, bei dem es schwierig wird, die Signale von Speicherarrays zu der CMOS-Schicht zu führen, und die Führungswege länger werden, derart, dass dieser Entwurf weniger effizient, komplexer wird und die Kosten ebenso ansteigen. Die Durchgangslöcher könnten klein gemacht werden, um einige der Probleme zu überwinden. Kleinere Durchgangslöcher jedoch erhöhen entsprechend das Risiko von Defekten und erhöhen die Schwierigkeit einer Ausrichtung. Zusätzlich werden Zwischenverbindungen zwischen Arrayschichten schwieriger und komplex.

**[0007]** Zusätzlich ist der Ertrag der Speichervorrichtungen relativ gering. Der geringe Ertrag hat seine Ursache in der Tatsache, dass eine einzelne Speicherschicht nicht aus einem Stapel von Schichten aussortiert und zurückgewiesen werden kann. Zur Darstellung ist, wenn eine einzelne Speicherschicht eine Wahrscheinlichkeit  $p(x)$ , defekt zu sein, aufweist, ohne weiteres ersichtlich, dass ein MCM-Speicher, der aus mehreren Schichten hergestellt ist, eine Wahrscheinlichkeit, zumindest eine defekte Schicht aufzuweisen, aufweist, die größer ist als  $p(x)$ . Aufgrund der Unfähigkeit eines Aussortierens und Zurückweisens von Defekten auf einer vereinzelten Speicherschichtebene leidet die Gesamtqualität der Speichervorrichtung und so ist der Ertrag niedrig.

**[0008]** Die US 2001-0017798 offenbart eine Speicherzellebene mit einer Mehrzahl von Speicherarrays und Arrayauswahlleitungen, wobei die Speicherzelle über eine aktive Schaltungsebene gestapelt ist, jedoch ohne Ebenenauswahlleitung, entsprechenden Bus und ohne Seitenkontaktanschlussflächen.

**[0009]** Die WO-99-63527 offenbart Speicherebenen mit Seitenkontakte, die Zeilen- und Spaltensignale tragen, die über eine aktive Ebene gestapelt sind, jedoch ohne Mehrzahl von Speicherarrays, ohne Arrayauswahlleitungen, ohne Ebenenauswahlleitungen und ohne entsprechende Busse, die mit der aktiven Schicht verbunden sind. Dieses Dokument offenbart außerdem Seitenkontaktanschlussflächen.

**[0010]** Die WO-95-09438 offenbart eine Speicherebene, die über eine aktive Ebene gestapelt ist, jedoch

ohne Mehrzahl von Speicherarrays, ohne Arrayauswahlleitungen, ohne Ebenenauswahlleitungen, ohne entsprechende Busse, die mit der aktiven Schicht verbunden sind, und ohne Seitenkontaktanschlussflächen.

**[0011]** Die EP-1-017-100 offenbart Speicherzellebenen, die über eine aktive Schaltungsebene gestapelt sind, jedoch ohne Mehrzahl von Speicherarrays, ohne Arrayauswahlleitungen, ohne Ebenenauswahlleitungen, ohne entsprechende Busse, die mit der aktiven Schicht verbunden sind, und ohne Seitenkontaktanschlussflächen.

**[0012]** Die US-5-483-488 offenbart eine Speicherebene mit einer Mehrzahl von Speicherarrays, mit einer Ebenenauswahlleitung und Arrayauswahlleitungen. Dieses Dokument offenbart keine aktive Schaltungsebene, die mit dem Datenbus verbunden ist, keinen Ebenenauswahlbus und Arrayauswahlbus und Seitenkontaktanschlussflächen zur Verbindung dieser Busse mit den Signalleitungen der Speicherebene.

**[0013]** Gemäß einem ersten Aspekt der Erfindung ist die Speichervorrichtung durch Anspruch 1 definiert.

**[0014]** In einer Hinsicht könnte ein exemplarisches Ausführungsbeispiel eines Speicherarrays ein nicht-silizium-basiertes Substrat umfassen. Das Speicherarray könnte außerdem einen Zeilenleiter, der über dem nicht-silizium-basierten Substrat gebildet ist und sich in einer Zeilenrichtung erstreckt, und einen Spaltenleiter umfassen, der über dem nicht-silizium-basierten Substrat gebildet ist und sich in einer Spaltenrichtung erstreckt, derart, dass ein Kreuzungspunkt an einem Schnittpunkt zwischen dem Zeilenleiter und dem Spaltenleiter gebildet wird. In dem Kreuzungspunkt könnte eine Speicherzelle gebildet sein. Das Speicherarray könnte ferner eine Arrayfreigabeschaltung umfassen, die geschaltet ist, um zumindest einen des Zeilenleiters und des Spaltenleiters freizugeben/zu sperren.

**[0015]** In anderer Hinsicht könnte ein exemplarisches Ausführungsbeispiel einer Speicherebene ein nicht-silizium-basiertes Substrat und eines oder mehrere Speicherarrays umfassen, die über dem nicht-silizium-basierten Substrat gebildet sind. Jedes Speicherarray könnte einen Zeilenleiter, der sich in einer Zeilenrichtung erstreckt, und einen Spaltenleiter umfassen, der sich in einer Spaltenrichtung erstreckt, derart, dass ein Kreuzungspunkt an einem Schnittpunkt zwischen dem Zeilenleiter und dem Spaltenleiter gebildet ist. Jedes Speicherarray könnte außerdem eine Speicherzelle, die in dem Kreuzungspunkt gebildet ist, und eine Arrayfreigabeschaltung umfassen, die geschaltet ist, um zumindest einen des Zeilenleiters und des Spaltenleiters freizugeben/zu sperren,

ren.

**[0016]** In anderer Hinsicht könnte ein exemplarisches Ausführungsbeispiel einer Speichervorrichtung eine Aktivschaltungsebene, z. B. eine CMOS-Schaltungsebene, und eine oder mehrere Schaltungsebenen, die über der aktiven Schaltungsebene gebildet sind, umfassen. Jede Speicherebene könnte ein nicht-silizium-basiertes Substrat und eines oder mehrere Speicherarrays, die über dem nicht-silizium-basierten Substrat gebildet sind, umfassen. Jedes Speicherarray jeder Speicherebene könnte einen Zeilenleiter, der sich in einer Zeilenrichtung erstreckt, und einen Spaltenleiter, der sich in einer Spaltenrichtung erstreckt, umfassen, derart, dass ein Kreuzungspunkt an dem Schnittpunkt zwischen dem Zeilenleiter und dem Spaltenleiter gebildet ist. Jedes Speicherarray könnte auch eine Speicherzelle, die in dem Kreuzungspunkt gebildet ist, und eine Arrayfreigabeschaltung umfassen, die geschaltet ist, um zumindest einen des Zeilenleiters und des Spaltenleiters freizugeben/zu sperren.

**[0017]** In wiederum anderer Hinsicht könnte ein exemplarisches Ausführungsbeispiel eines Verfahrens zum Herstellen einer Speichervorrichtung ein Bilden einer Aktivschaltungsebene und ein Bilden einer oder mehrerer Speicherebenen über der Aktivschaltungsebene umfassen. Das Verfahren könnte außerdem ein Bilden eines nicht-silizium-basierten Substrats für jede Speicherebene umfassen. Für jede Speicherebene könnte es ferner ein Bilden eines oder mehrerer Speicherarrays über dem Nicht-Silizium-Substrat umfassen. Zusätzlich könnte das Verfahren für jedes Speicherarray ein Bilden eines Zeilenleiters, der sich in einer Zeilenrichtung erstreckt, und ein Bilden eines Spaltenleiters, der sich in einer Spaltenrichtung erstreckt, umfassen, derart, dass ein Kreuzungspunkt an einem Schnittpunkt zwischen dem Zeilenleiter und dem Spaltenleiter gebildet wird. Das Verfahren könnte ferner ein Bilden einer Speicherzelle in dem Kreuzungspunkt und ein Bilden einer Arrayfreigabeschaltung, die geschaltet ist, um zumindest einen des Zeilenleiters und des Spaltenleiters für jedes Speicherarray freizugeben/zu sperren, umfassen.

**[0018]** Die oben offenbarten Ausführungsbeispiele der vorliegenden Erfindung könnten in der Lage sein, bestimmte Aspekte zu erreichen. Die Speichervorrichtung könnte z. B. mit einem Stapeln mehrerer Ebenen von Speicherarrays hergestellt werden, wobei jede Ebene einzeln hergestellt wird. Dies beseitigt den Bedarf einer Herstellung von Durchgangslöchern und so wird die relative Komplexität der Vorrichtung reduziert. Außerdem könnte jedes Array einzeln freigegeben und gesperrt werden, z. B. durch eine Arrayauswahlleitung. So könnten defekte Arrays und/oder Ebenen vor einer Fertigstellung der Vorrichtung aussortiert werden, was zu erhöhtem Ertrag und erhöhter Qualität führt. Ferner könnten, da die Spei-

cherebenen separat von dem aktiven Schaltungsaufbau hergestellt werden könnten, Substrate der Speicherebenen aus anderen Materialien als Silizium gebildet werden. Ferner könnten Speicherebenen ohne Beinhaltung von Mehraufwand, wie z. B. Lese-/Schreib-Steuerlogik, Leseverstärkern, Ausgangspuffern und Multiplexern, hergestellt werden, was die Kapazität erhöht, indem mehr Raum für einen Speicher reserviert werden kann. Ferner erlaubt ein Stapeln die Erzielung einer sehr hohen Kapazität. Zusätzlich könnte der Speicher flüchtig, nicht-flüchtig, direktzugriffsmäßig oder einmalig programmierbar sein.

**[0019]** Merkmale und Vorteile der Erfindung werden für Fachleute auf diesem Gebiet aus der folgenden Beschreibung Bezug nehmend auf die Zeichnungen ersichtlich werden:

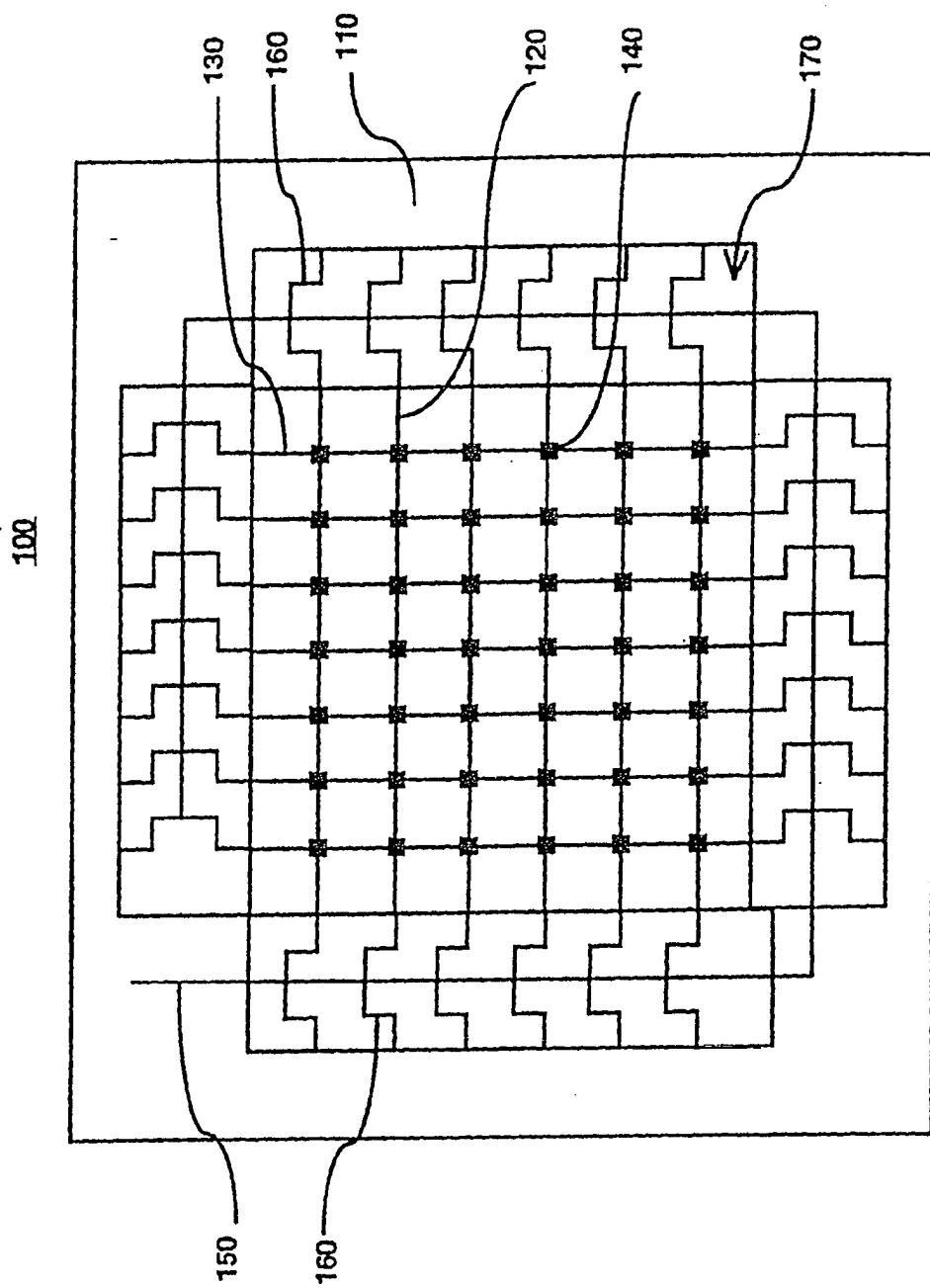

**[0020]** [Fig. 1A](#) stellt ein exemplarisches Ausführungsbeispiel eines Speicherarrays gemäß den Prinzipien der Erfindung dar;

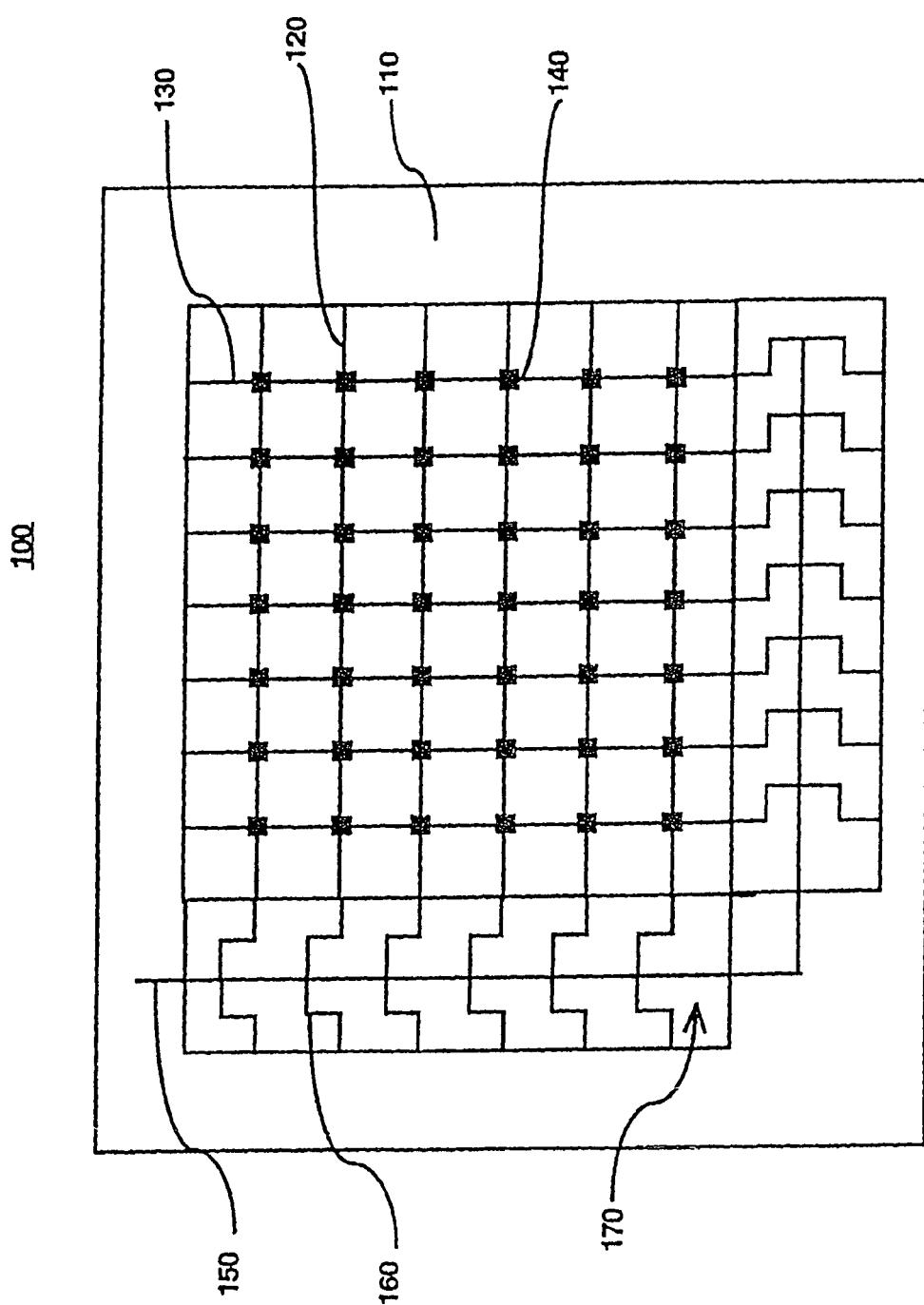

**[0021]** [Fig. 1B](#) stellt ein zweites exemplarisches Ausführungsbeispiel eines Speicherarrays gemäß den Prinzipien der Erfindung dar;

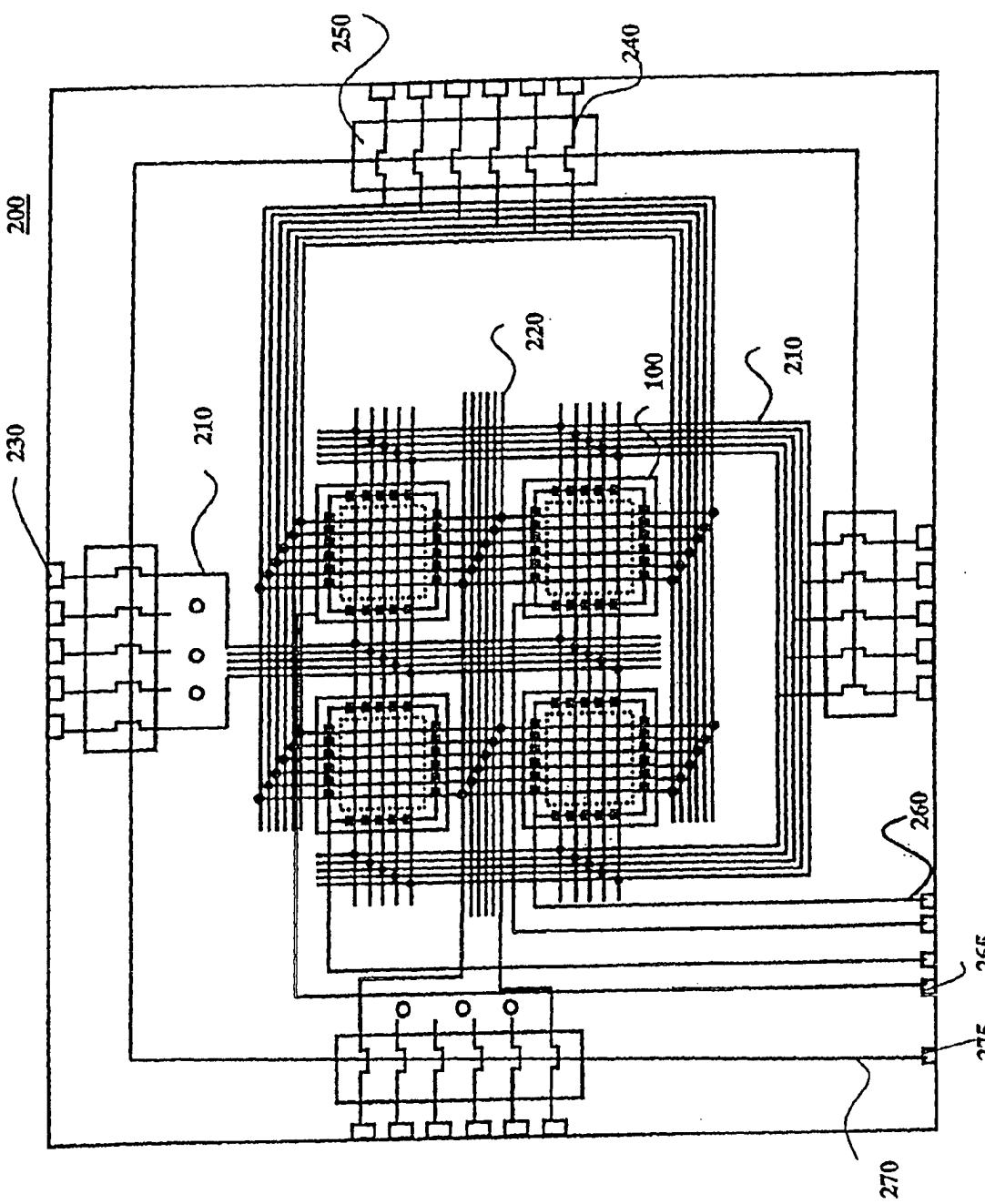

**[0022]** [Fig. 2](#) stellt ein exemplarisches Ausführungsbeispiel einer Speicherebene gemäß den Prinzipien der Erfindung dar;

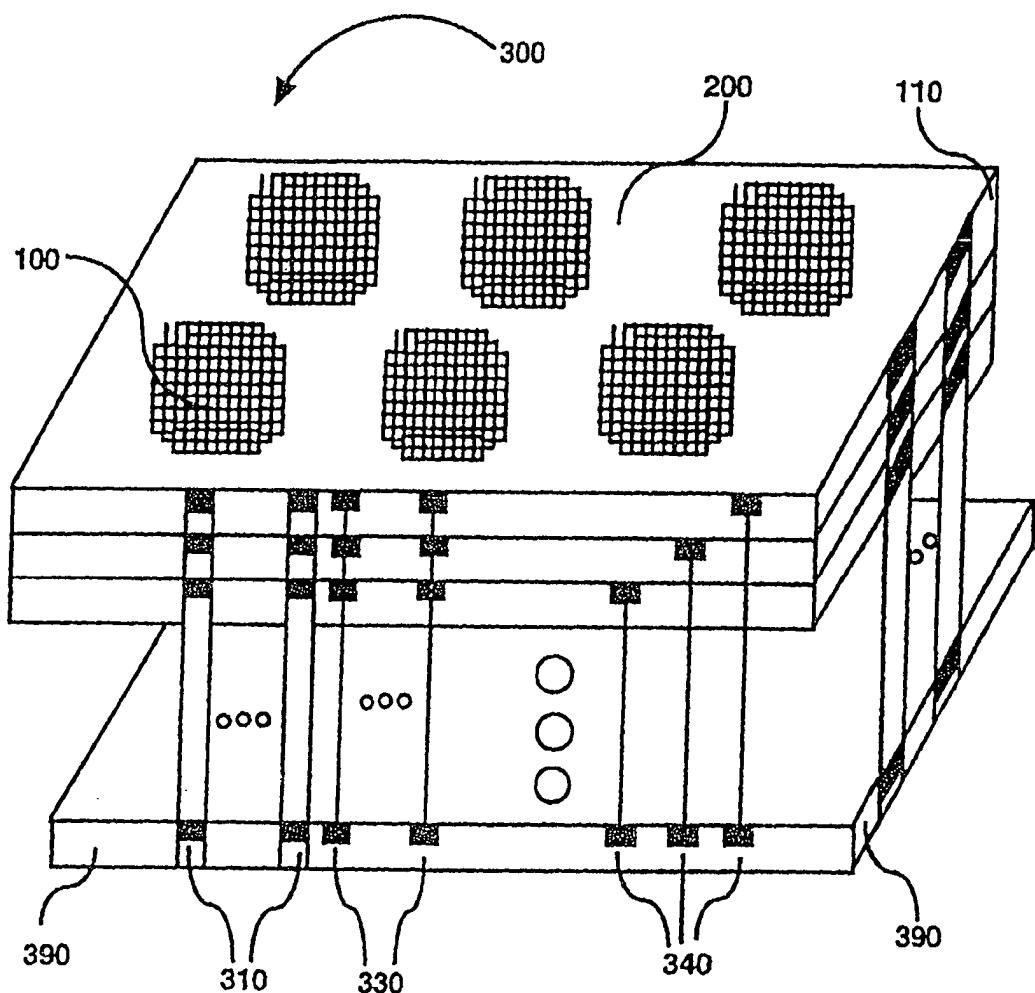

**[0023]** [Fig. 3](#) stellt ein exemplarisches Ausführungsbeispiel einer Speichervorrichtung gemäß den Prinzipien der Erfindung dar; und

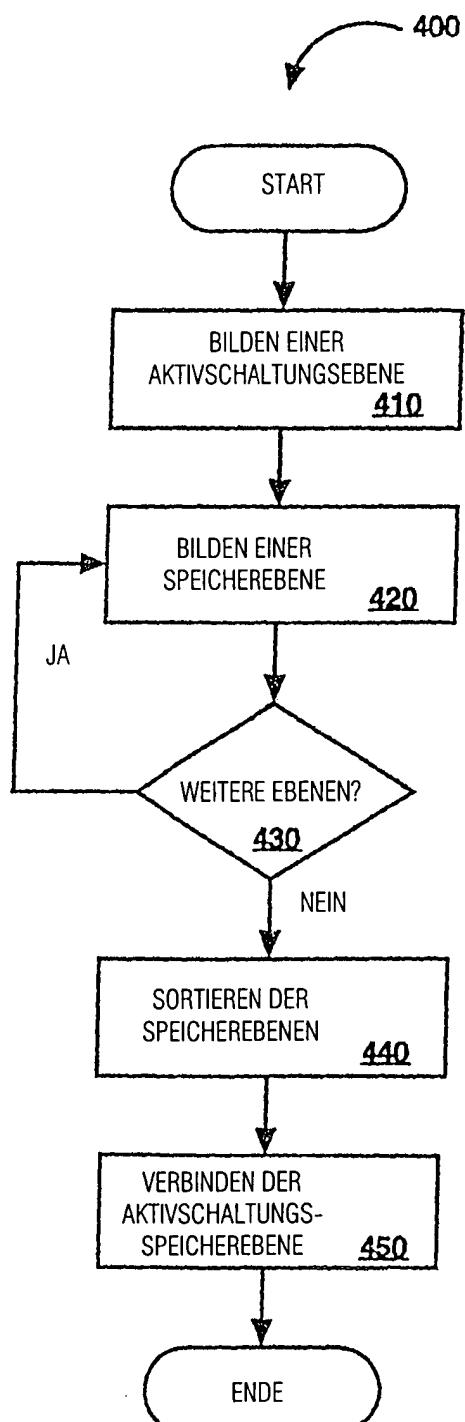

**[0024]** [Fig. 4](#) ist ein Flussdiagramm, das ein exemplarisches Verfahren zur Herstellung der Speichervorrichtung aus [Fig. 3](#) gemäß einem Aspekt der vorliegenden Erfindung darstellt.

**[0025]** Für eine Einfachheit und zu Darstellungs-zwecken sind die Prinzipien der Erfindung hauptsächlich Bezug nehmend auf exemplarische Ausführungsbeispiele derselben beschrieben. Ein Fachmann auf diesem Gebiet jedoch würde ohne weiteres erkennen, dass die gleichen Prinzipien gleichermaßen auf viele Typen von Festkörperspeichern und Verfahren zur Herstellung und Verwendung derselben anwendbar sind.

**[0026]** Gemäß den Prinzipien der Erfindung könnte ein Herstellen mehrerer Schichten von Speicherarrays aufeinander die Kapazität einer Speichervorrichtung erhöhen. Bei einem Aspekt der Erfindung könnten Ebenen von Speicherarrays gestapelt werden, um eine dreidimensionale (3-D-)Speichervorrichtung zu bilden. Jede Ebene könnte eines oder mehrere Speicherarrays beinhalten.

**[0027]** [Fig. 1A](#) stellt ein exemplarisches Ausfüh-

rungsbeispiel eines Speicherarrays **100** gemäß den Prinzipien der Erfindung dar. Wie in [Fig. 1A](#) gezeigt ist, könnte das Speicherarray **100** ein Substrat **110** umfassen. Das Substrat **110** könnte z. B. auf Silizium- oder auf Nicht-Silizium-Basis sein. Beispiele eines nicht-silizium-basierten Substrats umfassen Materialien aus Kunststoff, Glas, Keramiken, Nicht-Metallen, wie z. B. elektrische Isolatoren, und dergleichen.

**[0028]** Über dem Substrat **110** könnten einer oder mehrere Zeilenleiter **120** und einer oder mehrere Spaltenleiter **130** gebildet sein. Die Zeilen- und Spaltenleiter **120** und **130** könnten sich in einer Zeilenrichtung bzw. einer Spaltenrichtung erstrecken, um einen Kreuzungspunkt an jedem Schnittpunkt zu bilden. An einem Kreuzungspunkt könnte eine Speicherzelle **140** gebildet sein. Jede Speicherzelle **140** könnte einzeln durch den jeweiligen Zeilen- bzw. Spaltenleiter **120** und **130** adressierbar sein. Die Speicherzelle **140** könnte nur-lesemäßig, direkt zugänglich oder einmalig programmierbar sein, wobei so das Speicherarray **100** ein Nur-Lese-Speicher (ROM), ein Direktzugriffspeicher (RAM) bzw. ein einmalig programmierbarer Speicher (OTP) sein könnte. Die Speicherzelle **140** könnte z. B. eine Sicherungsspeicherzelle, eine Sicherungs-/Diodenspeicherzelle, eine Sicherungs-/Antisicherungsspeicherzelle, eine magnetische Speicherzelle, eine Dioden-Speicherzelle, eine Magnet-/Diodenspeicherzelle, eine Phasenänderungs-Speicherzelle, eine Resistivelementzelle und dergleichen sein.

**[0029]** Das Speicherarray **100** könnte auch eine Arrayfreigabeschaltung **170** umfassen. Die Arrayfreigabeschaltung **170** könnte einen oder mehrere Arrayfreigabentransistoren **160** umfassen. Vier Gruppen von Arrayfreigabetransistoren **160** sind z. B. in [Fig. 1A](#) gezeigt. Jeder Zeilen- oder Spaltenleiter **120** bzw. **130** könnte mit einem oder mehreren Arrayfreigabetransistoren **160** verbunden sein. Wie in [Fig. 1A](#) gezeigt ist, könnte jeder Zeilen- oder Spaltenleiter **120** bzw. **130** z. B. mit zwei Arrayfreigabetransistoren **160** an beiden Enden verbunden sein. Eine Leitung durch den Zeilenleiter **120** oder den Spaltenleiter **130** wird durch ein Steuern der Arrayfreigabetransistoren **160** freigegeben oder gesperrt. Die Arrayfreigabetransistoren **160** könnten aus Mikrokristallin-Silizium-Transistoren, Amorph-Silizium-Transistoren oder anderen Freigabeschaltern, die kein Siliziumsubstrat benötigen, gebildet sein.

**[0030]** Das Speicherarray **100** könnte ferner eine Arrayauswahlleitung **150** umfassen, die mit den Arrayfreigabetransistoren **160** verbunden ist. Durch ein Steuern des Signals zu der Arrayauswahlleitung **150** könnte das Speicherarray **100** ausgewählt oder gesperrt werden. Üblicherweise ist in einer Mehrarray-Einstellung eine einzelne Arrayleitung **150** reserviert für ein Array **100** und wird nicht gemeinschaftlich

mit einem anderen Array **100** verwendet.

**[0031]** Es wird angemerkt, dass es nicht nötig ist, dass beide Enden des Zeilen- oder des Spaltenleiters **120** oder **130** mit dem Arrayfreigabetransistor **160** verbunden sind. [Fig. 1B](#) stellt ein zweites exemplarisches Ausführungsbeispiel eines Speicherarrays gemäß den Prinzipien der Erfindung dar. Wie gezeigt ist, ist nur eines der Enden der Zeilen- bzw. Spaltenleiter **120** und **130** mit den Arrayfreigabetransistoren **160** verbunden. Andere Konfigurationen als [Fig. 1A](#) und [Fig. 1B](#) sind möglich, ohne von dem Schutzbereich der Erfindung abzuweichen.

**[0032]** Unabhängig davon, ob das Speicherarray **100** auf Siliziumoder Nicht-Silizium-Basis ist, lohnt sich die Anmerkung, dass das Speicherarray keinen Mehraufwand, wie z. B. Leseverstärker, Ausgangspuffer, Decodierer, Multiplexer und dergleichen, umfassen muss. Eine einzelne Aktivschaltungsaufbauschicht könnte die Speicherortauswahlen, Leseverstärker und Lese-/ und Schreibsteuerungen bereitstellen.

**[0033]** Während einzelne Speicherarrays **100** gestapelt sein könnten, um eine 3-D-Speichervorrichtung zu bilden, könnten Ebenen von Speicherarrays gemäß einem anderen Aspekt der vorliegenden Erfindung hergestellt sein. Die Ebenen von Speicherarrays könnten dann sortiert und gestapelt werden, um eine 3-D-Speichervorrichtung zu bilden, was die Speicherkapazität der Vorrichtung relativ erhöht.

**[0034]** [Fig. 2](#) stellt ein exemplarisches Ausführungsbeispiel einer Speicherebene **200** gemäß den Prinzipien der Erfindung dar. Wie in [Fig. 2](#) gezeigt ist, könnte die Speicherebene **200** eines oder mehrere Speicherarrays **100** umfassen, z. B. die Speicherarrays **100** der [Fig. 1A](#) und [Fig. 1B](#), die über dem Substrat **110** gebildet sind (nicht gezeigt). Wieder könnte das Substrat **110** auf Silizium- oder Nicht-Silizium-Basis sein. Die Speicherebene **200** könnte außerdem einen oder mehrere Zeilenbusse **210** und einen oder mehrere Spaltenbusse **220** umfassen. Die Zeilenbusse **210** könnten eine elektrische Verbindung zu den Zeilenleitern **120** (nicht beschriftet) der Speicherarrays **100** herstellen. Ähnlich könnten die Spaltenbusse **220** eine elektrische Verbindung zu den Spaltenleitern **130** (ebenso nicht beschriftet) der Speicherarrays **100** herstellen. Durch die Zeilen- und Spaltenbusse **210** und **220** könnte eine einzelne Speicherzelle **140** (in [Fig. 2](#) nicht gezeigt) einzelner Speicherarrays **100** adressiert werden.

**[0035]** Die Speicherebene **200** könnte ferner eine Ebenenfreigabeschaltung **250** umfassen. Die Ebenenfreigabeschaltung **250** könnte einen oder mehrere Ebenenfreigabetransistoren **240** umfassen. Vier Gruppen von Ebenenfreigabetransistoren **240** sind z. B. in [Fig. 2](#) gezeigt. Ein Datenfluss zu und von den

Zeilen- und Spaltenbussen **210** und **220** und folglich von den Speicherzellen **140** (in [Fig. 2](#) nicht gezeigt) der Speicherarrays **100** könnte durch ein Steuern der Ebenenfreigabetransistoren **240** freigegeben oder gesperrt werden. Der Ebenenfreigabetransistor **240** könnte aus einem Mikrokristallin-Dünnfilm-Transistor, einem amorphen Dünnfilm-Transistor oder jedem Freigabeschalter, der kein Siliziumsubstrat benötigt, gebildet sein.

**[0036]** Eine Ebenenauswahlleitung **270** könnte in der Specherebene **200** enthalten sein, in der die Ebenenauswahlleitung **270** mit den Ebenenfreigabetransistoren **240** verbunden ist. Auf diese Weise könnte die Specherebene **200** durch ein Steuern des Signals zu der Ebenenauswahlleitung **270** freigegeben oder gesperrt werden.

**[0037]** Die Specherebene **200** könnte ferner eine oder mehrere Datenseitenkontaktanschlussflächen **230** umfassen. Die Datenseitenkontaktanschlussflächen **230** könnten eine elektrische Verbindung zu den Zeilen- und Spaltenbussen **210** und **220** über die Ebenenfreigabetransistoren **240** herstellen. Die Specherebene **200** könnte so hergestellt sein, dass, wenn mehrere Specherebenen **200** gestapelt sind, die Datenseitenkontaktanschlussflächen **230** der Specherebenen **200** für den nächsten Leitervorgangsschritt ausgerichtet sind, um Datenbusse **310** zu bilden (siehe [Fig. 3](#)). Auf diese Weise könnte der Bedarf einer Herstellung der Zwischenverbindungs-durchgangslöcher zwischen Ebenen beseitigt werden und die relative Komplexität der Vorrichtung könnte reduziert werden.

**[0038]** Es wird angemerkt, dass die Arrayauswahlleitung **150** einzelner Speicherarrays **100** zusammengehen könnten, um eine Mehrzahl von Arrayauswahlleitungen **240** zu bilden. Die Specherebenen **200** und die Aktivschaltungsebene **390** könnten so hergestellt sein, dass, wenn mehrere Specherebenen **200** zusammen gestapelt sind, die Datenseitenkontaktanschlussflächen **230** ausgerichtet sind, die die Zwischenverbindung mehrerer Specherebenen und der Aktivschaltungsebene erleichtern. Ein Aufbringungs-, Plattierungs- oder Siebdruckleiterverfahrensschritt könnte für die Zwischenverbindungen und zur Bildung des Arrayauswahlbus **330** verwendet werden (siehe [Fig. 3](#)). Da die Leiter des Arrayauswahlbus **330** physisch breit sind, ist dieses Verfahren ohne weiteres zu erzielen.

**[0039]** [Fig. 3](#) stellt ein exemplarisches Ausführungsbeispiel einer Speichervorrichtung **300** gemäß den Prinzipien der Erfindung dar. Wie gezeigt ist, könnte die Speichervorrichtung **300** eine oder mehrere Specherebenen **200** umfassen, die gestapelt sind, um einen 3-D-Speicher zu bilden. Die Speichervorrichtung **300** könnte außerdem eine Aktivschaltungsebene **390** umfassen. Die Aktivschaltungsebene **390**

könnte auf einem Siliziumsubstrat gebildet sein und könnte Schaltungen enthalten, die nötig sind, um die Speicherarrays **100** von Speicherebenen **200** zu adressieren, die Mehraufwandselemente umfassen, wie z. B. Adressdecodierer, Lese-/Schreib-Steuerlogik, Leseverstärker, Ausgangspuffer, Multiplexer.

**[0040]** Die Speichervorrichtung **300** könnte ferner einen oder mehrere Datenbusse **310** umfassen. Die Datenbusse **310** könnten von einem Leiterverfahrensschritt gebildet sein, um die ausgerichteten Datenseitenkontaktanschlussflächen **230** (siehe [Fig. 2](#)) der Speicherebenen **200** zu verbinden. Es wird angemerkt, dass die Aktivschaltungsebene **390** auch Datenseitenkontaktanschlussflächen umfassen könnte, die ausgerichtet und elektrisch mit den Datenseitenkontaktanschlussflächen **230** der Speicherebenen **200** verbunden sind.

**[0041]** Die Speichervorrichtung **300** könnte ferner den Rrayaauswahlbus **330** umfassen. Der Arrayauswahlbus **330** könnte von einem Leitervorgang gebildet sein, der die Mehrzahl von Arrayauswahlleitungen **260** durch die Arrayauswahlseitenkontaktanschlussflächen **265** auf den Speicherebenen **200** und die Arrayauswahlseitenkontaktanschlussflächen auf der Aktivebene **390** elektrisch verbindet. Es wird angemerkt, dass die Aktivschaltungsebene **390** auch Arrayauswahlleitungen und Arrayauswahlseitenkontaktanschlussflächen umfassen könnte, die mit der Arrayauswahlseitenkontaktanschlussfläche **265** der Speicherebenen **200** ausgerichtet sind.

**[0042]** Die Speichervorrichtung **300** könnte einen Ebenenauswahlbus **340** umfassen. Der Ebenenauswahlbus **340** könnte aus einer Kombination der Ebenenauswahlleitungen **270** und einer Ebenenauswahlseitenkontaktanschlussfläche **275** (siehe [Fig. 2](#)) einzelner Speicherebenen gebildet sein. Ein Leiterverfahrensschritt verbindet elektrisch die Ebenenauswahlleitungen **270** über die Ebenenauswahlseitenkontaktanschlussfläche **275** auf den einzelnen Speicherebenen **200** mit der Aktivschaltungsebene **390**. Jede Ebene **200** könnte eine separate Ebenenauswahlleitung **270** aufweisen, der Arrayauswahlbus **330** könnte jedoch unter den Ebenen **200** gemeinschaftlich verwendet werden.

**[0043]** [Fig. 4](#) ist ein Flussdiagramm, das ein exemplarisches Verfahren **400** zur Herstellung der Speichervorrichtung **300** aus [Fig. 3](#) gemäß einem Aspekt der vorliegenden Erfindung darstellt. Wie in [Fig. 4](#) gezeigt ist, könnte die Aktivschaltungsebene **390** hergestellt werden (Schritt **410**). Außerdem könnten eine oder mehrere Speicherebenen **210** hergestellt werden (Schritte **420** und **430**). Es wird angemerkt, dass ein Herstellen der Aktivschaltungsebene **390** vor, nach oder gleichzeitig mit einem Herstellen der Speicherebenen **200** stattfinden könnte.

**[0044]** Dann könnten die Speicherebenen **200** gemäß einer vorbestimmten Fehlerschwelle sortiert werden (Schritt **440**). Eine Schwelle könnte z. B. gesetzt werden, um eine Speicherebene **200** zurückzuweisen, bei der mehr als 10% der Speicherarrays **100** defekt sind. So wird, wenn jede Speicherebene **200** sechzehn Speicherarrays **100** aufweist, eine Ebene **200** mit mehr als einem defekten Array **100** zurückgewiesen. Eine derartige Kontrolle stellt sicher, dass die resultierende Vorrichtung eine voreingestellte Toleranz für Defekte erfüllt. Um eine unbefriedigende Speicherebene auszusortieren, könnte ein Tester oder eine Elektronikanordnung, die Lese-/Schreib- und Steuerfunktionen aufweisen, ähnlich der Aktivschaltungsebene, eingesetzt werden. Der Aussiebschritt **440** wird bei einer Waferprobeteststufe durchgeführt, bevor die Wafer in einzelne Ebenen **200** vereinzelt werden. Ein Wafer könnte mehrere Ebenen **200** enthalten.

**[0045]** Tatsächlich könnten mehrere Schwellenpegel zum Sortieren der Speicherebenen **200** verwendet werden. Es könnte z. B. möglich sein, dass bestimmte Anwendungen in der Lage sind, mehr Defekte zu tolerieren als andere. Auf diese Weise können variierende Defekttoleranzpegel in den Speichervorrichtungen sichergestellt werden.

**[0046]** Zum Abschluss des Verfahrens könnten die Aktivschaltungsebene **390** und die Speicherebenen **200** gestapelt und mit Haftmittel verbunden werden, um aneinander zu halten. Der Stapelvorgang richtet außerdem die Seitenkontaktanschlussflächen (Daten **230**, Arrayauswahl **265** und Ebenenauswahl **275**) der Speicherebenen **200** und die Aktivschaltungsebenen **390** aus. Der Leitervorgang bildet die Ebenenzwischenverbindungsleiter **310**, **330** und **340**, um elektrische Verbindungen zwischen Speicherebenen und der Aktivschaltungsebene herzustellen. Die Speicherstapel werden dann durch einen Häusungsvorgang geschickt, um die Speichervorrichtung **300** zu bilden.

**[0047]** Während die Erfindung Bezug nehmend auf exemplarische Ausführungsbeispiele derselben beschrieben wurde, werden Fachleute auf diesem Gebiet in der Lage sein, verschiedene Modifizierungen an den beschriebenen Ausführungsbeispielen der Erfindung durchzuführen, ohne von der wahren Weisensart und dem Schutzbereich der Erfindung abzuweichen. Die Ausdrücke „Zeile“ und „Spalte“ sind nur relativ und implizieren keine feste Ausrichtung. Außerdem sind „Zeilen“ und „Spalten“ dahingehend austauschbar, dass sich andere auf etwas als „Zeilen“ beziehen, was dieses Dokument Spalten nennt, und umgekehrt. Die Ausdrücke „Zeile“ und „Spalte“ implizieren nicht notwendigerweise eine orthogonale Beziehung, obwohl dies das ist, was hierin dargestellt wurde. Die Ausdrücke und Beschreibungen, die hierin verwendet werden, sind lediglich zu Darstellungs-

zwecken dargelegt und nicht als Einschränkungen gedacht. Insbesondere könnten, obwohl das Verfahren der Erfindung durch Beispiele beschrieben wurde, die Schritte des Verfahrens in einer anderen Reihenfolge, als dargestellt ist, oder gleichzeitig durchgeführt werden. Fachleute auf diesem Gebiet werden erkennen, dass diese und andere Variationen innerhalb des Schutzbereichs der Erfindung, wie in den folgenden Ansprüchen und ihren Äquivalenten definiert ist, möglich sind.

### Patentansprüche

1. Eine Speichervorrichtung (300) mit folgenden Merkmalen:

einer Aktivschaltungsebene (390);

einem Datenbus (310), der elektrisch mit der Aktivschaltungsebene (390) verbunden ist;

einem Ebenenauswahlbus (340), der elektrisch mit der Aktivschaltungsebene (390) verbunden ist; einem Arrayauswahlbus (330), der elektrisch mit der Aktivschaltungsebene (390) verbunden ist; und einer oder mehreren Speicherebenen (200), die über der Aktivschaltungsebene (390) gestapelt sind, wobei zumindest eine Speicherebene (200) folgende Merkmale umfasst:

ein Substrat (110);

eine Mehrzahl von Arrayauswahlleitungen (150), die über dem Substrat (110) gebildet und elektrisch mit dem Arrayauswahlbus (330) verbunden sind;

eine Ebenenfreigabeschaltung (250), die konfiguriert ist, um die Speicherebene (200) freizugeben/zu sperren;

eine Ebenenauswahlleitung (270), die elektrisch mit der Ebenenfreigabeschaltung (250) und mit dem Ebenenauswahlbus (340) verbunden ist;

eines oder mehrere Speicherarrays (100), die über dem Substrat (110) gebildet sind; wobei zumindest ein Speicherarray (100) folgende Merkmale umfasst:

einen oder mehrere Zeilenleiter (120), die über dem Substrat (110) gebildet sind und sich in einer Zeilenrichtung erstrecken;

einen oder mehrere Spaltenleiter (130), die über dem Substrat (110) gebildet sind und sich in einer Spaltenrichtung erstrecken, derart, dass ein Kreuzungspunkt an jedem Schnittpunkt zwischen den Zeilen- und Spaltenleitern gebildet ist;

eine Speicherzelle (140), die in einem oder mehreren der Kreuzungspunkte gebildet ist; und

eine Arrayfreigabeschaltung (170), die konfiguriert ist, um das Speicherarray (100) freizugeben/zu sperren, und elektrisch mit zumindest einer der Mehrzahl von Arrayauswahlleitungen (150) verbunden ist, wobei die zumindest eine Speicherebene ferner folgende Merkmale umfasst:

einen Zeilenbus (210), der elektrisch mit dem einen oder den mehreren Zeilenleitern (120) des einen oder der mehreren Speicherarrays verbunden ist; und einen Spaltenbus (220), der elektrisch mit dem einen

oder den mehreren Spaltenleitern (130) des einen oder der mehreren Speicherarrays verbunden ist; eine Mehrzahl von Datenseitenkontaktanschlussflächen (310), die sich an der Seite der Speicherebene befinden, die elektrisch mit den Zeilenbussen (210) und Spaltenbussen (220) und mit dem Datenbus (310) verbunden sind;

eine Mehrzahl von Arrayauswahlseitenkontaktanschlussflächen (330), die sich an der Seite der Speicherebene befinden, die elektrisch mit den Arrayauswahlleitungen (150) und mit dem Arrayauswahlbus (330) verbunden sind;

eine Ebenenauswahlseitenkontaktanschlussfläche (340), die sich an der Seite der Speicherebene befindet, die elektrisch mit der Ebenenauswahlleitung (270) und mit einer Leitung des Ebenenauswahlbus (340) verbunden ist.

2. Die Speichervorrichtung (300) gemäß Anspruch 1, bei der zumindest:

die Mehrzahl von Datenseitenkontaktbussen (310) ausgerichtet ist und eine elektrische Verbindung zu dem Datenbus (310) herstellt;

die Mehrzahl von Arrayauswahlseitenkontaktanschlussflächen (330) ausgerichtet ist und eine elektrische Verbindung zu dem Arrayauswahlbus (330) herstellt; oder

die Ebenenauswahlseitenkontaktanschlussfläche (340) eine elektrische Verbindung zu einer Leitung des Ebenenauswahlbus (340) herstellt.

3. Die Speichervorrichtung (300) gemäß Anspruch 1 oder 2, bei der die Mehrzahl von Arrayauswahlleitungen (150) der Speicherebenen (200) elektrisch geschaltet ist, um den Arrayauswahlbus (330) zu bilden.

4. Die Speicherebene (200) gemäß Anspruch 1, 2 oder 3, bei der das Substrat (110) auf Silizium-Basis ist, und bei der jedes des einen oder der mehreren Speicherarrays (110) keine Leseverstärker, Ausgangspuffer, Decodierer und Multiplexer umfasst.

5. Die Speicherebene (200) gemäß Anspruch 1, 2 oder 3, bei der das Substrat (110) nicht auf Silizium-Basis ist und aus Basismaterialien von zumindest einem Kunststoff, Glas, Keramik oder einem Nicht-Metall gebildet ist.

6. Die Speicherebene (200) gemäß einem der vorherigen Ansprüche, bei der die Speicherzelle (140) zumindest eine Sicherungsspeicherzelle, eine Sicherungs-/Diodenspeicherzelle, eine Sicherungs-/Antisicherungsspeicherzelle, eine Magnetspeicherzelle, eine Diodenspeicherzelle, eine Magnet/Diodenspeicherzelle, eine Phasenänderungspeicherzelle oder eine Resistivelementzelle umfasst.

Es folgen 5 Blatt Zeichnungen

Anhängende Zeichnungen

FIGUR 1A

FIGUR 1B

FIGUR 2

FIGUR 3

FIGUR 4