(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7021619号**

**(P7021619)**

(45)発行日 令和4年2月17日(2022.2.17)

(24)登録日 令和4年2月8日(2022.2.8)

(51)国際特許分類

H 0 1 F 38/08 (2006.01)

H 0 1 F 27/24 (2006.01)

F I

H 0 1 F 38/08

H 0 1 F 27/24

C

J

請求項の数 11 (全28頁)

|          |                             |          |                                                             |

|----------|-----------------------------|----------|-------------------------------------------------------------|

| (21)出願番号 | 特願2018-159680(P2018-159680) | (73)特許権者 | 000002945<br>オムロン株式会社<br>京都府京都市下京区塙小路通堀川東入南<br>不動堂町801番地    |

| (22)出願日  | 平成30年8月28日(2018.8.28)       | (74)代理人  | 100101454<br>弁理士 山田 卓二                                      |

| (65)公開番号 | 特開2020-35835(P2020-35835A)  | (74)代理人  | 100091524<br>弁理士 和田 充夫                                      |

| (43)公開日  | 令和2年3月5日(2020.3.5)          | (74)代理人  | 100172236<br>弁理士 岩木 宣憲                                      |

| 審査請求日    | 令和2年12月14日(2020.12.14)      | (72)発明者  | 石橋 寛基<br>京都府京都市下京区塙小路通堀川東入南<br>不動堂町801番地 オムロン株式会社内<br>長岡 真吾 |

|          |                             | (72)発明者  | 京都府京都市下京区塙小路通堀川東入南<br>最終頁に続く                                |

(54)【発明の名称】 变圧器及び電力変換装置

**(57)【特許請求の範囲】****【請求項1】**

ループの形状を有する主コアと、

前記主コアのループのうちの第1の区間に於いて前記主コアに巻回された第1の巻線と、前記主コアのループのうちの前記第1の区間から離れた第2の区間に於いて前記主コアに巻回された第2の巻線と、

前記主コアの前記第1の区間に沿って、かつ、前記第1の巻線の外側に設けられた少なくとも1つの第1のバイパスコアと、

前記主コアの前記第1の区間に於いて前記主コア及び前記第1のバイパスコアに巻回された第3の巻線と、

前記主コアの前記第2の区間に沿って、かつ、前記第2の巻線の外側に設けられた少なくとも1つの第2のバイパスコアと、

前記主コアの前記第2の区間に於いて前記主コア及び前記第2のバイパスコアに巻回された第4の巻線と、

前記主コアの前記第1及び第2の区間の両方から離れた位置に於いて前記主コアのループに交差するように前記主コアに形成された少なくとも1つのギャップとを備えた、変圧器。

**【請求項2】**

前記第1のバイパスコアは、前記第1の区間の長さを超える長さにわたって延在し、前記第2のバイパスコアは、前記第2の区間の長さを超える長さにわたって延在する、

請求項 1 記載の変圧器。

**【請求項 3】**

前記第 1 及び第 2 のバイパスコアは、前記主コアに沿って延在し、両端において前記主コアに向かって又は前記主コアに沿って屈曲する、

請求項 2 記載の変圧器。

**【請求項 4】**

複数の第 1 のバイパスコア及び複数の第 2 のバイパスコアを備えた、

請求項 1 ~ 3 のうちの 1 つに記載の変圧器。

**【請求項 5】**

前記第 1 及び第 3 の巻線はそれぞれ、1 周ごとに前記主コアの表面に接するように、かつ、前記主コアの表面において交互に配置されるように巻回され、

10

前記第 2 及び第 4 の巻線はそれぞれ、1 周ごとに前記主コアの表面に接するように、かつ、前記主コアの表面において交互に配置されるように巻回された、

請求項 1 ~ 4 のうちの 1 つに記載の変圧器。

**【請求項 6】**

前記主コアのループのうちの前記第 1 の区間の一端と前記第 2 の区間の一端との間の第 3 の区間ににおいて、前記主コアのループに交差するように前記主コアに形成された少なくとも 1 つのギャップと、

前記主コアのループのうちの前記第 1 の区間の他端と前記第 2 の区間の他端との間の第 4 の区間ににおいて、前記主コアのループに交差するように前記主コアに形成された少なくとも 1 つのギャップとを備えた、

20

請求項 1 ~ 5 のうちの 1 つに記載の変圧器。

**【請求項 7】**

前記第 3 及び第 4 の区間のうちの少なくとも一方において、前記主コアのループに交差するように前記主コアに形成された複数のギャップを備えた、

請求項 6 記載の変圧器。

**【請求項 8】**

前記変圧器は第 1 ~ 第 4 の端子を備え、

前記第 1 及び第 2 の巻線は、前記第 1 及び第 2 の端子の間に電流が流れるときに前記第 1 及び第 2 の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第 1 及び第 2 の端子の間に直列に接続され、

30

前記第 3 及び第 4 の巻線は、前記第 3 及び第 4 の端子の間に電流が流れるときに前記第 3 及び第 4 の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第 3 及び第 4 の端子の間に直列に接続された、

請求項 1 ~ 7 のうちの 1 つに記載の変圧器。

**【請求項 9】**

前記変圧器は第 1 ~ 第 5 の端子を備え、

前記第 1 及び第 2 の巻線は、前記第 1 及び第 2 の端子の間に電流が流れるときに前記第 1 及び第 2 の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第 1 及び第 2 の端子の間に直列に接続され、

40

前記第 3 の巻線は、前記第 3 及び第 5 の端子の間に接続され、

前記第 4 の巻線は、前記第 4 及び第 5 の端子の間に接続され、

前記第 3 及び第 4 の巻線は、前記第 5 の端子から前記第 3 及び第 4 の端子にそれぞれ電流が流れるときに前記第 3 及び第 4 の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように互いに接続された、

請求項 1 ~ 7 のうちの 1 つに記載の変圧器。

**【請求項 10】**

前記変圧器は第 1 ~ 第 5 の端子を備え、

前記第 1 の巻線は、前記第 1 及び第 5 の端子の間に接続され、

前記第 2 の巻線は、前記第 2 及び第 5 の端子の間に接続され、

50

前記第1及び第2の巻線は、前記第5の端子から前記第1及び第2の端子にそれぞれ電流が流れるとときに前記第1及び第2の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように互いに接続され、

前記第3及び第4の巻線は、前記第3及び第4の端子の間に電流が流れるとときに前記第3及び第4の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第3及び第4の端子の間に直列に接続された、

請求項1～7のうちの1つに記載の変圧器。

【請求項1】

請求項1～10のうち1つに記載の変圧器を備えた、

電力変換装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、変圧器及び電力変換装置に関する。

【背景技術】

【0002】

変圧器の電力変換の性能を向上させるため、その漏れインダクタンスを増大させることが知られている。漏れインダクタンスは、変圧器の一次巻線及び二次巻線の一方のみに交差する磁束によって生じる。このような磁束を生じるために、従来、例えば特許文献1及び2に開示されているように、主コアに加えて、主コアから漏洩した磁束を導くための磁路であるバイパスコアを備えた変圧器が知られている。

20

【0003】

特許文献1は、変圧器の一次巻線と二次巻線間に電気絶縁された磁性体間隙片を挿入し、この間隙片によって、巻線の冷却を行うと共に、各巻線間の漏れ磁束の増加によるインダクタンス効果を持たせた電源変圧器を開示している。

【0004】

特許文献2は、主コア、第1巻線、第2巻線、及び1以上のパスコアとを具備する漏洩磁束型トランスを開示している。主コアは、閉磁路を形成する第1磁性体であって、外足および中足を有する。第1巻線は、中足の長手方向を軸として、当該中足を囲繞するように巻回される。第2巻線は、中足の長手方向を軸として、第1巻線を囲繞するように巻回される。パスコアは、第1巻線の最内周から第2巻線の最外周までの領域のうち、一部分を軸方向に沿って貫通する第2磁性体であって、当該第2磁性体の両方の端部からそれぞれ漏洩する磁束のうち第1巻線内部を通過する磁束が閾値以下となる位置まで、当該第2磁性体が延在する。

30

【先行技術文献】

【特許文献】

【0005】

【文献】特開昭53-024530号公報

特開2016-219540号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0006】

変圧器を備えた電力変換装置は、励磁インダクタンスと漏れインダクタンスにより利得などの特性が変化する。高い電力密度を達成しつつ所望の回路定数を満たすためには、大きい漏れインダクタンスを達成しつつ、励磁インダクタンスを調整する必要がある。励磁インダクタンスは、コアにギャップを設けることによって調整される。しかし、コアにギャップを設けると、漏れ磁束が生じる。この漏れ磁束が巻線に交差することにより、損失が生じる。従って、損失を増大させることなく、励磁インダクタンスを調整することができ、かつ、大きな漏れインダクタンスを有する変圧器が求められる。

【0007】

50

本開示の目的は、損失を増大させることなく、励磁インダクタンスを調整することができ、漏れインダクタンスを増大させることができる変圧器を提供することにある。本開示の目的はまた、そのような変圧器を備えた電力変換装置を提供することにある。

**【課題を解決するための手段】**

**【0008】**

本開示の側面に係る変圧器及び電力変換装置は、上述した課題を解決するために、以下の構成を有する。

**【0009】**

本開示の一側面に係る変圧器は、

ループの形状を有する主コアと、

10

前記主コアのループのうちの第1の区間において前記主コアに巻回された第1の巻線と、前記主コアのループのうちの前記第1の区間から離れた第2の区間において前記主コアに巻回された第2の巻線と、

前記主コアの前記第1の区間に沿って、かつ、前記第1の巻線の外側に設けられた少なくとも1つの第1のバイパスコアと、

前記主コアの前記第1の区間において前記主コア及び前記第1のバイパスコアに巻回された第3の巻線と、

前記主コアの前記第2の区間に沿って、かつ、前記第2の巻線の外側に設けられた少なくとも1つの第2のバイパスコアと、

前記主コアの前記第2の区間において前記主コア及び前記第2のバイパスコアに巻回された第4の巻線と、

20

前記主コアの前記第1及び第2の区間の両方から離れた位置において前記主コアのループに交差するように前記主コアに形成された少なくとも1つのギャップとを備える。

**【0010】**

ここで、「第1の巻線」と及び「第2の巻線」は変圧器の一次巻線として使用され、「第3の巻線」と及び「第4の巻線」は変圧器の二次巻線として使用されてもよい。代替として、「第1の巻線」と及び「第2の巻線」は変圧器の二次巻線として使用され、「第3の巻線」と及び「第4の巻線」は変圧器の一次巻線として使用されてもよい。

**【0011】**

本開示の一側面に係る変圧器によれば、バイパスコアを設けることにより、主コアからバイパスコアを介して再び主コアに戻る磁束（すなわち、バイパスコアを通る磁束）を発生する。バイパスコアを通る磁束は、第3及び第4の巻線に交差せず、第1及び第2の巻線のみに交差する。バイパスコアを通る磁束を発生することにより、大きな漏れインダクタンスを発生することができる。また、本開示の一側面に係る変圧器によれば、第1～第4の巻線から離れた位置に形成されたギャップにおいて漏れ磁束を発生させることにより、漏れ磁束が巻線に交差することを防止し、漏れ磁束が巻線に交差することに起因する損失の増大を防止しながら、励磁インダクタンスを調整することができる。このように、本開示の一側面に係る変圧器によれば、損失を増大させることなく、漏れインダクタンスを増大させることができる。

30

**【0012】**

本開示の一側面に係る変圧器では、

前記第1のバイパスコアは、前記第1の区間の長さを超える長さにわたって延在し、

前記第2のバイパスコアは、前記第2の区間の長さを超える長さにわたって延在してもよい。

40

**【0013】**

本開示の一側面に係る変圧器によれば、第1及び第2のバイパスコアの長さに応じて、バイパスコアを通る磁束の量を変化させ、従って、バイパスコアを通る磁束によって生じる漏れインダクタンスを変化させることができる。

**【0014】**

本開示の一側面に係る変圧器では、

50

前記第1及び第2のバイパスコアは、前記主コアに沿って延在し、両端において前記主コアに向かって又は前記主コアに沿って屈曲してもよい。

**【0015】**

本開示の一側面に係る変圧器によれば、前記第1及び第2のバイパスコアの両端を屈曲することにより、両端において屈曲しないバイパスコアを備える場合よりも、バイパスコアを通る磁束の量を増大させ、従って、バイパスコアを通る磁束によって生じる漏れインダクタンスを増大させることができる。

**【0016】**

本開示の一側面に係る変圧器は、

複数の第1のバイパスコア及び複数の第2のバイパスコアを備えてもよい。 10

**【0017】**

本開示の一側面に係る変圧器によれば、1つの第1のバイパスコア及び1つの第2のバイパスコアを備える場合よりも、バイパスコアを通る磁束の量を増大させ、従って、バイパスコアを通る磁束によって生じる漏れインダクタンスを増大させることができる。

**【0018】**

本開示の一側面に係る変圧器では、

前記第1及び第3の巻線はそれぞれ、1周ごとに前記主コアの表面に接するように、かつ、前記主コアの表面において交互に配置されるように巻回され、

前記第2及び第4の巻線はそれぞれ、1周ごとに前記主コアの表面に接するように、かつ、前記主コアの表面において交互に配置されるように巻回されてもよい。 20

**【0019】**

本開示の一側面に係る変圧器によれば、主コアの表面において一次巻線と二次巻線とを交互に配置するように巻回することにより、このように巻回しない場合よりも、巻線の近接効果による損失を低減することができる。

**【0020】**

本開示の一側面に係る変圧器は、

前記主コアのループのうちの前記第1の区間の一端と前記第2の区間の一端との間の第3の区間ににおいて、前記主コアのループに交差するように前記主コアに形成された少なくとも1つのギャップと、

前記主コアのループのうちの前記第1の区間の他端と前記第2の区間の他端との間の第4の区間ににおいて、前記主コアのループに交差するように前記主コアに形成された少なくとも1つのギャップとを備えてもよい。 30

**【0021】**

本開示の一側面に係る変圧器によれば、第1～第4の巻線から離れた位置に形成されたギャップにおいて漏れ磁束を発生させることにより、漏れ磁束が巻線に交差することに起因する損失の増大を防止しながら、励磁インダクタンスを調整することができる。

**【0022】**

本開示の一側面に係る変圧器は、

前記第3及び第4の区間のうちの少なくとも一方において、前記主コアのループに交差するように前記主コアに形成された複数のギャップを備えてもよい。 40

**【0023】**

本開示の一側面に係る変圧器によれば、ギャップの個数を増やすことにより、漏れ磁束の漏れ出る範囲が小さくなり、巻線に交差しにくくなる。

**【0024】**

本開示の一側面に係る変圧器は、

前記変圧器は第1～第4の端子を備え、

前記第1及び第2の巻線は、前記第1及び第2の端子の間に電流が流れるときに前記第1及び第2の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第1及び第2の端子の間に直列に接続され、

前記第3及び第4の巻線は、前記第3及び第4の端子の間に電流が流れるときに前記第3 50

及び第4の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第3及び第4の端子の間に直列に接続されてもよい。

**【0025】**

本開示の一側面に係る変圧器によれば、第1及び第2の端子に入力電流を供給し、第3及び第4の端子から出力電流を発生してもよい。また、本開示の一側面に係る変圧器によれば、第3及び第4の端子に入力電流を供給し、第1及び第2の端子から出力電流を発生してもよい。

**【0026】**

本開示の一側面に係る変圧器は、

前記変圧器は第1～第5の端子を備え、

10

前記第1及び第2の巻線は、前記第1及び第2の端子の間に電流が流れるときに前記第1及び第2の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第1及び第2の端子の間に直列に接続され、

前記第3の巻線は、前記第3及び第5の端子の間に接続され、

前記第4の巻線は、前記第4及び第5の端子の間に接続され、

前記第3及び第4の巻線は、前記第5の端子から前記第3及び第4の端子にそれぞれ電流が流れるときに前記第3及び第4の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように互いに接続されてもよい。

**【0027】**

本開示の一側面に係る変圧器によれば、第1及び第2の端子に入力電流を供給し、第3及び第5の端子から第1の出力電流を発生し、第4及び第5の端子から第2の出力電流を発生してもよい。

20

**【0028】**

本開示の一側面に係る変圧器は、

前記変圧器は第1～第5の端子を備え、

前記第1の巻線は、前記第1及び第5の端子の間に接続され、

前記第2の巻線は、前記第2及び第5の端子の間に接続され、

前記第1及び第2の巻線は、前記第5の端子から前記第1及び第2の端子にそれぞれ電流が流れるときに前記第1及び第2の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように互いに接続され、

30

前記第3及び第4の巻線は、前記第3及び第4の端子の間に電流が流れるときに前記第3及び第4の巻線により前記主コアのループに沿って同じ向きの磁束を発生するように、前記第3及び第4の端子の間に直列に接続されてもよい。

**【0029】**

本開示の一側面に係る変圧器によれば、第3及び第4の端子に入力電流を供給し、第1及び第5の端子から第1の出力電流を発生し、第2及び第5の端子から第2の出力電流を発生してもよい。

**【0030】**

本開示の一側面に係る電力変換装置は、本開示の各側面に係る変圧器を備える。

40

**【0031】**

本開示の一側面に係る電力変換装置によれば、変圧器の損失を増大させることなく、変圧器の漏れインダクタンスを増大させることができる。これにより、電力変換装置の利得を増大し、その電力密度を増大することができる。

**【発明の効果】**

**【0032】**

本開示の一側面に係る変圧器によれば、損失を増大させることなく、励磁インダクタンスを調整することができ、漏れインダクタンスを増大させることができる。

**【図面の簡単な説明】**

**【0033】**

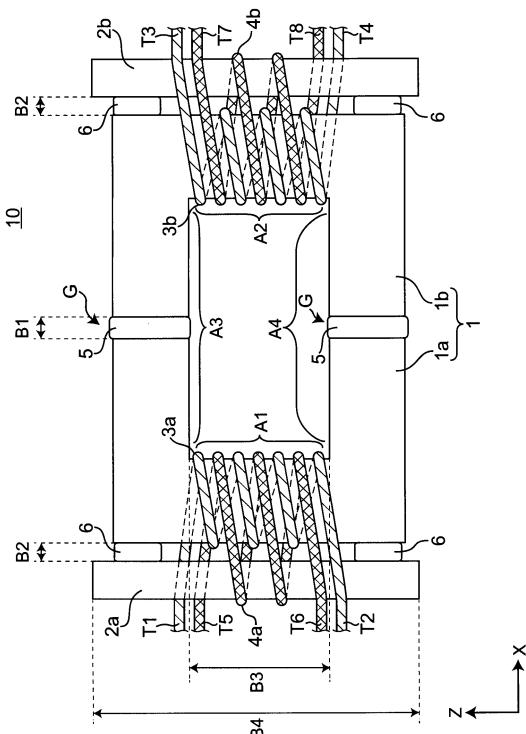

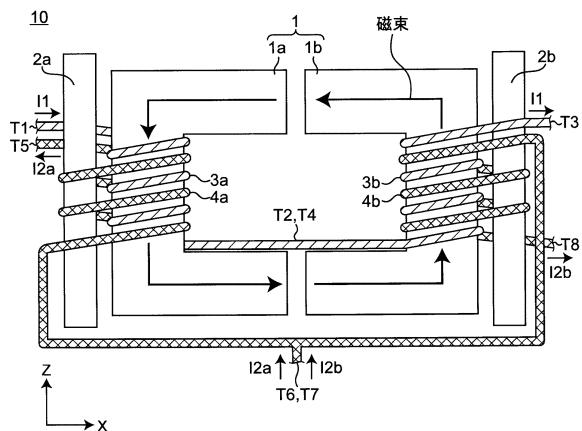

【図1】第1の実施形態に係る変圧器10の構成の一例を模式的に例示する正面図である。

50

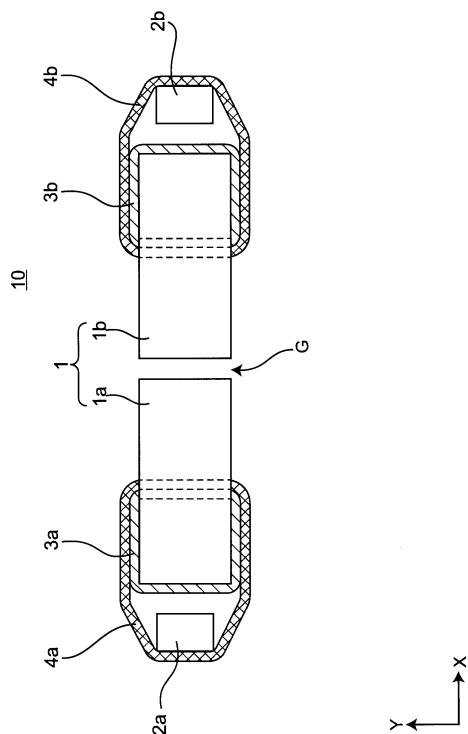

【図 2】図 1 の変圧器 10 の構成の一例を模式的に例示する上面図である。

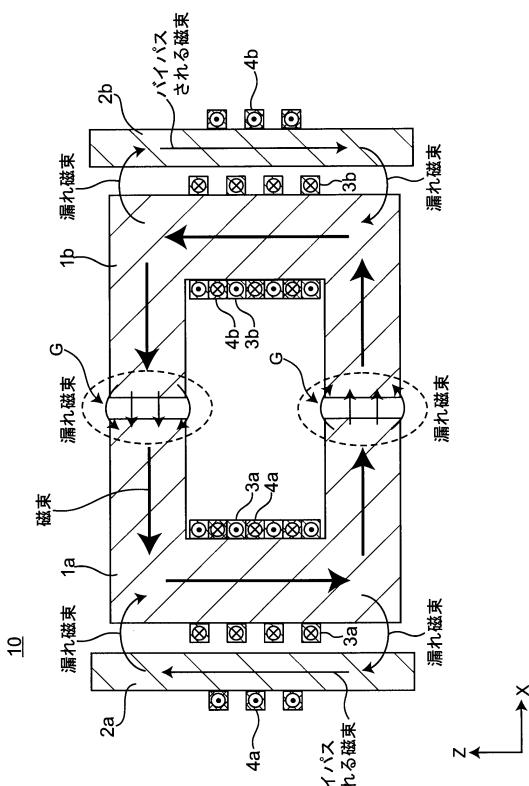

【図 3】図 1 の変圧器 10 に生じる磁束の一例を模式的に例示する断面図である。

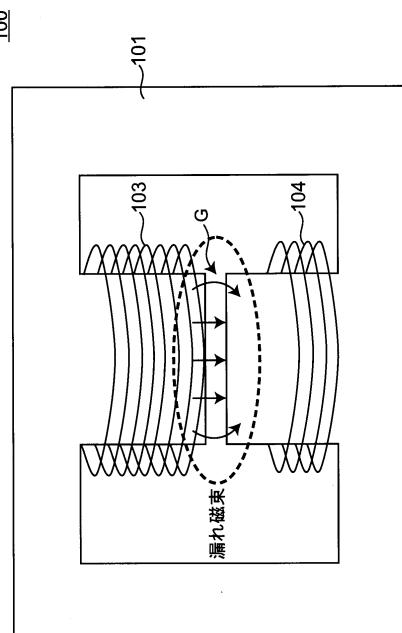

【図 4】比較例に係る変圧器 100 の構成の一例を模式的に例示する正面図である。

【図 5】比較例に係る巻線 103, 104 を備えた変圧器の動作の一例を模式的に例示するグラフである。

【図 6】図 1 の変圧器 10 の動作の一例を模式的に例示するグラフである。

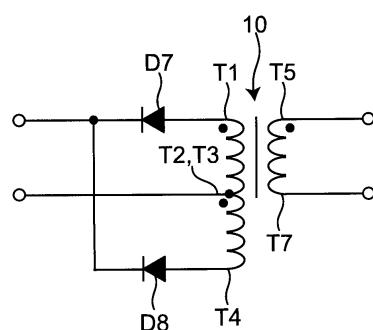

【図 7】図 1 の変圧器 10 における巻線 3a ~ 4b の結線の一例を模式的に例示する図である。

【図 8】図 7 の変圧器 10 を備えた電力変換装置の部分の一例を模式的に例示する回路図である。 10

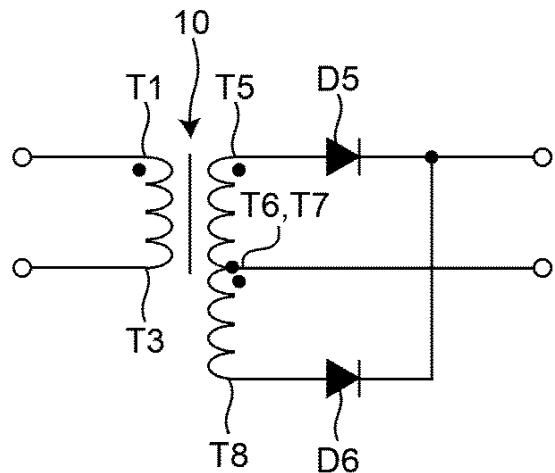

【図 9】図 1 の変圧器 10 における巻線 3a ~ 4b の結線の他の一例を模式的に例示する図である。

【図 10】図 9 の変圧器 10 を備えた電力変換装置の部分の一例を模式的に例示する回路図である。

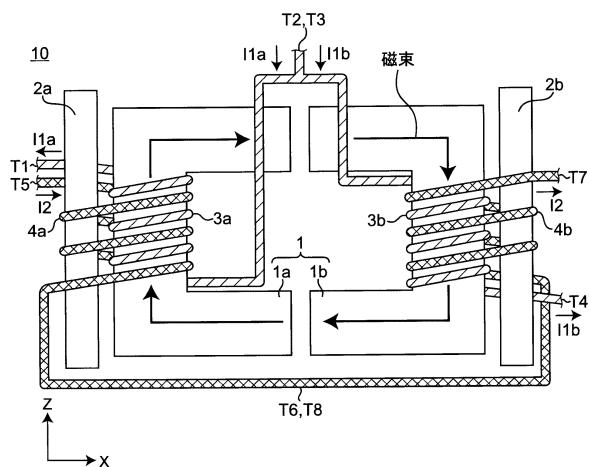

【図 11】図 1 の変圧器 10 における巻線 3a ~ 4b の結線のさらに他の一例を模式的に例示する図である。

【図 12】図 11 の変圧器 10 を備えた電力変換装置の部分の一例を模式的に例示する回路図である。

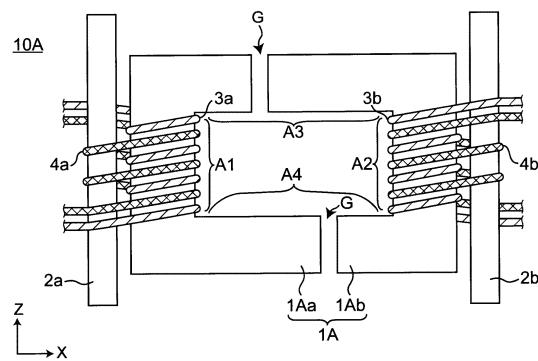

【図 13】第 1 の実施形態の第 1 の変形例に係る変圧器 10A の構成の一例を模式的に例示する正面図である。 20

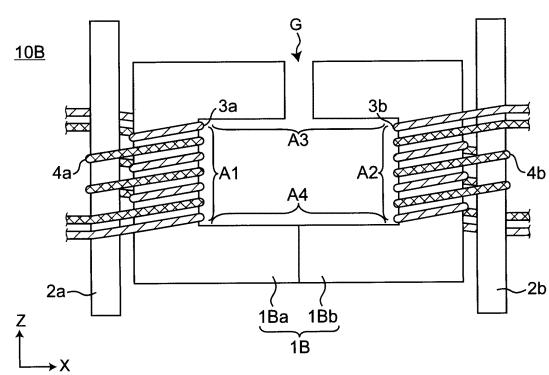

【図 14】第 1 の実施形態の第 2 の変形例に係る変圧器 10B の構成の一例を模式的に例示する正面図である。

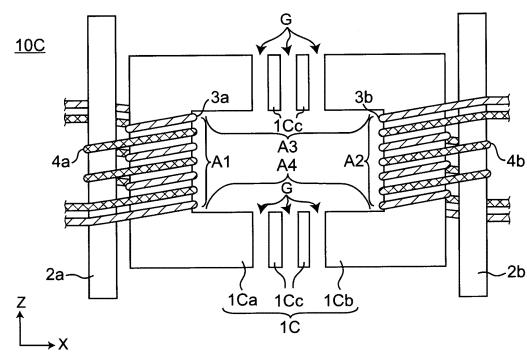

【図 15】第 1 の実施形態の第 3 の変形例に係る変圧器 10C の構成の一例を模式的に例示する正面図である。

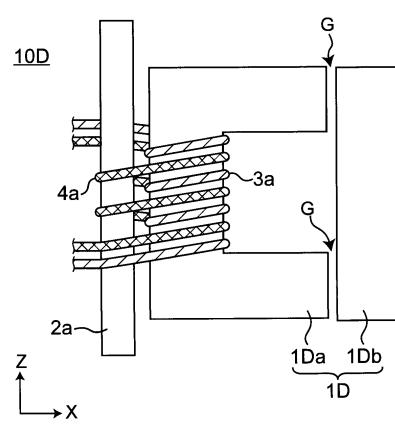

【図 16】第 1 の実施形態の第 4 の変形例に係る変圧器 10D の構成の一例を模式的に例示する正面図である。

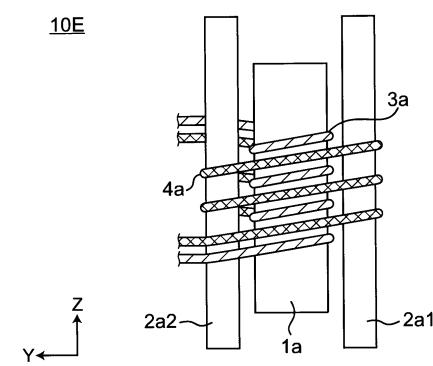

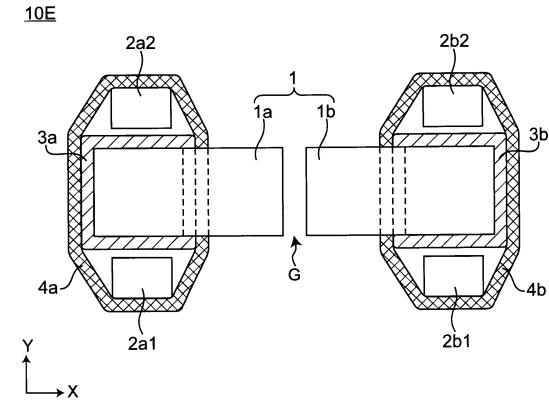

【図 17】第 1 の実施形態の第 5 の変形例に係る変圧器 10E の構成の一例を模式的に例示する側面図である。

【図 18】図 17 の変圧器 10E の構成の一例を模式的に例示する上面図である。

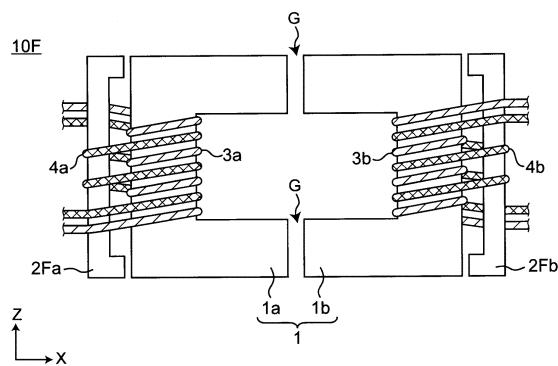

【図 19】第 1 の実施形態の第 6 の変形例に係る変圧器 10F の構成の一例を模式的に例示する正面図である。 30

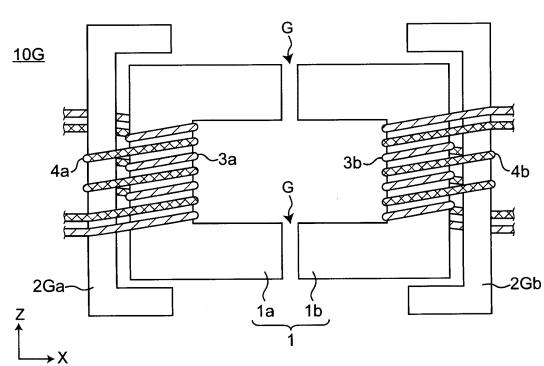

【図 20】第 1 の実施形態の第 7 の変形例に係る変圧器 10G の構成の一例を模式的に例示する正面図である。

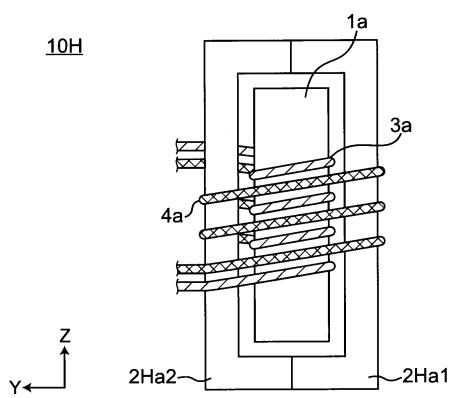

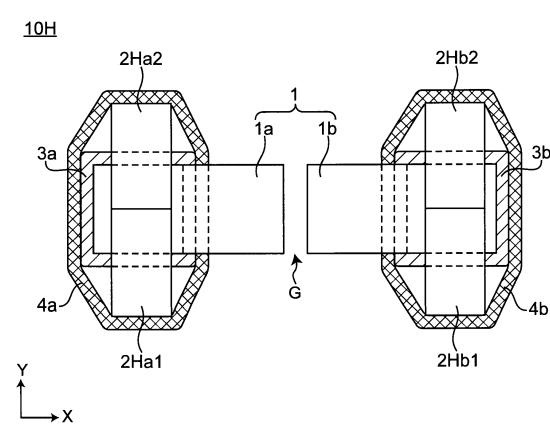

【図 21】第 1 の実施形態の第 8 の変形例に係る変圧器 10H の構成の一例を模式的に例示する側面図である。

【図 22】図 21 の変圧器 10H の構成の一例を模式的に例示する上面図である。

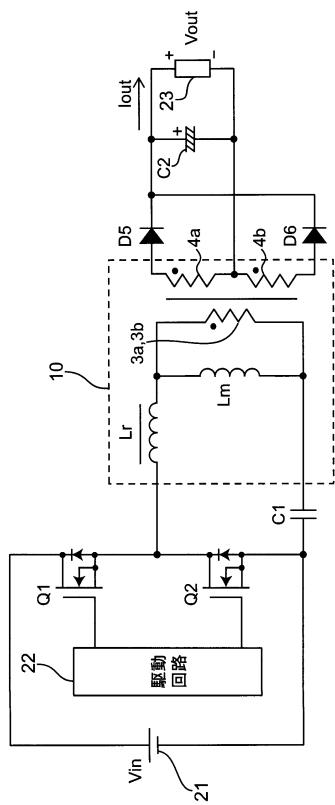

【図 23】第 2 の実施形態に係る電力変換装置の一例を模式的に例示する回路図である。

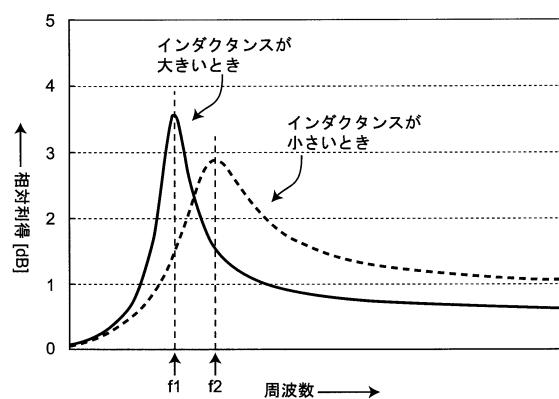

【図 24】図 23 の電力変換装置の共振回路の動作の一例を模式的に例示するグラフである。

【発明を実施するための形態】

【0034】

以下、本開示の一側面に係る実施形態（以下、「本実施形態」とも表記する）を、図面を参照して説明する。各図面において、同じ符号は同様の構成要素を示す。

【0035】

【第 1 の実施形態】

図 1 ~ 図 22 を参照して、第 1 の実施形態に係る変圧器について説明する。

【0036】

【第 1 の実施形態の構成例】

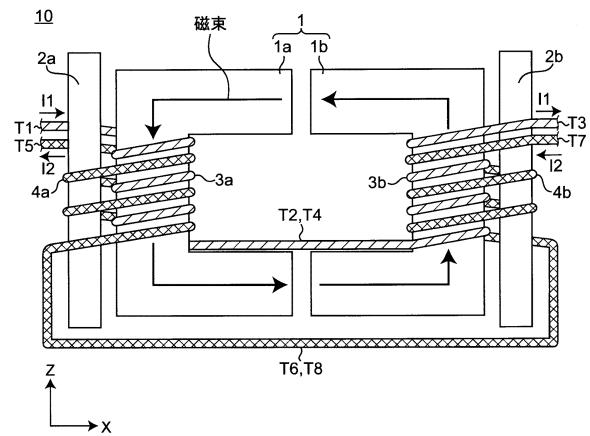

図 1 は、第 1 の実施形態に係る変圧器 10 の構成の一例を模式的に例示する正面図である。変圧器 10 は、主コア 1、少なくとも 1 つのバイパスコア 2a、少なくとも 1 つのバイ

10

20

30

40

50

パスコア 2 b、巻線 3 a , 3 b , 4 a , 4 b、及び少なくとも 1 つのギャップ G を備える。

**【 0 0 3 7 】**

主コア 1 は、複数の主コア部分 1 a , 1 b を含む。複数の主コア部分 1 a , 1 b は、例えば、フェライトなどの磁性体からなる。各主コア部分 1 a , 1 b は、例えば U 字形に形成される。複数の主コア部分 1 a , 1 b は、それらの間に所定距離 B 1 の少なくとも 1 つのギャップ G を形成するように、例えばスペーサ 5 を介して、互いに機械的に連結される。主コア 1 は、その全体として、ループの形状を有する。

**【 0 0 3 8 】**

図 1 の例では、主コア 1 のループに沿って、区間 A 1 ~ A 4 が設けられる。ここで、区間 A 1 及び A 2 は、所定長さ B 3 をそれぞれ有し、互いに離れた位置に設けられる。区間 A 3 は、区間 A 1 の一端と区間 A 2 の一端との間に設けられる。区間 A 4 は、区間 A 1 の他端と区間 A 2 の他端との間に設けられる。

10

**【 0 0 3 9 】**

本明細書では、区間 A 1 ~ A 4 をそれぞれ、「第 1 の区間」、「第 2 の区間」、「第 3 の区間」、及び「第 4 の区間」ともいう。

**【 0 0 4 0 】**

巻線 3 a は、主コア 1 のループのうちの区間 A 1 において主コア 1 ( 図 1 の例では、主コア部分 1 a ) に巻回される。巻線 3 a は、その両端に端部 T 1 , T 2 を備える。巻線 3 b は、主コア 1 のループのうちの区間 A 1 から離れた区間 A 2 において主コア 1 ( 図 1 の例では、主コア部分 1 b ) に巻回される。巻線 3 b は、その両端に端部 T 3 , T 4 を備える。

20

**【 0 0 4 1 】**

本明細書では、巻線 3 a を「第 1 の巻線」ともいい、巻線 3 b を「第 2 の巻線」ともいう。

**【 0 0 4 2 】**

バイパスコア 2 a は、主コア 1 の区間 A 1 に沿って、かつ、巻線 3 a の外側に設けられる。バイパスコア 2 b は、主コア 1 の区間 A 2 に沿って、かつ、巻線 3 b の外側に設けられる。バイパスコア 2 a , 2 b は、例えば、フェライトなどの磁性体からなる。図 1 の例では、バイパスコア 2 a , 2 b は直線状に形成される。バイパスコア 2 a , 2 b は、例えばスペーサ 6 を介して、主コア 1 に対して所定距離 B 2 を有して機械的に連結される。図 1 の例では、バイパスコア 2 a は主コア部分 1 a に対して機械的に連結され、バイパスコア 2 b は主コア部分 1 b に対して機械的に連結される。

30

**【 0 0 4 3 】**

バイパスコア 2 a は、区間 A 1 の長さ B 3 を超える長さ B 4 にわたって延在する。バイパスコア 2 b は、区間 A 2 の長さ B 3 を超える長さ B 4 にわたって延在する。

**【 0 0 4 4 】**

本明細書では、バイパスコア 2 a を「第 1 のバイパスコア」ともいい、バイパスコア 2 b を「第 2 のバイパスコア」ともいう。

**【 0 0 4 5 】**

巻線 4 a は、主コア 1 の区間 A 1 において主コア 1 ( 図 1 の例では、主コア部分 1 a ) 及びバイパスコア 2 a に巻回される。巻線 4 a は、その両端に端部 T 5 , T 6 を備える。巻線 4 b は、主コア 1 の区間 A 2 において主コア 1 ( 図 1 の例では、主コア部分 1 b ) 及びバイパスコア 2 b に巻回される。巻線 4 b は、その両端に端部 T 7 , T 8 を備える。

40

**【 0 0 4 6 】**

本明細書では、巻線 4 a を「第 3 の巻線」ともいい、巻線 4 b を「第 4 の巻線」ともいう。

**【 0 0 4 7 】**

巻線 3 a , 4 a はそれぞれ、1 周ごとに主コア 1 の表面に接するように、かつ、主コア 1 の表面において交互に配置されるように巻回される。巻線 3 b , 4 b はそれぞれ、1 周ごとに主コア 1 の表面に接するように、かつ、主コア 1 の表面において交互に配置されるように巻回される。

**【 0 0 4 8 】**

ギャップ G は、主コア 1 の区間 A 1 及び A 2 の両方から離れた位置において主コア 1 のル

50

ープに交差するように主コア1に形成される。図1の例では、変圧器10は、区間A3に形成された1つのギャップGと、区間A4に形成された1つのギャップGとを備える。

#### 【0049】

図7～図12を参照して後述するように、巻線3a, 3bを一次巻線として使用し、巻線4a, 4bを二次巻線として使用してもよい。また、巻線4a, 4bを一次巻線として使用し、巻線3a, 3bを二次巻線として使用してもよい。

#### 【0050】

複数の主コア部分1a, 1bは、スペーサ5に代えて支持枠又は樹脂モールドなど他の連結手段を用いて、互いに機械的に連結されてもよい。バイパスコア2a, 2bは、スペーサ6に代えて支持枠又は樹脂モールドなど他の連結手段を用いて、主コア1に対して機械的に連結されてもよい。図1以外の各図面では、図示の簡単化のために、スペーサ5, 6(又は他の連結手段)を省略する。

10

#### 【0051】

図2は、図1の変圧器10の構成の一例を模式的に例示する上面図である。前述のように、巻線3aは主コア部分1aに巻回され、巻線3bは主コア部分1bに巻回され、巻線4aは主コア部分1a及びバイパスコア2aに巻回され、巻線4bは主コア部分1b及びバイパスコア2bに巻回される。図2では、説明のため、巻線4aを巻線3aの外側に示すが、巻線3a, 4aはそれぞれ、前述のように、主コア1の表面に接するように巻回される。同様に、図2では、説明のため、巻線4bを巻線3bの外側に示すが、巻線3b, 4bはそれぞれ、前述のように、主コア1の表面に接するように巻回される。

20

#### 【0052】

##### [第1の実施形態の動作例]

図3は、図1の変圧器10に生じる磁束の一例を模式的に例示する断面図である。主コア1及びバイパスコア2a, 2bの上に示した矢印は磁束を示す。巻線3a, 3b又は巻線4a, 4bに電流を流すと、図3に示すように、主コア1のループに沿って磁束が発生し、ギャップGにおいて漏れ磁束が発生する。ギャップGの距離B1(図1を参照)が大きくなるほど、漏れ磁束は大きくなる。前述したように、漏れ磁束が巻線に交差すると損失が生じる。本実施形態に係る変圧器10では、ギャップGを巻線3a～4bから離れた位置に形成したので、ギャップGにおいて発生する漏れ磁束が巻線3a～4bに交差することを防止し、従って、漏れ磁束が巻線3a～4bに交差することに起因する損失の増大を防止することができる。

30

#### 【0053】

また、図3を参照すると、主コア1からバイパスコア2a, 2bを介して再び主コア1に戻る磁束(すなわち、バイパスコア2a, 2bを通る磁束)が発生する。バイパスコア2aを通る磁束は、ソレノイド状の巻線3aの内部及び外部を通る閉ループを形成して巻線3aに交差するが、この磁束は、実質的に、ソレノイド状の巻線4aの内部のみにおいて往復し、従って、巻線4aの内部及び外部を通る閉ループを形成せず、巻線4aに交差しない。同様に、バイパスコア2bを通る磁束は、ソレノイド状の巻線3bの内部及び外部を通る閉ループを形成して巻線3bに交差するが、この磁束は、実質的に、ソレノイド状の巻線4bの内部のみにおいて往復し、従って、巻線4bの内部及び外部を通る閉ループを形成せず、巻線4bに交差しない。バイパスコア2a, 2bを通る磁束を発生することにより、バイパスコアなしの場合よりも、変圧器10の漏れインダクタンスを増大させることができる。主コア1とバイパスコア2a, 2bとの距離B2(図1を参照)が小さいほど(すなわち、図1のスペーサ6が薄いほど)、バイパスコア2a, 2bを通る磁束が生じやすくなる。また、バイパスコア2a, 2bの長さB4(図1を参照)に応じて、バイパスコア2a, 2bとが互いに対向する領域の面積が増大するほど、バイパスコア2a, 2bを通る磁束の量が増大する。従って、例えば、主コア1とバイパスコア2a, 2bとの距離B2を変化させ、及び/又は、バイパスコア2a, 2bの長さB4を変化させることにより、変圧器10の励磁インダクタンスを調整することができる。

40

50

### 【0054】

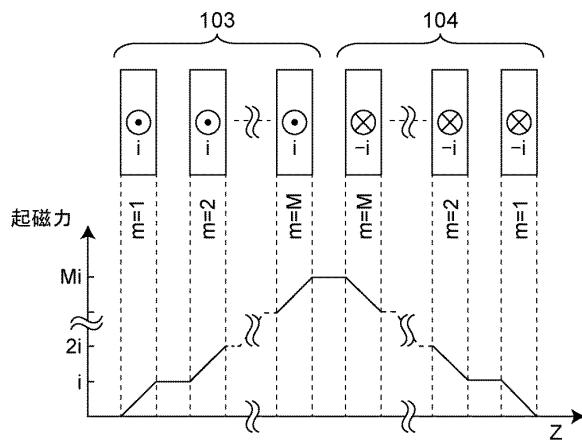

図4は、比較例に係る変圧器100の構成の一例を模式的に例示する正面図である。図4は、従来技術に係る、一般的な漏れ磁束の発生源を備える変圧器の例を示す。図4の変圧器100は、コア101、一次巻線103、及び二次巻線104を備え、コア101は、一次巻線103を巻回する部分と、二次巻線104を巻回する部分との間にギャップGを備える。ギャップGにおいて漏れ磁束が生じる。図4の変圧器100では、漏れインダクタンスを増大させるためには一次巻線103と二次巻線104との間の距離を増大させる。従って、一次巻線103及び二次巻線104の巻数を維持したまま漏れインダクタンスを増大することには限界がある。また、図4の変圧器100では、ギャップGが一次巻線103及び二次巻線104に近接しているので、ギャップGから生じる漏れ磁束が一次巻線103又は二次巻線104と交差して損失が生じる。

10

### 【0055】

一方、本実施形態に係る変圧器10では、バイパスコア2a, 2bを通る磁束を発生することにより、バイパスコアなしの場合よりも大きな漏れインダクタンスを発生することができる。また、本実施形態に係る変圧器10では、主コア1の区間A3及びA4におけるギャップGにより励磁インダクタンスを調整することができる。ここで、前述のように、ギャップGを巻線3a～4bから離れた位置に形成したので、漏れ磁束が巻線3a～4bに交差することに起因する損失の増大を防止することができる。

20

### 【0056】

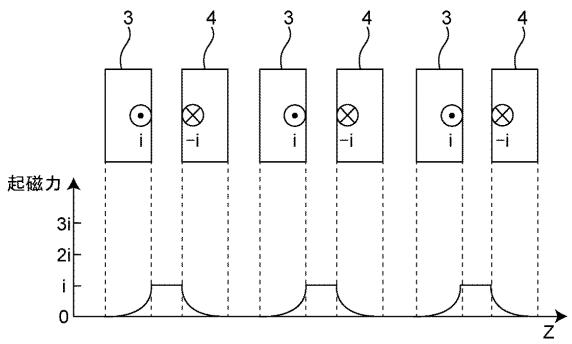

また、図3に示すように、巻線3a, 4aは主コア1の表面において交互に配置されるように巻回され、巻線3b, 4bは主コア1の表面において交互に配置されるように巻回される。これにより、本実施形態に係る変圧器10では、巻線3a～4bにおいて生じる「近接効果」を低減することができる。次に、図5及び図6を参照して、近接効果の低減について説明する。

30

### 【0057】

図5は、比較例に係る巻線103, 104を備えた変圧器の動作の一例を模式的に例示するグラフである。図5の例では、巻線103, 104がコアの表面において交互に配置されるように巻回されるのではなく、巻線103がコアの表面の所定区間にわたって連続して巻回され、巻線104がコアの表面の他の所定区間にわたって連続して巻回される場合を示す。巻線103, 104はそれぞれ、コアの表面において単層かつ巻数Mで巻回される。起磁力は、巻線に流れる電流iと、巻数mとに比例する。従って、同一方向に電流iが流れる巻線の巻数mが増えるほど( $m = 1, 2, \dots, M$ )、起磁力が増大し、また、近接効果による損失も増大する。

30

### 【0058】

図6は、図1の変圧器10の動作の一例を模式的に例示するグラフである。図6において、符号「3」は巻線3a又は3bを示し、符号「4」は巻線4a又は4bを示す。前述のように、主コア1の表面において交互に配置された巻線3a, 4aのうちの一方を一次巻線として使用し、他方を二次巻線として使用する。同様に、主コア1の表面において交互に配置された巻線3b, 4bのうちの一方を一次巻線として使用し、他方を二次巻線として使用する。二次巻線には、一次巻線に流れる電流とは逆方向の電流が流れる。従って、主コア1の表面において交互に配置された巻線3及び4には、互いに逆方向の電流が流れれる。従って、本実施形態に係る変圧器10によれば、一次巻線及び二次巻線を交互に配置することにより、起磁力が増大しにくくなり、また、図5のように巻線を巻回する場合よりも、近接効果による損失を低減することができる。

40

### 【0059】

次に、図7～図12を参照して、巻線3a～4bの結線について説明する。

### 【0060】

図7は、図1の変圧器10における巻線3a～4bの結線の一例を模式的に例示する図である。巻線3aの端部T2と巻線3bの端部T4とが互いに接続される。巻線4aの端部T6と巻線4bの端部T8とが互いに接続される。巻線3aの端部T1、巻線3bの端部

50

T 3、巻線 4 a の端部 T 5、及び巻線 4 b の端部 T 7 は、変圧器 1 0 の入出力端子として使用される。

#### 【 0 0 6 1 】

図 7 の例では、巻線 3 a の端部 T 1 を「第 1 の端子」ともいい、巻線 3 b の端部 T 3 を「第 2 の端子」ともいい、巻線 4 a の端部 T 5 を「第 3 の端子」ともいい、巻線 4 b の端部 T 7 を「第 4 の端子」ともいう。

#### 【 0 0 6 2 】

巻線 3 a , 3 b は、巻線 3 a の端部 T 1 及び巻線 3 b の端部 T 3 の間に電流が流れるときに巻線 3 a , 3 b により主コア 1 のループに沿って同じ向きの磁束を発生するように、端部 T 1 , T 3 の間に直列に接続される。巻線 4 a , 4 b は、巻線 4 a の端部 T 5 及び巻線 4 b の端部 T 7 の間に電流が流れるときに巻線 4 a , 4 b により主コア 1 のループに沿って同じ向きの磁束を発生するように、端部 T 5 , T 7 の間に直列に接続される。従って、巻線 3 a , 3 b を一次巻線として使用し、巻線 4 a , 4 b を二次巻線として使用する場合、端部 T 1 , T 3 の間に入力電流 I 1 が流れるとき、主コア 1 のループに沿う磁束の変化に応じて、端部 T 5 , T 7 の間に出力電流 I 2 が流れる。また、巻線 4 a , 4 b を一次巻線として使用し、巻線 3 a , 3 b を二次巻線として使用する場合、端部 T 5 , T 7 の間に入力電流 I 2 が流れるとき、主コア 1 のループに沿う磁束の変化に応じて、端部 T 1 , T 3 の間に出力電流 I 1 が流れる。

10

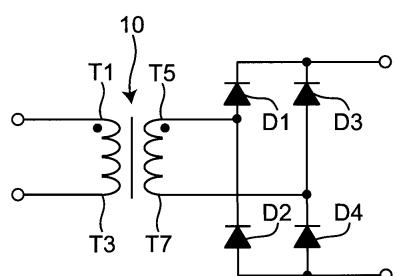

#### 【 0 0 6 3 】

図 8 は、図 7 の変圧器 1 0 を備えた電力変換装置の部分の一例を模式的に例示する回路図である。巻線 3 a , 3 b を一次巻線として使用し、巻線 4 a , 4 b を二次巻線として使用する場合、巻線 4 a の端部 T 5 及び巻線 4 b の端部 T 7 には、ダイオード D 1 ~ D 4 からなるダイオードブリッジを含む整流回路を接続してもよい。

20

#### 【 0 0 6 4 】

図 7 及び図 8 の例では、巻線 3 a , 3 b の巻数は、互いに等しくても、互いに異なっていてもよい。また、図 7 及び図 8 の例では、巻線 4 a , 4 b の巻数は、互いに等しくても、互いに異なっていてもよい。

#### 【 0 0 6 5 】

図 9 は、図 1 の変圧器 1 0 における巻線 3 a ~ 4 b の結線の他の一例を模式的に例示する図である。巻線 3 a の端部 T 2 と巻線 3 b の端部 T 4 とが互いに接続される。巻線 4 a の端部 T 6 と巻線 4 b の端部 T 7 とが互いに接続される。巻線 3 a の端部 T 1 及び巻線 3 b の端部 T 3 は、変圧器 1 0 の入力端子として使用され、巻線 4 a の端部 T 5 及び巻線 4 b の端部 T 8 は、変圧器 1 0 の出力端子として使用される。また、互いに接続された巻線 4 a の端部 T 6 及び巻線 4 b の端部 T 7 もまた、変圧器 1 0 の出力端子として使用される。図 9 の例では、巻線 3 a , 3 b を一次巻線として使用し、巻線 4 a , 4 b を二次巻線として使用する。

30

#### 【 0 0 6 6 】

図 9 の例では、巻線 3 a の端部 T 1 を「第 1 の端子」ともいい、巻線 3 b の端部 T 3 を「第 2 の端子」ともいい、巻線 4 a の端部 T 5 を「第 3 の端子」ともいい、巻線 4 b の端部 T 8 を「第 4 の端子」ともいい、互いに接続された巻線 4 a の端部 T 6 及び巻線 4 b の端部 T 7 を「第 5 の端子」ともいう。

40

#### 【 0 0 6 7 】

巻線 3 a , 3 b は、巻線 3 a の端部 T 1 及び巻線 3 b の端部 T 3 の間に電流が流れるときに巻線 3 a , 3 b により主コア 1 のループに沿って同じ向きの磁束を発生するように、端部 T 1 , T 3 の間に直列に接続される。巻線 4 a , 4 b は、巻線 4 a の端部 T 6 から端部 T 5 に電流が流れかつ巻線 4 b の端部 T 7 から端部 T 8 に電流が流れるときに（又は、巻線 4 a の端部 T 5 から端部 T 6 に電流が流れかつ巻線 4 b の端部 T 8 から端部 T 7 に電流が流れるときに）、巻線 4 a , 4 b により主コア 1 のループに沿って同じ向きの磁束を発生するように互いに接続される。従って、巻線 3 a の端部 T 1 及び巻線 3 b の端部 T 3 の間に入力電流 I 1 が流れるとき、主コア 1 のループに沿う磁束の変化に応じて、巻線 4 a

50

の端部 T 6 から端部 T 5 に出力電流  $I_{2a}$  が流れ、かつ、巻線 4 b の端部 T 7 から端部 T 8 に出力電流  $I_{2b}$  が流れる（又は、巻線 4 a の端部 T 5 から端部 T 6 に出力電流  $I_{2a}$  が流れ、かつ、巻線 4 b の端部 T 8 から端部 T 7 に出力電流  $I_{2b}$  が流れる）。

#### 【 0 0 6 8 】

図 10 は、図 9 の変圧器 10 を備えた電力変換装置の部分の一例を模式的に例示する回路図である。巻線 4 a, 4 b の巻数が互いに等しい場合、互いに接続された巻線 4 a の端部 T 6 及び巻線 4 b の端部 T 7 は二次巻線のセンタータップになる。この場合、巻線 4 a, 4 b の端部 T 5 ~ T 8 には、ダイオード D 5, D 6 を含む、センタータップを利用した整流回路を接続してもよい。

#### 【 0 0 6 9 】

図 9 及び図 10 の例では、巻線 3 a, 3 b の巻数は、互いに等しくても、互いに異なっていてもよい。また、図 9 及び図 10 の例では、巻線 4 a, 4 b の巻数は、前述のように、互いに等しく設定される。

#### 【 0 0 7 0 】

図 11 は、図 1 の変圧器 10 における巻線 3 a ~ 4 b の結線のさらに他の一例を模式的に例示する図である。巻線 3 a の端部 T 2 と巻線 3 b の端部 T 3 とが互いに接続される。巻線 4 a の端部 T 6 と巻線 4 b の端部 T 8 とが互いに接続される。巻線 4 a の端部 T 5 及び巻線 4 b の端部 T 7 は、変圧器 10 の入力端子として使用され、巻線 3 a の端部 T 1 及び巻線 3 b の端部 T 4 は、変圧器 10 の出力端子として使用される。また、互いに接続された巻線 3 a の端部 T 2 及び巻線 3 b の端部 T 3 もまた、変圧器 10 の出力端子として使用される。図 11 の例では、巻線 4 a, 4 b を一次巻線として使用し、巻線 3 a, 3 b を二次巻線として使用する。

#### 【 0 0 7 1 】

図 11 の例では、巻線 3 a の端部 T 1 を「第 1 の端子」ともいい、巻線 3 b の端部 T 4 を「第 2 の端子」ともいい、巻線 4 a の端部 T 5 を「第 3 の端子」ともいい、巻線 4 b の端部 T 7 を「第 4 の端子」ともいい、互いに接続された巻線 3 a の端部 T 2 及び巻線 3 b の端部 T 3 を「第 5 の端子」ともいう。

#### 【 0 0 7 2 】

巻線 3 a, 3 b は、巻線 3 a の端部 T 2 から端部 T 1 に電流が流れかつ巻線 3 b の端部 T 3 から端部 T 4 に電流が流れるときに（又は、巻線 3 a の端部 T 1 から端部 T 2 に電流が流れかつ巻線 3 b の端部 T 4 から端部 T 3 に電流が流れるときに）、巻線 3 a, 3 b により主コア 1 のループに沿って同じ向きの磁束を発生するように互いに接続される。巻線 4 a, 4 b は、巻線 4 a の端部 T 5 及び巻線 4 b の端部 T 7 の間に電流が流れるときに巻線 4 a, 4 b により主コア 1 のループに沿って同じ向きの磁束を発生するように、端部 T 5, T 7 の間に直列に接続される。従って、巻線 4 a の端部 T 5 及び巻線 4 b の端部 T 7 の間に入力電流  $I_{2a}$  が流れるとき、主コア 1 のループに沿う磁束の変化に応じて、巻線 3 a の端部 T 2 から端部 T 1 に出力電流  $I_{1a}$  が流れ、かつ、巻線 3 b の端部 T 3 から端部 T 4 に出力電流  $I_{1b}$  が流れる（又は、巻線 3 a の端部 T 1 から端部 T 2 に出力電流  $I_{1a}$  が流れ、かつ、巻線 3 b の端部 T 4 から端部 T 3 に出力電流  $I_{1b}$  が流れる）。

#### 【 0 0 7 3 】

図 12 は、図 11 の変圧器 10 を備えた電力変換装置の部分の一例を模式的に例示する回路図である。巻線 3 a, 3 b の巻数が互いに等しい場合、互いに接続された巻線 3 a の端部 T 2 及び巻線 3 b の端部 T 3 は二次巻線のセンタータップになる。この場合、巻線 3 a, 3 b の端部 T 1 ~ T 4 には、ダイオード D 7, D 8 を含む、センタータップを利用した整流回路を接続してもよい。

#### 【 0 0 7 4 】

図 11 及び図 12 の例では、巻線 3 a, 3 b の巻数は、前述のように、互いに等しく設定される。また、図 11 及び図 12 の例では、巻線 4 a, 4 b の巻数は、互いに等しくても、互いに異なっていてもよい。

#### 【 0 0 7 5 】

10

20

30

40

50

図7～図12を参照して説明したように、本実施形態に係る変圧器10は、例えば、ダイオードブリッジを含む整流回路を備えた電力変換装置に適用可能であり、また、センタータップを利用した整流回路を備えた電力変換装置にも適用可能である。

#### 【0076】

##### [第1の実施形態の効果]

本実施形態に係る変圧器10は、バイパスコア2a, 2bを通る磁束を発生することにより、大きな漏れインダクタンスを発生することができる。また、本実施形態に係る変圧器10は、巻線3a～4bから離れた位置に形成されたギャップGにおいて漏れ磁束を発生させることにより、漏れ磁束が巻線3a～4bに交差することを防止し、漏れ磁束が巻線3a～4bに交差することに起因する損失の増大を防止しながら、励磁インダクタンスを調整することができる。このように、本実施形態に係る変圧器10によれば、損失を増大させることなく、漏れインダクタンスを増大させることができる。10

#### 【0077】

また、本実施形態に係る変圧器10では、ギャップGの距離に応じて漏れ磁束の量を変化させることができる。また、本実施形態に係る変圧器10では、主コア1とバイパスコア2a, 2bとの距離B2に応じて、及び／又は、バイパスコア2a, 2bの長さに応じて、バイパスコア2a, 2bを通る磁束の量を変化させ、従って、バイパスコア2a, 2bを通る磁束によって生じる漏れインダクタンスを変化させることができる。

#### 【0078】

また、本実施形態に係る変圧器10では、主コア1の表面において一次巻線と二次巻線とを交互に配置するように巻回することにより、このように巻回しない場合よりも、巻線の近接効果による損失を低減することができる。20

#### 【0079】

また、本実施形態に係る変圧器10では、巻線3a～4bは1周ごとに主コア1の表面に接するように（すなわち単層で）巻回されるので、巻線3a～4bによって生じた熱を良好に放熱することができる。巻線3a, 3bの一部は主コア1及びバイパスコア2a, 2bによって挟まれているが、このことは、巻線3a, 3bの放熱を大幅にさまたげるものではない。

#### 【0080】

また、本実施形態に係る変圧器10では、前述のように各巻線3a～4bが主コア1の表面において単層で巻回されるが、主コア1のループに沿った複数の区間A1, A2に巻線3a～4bを巻回するので、主コア1の表面を有効に利用して巻線3a～4bの巻数を増やすことができる。30

#### 【0081】

また、本実施形態に係る変圧器10は、その簡単な構成により、バイパスコア2a, 2bを容易に組み込むことができる。

#### 【0082】

特許文献1では、漏れ磁束が巻線に交差することによる損失を考慮せず、従って、このような漏れ磁束による損失を低減することができない。

#### 【0083】

また、特許文献1では、磁性体間隙片が一次巻線及び二次巻線の間にがあるので、磁束が巻線にシールドされ、磁性体間隙片を通りにくい。よって、磁性体間隙片を備えていても、漏れインダクタンスを増加する効果は薄いと考えられる。40

#### 【0084】

また、特許文献1によれば、一次巻線は矩形のループの形状を有する鉄心の一辺の周りに巻回され、二次巻線は一次巻線の周りに巻回され、磁性体間隙片は一次巻線及び二次巻線の間に所定の角度幅ごとに挿入される。磁性体間隙片の長さは、一次巻線及び二次巻線の幅以下に制約される。従って、特許文献1では、漏れ磁束の量を変化させるために磁性体間隙片の長さを任意に変化させることはできない。

#### 【0085】

10

20

30

40

50

また、特許文献 1 によれば、前述のように、一次巻線は鉄心に巻回され、二次巻線は一次巻線の周りに巻回され、一次巻線及び二次巻線のそれぞれにおいて近接効果が生じると考えられる。特許文献 1 では、近接効果による損失を低減することができない。

#### 【 0 0 8 6 】

また、特許文献 1 では、一次巻線は鉄心に巻回され、二次巻線は一次巻線の周りに巻回されるので、一次巻線及び二次巻線によって生じた熱を放熱しにくく、変圧器の温度が上昇しやすいと考えられる。

#### 【 0 0 8 7 】

特許文献 2 によれば、第 1 巾線及び第 2 巾線は第 1 磁性体の中足に巻回されるので、第 1 磁性体において、第 1 巾線及び第 2 巾線から離れた位置にギャップを形成することができない。従って、漏れ磁束が巻線に交差しにくいようにギャップを形成することができず、損失を増大させることなく漏れ磁束を増大させることは困難である。

10

#### 【 0 0 8 8 】

また、特許文献 2 によれば、第 1 巾線は第 1 磁性体に巻回され、第 2 巾線は第 1 巾線の周りに巻回され、第 1 巾線及び第 2 巾線のそれぞれにおいて近接効果が生じると考えられる。特許文献 2 では、近接効果による損失を低減することができない。

#### 【 0 0 8 9 】

また、特許文献 2 によれば、第 1 巾線は第 1 磁性体に巻回され、第 2 巾線は第 1 巾線の周りに巻回されるので、第 1 巾線及び第 2 巾線によって生じた熱を放熱しにくく、変圧器の温度が上昇しやすいと考えられる。

20

#### 【 0 0 9 0 】

一方、本実施形態に係る変圧器 10 では、漏れインダクタンスを増大することと、漏れ磁束が巻線に交差することによる損失の増大を防止することと、近接効果による損失を低減することとのすべてを達成するものである。これらの要件のすべてを達成することができる変圧器を想到することは容易ではない。

#### 【 0 0 9 1 】

##### [ 第 1 の実施形態の変形例 ]

次に、図 13～図 22 を参照して、第 1 の実施形態の変形例について説明する。

#### 【 0 0 9 2 】

##### [ 第 1 の実施形態の第 1 の変形例 ]

30

図 13 は、第 1 の実施形態の第 1 の変形例に係る変圧器 10 A の構成の一例を模式的に例示する正面図である。図 13 の変圧器 10 A は、図 1 の主コア 1 に代えて、主コア 1 A を備える。主コア 1 A は、複数の主コア部分 1 A a , 1 A b を含む。図 1 では、区間 A 3 のギャップ G 及び区間 A 4 のギャップ G を区間 A 1 , A 2 から等距離の位置に示したが、各ギャップ G は、区間 A 3 , A 4 において任意の位置に形成されてもよい。図 13 の例では、変圧器 10 A は、区間 A 3 において区間 A 2 よりも区間 A 1 に近接して形成された 1 つのギャップ G と、区間 A 4 において区間 A 1 よりも区間 A 2 に近接して形成された 1 つのギャップ G とを備える。ギャップ G は、ギャップ G において生じた漏れ磁束が実質的に巻線 3 a ~ 4 b に交差しないように、主コア 1 A の区間 A 1 及び A 2 の両方から離れた位置において主コア 1 A のループに交差するように主コア 1 A に形成されるのであれば、任意の位置に形成されてもよい。

40

#### 【 0 0 9 3 】

##### [ 第 1 の実施形態の第 2 の変形例 ]

図 14 は、第 1 の実施形態の第 2 の変形例に係る変圧器 10 B の構成の一例を模式的に例示する正面図である。図 14 の変圧器 10 B は、図 1 の主コア 1 に代えて、主コア 1 B を備える。主コア 1 B は、複数の主コア部分 1 B a , 1 B b を含む。主コア 1 B は、区間 A 3 に形成された 1 つのギャップ G を備える。本実施形態に係る変圧器は、所望の漏れ磁束の量に応じて、1 つのギャップのみを備えてもよい。主コア 1 B は、区間 A 3 に形成されたギャップ G に代えて、区間 A 4 に形成された 1 つのギャップ G を備えてもよい。

#### 【 0 0 9 4 】

50

主コア 1 B が 1 つのみのギャップ G を備える場合、主コア 1 B は、複数の主コア部分からなるのではなく、一体的に形成されてもよい。

#### 【 0 0 9 5 】

##### [ 第 1 の実施形態の第 3 の変形例 ]

図 15 は、第 1 の実施形態の第 3 の変形例に係る変圧器 10 C の構成の一例を模式的に例示する正面図である。図 15 の変圧器 10 C は、図 1 の主コア 1 に代えて、主コア 1 C を備える。主コア 1 C は、複数の主コア部分 1 C a , 1 C b , 1 C c を含む。図 15 の例では、変圧器 10 C は、区間 A 3 に形成された複数のギャップ G と、区間 A 4 に形成された複数のギャップ G とを備える。本実施形態に係る変圧器は、所望の漏れ磁束の量に応じて、区間 A 3 , A 4 の少なくとも一方において、主コア 1 C のループに交差するように主コア 1 C に形成された複数のギャップ G を備えてもよい。各ギャップ G の距離が小さければ、漏れ磁束の漏れ出る範囲が小さくなり、巻線に交差しにくくなる。

10

#### 【 0 0 9 6 】

区間 A 3 , A 4 の一方において複数のギャップ G を備え、区間 A 3 , A 4 の他方において 1 つのギャップ G を備えてもよい。また、区間 A 3 , A 4 の一方において複数のギャップ G を備え、区間 A 3 , A 4 の他方においてギャップ G を備えなくてもよい。

#### 【 0 0 9 7 】

##### [ 第 1 の実施形態の第 4 の変形例 ]

図 16 は、第 1 の実施形態の第 4 の変形例に係る変圧器 10 D の構成の一例を模式的に例示する正面図である。図 16 の変圧器 10 D では、図 1 の巻線 3 b , 4 b 及びバイパスコア 2 b を除去している。また、図 16 の変圧器 10 D は、図 1 の主コア 1 に代えて、主コア 1 D を備える。主コア 1 D は、複数の主コア部分 1 D a , 1 D b を含む。主コア部分 1 D a は、図 1 の主コア部分 1 a と同様に、例えば U 字形に形成され、主コア部分 1 D b は、例えば I 字形に形成される。複数の主コア部分 1 D a , 1 D b は、それらの間に少なくとも 1 つのギャップ G を形成するように互いに機械的に連結される。主コア 1 D は、その全体として、ループの形状を有する。

20

#### 【 0 0 9 8 】

図 16 の変圧器 10 D もまた、図 1 の変圧器 10 と同様に、バイパスコア 2 a を通る磁束を発生することにより、大きな漏れインダクタンスを発生することができる。また、図 16 の変圧器 10 D もまた、図 1 の変圧器 10 と同様に、巻線 3 a , 4 a から離れた位置に形成されたギャップ G において漏れ磁束を発生させることにより、漏れ磁束が巻線 3 a , 4 a に交差することを防止し、漏れ磁束が巻線 3 a , 4 a に交差することに起因する損失の増大を防止しながら、励磁インダクタンスを調整することができる。このように、図 16 の変圧器 10 D によれば、損失を増大させることなく、漏れインダクタンスを増大させることができる。

30

#### 【 0 0 9 9 】

また、図 16 の変圧器 10 D もまた、図 1 の変圧器 10 と同様に、ギャップ G の距離に応じて漏れ磁束の量を変化させることができる。また、図 16 の変圧器 10 D もまた、図 1 の変圧器 10 と同様に、主コア 1 D 及びバイパスコア 2 a の距離に応じて、及び / 又は、バイパスコア 2 a の長さに応じて、バイパスコア 2 a を通る磁束の量を変化させ、従って、バイパスコア 2 a を通る磁束によって生じる漏れインダクタンスを変化させができる。

40

#### 【 0 1 0 0 】

また、図 16 の変圧器 10 D もまた、図 1 の変圧器 10 と同様に、主コア 1 D の表面において一次巻線と二次巻線とを交互に配置するように巻回することにより、このように巻回しない場合よりも、巻線の近接効果による損失を低減することができる。

#### 【 0 1 0 1 】

また、図 16 の変圧器 10 D もまた、図 1 の変圧器 10 と同様に、巻線 3 a , 4 a は 1 周ごとに主コア 1 D の表面に接するように（すなわち単層で）巻回されるので、巻線 3 a , 4 a によって生じた熱を良好に放熱することができる。

50

**【0102】**

また、図16の変圧器10Dもまた、図1の変圧器10と同様に、その簡単な構成により、バイパスコア2aを容易に組み込むことができる。

**【0103】****[第1の実施形態の第5の変形例]**

図17は、第1の実施形態の第5の変形例に係る変圧器10Eの構成の一例を模式的に例示する側面図である。図18は、図17の変圧器10Eの構成の一例を模式的に例示する上面図である。図17の変圧器10Eは、図1のバイパスコア2a, 2bに代えて、バイパスコア2a1～2b2を備える。

**【0104】**

バイパスコア2a1, 2a2は、巻線3aを巻回した主コア1の区間に沿って、かつ、巻線3aの外側に設けられる。バイパスコア2b1, 2b2は、巻線3bを巻回した主コア1の区間に沿って、かつ、巻線3bの外側に設けられる。巻線4aは、巻線3aを巻回した主コア1の区間ににおいて主コア1及びバイパスコア2a1, 2a2に巻回される。巻線4bは、巻線3bを巻回した主コア1の区間ににおいて主コア1及びバイパスコア2b1, 2b2に巻回される。

**【0105】**

図18の例では、バイパスコア2a1, 2a2を「第1のバイパスコア」ともいい、バイパスコア2b1, 2b2を「第2のバイパスコア」ともいう。

**【0106】**

図17の変圧器10Eは、巻線3a, 4aに関連して2つのバイパスコア2a1, 2a2を備え、巻線3b, 4bに関連して2つのバイパスコア2b1, 2b2を備える。これにより、図1のように1つずつのバイパスコア2a, 2bを備える場合よりも、バイパスコア2a1, 2a2, 2b1, 2b2を通る磁束の量を増大することができる。

**【0107】**

巻線3a, 4aに関連して3つ以上のバイパスコアを備え、巻線3b, 4bに関連して3つ以上のバイパスコアを備えてもよい。

**【0108】****[第1の実施形態の第6の変形例]**

図19は、第1の実施形態の第6の変形例に係る変圧器10Fの構成の一例を模式的に例示する正面図である。図19の変圧器10Fは、図1のバイパスコア2a, 2bに代えて、バイパスコア2Fa, 2Fbを備える。

**【0109】**

バイパスコア2Fa, 2Fbは、主コア1に沿って延在し、両端において主コア1に向かって屈曲する。

**【0110】**

図19の例では、バイパスコア2Faを「第1のバイパスコア」ともいい、バイパスコア2Fbを「第2のバイパスコア」ともいう。

**【0111】**

主コアとバイパスコアとの距離が十分に小さくない場合、バイパスコア2Fa, 2Fbを通る磁束は生じにくくなる。図19の変圧器10Fによれば、各バイパスコア2Fa, 2Fbの両端を屈曲することにより、主コア1と各バイパスコア2Fa, 2Fbとの距離が短くなる。これにより、図1の変圧器10の場合よりも、磁束がバイパスコア2Fa, 2Fbを通りやすくなり、バイパスコア2Fa, 2Fbを通る磁束の量を増大することができる。従って、図1の変圧器10の場合よりも、漏れインダクタンスを増大させることができる。

**【0112】****[第1の実施形態の第7の変形例]**

図20は、第1の実施形態の第7の変形例に係る変圧器10Gの構成の一例を模式的に例示する正面図である。図20の変圧器10Gは、図1のバイパスコア2a, 2bに代えて

10

20

30

40

50

、バイパスコア 2 G a , 2 G b を備える。

【 0 1 1 3 】

バイパスコア 2 G a , 2 G b は、主コア 1 に沿って延在し、両端において主コア 1 に沿つて屈曲する。

【 0 1 1 4 】

図 2 0 の例では、バイパスコア 2 G a を「第 1 のバイパスコア」ともいい、バイパスコア 2 G b を「第 2 のバイパスコア」ともいう。

【 0 1 1 5 】

前述のように、主コアとバイパスコアとが互いに対向する領域の面積が増大するほど、バイパスコア 2 G a , 2 G b を通る磁束の量が増大する。図 2 0 の変圧器 2 0 G によれば、各バイパスコア 2 G a , 2 G b の両端を屈曲することにより、主コア 1 とバイパスコア 2 G a , 2 G b とが互いに対向する領域の面積が増大する。これにより、図 1 の変圧器 1 0 の場合よりも、磁束がバイパスコア 2 G a , 2 G b を通りやすくなり、バイパスコア 2 G a , 2 G b を通る磁束の量を増大することができる。従って、図 1 の変圧器 1 0 の場合よりも、漏れインダクタンスを増大させることができる。

10

【 0 1 1 6 】

[ 第 1 の実施形態の第 8 の変形例 ]

図 2 1 は、第 1 の実施形態の第 8 の変形例に係る変圧器 1 0 H の構成の一例を模式的に例示する側面図である。図 2 2 は、図 2 1 の変圧器 1 0 H の構成の一例を模式的に例示する上面図である。図 2 1 の変圧器 1 0 H は、図 1 のバイパスコア 2 a , 2 b に代えて、バイパスコア 2 H a 1 ~ 2 H b 2 を備える。変圧器 1 0 H は、第 5 の変形例と第 7 の変形例との組み合わせに相当する。

20

【 0 1 1 7 】

バイパスコア 2 H a 1 , 2 H a 2 は、巻線 3 a を巻回した主コア 1 の区間に沿って、かつ、巻線 3 a の外側に設けられる。バイパスコア 2 H b 1 , 2 H b 2 は、巻線 3 b を巻回した主コア 1 の区間に沿って、かつ、巻線 3 b の外側に設けられる。巻線 4 a は、巻線 3 a を巻回した主コア 1 の区間ににおいて主コア 1 及びバイパスコア 2 H a 1 , 2 H a 2 に巻回される。巻線 4 b は、巻線 3 b を巻回した主コア 1 の区間ににおいて主コア 1 及びバイパスコア 2 H b 1 , 2 H b 2 に巻回される。バイパスコア 2 H a 1 ~ 2 H b 2 は、主コア 1 に沿って延在し、両端において主コア 1 に沿って屈曲する。

30

【 0 1 1 8 】

図 2 1 に示すように、各バイパスコア 2 H a 1 , 2 H a 2 は、その両端において互いに接してもよい。同様に、各バイパスコア 2 H b 1 , 2 H b 2 は、その両端において互いに接してもよい。

【 0 1 1 9 】

図 2 1 の例では、バイパスコア 2 H a 1 , 2 H a 2 を「第 1 のバイパスコア」ともいい、バイパスコア 2 H b 1 , 2 H b 2 を「第 2 のバイパスコア」ともいう。

【 0 1 2 0 】

図 2 1 の変圧器 2 0 H によれば、図 1 7 の変圧器 1 0 E の場合よりも、また、図 2 0 の変圧器 1 0 G の場合よりも、漏れインダクタンスを増大することができる。

40

【 0 1 2 1 】

[ 第 2 の実施形態 ]

図 2 3 ~ 図 2 4 を参照して、第 2 の実施形態に係る電力変換装置について説明する。

【 0 1 2 2 】

[ 第 2 の実施形態の構成例 ]

図 2 3 は、第 2 の実施形態に係る電力変換装置の一例を模式的に例示する回路図である。図 2 3 の電力変換装置は、電流共振型の D C - D C コンバータの一例を示す。図 2 3 の電力変換装置は、変圧器 1 0 、直流電源 2 1 、駆動回路 2 2 、負荷 2 3 、キャパシタ C 1 , C 2 、ダイオード D 5 , D 6 、及びスイッチ素子 Q 1 , Q 2 を備える。

【 0 1 2 3 】

50

直流電源 2 1 は、直流の入力電圧  $V_{in}$  を供給する。スイッチ素子 Q 1 , Q 2 は、駆動回路 2 2 の制御下で動作する。図 2 3 の変圧器 1 0 は、例えば、図 1 の変圧器 1 0 と同様に構成される。変圧器 1 0 は、等価的に、インダクタ  $L_r$ ,  $L_m$  を含む。インダクタ  $L_r$ ,  $L_m$  及びキャパシタ  $C_1$  は、共振回路を構成する。変圧器 1 0 は、図 9 及び図 1 0 を参照して説明したように、ダイオード D 5 , D 6 を含む、センタータップを利用した整流回路に接続される。整流された電圧はキャパシタ  $C_2$  によって平滑化され、平滑化された出力電圧  $V_{out}$  及び出力電流  $I_{out}$  は負荷 2 3 に供給される。

#### 【 0 1 2 4 】

図 2 4 は、図 2 3 の電力変換装置の共振回路の動作の一例を模式的に例示するグラフである。図 2 4 のグラフは、図 2 3 のインダクタ  $L_r$ ,  $L_m$  及びキャパシタ  $C_1$  を含む共振回路の周波数特性であって、インダクタ  $L_r$  のインダクタンスが小さいとき及び大きいときの周波数特性を示す。図 2 3 の電力変換装置では、スイッチ素子 Q 1 , Q 2 のスイッチング周波数を下げることで、共振回路の利得が増大する。この制御法により、入力電圧  $V_{in}$  の変動に対処し、また、負荷 2 3 の変動に対処することができる。しかしながら、図 2 4 によれば、インダクタ  $L_r$  のインダクタンスを調節することで、スイッチング周波数を変化させることなく共振回路の最大利得が増加することがわかる。周波数  $f_1$  では、インダクタ  $L_r$  のインダクタンスが大きいときの利得が、インダクタ  $L_r$  のインダクタンスが小さいときの利得よりも高くなる。一方、周波数  $f_2$  では、インダクタ  $L_r$  のインダクタンスが小さいときの利得が、インダクタ  $L_r$  のインダクタンスが大きいときの利得よりも高くなる。これにより、スイッチング周波数を大幅に高くしたり大幅に低下させたりすることなく、入力電圧及び負荷のワイドレンジ化を達成することができる。

10

#### 【 0 1 2 5 】

本開示の実施形態に係る変圧器 1 0 によれば、変圧器 1 0 の漏れインダクタンスがインダクタ  $L_r$  として作用する。従って、図 2 3 の電力変換装置では、インダクタ  $L_r$  の部品を追加することなく、共振回路のインダクタンスを調節することができる。追加のインダクタ  $L_r$  が不要であることにより、電力変換装置の電力密度を増大することができる。

20

#### 【 0 1 2 6 】

本実施形態に係る電力変換装置によれば、変圧器 1 0 を備えたことにより、変圧器 1 0 の損失を増大させることなく、励磁インダクタンスを調整することができ、変圧器 1 0 の漏れインダクタンスを増大させることができる。また、変圧器 1 0 の漏れインダクタンスが共振することにより、電力変換装置の利得を増大することができる。従って、本実施形態によれば、高い電力密度を有する電力変換装置を実現することができる。

30

#### 【 0 1 2 7 】

本実施形態に係る電力変換装置では、図 1 の変圧器 1 0 に代えて、他の変形例に係る変圧器 1 0 A ~ 1 0 H を用いてもよい。

#### 【 0 1 2 8 】

本開示の実施形態によれば、図 2 3 に示す回路に限らず、変圧器を含む他の電力変換装置を提供してもよい。

#### 【 0 1 2 9 】

本開示の実施形態によれば、電力変換装置に限らず、変圧器を含む他の電子回路を提供してもよい。

40

#### 【 0 1 3 0 】

#### 【 他の変形例 】

以上、本開示の実施形態を詳細に説明してきたが、前述までの説明はあらゆる点において本開示の例示に過ぎない。本開示の範囲を逸脱することなく種々の改良や変形を行うことができることは言うまでもない。例えば、以下のような変更が可能である。なお、以下では、上記実施形態と同様の構成要素に関しては同様の符号を用い、上記実施形態と同様の点については、適宜説明を省略した。

#### 【 0 1 3 1 】

上述した各実施形態及び各変形例は、任意に組み合わさってもよい。

50

**【 0 1 3 2 】**

本明細書で説明した実施形態は、あらゆる点において本開示の例示に過ぎない。本開示の範囲を逸脱することなく種々の改良や変形を行うことはできるとは言うまでもない。つまり、本開示の実施にあたって、実施形態に応じた具体的構成が適宜採用されてもよい。

**【 0 1 3 3 】**

図1他では、矩形の主コアを示したが、これに限定されない。主コアは矩形以外の形状、例えばリング形状を有してもよい。

**【 0 1 3 4 】**

図1他では、主コアが2つの主コア部分からなる場合について説明したが、これに限定されない。主コアは3つ以上の主コア部分から構成されてもよい。

10

**【 0 1 3 5 】**

図1他では、巻線3a～4bが2つの区間A1, A2に巻回される場合について説明したが、これに限定されない。巻線3a～4bは、主コアのループのうちの互いに離れた3つ以上の区間ににおいて主コアに巻回されてもよく、図16に示すように、1つの区間ににおいて主コアに巻回されてもよい。巻線3a～4bを巻回した区間の個数に応じて、3つ以上のバイパスコアが設けられてもよく、図16に示すように、1つのバイパスコアが設けられてもよい。

**【 0 1 3 6 】**

バイパスコアの形状及び個数は、主コアからバイパスコアを介して再び主コアに戻る磁束（すなわち、バイパスコアを通る磁束）を発生するのであれば、図1、図17～図22等に示すものに限定されず、他の任意の形状及び個数であってもよい。

20

**【 0 1 3 7 】****[まとめ]**

本開示の各側面に係る変圧器及び電力変換装置は、以下のように表現されてもよい。

**【 0 1 3 8 】**

本開示の第1の側面に係る変圧器(10, 10A～10H)は、

ループの形状を有する主コア(1, 1A～1C)と、

前記主コア(1, 1A～1C)のループのうちの第1の区間(A1)において前記主コア(1, 1A～1C)に巻回された第1の巻線(3a)と、

前記主コア(1, 1A～1C)のループのうちの前記第1の区間(A1)から離れた第2の区間(A2)において前記主コア(1, 1A～1C)に巻回された第2の巻線(3b)と、

30

前記主コア(1, 1A～1C)の前記第1の区間(A1)に沿って、かつ、前記第1の巻線(3a)の外側に設けられた少なくとも1つの第1のバイパスコア(2a)と、

前記主コア(1, 1A～1C)の前記第1の区間(A1)において前記主コア(1, 1A～1C)及び前記第1のバイパスコア(2a)に巻回された第3の巻線(4a)と、

前記主コア(1, 1A～1C)の前記第2の区間(A2)に沿って、かつ、前記第2の巻線(3b)の外側に設けられた少なくとも1つの第2のバイパスコア(2b)と、

前記主コア(1, 1A～1C)の前記第2の区間(A2)において前記主コア(1, 1A～1C)及び前記第2のバイパスコア(2b)に巻回された第4の巻線(4b)と、

40

前記主コア(1, 1A～1C)の前記第1及び第2の区間(A1, A2)の両方から離れた位置において前記主コア(1, 1A～1C)のループに交差するように前記主コア(1, 1A～1C)に形成された少なくとも1つのギャップ(G)とを備える。

**【 0 1 3 9 】**

本開示の第2の側面に係る変圧器(10, 10A～10H)によれば、第1の側面に係る変圧器において、

前記第1のバイパスコア(2a)は、前記第1の区間(A1)の長さを超える長さにわたって延在し、

前記第2のバイパスコア(2b)は、前記第2の区間(A2)の長さを超える長さにわたって延在する。

50

**【 0 1 4 0 】**

本開示の第3の側面に係る変圧器(10, 10A~10H)によれば、第2の側面に係る変圧器において、

前記第1及び第2のバイパスコア(2a, 2b)は、前記主コア(1, 1A~1C)に沿って延在し、両端において前記主コア(1, 1A~1C)に向かって又は前記主コア(1, 1A~1C)に沿って屈曲する。

**【 0 1 4 1 】**

本開示の第4の側面に係る変圧器(10, 10A~10H)は、第1~第3のうちの1つの側面に係る変圧器において、

複数の第1のバイパスコア(2a1, 2a2; 2Ha1, 2Ha2)及び複数の第2のバイパスコア(2b1, 2b2; 2Hb1, 2Hb2)を備える。10

**【 0 1 4 2 】**

本開示の第5の側面に係る変圧器(10, 10A~10H)によれば、第1~第4のうちの1つの側面に係る変圧器において、

前記第1及び第3の巻線(3a, 4a)はそれぞれ、1周ごとに前記主コア(1, 1A~1C)の表面に接するように、かつ、前記主コア(1, 1A~1C)の表面において交互に配置されるように巻回され、

前記第2及び第4の巻線(3b, 4b)はそれぞれ、1周ごとに前記主コア(1, 1A~1C)の表面に接するように、かつ、前記主コア(1, 1A~1C)の表面において交互に配置されるように巻回される。20

**【 0 1 4 3 】**

本開示の第6の側面に係る変圧器(10, 10A~10H)は、第1~第5のうちの1つの側面に係る変圧器において、

前記主コア(1, 1A~1C)のループのうちの前記第1の区間(A1)の一端と前記第2の区間(A2)の一端との間の第3の区間(A3)において、前記主コア(1, 1A~1C)のループに交差するように前記主コア(1, 1A~1C)に形成された少なくとも1つのギャップ(G)と、

前記主コア(1, 1A~1C)のループのうちの前記第1の区間(A1)の他端と前記第2の区間(A2)の他端との間の第4の区間(A4)において、前記主コア(1, 1A~1C)のループに交差するように前記主コア(1, 1A~1C)に形成された少なくとも1つのギャップ(G)とを備える。30

**【 0 1 4 4 】**

本開示の第7の側面に係る変圧器(10, 10A~10H)は、第6の側面に係る変圧器において、

前記第3及び第4の区間(A3, A4)のうちの少なくとも一方において、前記主コア(1C)のループに交差するように前記主コア(1C)に形成された複数のギャップ(G)を備える。

**【 0 1 4 5 】**

本開示の第8の側面に係る変圧器(10, 10A~10H)は、第1~第7のうちの1つの側面に係る変圧器において、40

前記変圧器は第1~第4の端子を備え、

前記第1及び第2の巻線(3a, 3b)は、前記第1及び第2の端子の間に電流が流れるときに前記第1及び第2の巻線(3a, 3b)により前記主コア(1, 1A~1C)のループに沿って同じ向きの磁束を発生するように、前記第1及び第2の端子の間に直列に接続され、

前記第3及び第4の巻線(4a, 4b)は、前記第3及び第4の端子の間に電流が流れるときに前記第3及び第4の巻線(4a, 4b)により前記主コア(1, 1A~1C)のループに沿って同じ向きの磁束を発生するように、前記第3及び第4の端子の間に直列に接続される。

**【 0 1 4 6 】**

10

20

30

40

50

本開示の第9の側面に係る変圧器(10, 10A~10H)は、第1~第7のうちの1つの側面に係る変圧器において、

前記変圧器は第1~第5の端子を備え、

前記第1及び第2の巻線(3a, 3b)は、前記第1及び第2の端子の間に電流が流れるときに前記第1及び第2の巻線(3a, 3b)により前記主コア(1, 1A~1C)のループに沿って同じ向きの磁束を発生するように、前記第1及び第2の端子の間に直列に接続され、

前記第3の巻線(4a)は、前記第3及び第5の端子の間に接続され、

前記第4の巻線(4b)は、前記第4及び第5の端子の間に接続され、

前記第3及び第4の巻線(4a, 4b)は、前記第5の端子から前記第3及び第4の端子にそれぞれ電流が流れるときに前記第3及び第4の巻線(4a, 4b)により前記主コア(1, 1A~1C)のループに沿って同じ向きの磁束を発生するように互いに接続される。 10

#### 【0147】

本開示の第10の側面に係る変圧器(10, 10A~10H)は、第1~第7のうちの1つの側面に係る変圧器において、

前記変圧器は第1~第5の端子を備え、

前記第1の巻線(3a)は、前記第1及び第5の端子の間に接続され、

前記第2の巻線(3b)は、前記第2及び第5の端子の間に接続され、

前記第1及び第2の巻線(3a, 3b)は、前記第5の端子から前記第1及び第2の端子にそれぞれ電流が流れるときに前記第1及び第2の巻線(3a, 3b)により前記主コア(1, 1A~1C)のループに沿って同じ向きの磁束を発生するように互いに接続され、前記第3及び第4の巻線(4a, 4b)は、前記第3及び第4の端子の間に電流が流れるときに前記第3及び第4の巻線(4a, 4b)により前記主コア(1, 1A~1C)のループに沿って同じ向きの磁束を発生するように、前記第3及び第4の端子の間に直列に接続される。 20

#### 【0148】

本開示の第11の側面に係る電力変換装置は、第1~第10のうちの1つの側面に係る変圧器(10, 10A~10H)を備える。

#### 【産業上の利用可能性】

#### 【0149】

本開示の各側面に係る変圧器は、例えば、高い電力密度を有する電力変換装置に適用可能である。 30

#### 【符号の説明】

#### 【0150】

1, 1A~1D...主コア、

1a, 1b, 1Aa~1Da, 1Ab~1Db, 1Cc...主コア部分、

2a, 2b, 2a1~2b2, 2Fa, 2Fb, 2Ga, 2Gb, 2Ha1~2Hb2...

バイパスコア、

3a, 3b, 4a, 4b...巻線、

5, 6...スペーサ、

10, 10A~10H...変圧器、

21...直流電源、

22...駆動回路、

23...負荷、

C1, C2...キャパシタ、

D1~D8...ダイオード、

G...ギャップ、

Q1, Q2...スイッチ素子。 40

10

20

30

40

50

## 【図面】 【図 1】

【 図 2 】

【図3】

【図4】

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

【図 1 3】

【図 1 4】

10

【図 1 5】

【図 1 6】

20

【図 1 7】

【図 1 8】

30

40

50

【図 1 9】

【図 2 0】

10

【図 2 1】

【図 2 2】

20

30

40

50

【図 2 3】

【図 2 4】

10

20

30

40

50

---

フロントページの続き

不動堂町 801 番地 オムロン株式会社内

(72)発明者 財津 俊行

京都府京都市下京区塩小路通堀川東入南不動堂町 801 番地 オムロン株式会社内

(72)発明者 上松 武

京都府京都市下京区塩小路通堀川東入南不動堂町 801 番地 オムロン株式会社内

審査官 井上 健一

(56)参考文献 特開 2016 - 219540 (JP, A)

特開 2001 - 203112 (JP, A)

特開平 10 - 163046 (JP, A)

特開昭 54 - 120828 (JP, A)

特開昭 53 - 24530 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01F 38/08

H01F 27/24