(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7072462号

(P7072462)

(45)発行日 令和4年5月20日(2022.5.20)

(24)登録日 令和4年5月12日(2022.5.12)

(51)国際特許分類

H 01 L 21/52 (2006.01)

B 22 F 3/105(2006.01)

F I

H 01 L 21/52

H 01 L 21/52

B 22 F 3/105

A

E

請求項の数 7 (全17頁)

(21)出願番号 特願2018-142168(P2018-142168)

(22)出願日 平成30年7月30日(2018.7.30)

(65)公開番号 特開2020-21756(P2020-21756A)

(43)公開日 令和2年2月6日(2020.2.6)

審査請求日 令和3年2月3日(2021.2.3)

(73)特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74)代理人 110001807

特許業務法人磯野国際特許商標事務所

鈴木 智久

東京都千代田区丸の内一丁目6番6号

株式会社日立製作所内

(72)発明者 守谷 浩志

東京都千代田区丸の内一丁目6番6号

株式会社日立製作所内

審査官 小池 英敏

最終頁に続く

(54)【発明の名称】 半導体装置、焼結金属シートおよび焼結金属シートの製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体素子が焼結金属層を介して支持基板の上に接合されてなる半導体装置であって、前記焼結金属層には、接合されたときの前記半導体素子の外縁部よりも内側に当たる領域に、空孔率が他の領域よりも低い低空孔率領域が形成されており、前記焼結金属層の中には、前記低空孔率領域として、前記焼結金属層を上面側から下面側まで貫く柱状の低空孔率領域が形成されており、前記柱状の低空孔率領域は、前記半導体素子の外縁部よりも内側領域の直下に当たる前記焼結金属層の領域内の全域にわたって所定の間隔で複数個設けられていることを特徴とする半導体装置。

## 【請求項2】

請求項1に記載の半導体装置であって、前記焼結金属層の前記低空孔率領域は、前記焼結金属層の前記他の領域と同じ材料で構成されていることを特徴とする半導体装置。

## 【請求項3】

請求項1に記載の半導体装置であって、前記焼結金属層の中には、前記低空孔率領域として、前記焼結金属層を上面側から下面側まで貫き、平面形状が細長紐状を呈する壁状の低空孔率領域が形成されており、前記壁状の低空孔率領域は、前記半導体素子の外縁部に沿って、前記半導体素子の中央部

直下の領域を取り囲むように形成され、

前記柱状の低空孔率領域は、複数個、前記壁状の低空孔率領域に囲まれた内側の領域に形成されていること

を特徴とする半導体装置。

【請求項 4】

半導体素子と支持基板との間に配置されて、前記半導体素子と前記支持基板とを接合する焼結金属シートであって、

前記半導体素子と前記支持基板とを接合したとき、前記半導体素子の外縁部よりも内側に当たる領域に、空孔率が他の領域よりも低い低空孔率領域が形成されており、

前記焼結金属シートの中には、前記低空孔率領域として、前記焼結金属シートを上面側から下面側まで貫く柱状の低空孔率領域が形成されており、

前記柱状の低空孔率領域は、前記半導体素子の外縁部よりも内側領域の直下に当たる前記焼結金属シートの領域内の全域にわたって所定の間隔で複数個設けられていること

を特徴とする焼結金属シート。

【請求項 5】

請求項 4 に記載の焼結金属シートであって、

前記低空孔率領域を構成する材料は、前記他の領域を構成する材料と同じであること

を特徴とする焼結金属シート。

【請求項 6】

金属微粒子を含むペースト材を焼成して焼結金属シートを作製する工程と、

前記焼結金属シート上の所定の位置に、前記焼結金属シートを上面および下面から挟むように電極を配置し、前記電極に挟まれた前記焼結金属シートの領域に通電することにより、空孔率が他の領域よりも低い低空孔率領域を形成する工程と、

を有すること

を特徴とする焼結金属シートの製造方法。

【請求項 7】

請求項 6 に記載の焼結金属シートの製造方法であって、

前記低空孔率領域を形成する工程において、前記焼結金属シート上に前記電極を配置するときには、前記焼結金属シートの外縁部よりも内側の位置に配置すること

を特徴とする焼結金属シートの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力変換機器などに好適に用いられる半導体装置、焼結金属シートおよび焼結金属シートの製造方法に関する。

【背景技術】

【0002】

近年、電気自動車や鉄道をはじめ幅広い分野で、インバータなど電力変換機器用途のパワー・モジュールの市場拡大が続いている。そして、環境保護や省エネに対する意識の高まりを背景として、パワー・モジュールには電力変換のさらなる高効率化が求められている。しかしながら、Si 半導体を用いたパワーモジュールでは、電力変換の効率向上の限界が見えてきており、電力変換のさらなる高効率化を目指して、SiC 半導体などを用いた次世代パワーモジュールの開発が進められている。

【0003】

SiC 半導体を用いたパワーモジュールでは、200 以上の高温動作が可能となり、電力変換の高効率化のみならず、大幅な小型化・軽量化が可能となる。一方、200 以上の高温環境下では、従来チップ接合材として使用されてきた鉛フリーはんだは、再溶融の問題から使用できなくなるという問題が生じる。また、現在は RoHS (Restriction of Hazardous Substances) 指令から除外されている鉛含有率 85 % 以上の高融点はんだも、将来的には RoHS 指令の対象となるのは必至である。そのため、鉛フリーはんだの代

10

20

30

40

50

替材料の開発が急務となっている。

【0004】

鉛フリーはんだの代替材料としては、 $n\text{m} \sim \mu\text{m}$ オーダの金属粒子を焼結させた焼結金属接合材に期待が集まっており、銀（Ag）や銅（Cu）を用いた焼結接合技術に関して開発が進められている。焼結金属材による接合層は、例えば特許文献1に示されているように内部に空孔を含んだ多孔質構造となる。また、電力変換用などのパワーモジュールでは、例えば特許文献2に示されているように、焼結金属材を介して半導体素子を基板に接合することが行われている。

【0005】

さらに、特許文献1には、金属微粒子と有機溶剤とを混合した金属ペースト材を事前に加熱、仮焼結させて作成した焼結金属シートを基板に設置し、その上に半導体素子を搭載した後、再度加熱、焼結させて、半導体素子を基板に接合する方法が示されている。また、特許文献2には、金属微粒子と有機溶剤とを混合した金属ペースト材を基板上に塗布し、その上に半導体素子を搭載した後、加熱により金属ペースト材を焼結させ、半導体素子を基板に接合する方法が示されている。

10

【0006】

ところで、とくにパワーモジュールなどでは、半導体素子の稼働や環境温度などによる熱サイクルが繰り返されると、両者の熱膨張係数差により半導体素子と焼結金属層には熱ひずみが生じる。これにより、焼結金属層の端部に亀裂（クラック）が生じ、その亀裂が焼結金属層の面内方向に進展する。その結果、焼結金属層が熱伝導や電気伝導の機能を喪失することとなり、パワーモジュールが故障に至るという問題が生じる。

20

【0007】

焼結金属層に亀裂が生じにくくするには、焼結時の加圧を高くして焼結金属層の空孔率を低くすればよい。しかしながら、焼結時の加圧を高くし過ぎると焼結金属層の剛性が高くなりすぎ、半導体素子などの周辺部材にダメージが及び易くなるという別の問題が生じる。

【0008】

これらの問題に対し、特許文献2には、金属ペースト塗布時に塗布の厚さに差をつけることにより、半導体素子の側部に近い部分で空孔率が低く、中央に近い部分で空孔率が高くなる焼結金属層を形成する技術が開示されている。このような焼結金属層では、その外縁端部が硬く形成されるので、外縁端部からの亀裂の進展を抑制することができる。また、特許文献3には、2種類の金属ペーストを用いることで、半導体素子の周辺部や角部に中央部よりも空孔率の低い領域を有する焼結金属層を形成する技術が開示されている。また、特許文献4には、金属ペーストを塗布後に金属発泡体を配置し、これを焼結プロセスで緻密化させることにより、外縁部や角部に空孔率の低い領域を有する焼結金属層の形成技術が開示されている。

30

【先行技術文献】

【特許文献】

【0009】

【文献】特開2010-248617号公報

40

特開2015-216160号公報

国際公開第2014/155619号

特開2015-185559号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

以上のように、半導体素子を基板に接合する接合部材として焼結金属層を用いた場合には、焼結金属層の空孔率が高いため、つまり隙間が大きいために、焼結金属層の側部や角部から亀裂が生じやすいという問題がある。また、焼結金属層の空孔率を単純に低くするだけでは、焼結金属層と半導体素子との界面には応力が集中し、その界面で剥離が生じやす

50

くなるという問題がある。

【0011】

これらの問題解決のために、特許文献2～4に開示された焼結金属層においては、半導体素子の外縁部の直下部分に空孔率の低い領域を設ける構造が提案されている。しかしながら、この場合には、半導体素子の外縁部が受ける応力が増大する。この応力の増大により、半導体素子の外縁部で焼結金属層が剥離し易くなるだけでなく、半導体素子自身の破壊のリスクが増大することが問題となる。

【0012】

なお、特許文献4には、外縁部より内側に空孔率の低い領域を有する焼結金属層にも言及されているが、その空孔率の低い領域は、材料の金属ペーストを印刷後に印刷面の上部から別の部材（金属発泡体）をマウントする方法により形成される。そのため、マウントの作業性の問題から、配置される金属発泡体のサイズは、自立可能な程度に大きい必要がある。つまり、空孔率の低い領域を微細なパターンで形成することは難しい。

10

【0013】

以上の従来技術の問題に鑑み、本発明の目的は、剥離の発生、亀裂の進展、半導体素子破壊などのリスクを抑制することが可能な高信頼の半導体装置、焼結金属シートおよび焼結金属シートの製造方法を提供することにある。

【課題を解決するための手段】

【0014】

本発明は、半導体素子が焼結金属層を介して支持基板の上に接合されてなる半導体装置であって、前記焼結金属層には、接合されたときの前記半導体素子の外縁部よりも内側に当たる領域に、空孔率が他の領域よりも低い低空孔率領域が形成されており、前記焼結金属層の中には、前記低空孔率領域として、前記焼結金属層を上面側から下面側まで貫く柱状の低空孔率領域が形成されており、前記柱状の低空孔率領域は、前記半導体素子の外縁部よりも内側領域の直下に当たる前記焼結金属層の領域内の全域にわたって所定の間隔で複数個設けられていることを特徴とする。

20

【発明の効果】

【0015】

本発明によれば、剥離の発生、亀裂の進展、半導体素子破壊などのリスクを抑制することが可能な高信頼の半導体装置、焼結金属シートおよび焼結金属シートの製造方法が提供される。

30

【図面の簡単な説明】

【0016】

【図1A】本発明の第1の実施形態に係る半導体装置の断面構造の例を示した図。

【図1B】本発明の第1の実施形態に係る半導体装置の上面図の例を示した図。

【図2A】本発明の第1の実施形態に係る半導体装置と従来技術に係る半導体装置との構造の相違を示した図。

【図2B】本発明の第1の実施形態に係る半導体装置と従来技術に係る半導体装置との効果の相違を示した図。

【図3】本発明の第1の実施形態に係る半導体装置の焼結金属層の端部から発生した亀裂が焼結金属層の内部に進展し、低空孔率領域で阻止されて停止する様子を模式的に示した図。

40

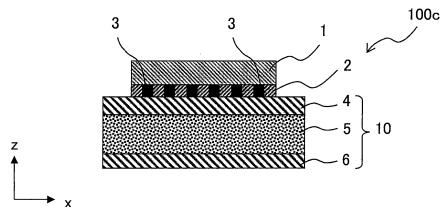

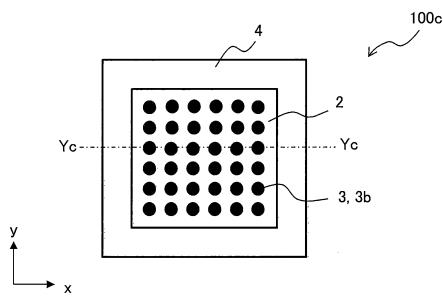

【図4A】本発明の第2の実施形態に係る半導体装置の断面構造の例を示した図。

【図4B】本発明の第2の実施形態に係る半導体装置の上面図の例を示した図。

【図5A】本発明の第3の実施形態に係る半導体装置の断面構造の例を示した図。

【図5B】本発明の第3の実施形態に係る半導体装置の上面図の例を示した図。

【図6A】本発明の第4の実施形態に係る半導体装置の断面構造の例を示した図。

【図6B】本発明の第4の実施形態に係る半導体装置の上面図の例を示した図。

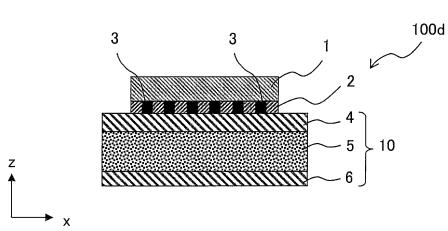

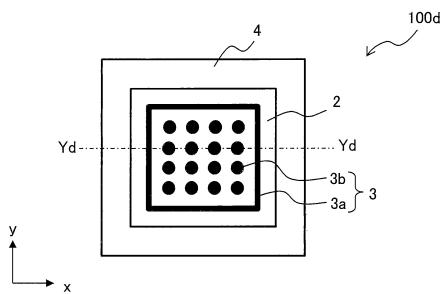

【図7A】本発明の第5の実施形態に係る半導体装置の断面構造の例を示した図。

【図7B】本発明の第5の実施形態に係る半導体装置の上面図の例を示した図。

50

【図 8 A】本発明の第 1 の実施形態に係る半導体装置の製造工程において、焼結金属層のシートを作製する工程の例を示した図。

【図 8 B】本発明の第 1 の実施形態に係る半導体装置の製造工程において、焼結金属層の中に低空孔率領域を形成し、焼結金属シートを作製する工程の例を示した図。

【図 8 C】本発明の第 1 の実施形態に係る半導体装置の製造工程において、焼結金属シートを用いて半導体装置製造する工程の例を示した図。

【図 9】通電による加熱の際の焼結金属層内部の温度分布を熱解析シミュレーションで計算した結果の例を示した図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について、図面を参照して詳細に説明する。なお、各図面において、共通する構成要素には同一の符号を付し、重複した説明を省略する。

【0018】

### 第 1 の実施形態

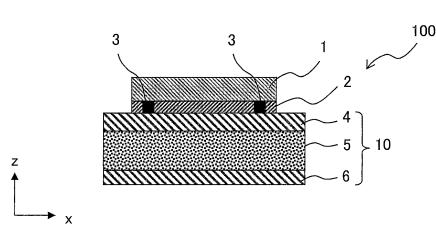

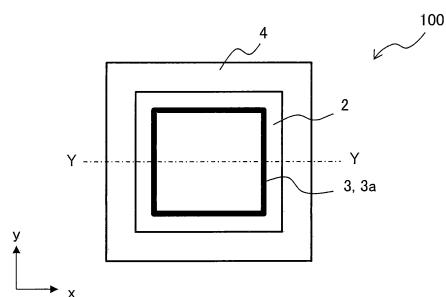

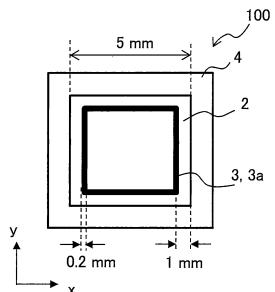

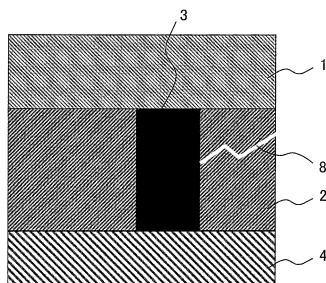

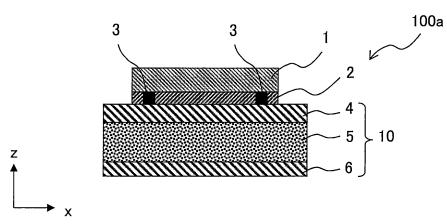

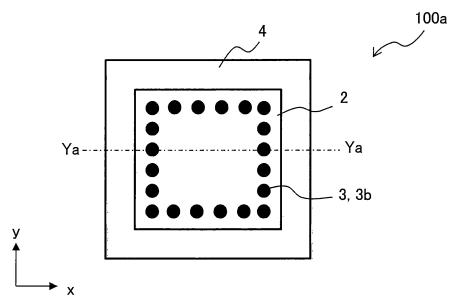

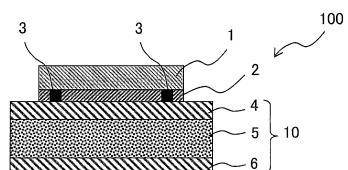

図 1 A は、本発明の第 1 の実施形態に係る半導体装置 100 の断面構造の例を示した図、図 1 B は、本発明の第 1 の実施形態に係る半導体装置 100 の上面図の例を示した図である。図 1 A、図 1 B に示すように、半導体装置 100 は、半導体素子 1 が焼結金属層 2 を介して支持基板 10 に接合されて構成される。ここで、図 1 B の半導体装置 100 の上面図は、半導体素子 1 が取り外されている状態の上面図を表し、また、図 1 A の断面図は、図 1 B の平面図の Y-Y 部分の半導体素子 1 を含む断面図を表している。

【0019】

半導体素子 1 は、電流制御用の IGBT (Insulated Gate Bipolar Transistor) やダイオードなどであり、シリコン (Si) や炭化シリコン (SiC)、窒化ガリウム (GaN) などの半導体材料により構成されている。この場合、半導体材料としては、電力損失の低い炭化シリコン (SiC)、窒化ガリウム (GaN) などのワイドバンドギャップ半導体を用いることが好ましい。

【0020】

支持基板 10 は、導電部材 4、絶縁部材 5 および冷却部材 6 からなる 3 層の積層構造を有している。ここで、導電部材 4 および冷却部材 6 は、いずれも銅 (Cu) やアルミニウム (Al) などの電気伝導度や熱伝導度の高い導電材料により構成されている。また、絶縁部材 5 は、窒化アルミニウム (AlN)、窒化シリコン (Si3N4)、酸化アルミニウム (Al2O3)、樹脂シート、グリースなどの絶縁材料によって構成される。

【0021】

なお、半導体装置 100 の断面構造は、これに限定されるものではなく、半導体素子 1 の周囲が封止材で覆われた構造などであってもよい。その場合、封止材としては、エポキシ樹脂などの熱硬化性樹脂とシリカフィラーからなる絶縁材料やシリコーンゲルなどが用いられる。また、支持基板 10 は、全体が導電部材 4 だけで構成されるものであってもよい。また、図 1 A には、半導体装置 100 として、支持基板 10 上に 1 つの半導体素子 1 が接合されたものしか示されていないが、半導体装置 100 は、1 つの支持基板 10 上に複数の半導体素子 1 が接合されたものであってもよい。

【0022】

焼結金属層 2 は、Ag, Cu, Au, Ni, Pt などの nm ~ μm オーダの金属微粒子と有機溶剤とを混合したペースト材を焼成して得られる焼結金属接合材によって構成される。この場合、ペーストの金属微粒子としては、Ag や Cu を用いることが好ましい。なお、こうして得られる焼結金属接合材は、内部に多数の空孔を有する多孔質体となっている。

【0023】

本実施形態では、焼結金属層 2 の中に他の領域よりも空孔率の低い領域である低空孔率領域 3 が設けられている。低空孔率領域 3 は、焼結金属層 2 と同じ組成のペースト材を焼結した焼結金属接合材からなり、空孔率が他の領域よりも低いことを特徴とする。この低空孔率領域 3 は、図 1 B に示すように、接合されたときの半導体素子 1 の外縁部よりも内側

10

20

30

40

50

に当たる焼結金属層 2 の中に、半導体素子 1 の外縁部に沿ってその外縁部を 1 周するよう に形成される。また、低空孔率領域 3 は、図 1 A に示すように、焼結金属層 2 の上面部か ら下面部まで焼結金属層 2 を貫くように形成される。

【 0 0 2 4 】

したがって、本実施形態では、低空孔率領域 3 は、焼結金属層 2 を平面的に外側の高空孔率領域と内側の高空孔率領域に 2 分する、平面形状が細長紐状を呈する壁状の構造体とい うことができる。このような低空孔率領域 3 は、平面的には、必ずしも直線状に形成され る必要はなく、うねりのある曲線状に形成されたものであってもよい。ただし、その平面 形状は、応力による変形の偏りを避けるために、対称的なパターンであることが好ましい。

【 0 0 2 5 】

なお、低空孔率領域 3 の空孔率は、低空孔率領域 3 以外の焼結金属層 2 における領域の空 孔率と比べて少なくとも 10 % 以上低いことが好ましく、さらには、低空孔率領域 3 の空 孔率が 10 % 未満であることが好ましい。また、低空孔率領域 3 の上下方向 ( z 軸方向 ) の構造は、空孔率が一定の 1 層に限定されるものではなく、例えば、空孔率が連続的に変 化するような多数の層から構成されるものであってもよい。

【 0 0 2 6 】

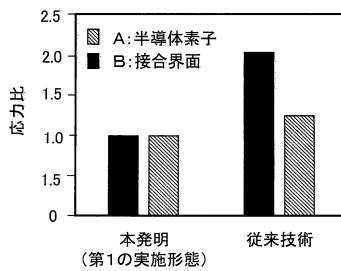

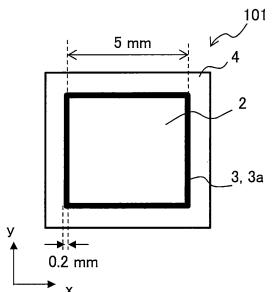

図 2 A は、本発明の第 1 の実施形態に係る半導体装置 100 と従来技術に係る半導体装置 101 との構造の相違を示した図、図 2 B は、本発明の第 1 の実施形態に係る半導体装置 100 と従来技術に係る半導体装置 101 との効果の相違を示した図である。

なお、図 2 A の左側上段および下段の図は、第 1 の実施形態に係る半導体装置 100 の断 面構造および上面図であり、実質的には、図 1 と同じ図である。ただし、その断面構造は 、半導体装置 100 の外縁部の構造として示されている。また、図 2 A の右側上段および 下段の図は、従来技術に係る半導体装置 101 の断面構造および上面図であり、その断面 構造は、半導体装置 101 の外縁部の構造として示されている。

【 0 0 2 7 】

図 2 B には、第 1 の実施形態に係る半導体装置 100 および従来の半導体装置 101 のそ れぞれにおける半導体素子 1 が受ける応力を計算して比較した結果が示されている。この 応力の計算では、本実施形態に係る半導体装置 100 および従来技術に係る半導体装置 101 のそれぞれに対し、次のような条件を設定した。

【 0 0 2 8 】

図 2 A に示すように、第 1 の実施形態および従来技術のいずれの場合も、半導体素子 1 の チップサイズを 5 mm × 5 mm とした。また、第 1 の実施形態では、焼結金属層 2 内の低 空孔率領域 3 は、半導体素子 1 の外縁部よりも 1 mm 内側の直下位置に、0.2 mm の幅 で設けられているものとした。これに対し、従来技術では、低空孔率領域 3 は、半導体素 子 1 の外縁部直下の位置、つまり焼結金属層 2 の外縁部に 0.2 mm の幅で設けられてい るものとした。また、焼結金属層 2 は、いずれの場合も厚さ 50 μm の焼結銅 ( Cu ) 層 であるとした。

【 0 0 2 9 】

さらに、半導体素子 1 は Si 、絶縁部材 5 は AlN 、導電部材および冷却部材は Cu であるとし、半導体装置 100, 101 全体に 200 ℃ から -40 ℃ の温度変化を与えた際の 応力分布を有限要素解析によって計算した。

【 0 0 3 0 】

その計算の結果、半導体素子 1 が受ける応力は、図 2 B に示されているように、第 1 の実 施形態では従来技術に比べ位置 A で約 1/1.3 に減少し、位置 B で 1/2.1 に減少し た。なお、図 2 A に示されているように、位置 A は、半導体素子 1 の外周端部の上下中央 位置を表し、位置 B は、半導体素子 1 と焼結金属層 2 との界面の外周端部位置を表して いる。

【 0 0 3 1 】

以上に説明したように、本実施形態では、従来技術に比べて半導体素子 1 が受ける応力が 小さくなるので、半導体素子 1 が受けるダメージが減少し、さらには半導体素子 1 が破壊

10

20

30

40

50

するリスクも減少する。また、半導体素子 1 と焼結金属層 2 との剥離のリスクも減少する。

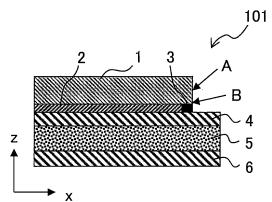

【 0 0 3 2 】

図 3 は、第 1 の実施形態に係る半導体装置 1 0 0 の焼結金属層 2 の端部から発生した亀裂 8 が焼結金属層 2 の内部に進展し、低空孔率領域 3 で阻止されて停止する様子を模式的に示した図である。本実施形態では、焼結金属層 2 の外縁部が高空孔率領域となるため、外周端部から亀裂が生じやすくなる。しかしながら、焼結金属層 2 の外周端部から亀裂が発生し、内部へ進展して行っても、その内側の位置に壁状の低空孔率領域 3 が設けられているため、その亀裂の進展は、低空孔率領域 3 で阻止されて停止することになる。これは、低空孔率領域 3 では、空孔の密度が低く金属組織が緻密になるため、亀裂が進展しにくくなるためである。したがって、本実施形態では、焼結金属層 2 の端部で生じる亀裂が中央部へ進展するのを抑制する効果を期待することができる。

10

【 0 0 3 3 】

以上のように、本実施形態では、従来技術に比べ、熱変動に由来する応力により半導体素子 1 と焼結金属層 2 とが剥離したり、半導体素子 1 が破壊などのダメージを受けたりするリスクが減少する。また、焼結金属層 2 の端部から発生する亀裂も、低空孔率領域 3 が設けられた位置で停止させることができる。よって、本実施形態では、熱変動に強い信頼性の高い半導体装置 1 0 0 が得られる。

【 0 0 3 4 】

第 2 の実施形態

図 4 A は、本発明の第 2 の実施形態に係る半導体装置 1 0 0 a の断面構造の例を示した図、図 4 B は、本発明の第 2 の実施形態に係る半導体装置 1 0 0 a の上面図の例を示した図である。図 4 A、図 4 B に示すように、半導体装置 1 0 0 a は、半導体素子 1 が焼結金属層 2 を介して支持基板 1 0 に接合されて構成される。ここで、図 4 B の半導体装置 1 0 0 a の上面図は、半導体素子 1 が取り外されている状態の上面図を表し、また、図 4 A の断面図は、図 4 B の平面図の Y a - Y a 部分の半導体素子 1 を含む断面図を表している。

20

【 0 0 3 5 】

図 4 A、図 4 B と図 1 A、図 1 B とを比較すれば容易に分かるように、本実施形態に係る半導体装置 1 0 0 a と第 1 の実施形態に係る半導体装置 1 0 0 との相違は、焼結金属層 2 の中に設けられた低空孔率領域 3 の形状にある。このことを除けば、両者の構造は、ほぼ同じであるので、以下、主に、第 1 の実施形態と相違する事項について説明する。

30

【 0 0 3 6 】

図 4 B に示すように、本実施形態では、低空孔率領域 3 は、好ましくは上面から見たときに角部のない形状（円形や橢円形など）となるように形成される。これは、応力が角部に集中しやすいので、これを避けることを目的としたものである。また、低空孔率領域 3 は、側面から見ると柱状に見えるが、その柱は、真直な円柱状の柱でなくともよく、樽型やくびれ型など曲面を有する柱でもあってもよい。また、その柱は、斜めに傾斜した柱などであってもよい。なお、これらの柱の径は、少なくとも焼結金属層 2 内の空孔の径よりも大きく、焼結金属層 2 の厚さより小さい、例えば、5  $\mu\text{m}$  ~ 1 0 0  $\mu\text{m}$  程度とするのが好ましい。

【 0 0 3 7 】

本実施形態では、図 4 B に示すように、柱状の低空孔率領域 3 が複数個連なって、接合される半導体素子 1 の外縁部よりも内側に当たる焼結金属層 2 の中に、半導体素子 1 の外縁部に沿って半導体素子 1 の中央部直下の領域を取り囲むように形成される。この際、柱状の低空孔率領域 3 は、図 4 B のように 1 列に並んで形成される必要はなく、半導体素子 1 の外縁部に沿って形成されていれば、複数列であったり、千鳥配置であったり、ランダムな配置であってもよい。ただし、応力による変形の偏りを避けるために、その配置の平面形状は、対称的なパターンであることが好ましい。

40

【 0 0 3 8 】

また、本実施形態でも、低空孔率領域 3 は、焼結金属層 2 と同じ組成のペースト材を焼結した焼結金属接合材からなり、空孔率が他の領域よりも高いことを特徴とする。この場合

50

、低空孔率領域3の空孔率は、低空孔率領域3以外の焼結金属層2の領域における空孔率と比べて少なくとも10%以上低いことが好ましく、さらには、低空孔率領域3の空孔率が10%未満であることが好ましい。

#### 【0039】

以上、本実施形態によれば、焼結金属層2の外周端部で発生し、内部へ進展する亀裂は、低空孔率領域3に突き当たり易くなるので、亀裂の進展を抑制する効果を期待することができる。また、低空孔率領域3が微小な柱からなることで、せん断変形に対して柔軟性を有することとなる。そのため、半導体素子1との界面における剥離や、半導体素子1を含む周辺部材へのダメージを低減させることができる。さらに、低空孔率領域3が微小な柱からなることで、焼結金属層2の面に沿った方向の亀裂よりも厚さ方向の亀裂が生じやすくなるが、厚さ方向の亀裂は、焼結金属層2の熱伝導性や電気伝導性を損なわない。逆に、厚さ方向に亀裂が進展することで、焼結金属層2における応力が緩和されるため、後続する亀裂の発生や進展が抑制されるという効果も期待することができる。

#### 【0040】

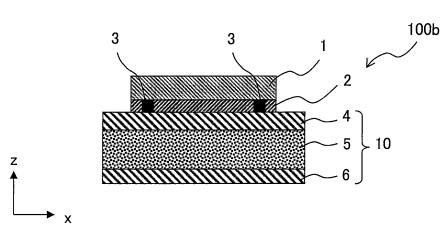

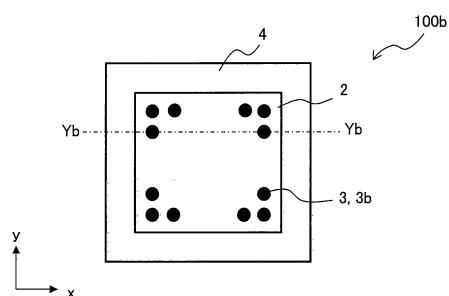

##### 第3の実施形態

図5Aは、本発明の第3の実施形態に係る半導体装置100bの断面構造の例を示した図、図5Bは、本発明の第3の実施形態に係る半導体装置100bの上面図の例を示した図である。図5A、図5Bに示すように、半導体装置100bは、半導体素子1が焼結金属層2を介して支持基板10に接合されて構成される。ここで、図5Bの半導体装置100bの上面図は、半導体素子1が取り外されている状態の上面図を表し、また、図5Aの断面図は、図5Bの平面図のYb-Yb部分の半導体素子1を含む断面図を表している。

#### 【0041】

図5A、図5Bと図4A、図4Bとを比較すれば容易に分かるように、本実施形態に係る半導体装置100bと第2の実施形態に係る半導体装置100aとの相違は、焼結金属層2の中に設けられた柱状の低空孔率領域3の配置の仕方にある。このことを除けば、両者の構造は、ほぼ同じであるので、以下、主に、第2の実施形態と相違する事項について説明する。

#### 【0042】

本実施形態でも、第2の実施形態と同様に、焼結金属層2の中に柱状の低空孔率領域3が設けられる。ただし、本実施形態では、この柱状の低空孔率領域3は、図5Bに示すように、半導体素子1の外縁部より内側の4つの角部近傍直下に相当する焼結金属層2の中に設けられる。

#### 【0043】

これは、焼結金属層2が矩形である場合、焼結金属層2の中で発生する亀裂は、応力が集中しがちな4つの角部で発生するケースが多いことを考慮したものである。すなわち、本実施形態では、柱状の低空孔率領域3を焼結金属層2の4つの角部近傍に設けることにより、焼結金属層2の端部で発生する亀裂の進展を効率よく抑制することができる。また、本実施形態では、焼結金属層2の中に形成される柱状の低空孔率領域3の数が少なくて済むので、低空孔率領域3を形成する製造プロセスの工程が簡便になるという効果を期待することができる。

#### 【0044】

なお、図5Bでは、低空孔率領域3は、焼結金属層2の各角部近傍に3つずつしか設けられていないが、その数は3つに限定されない。また、低空孔率領域3は、焼結金属層2の各角部の近傍に配置されていれば、どのように配置されていてもよい。ただし、応力による変形の偏りを避けるために、その配置の平面形状は、対称的なパターンであることが好ましい。

#### 【0045】

##### 第4の実施形態

図6Aは、本発明の第4の実施形態に係る半導体装置100cの断面構造の例を示した図、図6Bは、本発明の第4の実施形態に係る半導体装置100cの上面図の例を示した図

10

20

30

40

50

である。図 6 A、図 6 B に示すように、半導体装置 100 c は、半導体素子 1 が焼結金属層 2 を介して支持基板 10 に接合されて構成される。ここで、図 6 B の半導体装置 100 c の上面図は、半導体素子 1 が取り外されている状態の上面図を表し、また、図 6 A の断面図は、図 6 B の平面図の Yc - Yc 部分の半導体素子 1 を含む断面図を表している。

#### 【 0 0 4 6 】

図 6 A、図 6 B と図 4 A、図 4 B とを比較すれば容易に分かるように、本実施形態に係る半導体装置 100 c と第 2 の実施形態に係る半導体装置 100 a との相違は、焼結金属層 2 の中に設けられた柱状の低空孔率領域 3 の配置の仕方にある。このことを除けば、両者の構造は、ほぼ同じであるので、主に、第 2 の実施形態と相違する事項について説明する。

#### 【 0 0 4 7 】

本実施形態でも、第 2 の実施形態と同様に、焼結金属層 2 の中に柱状の低空孔率領域 3 が設けられる。本実施形態では、この低空孔率領域 3 は、図 6 B に示すように、半導体素子 1 の外縁部よりも内側領域の直下に当たる焼結金属層 2 の領域内の全域にわたって所定の間隔で敷き詰められるようにして設けられる。したがって、本実施形態でも、焼結金属層 2 の端部で生じる亀裂が焼結金属層 2 の面に沿って、中央部へ進展するのを抑制する効果を期待することができる。

#### 【 0 0 4 8 】

また、本実施形態では、焼結金属層 2 において生じる亀裂は、厚さ方向に誘導されやすくなるが、厚さ方向の亀裂は、焼結金属層 2 の熱伝導性や電気伝導性を損なわない。逆に、厚さ方向に亀裂が進展することで、焼結金属層 2 における応力が緩和されるため、その後の亀裂の発生や進展が抑制されるという効果も期待することができる。

#### 【 0 0 4 9 】

また、本実施形態では、半導体素子 1 と支持基板 10 の導電部材 4 との間の全域にわたって熱伝導性や電気伝導性に優れた柱状の低空孔率領域 3 が多数設けられることになるので、焼結金属層 2 の放熱性や電気伝導性が向上する効果を期待することができる。

#### 【 0 0 5 0 】

なお、柱状の低空孔率領域 3 は、焼結金属層 2 の中において、図 6 B のように一定の間隔で規則的に配置される必要はなく、焼結金属層 2 内の全域にわたって多数配置されたものであればよい。ただし、応力による変形の偏りを避けるために、その全体の配置は、平面的に対称的なパターンとなることが好ましい。

#### 【 0 0 5 1 】

##### 第 5 の実施形態

図 7 A は、本発明の第 5 の実施形態に係る半導体装置 100 d の断面構造の例を示した図、図 7 B は、本発明の第 5 の実施形態に係る半導体装置 100 d の上面図の例を示した図である。図 7 A、図 7 B に示すように、半導体装置 100 d は、半導体素子 1 が焼結金属層 2 を介して支持基板 10 に接合されて構成される。ここで、図 7 B の半導体装置 100 d の上面図は、半導体素子 1 が取り外されている状態の上面図を表し、また、図 7 A の断面図は、図 7 B の平面図の Yd - Yd 部分の半導体素子 1 を含む断面図を表している。

#### 【 0 0 5 2 】

図 7 A、図 7 B と、図 1 A、図 1 B と、図 6 A、図 6 B とを比較すれば容易に分かるように、本実施形態に係る半導体装置 100 d は、第 1 の実施形態に係る半導体装置 100 と第 4 の実施形態に係る半導体装置 100 c とを折衷した構造を有している。すなわち、本実施形態では、焼結金属層 2 の中には、壁状の低空孔率領域 3 a が設けられるとともに、柱状の低空孔率領域 3 b が設けられる。

#### 【 0 0 5 3 】

この場合、壁状の低空孔率領域 3 a は、第 1 の実施形態の場合と同様に、接合される半導体素子 1 の外縁部よりも内側に当たる焼結金属層 2 の中に、半導体素子 1 の外縁部に沿って半導体素子 1 の中央部直下の領域を取り囲むように形成される。また、柱状の低空孔率領域 3 b は、焼結金属層 2 において、壁状の低空孔率領域 3 a よりもさらに中央部側に形成される。

10

20

30

40

50

## 【0054】

したがって、本実施形態では、焼結金属層2の端部で生じる亀裂が焼結金属層2の面に沿って、中央部へ進展するのを抑制する効果を期待することができる。さらには、焼結金属層2の放熱性や電気伝導性が向上するという効果も期待することができる。

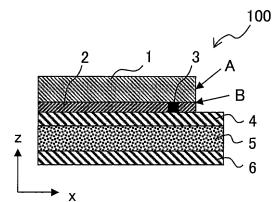

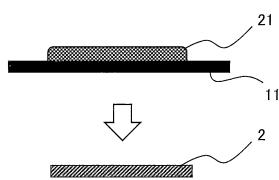

## 【0055】

## 第6の実施形態

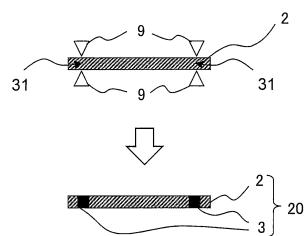

図8Aは、本発明の第1の実施形態に係る半導体装置100の製造工程において、焼結金属層2のシートを作製する工程の例を示した図、図8Bは、焼結金属層2の中に低空孔率領域3を形成し、焼結金属シート20を作製する工程の例を示した図、図8Cは、焼結金属シート20を用いて半導体装置100製造する工程の例を示したである。なお、ここでは説明の便宜上、焼結金属層2の中に低空孔率領域3が形成されたものの焼結金属シート20と呼び、低空孔率領域3が形成される前のものを焼結金属層2のシートと呼んで区別しているが、一般的には、両者ともに焼結金属シートと呼ぶべきものである。

10

## 【0056】

図8Aの工程では、まず、数10nm～数100nmの金属微粒子と有機溶剤とを混合して作製したペースト材21を、スクリーン印刷法やディスペンス法などによりプレート11上にシート状に塗布する。続いて、この塗布されたペースト材21を70～400程度で焼成し、プレート11から取り外すことにより、焼結金属層2のシートを得る。

## 【0057】

次に、図8Bの工程では、この焼結金属層2のシートについて、低空孔率領域3を形成しようとする部分を局所的に加熱する。この場合の加熱は、ヒータによる局所的な加熱、局所的な通電、局所的な加圧などにより実現することができる。また、この工程では、第1～第5の実施形態に示した低空孔率領域3の平面形状に合わせた加熱、通電、加圧用治具を用いることで、焼結金属層2の中に所望の低空孔率領域3を形成することができる。

20

## 【0058】

なお、図8Bの例では、局所的な通電により加熱する方法が示されている。すなわち、焼結金属層2の上面および下面の、低空孔率領域3を形成しようとする平面形状に合わせた位置に電極9を配置し、その上下の電極9間に位置する焼結金属層2内の領域31に通電する。この通電により、上下の電極9で挟まれた焼結金属層2の領域31を焼結金属層2の焼結温度よりも高い温度で加熱する。その結果、上下の電極9で挟まれた焼結金属層2の領域31での焼結が局所的に進行し、低空孔率領域3を備えた焼結金属シート20が作製される。

30

## 【0059】

なお、上下の電極9間の通電は、例えば複数の柱状の低空孔率領域3を形成するような場合には、複数の柱状の低空孔率領域3それぞれについて1つずつ上下に電極9を当てながら通電してもよい。また、複数の柱状の低空孔率領域3の上下に、その複数の低空孔率領域3それぞれに対応する複数の電極9を設け、その複数の上下の電極9間を一挙に通電するようにしてもよい。さらに、壁状の低空孔率領域3を形成するような場合には、上下の電極9の組を所定のスピードで所定のパスに従って連続的に移動させながら、例えば、図1Bのような壁状の低空孔率領域3aを形成するようにしてもよい。

40

## 【0060】

また、焼結金属層2の上下に設けられる電極9の平面方向の位置を少しずらせば、焼結金属層2内において上下方向に傾斜した低空孔率領域3を形成することができる。

## 【0061】

以上、ここでは、上下の電極9を用いた通電により焼結金属層2内の領域31を発熱させ、低空孔率領域3を形成する例を説明したが、その発熱の方法は、通電に限定されず、局所的なヒータによる発熱や局所的な加圧による発熱であってもよい。なお、このとき低空孔率領域3を形成するための温度は、焼結金属層2が焼結銀の場合、200以上、焼結銅の場合、350以上とすることが好ましい。

## 【0062】

50

以上に説明した焼結金属シート 20 を製造する工程の大きな特徴は、低空孔率領域 3 を備えた焼結金属シート 20 全体を同一の材料で形成できることにある。すなわち、低空孔率領域 3 が焼結金属層 2 と全く同一の材料で構成されているため、材料が異なることによる接合不良や剥離などの問題が発生しない。さらには、焼結金属シート 20 を製造する工程が簡単化されるなどのメリットも期待することができる。

#### 【 0 0 6 3 】

次に、図 8 C に示すように、支持基板 10 の導電部材 4 上に焼結金属シート 20 を配置し、さらにその上に半導体素子 1 を配置し、200 ~ 400 程度の高温の雰囲気下で焼結金属シート 20 を半導体素子 1 と支持基板 10 とに焼結接合させる。このとき、良好な焼結接合を得るためにには、加熱と同時に 0.01 MPa 以上の加圧を行うことが好ましい。また、その際に使用する金属微粒子に合わせて、大気中、N<sub>2</sub> 中、H<sub>2</sub> 中など適切な雰囲気を選択するのがよい。

10

#### 【 0 0 6 4 】

以上の工程により半導体装置 100 が製造される。なお、図 8 A ~ 図 8 C は、第 1 実施形態に係る半導体装置 100 の製造工程を説明するものであるが、その説明は、第 2 ~ 第 5 の実施形態に係る半導体装置 100 a ~ 100 d の製造工程にも同様に適用することができる。

20

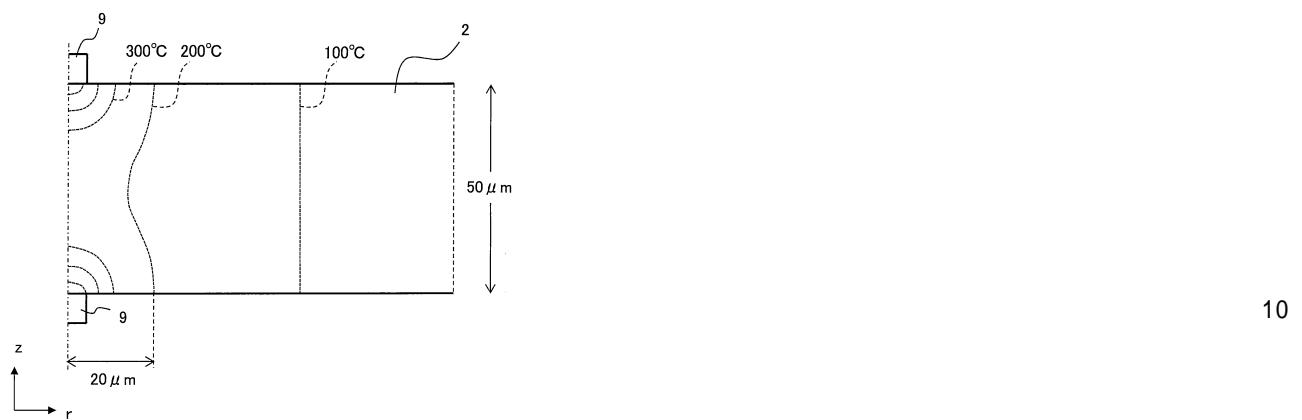

#### 【 0 0 6 5 】

図 9 は、通電による加熱の際の焼結金属層 2 内部の温度分布を熱解析シミュレーションで計算した結果を示した図である。この場合の熱解析シミュレーションは、2 次元軸対称モデルに基づく。したがって、計算結果は、柱状の低空孔率領域 3 が形成される場合の温度分布に相当する。

20

#### 【 0 0 6 6 】

ここでは、焼結金属層 2 のシートの厚さを 50 μm、電極 9 の通電領域の直径を 6 μm として通電時の発熱による焼結金属層 2 内部の温度分布を計算した。図 9 には、計算結果の温度分布が等温線の形で示されている。この場合、横軸は、円形の電極 9 の中心からの距離を表し、縦軸は、焼結金属層 2 の厚さ方向の位置を表す。

#### 【 0 0 6 7 】

図 9 によれば、200 以上の温度となる領域は、直径約 40 μm の柱状領域となること、また、厚さ方向中央部にはくびれが生じていることが分かる。したがって、例えば、焼結が 200 以上で開始する材料の場合、このような柱状領域に低空孔率領域 3 が形成されることとなる。

30

#### 【 0 0 6 8 】

以上、本実施形態によれば、とくに上下の電極 9 を用いた通電による低空孔率領域 3 を形成する方法によれば、低空孔率領域 3 を、従来困難であった微細な構造やパターンとして焼結金属層 2 内に作り込むことが可能となる。したがって、低空孔率領域 3 が形成された焼結金属層 2 (焼結金属シート 20) を用いて製造された半導体装置 100 では、焼結金属層 2 における応力を分散させることが容易になり、亀裂や剥離の発生、進展を防止可能な構造が実現される。

40

#### 【 0 0 6 9 】

なお、本発明は、以上に説明した実施形態および変形例に限定されるものではなく、さらには、様々な変形例が含まれる。例えば、前記した実施形態および変形例は、本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施形態や変形例の構成の一部を、他の実施形態や変形例の構成に置き換えることが可能であり、また、ある実施形態や変形例の構成に他の実施形態や変形例の構成を加えることも可能である。また、各実施形態や変形例の構成の一部について、他の実施形態や変形例に含まれる構成を追加・削除・置換することも可能である。

#### 【 符号の説明 】

#### 【 0 0 7 0 】

50

- 1 半導体素子

2 焼結金属層

3 低空孔率領域

3 a 壁状の低空孔率領域

3 b 柱状の低空孔率領域

4 導電部材

5 絶縁部材

6 冷却部材

8 亀裂

9 電極

10 支持基板

11 プレート

20 焼結金属シート

21 ベースト材

100, 100a, 100b, 100c, 100d 半導体装置

- 10

【図面】

【図 1 A】

【図 1 B】

20

30

40

50

【図 2 A】

【図 2 B】

【図 3】

【図 4 A】

10

20

30

40

50

【図 4 B】

【図 5 A】

10

【図 5 B】

【図 6 A】

20

30

40

50

【図 6 B】

【図 7 A】

10

【図 7 B】

【図 8 A】

20

【図 8 B】

【図 8 C】

30

40

50

【図9】

10

20

30

40

50

---

フロントページの続き

(56)参考文献      特開2015-185559 (JP, A)

国際公開第2014/155619 (WO, A1)

特開2015-216160 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/52

H01L 21/60

B22F 3/105