(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4450737号

(P4450737)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int.Cl.

HO3K 19/173 (2006.01)

F 1

HO3K 19/173 101

請求項の数 9 (全 16 頁)

(21) 出願番号 特願2005-4403 (P2005-4403)

(22) 出願日 平成17年1月11日 (2005.1.11)

(65) 公開番号 特開2006-197023 (P2006-197023A)

(43) 公開日 平成18年7月27日 (2006.7.27)

審査請求日 平成19年7月10日 (2007.7.10)

(出願人による申告) 平成15年度、通信・放送機器、

「第4世代移動体通信システム実現のための研究開発」

委託研究、産業再生法第30条の適用を受ける特許出願

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 依田 勝洋

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 杉山 巍

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 宮島 郁美

最終頁に続く

(54) 【発明の名称】半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

再構成可能に相互結合される複数の演算ユニットを含むリコンフィギュラブル回路と、

所定の処理を実行するよう構成される固定のロジック回路及びパラメータ設定により処理仕様を変更可能に構成されるパラメータ付専用ハードウェアの少なくとも一方である処理回路と、

該リコンフィギュラブル回路と該処理回路とに結合される接続変更可能なネットワークと、

該ネットワークを該ネットワーク以外と結合するために該ネットワークに接続される少なくとも2つのインターフェースを含み、該ネットワークは、

複数の信号線と、

該複数の信号線のうちから所定数の信号線を選択するセレクタ

を含み、該セレクタにより選択された信号線のみを該インターフェースの1つに接続することを特徴とする半導体集積回路。

## 【請求項 2】

該リコンフィギュラブル回路、該処理回路、及び該ネットワークを1つのセットとし、別のリコンフィギュラブル回路、別の処理回路、及び別のネットワークを含むセットを更に少なくとも1セット含み、該複数のセットの複数のネットワークを該インターフェースを介して直列に結合するとともに、両端に位置する該ネットワークについては該インター

フェースを介して該半導体集積回路の外部に結合可能に構成することを特徴とする請求項1記載の半導体集積回路。

【請求項3】

該リコンフィギュラブル回路と該処理回路とに結合されるバスと、

該バスに結合されるプロセッサ

を更に含むことを特徴とする請求項1記載の半導体集積回路。

【請求項4】

該ネットワークの接続を制御する制御回路を更に含み、該制御回路は該プロセッサからの指示に応じて該ネットワークの接続を設定するよう構成されることを特徴とする請求項3記載の半導体集積回路。

10

【請求項5】

該リコンフィギュラブル回路は該プロセッサからの設定データに応じて該複数の演算ユニットの演算内容を設定することを特徴とする請求項3記載の半導体集積回路。

【請求項6】

該プロセッサと外部システムとを結合するためのシステムインターフェースを更に含むことを特徴とする請求項3記載の半導体集積回路。

【請求項7】

該ネットワークは該リコンフィギュラブル回路と該処理回路とを相互結合するクロスバーを含むことを特徴とする請求項1記載の半導体集積回路。

【請求項8】

20

該パラメータ付専用ハードウェアは、

特定の処理を実行する専用ハードウェアと、

該専用ハードウェアの動作及び処理仕様を規定するデータを保持する設定レジスタを含むことを特徴とする請求項1記載の半導体集積回路。

【請求項9】

該処理回路は、該半導体集積回路の外部との信号のやり取りのためのインターフェースを更に含むことを特徴とする請求項1記載の半導体集積回路。

【発明の詳細な説明】

【技術分野】

【0001】

30

本発明は一般に半導体集積回路に関し、詳しくは再構成可能な半導体集積回路に関する。

【背景技術】

【0002】

通信分野において、ソフトウェア無線とは、通信方式に関わる処理の大部分をソフトウェアで実行することにより、変調方式等が異なる様々な無線通信に対して1台の無線機で対応可能とするものである。ソフトウェアを書き換えることにより通信方式を変更することができるので、新しい通信方式が登場したら新しいソフトウェアを書き込むことにより、ハードウェアを交換することなく通信方式の更新ができる。

【0003】

40

通信分野に限られることなく全ての分野で一般に、専用LSIを用いれば、高い性能且つ少ない消費電力で特定の処理を実行するシステムを実現することが出来る。但し、仕様を変更して異なる処理を実行しようとすると、設計及び製造を全てやり直す必要があり、専用LSIは仕様変更可能性が極めて低い構成である。

【0004】

仕様変更可能性が高い構成としては、プロセッサによりソフトウェアを実行し、仕様の変更はソフトウェアを書き換えることで実現する構成が挙げられる。この場合、仕様変更可能性は極めて高いが、プロセッサは汎用処理を実行可能なように構成されているために冗長性が高く、処理性能が低くなってしまう。

【0005】

50

仕様変更可能性を提供しながらもハードウェアによる処理を実現する技術として、FPGA (Field Programmable Gate Array) がある。FPGAは、メモリへのコンフィギュレーションデータの書き込みによって論理素子間の接続を自由に再構成可能とすることにより、ゲート単位での変更を可能な構成とするものである。FPGAはハードウェアの冗長性が高いために、回路規模の面では例えば専用LSIの10倍程度の大きさになってしまい、コストが高く消費電力も大きい。また専用LSIと比較すれば、処理速度は低いものとなる。

【0006】

ダイナミックリコンフィギュラブルLSI（動的再構成可能型半導体集積回路）は、再構成可能な回路を提供しながらも、高い処理性能を提供することができる手段として注目を集めている。ダイナミックリコンフィギュラブルLSIは、複数の演算器をアレイ状に配列し、縦横に配置したバスでこれら演算器を接続する構成となっている。演算器アレイ部の周辺には、演算器アレイ部に関するコンフィギュレーション情報を格納するコンフィギュレーションメモリや、動的再構成の切替えを制御する制御部等が設けられる。

10

【0007】

ダイナミックリコンフィギュラブルLSIでは、再構成可能な構造の基本要素は演算器であり、单一ゲート程度を基本要素とするFPGAと比較すると、格段に大きな粒度（変更可能な単位の大きさ）になっている。また演算器をアレイ上に並べることにより、並列に演算を実行することが可能となり、複素演算や積和演算等の重い演算処理を高速に実行することができる。

20

【発明の開示】

【発明が解決しようとする課題】

【0008】

ソフトウェア無線の分野においても、上記のようなFPGAやダイナミックリコンフィギュラブルLSI等の再構成可能な回路を用いることで、各種通信方式を変更可能な形で実現することができる。しかしダイナミックリコンフィギュラブルLSIは、処理の重い演算に対しては高い性能を発揮するが、粒度が大きいために、例えばデコード結果に基づいて条件分岐する等の細かい制御動作を効率よく実現することが難しいという難点がある。逆にFPGAでは、粒度が小さいので細かい制御を実現することは容易であるが、演算スピードという点において満足のいくものではない。

30

【0009】

以上を鑑みて、本発明は、細かい制御及び重い演算の両方について高い性能を有した再構成可能な半導体集積回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明による半導体集積回路は、再構成可能に相互結合される複数の演算ユニットを含むリコンフィギュラブル回路と、所定の処理を実行するよう構成される固定のロジック回路及びパラメータ設定により処理仕様を変更可能に構成されるパラメータ付専用ハードウェアの少なくとも一方である処理回路と、リコンフィギュラブル回路と処理回路とに結合される接続変更可能なネットワークと、ネットワークを当該ネットワーク以外と結合するために当該ネットワークに接続される少なくとも2つのインターフェースを含み、該ネットワークは、複数の信号線と、該複数の信号線のうちから所定数の信号線を選択するセレクタを含み、該セレクタにより選択された信号線のみを該インターフェースの1つに接続することを特徴とする。

40

【0011】

更に、本発明の別の構成によれば、該リコンフィギュラブル回路、該処理回路、及び該ネットワークを1つのセットとし、それらセットを少なくとも2セット含み、該複数のセットの複数のネットワークを該インターフェースを介して直列に結合するとともに、両端に位置するインターフェースに関しては外部に結合可能な構成とすることを特徴とする。

【発明の効果】

50

## 【0012】

本発明の少なくとも1つの実施例によれば、半導体集積回路は、細かい制御が必要な処理についてはロジック回路により容易に制御を実現することが可能であるとともに、複素演算や積和演算等の重い演算処理についてはリコンフィギュラブル回路及びパラメータ付専用ハードウェアにより高速な演算を実行することが可能である。また特に設計変更することなく半導体集積回路内部に設ける処理セットの数を増やすことが可能であるとともに、半導体集積回路のチップ同士を接続することで全体の処理セットの数を増やすことも可能である。このようにして処理セットの数を増やすことにより、全体の処理性能を必要に応じて高めることができる。

## 【発明を実施するための最良の形態】

10

## 【0013】

以下に本発明の実施例を添付の図面を用いて詳細に説明する。

## 【0014】

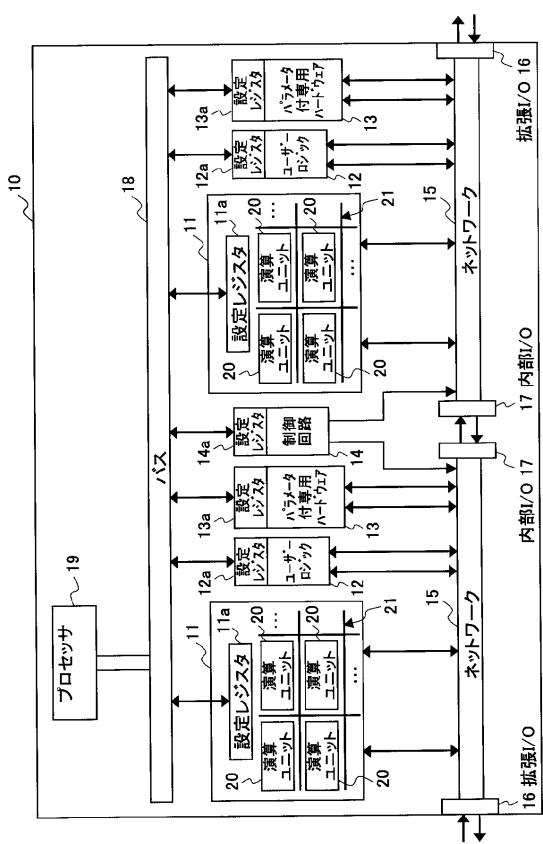

図1は、本発明による半導体集積回路の構成の一例を示すブロック図である。図1の半導体集積回路10は、ダイナミックリコンフィギュラブル回路11、ユーザロジック12、パラメータ付専用ハードウェア13、制御回路14、ネットワーク15、拡張I/O16、内部I/O17、バス18、及びプロセッサ19を含む。

## 【0015】

図1の構成では、ダイナミックリコンフィギュラブル回路11、ユーザロジック12、パラメータ付専用ハードウェア13、及びネットワーク15からなる処理セットが、半導体集積回路10のチップ内部に2セット設けられている。この処理セットの数は2に限定されるものではなく、1つ又は3つ以上の処理セットが1つのチップ内部に設けられていてよい。1つのチップ内に複数の処理セットが設けられる場合、隣接する処理セット間は、図1に示されるように内部I/O17により接続される。

20

## 【0016】

ダイナミックリコンフィギュラブル回路11は、縦横にアレイ状に配置された複数の演算ユニット20、各演算ユニット20を接続する縦横に配置されたバス21、及び複数の演算ユニット20からなるアレイ部分のコンフィギュレーション情報を格納する設定レジスタ11aを含む。プロセッサ19からバス18を介してコンフィギュレーション情報を設定レジスタ11aに書き込むことで、複数の演算ユニット20からなるアレイ部分に所望のデータ処理を実行させることができる。

30

## 【0017】

ユーザロジック12は、特定の処理を実行するための専用ハードウェアであり、設定レジスタ12aを含む。ユーザロジック12には、複数の処理内容に対応した複数のハードウェア機能が設けられてよい。プロセッサ19からバス18を介して設定レジスタ12aにデータ設定することによって、ユーザロジック12の動作条件等を制御することができる。

## 【0018】

パラメータ付専用ハードウェア13は、所定の処理を実行するために専用に設計・製造されたハードウェアであり、処理内容そのものを変更することはできないが、例えば処理のデータ数や精度等のパラメータを変更可能のように構成されている。このパラメータの情報は、設定レジスタ13aに格納される。プロセッサ19がバス18を介してこれらのパラメータを設定レジスタ13aに格納することにより、パラメータ付専用ハードウェア13に所定の動作を所望の仕様に従い実行させることができる。

40

## 【0019】

パラメータ付専用ハードウェア13は、例えば帯域制限フィルタであり、変更可能なパラメータはフィルタの係数及びタップ数である。或いはパラメータ付専用ハードウェア13は、例えばFFT演算器であり、変更可能なパラメータはFFT演算のポイント数である。また或いはパラメータ付専用ハードウェア13は、例えばビタビ復号器であり、変更可能なパラメータは拘束長、符号化率、及び生成多項式である。

50

## 【0020】

制御回路14は、ネットワーク15の信号線の接続を制御することにより、ダイナミックリコンフィギュラブル回路11、ユーザロジック12、及びパラメータ付専用ハードウェア13間（処理マクロ間）の相互結合関係を所望の状態に設定する。また制御回路14は更に、ネットワーク15の信号線の接続を制御することにより、隣接する処理セットの間の相互結合関係を所望の状態に設定する。ネットワーク15の信号線の接続に関する情報は、設定レジスタ14aに格納される。プロセッサ19がバス18を介して信号接続に関する情報を設定レジスタ13aに格納することにより、半導体集積回路10内での各処理マクロ間の相互結合関係を接続変更可能に設定することができる。

## 【0021】

10

ネットワーク15は、例えば入力側の任意の一点を出力側の任意の一点に接続することができるクロスバー構成でよい。これにより、ネットワーク15に結合される複数の処理マクロのうちで、任意の1つの出力を任意の1つの入力に供給することができる。2つの隣接するネットワーク15間は内部I/O17で互いに接続され、一方のネットワーク15に接続される処理マクロと他方のネットワーク15に接続される処理マクロとの間での信号のやり取りが可能とされる。

## 【0022】

この際、あるネットワーク15の信号線の全てを隣接するネットワーク15に繋げたのでは、n個の処理セットを設けた場合、単一の処理セットを設けた場合と比較して、ネットワーク15の信号線の数がn倍となってしまう。即ち、nセット分の処理マクロを1つのネットワーク15で相互結合するのと何ら違いが無いことになる。

20

## 【0023】

そこで本願発明では、あるネットワーク15の信号線のうちで選択したもののみを隣接するネットワーク15に繋げる構成とする。この構成により、n個の処理セットを設けた場合であっても、単一の処理セットを設けた場合とそれ程変わらない数に信号線の数を抑制することができる。従って、ネットワークの信号線数の増大を抑えながらも、半導体集積回路10内に所望の数の処理セットを設けることができる。

## 【0024】

また2つの拡張I/O16により、ネットワーク15は半導体集積回路10の外部と通信が可能な構成となっている。これにより、図1に示される半導体集積回路10を任意の個数連結することが可能となり、必要に応じた処理性能を容易に提供することができる。この際の拡張I/O16によるチップ間の相互接続についても、上記の内部I/O17によるチップ内の相互接続と同様に、ネットワーク15の信号線のうちで選択したもののみを外部に接続する構成とすればよい。

30

## 【0025】

上記のような構成の半導体集積回路10は、細かい制御が必要な処理についてはユーザロジック12により容易に実現することが可能であるとともに、ダイナミックリコンフィギュラブル回路11及びパラメータ付専用ハードウェア13により高速な演算を実行することが可能である。また特に設計変更することなく半導体集積回路10内部に設ける処理セットの数を増やすことが可能であるとともに、半導体集積回路10のチップ同士を接続することで全体の処理セットの数を増やすことも可能である。このようにして処理セットの数を増やすことにより、全体の処理性能を必要に応じて高めることができる。なおこのように処理セットの数に関して拡張性があるので、細かい制御が必要な処理については、リソースとして余裕のあるダイナミックリコンフィギュラブル回路11部分において実現してもよい。

40

## 【0026】

なお上記説明では、複数の演算ユニットで構成されたダイナミックリコンフィギュラブル回路11のみが再構成可能な部分として設けられる構成を示したが、ダイナミックリコンフィギュラブル回路11に加える、もしくは代えて、FPGA等の任意の再構成可能な回路を設けてもよい。

50

## 【0027】

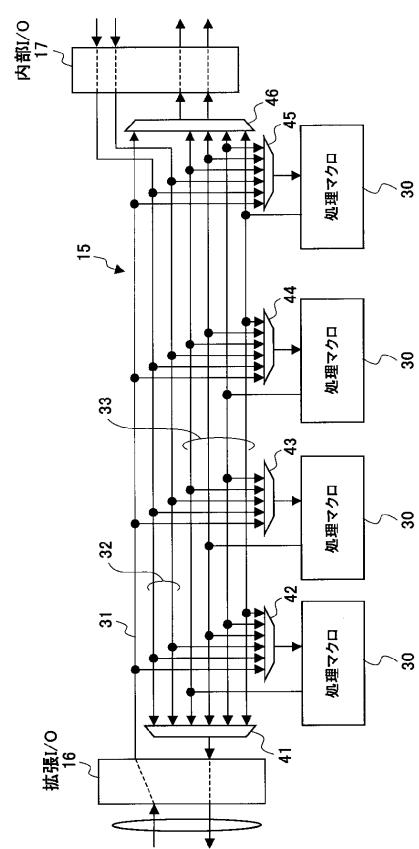

図2は、ネットワーク15の構成の一例を示す図である。図2のネットワーク15は、外部拡張用の信号線31、セット間接続用の信号線32、セット内接続用の信号線33、及びセレクタ41乃至46を含む。セレクタ41乃至46は、制御回路14により制御されてよい。図2の例では、外部拡張用の信号線31は1本、セット間接続用の信号線32は2本、セット内接続用の信号線33は4本であるが、これらの数に限定されるものではない。

## 【0028】

外部拡張用の信号線31は、拡張I/O16を介して半導体集積回路10の外部に接続され、外部から供給される信号を受け取る。セレクタ41は、セット間接続用の信号線32及びセット内接続用の信号線33のうちの1本を選択して半導体集積回路10外部に接続し、信号を外部に出力する。拡張I/O16は、インターフェース用の信号駆動バッファ等を含むものであり、論理的には図に点線で示されるように単に信号を素通りさせる機能しかない。

10

## 【0029】

セット間接続用の信号線32は、内部I/O17を介して半導体集積回路10内部の隣接するネットワーク15に接続され、このネットワーク15から供給される信号を受け取る。セレクタ46は、外部拡張用の信号線31及びセット内接続用の信号線33のうちの2本を選択して隣接するネットワーク15に接続し、信号を隣接するネットワーク15に供給する。内部I/O17は、インターフェース用の信号駆動バッファ等を含むものであり、論理的には図に点線で示されるように単に信号を素通りさせる機能しかない。

20

## 【0030】

セレクタ42乃至45は、各処理マクロ30に対して1つずつ設けられる。セレクタ42乃至45は、外部拡張用の信号線31、セット間接続用の信号線32、及びセット内接続用の信号線33のうちの1本を選択して、選択した信号線の信号を対応する処理マクロ30に供給する。各処理マクロ30の出力は、セット内接続用の信号線33のうちの対応する1本に接続されており、この1本はセレクタ42乃至45のうちの対応するセレクタには入力されていない。これは、自らの出力を自らの入力として供給する必要が無いからである。

## 【0031】

30

図2に示すように、セレクタ46により、ネットワーク15の信号線のうちで選択したもののみを隣接するネットワーク15に繋げる構成とする。この構成により、処理セットの数が変化した場合であっても、ネットワーク15の信号線の数は所定の数に固定することができる（図2の例では7本）。従って、ネットワークの信号線数の増大を抑えながらも、半導体集積回路10内に所望の数の処理セットを設けることができる。

## 【0032】

また同様に、セレクタ41により、ネットワーク15の信号線のうちで選択したもののみを拡張用として外部に繋げる構成とする。この構成により、ネットワークの信号線数の増大を抑えながらも、任意の数の半導体集積回路10を連結して、所望の数の処理セットを含むように拡張することができる。

40

## 【0033】

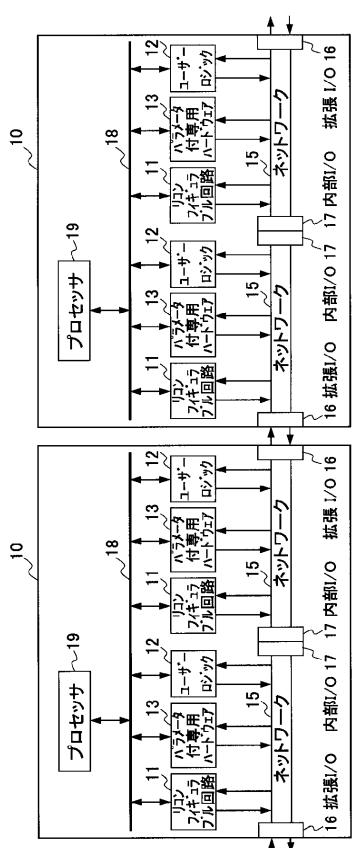

図3は、複数の半導体集積回路10を連結して拡張した構成の一例を示す図である。図3において、図1と同一の要素は同一の番号で参照し、その説明は省略する。

## 【0034】

図3では、2つの半導体集積回路10が互いに接続され、合計で4つの処理セットが連結されている。これら4つの処理セットは全体で1つの回路として動作することが可能であり、処理セットの数に応じた処理性能を提供することができる。図3に示される2つの半導体集積回路10に更に半導体集積回路10を接続していくことが可能であり、原理的には無制限に半導体集積回路10の数を増やして処理性能を高めていくことができる。

## 【0035】

50

以下に半導体集積回路10の応用例として、IEEE802.11a及びIEEE802.11bの両方に対応した端末装置を本発明の半導体集積回路10により構成する例について説明する。

【0036】

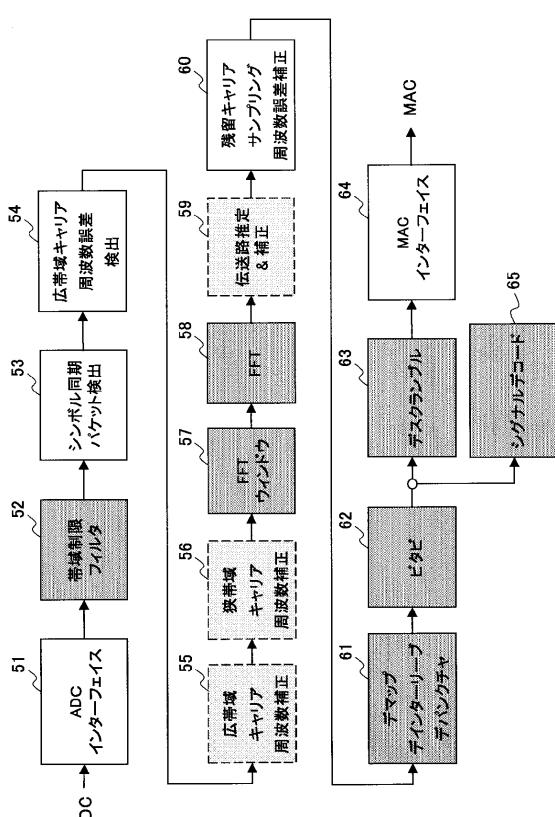

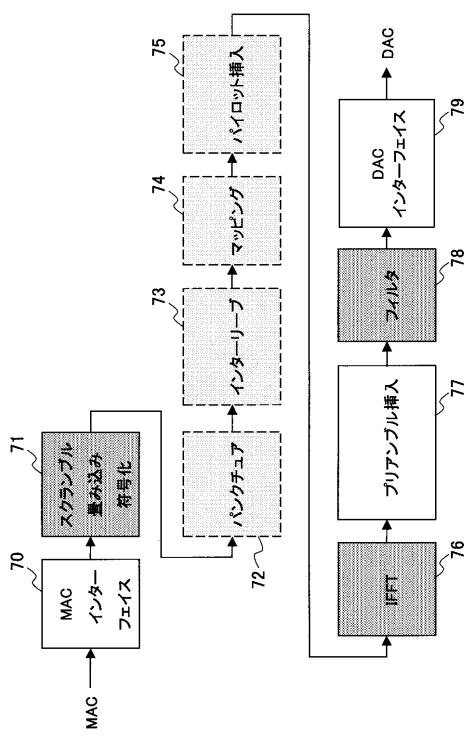

図4は、IEEE802.11aの受信機能構成を示すブロック図である。また図5は、IEEE802.11aの送信機能構成を示すブロック図である。

【0037】

図4に示されるように、IEEE802.11aの受信機能は、ADCインターフェース51、帯域制限フィルタ52、シンボル同期パケット検出53、広帯域キャリア周波数誤差検出54、広帯域キャリア周波数補正55、狭帯域キャリア周波数補正56、FFT10ウィンドウ57、FFT58、伝送路推定&補正59、残留キャリアサンプリング周波数誤差補正60、デマップ・デインターリーブ・デパンクチャ61、ビタビ62、デスクランブル63、MACインターフェース64、及びシグナルデコード65を含む。また図5に示されるように、IEEE802.11aの送信機能は、MACインターフェース70、スクランブル畳み込み符号化71、パンクチュア72、インターリーブ73、マッピング74、パイロット挿入75、IFFT76、ブリアンブル挿入77、フィルタ78、及びDACインターフェース79を含む。

【0038】

IEEE802.11aは5GHz帯の周波数帯域を使用し、OFDM(Orthogonal Frequency Division Multiplexing:直交周波数分割多重)を変調方式として、最大54Mbpsという高速な通信を行なうことができる。図4及び図5に示されるIFFT部分及びFFT部分は、OFDM変調処理及びOFDM復調処理を行う部分である。またMACインターフェース部64及び70は、MAC(Media Access Control)制御部を介してホスト装置との信号のやり取りを行う部分である。またADCインターフェース51はADC(Analog-to-Digital Converter)から信号を受けるインターフェースであり、DACインターフェース79はDAC(Digital-to-Analog Converter)へ信号を供給するインターフェースである。

【0039】

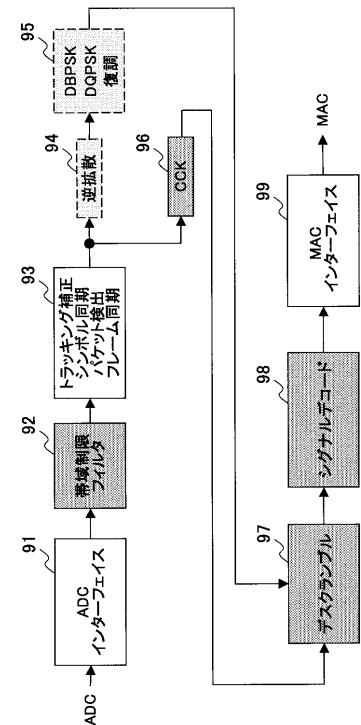

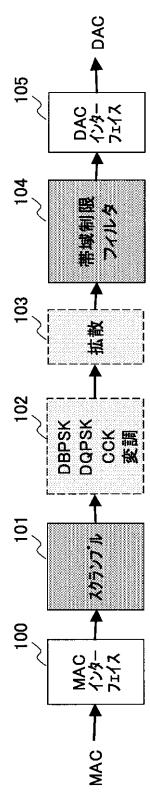

図6は、IEEE802.11bの受信機能構成を示すブロック図である。また図7は、IEEE802.11bの送信機能構成を示すブロック図である。

【0040】

図6に示されるように、IEEE802.11bの受信機能は、ADCインターフェース91、帯域制限フィルタ92、トラッキング補正・シンボル同期・パケット検出・フレーム同期93、逆拡散94、DBPSK・DQPSK復調95、CCK96、デスクランブル97、シグナルデコード98、及びMACインターフェース99を含む。また図6に示されるように、IEEE802.11bの送信機能は、MACインターフェース100、スクランブル101、DBPSK・DQPSK・CCK変調102、拡散103、帯域制限フィルタ104、及びDACインターフェース105を含む。

【0041】

IEEE802.11bは2.4GHz帯の周波数帯域を使用し、直接系列スペクトル拡散(DSSS)を伝送方式とし、CCK(Complementary Code Keying)等を変調方式として、11Mbpsの速度で通信を行なうことができる。図6及び図7に示される拡散103及び逆拡散94は、直接系列スペクトル拡散及び逆拡散を行う部分であり、DBPSK・DQPSK・CCK変調102及びDBPSK・DQPSK復調95が変調及び復調を行う部分である。またMACインターフェース部99及び100は、MAC(Media Access Control)制御部を介してホスト装置との信号のやり取りを行う部分である。またADCインターフェース91はADC(Analog-to-Digital Converter)から信号を受けるインターフェースであり、DACインターフェース105はDAC(Digital-to-Analog Converter)へ信号を供給するインターフェースである。

【0042】

10

20

30

40

50

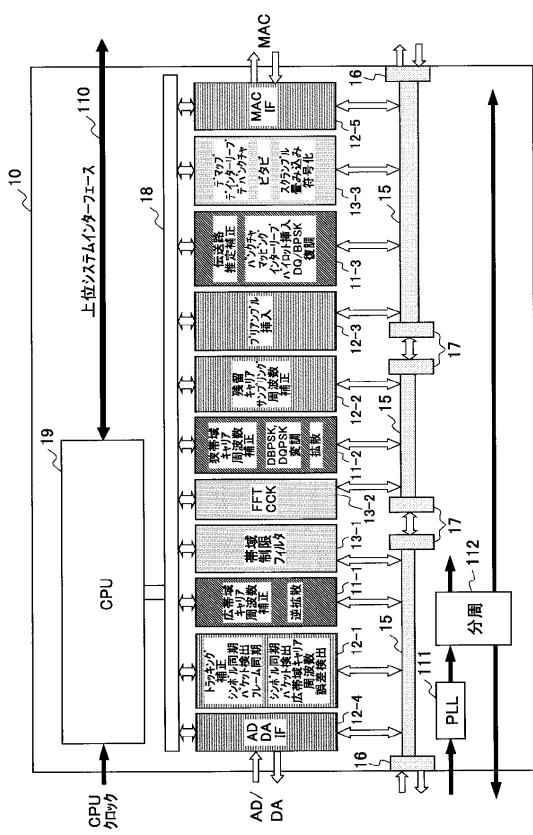

図8は、図4及び図5に示すI E E E 8 0 2 . 1 1 aの機能と図6及び図7に示すI E E 8 0 2 . 1 1 bの機能とを、本発明の半導体集積回路10により実現した構成を示す図である。図8において、図1と同一の要素は同一の番号で参照し、その説明は省略する。

#### 【0043】

図8に示す半導体集積回路10は、上位システムインターフェース110を含む。上位システムインターフェース110は、プロセッサ19と上位システムとのインターフェースを提供するものである。また半導体集積回路10は、PLL(Phase-Locked Loop)111及び分周器112を含む。これらは半導体集積回路10で使用する内部クロック信号を発生するために設けられている。

10

#### 【0044】

図8に示す半導体集積回路10には、3つの処理セット(即ち3つのネットワーク15)が設けられている。処理マクロ11-1乃至11-3はダイナミックリコンフィギュラブル回路であり、処理マクロ12-1乃至12-5はユーザロジックであり、処理マクロ13-1乃至13-3はパラメータ付専用ハードウェアである。

#### 【0045】

図8に示す例では、ダイナミックリコンフィギュラブル回路11-1は、図4の広帯域キャリア周波数補正55の機能又は図6の逆拡散94の機能の何れかを、I E E E 8 0 2 . 1 1 a及びI E E E 8 0 2 . 1 1 bの切換えに応じて、再構成可能な形で実現する。ダイナミックリコンフィギュラブル回路11-2は、図4の狭帯域キャリア周波数補正56の機能又は図7のDBPSK・DQPSK・CCK変調102及び拡散103の機能の何れかを、I E E E 8 0 2 . 1 1 a及びI E E E 8 0 2 . 1 1 bの切換えに応じて、再構成可能な形で実現する。ダイナミックリコンフィギュラブル回路11-3は、図4の伝送路推定補正59及び図5のパンクチュア72、インターリーブ73、マッピング74、バイロット挿入75の機能又は図6のDBPSK・DQPSK復調95の機能の何れかを、I E E E 8 0 2 . 1 1 a及びI E E E 8 0 2 . 1 1 bの切換えに応じて、再構成可能な形で実現する。

20

#### 【0046】

またユーザロジック12-1乃至12-5として、トラッキング補正・シンボル同期・パケット検出・フレーム同期93、シンボル同期パケット検出53、広帯域キャリア周波数誤差検出54、残留キャリアサンプリング周波数誤差補正60、ブリアンブル挿入77、ADCインターフェース51及び91、DACインターフェース79及び105等が実現される。更にパラメータ付専用ハードウェア13-1乃至13-3としては、帯域制限フィルタ52及び92、FFT58、IFFT76、CCK96、デマップ・デインターリーブ・デパンクチャ61、ビタビ62、スクランブル畳み込み符号化71等が実現される。

30

#### 【0047】

図8に示すような機能割り当てにおいては、まず基本的にパラメータ付専用ハードウェア13で処理可能な機能はパラメータ付専用ハードウェア13に割り当てる。次に、それ以外の処理で積和演算等の重い演算を多く含む処理はダイナミックリコンフィギュラブル回路11に割り当てる。その他の残りの処理については、ユーザロジック12に割り当てる。基本的には、固定的で変更のできないユーザロジック12の規模はなるべく小さくして、ダイナミックリコンフィギュラブル回路11やFPGA等の再構成可能な回路部分を優先的に利用することが望ましい。

40

#### 【0048】

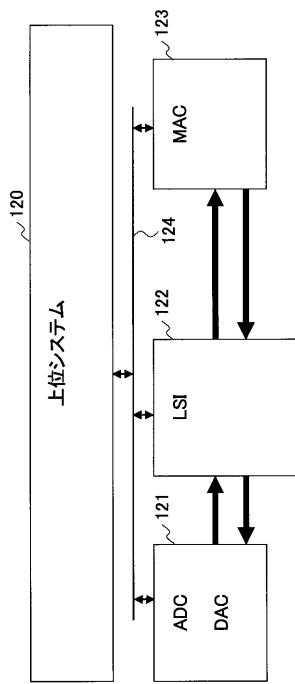

図9は、図8に示す半導体集積回路10を使用するシステム構成を示す図である。図9のシステムは、上位システム120、ADC/DAC121、図8の半導体集積回路10であるLSI122、MAC123、及びバス124を含む。上位システム120が、ADC/DAC121、LSI122、及びMAC123とバス124を介して制御信号をやり取りすることで、これらの装置を制御する。図8に示すAD/DAインターフェース

50

12-4 が ADC / DAC 121 と接続され、LSI 122 と ADC / DAC 121 とのデータ信号のやり取りを実現する。また図 8 に示す MAC インターフェース 12-5 が MAC 123 と接続され、LSI 122 と MAC 123 とのデータ信号のやり取りを実現する。

【0049】

上位システム 120 が、バス 124 を介して LSI 122 を制御することにより、LSI 122 を IEEE 802.11a 及び IEEE 802.11b の何れかの通信機能に設定することができる。また上位システム 120 が、バス 124 を介して ADC / DAC 121、LSI 122、及び MAC 123 を制御することで、所定の送受信動作を実行することができる。

10

【0050】

図 10 は、本発明の半導体集積回路 10 の別の応用例として、IEEE 802.11g に対応した端末装置を半導体集積回路 10 により構成した例を示す図である。

【0051】

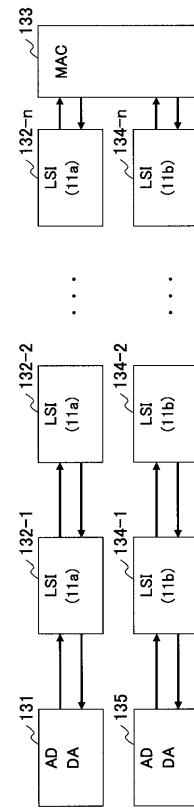

図 10 の構成は、AD / DA 変換器 131、本発明の半導体集積回路 10 である LSI 132-1 乃至 132-n、MAC 133、本発明の半導体集積回路 10 である LSI 134-1 乃至 134-n、及び AD / DA 変換器 135 を含む。半導体集積回路 10 である LSI 132-1 乃至 132-n は IEEE 802.11a の機能を実現するように設定され、LSI 134-1 乃至 134-n は IEEE 802.11b の機能を実現するように設定される。AD / DA 変換器 131 及び 135 から MAC 133 に向かう矢印の経路が受信信号の経路であり、MAC 133 から AD / DA 変換器 131 及び 135 に向かう矢印の経路が送信信号の経路である。

20

【0052】

これにより IEEE 802.11g に対応した端末装置を本発明の半導体集積回路 10 により構成することができる。なお図 10 の構成では、LSI 132-1 乃至 132-n 及び LSI 134-1 乃至 134-n はそれぞれ n 個示されているが、この数は任意でよい（図 8 の構成では 1 つの半導体集積回路 10 で IEEE 802.11a, b の機能を実現している）。

【0053】

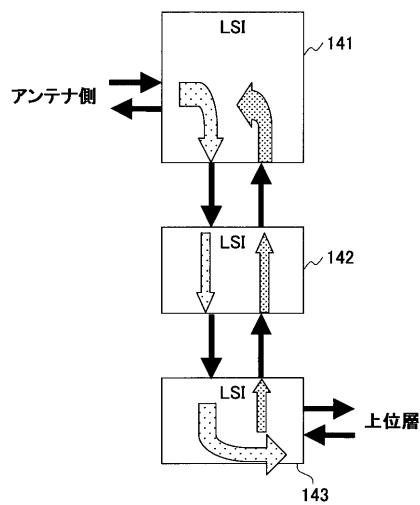

図 11 は、本発明の半導体集積回路 10 の別の応用例として、送受信が同時に行われない無線方式を半導体集積回路 10 により構成した例を示す図である。

30

【0054】

図 11 の構成は、本発明の半導体集積回路 10 である LSI 141 乃至 143 を直列に連結したものとなっている。受信時には、アンテナ側から供給された受信信号が、マスター装置である LSI 141 及び拡張用のスレーブ装置である LSI 142 及び 143 により順に処理されて、所定の信号処理で得られた受信データが上位層に供給される。送信時には、上位層から供給された送信データが、LSI 143、142、及び 141 により順に処理されて、送信信号としてアンテナ側に供給される。

【0055】

このように複数の半導体集積回路 10 を拡張 I / O 16 を介して直列に接続させることで、全体の信号処理性能を向上させることができる。また無線 LAN のように送受信が同時に実行されない無線方式の場合、図 11 のように一列の半導体集積回路 10 を受信用と送信用とに交互に使い分けることができる。

40

【0056】

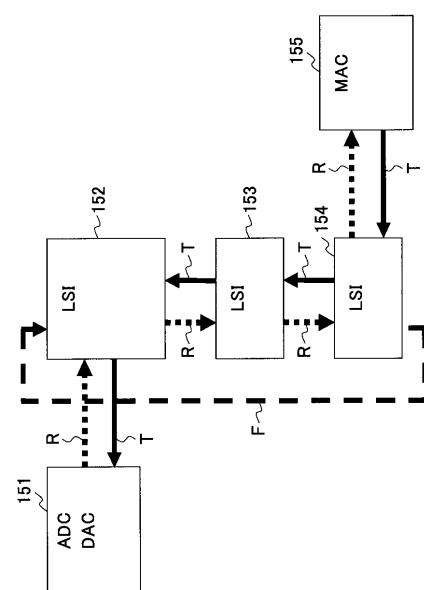

図 12 は、本発明の半導体集積回路 10 の別の応用例として、送受信が同時に行われる無線方式を半導体集積回路 10 により構成した例を示す図である。

【0057】

図 12 の構成は、ADC / DAC 151、本発明の半導体集積回路 10 である LSI 152 乃至 154、及び MAC 155 を含む。LSI 152 乃至 154 は、拡張 I / O 16 を介して直列に連結したものとなっている。図 12 において、T は送信データの流れ、R

50

は受信データの流れ、Fはフィードバックの制御情報の流れである。

【0058】

携帯電話のように常に受信を行いつつ送信を行うような通信方式の場合、上位層側からアンテナ側への制御情報（フィードバック）が多く存在する。図12の構成では、内部I/O17を利用して半導体集積回路10（LSI152乃至154）を直列に接続させることで、フィードバック及び送受信同時処理に対応するとともに、信号処理性能を拡張することが可能である。

【0059】

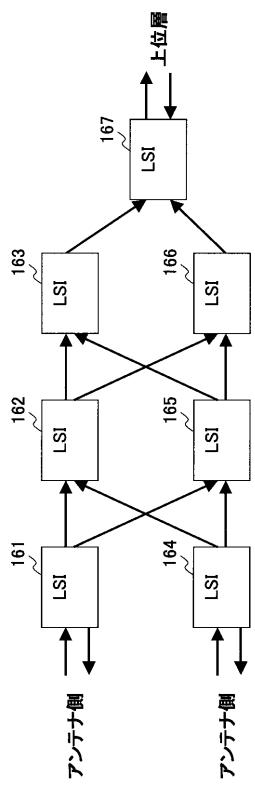

図13は、本発明の半導体集積回路10の別の応用例として、マルチアンテナ構成の端末を半導体集積回路10により構成した例を示す図である。図13の構成は、本発明の半導体集積回路10であるLSI161乃至167を含む。

10

【0060】

この例では、マルチアンテナ構成を実現するために、半導体集積回路10の複数の拡張I/O16を利用してMIMO（Multi Input Multi Output）を構成している。MIMOは、マトリクス演算（図13のように信号の流れを示す矢印がクロスするような演算）を実行するものである。本発明の半導体集積回路10には2つの拡張I/O16が設けられており、図1や図2に示すように、各拡張I/O16は入力部と出力部とを有している。従って各半導体集積回路10は、2つの入力と2つの出力とを有していることになる。これらの入出力を図13のように接続することにより、本発明の半導体集積回路10を用いてMIMOを構成することが可能となる。

20

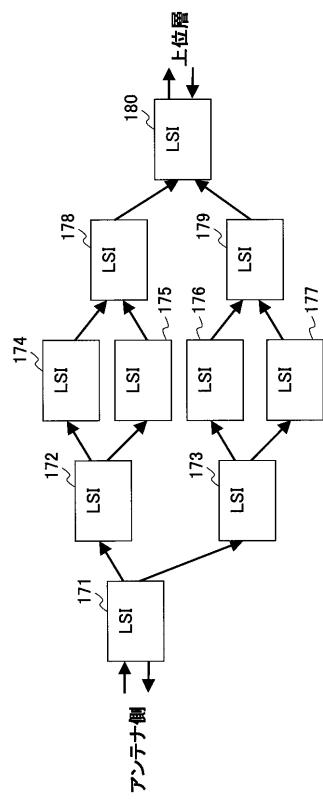

【0061】

図14は、本発明の半導体集積回路10の別の応用例として、並列処理を半導体集積回路10により実現する例を示す図である。図13の構成は、本発明の半導体集積回路10であるLSI171乃至180を含む。

【0062】

アンテナ側から見た1段目から2段目において、LSI171の2つの出力がLSI172及びLSI173に供給される。2段目から3段目において、LSI172の2つの出力がLSI174及びLSI175に供給され、LSI173の2つの出力がLSI176及びLSI177に供給される。従って3段目において、LSI174乃至177の4つの半導体集積回路10が並列に処理を実行する構成となっている。

30

【0063】

HARQ（Hybrid Automatic Repeat Request）は、例えば3GPP（3rd Generation Partnership Project）の拡張版であるHSDPA（High Speed Down Link Packet Access）方式で使用されている。この方式は、一旦受信したデータが誤っていた場合にはそれを保持し、符号化方式を変えて再送を行い、再送データを前回データと合わせて復号することにより性能を向上させる方法である。この場合、アンテナと上位層との中間地点において大きな処理性能が必要となる。図14に示す構成では、中間地点（3段目）において半導体集積回路10を並列に配置することで、このような処理要求に対応することができる。

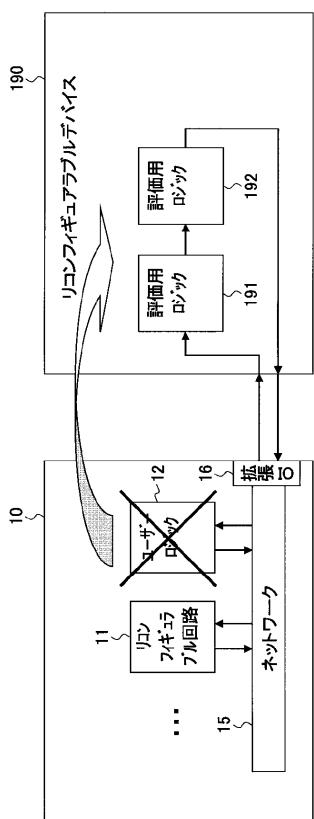

【0064】

図15は、本発明の半導体集積回路10において拡張I/O16を他のデバイスとの通信に使用する例である。図15の構成は、半導体集積回路10及びFPGA等のリコンフィギュラブルデバイス190を含む。リコンフィギュラブルデバイス190は半導体集積回路10の内部I/O17に接続されている。またリコンフィギュラブルデバイス190の内部には、ユーザロジック12の論理を実現する評価用ロジック191及び評価用ロジック192が構成されている。

40

【0065】

このような構成において、半導体集積回路10のユーザロジック12の動作を停止させ、評価用ロジック191及び評価用ロジック192をユーザロジック12の代わりに動作させる。これにより、ユーザロジック12の動作チェック、評価、設計の見直しなどを効

50

率的に行うことが可能となる。このように拡張 I / O 16 は、半導体集積回路 10 同士を繋げる以外にも、他の様々な用途に使用することが可能である。

#### 【0066】

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

#### 【図面の簡単な説明】

#### 【0067】

【図 1】本発明による半導体集積回路の構成の一例を示すブロック図である。

【図 2】ネットワークの構成の一例を示す図である。

【図 3】複数の半導体集積回路を連結して拡張した構成の一例を示す図である。 10

【図 4】IEEE 802.11a の受信機能構成を示すブロック図である。

【図 5】IEEE 802.11a の送信機能構成を示すブロック図である。

【図 6】IEEE 802.11b の受信機能構成を示すブロック図である。

【図 7】IEEE 802.11b の送信機能構成を示すブロック図である。

【図 8】図 4 及び図 5 に示す IEEE 802.11a の機能と図 6 及び図 7 に示す IEEE 802.11b の機能とを、本発明の半導体集積回路により実現した構成を示す図である。

【図 9】図 8 に示す半導体集積回路を使用するシステム構成を示す図である。

【図 10】本発明の半導体集積回路の別の応用例として、IEEE 802.11g に対応した端末装置を半導体集積回路により構成した例を示す図である。 20

【図 11】本発明の半導体集積回路の別の応用例として、送受信が同時に行われない無線方式を半導体集積回路により構成した例を示す図である。

【図 12】本発明の半導体集積回路の別の応用例として、送受信が同時に行われる無線方式を半導体集積回路により構成した例を示す図である。

【図 13】本発明の半導体集積回路の別の応用例として、マルチアンテナ構成の端末を半導体集積回路により構成した例を示す図である。

【図 14】本発明の半導体集積回路の別の応用例として、並列処理を半導体集積回路により実現する例を示す図である。

【図 15】本発明の半導体集積回路において拡張 I / O を他のデバイスとの通信に使用する例を示す図である。 30

#### 【符号の説明】

#### 【0068】

10 半導体集積回路

11 ダイナミックリコンフィギュラブル回路

12 ユーザロジック

13 パラメータ付専用ハードウェア

14 制御回路

15 ネットワーク

16 拡張 I / O

17 内部 I / O

18 バス

19 プロセッサ

40

【図1】

【図2】

【図3】

【図4】

【 义 5 】

【 図 6 】

【 四 7 】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特表2000-509948(JP,A)

特開2003-218212(JP,A)

特開平11-015866(JP,A)

特開平10-056376(JP,A)

特開2000-049287(JP,A)

特開2002-208638(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K19/098-19/23

G06F15/16-15/177, 15/78