(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5611224号

(P5611224)

(45) 発行日 平成26年10月22日(2014.10.22)

(24) 登録日 平成26年9月12日(2014.9.12)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO4L 25/02  | (2006.01) | HO4L 25/02 | 303B |

| HO4L 25/03  | (2006.01) | HO4L 25/03 | Z    |

| HO1L 21/822 | (2006.01) | HO1L 27/04 | F    |

| HO1L 27/04  | (2006.01) | HO1L 27/04 | L    |

| HO1L 21/66  | (2006.01) | HO1L 27/04 | T    |

請求項の数 26 (全 77 頁) 最終頁に続く

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2011-539323 (P2011-539323) |

| (86) (22) 出願日 | 平成22年10月13日(2010.10.13)      |

| (86) 国際出願番号   | PCT/JP2010/067903            |

| (87) 国際公開番号   | W02011/055611                |

| (87) 国際公開日    | 平成23年5月12日(2011.5.12)        |

| 審査請求日         | 平成25年10月11日(2013.10.11)      |

| (31) 優先権主張番号  | 特願2009-253900 (P2009-253900) |

| (32) 優先日      | 平成21年11月5日(2009.11.5)        |

| (33) 優先権主張国   | 日本国 (JP)                     |

| (31) 優先権主張番号  | 特願2009-273598 (P2009-273598) |

| (32) 優先日      | 平成21年12月1日(2009.12.1)        |

| (33) 優先権主張国   | 日本国 (JP)                     |

| (31) 優先権主張番号  | 特願2010-104192 (P2010-104192) |

| (32) 優先日      | 平成22年4月28日(2010.4.28)        |

| (33) 優先権主張国   | 日本国 (JP)                     |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000116024<br>ローム株式会社<br>京都府京都市右京区西院溝崎町21番地 |

| (74) 代理人  | 110001933<br>特許業務法人 佐野特許事務所                |

| (74) 代理人  | 100085501<br>弁理士 佐野 静夫                     |

| (74) 代理人  | 100134555<br>弁理士 林田 英樹                     |

| (72) 発明者  | 柳島 大輝<br>京都府京都市右京区西院溝崎町21 ローム株式会社内         |

| (72) 発明者  | 石川 俊行<br>京都府京都市右京区西院溝崎町21 ローム株式会社内         |

最終頁に続く

(54) 【発明の名称】信号伝達回路装置、半導体装置とその検査方法及び検査装置、並びに、信号伝達装置及びこれを用いたモータ駆動装置

## (57) 【特許請求の範囲】

## 【請求項1】

入力側回路と出力側回路との間で信号の伝達が行われる信号伝達回路装置であって、前記信号伝達回路装置は、

前記入力側回路に入力された制御入力信号を受信し、第1補正信号を出力する第1パルス生成回路と、

前記制御入力信号を受信し、第2補正信号を出力する第2パルス生成回路と、

前記第1補正信号および前記第2補正信号を受信し、前記入力側回路から前記出力側回路へ信号の伝達を行う入力信号伝達部と、

前記入力信号伝達部の出力を受信し、前記制御入力信号と等価な制御出力信号を出力する入力信号復元回路と、

前記制御出力信号を受信し、前記出力側回路から前記入力側回路へ信号の伝達を行い、帰還信号を出力する帰還信号伝達部と、

前記制御入力信号および前記帰還信号を受信し、前記制御入力信号と前記帰還信号の論理比較を行い、論理比較信号を出力する論理比較回路を備え、

前記第1パルス生成回路は、前記制御入力信号とともに前記論理比較信号を受信し、前記制御入力信号と前記論理比較信号が第1の組み合わせとなつた場合に前記第1補正信号を出力し、

前記第2パルス生成回路は、前記制御入力信号とともに前記論理比較信号を受信し、前記制御入力信号と前記論理比較信号が前記第1の組み合わせとは異なる第2の組み合わせ

10

20

となった場合に前記第2補正信号を出力することを特徴とする信号伝達回路装置。

**【請求項2】**

請求項1記載の信号伝達回路装置であって、

前記入力信号伝達部および前記帰還信号伝達部はそれぞれ少なくとも一つのアイソレータを有することを特徴とする信号伝達回路装置。

**【請求項3】**

請求項2記載の信号伝達回路装置であって、

前記アイソレータはトランスであることを特徴とする信号伝達回路装置。

**【請求項4】**

請求項3記載の信号伝達回路装置であって、

前記入力側回路、前記出力側回路、および前記トランスはそれぞれ異なる半導体基板上に形成されていることを特徴とする信号伝達回路装置。

**【請求項5】**

請求項3記載の信号伝達回路装置であって、

前記入力側回路と前記出力側回路はそれぞれ異なる半導体基板上に形成されており、前記トランスは、前記入力側回路または前記出力側回路と同じ基板上に形成されていることを特徴とする信号伝達回路装置。

**【請求項6】**

請求項3記載の信号伝達回路装置であって、

前記トランスの1次巻線と2次巻線は互いに別の接地電位に接続されていることを特徴とする信号伝達回路装置。

**【請求項7】**

請求項2記載の信号伝達回路装置であって、

前記アイソレータはフォトカプラであることを特徴とする信号伝達回路装置。

**【請求項8】**

請求項1記載の信号伝達回路装置であって、

前記入力信号復元回路はRSフリップフロップにより構成されていることを特徴とする信号伝達回路装置。

**【請求項9】**

請求項1記載の信号伝達回路装置であって、

前記帰還信号伝達部は、

前記制御出力信号に同期して連続パルスを有する帰還パルスを生成する帰還パルス生成回路と、

前記帰還パルスを波形整形する波形整形回路を有することを特徴とする信号伝達回路装置。

**【請求項10】**

請求項9記載の信号伝達回路装置であって、

前記波形整形回路は、

前記帰還パルスでオン、オフするスイッチングトランジスタと、

前記スイッチングトランジスタと協働して前記帰還パルスとは異なる整形帰還信号を生成するための電流源およびキャパシタと、

前記整形帰還信号が入力され前記整形帰還信号とは異なる前記帰還信号を生成するコンパレータを有することを特徴とする信号伝達回路装置。

**【請求項11】**

請求項1記載の信号伝達回路装置であって、

前記論理比較回路はエクスクルーシブOR回路を有することを特徴とする信号伝達回路装置。

**【請求項12】**

請求項1記載の信号伝達回路装置であって、

前記第1補正信号及び前記第2補正信号は連続パルスを有する信号であり、

10

20

30

40

50

前記第1パルス生成回路は、前記制御入力信号と前記論理比較信号が前記第1の組み合

わせとなった期間に連続パルスを有する前記第1補正信号を出力し、

前記第2パルス生成回路は、前記制御入力信号と前記論理比較信号が前記第2の組み合

わせとなった期間に連続パルスを有する前記第2補正信号を出力することを特徴とする信

号伝達回路装置。

【請求項13】

請求項1記載の信号伝達回路装置であって、

前記帰還信号伝達部は、

前記制御出力信号の立ち上がりエッジを検出し第1帰還パルスを生成する第1出力エッ

ジ検出回路と、

前記制御出力信号の立ち下がりエッジを検出し第2帰還パルスを生成する第2出力エッ

ジ検出回路と、

前記第1帰還パルスおよび前記第2帰還パルスがセット端子およびリセット端子に各別

に入力されるRSフリップフロップを有することを特徴とする信号伝達回路装置。 10

【請求項14】

請求項1記載の信号伝達回路装置であって、

前記帰還信号伝達部は、

前記制御出力信号の立ち上がりエッジおよび立ち下がりエッジを検出し帰還パルスを生

成する出力エッジ検出回路と、

前記帰還パルスがクロック端子に入力されるDフリップフロップを有することを特徴と

する信号伝達回路装置。 20

【請求項15】

請求項1記載の信号伝達回路装置であって、

前記入力信号復元回路はDフリップフロップにより構成されていることを特徴とする信

号伝達回路装置。

【請求項16】

請求項1記載の信号伝達回路装置であって、

前記信号伝達回路装置はさらに、

前記制御入力信号の立ち上がりエッジを検出し第1入力パルスを生成する第1エッジ検

出回路と、

前記制御入力信号の立ち下がりエッジを検出し第2入力パルスを生成する第2エッジ検

出回路を備え、

前記入力信号伝達部は、前記第1補正信号および前記第2補正信号とともに前記第1入

力パルスおよび前記第2入力パルスを受信することを特徴とする信号伝達回路装置。 30

【請求項17】

請求項16記載の信号伝達回路装置であって、

前記入力信号伝達部は、

前記第1補正信号と前記第1入力パルスを論理和処理する第1論理和回路と、

前記第2補正信号と前記第2入力パルスを論理和処理する第2論理和回路を有し、

前記入力信号復元回路は、

前記第1論理和回路の出力がセット端子に入力され、前記第2論理和回路の出力がリセ

ット端子に入力されるRSフリップフロップにより構成されていることを特徴とする信号

伝達回路装置。 40

【請求項18】

請求項17記載の信号伝達回路装置であって、

前記第1論理和回路および前記第2論理和回路は前記入力側回路に設けられていること

を特徴とする信号伝達回路装置。

【請求項19】

請求項16記載の信号伝達回路装置であって、

前記入力信号伝達部は、

50

前記第1補正信号、前記第2補正信号、前記第1入力パルス、および前記第2入力パルスを論理和処理する論理和回路を有し、

前記入力信号復元回路は、前記論理和回路の出力がクロック端子に入力されるDフリップフロップにより構成されていることを特徴とする信号伝遡回路装置。

**【請求項20】**

請求項19記載の信号伝遡回路装置であって、

前記論理和回路は前記入力側回路に設けられていることを特徴とする信号伝遡回路装置。

**【請求項21】**

入力側回路と出力側回路との間で信号の伝達が行われる信号伝遡回路装置であって、

10

前記信号伝遡回路装置は、

前記入力側回路に入力された制御入力信号を受信し、第1補正信号を出力する第1論理積回路と、

前記制御入力信号の反転信号を受信し、第2補正信号を出力する第2論理積回路と、

前記第1補正信号および前記第2補正信号を受信し、前記入力側回路から前記出力側回路へ信号の伝達を行う入力信号伝達部と、

前記入力信号伝達部の出力を受信し、前記制御入力信号と等価な制御出力信号を出力する入力信号復元回路と、

前記制御出力信号を受信し、前記出力側回路から前記入力側回路へ信号の伝達を行い、帰還信号を出力する帰還信号伝達部と、

20

前記制御入力信号および前記帰還信号を受信し、前記制御入力信号と前記帰還信号の論理比較を行い、論理比較信号を出力する論理比較回路と、

前記論理比較信号を受信し、前記論理比較信号に同期した論理比較パルス信号を出力する比較パルス生成回路を備え、

前記第1論理積回路は、前記制御入力信号とともに前記論理比較パルス信号を受信し、前記第2論理積回路は、前記制御入力信号の反転信号とともに前記論理比較パルス信号を受信することを特徴とする信号伝遡回路装置。

**【請求項22】**

入力側回路と出力側回路との間で信号の伝達が行われる信号伝遡回路装置であって、

30

前記信号伝遡回路装置は、

前記入力側回路に入力された制御入力信号の立ち上がりエッジを検出し第1入力パルスを生成する第1エッジ検出回路と、

前記制御入力信号の立ち下がりエッジを検出し第2入力パルスを生成する第2エッジ検出回路と、

前記制御入力信号、前記第1入力パルス、および前記第2入力パルスを受信し、前記第1入力パルスまたは前記第2入力パルスを受信したタイミングでセット信号またはリセット信号を出力する信号合成回路と、

前記セット信号および前記リセット信号を受信し、前記入力側回路から前記出力側回路へ信号の伝達を行う入力信号伝達部と、

前記入力信号伝達部の出力を受信し、前記制御入力信号と等価な制御出力信号を出力する入力信号復元回路と、

40

前記制御出力信号を受信し、前記出力側回路から前記入力側回路へ信号の伝達を行い、帰還信号を出力する帰還信号伝達部と、

前記制御入力信号および前記帰還信号を受信し、前記制御入力信号と前記帰還信号の論理比較を行い、論理比較信号を出力する論理比較回路と、

前記論理比較信号を受信し、前記論理比較信号に同期した論理比較パルス信号を出力する比較パルス生成回路を備え、

前記信号合成回路は、前記制御入力信号、前記第1入力パルス、および前記第2入力パルスとともに、前記論理比較パルス信号を受信し、前記論理比較パルス信号を受信したタイミングにおいても、前記セット信号または前記リセット信号の出力をを行うことを特徴と

50

する信号伝達回路装置。

【請求項 2 3】

請求項 2 2 記載の信号伝達回路装置であって、

前記信号合成回路は、前記第 1 入力パルス、前記第 2 入力パルス、および前記論理比較パルス信号を受信する論理和回路と、

前記制御入力信号と前記論理和回路の出力を受信し、前記セット信号を出力する第 1 論理積回路と、

前記制御入力信号の反転信号と前記論理和回路の出力を受信し、前記リセット信号を出力する第 2 論理積回路を有することを特徴とする信号伝達回路装置。

【請求項 2 4】

10

請求項 2 1 または 2 2 記載の信号伝達回路装置であって、

前記入力信号伝達部および前記帰還信号伝達部はそれ各自少なくとも一つのトランスを有することを特徴とする信号伝達回路装置。

【請求項 2 5】

請求項 2 1 または 2 2 記載の信号伝達回路装置であって、

前記入力信号復元回路は R S フリップフロップにより構成されていることを特徴とする信号伝達回路装置。

【請求項 2 6】

請求項 2 1 または 2 2 記載の信号伝達回路装置であって、

前記帰還信号伝達部は、

20

前記制御出力信号に同期して連続パルスを有する帰還パルスを生成する帰還パルス生成回路と、

前記帰還パルスを波形整形する波形整形回路を有することを特徴とする信号伝達回路装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本明細書中に開示されている第 1 の技術的特徴は、アイソレータを介して制御入力信号の伝達を行う信号伝達回路装置に関し、特に制御出力信号を入力側回路に帰還して信号の補正を行う機能を有する信号伝達回路装置に関する。

30

【0 0 0 2】

また、本明細書中に開示されている第 2 の技術的特徴は、コイルを集積化した半導体装置、並びに、その検査方法及び検査装置に関するものである。

【0 0 0 3】

また、本明細書中に開示されている第 3 の技術的特徴は、トランスを用いた信号伝達装置、及び、これを用いたモータ駆動装置に関するものである。

【背景技術】

【0 0 0 4】

<第 1 の背景技術>

従来、ハイブリッド自動車、電気自動車、家電機器、産業機器、および医療機器の分野において、入出力間を直流的に絶縁し、かつ信号の伝達を行うために、アイソレータを用いた信号伝達回路装置が用いられてきた。

40

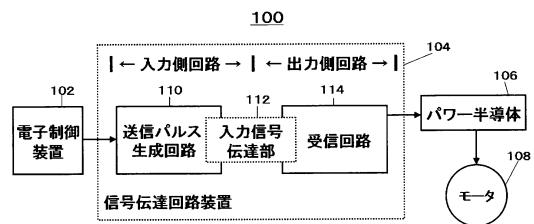

【0 0 0 5】

図 1 9 に、従来のたとえばハイブリッド自動車等に搭載されたモータを駆動するためのパワー半導体の駆動回路装置およびそれに用いる信号伝達回路装置を示す。パワー半導体の駆動回路装置 1 0 0 は、電子制御装置 1 0 2 、信号伝達回路装置 1 0 4 、パワー半導体 1 0 6 、およびモータ 1 0 8 を備えている。

【0 0 0 6】

電子制御装置 1 0 2 はたとえばハイブリッド自動車等に搭載されたモータ 1 0 8 を、パワー半導体 1 0 6 を介して制御するための制御入力信号を生成する。電子制御装置 1 0 2

50

は、この種の技術分野での E C U ( E n g i n e C o n t r o l U n i t ) に相当する。

**【 0 0 0 7 】**

信号伝達回路装置 104 は、送信パルス生成回路 110、入力信号伝達部 112 および受信回路 114 を備える。入力信号伝達部 112 は信号伝達回路装置 104 の入力側回路と出力側回路を直流的に絶縁するためのアイソレータとして、図示しないフォトカプラまたはトランジスタを有する。

**【 0 0 0 8 】**

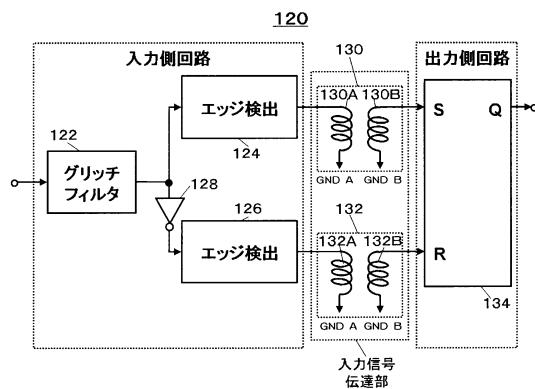

図 20 は特許文献 1 の図 1 に示された信号伝達回路装置であり、信号伝達回路装置 120 は、グリッヂフィルタ 122、エッジ検出器 124、126、インバータ 128、トランジスタ 130、132、およびフリップフロップ 134 を備える。

10

**【 0 0 0 9 】**

トランジスタ 130 は 1 次巻線 130A、2 次巻線 130B を備え、トランジスタ 132 は 1 次巻線 132A、2 次巻線 132B を備える。1 次巻線 130A、132A は接地電位 A ( G N D A ) に、2 次巻線 130B、132B は接地電位 A とは直流的に絶縁された別の接地電位 B ( G N D B ) に各別に接続されている。

**【 0 0 1 0 】**

また、特許文献 1 の図 8 を参照すると、第 1 基板 804 側に送信回路 802 および接地電位 A ( G N D A ) 等を設け、第 2 基板 808 側には 1 次巻線としての機能を有するトップコイル 806A、受信回路 810、2 次巻線としての機能を有するボトムコイル 806B および接地電位 B ( G N D B ) 等が設けられており、I C チップ上にトランジスタを含むアイソレータを形成するという技術思想が開示されている。

20

**【 0 0 1 1 】**

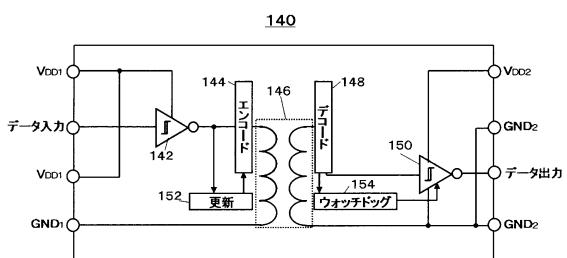

図 21 は、特許文献 2 の図 7 に開示されている信号伝達回路装置を参照符号を替えて示したものである。

**【 0 0 1 2 】**

特許文献 2 には、入力側回路において定期的にリフレッシュパルスを生成することで、制御入力信号と制御出力信号の不一致を修正する技術思想が開示されている。

**【 0 0 1 3 】**

信号伝達回路装置 140 はシュミットトリガインバータ 142、150、入力信号エンコード回路 144、トランジスタ 146、入力信号デコード回路 148、を備え、さらに入力信号更新回路 152、ウォッチドッグ回路 154 を備える。入力信号更新回路 152 は定期的にリフレッシュパルスを生成し、制御入力信号の更新を行う。ウォッチドッグ回路 154 は回路装置内の異常を検知し制御出力信号のシャットダウン等の制御を行う。

30

**【 0 0 1 4 】**

< 第 2 の背景技術 >

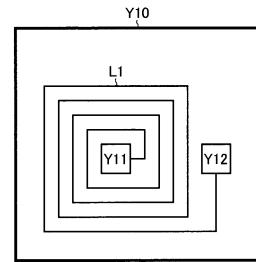

図 33 は、コイルを集積化した半導体装置の一従来例を示す模式図である。本従来例の半導体装置 Y10 は、コイル L1 と、パッド Y11 及び Y12 と、を有して成る。なお、コイル L1 の両端は、それぞれパッド Y11 及び Y12 に接続されている。

**【 0 0 1 5 】**

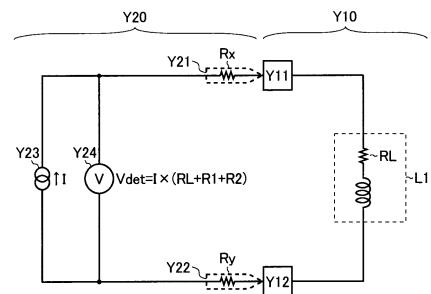

図 34 は、半導体装置 Y10 の不良品検査を説明するための模式図である。半導体装置 Y10 の不良品検査に用いられる検査装置 Y20 は、プローブ Y21 及び Y22 と、定電流源 Y23 と、電圧計 Y24 と、を有して成る。なお、定電流源 Y23 と電圧計 Y24 の各一端はプローブ Y21 に接続されており、各他端はプローブ Y22 に接続されている。

40

**【 0 0 1 6 】**

従来、半導体装置 Y10 の不良品検査では、パッド Y11 及び Y12 にそれぞれプローブ Y21 及び Y22 を接触させて、定電流源 Y23 からコイル L1 に所定の定電流 I を流し、そのときに発生するコイル L1 の両端間電圧 ( コイル L1 の直列抵抗成分 R\_L に起因して発生する電圧降下 ) を電圧計 Y24 で測定することにより、コイル L1 の断線チェックが行われていた。すなわち、コイル L1 の両端間電圧が正常に測定できない場合には、

50

コイル L 1 に断線が生じていると判断し、その半導体装置 Y 1 0 を不良品としてリジェクトしていた。

【 0 0 1 7 】

なお、コイルを集積化した半導体装置に関する従来技術の一例としては、特許文献 3 を挙げることができる。

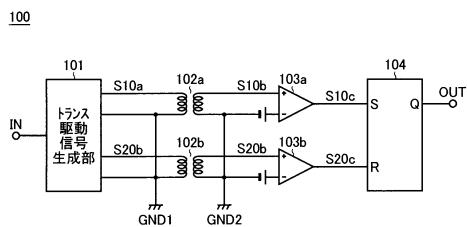

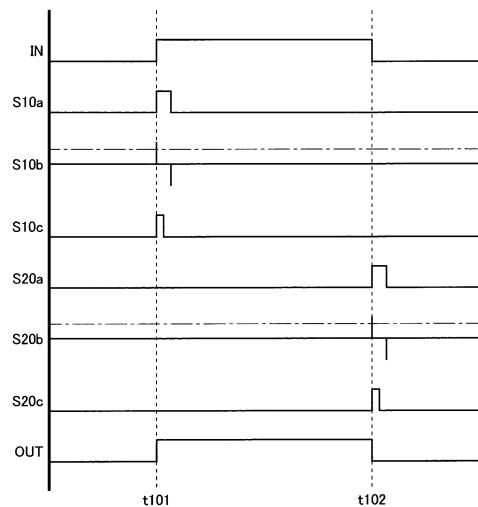

【 0 0 1 8 】

< 第 3 の背景技術 >

図 4 3 は、信号伝達装置の一従来例を示す回路ブロック図であり、図 4 4 は、その正常動作の一例を示すタイミングチャートである。本従来例の信号伝達装置 1 0 0 は、トランス駆動信号生成部 1 0 1 と、トランス 1 0 2 a 及び 1 0 2 b と、コンパレータ 1 0 3 a 及び 1 0 3 b と、S R フリップフロップ 1 0 4 と、を有しており、トランス 1 0 2 a 及び 1 0 2 b を用いて、一次側回路の接地電圧 G N D 1 と二次側回路の接地電圧 G N D 2 を絶縁しながら、両回路間での信号伝達を実現するものである。

10

【 0 0 1 9 】

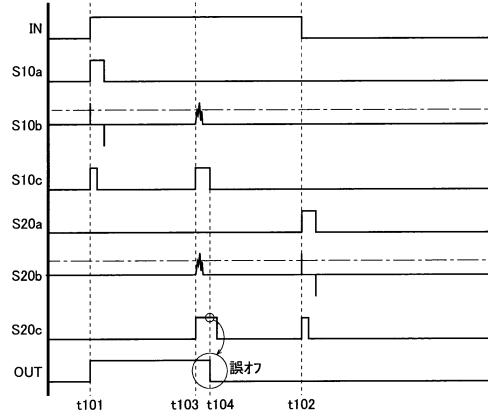

トランス駆動信号生成部 1 0 1 は、トランス駆動信号 S 1 0 a 及び S 2 0 a を生成し、これらをトランス 1 0 2 a 及び 1 0 2 b の一次側巻線に各々出力する。なお、トランス駆動信号生成部 1 0 1 は、入力信号 I N の立上がりエッジをトリガとしてトランス駆動信号 S 1 0 a に 1 発のパルスを発生させる一方、入力信号 I N の立下がりエッジをトリガとしてトランス駆動信号 S 2 0 a に 1 発のパルスを発生させる。

20

【 0 0 2 0 】

トランス 1 0 2 a 及び 1 0 2 b は、それぞれ、トランス駆動信号 S 1 0 a 及び S 2 0 a に応じた誘起信号 S 1 0 b 及び S 2 0 b を各々の二次側巻線に発生させる。

【 0 0 2 1 】

コンパレータ 1 0 3 a 及び 1 0 3 b は、それぞれ、誘起信号 S 1 0 b 及び S 2 0 b と所定の閾値電圧とを比較して比較信号 S 1 0 c 及び S 2 0 c を生成し、これらを S R フリップフロップ 1 0 4 のセット入力端 ( S ) 及びリセット入力端 ( R ) に各々出力する。

30

【 0 0 2 2 】

S R フリップフロップ 1 0 4 は、比較信号 S 1 0 c の立上がりエッジをトリガとして出力信号 O U T をハイレベルにセットし、比較信号 S 2 0 c の立上がりエッジをトリガとして出力信号 O U T をローレベルにリセットする。

30

【 0 0 2 3 】

従って、正常な信号伝達動作が行われていれば、S R フリップフロップ 1 0 4 から出力される出力信号 O U T は、トランス駆動信号生成部 1 0 1 に入力される入力信号 I N と同一信号となる。

【 0 0 2 4 】

なお、上記に関連する従来技術の一例としては、特許文献 1 を挙げることができる。

【 先行技術文献 】

【 特許文献 】

【 0 0 2 5 】

【 特許文献 1 】米国特許第 7 0 7 5 3 2 9 号明細書

40

【 特許文献 2 】特開 2 0 0 7 - 1 2 3 6 5 0 号公報

【 特許文献 3 】特開 2 0 0 1 - 8 5 2 4 8 号公報

【 発明の概要 】

【 発明が解決しようとする課題 】

【 0 0 2 6 】

< 第 1 の技術的特徴が解決しようとする第 1 の課題 >

しかしながら、図 1 9 、図 2 0 に示す信号伝達回路装置はともに、入力側回路において入力された信号を出力側回路へ一方的に送信するものであり、たとえば入力信号伝達部におけるノイズの発生等に起因する入出力信号の不一致といった異常状態を回避する手段を兼ね備えてはいない。

50

**【0027】**

特許文献2には、リフレッシュパルスの発生により所定間隔ごとに制御出力信号を更新する技術思想が開示されているものの、制御出力信号と制御入力信号を直接比較して入出力信号の不一致を回避する技術思想に関しては何ら示唆されていない。特許文献2記載の信号伝達回路装置においては、耐ノイズ特性を向上させるためにはリフレッシュパルスの周波数を高くする必要があり、安定性、消費電力の面において不具合が生じ得る。

**【0028】**

本発明はこうした不具合を克服したものであって、何らかの問題により制御入力信号が制御出力信号へ正確に伝達されない異常状態が発生した場合に、該異常状態の検出に基づいて制御出力信号の補正が行われる信号伝達回路装置を提供することを目的とする。 10

**【0029】**

<第2の技術的特徴が解決しようとする第2の課題>

ところで、図33、図34に示した半導体装置Y10の不良品検査に際して、電圧計Y24で得られる検出電圧Vdetの電圧値は、下記(1)式で表される。

**【0030】**

$$V_{det} = I \times (R_L + R_x + R_y) \quad \dots \quad (1)$$

**【0031】**

なお、上記(1)式中において、変数R<sub>x</sub>はプローブY21をパッドY11に接触させたときの接触抵抗成分であり、変数R<sub>y</sub>はプローブY22をパッドY12に接触させたときの接触抵抗成分である。 20

**【0032】**

上記(1)式から分かるように、検出電圧V<sub>det</sub>は、コイルL1の直列抵抗成分R<sub>L</sub>だけでなく、プローブY21及びY22の接触抵抗成分R<sub>x</sub>及びR<sub>y</sub>の影響を受ける。特に、コイルL1の直列抵抗成分R<sub>L</sub>は、プローブY21及びY22の接触抵抗成分R<sub>x</sub>及びR<sub>y</sub>と大差のない極めて微小な抵抗成分(数~数十)であるため、半導体装置Y10の不良品検査に際して、直列抵抗成分R<sub>L</sub>を正確に測定し、コイルL1の抵抗値異常を検出することは非常に困難であった。

**【0033】**

そのため、上記従来の半導体装置Y10では、コイルL1の抵抗値異常(例えば、巻線同士の中途短絡)が生じていても、コイルL1の断線が生じていなければ、これを不良品としてリジェクトすることができず、市場に流出させてしまうおそれがあった。 30

**【0034】**

本発明は、上記の問題点に鑑み、コイルの抵抗値異常を検査することが可能な半導体装置及びその検査方法を提供することを目的とする。

**【0035】**

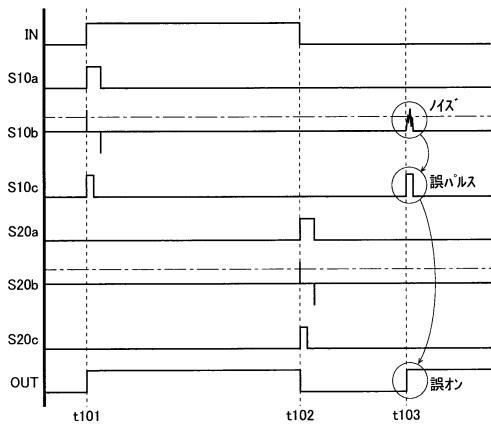

<第3の技術的特徴が解決しようとする第3の課題>

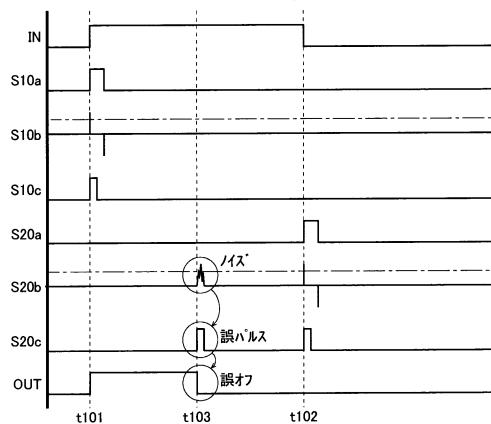

しかしながら、図43に示した上記従来例の信号伝達装置100では、二次側回路の接地電圧GND2に変動が生じた場合など、トランジスタ102a及び102bの二次側巻線に現れる誘起信号S10b及びS20bの一方または両方にノイズが発生した場合に、比較信号S10c及びS20cに誤パルスが生じて、出力信号OUTが意図しない論理レベルに変遷してしまうという課題があった。 40

**【0036】**

例えば、図45Aでは、入力信号INがローレベルであるときに、誘起信号S10bにノイズが発生したことにより、比較信号S10cに誤パルスが生じて、出力信号OUTが意図せずハイレベルに変遷してしまう様子が描写されている。また、図45Bでは、入力信号INがハイレベルであるときに、誘起信号S20bにノイズが発生したことにより、比較信号S20cに誤パルスが生じて、出力信号OUTが意図せずローレベルに変遷してしまう様子が描写されている。

**【0037】**

また、トランジスタ102a及び102bが近接して配置されている場合には、誘起信号S 50

10 b 及び S 20 b の両方に同一のノイズが発生すると考えられるが、このような場合でも、出力信号 OUT が意図しない論理レベルに変遷してしまう可能性はあり得る。

#### 【0038】

例えば、SR フリップフロップ 104 は、比較信号 S 10 c 及び S 20 c がいずれもハイレベルとなっている間、出力信号 OUT をそれ以前の論理レベルに保持する構成であると仮定する。このような構成が採用されている場合、誘起信号 S 10 b 及び S 20 b の両方に同一のノイズが発生したときに、比較信号 S 10 c 及び S 20 c が同時にハイレベルに立ち上がり、かつ、同時にローレベルに立ち下がるのであれば、出力信号 OUT が意図しない論理レベルに変遷することはない。

#### 【0039】

しかしながら、実際には、コンパレータ 103 a 及び 103 b の応答速度のばらつき等により、比較信号 S 10 c 及び S 20 c の論理変遷タイミングにはズレが生じるため、一方が先にハイレベルに立ち上がったり、一方が先にローレベルに立ち下がったりすると、出力信号 OUT が意図しない論理レベルに変遷してしまう。

#### 【0040】

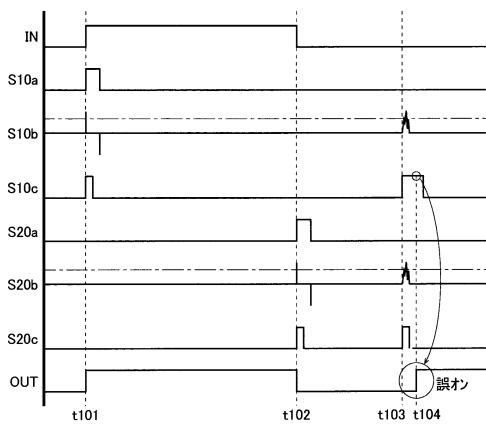

例えば、図 46 A では、入力信号 IN がローレベルであるときに、誘起信号 S 10 b 及び S 20 b の両方にノイズが発生した際、比較信号 S 10 c 及び S 20 c が同時にハイレベルに立ち上がったものの、比較信号 S 20 c が先にローレベルに立ち下がった結果、出力信号 OUT が意図せずハイレベルに変遷してしまう様子が描写されている。また、図 46 B では、入力信号 IN がハイレベルであるときに、誘起信号 S 10 b 及び S 20 b の両方にノイズが発生した際、比較信号 S 10 c 及び S 20 c が同時にハイレベルに立ち上がったものの、比較信号 S 10 c が先にローレベルに立ち下がった結果、出力信号 OUT が意図せずローレベルに変遷してしまう様子が描写されている。

#### 【0041】

本発明は、本願の発明者らによって見い出された上記の問題点に鑑み、ノイズの影響を受けにくい信号伝達装置、及び、これを用いたモータ駆動装置の提供を目的とする。

#### 【課題を解決するための手段】

#### 【0042】

##### <第 1 の課題を解決するための手段>

本明細書において、「復元」とは元の信号の形態、位置（位相）に戻すことである。たとえば制御出力信号を例にすると、入力端子に入力された制御入力信号は出力端子に至るまでに各種各様の信号に変換または整形されるが、出力端子に出力される時点では制御出力信号は元の制御入力信号の形態、位置（位相）に戻される。この動作を「復元」と称する。

#### 【0043】

また、本明細書において「等価」とは、回路機能に支障が生じない程度に信号形態、信号の位置（位相）が所定の範囲に収まっていることを指す。

#### 【0044】

また、本明細書において「入力側回路」、「出力側回路」とは、信号が入力される回路部を「入力側回路」、信号が出力される回路部を「出力側回路」としてそれぞれ称する。本明細書において、「入力側回路」と「出力側回路」の境界は後述の入力信号伝達部または帰還信号伝達部であるが、これらの信号伝達部は「入力側回路」および「出力側回路」に跨って設けられている。

#### 【0045】

また、本明細書において「直流的に絶縁する」とは絶縁すべき対象物が導体では接続されていないということである。

#### 【0046】

また、本明細書において「第 1 電位」、「第 2 電位」とは矩形波信号におけるハイレベルまたはローレベルを指し、各信号におけるハイレベルおよびローレベルの電圧値は回路構成により所定の値に設定される。もちろん、信号ごとに第 1 電位または第 2 電位の電圧

10

20

30

40

50

値が異なる場合もある。本明細書においては、「第1電位」をハイレベル、「第2電位」をローレベルとして説明するが、もちろん「第1電位」をローレベル、「第2電位」をハイレベルとして信号伝遡回路装置を構成してもよい。

#### 【0047】

また、本明細書において「第1の組み合わせ」とは、制御入力信号と後述する帰還信号の比較結果が“不一致”であり、かつ制御入力信号が第1電位である組み合わせを指し、「第2の組み合わせ」とは、制御入力信号と帰還信号の比較結果が“不一致”であり、かつ制御入力信号が第2電位である組み合わせを指す。

#### 【0048】

また、本明細書において「出力信号補正機能」とは、制御出力信号の電位（第1電位または第2電位）が制御入力信号の電位と“不一致”的な状態となった場合に、制御出力信号の電位を制御入力信号の電位と“一致”させる機能を指す。10

#### 【0049】

本発明は、入力側回路と出力側回路との間で信号の伝達が行われる信号伝遡回路装置であって、前記信号伝遡回路装置は、

(a) 前記入力側回路に入力された制御入力信号を受信し、第1補正信号を出力する第1パルス生成回路と、20

(b) 前記制御入力信号を受信し、第2補正信号を出力する第2パルス生成回路と、

(c) 前記第1補正信号および前記第2補正信号を受信し、前記入力側回路から前記出力側回路へ信号の伝達を行う入力信号伝達部と、20

(d) 前記入力信号伝達部の出力を受信し、前記制御入力信号と等価な制御出力信号を出力する入力信号復元回路と、20

(e) 前記制御出力信号を受信し、前記出力側回路から前記入力側回路へ信号の伝達を行い、帰還信号を出力する帰還信号伝達部と、20

(f) 前記制御入力信号および前記帰還信号を受信し、前記制御入力信号と前記帰還信号の論理比較を行い、論理比較信号を出力する論理比較回路を備え、20

(g) 前記第1パルス生成回路は、前記制御入力信号とともに前記論理比較信号を受信し、前記制御入力信号と前記論理比較信号が第1の組み合わせとなった場合に前記第1補正信号を出力し、前記第2パルス生成回路は、前記制御入力信号とともに前記論理比較信号を受信し、前記制御入力信号と前記論理比較信号が前記第1の組み合わせとは異なる第2の組み合わせとなった場合に前記第2補正信号を出力する（第1-1の構成）。30

#### 【0050】

こうした構成の信号伝遡回路装置は、制御出力信号を入力側回路に帰還する帰還信号伝達部と、帰還信号と制御入力信号の論理比較を行う論理比較回路を備えており、第1パルス生成回路および第2パルス生成回路は制御入力信号と論理比較回路の論理比較結果に基づいて、適宜、各補正信号を出力するので、制御入力信号と制御出力信号の“不一致”が発生した場合にも速やかに制御出力信号の補正を行い、制御入力信号と制御出力信号を“一致”させることができる。

#### 【0051】

本発明において、前記入力信号伝達部および前記帰還信号伝達部はそれぞれ少なくとも一つのアイソレータを有する（第1-2の構成）。40

#### 【0052】

こうした構成の信号伝遡回路装置は、入力側回路と出力側回路がアイソレータによって直列的に絶縁されるため、接地電位の異なる2つのブロック間の信号伝達を行うことができる。

#### 【0053】

本発明において、前記アイソレータはトランスである（第1-3の構成）。

#### 【0054】

こうした構成の信号伝遡回路装置は、入力側回路と出力側回路を直列的に絶縁するとともに、信号伝達時の遅延が少なく、高い周波数の信号に対しても正確な信号伝達を行うこ50

とができる。

【0055】

本発明において、前記入力側回路、前記出力側回路、および前記トランスはそれぞれ異なる半導体基板上に形成するとともに1つのパッケージの中に一体的に構成する（第1-4の構成）。

【0056】

本発明において、前記入力側回路、前記出力側回路をそれぞれ異なる半導体基板上に形成し、前記トランスは、前記入力側回路または前記出力側回路と同じ基板上に形成してもよい（第1-5の構成）。

【0057】

本発明において、前記トランスの1次巻線と2次巻線は互いに別の接地電位に接続されている（第1-6の構成）。

【0058】

本発明において、前記アイソレータはフォトカプラであってもよい（第1-7の構成）。

【0059】

本発明において、前記入力信号復元回路はRSフリップフロップにより構成されている（第1-8の構成）。

【0060】

こうした構成の信号伝達回路装置は、入力信号伝達部により入力側回路から出力側回路へ伝達された信号がRSフリップフロップのセット端子とリセット端子に各別に入力されるため、セット端子またはリセット端子に連続して信号が入力された場合であっても誤動作を生じる事なく制御入力信号と等価な制御出力信号を出力することができる。

【0061】

本発明において、前記帰還信号伝達部は、前記制御出力信号に同期して連続パルスを有する帰還パルスを生成する帰還パルス生成回路と、前記帰還パルスを波形整形する波形整形回路を有する（第1-9の構成）。

【0062】

こうした構成の信号伝達回路装置は、帰還信号伝達部におけるアイソレータの数がひとつで済み、さらに、帰還信号伝達部の耐ノイズ特性を高めることができる。

【0063】

本発明において、前記波形整形回路は、前記帰還パルスでオン、オフするスイッチングトランジスタと、前記スイッチングトランジスタと協働して前記帰還パルスとは異なる整形帰還信号を生成するための電流源およびキャパシタと、前記整形帰還信号が入力され前記整形帰還信号とは異なる前記帰還信号を生成するコンパレータを有する（第1-10の構成）。

【0064】

こうした構成の信号伝達回路装置は、比較的簡便な構成により帰還パルスの波形整形を行うことができる。

【0065】

本発明において、前記論理比較回路はエクスクルーシブOR回路を有する（第1-11の構成）。

【0066】

こうした構成の信号伝達回路装置は、論理比較回路の構成を簡便化することができる。

【0067】

本発明において、前記第1補正信号及び前記第2補正信号は連続パルスを有する信号であり、前記第1パルス生成回路は、前記制御入力信号と前記論理比較信号が前記第1の組み合わせとなった期間に連続パルスを有する前記第1補正信号を出力し、前記第2パルス生成回路は、前記制御入力信号と前記論理比較信号が前記第2の組み合わせとなった期間に連続パルスを有する前記第2補正信号を出力する構成としてもよい（第1-12の構成）

10

20

30

40

50

)。

#### 【0068】

こうした構成の信号伝達回路装置は、第1パルス生成回路および第2パルス生成回路が入出力“不一致”的期間に連続パルスを生成するため、入出力の不一致が解消されるまでパルスが生成され続けることとなり、信号伝達回路装置の信頼性が向上する。

#### 【0069】

本発明において、前記帰還信号伝達部は、前記制御出力信号の立ち上がりエッジを検出し第1帰還パルスを生成する第1出力エッジ検出回路と、前記制御出力信号の立ち下がりエッジを検出し第2帰還パルスを生成する第2出力エッジ検出回路と、前記第1帰還パルスおよび前記第2帰還パルスがセット端子およびリセット端子に各別に入力されるRSフリップフロップを有する構成としてもよい(第1-13の構成)。 10

#### 【0070】

こうした構成の信号伝達回路装置は、制御出力信号に対する帰還信号の遅延を大幅に低減することができる。

#### 【0071】

本発明において、前記帰還信号伝達部は、前記制御出力信号の立ち上がりエッジおよび立ち下がりエッジを検出し帰還パルスを生成する出力エッジ検出回路と、前記帰還パルスがクロック端子に入力されるDフリップフロップを有する構成としてもよい(第1-14の構成)。

#### 【0072】

こうした構成の信号伝達回路装置は、制御出力信号に対する帰還信号の遅延を大幅に低減することができ、さらに、帰還信号伝達部のアイソレータの数を減らすことができる。 20

#### 【0073】

本発明において、前記入力信号復元回路はDフリップフロップにより構成されていてもよい(第1-15の構成)。

#### 【0074】

こうした構成の信号伝達回路装置は、入力信号復元回路に入力する信号数が一つで済み、入力信号復元回路にRSフリップフロップを用いた場合と比較して、入力信号伝達部のアイソレータの数を減らすことができる。

#### 【0075】

本発明において、前記信号伝達回路装置はさらに、前記制御入力信号の立ち上がりエッジを検出し第1入力パルスを生成する第1エッジ検出回路と、前記制御入力信号の立ち下がりエッジを検出し第2入力パルスを生成する第2エッジ検出回路を備え、前記入力信号伝達部は、前記第1補正信号および前記第2補正信号とともに前記第1入力パルスおよび前記第2入力パルスを受信する構成としてもよい(第1-16の構成)。 30

#### 【0076】

こうした構成の信号伝達回路装置は、入力信号伝達部が、第1補正信号及び第2補正信号とともに、第1入力パルスおよび第2入力パルスを受信し、入力信号復元部へ信号を送信するので、制御入力信号における電位の遷移は第1入力パルスおよび第2入力パルスに基づいて速やかに制御出力信号へと反映される。従って制御出力信号は、制御入力信号に対する帰還信号の遅延等の影響を受けることが無く、第1パルス生成回路および第2パルス生成回路に基づく出力信号補正機能を有したまま、制御入力信号の最小入力パルス幅を大幅に小さくすることができる。 40

#### 【0077】

本発明において、前記入力信号伝達部は、前記第1補正信号と前記第1入力パルスを論理和処理する第1論理和回路と、前記第2補正信号と前記第2入力パルスを論理和処理する第2論理和回路を有し、前記入力信号復元回路は、前記第1論理和回路の出力がセット端子に入力され、前記第2論理和回路の出力がリセット端子に入力されるRSフリップフロップにより構成されていてもよい(第1-17の構成)。

#### 【0078】

50

本発明において、前記第1論理和回路および前記第2論理和回路は前記入力側回路に設けられている（第1-18の構成）。

【0079】

こうした構成の信号伝達回路装置は、信号の論理和処理を行うことで入力信号伝達部のアイソレータの数を減らすことができるとともに、第1補正信号と第1入力パルス、第2補正信号と第2入力パルスがそれぞれ相互補完の関係となり、信号伝達回路装置の耐ノイズ特性がさらに向上する。

【0080】

本発明において、前記入力信号伝達部は、前記第1補正信号、前記第2補正信号、前記第1入力パルス、および前記第2入力パルスを論理和処理する論理和回路を有し、前記入力信号復元回路は、前記論理和回路の出力がクロック端子に入力されるDフリップフロップにより構成されていてもよい（第1-19の構成）。

10

【0081】

本発明において、前記論理和回路は前記入力側回路に設けられている（第1-20の構成）。

【0082】

こうした構成の信号伝達回路装置は、入力信号伝達部におけるアイソレータの数を減らすことができ、信号伝達回路装置の小型化を図ることができる。

【0083】

本発明の別の信号伝達回路装置は、

20

(a) 入力側回路に入力された制御入力信号を受信し、第1補正信号を出力する第1論理積回路と、

(b) 前記制御入力信号の反転信号を受信し、第2補正信号を出力する第2論理積回路と、

(c) 前記第1補正信号および前記第2補正信号を受信し、前記入力側回路から出力側回路へ信号の伝達を行う入力信号伝達部と、

(d) 前記入力信号伝達部の出力を受信し、前記制御入力信号と等価な制御出力信号を出力する入力信号復元回路と、

(e) 前記制御出力信号を受信し、前記出力側回路から前記入力側回路へ信号の伝達を行い、帰還信号を出力する帰還信号伝達部と、

30

(f) 前記制御入力信号および前記帰還信号を受信し、前記制御入力信号と前記帰還信号の論理比較を行い、論理比較信号を出力する論理比較回路と、

(g) 前記論理比較信号を受信し、前記論理比較信号に同期した論理比較パルス信号を出力する比較パルス生成回路を備え、

(h) 前記第1論理積回路は、前記制御入力信号とともに前記論理比較パルス信号を受信し、前記第2論理積回路は、前記制御入力信号の反転信号とともに前記論理比較パルス信号を受信する（第1-21の構成）。

【0084】

本発明のさらに別の信号伝達回路装置は、

(a) 入力側回路に入力された制御入力信号の立ち上がりエッジを検出し第1入力パルスを生成する第1エッジ検出回路と、

40

(b) 前記制御入力信号の立ち下がりエッジを検出し第2入力パルスを生成する第2エッジ検出回路と、

(c) 前記制御入力信号、前記第1入力パルス、および前記第2入力パルスを受信し、前記第1入力パルスまたは前記第2入力パルスを受信したタイミングでセット信号またはリセット信号を出力する信号合成回路と、

(d) 前記セット信号および前記リセット信号を受信し、前記入力側回路から前記出力側回路へ信号の伝達を行う入力信号伝達部と、

(e) 前記入力信号伝達部の出力を受信し、前記制御入力信号と等価な制御出力信号を出力する入力信号復元回路と、

50

( f ) 前記制御出力信号を受信し、前記出力側回路から前記入力側回路へ信号の伝達を行い、帰還信号を出力する帰還信号伝達部と、

( g ) 前記制御入力信号および前記帰還信号を受信し、前記制御入力信号と前記帰還信号の論理比較を行い、論理比較信号を出力する論理比較回路と、

( h ) 前記論理比較信号を受信し、前記論理比較信号に同期した論理比較パルス信号を出力する比較パルス生成回路を備え、

( i ) 前記信号合成回路は、前記制御入力信号、前記第1入力パルス、および前記第2入力パルスとともに、前記論理比較パルス信号を受信し、前記論理比較パルス信号を受信したタイミングにおいても、前記セット信号または前記リセット信号の出力を行う（第1-22の構成）。

10

#### 【0085】

本発明において前記信号合成回路は、

( a ) 前記第1入力パルス、前記第2入力パルス、および前記論理比較パルス信号を受信する論理和回路と、

( b ) 前記制御入力信号と前記論理和回路の出力を受信し、前記セット信号を出力する第1論理積回路と、

( c ) 前記制御入力信号の反転信号と前記論理和回路の出力を受信し、前記リセット信号を出力する第2論理積回路を有する構成としてもよい（第1-23の構成）。

#### 【0086】

また、上記第1-21または第1-22の構成から成る信号伝達回路装置において、前記入力信号伝達部および前記帰還信号伝達部はそれぞれ少なくとも一つのトランスを有する構成（第1-24の構成）にするとよい。

20

#### 【0087】

また、上記第1-21または第1-22の構成から成る信号伝達回路装置において、前記入力信号復元回路はRSフリップフロップにより構成されている構成（第1-25の構成）にするとよい。

#### 【0088】

また、上記第1-21または第1-22の構成から成る信号伝達回路装置において、前記帰還信号伝達部は、前記制御出力信号に同期して連続パルスを有する帰還パルスを生成する帰還パルス生成回路と、前記帰還パルスを波形整形する波形整形回路とを有する構成（第1-26の構成）にするとよい。

30

#### 【0089】

##### <第2の課題を解決するための手段>

上記目的を達成するために、本発明に係る半導体装置は、コイルを集積化した半導体装置であって、前記コイルの一端には、第1の電流供給用パッドと第1の電圧測定用パッドが接続されており、前記コイルの他端には、第2の電流供給用パッドと第2の電圧測定用パッドが接続されている構成（第2-1の構成）とされている。

#### 【0090】

なお、上記第2-1の構成から成る半導体装置において、前記第1の電流供給用パッドと前記第1の電圧測定用パッドは、第1の電流供給用プローブと第1の電圧測定用プローブを同時に接触させることができ面積を有する第1の共用パッドとして一体的に形成されており、前記第2の電流供給用パッドと前記第2の電圧測定用パッドは、第2の電流供給用プローブと第2の電圧測定用プローブを同時に接触させることができ面積を有する第2の共用パッドとして一体的に形成されている構成（第2-2の構成）にするとよい。

40

#### 【0091】

また、上記第2-1または第2-2の構成から成る半導体装置を検査する検査方法は、前記第1の電流供給用パッドと前記第2の電流供給用パッドとの間に所定の定電流を流すステップと、前記第1の電圧測定用パッドと前記第2の電圧測定用パッドとの間に発生する電圧を測定するステップと、を有する構成（第2-3の構成）にするとよい。

#### 【0092】

50

また、上記第2-1または第2-2の構成から成る半導体装置を検査する検査装置は、前記第1の電流供給用パッドに接触させる第1の電流供給用プローブと、前記第1の電圧測定用パッドに接触させる第1の電圧測定用プローブと、前記第2の電流供給用パッドに接触させる第2の電流供給用プローブと、前記第2の電圧測定用パッドに接触させる第2の電圧測定用プローブと、前記第1の電流供給用プローブと前記第2の電流供給用プローブとの間に所定の定電流を流す定電流源と、前記第1の電圧測定用プローブと前記第2の電圧測定用プローブとの間に発生する電圧を測定する電圧計と、を有する構成（第2-4の構成）にするとよい。

#### 【0093】

<第3の課題を解決するための手段>

上記目的を達成するために、本発明に係る信号伝達装置は、入力信号が第1論理レベルから第2論理レベルに変遷するパルスエッジに応じて第1トランス駆動信号に（ $N + a$ ）発（ただし、 $N \geq 2$ 、 $a \geq 0$ ）のパルスを発生させ、前記入力信号が前記第2論理レベルから前記第1論理レベルに変遷するパルスエッジに応じて第2トランス駆動信号に（ $N + a$ ）発のパルスを発生させるトランス駆動信号生成部と；一次側巻線に入力される前記第1トランス駆動信号に応じて二次側巻線に第1誘起信号を発生させる第1トランスと；一次側巻線に入力される前記第2トランス駆動信号に応じて二次側巻線に第2誘起信号を発生させる第2トランスと；前記第1誘起信号と所定の閾値電圧とを比較して第1比較信号を生成する第1コンパレータと；前記第2誘起信号と所定の閾値電圧とを比較して第2比較信号を生成する第2コンパレータと；前記第1比較信号に $N$ 発のパルスが発生したことを検出して第1検出信号にパルスを発生させる第1パルス検出部と；前記第2比較信号に $N$ 発のパルスが発生したことを検出して第2検出信号にパルスを発生させる第2パルス検出部と；前記第1検出信号に発生されたパルスに応じて出力信号を前記第1論理レベルから前記第2論理レベルに変遷させ、前記第2検出信号に発生されたパルスに応じて前記出力信号を前記第2論理レベルから前記第1論理レベルに変遷させるS R フリップフロップと；を有する構成（第3-1の構成）とされている。

#### 【0094】

なお、上記第3-1の構成から成る信号伝達装置において、前記第1パルス検出部は、前記第1比較信号に発生されたパルス数をカウントし、そのカウント値が $N$ に達したときに前記第1検出信号にパルスを発生させるカウンタであり、前記第2パルス検出部は、前記第2比較信号に発生されたパルス数をカウントし、そのカウント値が $N$ に達したときに前記第2検出信号にパルスを発生させるカウンタである構成（第3-2の構成）にするとよい。

#### 【0095】

また、上記第3-2の構成から成る信号伝達装置において、前記第1パルス検出部は、前記第2比較信号に発生されたパルスによってカウント値がリセットされ、前記第2パルス検出部は、前記第1比較信号に発生されたパルスによってカウント値がリセットされる構成（第3-3の構成）にするとよい。

#### 【0096】

また、上記第3-3の構成から成る信号伝達装置において、前記トランス駆動信号生成部は所定周波数のパルス信号を生成するパルス生成部と；前記パルス信号のパルス数をカウントし、そのカウント値が（ $N + a$ ）に達したときに前記パルス生成部の駆動を停止させるカウンタと；前記入力信号のパルスエッジを検出したときに、前記パルス生成部の駆動を開始させるとともに、前記カウンタのカウント値をリセットするエッジ検出部と；前記入力信号に応じて、前記パルス信号を前記第1トランス駆動信号及び前記第2トランス駆動信号のいずれか一方として分配するパルス分配部と；を有する構成（第3-4の構成）にするとよい。

#### 【0097】

また、上記第3-4の構成から成る信号伝達装置において、前記パルス生成部は、前記エッジ検出部で前記入力信号のパルスエッジをが検出されてから、所定時間が経過するま

10

20

30

40

50

での間、前記パルス信号を生成しない構成（第3-5の構成）にするとよい。

**【0098】**

また、本発明に係る信号伝達装置は、入力信号のパルスエッジに応じてトランス駆動信号に( $N + a$ )発(ただし、 $N \geq 2$ 、 $a \geq 0$ )のパルスを発生させるトランス駆動信号生成部と；一次側巻線に入力される前記トランス駆動信号に応じて二次側巻線に誘起信号を発生させるトランスと；前記誘起信号と所定の閾値電圧とを比較して比較信号を生成するコンパレータと；前記比較信号に $N$ 発のパルスが発生したことを検出して出力信号にパルスを発生させるパルス検出部と；を有する構成（第3-6の構成）にするとよい。

**【0099】**

また、本発明に係るモータ駆動装置は、上記第3-1～第3-6いずれかの構成から成る信号伝達装置を有し、前記出力信号を用いてモータの駆動制御を行う構成（第3-7の構成）とされている。

10

**【発明の効果】**

**【0100】**

<第1の技術的特徴の効果>

本発明の信号伝達回路装置は、制御出力信号を帰還する帰還信号伝達部、制御入力信号と帰還信号の論理比較を行う論理比較回路、第1補正信号を出力する第1パルス生成回路、第2補正信号を出力する第2パルス生成回路を備えているので、制御入力信号と制御出力信号の不一致を検知し、速やかに制御出力信号の補正を行うことができる。また、第1パルス生成回路および第2パルス生成回路は入出力信号が不一致の場合のみ補正信号を出力するので低消費電力による動作が可能である。

20

**【0101】**

また、本発明においてさらに、制御入力信号の立ち上がりエッジを検出し第1入力パルスを生成する第1エッジ検出回路、制御入力信号の立ち下がりエッジを検出し第2入力パルスを生成する第2エッジ検出回路を有する構成とすれば、制御入力信号における電位の遷移が速やかに制御出力信号に反映され、制御入力信号に対する帰還信号の遅延等の影響を受けること無く、制御入力信号の最小入力パルス幅を大幅に小さくすることができる。これにより、信号伝達回路装置の用途を拡大することができる。

**【0102】**

<第2の技術的特徴の効果>

30

本発明に係る半導体装置及びその検査方法であれば、コイルの抵抗値異常を検査することが可能となる。

**【0103】**

<第3の技術的特徴の効果>

本発明によれば、ノイズの影響を受けにくい信号伝達装置、及び、これを用いたモータ駆動装置を提供することが可能となる。

**【図面の簡単な説明】**

**【0104】**

【図1】本発明の第1の実施の形態にかかる信号伝達回路装置を示す図

40

【図2】本発明の第2の実施の形態にかかる信号伝達回路装置を示す図

【図3】本発明の第2の実施の形態（図2）の変形例

【図4】本発明の第2の実施の形態（図2）の各部のパルス信号を示すタイミングチャート

【図5】本発明にかかる波形整形回路の具体的な回路構成を示す図

【図6】図5に示す波形整形回路の各部のタイミングチャート

【図7】本発明の第2の実施の形態（図2）にパルス幅の小さい信号を入力した場合の各部のパルス信号を示すタイミングチャート

【図8】本発明の第3の実施の形態にかかる信号伝達回路装置を示す図

【図9】本発明の第3の実施の形態（図8）の変形例

【図10】本発明の第3の実施の形態（図8）の別の変形例

50

- 【図11】本発明の第3の実施の形態(図8)の各部のパルス信号を示すタイミングチャート

- 【図12】本発明の第4の実施の形態にかかる信号伝回路装置を示す図

- 【図13】本発明の第4の実施の形態(図12)の変形例

- 【図14】本発明の第4の実施の形態(図12)の別の変形例

- 【図15】本発明の第4の実施の形態(図12)のさらに別の変形例

- 【図16】本発明の第4の実施の形態(図12)のさらに別の変形例

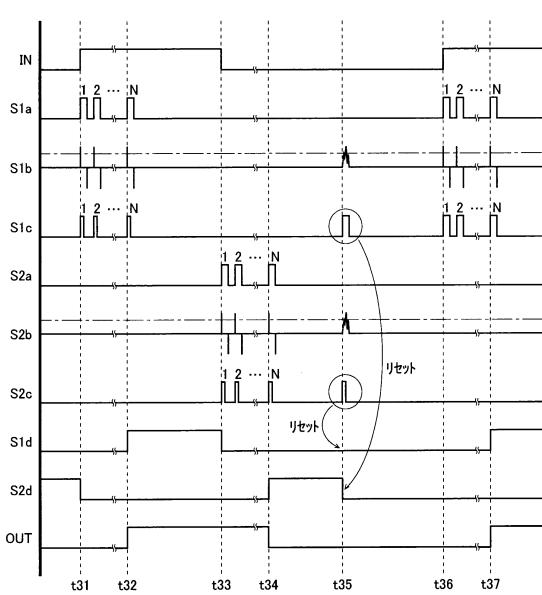

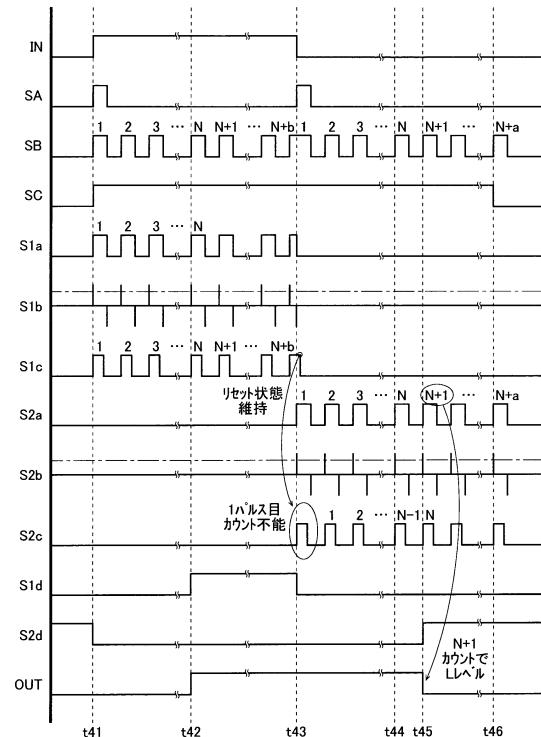

- 【図17】本発明の第4の実施の形態(図12)の各部のパルス信号を示すタイミングチャート

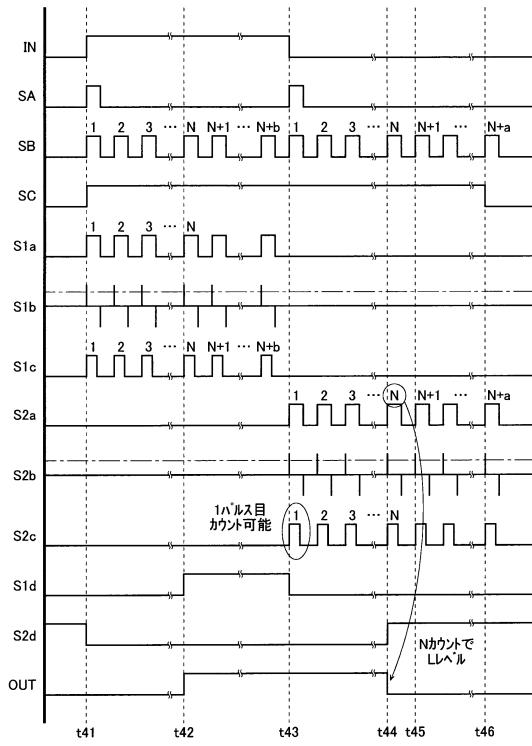

- 【図18】本発明の第4の実施の形態(図12)にパルス幅の小さい信号を入力した場合の各部のパルス信号を示すタイミングチャート 10

- 【図19】従来のパワー半導体の駆動回路装置を示す図

- 【図20】従来の信号伝回路装置を示す図

- 【図21】従来の別の信号伝回路装置を示す図

- 【図22】本発明に係る半導体装置の第1実施形態を示す模式図

- 【図23】半導体装置X10Aの不良品検査を説明するための模式図

- 【図24】本発明に係る半導体装置の第2実施形態を示す模式図

- 【図25】半導体装置X10Bの不良品検査を説明するための模式図

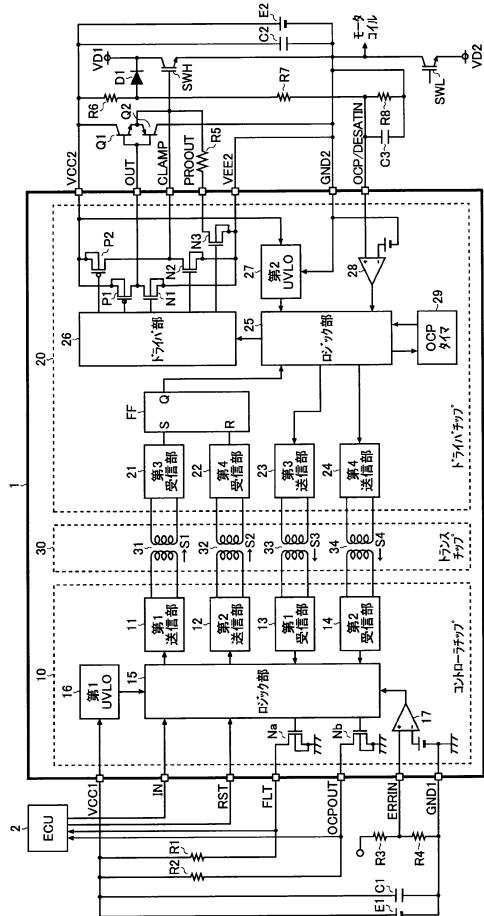

- 【図26】本発明に係る半導体装置を用いたモータ駆動装置の一構成例を示すブロック図

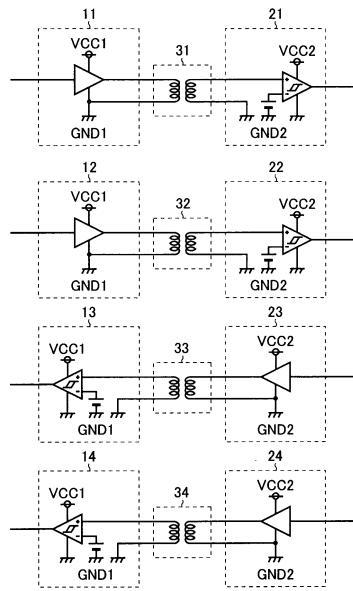

- 【図27】トランス31～34を介した送受信回路部分の詳細図 20

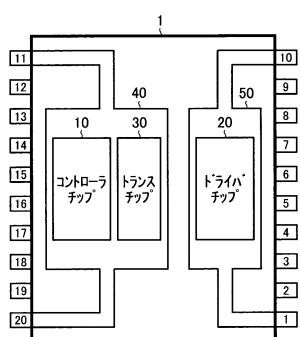

- 【図28】端子配置及びパッケージ内におけるチップ配列の一例を示す模式図

- 【図29】外部端子の説明テーブル

- 【図30】スイッチ制御装置1の電気的特性テーブル

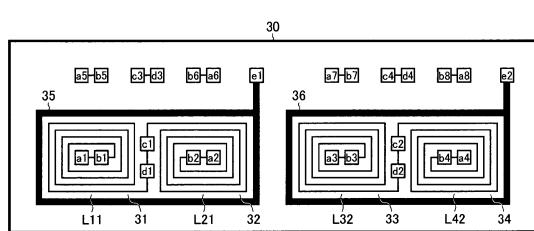

- 【図31】トランス31～34のレイアウト例を示す模式図

- 【図32】トランス31の縦構造を示すチップ断面図

- 【図33】コイルを集積化した半導体装置の一従来例を示す模式図

- 【図34】半導体装置Y10の不良品検査を説明するための模式図

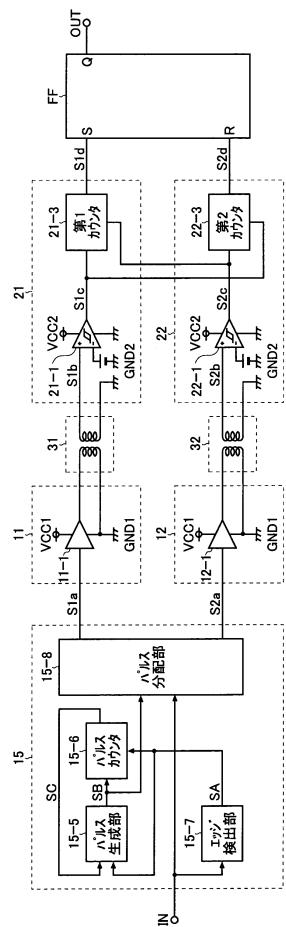

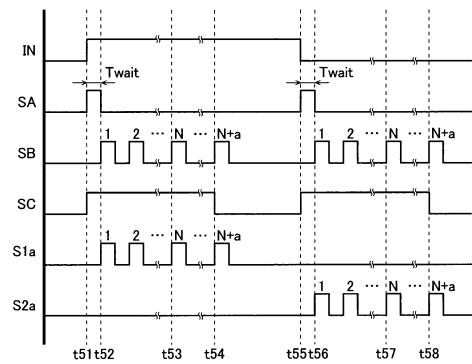

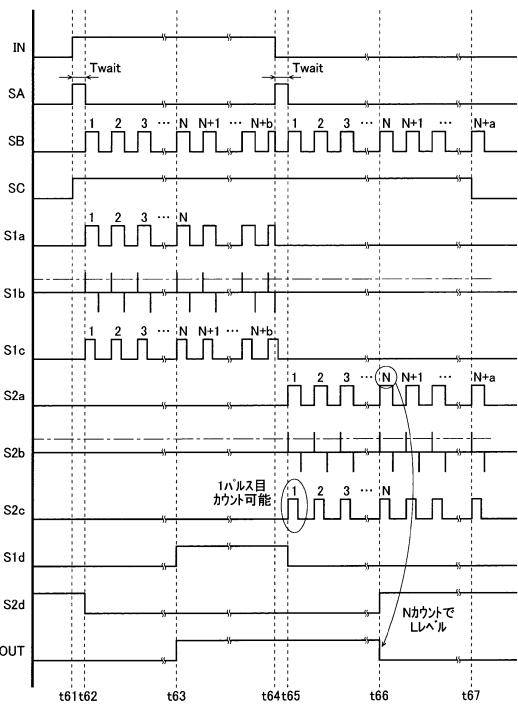

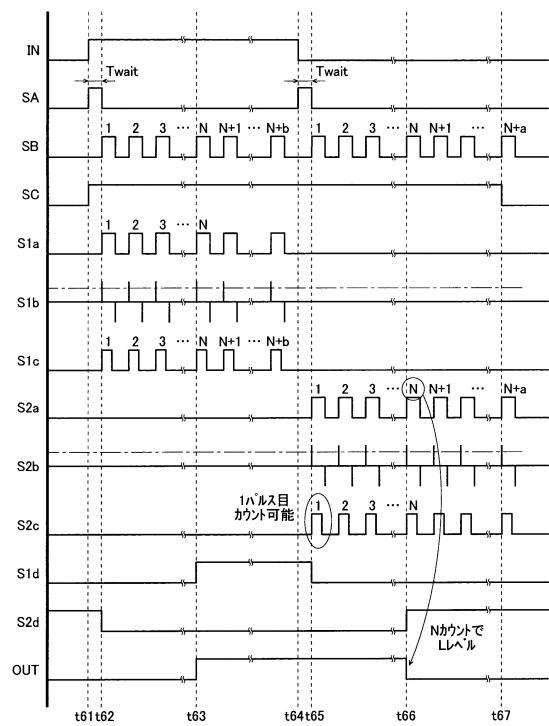

- 【図35】本発明に係る信号伝達装置の第1実施形態を示す回路ブロック図

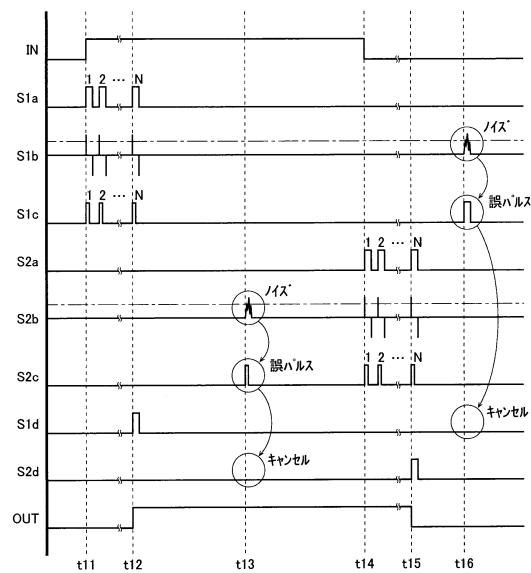

- 【図36】ノイズキャンセル動作の一例を示すタイミングチャート

- 【図37】本発明に係る信号伝達装置の第2実施形態を示す回路ブロック図 30

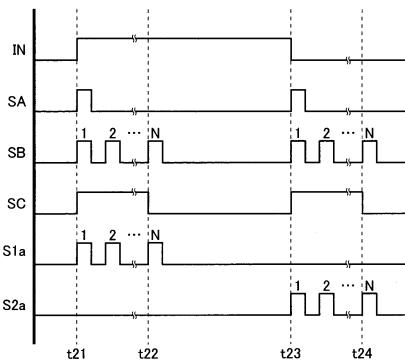

- 【図38】トランス駆動信号の第1生成動作を示すタイミングチャート

- 【図39】ノイズキャンセル動作の一例を示すタイミングチャート

- 【図40A】出力ジッタの発生理由を説明するためのタイミングチャート

- 【図40B】出力ジッタの発生理由を説明するためのタイミングチャート

- 【図41】トランス駆動信号の第2生成動作を示すタイミングチャート

- 【図42A】出力ジッタの解消理由を説明するためのタイミングチャート

- 【図42B】出力ジッタの解消理由を説明するためのタイミングチャート

- 【図43】信号伝達装置の一従来例を示す回路ブロック図

- 【図44】正常動作の一例を示すタイミングチャート

- 【図45A】異常動作の一例を示すタイミングチャート 40

- 【図45B】異常動作の一例を示すタイミングチャート

- 【図46A】異常動作の一例を示すタイミングチャート

- 【図46B】異常動作の一例を示すタイミングチャート

- 【発明を実施するための形態】

- 【0105】

- <第1の技術的特徴について>

- (第1の実施の形態)

- 図1は第1の実施の形態にかかる信号伝回路装置である。信号伝回路装置200は、入力端子201、第1パルス生成回路202、第2パルス生成回路204、入力信号伝達部206、入力信号復元回路208、出力端子219、帰還信号伝達部210、論理比 50

較回路 212 を備える。

**【0106】**

信号伝達回路装置 200 は入力信号伝達部 206 および帰還信号伝達部 210 を境にして入力側回路 200A と出力側回路 200B に分けることができる。また、入力信号伝達部 206 および帰還信号伝達部 210 は入力側回路 200A と出力側回路 200B に跨るように存在しており、入力信号伝達部 206 および帰還信号伝達部 210 は、アイソレータを有する構成とすることで、入力側回路 200A と出力側回路 200B を直流的に絶縁することができる。

**【0107】**

アイソレータとしては一般的にフォトカプラやトランスを用いる。近年、アイソレータは、I C チップ上にコイルを形成し、このコイルをトランスの 1 次巻線および 2 次巻線に適用したトランスが用いられてきている。本発明の各実施の形態はフォトカプラおよびトランスのどちらでも構成可能である。10

**【0108】**

ただし、アイソレータの特性の違いによる不具合を回避するために、入力信号伝達部 206 におけるアイソレータと帰還信号伝達部 210 におけるアイソレータは同じ種類の素子を用いることが望ましい。すなわち、入力信号伝達部 206 においてアイソレータとしてトランスを用いた場合には、帰還信号伝達部 210 においてもトランスを用いる。

**【0109】**

アイソレータとしてトランスを用いる場合、入力側回路 200A、トランス、出力側回路 200B をそれぞれ別の半導体基板上に形成する構成としてもよいし、入力側回路 200A、出力側回路 200B をそれぞれ別の半導体基板上に形成し、トランスは入力側回路 200A または出力側回路 200B と同一の基板上に形成する構成としてもよい。これは、本明細書における他の実施例についても同様である。20

**【0110】**

入力端子 201 に入力された制御入力信号 Sin は第 1 パルス生成回路 202 および第 2 パルス生成回路 204 へ送信される。通常、制御入力信号 Sin としては矩形パルス信号が用いられる。

**【0111】**

第 1 パルス生成回路 202 および第 2 パルス生成回路 204 は、制御入力信号 Sin の他に後述する論理比較回路 212 の出力である論理比較信号 Sc を受信し、それぞれ、制御入力信号 Sin と論理比較信号 Sc が第 1 の組み合わせまたは第 2 の組み合わせとなつた場合に、制御出力信号 Sout を補正する第 1 補正信号 Sa1 または第 2 補正信号 Sa2 を出力するように構成されている。30

**【0112】**

論理比較回路 212 は制御入力信号 Sin と帰還信号 Sf の論理比較を行い、両者の論理比較結果を論理比較信号 Sc として出力している。帰還信号 Sf は帰還信号伝達部 210 により制御出力信号 Sout を入力側回路 200A へ帰還した信号である。

**【0113】**

論理比較信号 Sc はたとえば、制御入力信号 Sin が第 1 電位（たとえばハイレベル）かつ帰還信号 Sf が第 1 電位の場合や、制御入力信号 Sin が第 2 電位（たとえばロー レベル）かつ帰還信号 Sf が第 2 電位の場合に、制御入力信号 Sin と帰還信号 Sf の論理比較結果が“一致”であることを示す第 2 電位となり、制御入力信号 Sin が第 1 電位かつ帰還信号 Sf が第 2 電位の場合や、制御入力信号 Sin が第 2 電位かつ帰還信号 Sf が第 1 電位の場合に、制御入力信号 Sin と帰還信号 Sf が“不一致”であることを示す第 1 電位となる信号である。40

**【0114】**

第 1 パルス生成回路 202 は、制御入力信号 Sin と論理比較信号 Sc の組み合わせが第 1 の組み合わせとなつた場合に、第 1 補正信号 Sa1 を出力する。第 1 の組み合わせとは論理比較回路 212 の論理比較結果が“不一致”であり、かつ制御入力信号 Sin が第50

1電位となる組み合わせである。すなわち、第1補正信号  $S_{a1}$  は入出力が“不一致”かつ制御入力信号  $S_{in}$  が第1電位の場合に、後述する制御出力信号  $S_{out}$  を第1電位に補正するための信号である。

#### 【0115】

第2パルス生成回路204は、制御入力信号  $S_{in}$  と論理比較信号  $S_c$  の組み合わせが第1の組み合わせとは異なる第2の組み合わせとなった場合に、第2補正信号  $S_{a2}$  を出力する。第2の組み合わせとは論理比較回路212の論理比較結果が“不一致”であり、かつ制御入力信号  $S_{in}$  が第2電位となる組み合わせである。すなわち、第2補正信号  $S_{a2}$  は入出力が“不一致”かつ制御入力信号  $S_{in}$  が第2電位の場合に、後述する制御出力信号  $S_{out}$  を第2電位に補正するための信号である。

10

#### 【0116】

第1パルス生成回路202および第2パルス生成回路204は、制御入力信号  $S_{in}$  における電位の遷移に基づく入出力の不一致によって、各補正信号を出力し後述する制御出力信号  $S_{out}$  を遷移させることはもちろん、何らかの異常により、制御入力信号  $S_{in}$  と制御出力信号  $S_{out}$  に不一致が生じた場合にも同様に補正信号を出力し、入出力の不一致を解消する。

#### 【0117】

第1補正信号  $S_{a1}$  および第2補正信号  $S_{a2}$  は入力信号伝達部206によって出力側回路200Bへ伝達され、出力側回路200Bにおいて入力信号復元回路208へと送信される。

20

#### 【0118】

入力信号復元回路208は、入力信号伝達部206によって伝達された第1補正信号  $S_{a1}$  および第2補正信号  $S_{a2}$  を受信し、両者の信号を基に制御入力信号  $S_{in}$  と等価な制御出力信号  $S_{out}$  を出力端子219へと出力する。

#### 【0119】

入力信号復元回路208は、たとえばDフリップフロップやRSフリップフロップを用いて構成することができる。

#### 【0120】

制御出力信号  $S_{out}$  はさらに、帰還信号伝達部210にも送信され、帰還信号伝達部210は出力側回路200Bから入力側回路200Aへ信号の伝達を行い、入力側回路200Aにおいて帰還信号  $S_f$  を出力する。帰還信号  $S_f$  は論理比較回路212へ送信され、制御入力信号  $S_{in}$  との論理比較が行われる。

30

#### 【0121】

論理比較回路212はたとえばエクスクルーシブOR回路を用いて構成することができる。これは、本明細書における他の実施例についても同様である。

#### 【0122】

帰還信号伝達部210は、信号伝達に伴う電力消費を低減させるため、出力側回路200Bにおいて制御出力信号  $S_{out}$  をパルス幅の小さい信号へと変換し、出力側回路200Bから入力側回路200Aへ信号の伝達を行った後、入力側回路200Aにおいて制御出力信号  $S_{out}$  と等価な帰還信号  $S_f$  への復元を行うことが望ましい。これは、本明細書の他の実施例についても同様である。

40

#### 【0123】

以上説明した、一連の信号経路によって制御出力信号  $S_{out}$  は常に制御入力信号  $S_{in}$  と一致した状態に保たれる。すなわち、第1パルス生成回路202および第2パルス生成回路204は制御入力信号  $S_{in}$  における電位の遷移を制御出力信号  $S_{out}$  へと反映させる機能と、回路内の異常による入出力の不一致を解消する機能の2つを兼ね備えている。

#### 【0124】

(第2の実施の形態)

図2は第2の実施の形態にかかる信号伝達回路装置である。図2は図1の一部を具体的

50

な回路で示したものである。

**【0125】**

信号伝達回路装置220は、入力端子221、第1パルス生成回路222、第2パルス生成回路224、第1トランス226、第2トランス228、RSフリップフロップ230、出力端子249、帰還パルス生成回路232、第3トランス234、波形整形回路236、論理比較回路238を備える。

**【0126】**

入力側回路220Aから出力側回路220Bへ信号を伝達する入力信号伝達部220Cは第1トランス226および第2トランス228により構成され、出力側回路220Bから入力側回路220Aへ信号を伝達する帰還信号伝達部220Dは、帰還パルス生成回路232、第3トランス234、および波形整形回路236により構成される。

10

**【0127】**

入力端子221に入力された制御入力信号Sinは、第1パルス生成回路222および第2パルス生成回路224へ送信される。

**【0128】**

第1パルス生成回路222は制御入力信号Sinと後述する論理比較信号Scが第1の組み合わせ（たとえば両方とも第1電位）となった場合に第1補正信号Sa1を出力する。すなわち、第1補正信号Sa1は、論理比較回路238における制御入力信号Sinと帰還信号Sfの論理比較結果が“不一致”であり、かつ制御入力信号Sinが第1電位の場合に制御出力信号Soutを第1電位に補正するための信号である。

20

**【0129】**

第2パルス生成回路224は制御入力信号Sinと後述する論理比較信号Scが第1の組み合わせとは異なる第2の組み合わせ（たとえば制御入力信号Sinが第2電位、論理比較信号Scが第1電位）となった場合に第2補正信号Sa2を出力する。すなわち、第2補正信号Sa2は、論理比較回路238における制御入力信号Sinと帰還信号Sfの論理比較結果が“不一致”であり、かつ制御入力信号Sinが第2電位の場合に制御出力信号Soutを第2電位に補正するための信号である。

**【0130】**

第1補正信号Sa1および第2補正信号Sa2のパルス幅は、信号伝達時の電力消費を低減するために、制御入力信号Sinのパルス幅と比較して小さく設定される。これは、本明細書における他の実施例についても同様である。

30

**【0131】**

第1パルス生成回路222および第2パルス生成回路224は制御入力信号Sinと論理比較信号Scが所定の組み合わせ（第1の組み合わせまたは第2の組み合わせ）となった時に単パルス（たとえばパルス幅25nsに設定する）を発生させる構成としてもよいし、制御入力信号Sinと論理比較信号Scが所定の組み合わせ（第1の組み合わせまたは第2の組み合わせ）となった期間に連続パルス信号を発生させる構成としてもよい（たとえばパルス幅25ns、周期200nsに設定する）。これは本明細書中の他の実施例についても同様である。

**【0132】**

単パルスを発生させる場合、第1パルス生成回路222および第2パルス生成回路224は、たとえば、論理積回路と立ち上がりエッジ検出回路を組み合わせる構成とすればよい。

**【0133】**

連続パルス信号を発生させる場合、第1パルス生成回路222および第2パルス生成回路224は、たとえば、論理積回路、リングオシレータ、および立ち上がりエッジ検出回路を組み合わせる構成とすればよい。

**【0134】**

連続パルス信号を発生させる構成とした場合、第1パルス生成回路222および第2パルス生成回路224は制御入力信号Sinと制御出力信号Soutの“不一致”が解消さ

40

50

れるまでパルス信号を発生させることになり、信号伝達回路装置の信頼性が向上する。

【0135】

第1補正信号S<sub>a1</sub>は第1トランス226によって出力側回路220Bへと伝達され、RSフリップフロップ230のセット端子Sへと入力される。

【0136】

第2補正信号S<sub>a2</sub>は第2トランス228によって出力側回路220Bへと伝達され、RSフリップフロップ230のリセット端子Rへと入力される。

【0137】

RSフリップフロップ230は第1補正信号S<sub>a1</sub>および第2補正信号S<sub>a2</sub>を受信し、制御入力信号S<sub>in</sub>と等価な制御出力信号S<sub>out</sub>を出力する。 10

【0138】

制御出力信号S<sub>out</sub>は出力端子249から取り出されるとともに、帰還パルス生成回路232へと送信される。帰還パルス生成回路232は制御出力信号S<sub>out</sub>が第2電位となっている期間に、連続パルスを有する帰還パルスS<sub>f p</sub>を生成する。帰還パルスS<sub>f p</sub>はたとえばパルス幅25ns、周期600nsに設定される。もちろん、制御出力信号S<sub>out</sub>が第1電位となっている期間に帰還パルスS<sub>f p</sub>を生成する構成としてもよいが、波形整形回路236での波形整形、および論理比較回路238での論理比較の利便性に考慮しなければならない。

【0139】

帰還パルス生成回路232はたとえば矩形波信号（連続パルス信号）を生成する発振器と、この発振器から生成された発振パルス信号と制御出力信号S<sub>out</sub>との論理積をとるための論理積回路と、必要に応じてインバータ回路を用いて構成することができる。 20

【0140】

帰還パルスS<sub>f p</sub>は第3トランス234によって入力側回路220Aへと伝達され、波形整形回路236へと送信される。波形整形回路236は帰還パルスS<sub>f p</sub>を制御出力信号S<sub>out</sub>とほぼ等価な矩形波信号に整形する。

【0141】

波形整形回路236はたとえばスイッチングトランジスタ、電流源、キャパシタ、およびコンパレータ等を用いて構成することができる。回路の具体的な構成については後述する。 30

【0142】

波形整形回路236は整形された矩形波信号を帰還信号S<sub>f</sub>として出力し、出力された帰還信号S<sub>f</sub>は論理比較回路238へ送信され、制御入力信号S<sub>in</sub>と一致しているか否かの比較が行われる。両者の信号が比較され、制御入力信号S<sub>in</sub>と帰還信号S<sub>f</sub>の一致または不一致を示す論理比較信号S<sub>c</sub>が第1パルス生成回路222および第2パルス生成回路224へ送信される。論理比較回路238は例えばエクスクルーシブOR回路によって構成可能である。

【0143】

したがって、本構成の信号伝達回路装置220は、制御入力信号S<sub>in</sub>と制御出力信号S<sub>out</sub>が“不一致”となった場合に、その時の制御入力信号S<sub>in</sub>の電位に応じて、第1補正信号S<sub>a1</sub>または第2補正信号S<sub>a2</sub>が生成され、制御出力信号S<sub>out</sub>の補正が行われる。結果として制御入力信号S<sub>in</sub>と制御出力信号S<sub>out</sub>は常に同じ電位（第1電位または第2電位）に保たれる。 40

【0144】

図3は、図2に示した信号伝達回路装置220の変形例である。信号伝達回路装置800は、論理比較信号S<sub>c</sub>を該論理比較信号S<sub>c</sub>に同期した論理比較パルス信号S<sub>c p</sub>に変換する比較パルス生成回路820を設け、第1パルス生成回路222、第2パルス生成回路224に代えて第1論理積回路802、第2論理積回路804を設けた点が図2とは異なる。このように構成すれば、信号伝達回路装置の回路構成を簡略化することができる。

【0145】

10

20

30

40

50

比較パルス生成回路 820 は論理比較信号 S<sub>c</sub> が第 1 電位となった時に単パルス（たとえばパルス幅 25 ns に設定する）を発生させる構成としてもよいし、論理比較信号 S<sub>c</sub> が第 1 電位である期間に連続パルス信号を発生させる構成としてもよい（たとえばパルス幅 25 ns、周期 200 ns に設定する）。これは本明細書中の他の実施例についても同様である。

#### 【0146】

単パルスを発生させる場合、比較パルス生成回路 820 は、たとえば、立ち上がりエッジ検出回路により構成すればよい。

#### 【0147】

連続パルス信号を発生させる場合、比較パルス生成回路 820 は、たとえば、リングオシレータおよび立ち上がりエッジ検出回路を組み合わせる構成とすればよい。10

#### 【0148】

信号伝達回路装置 800 における、第 1 トランス 806、第 2 トランス 808、RS フリップフロップ 810、帰還パルス生成回路 812、第 3 トランス 814、波形整形回路 816、および論理比較回路 818 の構成は、図 2 に示す信号伝達回路装置 220 における、第 1 トランス 226、第 2 トランス 228、RS フリップフロップ 230、帰還パルス生成回路 232、第 3 トランス 234、波形整形回路 236、論理比較回路 238 と同様であるから詳しい説明は省略する。

#### 【0149】

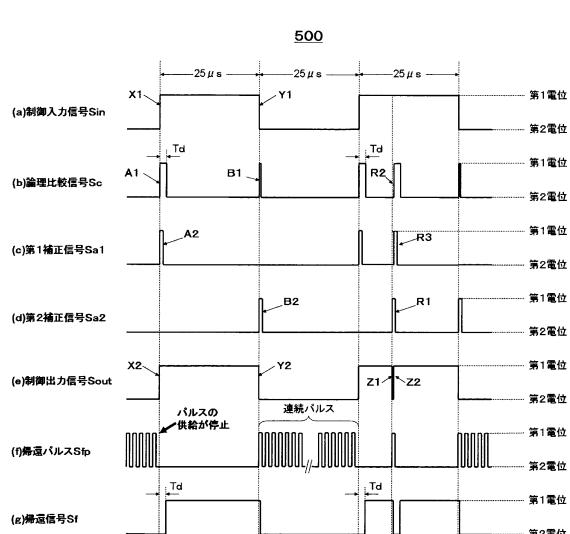

図 4 は、図 2 に示した信号伝達回路装置 220 の各部の信号を示すタイミングチャートである。タイミングチャート 500 は、信号伝達回路装置 220 における、前述した制御入力信号 S<sub>in</sub>、論理比較信号 S<sub>c</sub>、第 1 補正信号 S<sub>a1</sub>、第 2 補正信号 S<sub>a2</sub>、制御出力信号 S<sub>out</sub>、帰還パルス S<sub>f p</sub>、および帰還信号 S<sub>f</sub> の、時間経過に伴う電位（第 1 電位または第 2 電位）の遷移を示したものである。20

#### 【0150】

なお、この種の信号の送受信においては、信号形態や信号位置（位相）に何らかの変化や位相遅延が生じるが、本明細書においては、一部を除きこうしたことを無視しているので理解されたい。また、作図の都合上、各パルス幅の比率は必ずしも正確ではない。

#### 【0151】

図 4 (a) に示す制御入力信号 S<sub>in</sub> は、信号伝達回路装置 220 の入力端子 221 に入力される制御入力信号 S<sub>in</sub> の一例であり、パルス幅 25 μs、周期 50 μs の信号を示している。30

#### 【0152】

制御入力信号 S<sub>in</sub> が第 2 電位から第 1 電位に遷移すると（図 4 (a)、立ち上がり X 1）、遷移の瞬間ににおける帰還信号 S<sub>f</sub> は第 2 電位のままであるから、論理比較回路 238 での論理比較の結果は“不一致”となり、論理比較信号 S<sub>c</sub> が第 1 電位となる（図 4 (b)、立ち上がり A 1）。

#### 【0153】

論理比較信号 S<sub>c</sub> が第 1 電位となると、第 1 パルス生成回路 222 は制御入力信号 S<sub>in</sub> と論理比較信号 S<sub>c</sub> が第 1 の組み合わせ（たとえば両方とも第 1 電位）となったことに基づいて図 4 (c)、パルス A 2 を生成する。40

#### 【0154】

信号伝達時の消費電力を低減させるために、第 1 補正信号 S<sub>a1</sub> および第 2 補正信号 S<sub>a2</sub> におけるパルス幅は制御入力信号 S<sub>in</sub> と比較して十分に小さく設定される。

#### 【0155】

第 1 補正信号 S<sub>a1</sub> は第 1 トランス 226 を介して RS フリップフロップ 230 のセット端子 S に入力されるので、図 4 (c)、パルス A 2 と同じタイミングで制御出力信号 S<sub>out</sub> は制御入力信号 S<sub>in</sub> と同じ第 1 電位へと補正される（図 4 (e)、立ち上がり X 2）。

#### 【0156】

制御出力信号  $S_{out}$  が第 1 電位となると、それに伴い帰還パルス  $S_f p$  の供給が停止され（図 4（f））、帰還信号  $S_f$  が第 1 電位へと遷移する（図 4（g））。

#### 【0157】

図 4（g）に示した帰還信号  $S_f$  の立ち上がりは波形整形回路 236 での波形整形時間の影響を受け遅延時間  $T_d$  だけ遅れるが、入力パルス幅が遅延時間  $T_d$  と比較して十分に大きい場合には、制御出力信号  $S_{out}$  への影響は無い。入力パルス幅が短い場合については後述する。

#### 【0158】

制御入力信号  $S_{in}$  が第 1 電位から第 2 電位に遷移すると（図 4（a）、立ち下がり Y 1）、遷移の瞬間ににおける帰還信号  $S_f$  は第 1 電位のままであるから、論理比較回路 238 での論理比較の結果は“不一致”となり、論理比較信号  $S_c$  が第 1 電位となる（図 4（b）、立ち上がり B 1）。

#### 【0159】

論理比較信号  $S_c$  が第 1 電位となると、第 2 パルス生成回路 224 は制御入力信号  $S_{in}$  と論理比較信号  $S_c$  が第 2 の組み合わせ（たとえば制御入力信号  $S_{in}$  が第 2 電位、論理比較信号  $S_c$  が第 1 電位）となつたことに基づいて図 4（d）、パルス B 2 を生成する。

#### 【0160】

第 2 補正信号  $S_{a2}$  は第 2 トランス 228 を介して RS フリップフロップ 230 のリセット端子 R に入力されるので、図 4（d）、パルス B 2 と同じタイミングで制御出力信号  $S_{out}$  は制御入力信号  $S_{in}$  と同じ第 2 電位へと補正される（図 4（e）、立ち下がり Y 2）。

#### 【0161】

結果的に、回路が正常に動作している状態において、制御入力信号  $S_{in}$  と制御出力信号  $S_{out}$  は常に一致した状態が保たれる。

#### 【0162】

次に、第 2 補正信号  $S_{a2}$  に、図 4（d）、ノイズ R 1 が混入した場合について説明する。

#### 【0163】

第 2 補正信号  $S_{a2}$  にノイズ R 1 が混入すると、制御出力信号  $S_{out}$  は一時的に第 1 電位から第 2 電位へと遷移する（図 4（e）、立ち下がり Z 1）が、制御出力信号  $S_{out}$  における電位の遷移は帰還信号  $S_f$  における電位の遷移として、論理比較回路 238 へと送信され、論理比較回路 238 は制御入力信号  $S_{in}$  と帰還信号  $S_f$  が“不一致”となつたことに基づいて図 4（b）、立ち上がり R 2 に示すように第 1 電位となる。

#### 【0164】

すると、いま制御入力信号  $S_{in}$  は第 1 電位であるから、第 1 パルス生成回路 222 は図 4（c）、パルス R 3 を送信し、RS フリップフロップ 230 はパルス R 3 に基づき制御出力信号  $S_{out}$  を第 1 電位に補正する（図 4（e）、立ち上がり Z 2）。

#### 【0165】

結果的に、回路内にノイズが混入した場合、論理比較回路 238 において、制御入力信号  $S_{in}$  と制御出力信号  $S_{out}$  が“不一致”となつたことが即座に検知され、第 1 補正信号  $S_{a1}$  または第 2 補正信号  $S_{a2}$  が送信されることにより、制御出力信号  $S_{out}$  は入出力が“不一致”となつた直後に制御入力信号  $S_{in}$  と同じ電位（第 1 電位または第 2 電位）へと補正される。

#### 【0166】

異常状態としては、前述したノイズ混入の他に、たとえば第 1 トランスまたは第 2 トランスにおいて、パルスが伝達されない場合等が考えられるが、その場合においても同様に出力信号補正機能が働き、制御出力信号  $S_{out}$  を制御入力信号  $S_{in}$  と同じ電位（第 1 電位または第 2 電位）に補正する。各部の信号の流れは同様であるから詳しい説明については省略する。

**【0167】**

ところで、波形整形回路236における帰還パルスS<sub>f</sub>pの波形整形時間の影響を受け、帰還信号S<sub>f</sub>の立ち上がりは、厳密には遅延時間T<sub>d</sub>だけ制御出力信号S<sub>out</sub>よりも遅れる。

**【0168】**

遅延時間T<sub>d</sub>の長さはたとえば1μsから2μs程度であり、制御入力信号S<sub>in</sub>のパルス幅が遅延時間T<sub>d</sub>よりも長い場合においては制御出力信号S<sub>out</sub>に何ら影響を及ぼさないが、制御入力信号S<sub>in</sub>のパルス幅が遅延時間T<sub>d</sub>よりも短い場合、制御出力信号S<sub>out</sub>のパルス幅が遅延時間T<sub>d</sub>まで増大してしまう。以下に詳しく説明する。

**【0169】**

図5に信号伝達回路装置220に用いられる波形整形回路236の回路構成を示す。波形整形回路236は入力端子901に入力された帰還パルスS<sub>f</sub>pによりオン、オフするスイッチングトランジスタ904、スイッチングトランジスタ904と協働して帰還パルスS<sub>f</sub>pとは異なる整形帰還信号S<sub>fc</sub>を生成するための電流源902およびキャパシタ906と、整形帰還信号S<sub>fc</sub>が入力され、該整形帰還信号S<sub>fc</sub>とは異なる帰還信号S<sub>f</sub>を生成するコンパレータ910と、帰還信号S<sub>f</sub>を取り出す出力端子949を有する。

**【0170】**

制御出力信号S<sub>out</sub>と同期した帰還パルスS<sub>f</sub>pは制御出力信号S<sub>out</sub>が第2電位の期間に連続パルスを有する信号であって、たとえばパルス幅は25ns、周期は600nsに設定される。

**【0171】**

帰還パルスS<sub>f</sub>pはスイッチングトランジスタ904のゲート電極へ入力される。帰還パルスS<sub>f</sub>pが第1電位の間、スイッチングトランジスタ904はオンされ、電流源902から供給される電流をGNDへと導く。その間、キャパシタ906は放電される。

**【0172】**

帰還パルスS<sub>f</sub>pが第2電位の間は、スイッチングトランジスタ904はオフされ、電流源902から供給される電流により、キャパシタ906に電荷が溜まっていき、整形帰還信号S<sub>fc</sub>の電位が上昇する。

**【0173】**

整形帰還信号S<sub>fc</sub>はコンパレータ910に入力される。コンパレータ910は整形帰還信号S<sub>fc</sub>の電位が閾値電圧V<sub>ref</sub>よりも高い場合に帰還信号S<sub>f</sub>を第1電位とし、整形帰還パルスS<sub>fc</sub>の電位が閾値電圧V<sub>ref</sub>よりも低い場合に帰還信号S<sub>f</sub>を第2電位とする。

**【0174】**

すなわち、帰還パルスS<sub>f</sub>pとして定期的にパルス信号が送られてくる間は整形帰還信号S<sub>fc</sub>の電位が閾値電圧V<sub>ref</sub>に達することはなく、帰還信号S<sub>f</sub>は第2電位に保たれるが、パルス信号が供給されなくなると、キャパシタ906に電荷が蓄積されていき、閾値電圧V<sub>ref</sub>を超える電荷が蓄積されると帰還信号S<sub>f</sub>は第1電位となる。

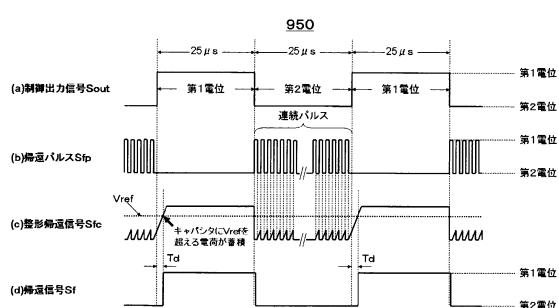

**【0175】**

図6は波形整形回路236の各部の信号、および制御出力信号S<sub>out</sub>を示すタイミングチャートである。タイミングチャート950は、信号伝達回路装置220における、前述した制御出力信号S<sub>out</sub>、帰還パルスS<sub>f</sub>p、整形帰還信号S<sub>fc</sub>、および帰還信号S<sub>f</sub>の、時間経過に伴う電位の遷移を示したものである。制御出力信号S<sub>out</sub>としては例えばパルス幅25μs、周期50μsの信号が帰還される。

**【0176】**

帰還パルスS<sub>f</sub>pは、帰還パルス生成回路232により生成される信号であり、制御出力信号S<sub>out</sub>が第2電位の期間に連続パルスを有する信号である。例えばパルス幅25ns、周期600nsに設定される。

**【0177】**

整形帰還信号S<sub>fc</sub>は帰還パルスS<sub>f</sub>pが第1電位の間は接地電位となり、帰還パルス

10

20

30

40

50

$S_{fp}$  が第 2 電位の間はキャパシタ 906 に蓄積される電荷により電位が上昇してゆく。

【0178】

帰還信号  $S_f$  は整形帰還信号  $S_{fc}$  の電位が  $V_{ref}$  未満の場合は第 2 電位となり、整形帰還信号  $S_{fc}$  の電位が  $V_{ref}$  を超えると第 1 電位となる。

【0179】

すなわち、制御出力信号  $S_{out}$  が第 1 電位となり、帰還パルス  $S_{fp}$  による連続パルスの供給が停止してから、キャパシタ 906 に  $V_{ref}$  を超える電荷が蓄積されるまでの時間により、帰還信号  $S_f$  の立ち上がりは制御出力信号  $S_{out}$  の立ち上がりから遅延時間  $T_d$  だけ遅れる。

【0180】

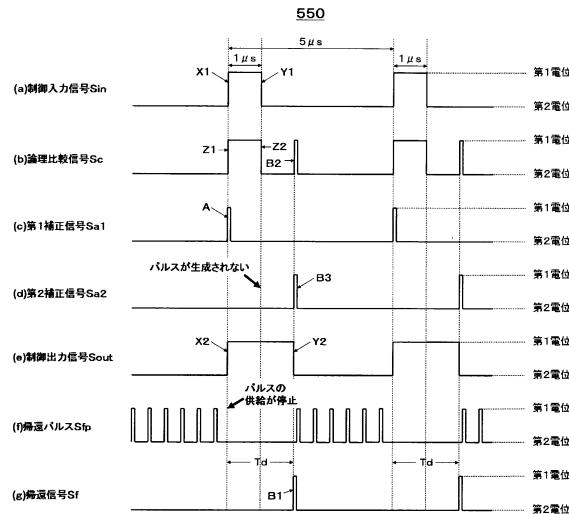

図 7 は、図 4 に示す信号伝達回路装置 220 に、前述した遅延時間  $T_d$  よりも短いパルス幅をもつ制御入力信号  $S_{in}$  を入力した場合の、各部の信号のタイミングチャートである。

【0181】

タイミングチャート 550 は、信号伝達回路装置 220 における、前述した制御入力信号  $S_{in}$ 、論理比較信号  $S_c$ 、第 1 補正信号  $S_{a1}$ 、第 2 補正信号  $S_{a2}$ 、制御出力信号  $S_{out}$ 、帰還パルス  $S_{fp}$ 、および帰還信号  $S_f$  の、時間経過に伴う電位（第 1 電位または第 2 電位）の遷移を示したものである。

【0182】

図 7 (a) に示す信号は入力端子 221 に入力される制御入力信号  $S_{in}$  の一例であり、パルス幅  $1 \mu s$ 、周期  $5 \mu s$  の信号を示している。制御入力信号  $S_{in}$  が第 2 電位から第 1 電位に遷移すると（図 7 (a)、立ち上がり X 1）、遷移の瞬間ににおける帰還信号  $S_f$  は第 2 電位のままであるから、論理比較信号  $S_c$  が制御入力信号  $S_{in}$  と帰還信号  $S_f$  の不一致を示す第 1 電位となる（図 7 (b)、立ち上がり Z 1）。

【0183】

論理比較信号  $S_c$  が第 1 電位となったことに伴い、第 1 パルス生成回路 222 は第 1 補正信号  $S_{a1}$  として図 7 (c)、パルス A を生成する。

【0184】

第 1 補正信号  $S_{a1}$  は RS フリップフロップ 230 のセット端子 S に入力され、制御出力信号  $S_{out}$  は第 1 電位に補正される（図 7 (e)、立ち上がり X 2）。

【0185】

制御出力信号  $S_{out}$  が第 1 電位となったことに伴い、帰還パルス  $S_{fp}$  は連続パルスの供給を停止する（図 7 (f)）。

【0186】

制御入力信号  $S_{in}$  が第 1 電位から第 2 電位に遷移すると（図 7 (a)、立ち下がり Y 1）、帰還信号  $S_f$  は遅延時間  $T_d$  の遅れにより第 2 電位のままであるから、論理比較信号  $S_c$  が制御入力信号  $S_{in}$  と帰還信号  $S_f$  の一致を示す第 2 電位となってしまい（図 7 (b)、立ち下がり Z 2）、制御入力信号  $S_{in}$  の立ち下がり時には第 2 パルス生成回路 224 はパルスを生成しない（図 7 (d)）。

【0187】

制御出力信号  $S_{out}$  の立ち上がりから遅延時間  $T_d$  の経過後、帰還信号  $S_f$  は第 1 電位となり（図 7 (g)、立ち上がり B 1）、この時制御入力信号  $S_{in}$  は既に第 2 電位となっているため、論理比較信号  $S_c$  は、帰還信号  $S_f$  と制御入力信号  $S_{in}$  の“不一致”を示す第 1 電位となる（図 7 (b) 立ち上がり B 2）。

【0188】

論理比較信号  $S_c$  が第 1 電位となったことに伴い、第 2 パルス生成回路は第 2 補正信号  $S_{a2}$  を生成する（図 7 (d)、パルス B 3）。

【0189】

第 2 補正信号  $S_{a2}$  は RS フリップフロップ 230 のリセット端子 R に入力され、制御出力信号  $S_{out}$  は第 2 電位に補正される（図 7 (e)、立ち下がり Y 2）。

10

20

30

40

50

**【0190】**

結果的に、信号伝達回路装置220に遅延時間T<sub>d</sub>よりも短いパルス幅をもった制御入力信号S<sub>in</sub>を入力すると、制御出力信号S<sub>out</sub>のパルス幅は遅延時間T<sub>d</sub>まで増大してしまうという不具合が生ずる。

**【0191】**

この不具合を克服するためには、帰還信号伝達部220Dに波形整形回路236を用いない構成とすることで遅延時間T<sub>d</sub>を無くす方法や、第1パルス生成回路222および第2パルス生成回路224と並列に制御入力信号S<sub>in</sub>のエッジ検出回路を設けることにより、制御入力信号S<sub>in</sub>を直ちに制御出力信号S<sub>out</sub>へ反映させる方法等が考えられる。帰還信号伝達部220Dに波形整形回路236を用いない構成については第3の実施の形態で、制御入力信号S<sub>in</sub>のエッジ検出回路を設ける構成については第4の実施の形態で示す。10

**【0192】**

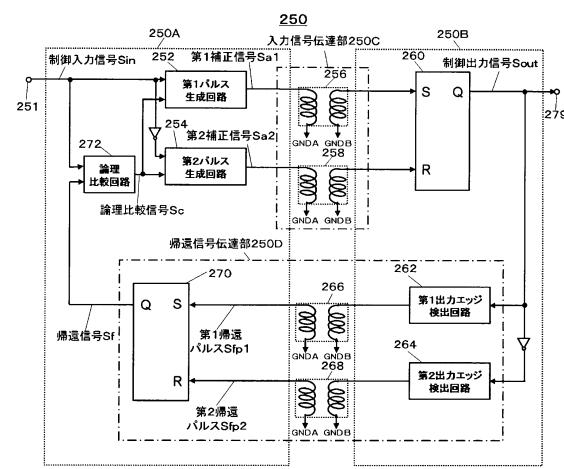

## (第3の実施の形態)

図8は第3の実施の形態にかかる信号伝達回路装置である。信号伝達回路装置250は、入力端子251、第1パルス生成回路252、第2パルス生成回路254、第1トランス256、第2トランス258、RSフリップフロップ260、出力端子279、第1出力エッジ検出回路262、第2出力エッジ検出回路264、第3トランス266、第4トランス268、第2RSフリップフロップ270、および論理比較回路272を備える。

**【0193】**

入力側回路250Aから出力側回路250Bへ信号を伝達する入力信号伝達部250Cは第1トランス256および第2トランス258により構成され、出力側回路250Bから入力側回路250Aへ信号を伝達する帰還信号伝達部250Dは、第1出力エッジ検出回路262、第2出力エッジ検出回路264、第3トランス266、第4トランス268、および第2RSフリップフロップ270により構成される。20

**【0194】**

信号伝達回路装置250は図2に示す信号伝達回路装置220における遅延時間T<sub>d</sub>による不具合を克服するために、帰還信号伝達部250Dを、第1出力エッジ検出回路262、第2出力エッジ検出回路264、第3トランス266、第4トランス268、第2RSフリップフロップ270により構成した点が図2と異なる。30

**【0195】**

信号伝達回路装置250における、第1パルス生成回路252、第2パルス生成回路254、第1トランス256、第2トランス258、RSフリップフロップ260、および論理比較回路272の構成については図2に示す信号伝達回路装置220における、第1パルス生成回路222、第2パルス生成回路224、第1トランス226、第2トランス228、RSフリップフロップ230、および論理比較回路238、と同様であるから詳しい説明は省略する。

**【0196】**

出力側回路250Bにおいて復元された制御出力信号S<sub>out</sub>は、該制御出力信号S<sub>out</sub>の立ち上がりエッジを検出する第1出力エッジ検出回路262および制御出力信号S<sub>out</sub>の立ち下がりエッジを検出する第2出力エッジ検出回路264により一時的に第1帰還パルスS<sub>f p 1</sub>および第2帰還パルスS<sub>f p 2</sub>に変換された後、第3トランス266および第4トランス268によって入力側回路250Aへ伝達される。40

**【0197】**

第1帰還パルスS<sub>f p 1</sub>および第2帰還パルスS<sub>f p 2</sub>は、入力側回路250Aにおいて第2RSフリップフロップ270により、制御出力信号S<sub>out</sub>と等価な帰還信号S<sub>f</sub>に復元される。

**【0198】**

信号伝達回路装置250の帰還信号伝達部250Dは波形整形回路を持たないので、帰還信号S<sub>f</sub>の立ち上がりは制御出力信号S<sub>out</sub>に対してほとんど遅延しない。50

**【 0 1 9 9 】**

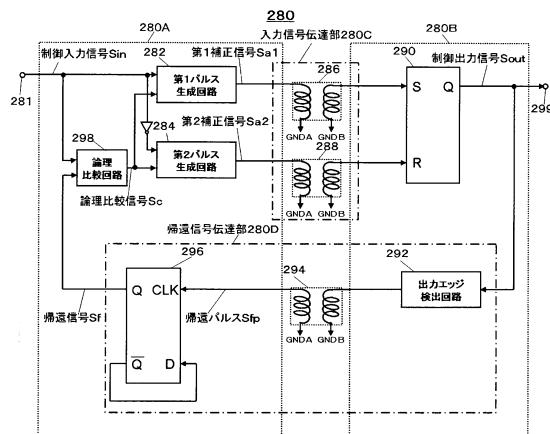

図9は、図8に示した信号伝達回路装置250の変形例である。信号伝達回路装置280は帰還信号伝達部280Dを、出力エッジ検出回路292、第3トランス294、Dフリップフロップ296により構成した点が図8と異なる。

**【 0 2 0 0 】**

信号伝達回路装置280における、第1パルス生成回路282、第2パルス生成回路284、第1トランス286、第2トランス288、RSフリップフロップ290、および論理比較回路298の構成については図8に示す信号伝達回路装置250における、第1パルス生成回路252、第2パルス生成回路254、第1トランス256、第2トランス258、RSフリップフロップ260、および論理比較回路272、と同様であるから詳しい説明は省略する。10

**【 0 2 0 1 】**

出力エッジ検出回路292は制御出力信号Soutの立ち上がりエッジおよび立ち下がりエッジを検出し、帰還パルスSfpを生成する。帰還パルスSfpは第3トランス294により入力側回路280Aへ伝達され、Dフリップフロップ296のクロック端子CLKへと入力される。

**【 0 2 0 2 】**

Dフリップフロップ296はクロック端子CLKに入力されたパルスの立ち上がり時のタイミングで出力端子Qの出力電位（第1電位または第2電位）が遷移するように構成されており、結果的に、制御出力信号Soutは出力エッジ検出回路292によって一時的に帰還パルスSfpへと変化した後、Dフリップフロップ296により制御出力信号Soutと等価な帰還信号Sfpへと復元される。20

**【 0 2 0 3 】**

このように構成すれば、帰還信号伝達部280Dにおけるトランスの数を一つにすることができ、信号伝達回路装置の小型化を図ることができる。

**【 0 2 0 4 】**

ただし、信号伝達回路装置280においては制御出力信号Soutの立ち上がりエッジを示すパルスと制御出力信号Soutの立ち下がりエッジを示すパルスが一つのクロック端子CLKに入力されることとなるため、ノイズの発生に弱く、図8と比較して信号伝達回路装置280の耐ノイズ特性は低下する。30

**【 0 2 0 5 】**

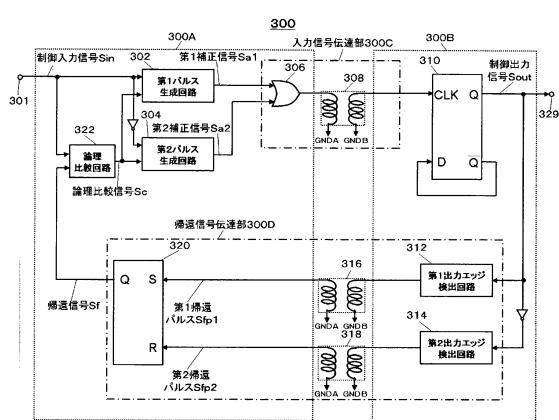

図10は、図8に示した信号伝達回路装置250の別の変形例である。信号伝達回路装置300は、第1補正信号Sa1と第2補正信号Sa2を論理和処理する論理和回路306を備えることにより、入力信号伝達部300Cにおけるトランスの数をひとつにし、出力側回路300BにおいてRSフリップフロップ260の代わりにDフリップフロップ310を用いた構成が図8と異なる。

**【 0 2 0 6 】**

信号伝達回路装置300における、第1パルス生成回路302、第2パルス生成回路304、第1出力エッジ検出回路312、第2出力エッジ検出回路314、第2トランス316、第3トランス318、RSフリップフロップ320、および論理比較回路322の構成については、図8に示す信号伝達回路装置250における、第1パルス生成回路252、第2パルス生成回路254、第1出力エッジ検出回路262、第2出力エッジ検出回路264、第3トランス266、第4トランス268、第2RSフリップフロップ270、および論理比較回路272と同様であるから詳しい説明は省略する。40

**【 0 2 0 7 】**

このように構成すれば、入力信号伝達部300Cにおけるトランスの数を一つにすることができ、回路の小型化を図ることができる。

**【 0 2 0 8 】**

ただし、信号伝達回路装置300においては制御出力信号Soutを第1電位に補正する第1補正信号Sa1と制御出力信号Soutを第2電位に補正する第2補正信号Sa250

が一つのクロック端子 C L K に入力されることとなるため、各信号のパルス幅、位相遅れ等に配慮した設計が必要である。また、第 1 パルス生成回路 302 および第 2 パルス生成回路 304 は単パルスを発生する構成とする。

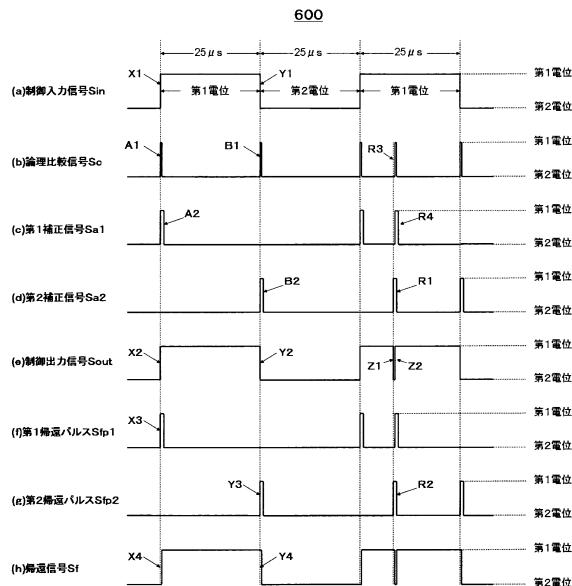

#### 【 0209 】

図 11 は、図 8 に示した信号伝達回路装置 250 の各部の信号を示すタイミングチャートである。タイミングチャート 600 は、信号伝達回路装置 250 における、前述した制御入力信号 S<sub>in</sub>、論理比較信号 S<sub>c</sub>、第 1 補正信号 S<sub>a1</sub>、第 2 補正信号 S<sub>a2</sub>、制御出力信号 S<sub>out</sub>、第 1 帰還パルス S<sub>f p1</sub>、第 2 帰還パルス S<sub>f p2</sub>、および帰還信号 S<sub>f</sub> の、時間経過に伴う電位（第 1 電位または第 2 電位）の遷移を示したものである。また、作図の都合上、各パルス幅の比率は必ずしも正確ではない。10

#### 【 0210 】

図 11 (a) に示す信号は、信号伝達回路装置 250 の入力端子 251 に入力される制御入力信号 S<sub>in</sub> の一例であり、パルス幅 25 μs、周期 50 μs の信号を示している。

#### 【 0211 】

制御入力信号 S<sub>in</sub> が第 2 電位から第 1 電位に遷移すると（図 11 (a)、立ち上がり X 1）、遷移の瞬間ににおける帰還信号 S<sub>f</sub> は第 2 電位のままであるから、論理比較回路 272 での論理比較の結果は“不一致”となり、論理比較信号 S<sub>c</sub> が第 1 電位となる。（図 11 (b)、立ち上がり A 1）。20

#### 【 0212 】

論理比較信号 S<sub>c</sub> が第 1 電位となると、第 1 パルス生成回路 252 は制御入力信号 S<sub>in</sub> と論理比較信号 S<sub>c</sub> が第 1 の組み合わせ（たとえば両方とも第 1 電位）となったことに基づいて図 11 (c)、パルス A 2 を生成する。20

#### 【 0213 】

ここで、信号伝達時の消費電力を低減させるために、第 1 補正信号 S<sub>a1</sub> および第 2 補正信号 S<sub>a2</sub> におけるパルス幅は制御入力信号 S<sub>in</sub> と比較して十分に小さく設定される。20

#### 【 0214 】

第 1 補正信号 S<sub>a1</sub> は第 1 トランス 256 を介して RS フリップフロップ 260 のセット端子 S に入力されるので、図 11 (c)、パルス A 2 と同じタイミングで制御出力信号 S<sub>out</sub> は制御入力信号 S<sub>in</sub> と同じ第 1 電位へと補正される（図 11 (e)、立ち上がり X 2）。30

#### 【 0215 】

制御出力信号 S<sub>out</sub> が第 2 電位から第 1 電位へ遷移すると、それに伴い第 1 出力エッジ検出回路 262 が第 1 帰還パルス S<sub>f p1</sub> として図 11 (f)、パルス X 3 を生成する。30

#### 【 0216 】

第 1 帰還パルス S<sub>f p1</sub> および第 2 帰還パルス S<sub>f p2</sub> のパルス幅はたとえば 25 ns に設定され、制御出力信号 S<sub>out</sub> のパルス幅と比較して十分に小さい。

#### 【 0217 】

第 1 帰還パルス S<sub>f p1</sub> は第 3 トランス 266 により入力側回路 250A へ伝達され、第 2 RS フリップフロップ 270 のセット端子 S へと入力されるため、帰還信号 S<sub>f</sub> が第 1 電位へと遷移する（図 11 (h)、立ち上がり X 4）。40

#### 【 0218 】

信号伝達回路装置 250 の帰還信号伝達部 250D においては、波形整形回路による遅延が発生しないため、帰還信号 S<sub>f</sub> の立ち上がりは制御出力信号 S<sub>out</sub> の立ち上がりとほぼ同時である。

#### 【 0219 】

制御入力信号 S<sub>in</sub> が第 1 電位から第 2 電位に遷移すると（図 11 (a)、立ち下がり Y 1）、遷移の瞬間ににおける帰還信号 S<sub>f</sub> は第 1 電位のままであるから、論理比較回路 272 での論理比較の結果は“不一致”となり、論理比較信号 S<sub>c</sub> が第 1 電位となる（図 150 1

1 ( b )、立ち上がり B 1 )。

**【 0 2 2 0 】**

論理比較信号 S c が第 1 電位となると、第 2 パルス生成回路 254 は制御入力信号 S in と論理比較信号 S c が第 2 の組み合わせ（たとえば制御入力信号 S in が第 2 電位、論理比較信号 S c が第 1 電位）となつたことに基づいて図 11 ( d )、パルス B 2 を生成する。

**【 0 2 2 1 】**

第 2 補正信号 S a 2 は第 2 トランス 258 を介して RS フリップフロップ 260 のリセット端子 R に入力されるので、図 11 ( d )、パルス B 2 と同じタイミングで制御出力信号 S out は制御入力信号 S in と同じ第 2 電位へと補正される（図 11 ( e )、立ち下がり Y 2 ）。

10

**【 0 2 2 2 】**

制御出力信号 S out が第 1 電位から第 2 電位へ遷移すると、それに伴い第 2 出力エッジ検出回路 264 が第 2 帰還パルス S fp 2 として図 11 ( g )、パルス Y 3 を生成する。

**【 0 2 2 3 】**

第 2 帰還パルス S fp 2 は第 4 トランス 268 により入力側回路 250A へ伝達され、第 2 RS フリップフロップ 270 のリセット端子 R へと入力されるため、帰還信号 S f が第 2 電位へと遷移する（図 11 ( h )、立ち下がり Y 4 ）。

**【 0 2 2 4 】**

20

結果的に、回路が正常に動作している状態において、制御入力信号 S in と制御出力信号 S out の電位（第 1 電位または第 2 電位）は常に一致した状態が保たれる。

**【 0 2 2 5 】**

また、帰還信号 S f は制御出力信号 S out に対してほとんど遅延しないので、図 8 に示す信号伝達回路装置 250 は、図 2 に示す信号伝達回路装置 220 と比較して短いパルス幅をもった制御入力信号 S in に対しても正確な制御出力信号 S out を出力することが可能である。

**【 0 2 2 6 】**

次に、第 2 補正信号 S a 2 に図 11 ( d )、ノイズ R 1 が混入した場合について説明する。

30

**【 0 2 2 7 】**

第 2 補正信号 S a 2 にノイズ R 1 が混入すると、制御出力信号 S out は一時的に第 1 電位から第 2 電位へと遷移するが（図 11 ( e )、立ち下がり Z 1 ）、制御出力信号 S out における電位の遷移は第 2 帰還パルス S fp 2 （図 11 ( g )、パルス R 2 ）により帰還信号 S f に反映され、論理比較回路 272 は制御入力信号 S in と帰還信号 S f が“不一致”となつたことに基づいて第 1 電位となる（図 11 ( b )、立ち上がり R 3 ）。

**【 0 2 2 8 】**

すると、いま制御入力信号 S in は第 1 電位であるから、第 1 パルス生成回路 252 は第 1 補正信号 S a 1 として図 11 ( c )、パルス R 4 で示すパルスを送信し、RS フリップフロップ 260 はパルス R 4 に基づき制御出力信号 S out を第 1 電位に補正する（図 11 ( e )、立ち上がり Z 2 ）。

40

**【 0 2 2 9 】**

結果的に、回路内にノイズが混入した場合、論理比較回路 272 において、制御入力信号 S in と制御出力信号 S out が“不一致”となつたことが即座に検知され、第 1 補正信号 S a 1 または第 2 補正信号 S a 2 が送信されることにより、制御出力信号 S out は入出力が“不一致”となつた直後に制御入力信号 S in と同じ電位（第 1 電位または第 2 電位）へと補正される。

**【 0 2 3 0 】**

異常状態としては、前述したノイズ混入の他に、たとえば第 1 トランス 256 または第 2 トランス 258 において、パルスが伝達されない場合等が考えられるが、その場合にお

50

いても同様に出力信号補正機能が働き、制御出力信号 Sout を制御入力信号 Sin と同じ電位（第 1 電位または第 2 電位）に補正する。各部の信号の流れは同様であるから詳しい説明については省略する。

#### 【0231】

ただし、信号伝達回路装置 250においては、帰還信号伝達部 250D を第 1 出力エッジ検出回路 262、第 2 出力エッジ検出回路 264、第 3 トランス 266、第 4 トランス 268、および第 2 RS フリップフロップ 270 により構成したため、たとえば第 1 帰還パルス Sfp1 にノイズが混入した場合に、入力側回路 250A に正常な帰還信号 Sf が帰還されないという不具合が生じ得る。こうした不具合を克服した信号伝達回路装置については後述する第 4 の実施の形態で示す。

10

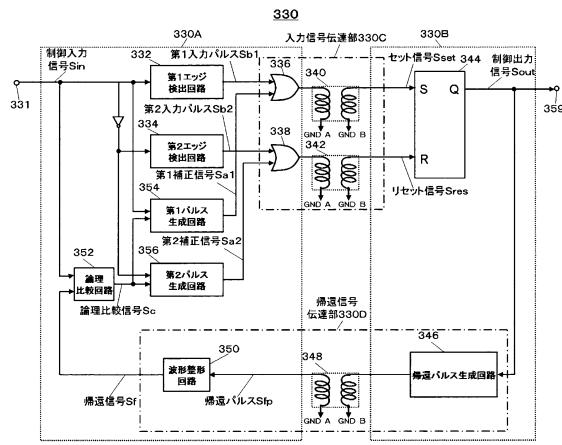

#### 【0232】

##### （第 4 の実施の形態）

図 12 は第 4 の実施の形態にかかる信号伝達回路装置である。信号伝達回路装置 330 は、入力端子 331、第 1 エッジ検出回路 332、第 2 エッジ検出回路 334、第 1 論理和回路 336、第 2 論理和回路 338、第 1 トランス 340、第 2 トランス 342、RS フリップフロップ 344、出力端子 359、帰還パルス生成回路 346、第 3 トランス 348、波形整形回路 350、論理比較回路 352、第 1 パルス生成回路 354、および第 2 パルス生成回路 356 を備える。

#### 【0233】

入力側回路 330A から出力側回路 330B へ信号を伝達する入力信号伝達部 330C は第 1 論理和回路 336、第 2 論理和回路 338、第 1 トランス 340、および第 2 トランス 342 により構成され、出力側回路 330B から入力側回路 330A へ信号を伝達する帰還信号伝達部 330D は、帰還パルス生成回路 346、第 3 トランス 348、および波形整形回路 350 により構成される。

20

#### 【0234】

信号伝達回路装置 330 は、制御入力信号 Sin の立ち上がりエッジを検出し第 1 入力パルス Sb1 を出力する第 1 エッジ検出回路 332、制御入力信号 Sin の立ち下がりエッジを検出し第 2 入力パルス Sb2 を出力する第 2 エッジ検出回路 334、第 1 入力パルス Sb1 と第 1 補正信号 Sa1 を論理和処理する第 1 論理和回路 336、第 2 入力パルス Sb2 と第 2 補正信号 Sa2 を論理和処理する第 2 論理和回路 338 を備える構成が図 2 とは異なる。

30

#### 【0235】

入力端子 331 に入力された制御入力信号 Sin は第 1 エッジ検出回路 332 および第 2 エッジ検出回路 334 により、制御入力信号 Sin の立ち上がりエッジを示す第 1 入力パルス Sb1 及び制御入力信号 Sin の立ち下がりエッジを示す第 2 入力パルス Sb2 に変換される。第 1 入力パルス Sb1 及び第 2 入力パルス Sb2 のパルス幅は第 1 トランス 340 および第 2 トランス 342 での消費電力を低減させるために制御入力信号 Sin のパルス幅よりも小さく設定される。

#### 【0236】

第 1 入力パルス Sb1 は後述する第 1 補正信号 Sa1 とともに第 1 論理和回路 336 で論理和処理され第 1 入力パルス Sb1 と第 1 補正信号 Sa1 の論理和であるセット信号 Sset へと変換される。セット信号 Sset は第 1 トランス 340 によって出力側回路 330B へと伝達され RS フリップフロップ 344 のセット端子 S へ入力される。

40

#### 【0237】

第 2 入力パルス Sb2 は後述する第 2 補正信号 Sa2 とともに第 2 論理和回路 338 で論理和処理され第 2 入力パルス Sb2 と第 2 補正信号 Sa2 の論理和であるリセット信号 Sres へと変換される。リセット信号 Sres は第 2 トランス 342 によって出力側回路 330B へと伝達され RS フリップフロップ 344 のリセット端子 R へ入力される。

#### 【0238】

RS フリップフロップ 344 はセット信号 Sset およびリセット信号 Sres に基づ

50

いて、制御入力信号  $S_{in}$  と等価な制御出力信号  $S_{out}$  を出力する。

**【0239】**

RSフリップフロップ344から出力された制御出力信号  $S_{out}$  は出力端子359から取り出されるとともに、帰還パルス生成回路346へと送信される、帰還パルス生成回路346は制御出力信号  $S_{out}$  が第2電位となっている期間に連続パルスを有する帰還パルス  $S_{fp}$  を生成する。

**【0240】**

帰還パルス  $S_{fp}$  はたとえばパルス幅25ns、周期600nsに設定される。もちろん、制御出力信号  $S_{out}$  が第1電位となっている期間に帰還パルス  $S_{fp}$  を生成する構成としてもよいが、波形整形回路350での波形整形、および論理比較回路352での論理比較の利便性に考慮しなければならない。10

**【0241】**

帰還パルス生成回路346はたとえば矩形波信号（連続パルス信号）を生成する発振器と、この発振器から生成された発振パルス信号と制御出力信号  $S_{out}$  との論理積をとるための論理積回路と、必要に応じてインバータ回路を用いて構成することができる。

**【0242】**

帰還パルス  $S_{fp}$  は第3トランス348によって入力側回路330Aへと伝達され、波形整形回路350へと送信される。波形整形回路350は帰還パルス  $S_{fp}$  を制御出力信号  $S_{out}$  とほぼ等価な矩形波信号に整形する。

**【0243】**

波形整形回路350はたとえばスイッチングトランジスタ、電流源、キャパシタ、およびコンパレータ等を用いて構成することができる。回路構成は第2の実施の形態と同様である。回路の具体的な構成については図5に示した。20

**【0244】**

波形整形回路350は整形された矩形波信号を帰還信号  $S_f$  として出力し、出力された帰還信号  $S_f$  は論理比較回路352へ送信され、制御入力信号  $S_{in}$  と一致しているか否かの比較が行われる。両者の信号が比較され、制御入力信号  $S_{in}$  と帰還信号  $S_f$  の一致または不一致を示す論理比較信号  $S_c$  が第1パルス生成回路354および第2パルス生成回路356へ送信される。論理比較回路352は例えばエクスクルーシブOR回路によって構成可能である。30

**【0245】**

第1パルス生成回路354は制御入力信号  $S_{in}$  と論理比較信号  $S_c$  が第1の組み合わせ（たとえば両方とも第1電位）となった場合に第1補正信号  $S_{a1}$  を出力する。すなわち、第1補正信号  $S_{a1}$  は、論理比較回路352における制御入力信号  $S_{in}$  と帰還信号  $S_f$  の論理比較結果が“不一致”であり、かつ制御入力信号  $S_{in}$  が第1電位の場合に制御出力信号  $S_{out}$  を第1電位に補正するための信号である。

**【0246】**

第1補正信号  $S_{a1}$  は第1入力パルス  $S_{b1}$  と論理和処理され出力側回路330BにおけるRSフリップフロップ344のセット端子Sへと入力される。第1補正信号  $S_{a1}$  と第1入力パルス  $S_{b1}$  は相互補完の関係にある。40

**【0247】**

第2パルス生成回路356は制御入力信号  $S_{in}$  と論理比較信号  $S_c$  が第1の組み合わせとは異なる第2の組み合わせ（たとえば制御入力信号  $S_{in}$  が第2電位、論理比較信号  $S_c$  が第1電位）となった場合に第2補正信号  $S_{a2}$  を出力する。すなわち、第2補正信号  $S_{a2}$  は、論理比較回路352における制御入力信号  $S_{in}$  と帰還信号  $S_f$  の論理比較結果が“不一致”であり、かつ制御入力信号  $S_{in}$  が第2電位の場合に制御出力信号  $S_{out}$  を第2電位に補正するための信号である。

**【0248】**

第2補正信号  $S_{a2}$  は第2入力パルス  $S_{b2}$  と論理和処理され出力側回路330BにおけるRSフリップフロップ344のリセット端子Rへと入力される。第2補正信号  $S_{a2}$  50

と第2入力パルスSb2は相互補完の関係にある。

**【0249】**

すなわち、信号伝達回路装置330において、制御入力信号Sinにおける電位の遷移は第1エッジ検出回路332または第2エッジ検出回路334によって第1入力パルスSb1または第2入力パルスSb2へと変換され、RSフリップフロップ344のセット端子Sまたはリセット端子Rに入力されることにより直ちに制御出力信号Soutへと反映される。

**【0250】**

また、回路内における何らかの異常により制御入力信号Sinが制御出力信号Soutへ正確に伝達されない場合であっても、論理比較回路352が制御入力信号Sinと帰還信号Sfの“不一致”を検出し、それに伴い第1パルス生成回路354または第2パルス生成回路356が第1補正信号Sa1または第2補正信号Sa2を出力するので、制御出力信号Soutは常に制御入力信号Sinと同じ電位（第1電位または第2電位）に保たれる。

10

**【0251】**

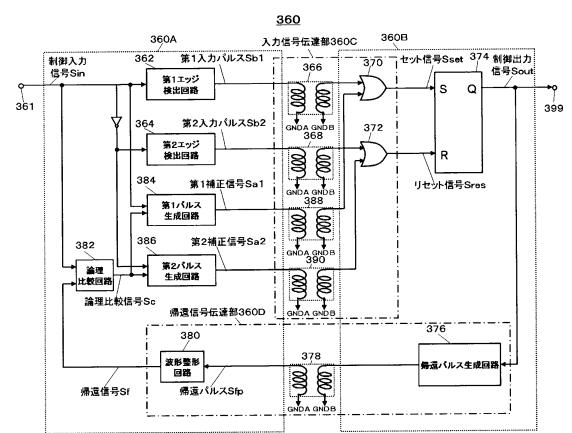

信号伝達回路装置330では、第1論理和回路336および第2論理和回路338が入力側回路330Aに設けられているが、出力側回路330Bに設ける構成としてもよい。上記変形例を図13に示す。

**【0252】**

信号伝達回路装置360は第1入力パルスSb1を出力側回路360Bへ伝達する第1トランス366、第2入力パルスSb2を出力側回路360Bへ伝達する第2トランス368、第1補正信号Sa1を出力側回路360Bへ伝達する第3トランス388、第2補正信号Sa2を出力側回路360Bへ伝達する第4トランス390を備え、出力側回路360Bに、第1入力パルスSb1と第1補正信号Sa1を論理和処理する第1論理和回路370、第2入力パルスSb2と第2補正信号Sa2を論理和処理する第2論理和回路372を設けた構成が図12と異なる。

20

**【0253】**

信号伝達回路装置360における、第1エッジ検出回路362、第2エッジ検出回路364、RSフリップフロップ374、帰還パルス生成回路376、第5トランス378、波形整形回路380、論理比較回路382、第1パルス生成回路384、第2パルス生成回路386の構成については、図12に示す信号伝達回路装置330における、第1エッジ検出回路332、第2エッジ検出回路334、RSフリップフロップ344、帰還パルス生成回路346、第3トランス348、波形整形回路350、論理比較回路352、第1パルス生成回路354、第2パルス生成回路356と同様であるから詳しい説明は省略する。

30

**【0254】**

このように構成すれば、第1入力パルスSb1、第2入力パルスSb2、第1補正信号Sa1、第2補正信号Sa2はそれぞれ別のトランスによって出力側回路360Bへ伝達されるため、入力信号伝達部360Cにおけるトランスの寿命を延ばすことができる。

**【0255】**

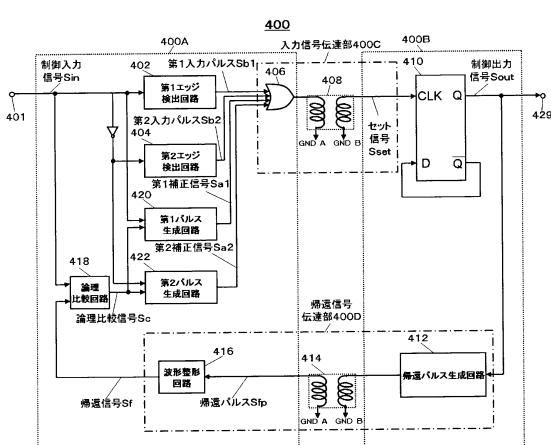

図14は、図12に示した信号伝達回路装置330の別の変形例である。信号伝達回路装置400は、第1論理和回路336、第2論理和回路338に代えて、第1入力パルスSb1、第2入力パルスSb2、第1補正信号Sa1、および第2補正信号Sa2を論理和処理する論理和回路406を備えることにより、入力信号伝達部400Cにおけるトランスの数をひとつにし、出力側回路400BにおいてRSフリップフロップ344の代わりにDフリップフロップ410を用いた構成が図12と異なる。

40

**【0256】**

信号伝達回路装置400における、第1エッジ検出回路402、第2エッジ検出回路404、帰還パルス生成回路412、第2トランス414、波形整形回路416、論理比較回路418、第1パルス生成回路420、第2パルス生成回路422の構成については、

50

図12に示す信号伝達回路装置330における、第1エッジ検出回路332、第2エッジ検出回路334、帰還パルス生成回路346、第3トランス348、波形整形回路350、論理比較回路352、第1パルス生成回路354、第2パルス生成回路356と同様であるから詳しい説明は省略する。

#### 【0257】

このように構成すれば、入力信号伝達部400Cにおけるトランスの数を一つにすることができ、信号伝達回路装置の小型化を図ることができる。

#### 【0258】

ただし、信号伝達回路装置400においては、第1入力パルスSb1、第2入力パルスSb2、第1補正信号Sa1、および第2補正信号Sa2が全て一つのクロック端子CLKに入力されることとなるため、各信号のパルス幅、位相遅れ等に配慮した設計が必要である。また、第1パルス生成回路420および第2パルス生成回路422は単パルスを発生する構成とする。

10

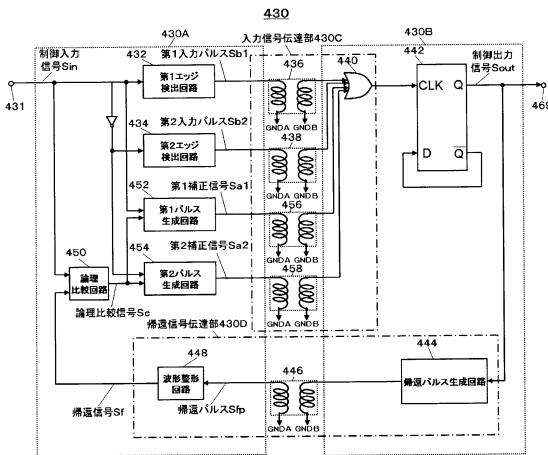

#### 【0259】

信号伝達回路装置400において、論理和回路406を出力側回路400Bに設ける構成としてもよい。上記変形例を図15に示す。信号伝達回路装置430は第1入力パルスSb1を出力側回路430Bへ伝達する第1トランス436、第2入力パルスSb2を出力側回路430Bへ伝達する第2トランス438、第1補正信号Sa1を出力側回路430Bへ伝達する第3トランス456、第2補正信号Sa2を出力側回路430Bへ伝達する第4トランス458を備え、出力側回路430Bに、第1入力パルスSb1、第2入力パルスSb2、第1補正信号Sa1、および第2補正信号Sa2を論理和処理する論理和回路440を設けた構成が図14と異なる。

20

#### 【0260】

信号伝達回路装置430における、第1エッジ検出回路432、第2エッジ検出回路434、Dフリップフロップ442、帰還パルス生成回路444、第5トランス446、波形整形回路448、論理比較回路450、第1パルス生成回路452、第2パルス生成回路454の構成については、図14に示す信号伝達回路装置400における、第1エッジ検出回路402、第2エッジ検出回路404、Dフリップフロップ410、帰還パルス生成回路412、第2トランス414、波形整形回路416、論理比較回路418、第1パルス生成回路420、第2パルス生成回路422と同様であるから詳しい説明は省略する。

30

#### 【0261】

このように構成すれば、第1入力パルスSb1、第2入力パルスSb2、第1補正信号Sa1、第2補正信号Sa2はそれぞれ別のトランスによって出力側回路430Bへ伝達されるため、入力信号伝達部430Cにおけるトランスの寿命を延ばすことができる。

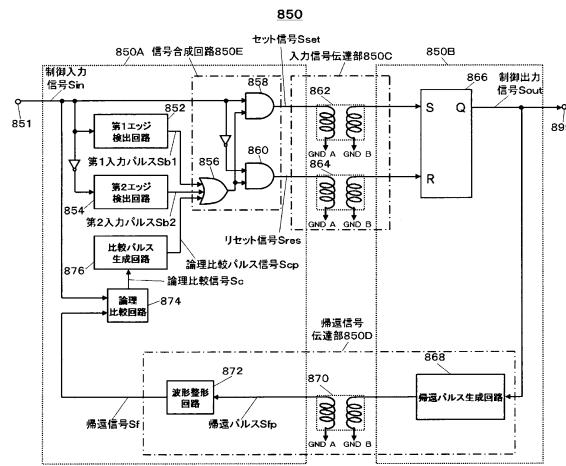

#### 【0262】

図16は、図12に示した信号伝達回路装置330のさらに別の変形例である。信号伝達回路装置850は、論理比較信号Scを該論理比較信号Scに同期した論理比較パルス信号Scpに変換する比較パルス生成回路876を設けたことにより、第1パルス生成回路354および第2パルス生成回路356を不要とした点が図12と異なる。このように構成すれば、信号伝達回路装置の構成を簡略化することができる。

40

#### 【0263】

比較パルス生成回路876の構成は図3に示した信号伝達回路装置800における比較パルス生成回路820と同様である。

#### 【0264】

信号伝達回路装置850における、第1エッジ検出回路852、第2エッジ検出回路854、第1トランス862、第2トランス864、RSフリップフロップ866、帰還パルス生成回路868、第3トランス870、波形整形回路872、および論理比較回路874の構成は、図12に示す信号伝達回路装置330における、第1エッジ検出回路332、第2エッジ検出回路334、第1トランス340、第2トランス342、RSフリッ

50

プロップ 344、帰還パルス生成回路 346、第3トランス 348、波形整形回路 350、論理比較回路 352 と同様であるから詳しい説明は省略する。

#### 【0265】

信号合成回路 850E は、制御入力信号 S<sub>in</sub>、第1入力パルス S<sub>b1</sub>、第2入力パルス S<sub>b2</sub>、および論理比較パルス信号 S<sub>c p</sub> を受信し、第1入力パルス S<sub>b1</sub>、第2入力パルス S<sub>b2</sub>、または論理比較パルス信号 S<sub>c p</sub> を受信したタイミングで、その時点での制御入力信号 S<sub>in</sub> の電位に基づいてセット信号 S<sub>set</sub> またはリセット信号 S<sub>res</sub> を出力する。図 16 に示すように、第1入力パルス S<sub>b1</sub>、第2入力パルス S<sub>b2</sub>、および論理比較パルス信号 S<sub>c p</sub> を受信する論理和回路 856 と、論理和回路 856 の出力と制御入力信号 S<sub>in</sub> を受信する第1論理積回路 858 と、論理和回路 856 の出力と制御入力信号 S<sub>in</sub> の反転信号を受信する第2論理積回路 860 により信号合成回路 850E を構成すれば、比較的簡便な構成により信号合成回路 850E を構成することが可能であるが、信号合成回路 850E の構成については図 16 に示した構成に限定されるものではなく、種々の変形実施が可能である。10

#### 【0266】

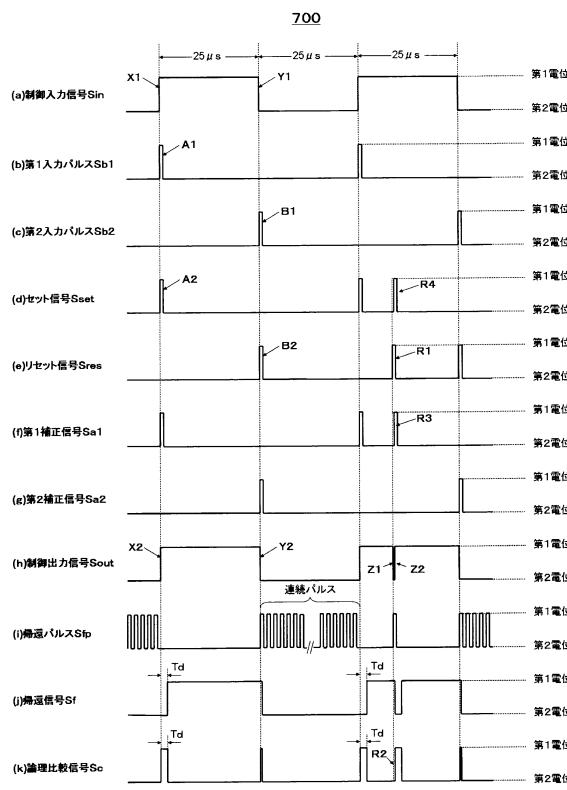

図 17 は、図 12 に示した信号伝達回路装置 330 の各部の信号を示すタイミングチャートである。タイミングチャート 700 は、信号伝達回路装置 330 における、前述した制御入力信号 S<sub>in</sub>、第1入力パルス S<sub>b1</sub>、第2入力パルス S<sub>b2</sub>、セット信号 S<sub>set</sub>、リセット信号 S<sub>res</sub>、第1補正信号 S<sub>a1</sub>、第2補正信号 S<sub>a2</sub>、制御出力信号 S<sub>out</sub>、帰還パルス S<sub>f p</sub>、帰還信号 S<sub>f</sub>、および論理比較信号 S<sub>c</sub> の、時間経過に伴う電位（第1電位または第2電位）の遷移を示したものである。なお、作図の都合上、各パルス幅の比率は必ずしも正確ではない。20

#### 【0267】

第1補正信号 S<sub>a1</sub>、第2補正信号 S<sub>a2</sub>、帰還パルス S<sub>f p</sub>、帰還信号 S<sub>f</sub>、および論理比較信号 S<sub>c</sub> の動作については第2の実施の形態と同様であるから詳しい説明については省略する。

#### 【0268】

ここで、信号伝達回路装置 330 における帰還信号伝達部 330D の構成は図 2 と同様であるから、帰還信号 S<sub>f</sub> の立ち上がりは制御出力信号 S<sub>out</sub> の立ち上がりから遅延時間 T<sub>d</sub> だけ遅れる。30

#### 【0269】

図 17(a) に示す制御入力信号 S<sub>in</sub> は、信号伝達回路装置 330 の入力端子 331 に入力される制御入力信号 S<sub>in</sub> の一例であり、パルス幅 25 μs、周期 50 μs の信号を示している。

#### 【0270】

制御入力信号 S<sub>in</sub> が第2電位から第1電位へ遷移すると（図 17(a)、立ち上がり X<sub>1</sub>）、第1エッジ検出回路 332 が制御入力信号 S<sub>in</sub> の立ち上がりエッジを検出し、第1入力パルス S<sub>b1</sub> として図 17(b)、パルス A<sub>1</sub> を生成する。ここで、信号伝達時の消費電力を低減させるために、第1入力パルス S<sub>b1</sub> および第2入力パルス S<sub>b2</sub> におけるパルス幅は制御入力信号 S<sub>in</sub> と比較して十分に小さく設定される。40

#### 【0271】

第1入力パルス S<sub>b1</sub> は第1論理和回路 336 に入力され、第1論理和回路 336 はセット信号 S<sub>set</sub> として図 17(d)、パルス A<sub>2</sub> を送信する。

#### 【0272】

セット信号 S<sub>set</sub> は第1トランス 340 を介して RS フリップフロップ 344 のセット端子 S に入力されるので、図 17(d)、パルス A<sub>2</sub> 同じタイミングで制御出力信号 S<sub>out</sub> は第1電位へと遷移する（図 17(h)、立ち上がり X<sub>2</sub>）。

#### 【0273】

制御入力信号 S<sub>in</sub> が第1電位から第2電位へ遷移すると（図 17(a)、立ち下がり Y<sub>1</sub>）、第2エッジ検出回路 334 が制御入力信号 S<sub>in</sub> の立ち下がりエッジを検出し、50

第2入力パルス S b 2として図17(c)、パルスB1を生成する。

**【0274】**

第2入力パルス S b 2は第2論理和回路338に入力され、第2論理和回路338はリセット信号 S res として図17(e)、パルスB2を送信する。

**【0275】**

リセット信号 S res は第2トランス342を介して RS フリップフロップ344 のリセット端子 R に入力されるので、図17(e)、パルスB2と同じタイミングで制御出力信号 S out は第2電位へと遷移する(図17(h)、立ち下がり Y 2)。

**【0276】**

したがって、入力側回路330Aから出力側回路330Bへの信号伝達が正常に行われている状態において、制御入力信号 S in は常に制御出力信号 S out と同じ電位(第1電位または第2電位)に保たれる。 10

**【0277】**

次に、リセット信号 S res に図17(e)、ノイズ R 1 が混入した場合について説明する。

**【0278】**

リセット信号 S res にノイズ R 1 が混入すると、制御出力信号 S out は一時的に第1電位から第2電位へと遷移する(図17(h)、立ち下がり Z 1)が、制御出力信号 S out における電位の遷移は帰還信号 S f における電位の遷移として、論理比較回路352へと送信され、論理比較回路352は制御入力信号 S in と帰還信号 S f が“不一致”となつたことに基づいて第1電位となる(図17(k)、立ち上がり R 2)。 20

**【0279】**

すると、いま制御入力信号 S in は第1電位であるから、第1パルス生成回路354は第1補正信号 S a 1 として図17(f)、パルス R 3 を生成し、第1論理和回路336は入力された第1補正信号 S a 1 に基づき、セット信号 S set として図14(d)、パルス R 4 を送信する。セット信号 S set は第1トランス340を介して RS フリップフロップ344 のセット端子 S に入力され、制御出力信号 S out を第1電位に補正する(図17(h)、立ち上がり Z 2)。

**【0280】**

結果的に、回路内にノイズが混入した場合、論理比較回路352において、制御入力信号 S in と制御出力信号 S out が“不一致”となつたことが即座に検知され、第1パルス生成回路または第2パルス生成回路により、第1補正信号 S a 1 または第2補正信号 S a 2 が送信される。したがって、制御出力信号 S out は入出力が“不一致”となつた直後に制御入力信号 S in と同じ電位(第1電位または第2電位)へと補正される。 30

**【0281】**

異常状態としては、前述したノイズ混入の他に、たとえば第1トランスまたは第2トランスにおいて、パルスが伝達されない場合等が考えられるが、その場合においても同様に出力信号補正機能が働き、制御出力信号 S out を制御入力信号 S in と同じ電位(第1電位または第2電位)に補正する。各部の信号の流れは同様であるから詳しい説明については省略する。 40

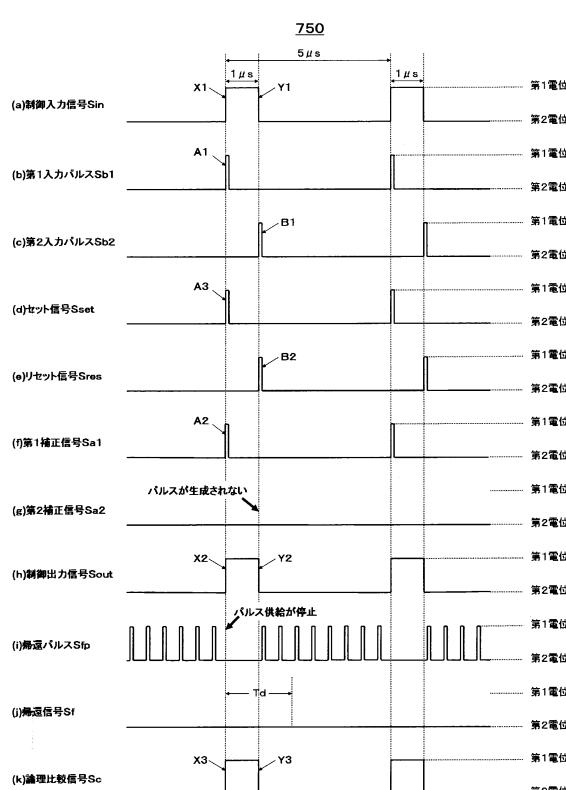

**【0282】**

次に、図12に示す信号伝達回路装置330に帰還信号 S f の遅延時間 T d よりも短いパルス幅をもつ制御入力信号 S in を入力した場合の各部の信号のタイミングチャートを図18に示す。タイミングチャート750は、信号伝達回路装置330における、前述した制御入力信号 S in 、第1入力パルス S b 1 、第2入力パルス S b 2 、セット信号 S set 、リセット信号 S res 、第1補正信号 S a 1 、第2補正信号 S a 2 、制御出力信号 S out 、帰還パルス S fp 、帰還信号 S f 、および論理比較信号 S c の、時間経過に伴う電位(第1電位または第2電位)の遷移を示したものである。

**【0283】**

図18(a)に示す信号は信号伝達回路装置330の入力端子331に入力される制御

50

入力信号  $S_{in}$  の一例であり、パルス幅  $1 \mu s$ 、周期  $5 \mu s$  の信号を示している。

#### 【0284】

制御入力信号  $S_{in}$  が第2電位から第1電位に遷移すると(図18(a)、立ち上がり  $X_1$ )、第1エッジ検出回路332が制御入力信号  $S_{in}$  の立ち上がりエッジを検出し、第1入力パルス  $S_{b1}$  として図18(b)、パルス  $A_1$  を生成する。

#### 【0285】

この時、制御入力信号  $S_{in}$  の遷移の瞬間ににおける帰還信号  $S_f$  は第2電位のままであるから、論理比較回路352での論理比較の結果は“不一致”となり、論理比較信号  $S_c$  は第1電位となる(図18(k)、立ち上がり  $X_3$ )。それに伴い第1パルス生成回路は図18(f)、パルス  $A_2$  を生成する。第1入力パルス  $S_{b1}$  におけるパルス  $A_1$  と、第1補正信号  $S_{a1}$  におけるパルス  $A_2$  は相互補完の関係にある。

10

#### 【0286】

第1論理和回路336は第1入力パルス  $S_{b1}$  と第1補正信号  $S_{a1}$  を論理和処理し、セット信号  $S_{set}$  として図18(d)、パルス  $A_3$  を送信する。セット信号  $S_{set}$  は第1トランス340を介してRSフリップフロップ344のセット端子  $S$  に入力されるので、図18(d)、パルス  $A_3$  と同じタイミングで制御出力信号  $S_{out}$  は第1電位へと遷移する(図18(h)、立ち上がり  $X_2$ )。

#### 【0287】

この時、制御出力信号  $S_{out}$  が第1電位となったことに伴い、帰還パルス生成回路346は連続パルスの供給を停止する(図18(i))が、帰還信号  $S_f$  は遅延時間  $T_d$  の遅れにより第2電位のままとなる(図18(j))。

20

#### 【0288】

制御入力信号  $S_{in}$  が第1電位から第2電位に遷移すると(図18(a)、立ち下がり  $Y_1$ )、第2エッジ検出回路334が制御入力信号  $S_{in}$  の立ち下がりエッジを検出し、第2入力パルス  $S_{b2}$  として図18(c)、パルス  $B_1$  を生成する。

#### 【0289】

第2入力パルス  $S_{b2}$  は第2論理和回路338に入力され、第2論理和回路338はリセット信号  $S_{res}$  として図18(e)、パルス  $B_2$  を送信する。リセット信号  $S_{res}$  は、第2トランス342を介してRSフリップフロップ344のリセット端子  $R$  に入力されるので、図18(e)、パルス  $B_2$  と同じタイミングで制御出力信号  $S_{out}$  は第2電位へと遷移する(図18(h)、立ち下がり  $Y_2$ )。

30

#### 【0290】

この時、制御出力信号  $S_{out}$  の立ち上がりから遅延時間  $T_d$  が経過する前に、制御出力信号  $S_{out}$  が第2電位となってしまうため、帰還信号  $S_f$  は第2電位のままとなり、論理比較信号  $S_c$  は、制御入力信号  $S_{in}$  の立ち下がりのタイミングで第2電位となる(図18(k)、立ち下がり  $Y_3$ )。

#### 【0291】

したがって、制御入力信号  $S_{in}$  の立ち下がりのタイミングで第2パルス生成回路356はパルスを生成しないが(図18(g))、制御出力信号  $S_{out}$  は第2入力パルス  $S_{b2}$  によって既に第2電位へと遷移しているため、制御出力信号  $S_{out}$  のパルス幅が増大することは無い。

40

#### 【0292】

結果的に、信号伝達回路装置330に遅延時間  $T_d$  よりも小さいパルス幅を有する制御入力信号  $S_{in}$  を入力しても制御出力信号  $S_{out}$  のパルス幅は増大せず、図2に示した信号伝達回路装置220と比較して、制御入力信号  $S_{in}$  の最小入力パルス幅を大幅に小さくすることができる。

#### 【0293】

以上、第4の実施の形態について説明した。信号伝達回路装置330は、第1パルス生成回路354および第2パルス生成回路356とともに第1エッジ検出回路332および第2エッジ検出回路334を備えているので、出力信号補正機能を有したまま、遅延時間

50

$T_d$  の影響を受けることなく制御入力信号  $S_{in}$  の最小入力パルス幅を大幅に小さくすることができる。

【0294】

さらに、帰還信号伝達部 330D を帰還パルス生成回路 346、第3トランジスタ 348、波形整形回路 350 により構成したので、帰還信号伝達部 250D を第1出力エッジ検出回路 262、第2出力エッジ検出回路 264、第3トランジスタ 266、第4トランジスタ 268、および第2RSフリップフロップ 270 により構成した図8と比較して帰還信号伝達部 330D におけるトランジスタの数を一つにすることができ、信号伝達回路装置の小型化を図るとともに帰還信号伝達部の耐ノイズ特性が向上する。

【0295】

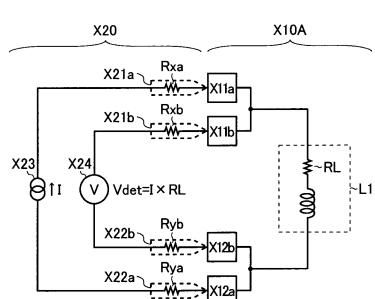

<第2の技術的特徴について>

図22は、本発明に係る半導体装置の第1実施形態を示す模式図である。本実施形態の半導体装置 X10A は、コイル L1 を集積化した半導体装置であって、コイル L1 の一端には、第1の電流供給用パッド X11a と第1の電圧測定用パッド X11b が接続されており、コイル L1 の他端には、第2の電流供給用パッド X12a と第2の電圧測定用パッド X12b が接続されている。

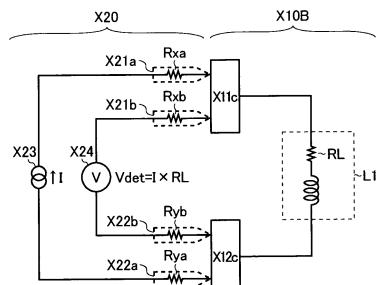

【0296】

図23は、半導体装置 X10A の不良品検査を説明するための模式図である。半導体装置 X10A の不良品検査に用いられる検査装置 X20 は、第1の電流供給用パッド X11a に接触させる第1の電流供給用プローブ X21a と、第1の電圧測定用パッド X11b に接触させる第1の電圧測定用プローブ X21b と、第2の電流供給用パッド X12a に接触させる第2の電流供給用プローブ X22a と、第2の電圧測定用パッド X12b に接触させる第2の電圧測定用プローブ X22b と、第1の電流供給用プローブ X21a と第2の電流供給用プローブ X22aとの間に所定の定電流 I を流す定電流源 X23 と、第1の電圧測定用プローブ X21b と第2の電圧測定用プローブ X22b との間に発生する電圧を測定する電圧計 X24 と、を有して成る。

【0297】

半導体装置 X10A の不良品検査では、定電流源 X23 からコイル L1 に所定の定電流 I が流され、そのときに発生するコイル L1 の両端間電圧（コイル L1 の直列抵抗成分 R<sub>L</sub> に起因して発生する電圧降下）を電圧計 X24 で測定される。

【0298】

ここで、定電流源 X23 からコイル L1 に定電流 I を流すためには、パッド X11a 及び X12a にそれぞれプローブ X21a 及び X22a を接触させる必要があり、接触抵抗成分 R<sub>x a</sub> 及び R<sub>y a</sub> が不可避的に発生する。従って、定電流源 X23 からコイル L1 に定電流 I を流す経路上では、接触抵抗成分 R<sub>x a</sub> 及び R<sub>y a</sub> に起因する電圧降下 (= I × (R<sub>x a</sub> + R<sub>y a</sub>)) が発生する。

【0299】

一方、コイル L1 の両端間電圧を電圧計 X24 で測定するためには、パッド X11b 及び X12b にそれぞれプローブ X21b 及び X22b を接触させる必要があり、上記と同様、接触抵抗成分 R<sub>x b</sub> 及び R<sub>y b</sub> が不可避的に発生する。しかし、電圧計 X24 の内部インピーダンスは極めて高く、電圧計 X24 の両端間には殆ど電流が流れないと想定する。

【0300】

すなわち、本実施形態の半導体装置 X10A の不良品検査に際して、電圧計 X24 で得られる検出電圧 V<sub>det</sub> の電圧値は、下記(2)式で表される通り、上記した接触抵抗成分の影響を何ら受けすことなく、コイル L1 の直列抵抗成分 R<sub>L</sub> のみに応じて変動する。

【0301】

$$V_{det} = I \times R_L \quad \dots \quad (2)$$

【0302】

従って、本実施形態の半導体装置 X10A であれば、その不良品検査に際して、コイル

10

20

30

40

50

L 1 の直列抵抗成分 R L を正確に測定することができるので、コイル L 1 の断線が生じている不良品をリジェクトすることはもちろん、コイル L 1 の抵抗値異常（例えば、巻線同士の中途短絡）が生じている不良品についても、これを適切にリジェクトすることが可能となり、不良品の市場流出を未然に防止することが可能となる。

### 【0303】

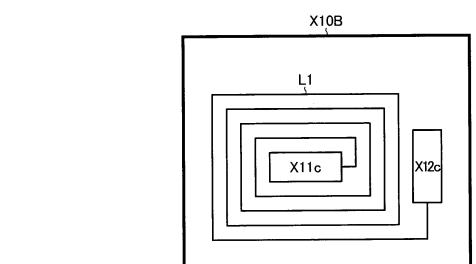

図24は、本発明に係る半導体装置の第2実施形態を示す模式図であり、図25は、半導体装置X10Bの不良品検査を説明するための模式図である。

### 【0304】

本実施形態の半導体装置X10Bにおいて、先に述べた第1の電流供給用パッドX11aと第1の電圧測定用パッドX11bは、第1の共用パッドX11cとして一体的に形成されている。なお、第1の共用パッドX11cは、第1の電流供給用プローブX21aと第1の電圧測定用プローブX21bを同時に接触させることができ可能な面積（第1の電流供給パッドX21aや第1の電圧測定用パッドX11bの面積に比べて2倍程度の大きさ）を有するように形成されている。10

### 【0305】

また、本実施形態の半導体装置X10Bにおいて、先に述べた第2の電流供給用パッドX12aと第2の電圧測定用パッドX12bは、第2の共用パッドX12cとして一体的に形成されている。なお、第2の共用パッドX12cは、第2の電流供給用プローブX22aと第2の電圧測定用プローブX22bを同時に接触させることができ可能な面積（第2の電流供給パッドX12aや第2の電圧測定用パッドX12bの面積に比べて2倍程度の大きさ）を有するように形成されている。20

### 【0306】

このように、1つのパッドサイズを十分に大きく設計できるのであれば、1つのパッドに2つのプローブを接触させる検査方法を採用してもよい。

### 【0307】

なお、半導体装置X10Bの不良品検査に用いられる検査装置X20の構成や検査方法については、先に述べた通りであるため、重複した説明は省略する。

### 【0308】

次に、ハイブリッド自動車に搭載されるモータ駆動装置に本発明を適用した構成を例に挙げて詳細な説明を行う。30

### 【0309】

図26は、本発明に係る半導体装置を用いたモータ駆動装置の一構成例を示すブロック図である。本構成例のモータ駆動装置は、ハイサイドスイッチSWHと、ローサイドスイッチSWLと、ハイサイドスイッチSWHの制御手段であるスイッチ制御装置1と、エンジンコントロールユニット2（以下では、ECU [Engine Control Unit] 2と呼ぶ）と、直流電圧源E1及びE2と、n-p-n型バイポーラトランジスタQ1と、p-n-p型バイポーラトランジスタQ2と、キャパシタC1～C3と、抵抗R1～R8と、ダイオードD1とを有して成る。

### 【0310】

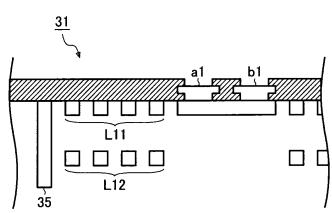

スイッチ制御装置1は、第1半導体チップ10と、第2半導体チップ20と、第3半導体チップ30と、を一のパッケージに封止して成る。40

### 【0311】

スイッチ制御装置1に関する第1の特長は、入出力間絶縁耐圧が1200Vという点である。第2の特長は、UVLOを内蔵している点である。第3の特長は、ウォッチドッグタイマ機能を内蔵している点である。第4の特長は、過電流保護機能（自動復帰型）を内蔵している点である。第5の特長は、過電流保護動作時におけるスローオフ機能を内蔵している点である。第6の特長は、外部エラー検出機能（ERRIN）を内蔵している点である。第7の特長は、異常状態出力機能（FLT、OCPOUT）を内蔵している点である。第8の特長は、アクティブミラークランプ機能を内蔵している点である。第9の特長は、ショートサーキットクランプ機能を内蔵している点である。50

**【0312】**

第1半導体チップ10は、直流電圧源E1から第1電源電圧VCC1（GND1基準で5[V]や3.3[V]など）の供給を受けて駆動され、入力信号INに基づいてスイッチ制御信号S1及びS2を生成するコントローラが集積化されたコントローラチップである。第1半導体チップ10の主な機能としては、スイッチ制御信号S1、S2の生成機能ないし出力機能、トランス伝達異常監視機能（入力信号INの入出力論理監視機能）、エラー状態出力機能、UVLO機能、及び、外部エラー入力信号処理機能を挙げることができる。なお、第1半導体チップ10の耐圧は、第1電源電圧VCC1（GND1基準）を考慮して、適切な耐圧（例えば7[V]耐圧）に設計すればよい。

**【0313】**

第2半導体チップ20は、直流電圧源E2から第2電源電圧VCC2（GND2基準で10～30[V]）の供給を受けて駆動され、第1半導体チップ10から第3半導体チップ30を介して入力されるスイッチ制御信号S1及びS2に基づいて、一端に数[kV]の高電圧が印加されるハイサイドスイッチSWHの駆動制御を行うドライバが集積化されたドライバチップである。第2半導体チップ20の主な機能としては、出力信号OUTの生成機能ないし出力機能、過電流／過電圧保護機能、及び、UVLO機能を挙げることができる。なお、第2半導体チップ20の耐圧は、第2電源電圧VCC2（GND2基準）を考慮して、適切な耐圧（例えば40[V]耐圧）に設計すればよい。

**【0314】**

第3半導体チップ30は、第1半導体チップ10と第2半導体チップ20との間を直流传導しながら、スイッチ制御信号S1及びS2、ウォッチドッグ信号S3、及び、フォルト信号S4の受け渡しを行うトランスが集積化されたトランスピップである。

**【0315】**

上記したように、本構成例のスイッチ制御装置1は、コントローラが集積化される第1半導体チップ10やドライバが集積化される第2半導体チップ20とは別に、トランスのみを搭載する第3半導体チップ30を独立に有して成り、これらを一のパッケージに封止して成る構成とされている。

**【0316】**

このような構成とすることにより、第1半導体チップ10、及び、第2半導体チップ20については、いずれも一般的の低耐圧プロセス（数[V]耐圧～数十[V]耐圧）で作成することが可能となるので、専用の高耐圧プロセス（数[kV]耐圧）を用いる必要がなくなり、製造コストを低減することが可能となる。

**【0317】**

また、第1半導体チップ10、及び、第2半導体チップ20については、いずれも実績のある既存プロセスで作成することが可能であり、新たに信頼性試験を行う必要がないので、開発期間の短縮や開発コストの低減に貢献することができる。

**【0318】**

また、トランス以外の直流絶縁素子（例えばフォトカプラ）を用いる場合であっても、第3半導体チップ30のみを載せ換えることにより、容易に対応することが可能となるので、コントローラチップやドライバチップまで開発し直す必要がなくなり、開発期間の短縮や開発コストの低減に貢献することができる。

**【0319】**

ECU2は、エンジン運転及びモータ運転における電気的な制御を総合的に行うための手段であり、スイッチ制御装置1との間で、各種信号（IN、RST、FLT、OCP OUT）のやり取りを行うマイクロコントローラである。

**【0320】**

ハイサイドスイッチSWH、及び、ローサイドスイッチSWLは、それぞれ、第1モータ駆動電圧VD1の印加端とモータコイルの一端との間、及び、第2モータ駆動電圧VD2の印加端とモータコイルの一端との間に接続され、各々のオン／オフ制御に応じて、モータ駆動電流の供給制御を行う手段である。なお、本構成例のモータ駆動装置では、ハイ

10

20

30

40

50

サイドスイッチS W H及びローサイドスイッチS W Lとして、それぞれ、絶縁ゲートバイポーラトランジスタ(IGBT[Insulated Gate Bipolar Transistor])を用いているが、本発明の構成はこれに限定されるものではなく、SiC[Silicon Carbide]半導体を用いたMOS[Metal Oxide Semiconductor]電界効果トランジスタや、Si半導体を用いたMOS電界効果トランジスタを採用しても構わない。特に、SiC半導体を用いたMOS電界効果トランジスタは、Si半導体を用いたMOS電界効果トランジスタよりも消費電力が小さく、耐熱温度が高いため、ハイブリッド自動車への搭載に好適である。

#### 【0321】

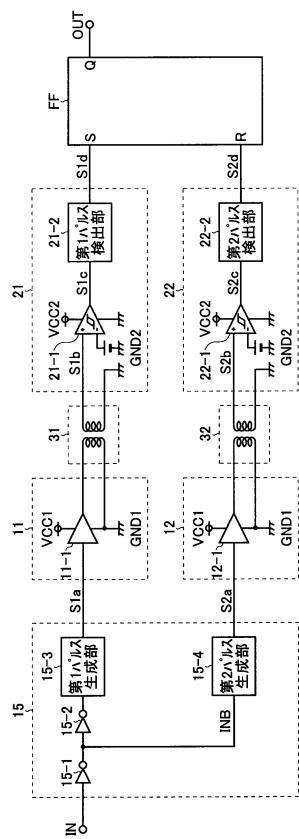

次に、スイッチ制御装置1の内部構成について詳細に説明する。

10

#### 【0322】

第1半導体チップ10は、第1送信部11と、第2送信部12と、第1受信部13と、第2受信部14と、ロジック部15と、第1低電圧ロックアウト部16(以下では第1UVLO[Under Voltage Lock Out]部16と呼ぶ)と、外部エラー検出部(外部エラー検出用コンパレータ)17と、Nチャネル型MOS電界効果トランジスタNa及びNbと、を有して成る。

#### 【0323】

第2半導体チップ20は、第3受信部21と、第4受信部22と、第3送信部23と、第4送信部24と、ロジック部25と、ドライバ部26と、第2低電圧ロックアウト部27(以下では、第2UVLO部27と呼ぶ)と、過電流検出部(過電流検出用コンパレータ)28と、OCP[Over Current Protection]タイマ29と、Pチャネル型MOS電界効果トランジスタP1及びP2と、Nチャネル型MOS電界効果トランジスタN1～N3と、SRフリップフロップFFと、を有して成る。

20

#### 【0324】

第3半導体チップ30は、第1トランス31と、第2トランス32と、第3トランス33と、第4トランス34と、を有して成る。

#### 【0325】

第1送信部11は、ロジック部15から入力されるスイッチ制御信号S1を第1トランス31経由で第3受信部21に送信する手段である。第2送信部12は、ロジック部15から入力されるスイッチ制御信号S2を第2トランス32経由で第4受信部22に送信する手段である。第1受信部13は、第3送信部23から第3トランス33経由で入力されるウォッチドッグ信号S3を受信してロジック部15に伝達する手段である。第4受信部14は、第4送信部24から第4トランス34経由で入力されるドライバ異常信号S4を受信してロジック部15に伝達する手段である。

30

#### 【0326】

ロジック部15は、ECU2との間で、各種信号(IN、RST、FLT、OCPOT)のやり取りを行うとともに、第1送信部11、第2送信部12、第1受信部13、及び、第2受信部14を用いて、第2半導体チップ20との間で、各種信号(S1～S4)のやり取りを行う手段である。

#### 【0327】

40

なお、ロジック部15は、入力信号INがハイレベルであるときには、出力信号OUTをハイレベルとするようにスイッチ制御信号S1、S2を生成し、逆に、入力信号INがローレベルであるときには、出力信号OUTをローレベルとするようにスイッチ制御信号S1、S2を生成する。より具体的に述べると、ロジック部15は、入力信号INのポジティブエッジ(ローレベルからハイレベルへの立上がりエッジ)を検出してスイッチ制御信号S1にパルスを立てる一方、入力信号INのネガティブエッジ(ハイレベルからローレベルへの立下がりエッジ)を検出してスイッチ制御信号S2にパルスを立てる。

#### 【0328】

また、ロジック部15は、リセット信号RSTがローレベルであるときには、出力信号OUTの生成動作をディセーブルとするように、すなわち、出力信号OUTをローレベル

50

で固定するようにスイッチ制御信号 S<sub>1</sub>、S<sub>2</sub>を生成し、逆に、リセット信号 RSTがハイレベルであるときには、出力信号 OUTの生成動作をイネーブルとするよう、すなわち、出力信号 OUTを入力信号 INに応じた論理レベルとるようにスイッチ制御信号 S<sub>1</sub>、S<sub>2</sub>を生成する。なお、リセット信号 RSTが所定時間（例えば 500 [ns]）にわたってローレベルに維持された場合、ロジック部 15は、過電流検出部 28による保護動作を復帰させるようにスイッチ制御信号 S<sub>1</sub>、S<sub>2</sub>を生成する。

#### 【0329】

また、ロジック部 15は、スイッチ制御装置 1の正常時には、トランジスタ Naをオフとして、第 1 状態信号 FLTをオープン（抵抗 R<sub>1</sub>によるプルアップ状態）とし、スイッチ制御装置 1の異常時（第 1 半導体チップ 10 側での低電圧異常やスイッチ制御信号 S<sub>1</sub>及び S<sub>2</sub>のトランス伝達異常、或いは、ERRIN 信号異常が検出された時）には、トランジスタ Naをオンとして、第 1 状態信号 FLTをローレベルとする。このような構成であれば、ECU 2は、第 1 状態信号 FLTを監視することにより、スイッチ制御装置 1の状態を把握することが可能となる。なお、第 1 半導体チップ 10 側での低電圧異常については、第 1 UVLO 部 16での検知結果に基づいて判断すればよく、また、スイッチ制御信号 S<sub>1</sub>、S<sub>2</sub>のトランス伝達異常については、入力信号 IN（スイッチ制御信号 S<sub>1</sub>、S<sub>2</sub>）とウォッチャドッグ信号 S<sub>3</sub>との比較結果に基づいて判断すればよい。また、ERRIN 信号異常については、外部エラー検出部 17の出力結果に基づいて判断すればよい。

#### 【0330】

また、ロジック部 15は、スイッチ制御装置 1の正常時には、トランジスタ Nbをオフとして、第 2 状態信号 OCP OUTをオープン（抵抗 R<sub>2</sub>によるプルアップ状態）とし、スイッチ制御装置 1の異常時（第 2 半導体チップ 20 側での低電圧異常やハイサイドスイッチ SWH に流れるモータ駆動電流の過電流が検出された時）には、トランジスタ Nbをオンとして、第 2 状態信号 OCP OUTをローレベルとする。このような構成であれば、ECU 2は、第 2 状態信号 OCP OUTを監視することにより、スイッチ制御装置 1の状態を把握することが可能となる。なお、第 2 半導体チップ 20 側での低電圧異常やハイサイドスイッチ SWH に流れるモータ駆動電流の過電流については、ドライバ異常信号 S<sub>4</sub>に基づいて判断すればよい。

#### 【0331】

第 1 UVLO 部 16は、第 1 電源電圧 VCC<sub>1</sub>が低電圧状態であるか否かを監視し、その監視結果をロジック部 15に伝達する手段である。

#### 【0332】

外部エラー検出部 17は、抵抗 R<sub>3</sub>と抵抗 R<sub>4</sub>の接続ノードから ERRIN 端子に入力される電圧（監視対象となるアナログ電圧を抵抗分割して得られる分圧電圧）と所定の閾値電圧とを比較し、その比較結果をロジック部 15に伝達する手段である。

#### 【0333】

第 3 受信部 21は、第 1 送信部 11から第 1 トランス 31 経由で入力されるスイッチ制御信号 S<sub>1</sub>を受信して SR フリップフロップ FF のセット入力端（S）に伝達する手段である。第 4 受信部 22は、第 2 送信部 12から第 2 トランス 32 経由で入力されるスイッチ制御信号 S<sub>2</sub>を受信して SR フリップフロップ FF のリセット入力端（R）に伝達する手段である。第 3 送信部 23は、ロジック部 25から入力されるウォッチャドッグ信号 S<sub>2</sub>を第 3 トランス 33 経由で第 1 受信部 13に送信する手段である。第 4 送信部 24は、ロジック部 25から入力されるドライバ異常信号 S<sub>4</sub>を第 4 トランス 34 経由で第 2 受信部 14に送信する手段である。

#### 【0334】

SR フリップフロップ FF は、セット入力端（S）に入力されるスイッチ制御信号 S<sub>1</sub>のパルスエッジをトリガとして出力信号をハイレベルにセットし、リセット入力端（R）に入力されるスイッチ制御信号 S<sub>2</sub>のパルスエッジをトリガとして出力信号をローレベルにリセットする。すなわち、上記の出力信号は、ECU 2からロジック部 15に入力される入力信号 IN と同一信号となる。なお、上記の出力信号は、SR フリップフロップ FF

10

20

30

40

50

の出力端( Q )からロジック部 25 に送出される。

**【 0 3 3 5 】**

ロジック部 25 は、SR フリップフロップ FF の出力信号(入力信号 IN と同一信号)に基づいて、ドライバ部 26 の駆動信号を生成する。

**【 0 3 3 6 】**

また、ロジック部 25 は、第 2 UVLO 部 27 及び過電流検出部 28 での検知結果に基づいて、低電圧異常や過電流が生じていると判断した場合、その旨を異常検知信号でドライバ部 26 に伝達するとともに、ドライバ異常信号 S4 でロジック部 15 にも伝達する。このような構成とすることにより、第 2 半導体チップ 20 に異常が生じた場合でも、ドライバ部 26 は速やかに保護動作を行うことが可能となり、ロジック部 15 は ECU 2 への異常通知動作(第 2 状態信号 OCP OUT のローレベル遷移)を行うことが可能となる。なお、ロジック部 25 は、過電流保護動作後、所定時間が経過した時点で過電流保護動作からの自動復帰を行う機能を有している。10

**【 0 3 3 7 】**

また、ロジック部 25 は、SR フリップフロップ FF の出力信号をそのままウォッチドッグ信号 S3 として第 3 送信部 23 に出力する。このように、第 2 半導体チップ 20 から第 1 半導体チップ 10 に向けてウォッチドッグ信号 S3 を返信する構成であれば、ロジック部 15 において、第 1 半導体チップ 10 に入力された入力信号 IN と、これに対して第 2 半導体チップ 20 から返信されたウォッチドッグ信号 S3 を比較することにより、トランス伝達異常の有無を判定することが可能となる。20

**【 0 3 3 8 】**

ドライバ部 26 は、ロジック部 25 から入力される駆動信号に基づいて、トランジスタ P1 とトランジスタ N1 のオン / オフ制御を行い、トランジスタ P1 とトランジスタ N1 との接続ノードから出力信号 OUT を出力する手段である。出力信号 OUT は、トランジスタ Q1 及び Q2 から成る駆動回路を介して、ハイサイドスイッチ SWH に入力されている。上記の駆動回路は、出力信号 OUT にハイサイドスイッチ SWH の駆動能力を持たせるべく、出力信号 OUT の立上がり / 立下がり時間(スルーレート)を調整する手段である。なお、出力信号 OUT がハイレベルであるときには、ハイサイドスイッチ SWH がオンとされ、逆に、出力信号 OUT がローレベルであるときには、ハイサイドスイッチ SWH がオフとされる。30

**【 0 3 3 9 】**

なお、ドライバ部 26 は、出力信号 OUT の電圧レベル( GND 2 基準)がローレベルとなったとき、ハイサイドスイッチ SWH のゲートから CLAMP 端子を介して電荷(ミラー電流)を吸い込むように、トランジスタ N2 をオンとする機能(アクティブミラークランプ機能)を有している。このような構成とすることにより、ハイサイドスイッチ SWH をオフする際には、上記の駆動回路で設定されるスルーレートに依ることなく、トランジスタ N2 を介してハイサイドスイッチ SWH のゲート電位を速やかにローレベルへ立ち下げる事が可能となる。

**【 0 3 4 0 】**

また、ドライバ部 26 は、出力信号 OUT の電圧レベル( GND 2 基準)がハイレベルとなったとき、CLAMP 端子を介してハイサイドスイッチ SWH のゲートを電源電圧 VCC 2 にクランプするように、トランジスタ P2 をオンとする機能(ショートサーキットクランプ機能)を有している。このような構成とすることにより、ハイサイドスイッチ SWH をオンする際、ハイサイドスイッチ SWH のゲート電位が電源電圧 VCC 2 よりも高電位まで上昇することはなくなる。40

**【 0 3 4 1 】**

また、ドライバ部 26 は、ロジック部 25 から入力される異常検知信号に基づいて保護動作を行う必要があると判断した場合、トランジスタ P1 、 P2 及びトランジスタ N1 、 N2 をいずれもオフとする一方、トランジスタ N3 をオンとする機能(スローオフ機能)を有している。このようなスイッチ制御により、保護動作時には、ハイサイドスイッチ S50

W H のゲートから抵抗 R 5 を介して、通常動作時よりも緩やかに電荷を引き抜くことができる。このような構成とすることにより、保護動作時にモータ電流が瞬断されることを回避できるので、モータコイルの逆起電力によって生じるサージを抑制することが可能となる。なお、抵抗 R 5 の抵抗値を適宜選択することにより、保護動作時の立ち下がり時間を任意に調整することができる。

#### 【 0 3 4 2 】

第 2 U V L O 部 2 7 は、第 2 電源電圧 V C C 2 が低電圧状態であるか否かを監視し、その監視結果をロジック部 2 5 に伝達する手段である。

#### 【 0 3 4 3 】

過電流検出部 2 8 は、抵抗 R 7 と抵抗 R 8 の接続ノードから O C P / D E S A T I N 端子に入力される電圧（ダイオード D 1 のアノード電圧を抵抗分割して得られる分圧電圧）と所定の閾値電圧とを比較し、その比較結果をロジック部 2 5 に伝達する手段である。なお、ハイサイドスイッチ S W H に流れるモータ駆動電流が大きいほど、ハイサイドスイッチ S W H として用いられている絶縁ゲートバイポーラトランジスタのコレクタ・エミッタ間電圧が大きくなる。従って、ハイサイドスイッチ S W H に流れるモータ駆動電流が大きいほど、ダイオード D 1 のアノード電圧が上昇し、延いては、O C P / D E S A T I N 端子に入力される電圧が上昇する。そこで、過電流検出部 2 8 は、O C P / D E S A T I N に入力される電圧（G N D 2 基準）が所定の閾値（例えば 0 . 5 [ V ] ）に達したとき、ハイサイドスイッチ S W H に流れるモータ駆動電流が過電流状態であると判定する。

#### 【 0 3 4 4 】