53

DEUTSCHE DEMOKRATISCHE REPUBLIK

(12) Wirtschaftspatent

Teilweise bestätigt gemäß § 18 Absatz 1

Patentgesetz

# PATENTSCHRIFT

(19) DD (11) 201 214 B1

4(51) G 11 B 20/14

H 04 L 7/02

H 03 K 9/00

## AMT FÜR ERFINDUNGS- UND PATENTWESEN

---

(21) WP G 11 B / 234 102 1 (22) 15.10.81 (45) 09.04.86

(44) 06.07.83

---

(71) VEB Geophysik Leipzig, 7010 Leipzig, PSF 370, DD

(72) Werner, Frank, Dipl.-Phys., DD

---

(54) Schaltungsanordnung zur Taktrückgewinnung bei der Demodulation von Wiedergabesignalen

---

ISSN 0433-6461

7 Seiten

**Patentansprüche:**

1. Schaltungsanordnung zur Taktrückgewinnung bei der Demodulation von Wiedergabesignalen unter Verwendung eines Begrenzers als Eingangsteil und eines aus einem spannungsgesteuerten Oszillator, einer aus einem 4:1-Taktteiler und einer Auswertelogik bestehenden Abfrage- und Auswerteschaltung und einem Filter zusammengeschalteten Phasenregelkreis, gekennzeichnet dadurch, daß die Abfrage- und Auswerteschaltung weiterhin aus zwei 1-Bit-Schieberegistern besteht, deren Dateneingänge unmittelbar mit dem begrenzten Wiedergabesignal verbunden sind, wobei der Takteingang des ersten Schieberegisters, dessen Ausgänge an Eingängen der Auswertelogik liegen mit dem negierten Ausgang des Taktteilers verbunden ist, während der wahre Ausgang des Taktteilers mit dem Takteingang des zweiten Schieberegisters verbunden ist, dessen Ausgänge ebenfalls an Eingängen der Auswertelogik liegen, deren letzter Eingang mit dem begrenzten Wiedergabesignal beschaltet ist.

2. Schaltungsanordnung nach Anspruch 1, gekennzeichnet dadurch, daß die Ausgänge beider Flip-Flop-Stufen des zweistufigen Taktteilers mit den Eingängen der NAND-Gatter und die Ausgänge der beiden 1-Bit-Schieberegister mit den Eingängen der EXKLUSIV-ODER-Gatter der Auswertelogik verbunden sind.

Hierzu 4 Seiten Zeichnungen

**Anwendungsgebiet der Erfindung**

Die erfindungsgemäße Schaltungsanordnung dient bei Magnetspeichermedien zur Demodulation des Wiedergabesignals und ist für die Rückgewinnung des Bittaktes einzusetzen. Die Anwendung kann sowohl bei Richtungstakt- als auch bei Zweifrequenzschrift erfolgen.

**Charakteristik der bekannten technischen Lösungen**

In der DD-PS 124408 wird eine Schaltungsanordnung zur Demodulation von Wiedergabesignalen vorgestellt, bei der die Taktrückgewinnung über einen Nulldurchgangsdetektor und einen monostabilen Multivibrator erfolgt, an dem eine digitale Abfrageschaltung angeschlossen ist. Diese Schaltungsanordnung hat den Nachteil, daß der fest eingestellte monostabile Multivibrator nicht den laut Norm zulässigen Schwankungen der Eingangs frequenz folgt. Das führt dazu, daß zwischen Eingangssignal und wiedergewonnenem Takt größere Phasenabweichungen entstehen. Der zur zeitrichtigen Abfrage benötigte Bittakt wird dadurch gewonnen, daß mit Hilfe der Abtastung eines Sägezahnimpulses zu den Zeitpunkten des Nulldurchgangs des Wiedergabesignals eine Steuerspannung erzeugt wird, die nach Filterung zur Steuerung eines Oszillators verwendet wird (siehe Fig. 6 der o. a. PS). Dieser spannungsgesteuerte Oszillator hat die Aufgabe, mit Hilfe der Steuerspannung die Taktfrequenz und Phasenlage dem Wiedergabesignal nachzuführen.

In der DD-PS 139075 wird die technische Lösung der DD-PS 124408 durch eine digitale Abfrage- und Auswerteschaltung verbessert. Hier wird kein Sägezahnimpuls verwendet. Dafür weist diese Lösung einen breiteren Nullimpuls auf. Dieser soll eine Breite von einer 1/4-Periode haben, welche nur fest eingestellt werden kann. Damit besitzt diese Schaltung auch einen fest eingestellten Nullimpuls wie die erste Lösung, wodurch der bereits genannte Nachteil erhalten bleibt.

**Ziel der Erfindung**

Das Ziel der Erfindung besteht im Erreichen einer wesentlich höheren Sicherheit bei der Rückgewinnung von Information und Bittakt durch Erzeugung einer fehlerfreien Steuerspannung bei zulässigen Frequenzabweichungen. Ein entscheidender weiterer Effekt ist, daß die Auswerteschaltung unabhängig von verschiedenen Lesegeschwindigkeiten sein soll. Damit wird bei notwendiger Umschaltung auf andere Lesegeschwindigkeiten der schaltungstechnische Aufwand reduziert.

**Wesen der Erfindung**

Der Erfindung liegt die Aufgabe zugrunde, im Zweig der Bittaktrückgewinnung die Zeitabhängigkeit durch Wegfall der Zeitglieder so weit wie möglich zu beseitigen und damit den durch die Verwendung des Nullimpulses in der Steuerspannung entstehenden Fehler bei zulässigen Frequenzabweichungen auszuschalten. Dabei wird von der Schaltungsanordnung gemäß DD-PS 124408 ausgegangen und die digitale Abfrage- und Auswerteschaltung gemäß der DD-PS 139075 verändert.

Erfindungsgemäß wird die Aufgabe dadurch gelöst, daß zur Gewinnung des phasenrichtigen Bittaktes durch Abfrage des logischen Zustandes des begrenzten Wiedergabesignals an beiden Flanken des Bittaktes der Begrenzer unmittelbar mit zwei 1-Bit-Schieberegistern verbunden wird. Dabei übernimmt das eine 1-Bit-Schieberegister zum Zeitpunkt der einen Flanke und das zweite 1-Bit-Schieberegister zum Zeitpunkt der anderen Flanke des Bittaktes das vom Begrenzer ankommende begrenzte Wiedergabesignal.

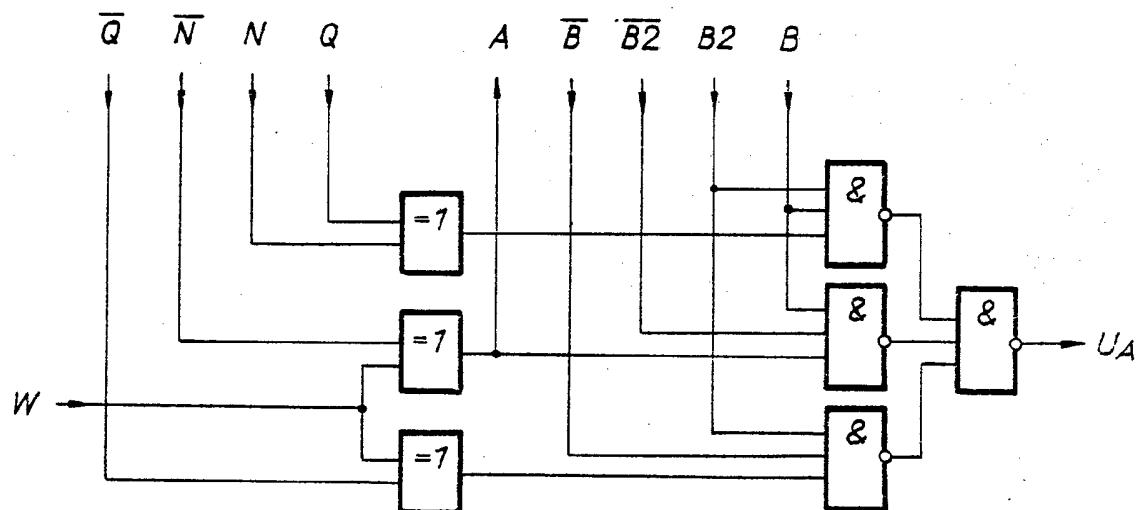

Weiterhin ist es erforderlich, das logische Wiedergabesignal mit dem logischen Taktzustand so zu verknüpfen, daß die Ausgangsspannung der Abfrage- und Auswerteschaltung in bekannter Weise über einen Filter zur Steuerung des spannungsgesteuerten Oszillators verwendet werden kann. Dazu wird der Begrenzer parallel zu den beiden 1-Bit-Schieberegistern mit der digitalen Auswertelogik der Abfrage- und Auswerteschaltung und der zweistufigen Taktteiler der Abfrage- und Auswerteschaltung zur Ansteuerung der beiden Schieberegister mit diesen verbunden. Der Oszillator muß — wie bereits bekannt — mindestens auf der vierfachen Frequenz des Bittaktes schwingen. Von Bedeutung ist die Zuordnung von Bedingungen gemäß Tabelle 1 zu vier zeitlichen Taktintervallen, die durch den Bittakt B und den doppelten Bittakt B2 bestimmt sind. Diese Bedingungen werden dadurch erreicht, daß unter Verwendung einer Auswertelogikschaltung gemäß Figur 5 b der Begrenzer direkt mit der Auswertelogikschaltung verbunden ist und die Ausgänge der Flip-Flop-Stufen des zweistufigen Taktteilers der Abfrage- und Auswerteschaltung auf die NAND-Gatter sowie die Ausgänge der beiden 1-Bit-Schieberegister auf die EXKLUSIV-ODER-Gatter der Auswertelogik geschaltet sind. Damit erfolgt die logische Verknüpfung des logischen Zustandes des begrenzten Wiedergabesignals W mit dessen abgefragtem logischem Zustand  $W_\alpha$  zu bestimmten Taktphasen  $\alpha$ . Der zeitliche Mittelwert der Ausgangsspannung der Auswertelogikschaltung stellt die Steuerspannung für den spannungsgesteuerten Oszillator dar. Innerhalb einer Phasenverschiebung von  $\pm \frac{\pi}{2}$  zwischen Bittakt und Wiedergabesignal zeigt die Steuerspannung einen linearen Verlauf und gleiche Steilheit für eine LO- und L- bzw. O-Folge bei Richtungstaktschrift, was bei Diphase-Schrift einer O- und L-Folge entspricht.

### Ausführungsbeispiel

Nachstehend wird die Erfindung an einem Ausführungsbeispiel erläutert. Die dazugehörigen Zeichnungen und Tabellen zeigen in

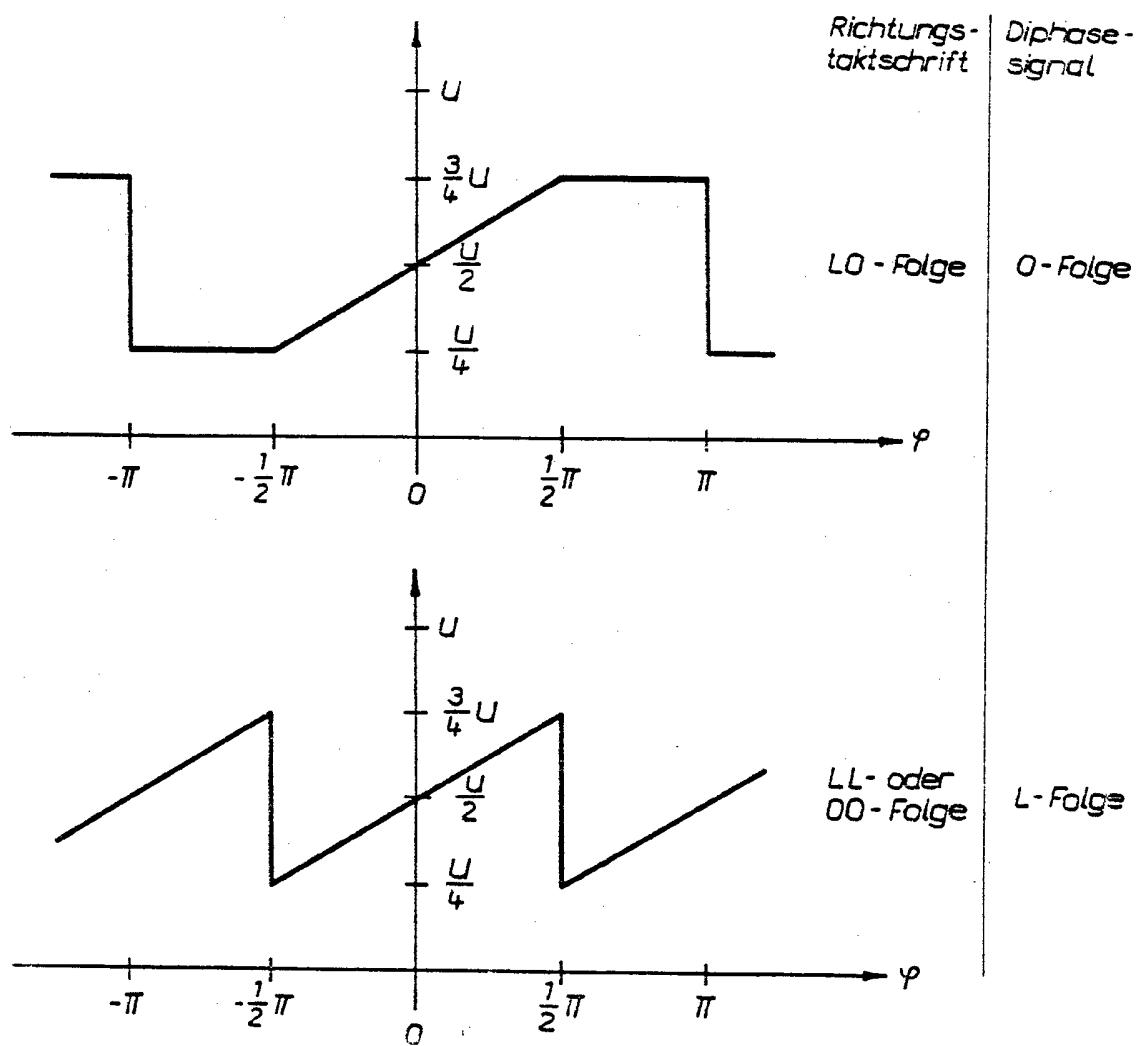

Fig.1: Verlauf der Steuerspannung in Abhängigkeit von der Phasenverschiebung zwischen Bittakt und Wiedergabesignal bei verschiedenen Datenfolgen.

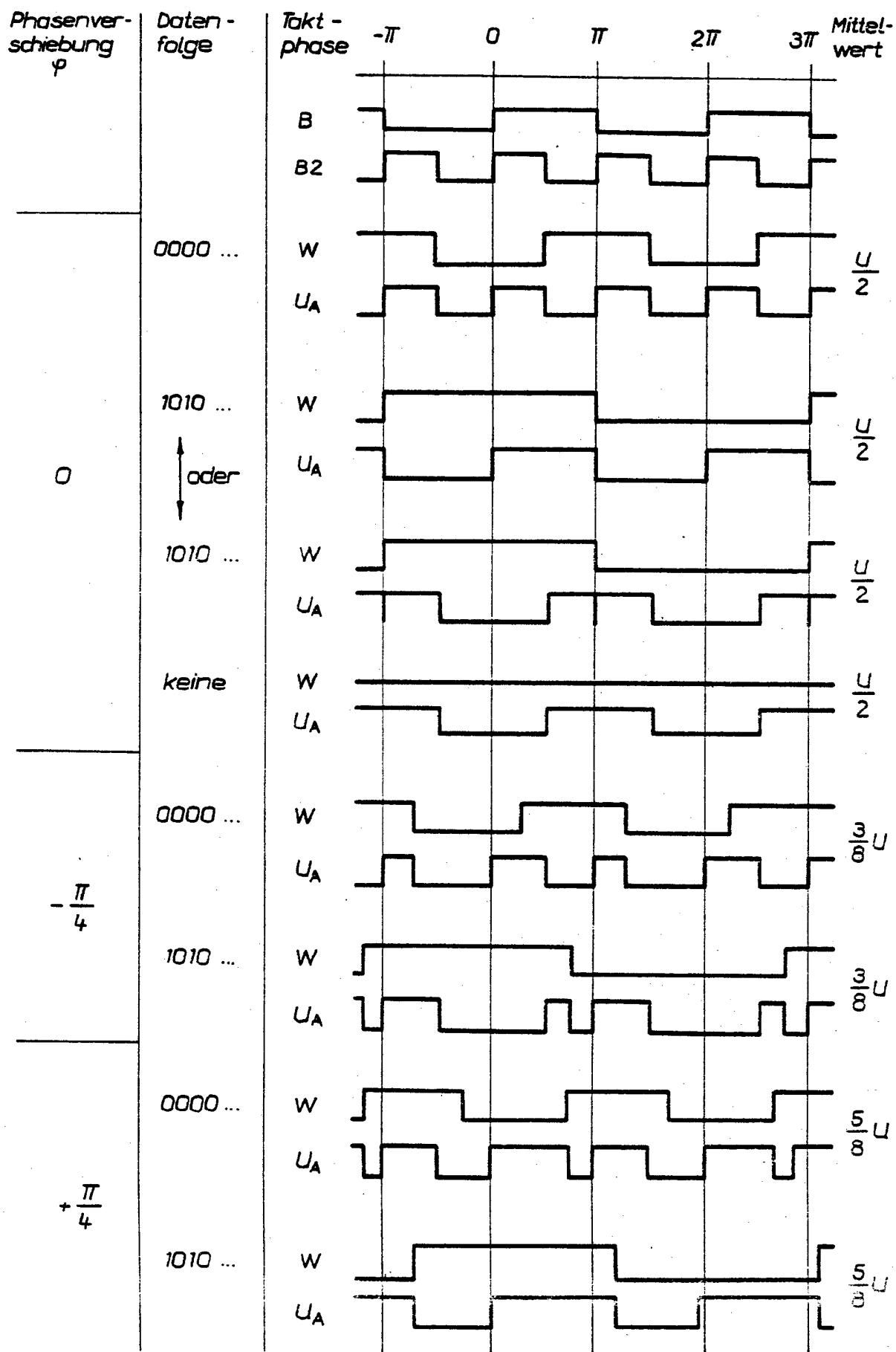

Fig.2: Bildung der Ausgangsspannung der Auswertelogik bei verschiedenen Datenfolgen in Richtungstaktschrift und Phasenverschiebungen zwischen Bittakt und Wiedergabesignal.

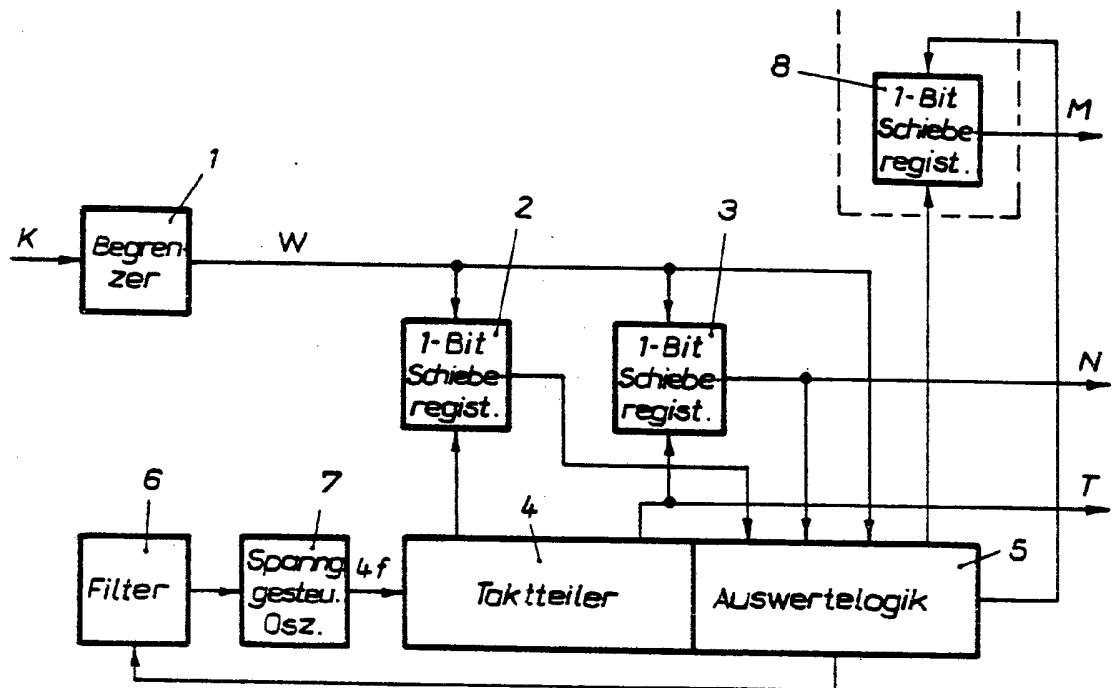

Fig.3: Blockschaltbild der Schaltungsordnung

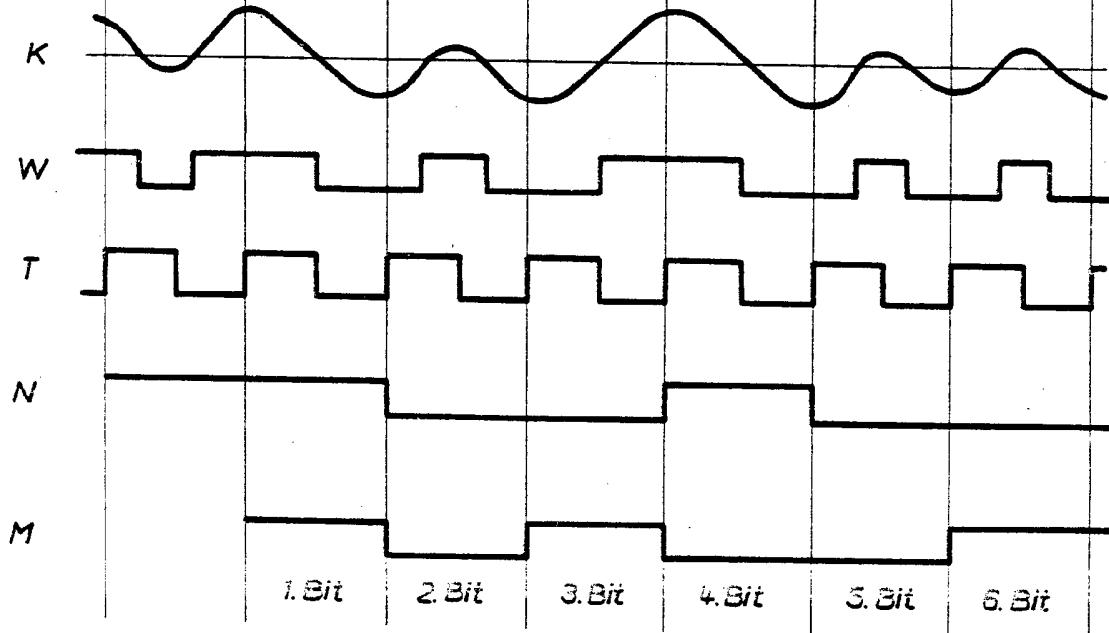

Fig.4: Impulsplan der Schaltungsanordnung nach Fig.3

Fig.5: Ausführungsbeispiel der Schaltungsanordnung zur Erzeugung der Steuerspannung unterteilt nach

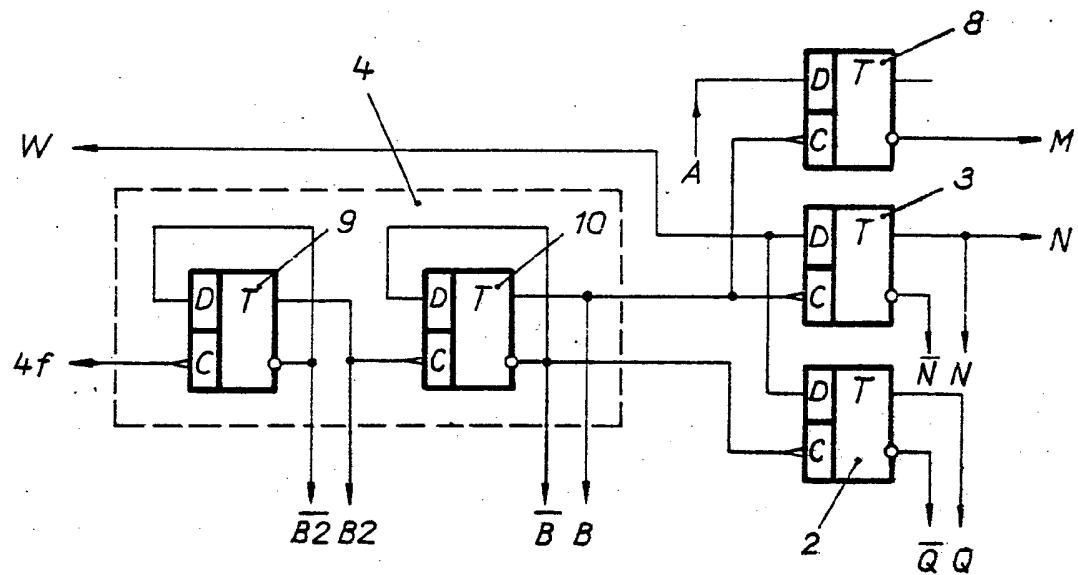

Fig.5a: Zweistufiger Taktteiler mit Schieberegistern und

Fig.5b: Auswertelogik

Tab.1: Bildung der Analogspannung  $U_a$  am Ausgang der Auswertelogik.

In der Fig.1 ist der Verlauf der Steuerspannung  $U_a$  in Abhängigkeit von der Phasenverschiebung  $\phi$  zwischen Bittaktsignal B und begrenztem Wiedergabesignal W für die möglichen Daten bei beiden Schriftarten dargestellt. Da ein Phasenfehler bis zu  $\pm$  zugelassen wird, ist der von der Datenfolge unabhängige Verlauf in diesem Bereich optimal. Die Bildung dieser Steuerspannung verdeutlicht Fig.2 für mögliche Datenfolgen und ausgewählte Phasenverschiebungen  $\phi$ . Die Steuerspannung  $U_a$  ist dabei nach Tabelle 1 gebildet. Der angegebene Mittelwert bezieht sich auf eine Taktperiode der Länge  $2\pi$ . Aus dieser Darstellung wird auch der Zusammenhang mit dem Bittaktsignal B bzw. dem doppeltfrequenten Bittaktsignal B2 deutlich.

Die Schaltungsanordnung zur Demodulation von aufgezeichneten Split-Phase-Signalen Fig.3 beginnt mit dem Begrenzer 1, dem das Wiedergabesignal K zugeführt wird. Der Begrenzer ist mit zwei 1-Bit-Schieberegistern 2 und 3 zusammengeschaltet, so daß das begrenzte Wiedergabesignal W direkt auf beide Schieberegister 2 und 3 gelangt. Parallel dazu ist der Begrenzer 1 mit der Auswertelogik 5 verbunden, welche zusammen mit dem Taktteiler 4 die Abfrage und Auswerteschaltung bildet. Der zweistufig aufgebaute Taktteiler 4 besteht aus zwei D-Flip-Flops 9 und 10 Fig.5a. Er liefert den rückgewonnenen Bittakt. Der Ausgang des Taktteilers 4 liegt an beiden Schieberegistern 2 und 3 zur Steuerung dieser beiden Schieberegister. Das auf den Schieberegistern 2 und 3 ankommende Signal W wird durch diese zu verschiedenen Taktpassen  $\alpha$  abgefragt. Dabei liefert das Schieberegister 3 die NRZ-Information N für die Richtungstaktschrift.

Die Ausgänge Q und  $\bar{Q}$  bzw. N und  $\bar{N}$  der beiden Schieberegister 2 bzw. 3 sowie die Ausgänge B2 und  $\bar{B}2$  bzw. B und  $\bar{B}$  der Stufen 9 bzw. 10 des Taktteilers 4 sind gemäß Fig.5a und 5b mit den entsprechenden Eingängen der Auswertelogik verbunden. Durch die logische Verknüpfung wird über diese Zusammenschaltung die Steuerspannung  $U_a$  gebildet. Über die Zusammenschaltung des Ausgangs der Auswertelogik 5 über einen Filter 6 mit dem Eingang des spannungsgesteuerten Oszillators 7 wird die Steuerspannung  $U_a$  zur Steuerung des Oszillators 7 genutzt. Dieser ist mit dem Taktteiler 4 verbunden und gibt das Signal 4f an den Takteingang der ersten Teilerstufe 9. Über die Ausgänge der zweiten Teilerstufe 10 erfolgt, durch die Verbindung mit den Takteingängen der Schieberegister-Flip-Flop 2 und 3, die Übernahme des an deren D-Eingängen anliegenden logischen Zustandes des begrenzten Wiedergabesignals W, bzw. bei Diphase-Modulation auch des Signales A. Dieses Signal ist bei Diphase-Aufzeichnungen das Eingangssignal für das im Fall dieser Schriftart notwendige 1-Bit-Schieberegister 8, welches dann die NRZ-Information M liefert.

Die Schaltung der Auswertelogik 5 ist, wie aus Fig.5b zu ersehen, aus an sich bekannten EXKLUSIV-ODER-Gattern und NAND-Gattern aufgebaut.

Zur phasenrichtigen Einsynchronisation des spannungsgesteuerten Oszillators ist bei Datenbeginn mit geeigneten an sich bekannten Mitteln die Anfangsphasenabweichung kleiner  $\pm \frac{\pi}{2}$  zu halten.

| $\alpha$         | $T$ | $T_2$ | Bedingung             | $U_A$ |

|------------------|-----|-------|-----------------------|-------|

| $0\pi$           |     |       |                       |       |

| $\frac{\pi}{2}$  | $L$ | $L$   | $W_{0\pi} = W_{-\pi}$ | 0     |

| $\pi$            | $L$ | 0     | $W_{0\pi} = W$        | u     |

| $\frac{3\pi}{2}$ | 0   | $L$   | $W_{1\pi} = W$        | u     |

| $2\pi$           | 0   | 0     | —                     | 0     |

Tab. 1

Figur 1

-8- 4 234102 1

Figur 2

234102 1

Figur 3

| Diphase-<br>signal           | 1. Bit<br>L | 2. Bit<br>0 | 3. Bit<br>L | 4. Bit<br>0 | 5. Bit<br>0 | 6. Bit<br>L | 7. Bit<br>L |             |

|------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Richtgs-<br>takt-<br>schrift |             | 2. Bit<br>L | 3. Bit<br>0 | 4. Bit<br>0 | 5. Bit<br>L | 6. Bit<br>0 | 7. Bit<br>0 | 8. Bit<br>0 |

Figur 4

201 214

6 ~~234402~~ 1

Figur 5a

Figur 5b