(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4529493号

(P4529493)

(45) 発行日 平成22年8月25日(2010.8.25)

(24) 登録日 平成22年6月18日(2010.6.18)

(51) Int.Cl.

H01L 27/105 (2006.01)

F 1

H01L 27/10 448

請求項の数 11 (全 16 頁)

(21) 出願番号 特願2004-69985 (P2004-69985)

(22) 出願日 平成16年3月12日 (2004.3.12)

(65) 公開番号 特開2005-260014 (P2005-260014A)

(43) 公開日 平成17年9月22日 (2005.9.22)

審査請求日 平成19年2月23日 (2007.2.23)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100100310

弁理士 井上 学

(72) 発明者 長田 健一

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 伊藤 清男

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

審査官 粟野 正明

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のワード線と、前記複数のワード線と交差する複数のビット線と、前記複数のワード線と前記複数のビット線の交点に配置される複数のメモリセルとを有するメモリアレイを具備し、

前記複数のメモリセルの各々は、チャネル部が該メモリセルの深さ方向に形成された縦型トランジスタと、その上下どちらか一方に与えられる温度によりその抵抗値が変化する相変化抵抗を含み、

前記メモリアレイは、前記深さ方向に積層され、前記縦型トランジスタのチャネル部分に電位を供給することを特徴とする半導体装置。

10

## 【請求項 2】

請求項 1において、前記縦型トランジスタのチャネル部分は、半導体基板上に形成された多結晶シリコンからなることを特徴とする半導体装置。

## 【請求項 3】

請求項 1において、前記メモリアレイは、前記複数のワード線の夫々に接続される複数のワードドライバと前記複数のビット線に接続されるカラム選択回路を更に有することを特徴とする半導体装置。

## 【請求項 4】

請求項 3において、前記ワードドライバと前記カラム選択回路は、チャネル部が該メモリセルの深さ方向に形成された縦型トランジスタを用いて構成されていることを特徴とす

20

る半導体装置。

【請求項 5】

請求項 1において、前記メモリアレイは、シリコン基板の表面より上方に存在することを特徴とする半導体装置。

【請求項 6】

請求項5において、

前記シリコン基板に、入出力回路が形成されていることを特徴とする半導体装置。

【請求項 7】

請求項 1において、積層された前記メモリアレイのメモリセルの実効的なセルサイズは、F を最小加工寸法としてときに、2 F 2 または 1 F 2 であることを特徴とする半導体装置。10

【請求項 8】

請求項 1において、前記ビット線は、2 つの異なる前記メモリアレイ内に夫々配置された 2 つの縦型トランジスタで共有されていることを特徴とする半導体装置。

【請求項 9】

請求項 8において、

前記 2 つの縦型トランジスタは、前記 2 つの縦型トランジスタの間に配置された前記ビット線と前記深さ方向の直線上に配置されていることを特徴とする半導体装置。

【請求項 10】

請求項 1において、

積層された前記メモリアレイは、前記ビット線を共有していることを特徴とする半導体装置。20

【請求項 11】

請求項 10において、

積層された 2 つの異なる前記メモリアレイ内に存在する夫々の前記縦型トランジスタは、2 つの前記縦型トランジスタの間に配置された前記ビット線と前記深さ方向の直線上に配置されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置又は半導体記憶装置に関し、特に、高集積かつ不揮発性を有する、ランダムアクセスメモリに関する。30

【背景技術】

【0002】

高速で高集積な不揮発性メモリを目指して、非特許文献1で述べられているように、相変化メモリの開発が進められている。相変化メモリでは、カルコゲナイト材料と呼ばれる相変化材料が、状態により抵抗が異なることを利用して、情報を記憶する。相変化抵抗の書き換えは、電流を流して発熱させることにより、状態を変化させて行う。リセット( RESET )動作と呼ばれる高抵抗化(アモルファス化)は、比較的高温に保つことにより行い、セット( SET )動作とも呼ばれる低抵抗化(結晶化)は、比較的低温に十分な期間保つことにより行う。相変化材料の読み出し動作は、相変化抵抗の状態を変化させない範囲で電流を流して行う。40

【0003】

非特許文献2および特許文献1には、相変化抵抗の特性について述べられている。さらに、非特許文献3には、相変化抵抗とNMOSトランジスタにより構成されたメモリセルについて述べられている。

これらの文献で、高速なROM(Read-Only Memory)に留まらず、不揮発性のRAM(Random Access Memory)の可能性も述べられており、ROMとRAMの機能を併せ持つ統合型メモリの実現も言及されている。相変化メモリは、相変化抵抗の電極面積が小さい方が、小さな電力で抵抗値を変化させられるため、セルのスケーリングが容易である。また、アモルファ

50

ス状態と結晶状態の抵抗値の差も大きいため、高速な読み出し動作が実現できる。これらの理由から、相変化メモリによる高速不揮発性メモリの実現が期待されている。

特許文献2では、相変化抵抗と縦型トランジスタを用いたメモリセル構造について述べられている。このメモリセル構造を用いることにより従来のDRAMに比べて面積の小さいメモリセルを実現している。

#### 【0004】

【非特許文献1】アイ・イー・イー・イー、インターナショナル・ソリッドステート・サークル・コンファレンス、ダイジェスト・オブ・テクニカル・ペーパーズ、第202頁から第203頁（2002年）（2002 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 202-203.）

10

#### 【0005】

【非特許文献2】アイ・イー・イー・イー、インターナショナル・エレクトロン・デバイシズ・ミーティング、テクニカル・ダイジェスト、第923頁から第926頁（2002年）（2002 IEEE International Electron Devices Meeting, Technical Digest, pp. 923-926.）

【非特許文献3】ノンボラタイル・セミコンダクタ・メモリ・ワークショップ、ダイジェスト・オブ・テクニカル・ペーパーズ、第91頁から第92頁（2003年）（2003 Non-Volatile Semiconductor Memory Workshop, Digest of Technical Papers, pp. 91-92.）

#### 【特許文献1】特開2003-100084号公報

#### 【特許文献2】特開2003-229537号公報

#### 【発明の開示】

20

#### 【発明が解決しようとする課題】

#### 【0006】

背景技術で述べた相変化抵抗と縦型トランジスタで構成されるメモリセルの面積は $4F^2$ であり、汎用DRAMの $8F^2$ とくらべて半分程度である。しかし、パソコンなどに広く使用されるハードディスク装置のような記憶装置と比べると、ビットあたりの単価が約1桁程度高い。ここで、Fは最小加工寸法である。

本発明が解決しようとする課題は、例えば実効的に、メモリセルの更なる高集積化を実現したり、あるいは実効的に製造プロセスを単純にすることによって、ビット単価を低減することである。

#### 【課題を解決するための手段】

30

#### 【0007】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

縦型トランジスタと、その上方または下方に与えられる温度によりその抵抗値が変化する記憶素子で構成されるメモリセルを有するメモリブロックを積層させ、高集積な不揮発メモリを形成する。

#### 【発明の効果】

#### 【0008】

本発明によれば、高集積の不揮発メモリを実現できる。

#### 【発明を実施するための最良の形態】

40

#### 【0009】

以下、本発明に係わる半導体記憶装置の好適ないくつかの事例につき、図面を用いて説明する。特に断りのない場合、信号のロウレベルを‘L’、ハイレベルを‘H’とする。

#### 【実施例1】

#### 【0010】

#### <平面図および断面図>

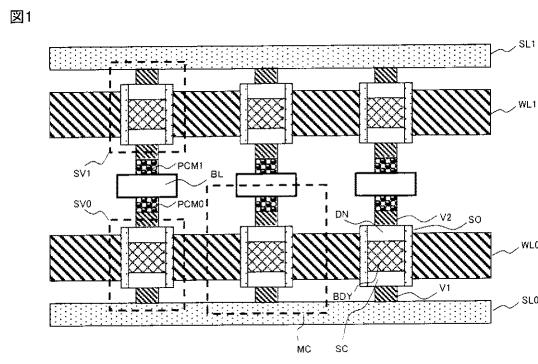

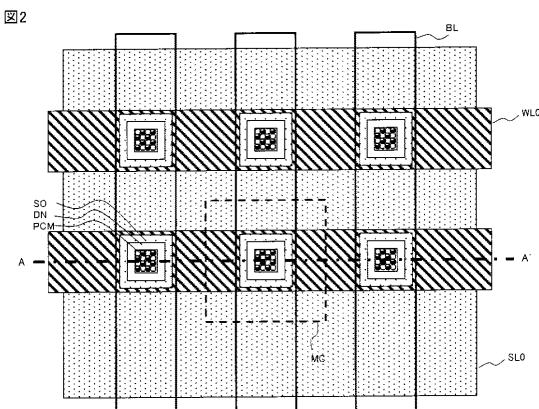

図1は、本発明に関わるメモリの断面図を示す。図2は図1のメモリのビット線BLから下の部分の平面図を示している。図1は図2の平面図のA-A'断面に相当する。図1、図2では、メモリセルMCを、ワード線WL方向に3セル、ビット線BL方向に2セル並べ、さらに縦方向に2層重ねた構成が示されている。ビット線BLとワード線WLが最小ピッチ2Fで配置されて

50

いるので、各層のメモリセルの面積は4F<sub>2</sub>であるが、これを2層重ねることにより、実効的なセルサイズを2F<sub>2</sub>とすることができる、従来方式に比べ、更なる高集積化を実現することができる。

#### 【0011】

メモリの第1層目は、第1の配線で形成されたソース電極プレートSL0の上に、縦型トランジスタSV0と記憶素子である相変化抵抗PCM0、ビット線BLが形成された構造である。メモリの第2層目は、第1層目のビット線BLを共有し、この上に、相変化抵抗PCM1と縦型トランジスタSV1、ソース電極プレートSL1が形成された構造である。V2は相変化抵抗PCMと縦型トランジスタSV1をつなぐビアであるが、取り除いた構成とすることも可能である。また、本実施例ではSLはプレートで形成されているが、ライン形状で形成することも可能である。縦型トランジスタSV1はチャネル部BDY、不純物拡散層であるソース層SCとドレイン層DN、ゲート酸化膜SOから構成される。縦型トランジスタSV1は第2の配線で形成されるワード線WLに囲まれており、ワード線WLは縦型トランジスタSV1のゲート電極となっている。第2の配線はポリシリコンで形成してもいいし、金属層とすることも可能である。

10

#### 【0012】

ソース層SCはビア層V1を介してソース電極プレートSLに接続され、ドレイン層DNはビア層V2を介して相変化抵抗PCMに接続される。ビア層V2は、タングステンやポリシリコンなどで形成される。この縦型トランジスタSV1は縦型Nチャネル型MOSトランジスタでも縦型Pチャネル型MOSトランジスタでもどちらでも良い。縦型Nチャネル型MOSトランジスタを使用する場合には、不純物拡散層(SC、DN)に、不純物としてリンを $10^{20}/\text{cm}^3$ 程度の高濃度にドープしたN+層を用い、チャネル部BDYには不純物としてボロンが $10^{16}/\text{cm}^3$ 程度の不純物層を用いる。ゲート酸化膜SOの膜厚は、2nm-3nm程度を用いる。チャネル部BDYは、アモルファスシリコン膜を堆積させたあとアニールを600 -750 で2分-12時間行う。これにより多結晶化し、オン電流を増加させることができる。またレーザーアニールを使うことにより低温でのアニールも可能である。

20

#### 【0013】

##### <相変化抵抗>

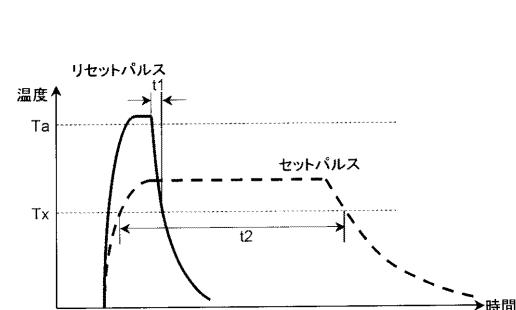

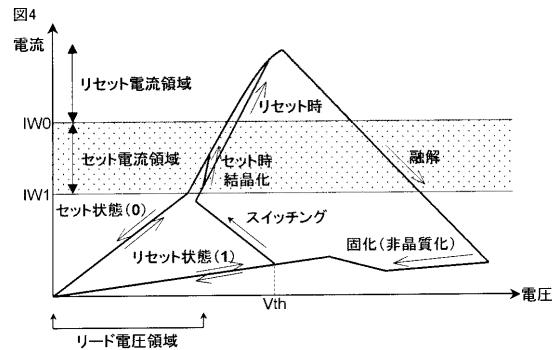

相変化抵抗は、アンチモン(Sb)とテルル(Te)を含むGe-Sb-Te系や、Ag-In-Sb-Te系などのカルコゲナイト材料を用いる。この記憶素子である相変化抵抗に記憶情報‘1’を書き込む場合、図3に示すように、抵抗素子をカルコゲナイト材料の融点Ta以上に熱してから急冷するようなリセットパルスを印加する。リセットパルスを短くして与えるエネルギーを小さくし、冷却時間t1を短く、例えば約1nsに設定することにより、カルコゲナイト材料は高抵抗のアモルファス状態となる。逆に、記憶情報‘0’を書き込む場合、相変化抵抗を融点よりも低く、ガラス転移点と同じかそれよりも高い結晶化温度Txより高い温度領域に保つようなセットパルスを印加する。カルコゲナイト材料は低抵抗の多結晶状態となる。結晶化に要する時間t2はカルコゲナイト材料の組成や温度によって異なるが、例えば、約50nsである。同図に示した素子の温度は、記憶素子自身が発するジュール熱、および周囲への熱拡散に依存する。したがって、図4のI-V特性に示すように、書き込み情報に応じた値の電流パルスを記憶素子に印加することにより、記憶素子の結晶状態が制御される。同図は、カルコゲナイト材料を用いた記憶素子の動作原理を模式的に示しており、IW1からIW0の範囲内のセット電流を印加する場合に記憶情報‘0’が書き込まれ、IW0以上のリセット電流を印加する場合に記憶情報‘1’が書き込まれることを示している。ただし、どちらの状態を‘0’、どちらの状態を‘1’としても良い。以下では、同図に従い、四通りの書き込み動作を詳しく説明する。

30

#### 【0014】

第1に、初期状態‘0’の記憶素子に‘0’書き込みを行う場合、セット電流が印加されると、セット(結晶)状態の低抵抗曲線を辿って初期状態とセット領域との間を往復するので、状態が保持される。第2に、初期状態‘0’の記憶素子に‘1’書き込みを行う場合、リセット電流が印加されると、セット状態の低抵抗曲線を辿ってリセット電流に達する。次に、ジュール熱により部分的に融解が始まるので、導電率が徐々に下がる。さらに、

40

50

融解が進むと高抵抗状態になる。液相の記憶素子を急冷すると、アモルファス状態に相変化するので、液相時の抵抗よりも若干低いリセット（非晶質）状態の高抵抗曲線を辿って初期状態に戻る。第3に、初期状態‘1’の記憶素子に‘0’書き込みを行う場合、セット電流を印加すると、記憶素子の端子電圧がしきい電圧Vthを超えた時に、低抵抗状態にスイッチする。スイッチング後は、ジユール熱によって結晶化が進行する。電流値がセット電流に達すると、結晶化領域が広がって相変化することにより、さらに抵抗値が下がるので、低抵抗曲線を辿って初期状態に戻る。第4に、初期状態‘1’の記憶素子に‘1’書き込みを行う場合、前述したスイッチング後に結晶化し、スイッチングしたことによる低抵抗曲線を辿ってリセット領域に達し、融解、急冷、固化して初期状態に戻る。

## 【0015】

10

このような記憶素子の動作原理から、読み出し時には記憶情報を破壊しないようにするために、最高でもしきい電圧Vthより低い電圧に抑制しながら動作しなければならない。実際には、しきい電圧Vthは読み出し時や書き込み時の電圧印加時間にも依存し、時間が長いと低下する傾向があるため、読み出し時間内にしきい電圧を越えて低抵抗状態へのスイッチングが起こらない電圧にする必要がある。

## 【0016】

## &lt;メモリブロック構成&gt;

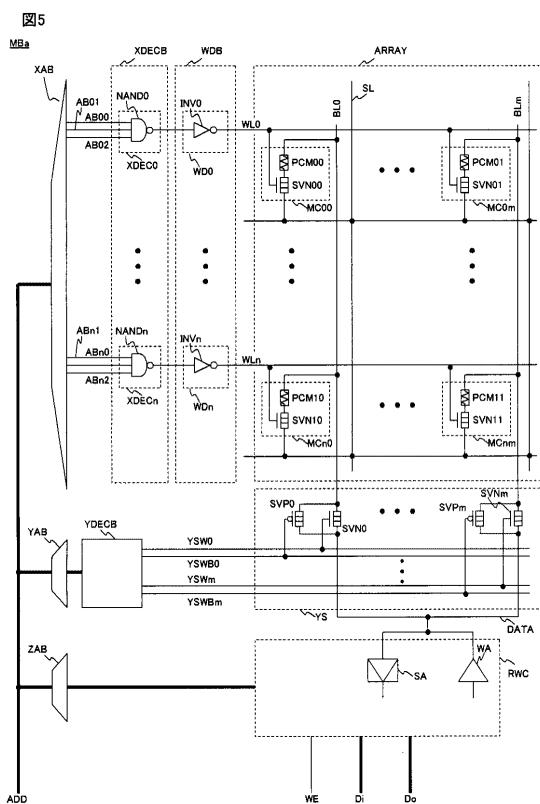

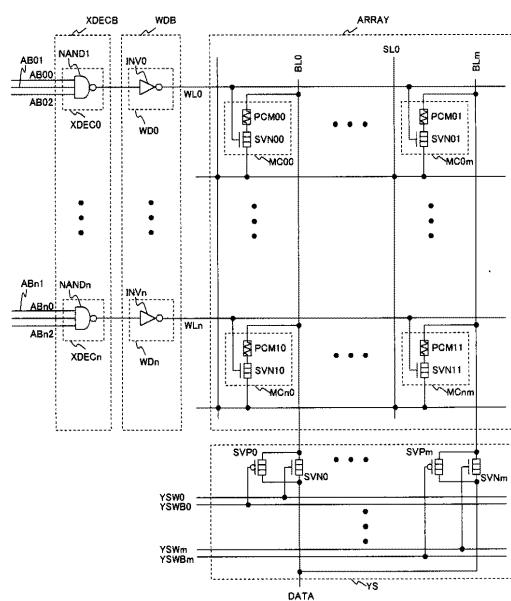

たとえば図1で示したメモリアレイの1つの層であるメモリブロックMBaについて図5を用いて詳細に説明する。メモリアレイARRAYは、複数のワード線WLと複数のビット線BLとメモリアレイを覆うソース電極プレートSLから構成されており、ワード線WLとビット線BLの交点にメモリセルMCが接続されている。ソース電極プレートSLはプレートで構成されるが、図5の回路図では便宜的にメッシュ状の配線で示した。各メモリセルMCは、メモリセルMC00で例示されているように縦型のNチャネル型MOSトランジスタSVN00と記憶素子PCM00で構成される。記憶素子PCM00は、例えば相変化抵抗と呼ばれる素子であり、例えば、結晶状態では1K ~ 10K 程度の低い抵抗で、アモルファス状態では100K 以上の高い抵抗であることを特徴とする素子である。縦型Nチャネル型MOSトランジスタSVN00のゲート電極には、ワード線WL0が接続され、縦型Nチャネル型MOSトランジスタを選択状態ではオン状態に、非選択状態ではオフ状態となるように制御する。PCM00の一方の端子がビット線に接続され、SVN00のソース電極がソース電極プレートSLに接続される。

20

## 【0017】

30

ワード線WLには、ワードドライバ回路(WD0, ..., WDn)が接続されている。例えば、ワードドライバ回路WD0は、縦型Pチャネル型MOSトランジスタと縦型Nチャネル型MOSトランジスタからなるインバータ回路INV0で構成される。このワードドライバ回路(WD0, ..., WDn)は縦方向に並べられてワードドライバブロックWDBを形成する。また、ワードドライバブロックWDBの隣には、X系アドレスデコーダ(XDEC0, ..., XDECn)からなるX系アドレスデコーダブロックXDECBが置かれている。

## 【0018】

例えばX系アドレスデコーダXDEC0は、縦型Pチャネル型MOSトランジスタと縦型Nチャネル型MOSトランジスタからなる3入力NAND0 NAND回路で構成され、アドレス信号(AB00, A B01, AB02)によりワード線WL0を選択する。このアドレス信号はX系アドレスパッファブロックXABから入力される。

40

ビット線(BL0, ..., BLm)には、カラム選択回路YSが接続されている。例えば、ビット線BL0は縦型Pチャネル型MOSトランジスタSVP0と縦型Nチャネル型MOSトランジスタSVN0に接続されており、制御信号(YSW0, YSWB0)により選択的にデータ線DATAと接続される。アクセススピードを気にしない場合は、縦型Pチャネル型MOSトランジスタSVP0か縦型Nチャネル型MOSトランジスタSVN0どちらか一方のみとしてもよい。制御信号YSWはY系アドレスデコーダブロックYDECBにより生成される。Y系アドレスデコーダブロックYDECにはY系アドレスパッファブロックYABからアドレス信号が与えられる。

## 【0019】

読み出し・書き込み回路RWCは、センスアンプ回路SAとライトアンプ回路WAから構成される

50

。センスアンプ回路SAは、活性化信号で活性化されデータ線DATAの信号を増幅する。ライトアンプ回路WAは、活性化信号で活性化され書き込みデータをデータ線DATAへ出力する。メモリブロック層を選択するZ系アドレスは、Z系アドレスバッファブロックZABを通って読み出し・書き込み回路RWCへ送られる。メモリブロック層が選択された場合に、読み出し時にはデータをD<sub>0</sub>に出力し、書き込み時にはデータをD<sub>i</sub>より取り込む。読み出し・書き込み回路RWCには書き込み制御信号であるWEも入力される。また、ここで使用されるメモリセルMCは、図1および図2で示した以外の構造とすることも可能である。

#### 【0020】

メモリブロックMBaは、縦型MOSトランジスタと記憶素子およびこれらを接続する配線のみで構成されるため、ポリシリコン層や配線層、記憶素子層のみで作ることが可能である。10 配線層にタングステンやポリシリコン層を使った場合には、すべての層の形成が、600度以下で可能であり、さらにこれらの層は600度以上の耐熱性を持っている。このため、従来のシリコン基板上にCMOSを使って構成するメモリと異なり、何層も積み上げて集積度を上げることが可能である。

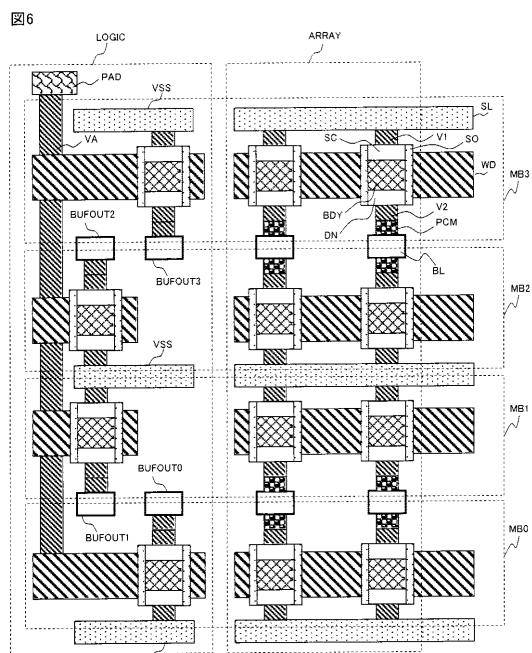

#### 【0021】

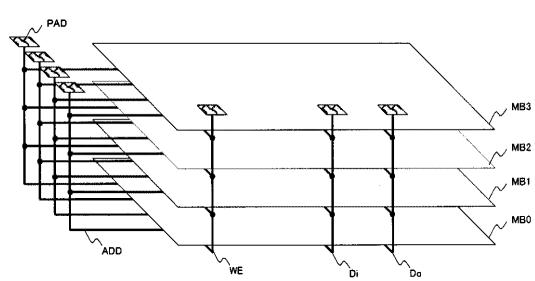

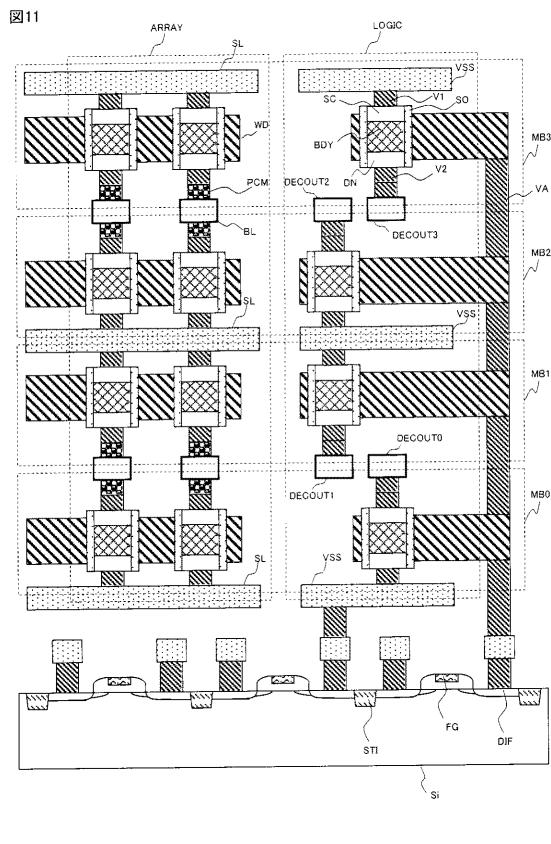

メモリブロックMBaを4層(MB0、MB1、MB2、MB3)シリコン基板Si上に積み上げた場合の断面図を図6に示した。各メモリブロック層MBではメモリセルサイズは4F<sub>2</sub>であるが、4層積層することにより、実効的なセルサイズを1F<sub>2</sub>とすることができる、DRAMに比べ8倍の集積度を実現できる。この結果ハードディスク装置に匹敵するピット単価を実現できる。

各メモリブロック層(MB0、MB1、MB2、MB3)は、それぞれメモリアレイARRAY部分とワードドライバなどの周辺回路LOGIC部よりなる。また、メモリブロック層(MB0、MB1、MB2、MB3)とは別にアドレスADDを入力する入力PADが最上層に形成され、入力されたアドレスADDはメモリブロック層を縦に貫通する配線VAによって各層のゲートへ入力される。図6に示した周辺回路LOGIC部は、アドレスバッファブロックABの一部を示している。20

#### 【0022】

周辺回路LOGIC部で使われる縦型トランジスタは、メモリセル部で使われるトランジスタと同一であるが、記憶素子PCMの部分がビアV2で置き換えられている。MB1とMB3はMB0とMB2を上下逆にした構成となっており、MB0とMB1はピット線BLを共有している。MB1とMB2はソース電極プレートSLを共有しており、MB2とMB3は同様にピット線BLを共有している。従って製造プロセスが簡単になり低価格にできる。30

ピット線BLを上下のメモリブロック層MBで共有するため、選択されたメモリブロック層MBのワード線WLのみを活性化する必要があるが、これはZ系アドレスバッファブロックZABの出力信号とX系をX-DECに入力させアンドをとることにより容易に実現できる。

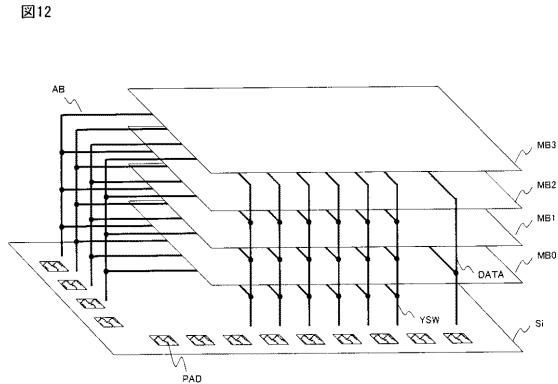

鳥瞰図を図7に示した。アドレスADDや書き込み制御信号WE、データ(D<sub>i</sub>、D<sub>0</sub>)の配線数は、メモリの集積度や構成により、別の構成とすることも可能である。

#### 【0023】

##### <動作方式>

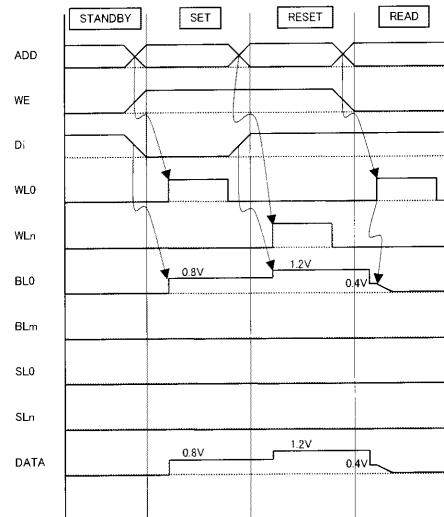

次に、図8を用いて詳細な動作について説明する。電源電圧は例えば1.2Vである。はじめは待機状態STANDBYにあり、アドレスADDが切り替わり、書き込み制御信号WEが‘H’になると書き込み動作が始まる。はじめは、‘0’をメモリセルMC00に書き込むSET動作について説明する。書き込みデータD<sub>i</sub>が‘L’となり、カラム選択回路YSや読み出し・書き込み回路RWCによりピット線BL0が駆動される。これと同時にX系アドレスデコーダXDEC0やワードドライバ回路WD0によりワード線WL0が選択される。本実施例におけるSET動作では、ピット線BL0に0.8Vが供給され、ソース線SL0が0Vに保たれ、素子が高抵抗化している場合には、数マイクロ程度の電流が流れ続ける。この電圧差は電源電圧より小さい値としてもよいし、大きい値としてもよい。この状態を100ナノ秒から数マイクロ秒続けることにより記憶素子PCM00は結晶化し低抵抗化する。一方あらかじめ低抵抗化している素子にも同様の電圧が印加される。また、非選択のピット線BLmは、図示しない回路により、接地電位に設定している。40

#### 【0024】

10

20

30

40

50

書込みが終了するとワード線WL0がゆっくりと‘H’から‘L’へ遷移しSET動作が終了する。続いて‘1’をメモリセルMCn0に書込むRESET動作について説明する。アドレスが変わり、書込みデータDiが‘H’となり、カラム選択回路YSや読み出し・書込み回路RWCによりビット線BL0が駆動される。これと同時にX系アドレスデコーダXDECnやワードドライバ回路WDnによりワード線WL<sub>n</sub>が選択される。RESET動作では、たとえばビット線BL0の電位が1.2Vで、ソース線SL0が0Vに保たれ、素子が低抵抗化している場合には、数十マイクロアンペア程度の電流がビット線BL0からソース線SL0へ流れ続ける。この状態を5ナノ秒から数十ナノ秒続けることにより素子は溶融状態となる。この後ワード線WL<sub>n</sub>を‘H’から‘L’へ遷移させ、素子に印加される電圧を急激に下げる急冷する。この急冷により記憶素子PCM10 0はアモルファス化し高抵抗となる。一方、あらかじめ高抵抗化している素子にも同様の電圧が印加される。このとき素子には数マイクロアンペア以上の電流が流れることになる。ただし、この時間が数10ナノ秒程度であれば素子の抵抗は変化せず、問題とはならない。また、非選択のビット線BLmは、図示していないが、接地電位に接続されている。

#### 【0025】

次に読み出し動作であるREAD動作について、メモリセルMC00から書込んだデータ‘0’を読み出す場合について説明する。アドレスADDが変わり、書込み制御信号WEが‘L’になると読み出し動作が始まる。カラム選択回路や読み出し・書込み回路RWCによりビット線BL0とデータ線DATAを例えば0.4Vにプリチャージする。この後X系アドレスデコーダXDEC0やワードドライバ回路WD0によりワード線WL0を‘L’から‘H’に活性化し、ビット線BL0から電流をソース線SL0に向かって流す。メモリセルMC00には低抵抗の値が書き込まれているので、ビット線BL0およびデータ線DATAはディスチャージされ0Vとなる。もしメモリセルMC00に高抵抗の値が書き込まれていれば、ビット線BL0はほとんど変化せず0.4Vが保持される。この電圧の違いを読み出し・書込み回路RWCにより増幅・検知し、検知したデータをD0へ出力し読み出しが終了する。増幅を行うためには、例えば0.2V程度のリファレンス電圧を作り、低抵抗の読み出しを行った場合は0Vと0.2Vの差を増幅しデータ‘0’を出力する。高抵抗の読み出しを行った場合は0.2Vと0.4Vの差を増幅しデータ‘1’を出力する。また、非選択のビット線BLmは、接地電位と接続されている。

書込み時にビット線電圧として必要な0.4Vと0.8Vや、読み出し時にリファレンス電圧として必要な0.2Vは、電圧コンバータを用いて発生させる。電圧コンバータは既知の技術であり、リファレンス電圧を発生する回路と電圧を出力する回路で構成される。

#### 【実施例2】

#### 【0026】

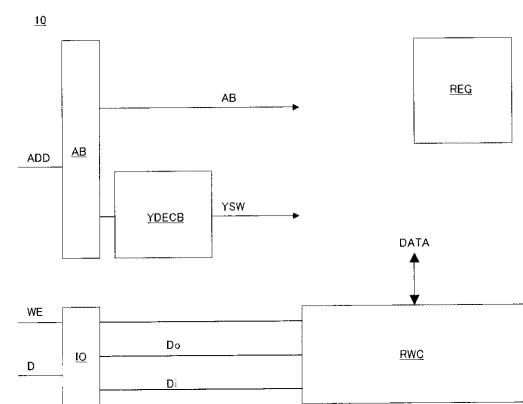

実施例1では、縦型MOSトランジスタのみで構成されるメモリブロック層を積層したが、メモリブロック層の一部の回路をシリコン基板Si上に置くことも可能である。本実施例では、シリコン基板SiにアドレスバッファブロックABやY系アドレスデコーダブロックYDECB、読み出し・書込み回路RWCを置いた場合について説明する。なおZ系の回路はここではY系と一緒にした構成である。

メモリブロック層MBbの詳細な回路図を図9に示した。メモリブロック層MBbは、実施例1で示したメモリブロック層から、間接周辺回路を取り去り、メモリアレイARRAYとX系アドレスデコーダブロックXDECB、ワードドライバブロックWDB、カラム選択回路YSのみで構成される。すべての回路は、縦型トランジスタを用いて形成される。

#### 【0027】

このメモリブロック層MBbをシリコン基板Siに4層(MB0、MB1、MB2、MB3)積層し、シリコン基板Siには、周辺回路を通常のCMOSトランジスタで形成する。各メモリブロック層MBbではメモリセルサイズは4F<sup>2</sup>であるが、4層積層することにより、実効的なセルサイズを1F<sup>2</sup>とことができ、DRAMに比べ約8倍の集積度を実現できる。この結果ハードディスク装置に匹敵するビット単価を実現できる。

#### 【0028】

シリコン基板Siに形成される回路は、図10に示したように、アドレスバッファブロックAB、入出力回路IO、Y系アドレスデコーダブロックYDECB、読み出し・書込み回路RWC、電圧

10

20

30

40

50

コンバータREGなどである。アドレスバッファブロックABには、外部よりアドレスADDが入力される。入出力回路IOには、外部より書き込み制御信号WE、データDが入力される。アドレスバッファブロックABからはアドレス信号ABが、YDECBからは制御信号YSWが、RWCからはデータ線DATAが、各メモリブロック層(MB0、MB1、MB2、MB3)に入力される。

#### 【0029】

図11は、本半導体記憶装置の断面図である。シリコン基板Si上に4つのメモリブロック層(MB0、MB1、MB2、MB3)が積層されており、各層はメモリアレイARRAYと周辺回路LOGICにより構成される。シリコン基板Siには通常のMOSトランジスタが形成されている。MOSトランジスタは、素子分離層STIで分離されており、ゲート電極FGとソース電極やゲート電極を構成する拡散層DIFにより構成される。各メモリブロックMB層には、縦に貫通するビアVAを通して、シリコン基板Siからの信号が入力される。

10

この鳥瞰図を図12に示した。アドレス信号ABや制御信号YSW、データDATAの配線数は、メモリの集積度や構成により異なる。

#### 【実施例3】

#### 【0030】

##### <平面図および断面図>

実施例1で示した縦型トランジスタは、チャネル部BDYに給電がないためフローティングとなり電位が不安定で、トランジスタのしきい値が変化するヒストリー効果が問題となる。そこで、縦型トランジスタのチャネル部に給電を行う例について説明する。

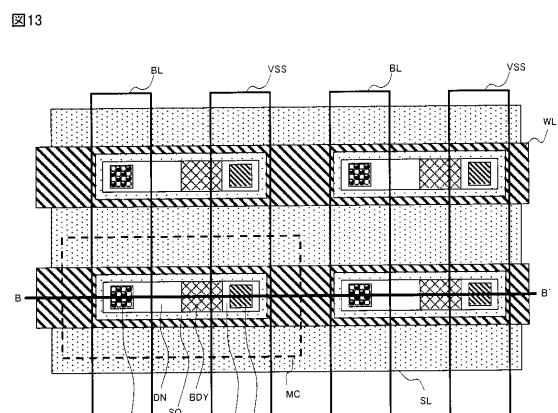

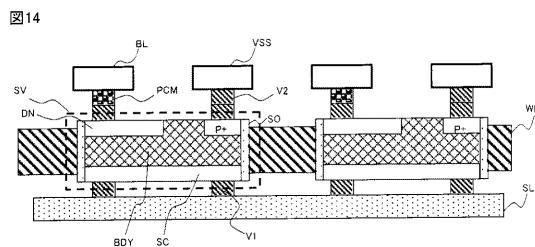

図13は、本実施例のメモリアレイの平面図を示す。メモリアレイはワード線WL方向に2セル、ピット線BL方向に2セルが示されている。ワード線WLとピット線BLの交点に縦型トランジスタと記憶素子からなるメモリセルMCが置かれている。ピット線BLがピッチ4Fでワード線WLがピッチ2Fで配置されているので、メモリセルの面積は8F<sup>2</sup>と実施例1の時と比べて2倍となる。平面図のB-B'で切った断面図を図14に示す。第1の配線でソース電極プレートSLが、その上に縦型トランジスタSVと記憶素子である相変化抵抗PCMが形成される。

20

#### 【0031】

縦型トランジスタSVはチャネル部BDY、不純物拡散層であるソース層SCとドレイン層DN、ゲート酸化膜SO、給電拡散層P+から構成される。縦型トランジスタSVは第2の配線で形成されるワード線WLに囲まれており、ワード線WLは縦型トランジスタSVのゲート電極配線となっている。ソース層SCはビア層V1を介してソース線SLに接続され、ドレイン層DNはビア層V2を介して相変化抵抗PCMに接続される。相変化抵抗は、ピット線BLにも接続されている。給電拡散層P+は、ビアV2を介して接地電位線VSSに接続される。この縦型トランジスタSVは縦型Nチャネル型MOSトランジスタでも縦型Pチャネル型MOSトランジスタMPでも良い。縦型Nチャネル型MOSトランジスタを使用する場合には、不純物拡散層(SC、DN)に、不純物としてリンを10<sup>20</sup>/cm<sup>3</sup>程度の高濃度にドープしたN+層を用い、チャネル部BDYには不純物としてボロンが10<sup>16</sup>/cm<sup>3</sup>程度の不純物層を用いる。また、給電拡散層P+に、不純物としてボロンを10<sup>20</sup>/cm<sup>3</sup>程度の高濃度にドープしたP+層を用いる。

30

#### 【0032】

このような構成とすることにより縦型トランジスタのチャネル部BDY電位が固定され安定した電流を得ることができる。また、本方式ではピット線BLが接地電位線VSSによりシールドされており、ピット線BLへのノイズを低減することが可能である。このようなトランジスタはメモリセルだけでなく、センスアンプや電源回路のペアトランジスタにも有効である。

40

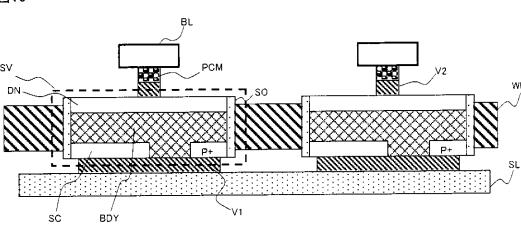

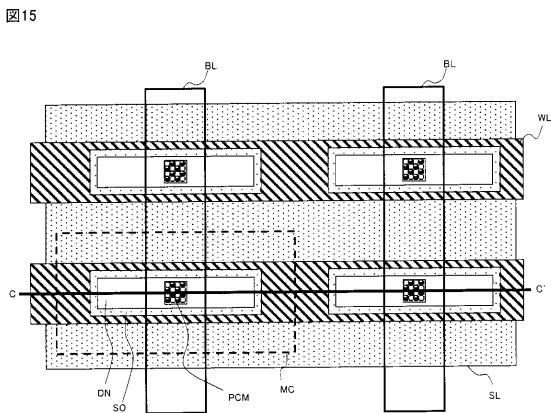

#### 【0033】

さらに、給電拡散層P+を縦型トランジスタSVの下側に形成して、VSSとSLと一緒にした構成を図15に示した。平面図のC-C'で切った断面図は図16に示した。

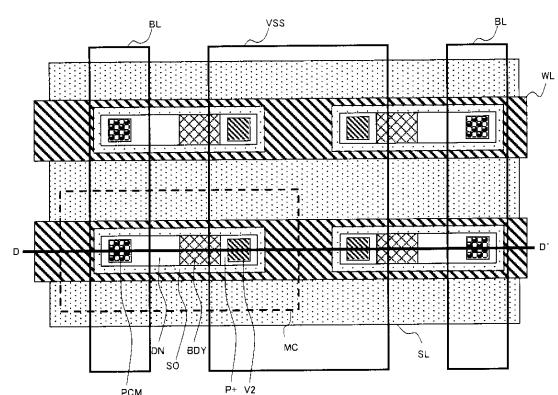

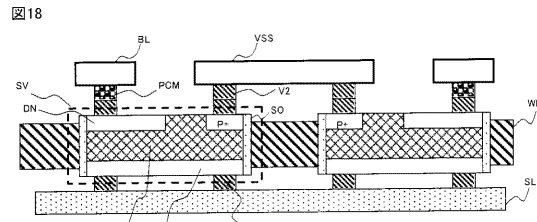

さらに、電源ノイズを低減するように変更したセルの例を図17に示した。平面図のC-C'で切った断面図は図18に示した。接地電位VSSが2つのセルで共有されている以外は、図13とほぼ同一構造である。

#### 【実施例4】

10

20

30

40

50

**【 0 0 3 4 】**

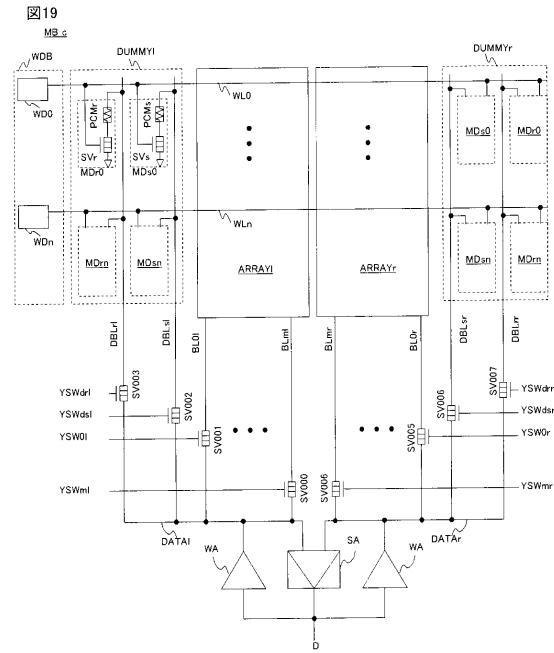

実施例1で示したメモリブロックMBを別の構成とした場合について、図19を用いて説明する。

**<メモリブロック構成>**

メモリブロックMBcのメモリアレイは、2つのメモリアレイ（ARRAYl、ARRAYr）に分割されている。各アレイは複数のワード線と複数のビット線により構成されており、ワード線とビット線の交点にメモリセルが接続されている。各メモリセルは、縦型のNチャネル型MOSトランジスタと記憶素子で構成される。記憶素子は、例えば相変化抵抗と呼ばれる素子である。

**【 0 0 3 5 】**

ワード線（WL0、WL<sub>n</sub>）には、ワードドライバ回路（WD0、WD<sub>n</sub>）が接続されている。ワードドライバ回路（WD0、WD<sub>n</sub>）はアレイに並べられてワードドライバブロックWDBを形成する。

メモリアレイ（ARRAYl、ARRAYr）の両サイドにはダミーアレイ（DUMMYl、DUMMYr）が配置される。各ダミーアレイ（DUMMYl、DUMMYr）は、2つのカラムからなり、1つのカラムは、ダミーセル（MDr0、…、MDr<sub>n</sub>）で構成され、もう1つのカラムはダミーセル（MDs0、…、MDs<sub>n</sub>）で構成される。

例えばダミーセルMDr0は、縦型のNチャネル型MOSトランジスタSV<sub>r</sub>と相変化抵抗PCM<sub>r</sub>で構成される。ダミーセルMDr0は、メモリアレイARRAYと同一のワード線WL0とダミービット線DBLrlに接続される。相変化抵抗PCM<sub>r</sub>には常に高抵抗が書き込まれる。

**【 0 0 3 6 】**

また、ダミーセルMDs0は、縦型のNチャネル型MOSトランジスタSV<sub>s</sub>と相変化抵抗PCMsで構成される。ダミーセルMDs0は、メモリアレイARRAYと同一のワード線WL0とダミービット線DBLlsに接続される。相変化抵抗PCMsには常に低抵抗が書き込まれる。

ダミービット線DBLrlは、縦型トランジスタSV003を介してデータ線DATAIに接続される。縦型トランジスタSV003のゲート電極には制御信号YSWdr<sub>l</sub>が接続される。ダミービット線DBLlsは、縦型トランジスタSV002を介してデータ線DATAIに接続される。縦型トランジスタSV002のゲート電極には制御信号YSWds<sub>l</sub>が接続される。

**【 0 0 3 7 】**

同様にダミービット線DBLrrは、縦型トランジスタSV007を介してデータ線DATArに接続される。縦型トランジスタSV007のゲート電極には制御信号YSWdrrが接続される。ダミービット線DBLsrは、縦型トランジスタSV006を介してデータ線DATArに接続される。縦型トランジスタSV006のゲート電極には制御信号YSWdsrが接続される。

また、メモリアレイARRAYlのビット線BL0<sub>l</sub>は、縦型トランジスタSV001を介してデータ線DATAIに、ビット線BLm<sub>l</sub>は、縦型トランジスタSV000を介してデータ線DATAIにそれぞれ接続される。縦型トランジスタSV001のゲート電極には制御信号YSW0<sub>l</sub>が接続され、縦型トランジスタSV000のゲート電極には制御信号YSWm<sub>l</sub>が接続される。

**【 0 0 3 8 】**

メモリアレイARRAYrのビット線BL0<sub>r</sub>は、縦型トランジスタSV005を介してデータ線DATArに、ビット線BLmrは、縦型トランジスタSV006を介してデータ線DATArにそれぞれ接続される。縦型トランジスタSV005のゲート電極には制御信号YSW0<sub>r</sub>が接続され、縦型トランジスタSV006のゲート電極には制御信号YSWmrが接続される。データ線（DATAI、DATAr）には、センサアンプ回路SAとライトアンプ回路WAが接続される。

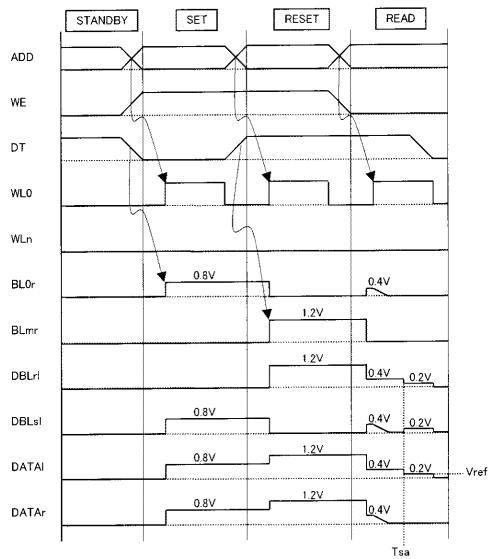

**【 0 0 3 9 】****<動作方式>**

次に、図20を用いて詳細な動作について説明する。基本的な動作は実施例1で示した方法とほとんど同じであるので、異なるところを主に説明する。電源電圧は例えば1.2Vである。はじめは待機状態STANDBYにあり、アドレスADDが切り替わり、書き込み制御信号WEが‘H’になると書き込み動作が始まる。ビット線BL0<sub>r</sub>とワード線WL0の交点に置かれているメモリセルMC00（図示されず）に‘0’を書き込み、ビット線BLmrとワード線WL0の交点に置かれ

10

20

30

40

50

ているメモリセルMC0m（図示されず）に‘1’を書込む場合について説明する。この書込みは同時に要求されるが、まず‘0’を書込むSET動作を行い、その後‘1’を書込むRESET動作を行う。まず、実施例1で示した方式でビット線BL0rとワード線WL0が選択される。このとき同時にダミービット線DBLsIも駆動される。本実施例におけるSET動作では、ビット線BL0rおよびダミービット線DBLsIに0.8Vが供給され、この状態を100ナノ秒から数マイクロ秒続けることによりメモリセルMC00とダミーセルMDs0の記憶素子はそれぞれ結晶化し低抵抗化する。

#### 【0040】

その後、ワード線WL0がゆっくりと‘H’から‘L’へ遷移しSET動作が終了する。続いて‘1’をメモリセルMC0mに書込むRESET動作について説明する。ビット線BLmrとワード線WL0が選択され、このとき同時にダミービット線DBLrIも駆動される。RESET動作では、たとえばビット線BLmrとダミービット線DBLrIの電位が1.2Vに保たれ、この状態を5ナノ秒から数十ナノ秒続けることにより素子は溶融状態となる。この後ワード線WLnを‘H’から‘L’へ遷移させ、素子に印加される電圧を急激に下げて急冷する。この急冷によりメモリセルMC0mとダミーセルMDr0の記憶素子はアモルファス化し高抵抗となる。

10

#### 【0041】

次に読み出し動作であるREAD動作について、メモリセルMC00から上記で書込んだデータ‘0’を読み出す場合について説明する。READ動作が始まると、Y系アドレスデコーダプロックYDECBや読み出し・書き込み回路RWCによりビット線BL0rとデータ線DATArを例えば0.4Vにプリチャージする。また同時にダミービット線(DBLrI、DBLsI)とデータ線DATAIも例えば0.4Vにプリチャージする。この後、ワード線WL0を‘L’から‘H’に活性化し、ビット線BL0rから電流を接地電位に向かって流す。メモリセルMC00には低抵抗の値が書き込まれているので、ビット線BL0およびデータ線DATArはディスチャージされ0Vとなる。もしメモリセルMC00に高抵抗の値が書き込まれていれば、ビット線BL0はほとんど変化せず0.4Vが保持される。一方ダミービット線(DBLrI、DBLsI)からも接地電位に向かって電流が流れる。

20

#### 【0042】

ダミーセルMDs0には低抵抗の値が書き込まれているので、ダミービット線DBLsIはディスチャージされ0Vとなる。ダミーセルMDr0には、高抵抗の値が書き込まれているので、ダミービット線DBLrIはほとんど変化せず0.4Vが保持される。ビット線およびダミービット線の電位が十分変化した時刻Tsa後、例えば10ナノ秒後、に縦型トランジスタ(SV003、SV002)をオンさせ、データ線DATAIを駆動する。データ線DATAIの電位は、ダミービット線DBLrIとミービット線DBLsIの中間電位、約0.2V程度となる。読み出し・書き込み回路RWCでは、データ線DATArとデータ線DATAIの電位差を増幅しデータをDへ出力し、読み出しが終了する。

30

#### 【0043】

メモリセルMC00には低抵抗の値が書き込まれているので、データ線DATArはディスチャージされ0Vとなり、一方データ線DATAIの電位はこれより高いので、電位差を増幅して‘0’が読み出される。もし、メモリセルMC00に高抵抗の値が書き込まれていれば、データ線DATArはほぼ0.4Vに維持され、データ線DATAIの電位はこれより低いので、電位差を増幅して‘1’が読み出される。

40

また、1つのメモリセルを2つの縦型トランジスタと2つの記憶素子で構成し、2つの記憶素子には常に逆のデータを入力しておく構成とすることもできる。2つの記憶素子で駆動される2本のビット線の電位差を増幅することにより、ダミー回路を不要とすることができる。

本方式は、メモリブロックを積層化しない構成のメモリやCMOSのみで構成したメモリにおいても有効である。

#### 【図面の簡単な説明】

#### 【0044】

【図1】メモリセルアレイの断面図である。

【図2】図1におけるメモリセルアレイの平面図である。

50

【図3】図1で使用される相変化抵抗の書き込み方式の概念図である。

【図4】図1で使用される相変化抵抗の特性を示す図である。

【図5】図1を含むメモリブロックの一つの実施例を示す回路図である。

【図6】図5のメモリブロックを積層したメモリチップの断面図である。

【図7】図6の鳥瞰図である。

【図8】図6に示すメモリチップの動作波形図である。

【図9】実施例2に関するメモリブロックの回路図である。

【図10】図9の基板に形成される回路のブロック図である。

【図11】図9のメモリブロックを積層したメモリチップの断面図である。

【図12】図11の鳥瞰図である。

10

【図13】実施例3に関するメモリセルアレイの平面図である。

【図14】図13におけるメモリセルアレイの断面図である。

【図15】実施例3に関する別のメモリセルアレイの平面図である。

【図16】図15におけるメモリセルアレイの断面図である。

【図17】実施例3に関する別のメモリセルアレイの平面図である。

【図18】図18におけるメモリセルアレイの断面図である。

【図19】実施例4に関するメモリブロックの回路図である。

【図20】図19に示すメモリブロックの動作波形図である。

【符号の説明】

【0045】

20

AB.....アドレスバッファブロック、ADD.....アドレス、ARRAY.....メモリアレイ、BD

Y.....チャネル部、BL.....ビット線、BUFOUT.....アドレスバッファ出力、D.....データ、DATA.....データ線、DBL.....ダミービット線、DECOUT.....デコーダ出力、DIF

.....拡散層、DN.....ドレイン層、DUMMY.....ダミーアレイ、FG.....ゲート電極、I

0.....入出力回路、INV.....インバータ回路、LOGIC.....周辺回路、MB.....メモリ

ブロック層、MC.....メモリセル、MD.....ダミーセル、MN.....Nチャネル型MOSトラン

ジスタ、MP.....Pチャネル型MOSトランジスタ、NAND..... NAND回路、P+.....給電拡

散層、PCM.....相変化抵抗、R.....抵抗、REG.....電圧コンバータ、RWC.....読み出し

・書き込み回路、SA.....センスアンプ回路、SC.....ソース層、Si.....シリコン基板、

SL.....ソース電極プレート、S0.....ゲート酸化膜、STI.....素子分離層、SV.....

縦型トランジスタ、SVN.....縦型Nチャネル型MOSトランジスタ、SVP.....縦型Pチャネ

ル型MOSトランジスタ、t1.....冷却時間、t2.....結晶化に要する時間、Ta.....融点

、Tx.....結晶化温度、V、VA.....ビア層、VSS.....接地電位線、Vth.....しきい電

圧、WA.....ライトアンプ回路、WD.....ワードドライバ回路、WDB.....ワードドライ

バブロック、WE.....書き込み制御信号、WL.....ワード線、XAB.....X系アドレスバッ

ファブロック、XDEC.....X系アドレスデコーダ、XDECB.....X系アドレスデコーダブロ

ック、YAB.....Y系アドレスバッファブロック、YDECB.....Y系アドレスデコーダブロ

ック、YS.....カラム選択回路、YSW.....制御信号、ZAB.....Z系アドレスバッファブ

ロック。

30

【 図 1 】

【図2】

【 図 5 】

【図3】

【図4】

【 四 6 】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

【図20】

图20

---

フロントページの続き

(56)参考文献 国際公開第03/065377(WO,A1)

特開2003-229537(JP,A)

国際公開第03/085675(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 27/105

H01L 21/8246

H01L 27/10